(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2015-18564

(P2015-18564A)

(43) 公開日 平成27年1月29日(2015.1.29)

(51) Int.Cl.

**G06F 3/00** (2006.01)

**G06F 13/38** (2006.01)

**G06F 13/36** (2006.01)

F 1

GO6F 3/00

GO6F 13/38 350

GO6F 13/36 520C

テーマコード (参考)

5B061

5B077

審査請求 有 請求項の数 20 O L 外国語出願 (全 54 頁)

(21) 出願番号 特願2014-165486 (P2014-165486)

(22) 出願日 平成26年8月15日 (2014.8.15)

(62) 分割の表示 特願2013-554620 (P2013-554620)

原出願日 平成24年2月16日 (2012.2.16)

(31) 優先権主張番号 13/029,934

(32) 優先日 平成23年2月17日 (2011.2.17)

(33) 優先権主張国 米国(US)

(71) 出願人 595020643

クアアルコム・インコーポレイテッド

QUALCOMM INCORPORATED

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100103034

弁理士 野河 信久

(74) 代理人 100075672

弁理士 峰 隆司

最終頁に続く

(54) 【発明の名称】検出されたエラーレートに応じたSerDes電力調節

(57) 【要約】 (修正有)

【課題】SerDes(直列化器/並列化器)インターフェースを低電力モバイルデバイスに対してより適切にする節電技術を提供する。

【解決手段】第1の集積回路(I.C.)から第2のI.C.までの第1のSerDesリンク31と、第2のI.C.から第1のI.C.までの第2のリンク35において、第1のリンクの回路内の消費電力設定が、第1のリンクのビットエラーレートがある範囲内に維持されるように消費電力を制御するように調整され、範囲の下限は実質的にゼロより大きい。第2のリンクに対する回路内の消費電力設定が、第2のリンクのビットエラーレートが範囲内に維持されるように消費電力を制御するように調整され、範囲の下限は実質的にゼロより大きい。第2のI.C.内の回路が第1のリンク内のエラーを検出し、第2のリンクを介して報告を返す。第1のI.C.は、第1のリンクに対するビットエラーレートを決定するために、報告された情報を使用する。

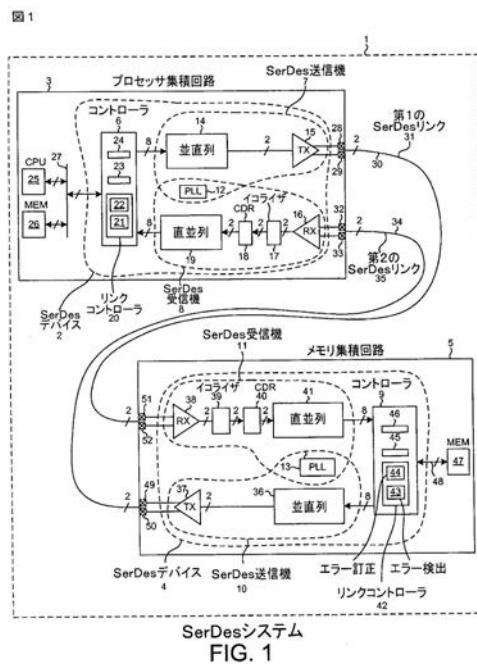

【選択図】図1

**【特許請求の範囲】**

**【請求項 1】**

SerDes(直列化器／並列化器)リンクを介した情報の通信においてSerDes回路を使用することであって、前記SerDes回路が、前記SerDesリンクを介して情報を送信するSerDes送信機と、前記SerDesリンクから情報を受信するSerDes受信機とからなる群から得られることと、

前記SerDesリンクのエラーレートが、実質的にゼロより大きいエラーレート下限とエラーレート上限との間に実質的に維持されるように、前記SerDes回路の消費電力を制御することとを備え、前記制御することが行われる間、前記消費電力があるときは増大され、またあるときは低減される、方法。10

**【請求項 2】**

SerDes(直列化器／並列化器)リンクを介して情報を通信するように適合されたSerDes回路に動作可能に結合されたコントローラを備え、前記SerDesリンクのエラーレートが実質的にゼロより大きいエラーレート下限とエラーレート上限との間に実質的に維持されるように前記SerDes回路の消費電力を制御するように前記コントローラが適合され、前記制御することが行われる間、前記消費電力があるときは増大され、またあるときは低減される、装置。

**【請求項 3】**

前記コントローラが第1のSerDesデバイスの一部であり、前記SerDes回路が第2のSerDesデバイスの一部であり、前記SerDesリンクが前記第1のSerDesデバイスと前記第2のSerDesデバイスとの間に延在する、請求項2に記載の装置。20

**【請求項 4】**

前記コントローラおよび前記SerDes回路が第1のSerDesデバイスの一部であり、前記SerDesリンクが前記第1のSerDesデバイスと第2のSerDesデバイスとの間に延在する、請求項2に記載の装置。

**【請求項 5】**

(a) SerDes(直列化器／並列化器)リンクのエラーレートを決定することであって、前記SerDesリンクを介して進む情報がSerDes受信機によって受信されることと、30

(b) 前記エラーレートが実質的にゼロより大きいエラーレート下限とエラーレート上限との間に実質的に維持されるように前記SerDes受信機の消費電力設定を制御することとを備え、(b)の前記制御することが、

前記エラーレートが前記エラーレート下限を下回っていると判断される場合、前記エラーレートが増加して実質的に前記エラーレート下限以上になるように、前記消費電力設定を前記SerDes受信機の消費電力が低減されるように調整することと、

前記エラーレートが前記エラーレート上限を上回っていると判断される場合、前記エラーレートが減少して実質的に前記エラーレート上限以下になるように、前記消費電力設定を前記SerDes受信機の前記消費電力が増加するように調整することとを伴い、(b)の前記制御することが行われる間、あるときは前記消費電力が増大され、またあるときは低減される、方法。40

**【請求項 6】**

(a) の前記決定することおよび(b)の前記制御することが、電池式モバイル通信デバイス内で行われ、前記SerDesリンクが前記電池式モバイル通信デバイス内に配設される、請求項5に記載の方法。

**【請求項 7】**

前記SerDesリンクが、電池式モバイル通信デバイス内の第1の集積回路から前記電池式モバイル通信デバイス内の第2の集積回路まで延在する、請求項5に記載の方法。

**【請求項 8】**

(a) の前記決定することおよび(b)の前記制御することが前記SerDes受信機50

を含む第1の集積回路によって実行され、前記SerDesリンクを介して進む前記情報が、第2の集積回路の一部であるSerDes送信機から受信され、前記第1の集積回路が中央処理装置(CPU)を含み、前記第2の集積回路がメモリを含み、前記方法が、

前記SerDesリンクの前記SerDes受信機を使用して前記第2の集積回路の前記メモリにアクセスすることをさらに備え、前記第1の集積回路の前記CPUが前記アクセスすることを実行する、請求項5に記載の方法。

#### 【請求項9】

(a)の前記決定することおよび(b)の前記制御することが集積回路によって実行され、前記集積回路が前記SerDes受信機を含み、(a)の前記決定することが、

データ部分とエラー検出コード部分とを含む情報を前記SerDes受信機を介して受信することと。10

前記エラー検出コード部分を使用して前記データ部分内の1つまたは複数のビットエラーを検出するために前記集積回路上のエラー検出回路を使用することとを伴う、請求項5に記載の方法。

#### 【請求項10】

前記エラー検出コード部分が、エラー訂正コードと、エラー検出および訂正コードと、CRC(巡回冗長コード)コードとからなる群から得られる、請求項9に記載の方法。

#### 【請求項11】

(a)の前記決定することが、

検出されたビットエラーの数の合計を保持することと、20

エラーなしで受信されたビットの数の合計を保持することとをさらに伴う、請求項9に記載の方法。

#### 【請求項12】

前記SerDes受信機がループフィルタを含み、前記消費電力設定が前記ループフィルタの設定を備える、請求項5に記載の方法。

#### 【請求項13】

前記SerDes受信機がデジタルフィルタを含み、前記消費電力設定が、デジタルクロック信号が前記デジタルフィルタの一部分に供給されるのを防止する設定である、請求項5に記載の方法。

#### 【請求項14】

前記SerDes受信機がクロックとデータ回復回路とを含み、前記消費電力設定が前記クロックおよびデータ回復回路の設定を備える、請求項5に記載の方法。30

#### 【請求項15】

前記SerDes受信機がイコライザを含み、前記消費電力設定が前記イコライザの設定を備える、請求項5に記載の方法。

#### 【請求項16】

前記SerDes受信機がイコライザを含み、前記消費電力設定が、前記イコライザの高周波数ブーストをイネーブルする設定を備える、請求項5に記載の方法。

#### 【請求項17】

前記SerDes受信機が多相クロック信号を出力する位相ロックループ(PLL)を含み、前記消費電力設定が前記PLLの設定を備える、請求項5に記載の方法。40

#### 【請求項18】

前記SerDes受信機が入力インピーダンスを有し、前記消費電力設定が前記SerDes受信機の前記入力インピーダンスを決定する設定を備える、請求項5に記載の方法。45

#### 【請求項19】

(a)第1のSerDes(直列化器/並列化器)リンクのエラーレートを決定することであって、前記第1のSerDesリンクを介して進む情報がSerDes受信機によって受信されることと、

(b)前記エラーレートが実質的にゼロより大きいエラーレート下限とエラーレート上50

限との間に実質的に維持されるように、前記 SerDes 受信機の入力インピーダンス設定を制御することとを備え、(b) の前記制御することが、

前記エラーレートが前記エラーレート下限を下回っていると判断される場合、前記エラーレートが増加して実質的に前記エラーレート下限以上になるように、前記入力インピーダンス設定を前記 SerDes 受信機の前記入力インピーダンスが増大されるように調整することと、

前記エラーレートが前記エラーレート上限を上回っていると判断される場合、前記エラーレートが減少して実質的に前記エラーレート上限以下になるように、前記入力インピーダンス設定を前記 SerDes 受信機の前記入力インピーダンスが低減されるように調整することとを伴い、(b) の前記制御することが行われる間、前記 SerDes 受信機の入力インピーダンスがあるときは増大され、またあるときは低減される、方法。

10

#### 【請求項 20】

(a) における前記エラーレートを前記決定することが第 1 の集積回路上で実行され、前記 SerDes 受信機が第 2 の集積回路の一部である、請求項 19 に記載の方法。

#### 【請求項 21】

(a) における前記第 1 の SerDes リンクを介して進む前記情報が第 1 の集積回路の SerDes 送信機によって出力され、(a) における前記情報を受信する前記 SerDes 受信機が第 2 の集積回路の一部であり、(a) の前記決定することおよび(b) の前記制御することが前記第 1 の集積回路によって実行される、請求項 19 に記載の方法。

20

#### 【請求項 22】

前記エラーレートを決定するために、第 2 の SerDes リンクを介して第 1 の集積回路上で受信されるパケット内のエラー情報を使用することをさらに備え、(a) の前記決定することが前記第 1 の集積回路によって実行され、前記 SerDes 受信機が前記第 1 の集積回路の一部ではない、請求項 19 に記載の方法。

#### 【請求項 23】

前記パケットがキープアライブ同期パケットである、請求項 22 に記載の方法。

#### 【請求項 24】

前記エラー情報が、(a) における前記第 1 の SerDes リンクを介して進む前記情報に関連する、請求項 22 に記載の方法。

30

#### 【請求項 25】

第 2 の集積回路内の回路が、(a) における前記 SerDes リンクを介して進む前記情報内のエラーを検出し、前記エラーから前記エラー情報を生成し、前記第 2 の集積回路が前記エラー情報を前記パケットに組み込んで、前記パケットを前記第 2 の SerDes リンクを介して前記第 1 の集積回路に送信する、請求項 22 に記載の方法。

40

#### 【請求項 26】

前記第 1 の集積回路が、パケットを前記第 1 の SerDes リンクを介して前記第 2 の集積回路に送信することによって(b) の前記制御することを実行し、前記第 2 の集積回路に送信された前記パケットが前記入力インピーダンス設定を含み、前記入力インピーダンス設定が前記第 2 の集積回路の前記 SerDes 受信機に供給される、請求項 20 に記載の方法。

#### 【請求項 27】

前記パケットが制御パケットである、請求項 26 に記載の方法。

#### 【請求項 28】

(a) の前記決定することおよび(b) の前記制御することが、SerDes 送信機を含む第 1 の集積回路によって実行され、前記第 1 の SerDes リンクを介して進む前記情報が前記 SerDes 送信機から送信され、前記 SerDes 受信機が第 2 の集積回路の一部であり、前記第 1 の集積回路が中央処理装置(CPU)を含み、前記第 2 の集積回路がメモリを含み、前記第 1 の集積回路の前記 CPU が前記第 1 の SerDes リンクを使用して前記第 2 の集積回路の前記メモリにアクセスする、請求項 19 に記載の方法。

#### 【請求項 29】

10

20

30

40

50

(a) の前記決定することおよび(b) の前記制御することが、電池式ワイヤレスモバイル通信デバイス内の第1の集積回路によって実行される、請求項19に記載の方法。

**【請求項30】**

(a) 第1のSerDes通信を第1のデバイスから第1のSerDesリンクを介して第2のデバイス上で受信することであって、前記第1のSerDes通信が前記第2のデバイスのSerDes受信機上で受信されることと、

(b) 前記第1のSerDes通信内でエラーが発生したことを前記第2のデバイス上で判断することと、前記判断することに応答して、前記第1のSerDes通信に関連するエラー情報を含む第2のSerDes通信を前記第2のデバイスから前記第1のデバイスに第2のSerDesリンクを介して送信することと、

(c) 第3のSerDes通信を前記第1のデバイスから前記第1のSerDesリンクを介して前記第2のデバイス上で受信することと、

(d) 前記第2のデバイスの前記SerDes受信機の入力インピーダンス設定を調整するために、前記第3のSerDes通信内の情報を使用することとを備える、方法。

**【請求項31】**

(c)において受信された前記第3のSerDes通信内の前記情報が、(b)における前記エラー情報の関数である、請求項30に記載の方法。

**【請求項32】**

(a)、(b)、(c)および(d)が第2の集積回路によって実行され、前記第1のSerDesリンクのエラーレートが実質的にゼロより大きいエラーレート下限とエラーレート上限との間に実質的に維持されるように複数回繰り返される、請求項30に記載の方法。

**【請求項33】**

SerDes受信機と、

前記SerDes受信機に結合されたコントローラとを備え、前記コントローラが、前記SerDes受信機を伴うSerDesリンクに対するエラーレートを決定し、前記コントローラが、前記エラーレートが実質的にゼロより大きいエラーレート下限とエラーレート上限との間に実質的に維持されるように、前記コントローラによって前記SerDes受信機に供給される消費電力設定を調整する、集積回路。

**【請求項34】**

前記コントローラが、前記SerDesリンクを介して行われた通信内のエラーを検出するエラー検出回路を含み、前記コントローラが、前記SerDesリンクに対する前記エラーレートを決定するために、前記エラー検出回路によって生成されたエラー情報を使用する、請求項33に記載の集積回路。

**【請求項35】**

前記SerDes受信機がループフィルタを含み、前記消費電力設定が前記ループフィルタの設定を備える、請求項33に記載の集積回路。

**【請求項36】**

前記SerDes受信機がデジタルフィルタを含み、前記消費電力設定が、デジタルクロック信号が前記デジタルフィルタの一部分に供給されるのを防止する設定である、請求項33に記載の集積回路。

**【請求項37】**

前記SerDes受信機がクロックおよびデータ回復回路を含み、前記消費電力設定が前記クロックおよびデータ回復回路の設定を備える、請求項33に記載の集積回路。

**【請求項38】**

前記SerDes受信機がイコライザを含み、前記消費電力設定が前記イコライザの設定を備える、請求項33に記載の集積回路。

**【請求項39】**

前記SerDes受信機がイコライザを含み、前記消費電力設定が、前記イコライザの高周波数ブーストをイネーブルする設定を備える、請求項33に記載の集積回路。

10

20

30

40

50

**【請求項 4 0】**

前記 SerDes 受信機が、多相クロック信号を出力する位相ロックループ（PLL）を含み、前記消費電力設定が前記 PLL の設定を備える、請求項 33 に記載の集積回路。

**【請求項 4 1】**

前記 SerDes 受信機が入力インピーダンスを有し、前記消費電力設定が、前記 SerDes 受信機の前記入力インピーダンスを決定する設定を備える、請求項 33 に記載の集積回路。

**【請求項 4 2】**

第 2 の SerDes リンクを介して情報を受信するように適合された第 1 の SerDes 受信機と、10

第 1 の SerDes リンクを介して第 2 の SerDes 受信機に情報を送信するように適合された SerDes 送信機と、

前記第 1 の SerDes 受信機と前記 SerDes 送信機とに結合されたコントローラとを備え、前記コントローラが、前記第 1 の SerDes 受信機を介してエラー情報を受信し、前記第 1 の SerDes リンクのエラーレートを決定するために前記エラー情報を使用し、前記コントローラが、前記第 1 の SerDes リンクの前記エラーレートが実質的にゼロより大きいエラーレート下限とエラーレート上限との間に実質的に維持されるように前記第 2 の SerDes 受信機の入力インピーダンスを調整するために、前記 SerDes 送信機に制御パケットを送信させる、集積回路。

**【請求項 4 3】**

前記エラー情報が、キープアライブ同期パケットの一部として前記第 2 の SerDes リンクを介して前記集積回路上で受信される、請求項 42 に記載の集積回路。

**【請求項 4 4】**

前記第 1 の SerDes リンクおよび第 2 の SerDes リンクを介してメモリアクセスを実行する中央処理装置（CPU）をさらに備える、請求項 42 に記載の集積回路。

**【請求項 4 5】**

エラーレートを有する第 1 の SerDes リンクを介して情報を受信するように適合された SerDes 受信機と、

第 2 の SerDes リンクを介して情報を送信するように適合された SerDes 送信機と、30

前記第 1 の SerDes 受信機と前記 SerDes 送信機とに結合されたコントローラとを備え、前記コントローラが、前記第 1 の SerDes リンクを介した第 1 の SerDes 通信に関するエラー情報を生成し、前記コントローラが、前記第 2 の SerDes リンクを介して第 2 の SerDes 通信内で前記エラー情報を通信させ、前記コントローラが前記第 1 の SerDes リンクを介して第 3 の SerDes 通信内の制御パケットを受信し、前記制御パケットに応答して、前記第 1 の SerDes リンクの前記エラーレートが実質的にゼロより大きいエラーレート下限とエラーレート上限との間に実質的に維持されるように前記第 2 の SerDes 受信機の入力インピーダンスを調整する、集積回路。

**【請求項 4 6】**

前記第 2 の SerDes 通信がキープアライブ同期パケットの通信である、請求項 45 に記載の集積回路。40

**【請求項 4 7】**

前記コントローラに結合され、前記第 1 の SerDes リンクおよび前記第 2 の SerDes リンクを使用して別の集積回路によってアクセスされ得るメモリをさらに備える、請求項 45 に記載の集積回路。

**【発明の詳細な説明】****【技術分野】****【0001】**

本開示は、直列 / 並列化器（SerDes）デバイスに関する。

**【背景技術】**

10

20

30

40

50

## 【0002】

旧来、コンピュータの中央処理装置（CPU）とコンピュータのメインメモリとの間のコンピュータ内バスは、並列バスであった。コンピュータの処理スループットが増加するにつれて、またメモリ帯域幅の需要が増加するにつれて、CPUとメモリ間のバスが、1つまたは複数の直列化器／並列化器（SerDes：Serializer/Deserializer）リンクとして実装されることが次第に一般的になってきた。これらのSerDesリンクは比較的高価であり、概して大量の電力を消費する傾向があった。したがって、SerDesリンクは概して、消費電力を低く保つことが非常に重要であるモバイルデバイス（セルラー電話など）における使用に適しているとは思われていなかった。しかしながら、最近、セルラー電話など、低電力モバイルデバイスにおいてSerDesまたはSerDesライクな技術を使用する動きがある。たとえば、SerDesインターフェースに対する議論の下でJEDEC（Joint Electron Device Engineering Council）が提案する規格が存在する。この提案された規格は、提案されたSerDesインターフェースを低電力モバイルデバイスに対してより適切にする節電の特徴を含む。提案されたJEDEC規格におけるSerDesインターフェースに加えて、多数の他の知られているSerDes設計が存在する。これらの規格および知られている設計は、消費電力を低減するために多数の特徴および方法を含んでいる。

10

## 【0003】

そのような節電の特徴の第1の例は、インターフェースがプロセッサによってアクティブにアクセスされていない低電力モードにおいてSerDesインターフェースを置くことを使う。しかしながら、一般的なCPUによるメモリの使用は本来ランダムアクセスであるので、メモリは本質的に、（スリープモード動作を除いて）ほとんど常にプロセッサに対して利用可能でなければならない。その結果、節電のこの第1の例は、消費電力を低減することにおいてほとんど効果的ではない。節電特徴の第2の例は、SerDesのPLL（位相ロックループ）および（CDR）クロックおよびデータ回復回路への電源を切って、それらをディセーブルすることを使う。SerDesリンクの両側は、PLLとCDRとを含む。この回路は多くの電力を消費する可能性がある。インターフェースがアクティブでないときに消費電力を低減するために、これらの回路をターンオフができる。残念ながら、これらの回路を再びターンオンして（PLLのロック時間を整定させ）、それらを再び機能させるために、ある時間量が必要である。プロセッサがメモリにアクセスする必要があるときにこれらの回路がオフ状態にある場合、メモリがSerDesリンクを介してアクセス可能になるまでに遅延が存在し、その遅延が、事実上プロセッサを失速させる。これは望ましくない。節電特徴の第3の例は、米国特許出願公開第2006/01115316号に説明されている。この例では、SerDes送信機の信号振幅は、送信エラーを防止するために必要なだけの大きさに作られる。しかしながら、モバイルアプリケーションに対してもっと節電する必要が残されており、第1と第2の両方の例では、主たる節電は、一部の時間にSerDesインターフェースを使用不能で非アクティブにさせ、それによりプロセッサのインターフェース使用が複雑となって部分的に機能低下する（compromise）ことによって達成される。

20

30

## 【発明の概要】

40

## 【0004】

コンピュータシステムは、プロセッサ集積回路内のSerDesデバイスとメモリ集積回路内のSerDesデバイスとを伴う。両SerDesデバイスは、SerDes送信機部とSerDes受信機部とを含む。メモリ集積回路内のSerDes受信機部は、第1のSerDesリンクを介してプロセッサ集積回路内のSerDesデバイスからメモリ集積回路内のSerDesデバイスに送信されたパケットがエラーを含んでいるかどうかを検出するためのエラー検出機構を有する。一例では、この第1のSerDesリンクを介して送信された各パケットは、データペイロード部分とCRC照合部分とを含む。メモリ集積回路内のSerDesデバイスは、パケットを受信し、CRC部分がデータペイロード部分に対して正しいかどうかを判断するために、CRCエラー検出回路を使用する

50

。エラーが検出されると、メモリ集積回路内のSerDesデバイスは、第2のSerDesリンクを介してプロセッサ集積回路内のSerDesデバイスにエラー（または複数のエラー）の表示を報告する。一例では、メモリ集積回路内のSerDesデバイスは、ヘルスステータスフラグの形態のエラー情報を含むSerDes「キープアライブ（keep alive）」同期パケットを送信することによってこの報告を行う。キープアライブ同期パケットは、第2のSerDesリンクを介してメモリ集積回路からプロセッサ集積回路に送信される。エラー情報は、このプロセッサ-メモリリンクに対してメモリ集積回路内でSerDesデバイスによって保持されているエラーレートであってよく、またはエラー情報は、第1のSerDesリンク介する前のプロセッサ-メモリ通信内の個別のエラーもしくは複数のエラーの発生の表示であってよい。プロセッサ集積回路内のSerDesデバイスはまた、メモリ集積回路のSerDesデバイスからプロセッサ集積回路のSerDesデバイスに第2のリンクを介して送信されたパケット内のエラーを検出するエラー検出および訂正回路を有する。

10

#### 【0005】

プロセッサ集積回路内のSerDesデバイスは、「キープアライブ」同期パケットを受信し、プロセッサからメモリへの第1のSerDesリンクに対するエラーレートを決定するために、パケットによって搬送されるエラー情報を使用する。加えて、SerDesデバイスは、第2のSerDesリンクを介してメモリ集積回路から受信された着信パケット内のエラーを検出するために、そのエラー検出CRC照合部分を使用する。プロセッサ集積回路内のSerDesデバイスは、メモリからプロセッサへの第2のSerDesリンクに対するエラーレートを決定するために、そのCRC照合部分からのこのエラー情報を使用する。

20

#### 【0006】

決定された第1のSerDesリンクに対するエラーレートが、第1のSerDesリンクに対するエラーレート下限を下回る場合、第1のSerDesリンクの回路内の消費電力は低減される。一例では、メモリ集積回路内のSerDes受信機の入力インピーダンス設定は、入力インピーダンスがより高くなるように調整される。このことは、第1のSerDesリンクのビットエラーレートを劣化させる。決定された第1のSerDesリンクに対するエラーレートが、第1のSerDesリンクに対するエラーレート上限を上回る場合、第1のSerDesリンクの回路内の消費電力は、メモリ内のSerDes受信機の入力インピーダンス設定を低減することによって増大される。このことは、第1のSerDesリンクのビットエラーレートを改善させる。決定された第1のSerDesリンクに対するエラーレートが上限と下限との間である場合、その許容可能なビットエラーレート範囲内にあるものと判断され、第1のSerDesリンクの回路に対する消費電力設定は変更されない。

30

#### 【0007】

同様に、決定されたメモリ集積回路からプロセッサ集積回路への第2のSerDesリンクに対するエラーレートが、第2のSerDesリンクに対するエラーレート下限を下回る場合、プロセッサ集積回路内のSerDes受信機の消費電力設定が第2のSerDesリンクの回路内の消費電力を低減するように調整され、それにより第2のSerDesリンクのビットエラーレートが劣化する。決定された第2のSerDesリンクに対するエラーレートが、第2のSerDesリンクに対するエラーレート上限を上回る場合、プロセッサ集積回路内のSerDes受信機の消費電力設定が、第2のSerDesリンクの回路内の消費電力を増加させるように調整され、それにより、第2のSerDesリンクのビットエラーレートが改善する。決定された第2のSerDesリンクに対するエラーレートが上限と下限との間である場合、その許容可能な範囲内にあるものと判断され、第2のSerDesリンクの回路の消費電力設定は変更されない。SerDesリンクは、信号の1つまたは複数のペアを伴う。

40

#### 【0008】

パケットが第1のSerDesリンクを介して通信されるにつれて、決定された第1の

50

SerDesリンクに対するビットエラーレートが更新され、メモリ集積回路のSerDes受信機の入力インピーダンス設定が、第1のリンクのエラーレートがその許容範囲内に実質的に維持されるように調整される。エラーレート下限は実質的にゼロより大であり、したがって、第1のSerDesリンクの回路の消費電力は、別法によりリンクがビットエラーを最小化するように動作されているよりも小さくなる。第1のSerDesリンクに対するエラーレート上限および下限は、消費電力とビットエラーレートとの間のトレードオフを変更するために調整され得る。消費電力と第1のSerDesリンクに対するビットエラーレートとの間のトレードオフは、プロセッサおよびコンピュータシステムの特定の動作条件ならびに環境条件に対して動的に制御および最適化され得る。

## 【0009】

10

同様に、パケットが第2のSerDesリンクを介して通信されるにつれて、決定された第2のSerDesリンクに対するビットエラーレートが更新され、プロセッサのSerDes受信機の消費電力設定は、第2のリンクのエラーレートがその許容範囲内に実質的に維持されるように調整される。エラーレート下限は実質的にゼロより大であり、したがって、第2のSerDesリンクの回路の消費電力は、別法によりリンクがビットエラーを最小化するように動作されているよりも小さくなる。第1のSerDesリンクに対するエラーレート上限および下限は、消費電力とビットエラーレートとの間のトレードオフを変更するために調整され得る。消費電力と第2のSerDesリンクに対するビットエラーレートとの間のトレードオフは、プロセッサおよびコンピュータシステムの特定の動作条件ならびに環境条件に対して動的に制御および最適化され得る。

## 【0010】

20

エラー検出および訂正回路が、第1と第2の両SerDesリンクのSerDes受信機内に設けられる。このエラー検出および訂正回路は、SerDes通信内の1つまたは複数のビットエラーを検出してシングルビットエラーを訂正することができる。このエラー検出および訂正回路を設けることによって、許容可能なビットエラーレート範囲の下限が実質的にゼロより大に設定されているという事実にもかかわらず、SerDesリンクを介してデータを正常に通信するために再送信する必要性が低減される。より強力なエラー訂正回路が設けられるならば、2つのリンクの許容可能なビットエラーレート範囲の下限は、リンクを介する再送信レートに影響を実質的に与えることなく増大され得る。SerDes受信機をディセーブルしてリンクの使用を機能低下させることによって消費電力が低減される従来技術の例とは対照的に、リンクのSerDes受信機の消費電力は、SerDesリンクがアクティブでかつ使用可能である状況において低減される。

## 【0011】

30

上記は概要であり、したがって当然、詳細の簡略化、一般化および省略を含んでおり、したがって、概要はいかなる形でも例示的なものに過ぎず、限定的なものではないことを当業者は諒解されたい。特許請求の範囲のみによって定義される、本明細書で説明するデバイスおよび/またはプロセスの他の態様、発明的特徴、および利点は、本明細書に記載する非限定的な詳細な説明において明らかになるであろう。

## 【図面の簡単な説明】

## 【0012】

40

【図1】新規の一態様による、電池式モバイル通信デバイス内のSerDesシステムの簡略図。

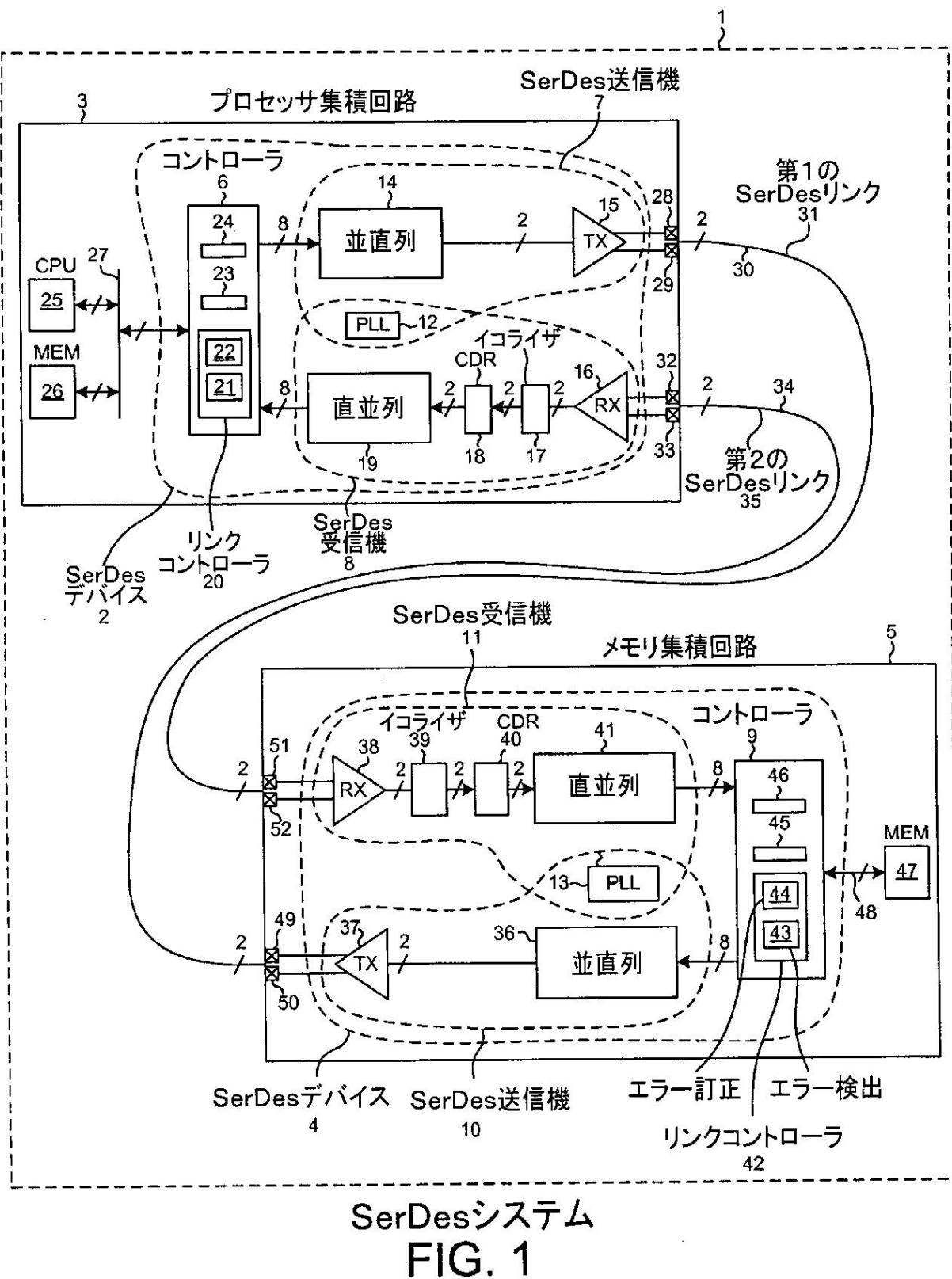

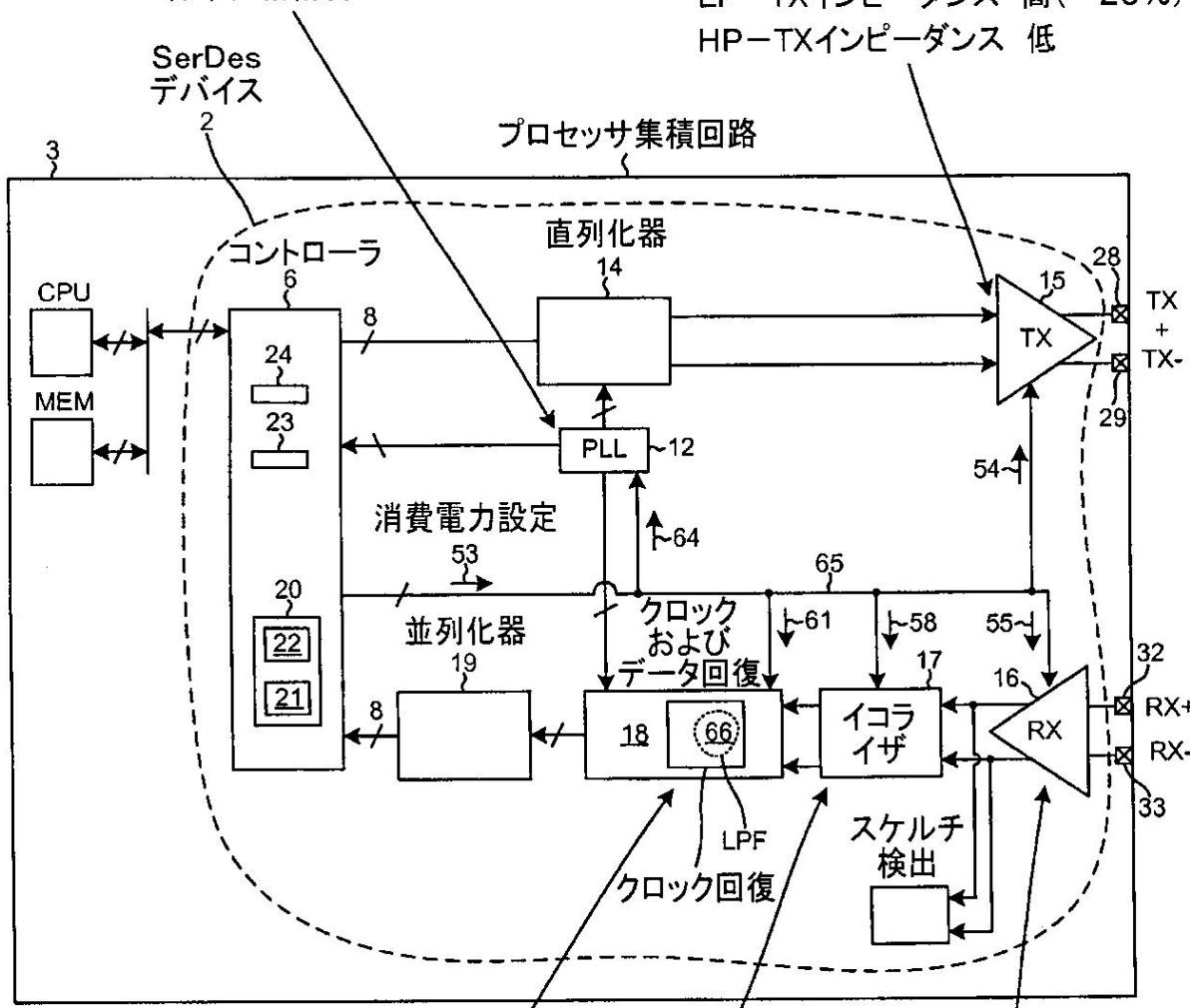

【図2】SerDes信号が図1のシステム内でいかにして受信されるかを示す波形図。

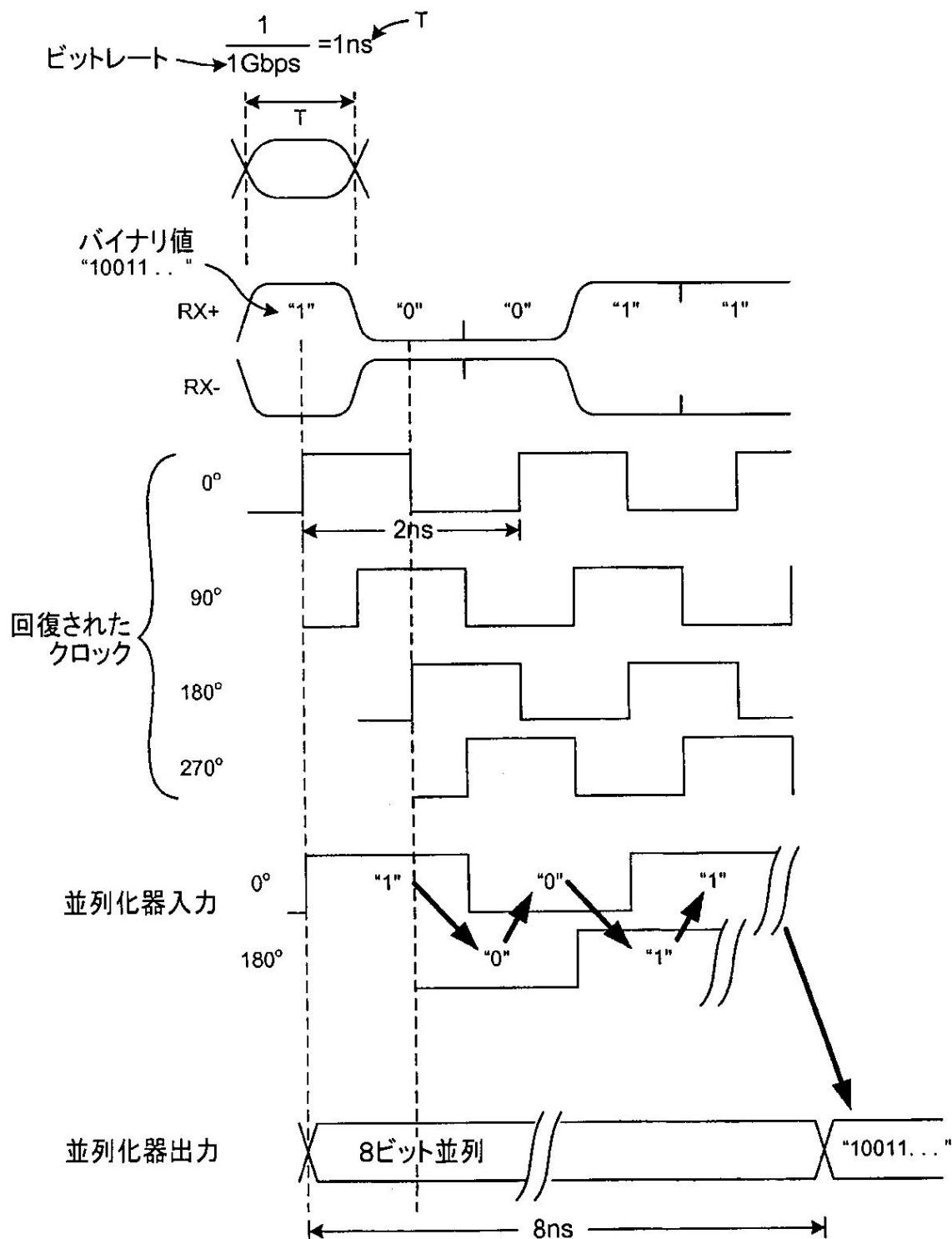

【図3】図1のSerDesシステムのプロセッサ集積回路3内のSerDesデバイス2のより詳細な図。

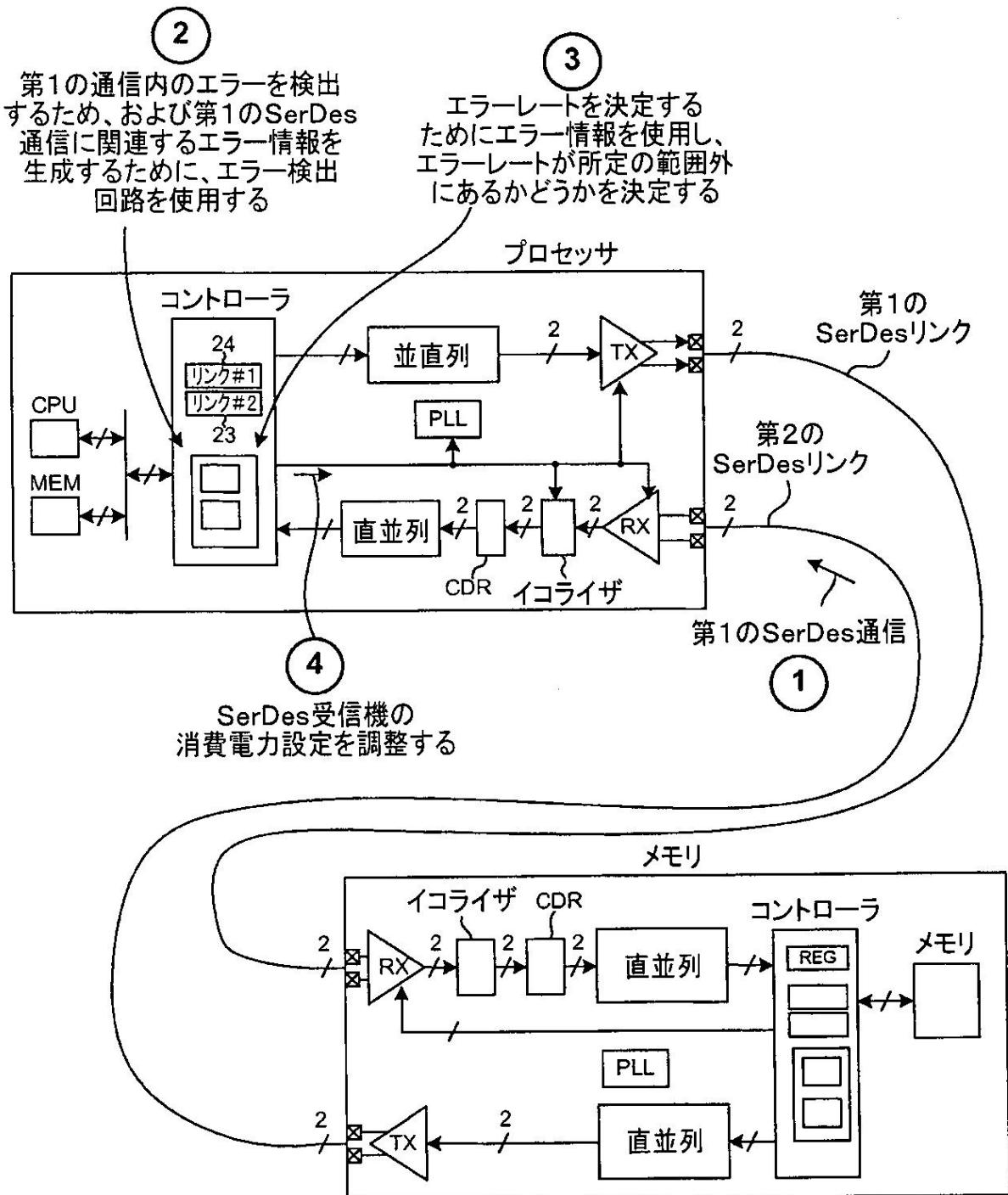

【図4】第1の新規な態様による、図1のシステム1の動作の方法の図。

【図5】ビットエラーが図1のシステム内で保持される許容可能なビットエラーレート範囲を示す図。

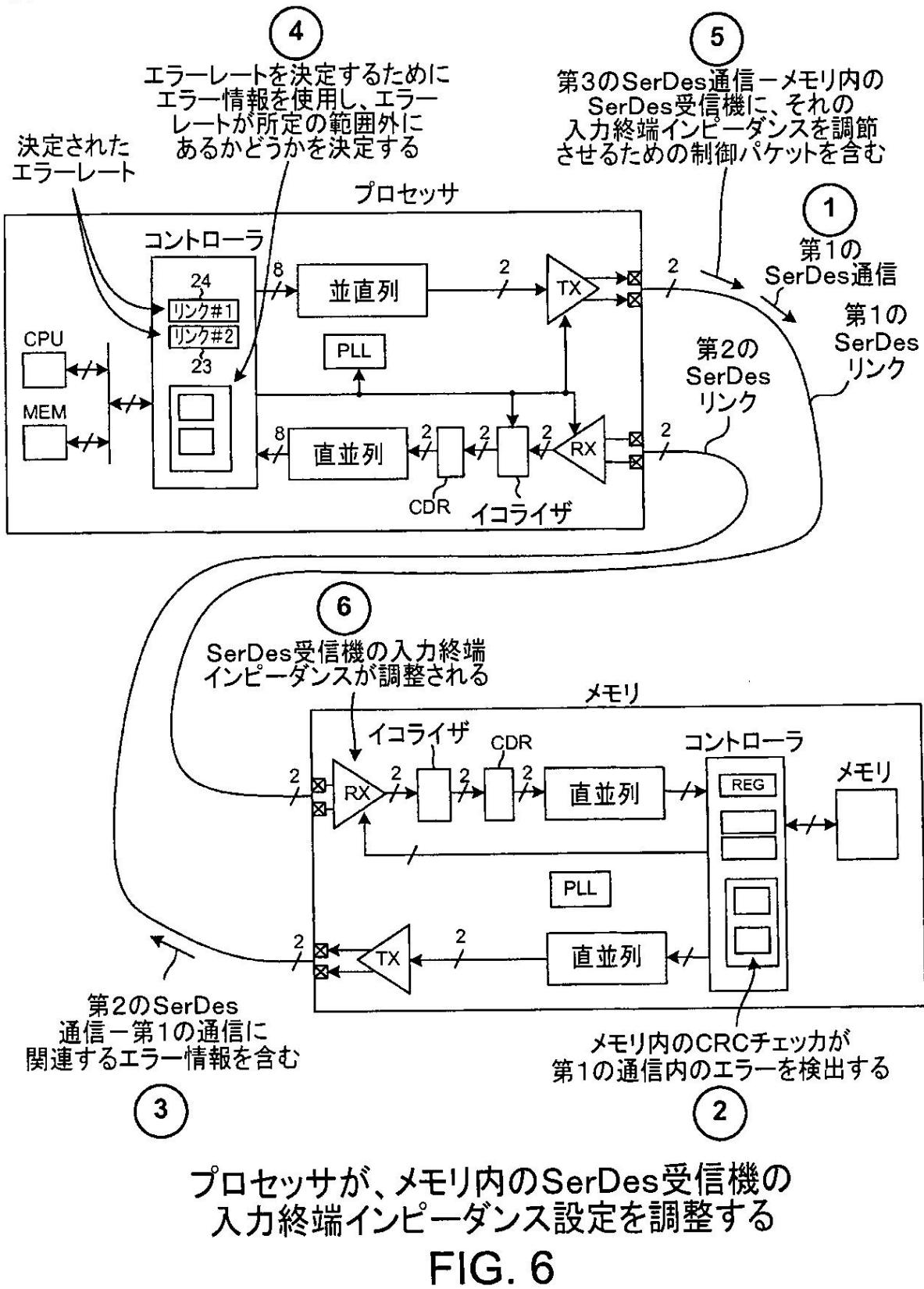

【図6】第2の新規な態様による、図1のシステム1の動作の方法の図。

【図7A】図1のシステムのプロセッサ集積回路3内のSerDesデバイス2の動作の

50

方法のフローチャート。

【図 7 B】図 1 のシステムのプロセッサ集積回路 3 内の SerDes デバイス 2 の動作の方法のフローチャート。

【図 8】図 1 のシステムのメモリ集積回路 5 内の SerDes デバイス 4 の動作の方法のフローチャート。

【図 9】図 1 のシステムの SerDes 受信機 RX 16 の簡略回路図。

【図 10】図 1 のシステムのイコライザ 17 の簡略図。

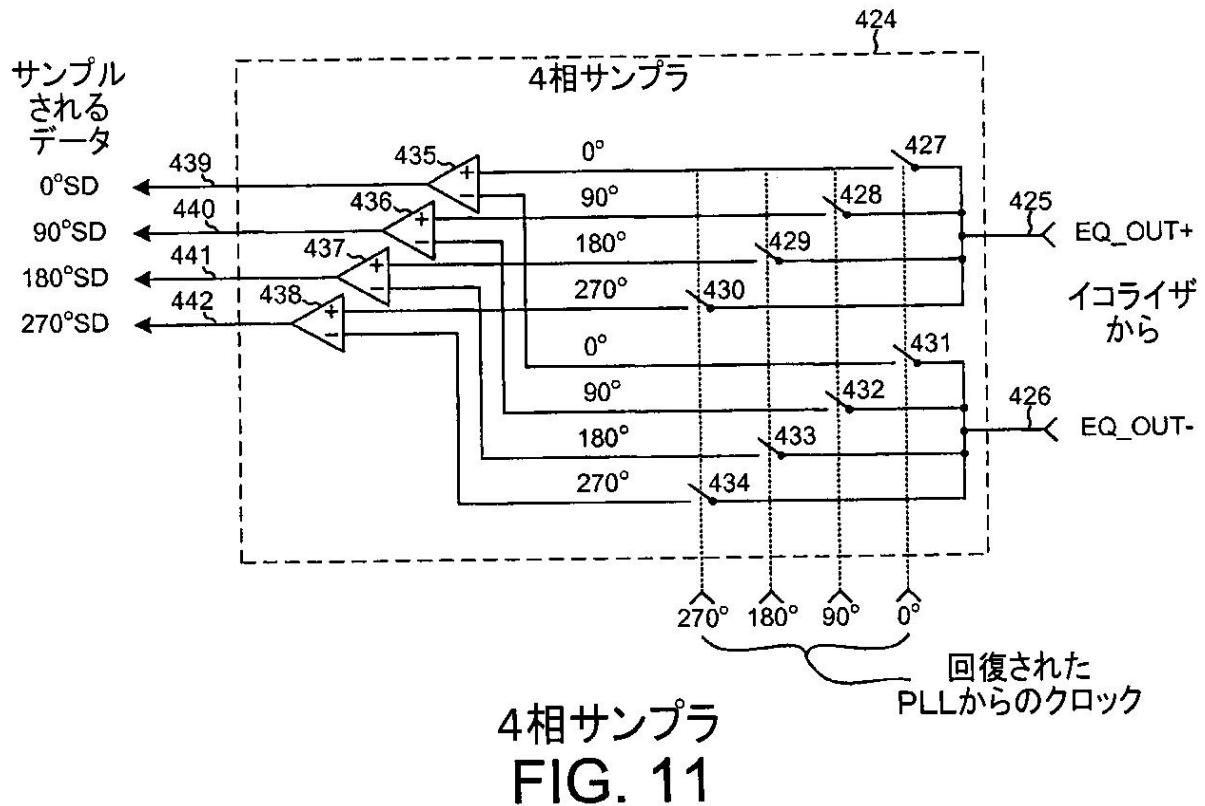

【図 11】図 1 のシステムの CDR 回路 18 内の 4 相サンプラー 424 の図。

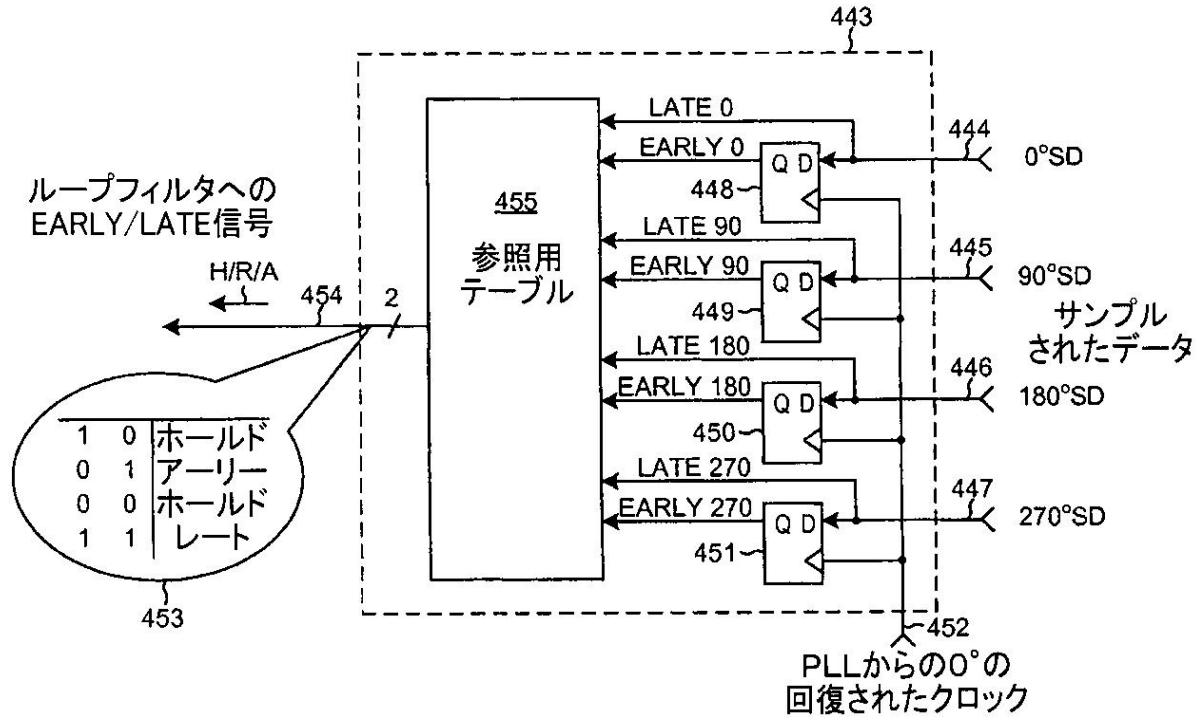

【図 12】図 1 のシステムの CDR 回路 18 内のアーリーレート (early-late) 検出器 443 の図。 10

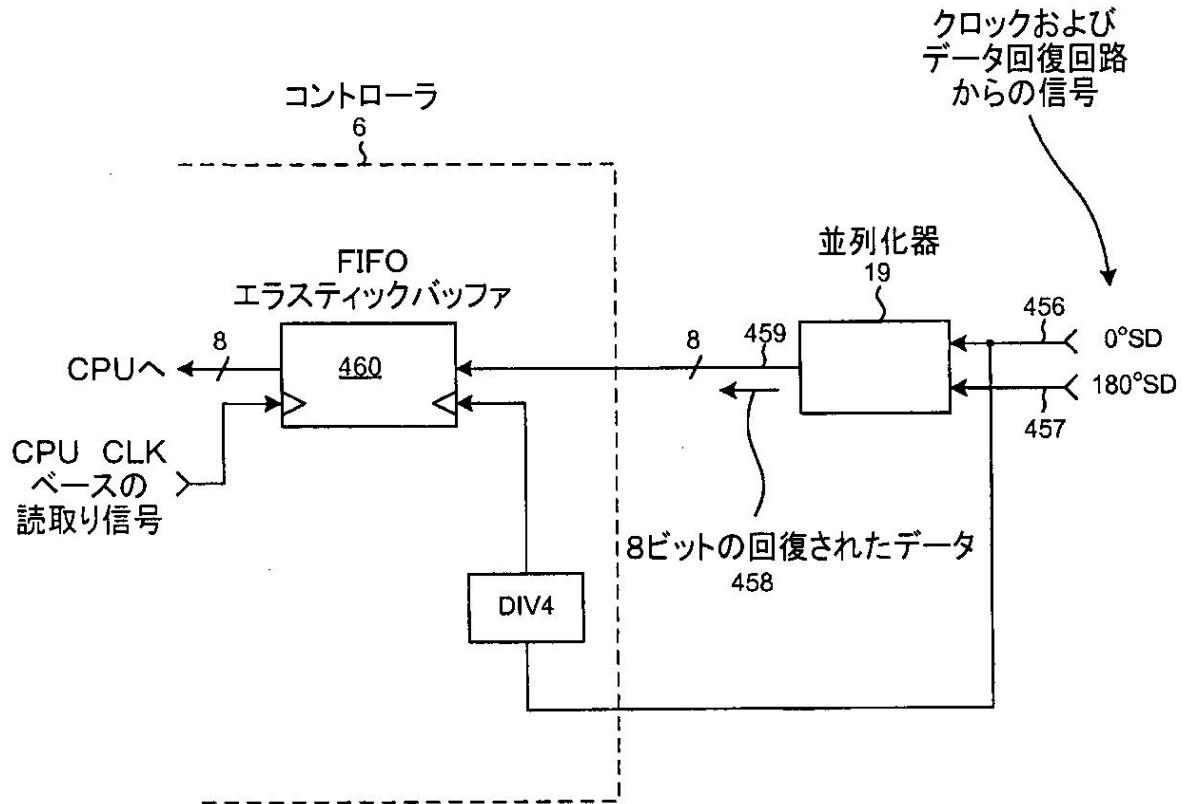

【図 13】図 1 のシステムにおいて、データが並列化器 (deserializer) 19 からコントローラ 6 内に、いかにして進むかを示す図。

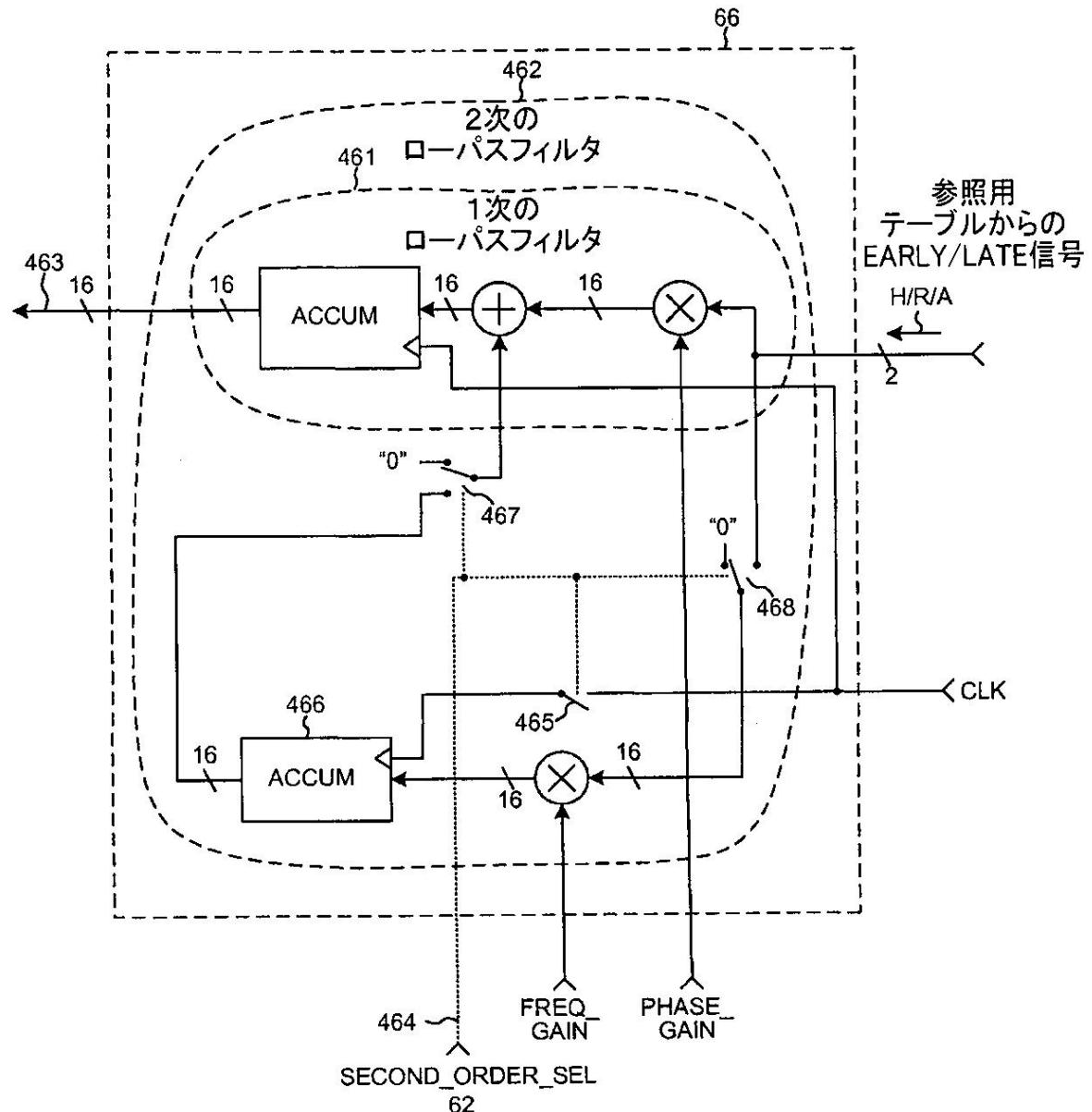

【図 14】図 1 のシステムの CDR 回路 18 内のループフィルタ 66 の図。

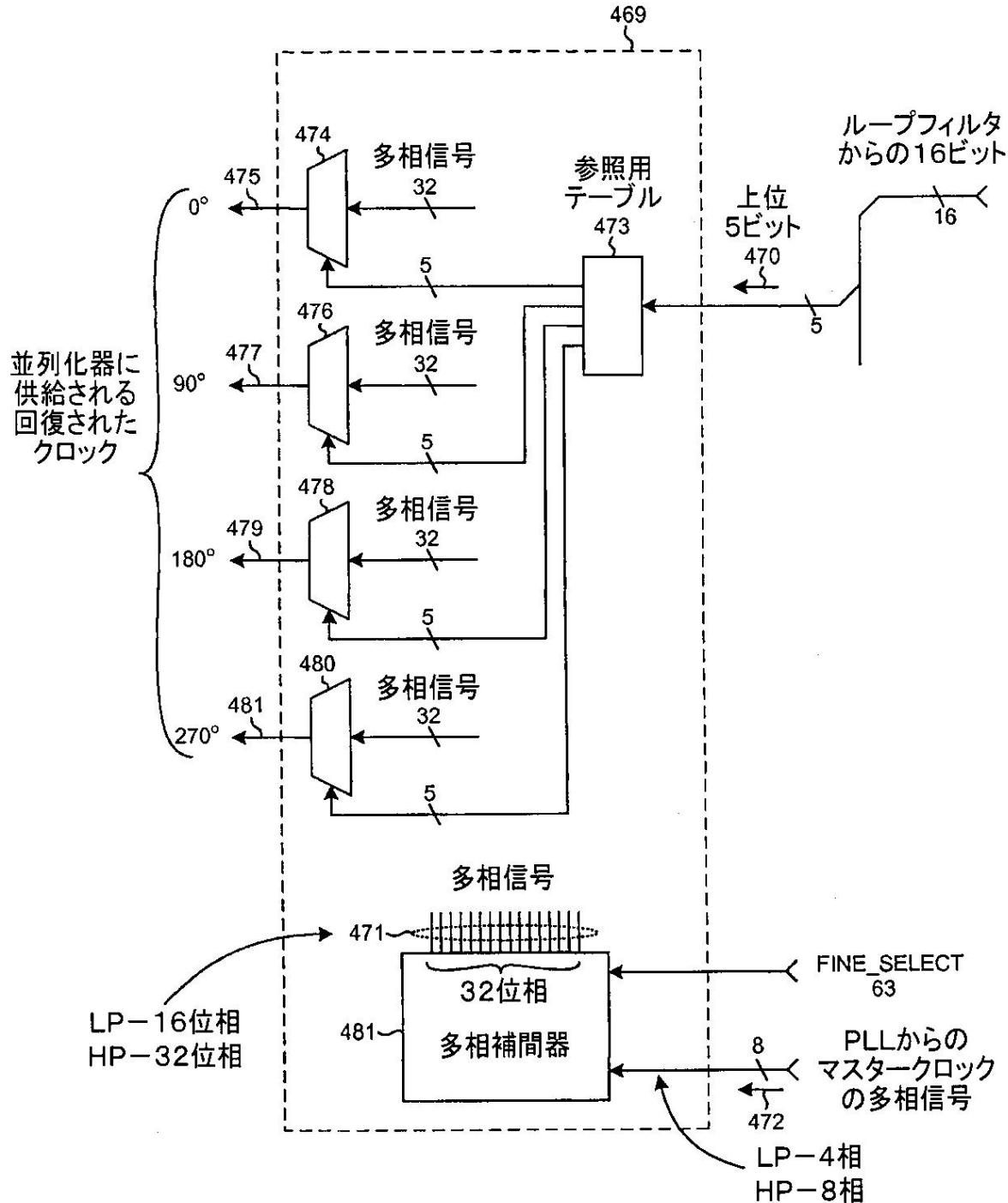

【図 15】図 1 のシステムの CDR 回路 18 内の 4 相クロック発生器 469 の図。

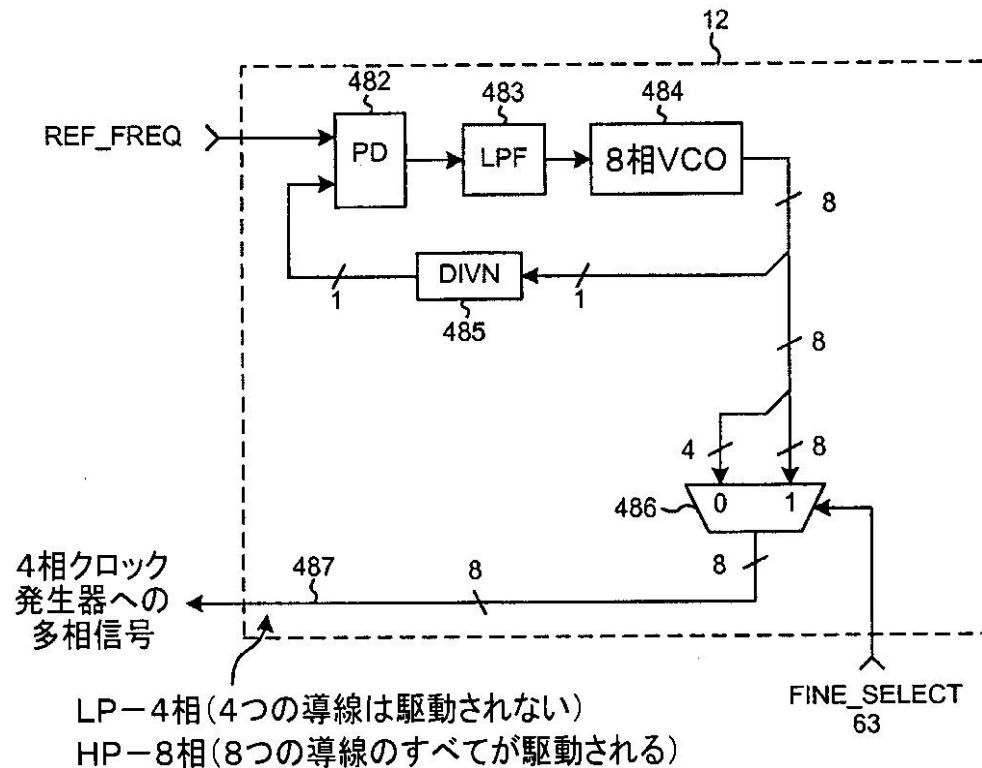

【図 16】図 1 のシステムの PLL 12 の図。

【図 17】PLL 12 から導線 487 上に出力される信号を示す表。

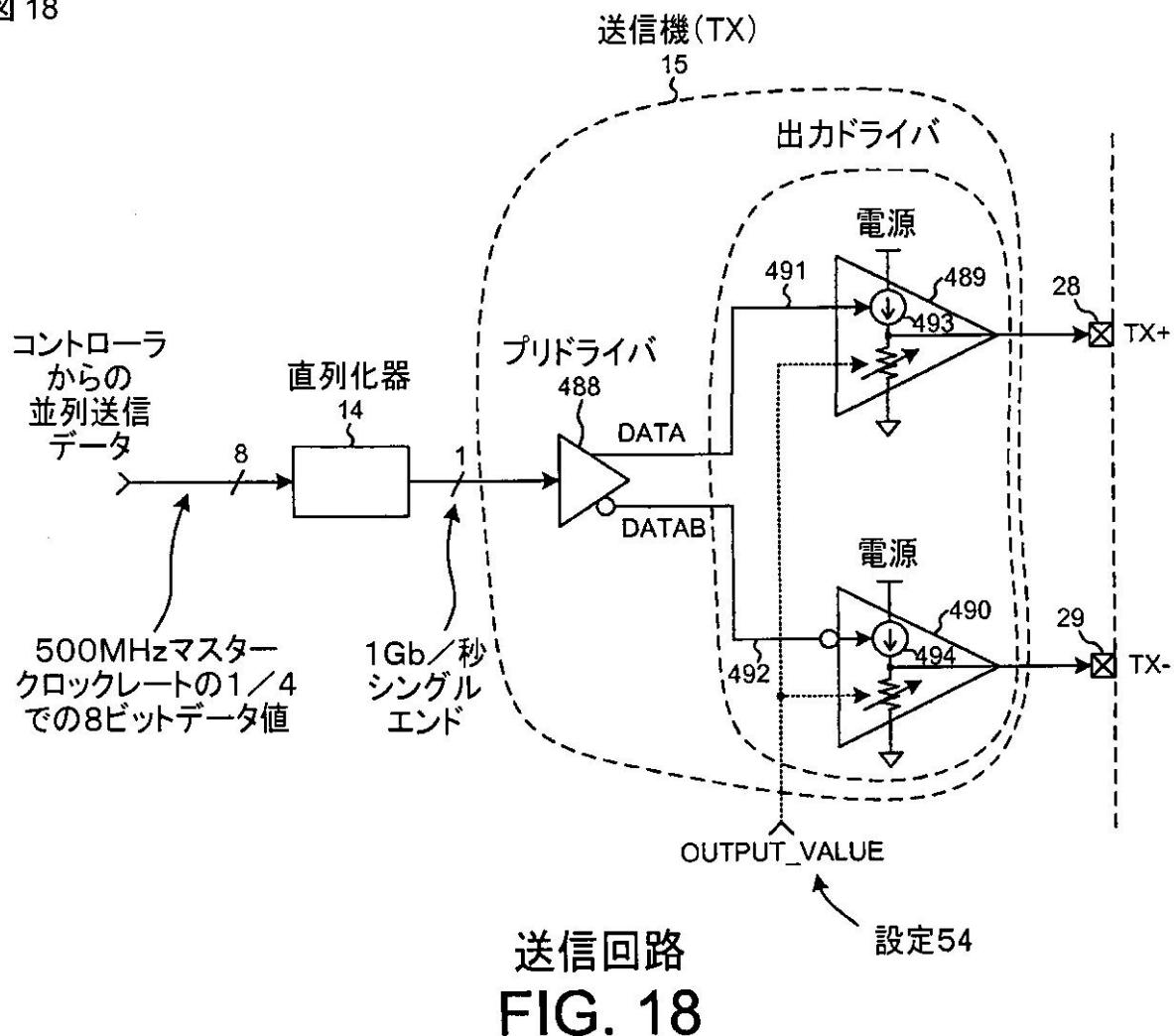

【図 18】図 1 のシステムの送信回路の簡略図。

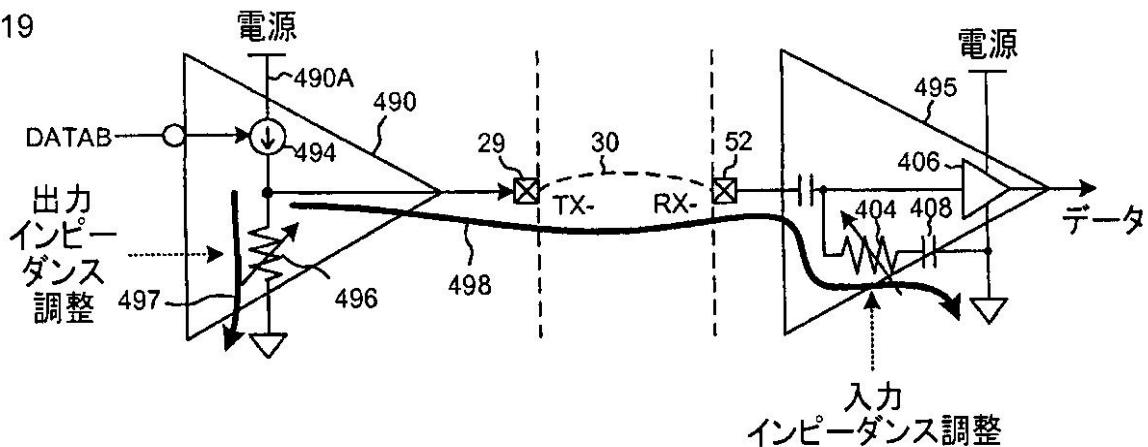

【図 19】SerDes 受信機の入力インピーダンスを変更することが、SerDes リンクの他端における SerDes 送信機の消費電力にいかに影響するかを示す図。

【図 20】図 1 のシステムのプロセッサ集積回路 3 内の SerDes デバイス 2 における消費電力の内訳を示すパイチャート。 20

【図 21】高電力モードおよび低電力モードにおける SerDes デバイス 2 の全消費電力を示す表。

【図 22】SerDes リンクが広帯域チャネルである一例を示す図。

【図 23】SerDes リンクがわずかに帯域制限されたチャネルである一例を示す図。

【図 24】SerDes リンクが実質的に帯域制限されたチャネルである一例を示す図。

【詳細な説明】

【0013】

図 1 は、プロセッサ集積回路 3 内の SerDes デバイス 2 と、メモリ集積回路 5 内の SerDes デバイス 4 とを伴うシステム 1 の図である。一例では、システム 1 は、セラーテlephone ハンドセットなど、電池式ワイヤレスモバイル通信デバイスである。SerDes デバイス 2 は、コントローラ部 6 と、SerDes 送信機部 7 と、SerDes 受信機部 8 とを含む。SerDes デバイス 4 は、コントローラ部 9 と、SerDes 送信機部 10 と、SerDes 受信機部 11 とを含む。プロセッサ集積回路 3 の SerDes デバイス 2 内の位相ロックループ (PLL) 12 は、SerDes 送信機部 7 の一部と SerDes 受信機部 8 の一部の両方であるものと考えられる。同様に、メモリ集積回路 5 の SerDes デバイス 4 内の PLL 13 は、SerDes 送信機部 10 の一部と SerDes 受信機部 11 の一部の両方であるものと考えられる。 30

【0014】

プロセッサ集積回路 3 の SerDes 送信機部 7 は、直列化器 (serializer) と呼ばれる並列変換回路 (parallel-to-serial circuit) 14 と送信機ドライバ TX 15 とを含む。プロセッサ集積回路 3 の SerDes 受信機部 8 は、受信機増幅器 RX 16 と、イコライザ 17 と、クロックおよびデータ回復 (CDR) 回路 18 と、並列化器 (deserializer) と呼ばれる直並列回路 19 とを含む。コントローラ部 6 は、エラー検出回路 21 を次に含むリンクコントローラ 20 と、エラー訂正回路 22 と、レジスタ 23 および 24 のペアとを含む。中央処理装置 (CPU) 25 は、並列ローカルバス機能 27 を介してローカルキャッシュメモリ 26 およびコントローラ 6 と通信する。記号 28 および 29 は、送信機 TX 15 が第 1 の SerDes リンク 31 の 2 つの対応する導線 30 上に差動 SerDes 信号を送信する、2 つの集積回路端子を表す。記号 32 および 33 は、受信機 RX 16 が第 2 の SerDes リンク 35 の 2 つの対応する導線 34 上から差動 SerDes 信号を受信する、2 つの集積回路端子を表す。 40

JP 2015-18564 A 2015.1.29

Des 信号を受信する、2つの集積回路端子を表す。

【0015】

メモリ集積回路5のSerDes送信機部10は、並直列変換回路36と送信機TX37とを含む。メモリ集積回路5のSerDes受信機部11は、受信機増幅器RX38と、イコライザ39と、クロックおよびデータ回復(CDR)回路40と、直並列変換回路41とを含む。コントローラ部9は、エラー検出回路43およびエラー訂正回路44をさらに含むリンクコントローラ42と、レジスタ45および46のペアとを含む。メモリ量47は、バスインターフェース48を介してコントローラ9に結合される。記号49および50は、送信機TX37が第2のSerDesリンク35の2つの導線34上に差動SerDes信号を送信する、2つの集積回路端子を表す。記号51および52は、受信機RX38が第1のSerDesリンク31の2つの導線30上から差動SerDes信号を受信する、2つの集積回路端子を表す。

【0016】

図2は、図1のSerDesリンクを介して通信されるSerDes信号の波形図である。たとえば、第1のSerDesリンク31を介して通信されるSerDes信号を取り上げる。信号RX+およびRX-は、メモリ集積回路5の入力端子51および52上で受信される、導線30上のSerDes信号である。図2で0°、90°、180°および270°と標示された波形は、クロックおよびデータ回復(CDR)40によって生成される多相クロック信号を表す。これらの回復されたクロック信号は、受信機RX38の差動出力をサンプリングするために使用される。回復されたクロック信号のうちの1つは、直列データストリームの値がサンプリングされ得るように、示されるような着信直列データストリームのビット時間のそれぞれの中央で高に遷移する。図2で「直並化器(DESERIALIZER)入力」と標示された波形は、図1のイコライザブロック39およびCDRブロック40によって出力された信号を表す。図2で「並列化器(DESERIALIZER)出力」と標示された波形は、図1の直並列変換回路41の8ビット並列出力を表す。端子51および52において差動信号RX+およびRX-として直列に受信された、1、0、0、1および1のビット値の直列ストリームが、波形「並列化器出力」で示されるように、直並列変換器回路41の8ビット出力においてデジタル形式で出力される。本例では、1ビットが1ナノ秒ごとに通信される。これは、1ギガビット毎秒のビットレートに相当する。

【0017】

図3は、プロセッサ集積回路3内のSerDesデバイス2のより詳細な図である。コントローラ6は、マルチビットデジタル消費電力設定53を出力する。消費電力設定53は、SerDesデバイスの様々なサブブロックに供給される複数のデジタル設定54、55、58、61および64の合成である。たとえば、第1の設定54は、送信機TX15に供給されるマルチビットデジタル値である。設定54は、送信機TX15の出力インピーダンスを設定する。送信機の出力インピーダンスは、SerDes送信機15が出力信号を駆動する、送信機におけるエッジレートと信号反射とを決定する。低電力モードでは送信機TX15の出力インピーダンスはより高い(より遅いエッジレート)のに対し、高電力モードでは送信機TX15の出力インピーダンスはより低い(より速いエッジレート)。出力インピーダンスがより高いかまたはより低いかは、設定54の値によって決定される。加えて、プロセッサ内のSerDesデバイスの送信機TXがその出力を駆動する、高信号レベルおよび低信号レベルのレベル(電流レベル)を設定するV<sub>DIF</sub>設定が存在する。低電力設定では、高信号レベルと低信号レベルとの間により小さい差(電流差)が存在するのに対して、高電力設定では、高信号レベルと低信号レベルとの間により大きい差(電流差)が存在する。図3の概念では、「LP」は低電力モードまたは設定を示すのに対して、「HP」は高電力モードまたは設定を示す。「-25%」の表記は、送信機TXが、高電力モードにおけるその消費電力と比較して、低電力モードにおいて約25パーセント少ない電力を消費することを示す。

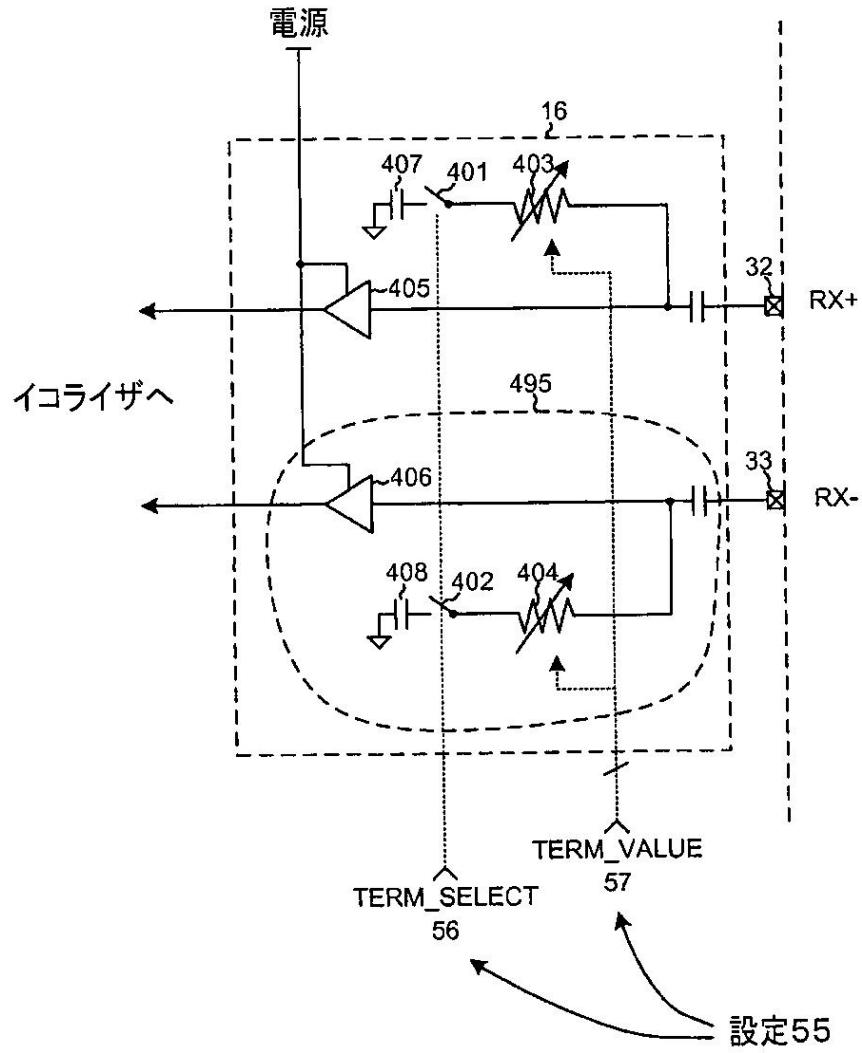

【0018】

第2の設定は、受信機RX16に供給される設定55である。設定55は、1ビット

10

20

30

40

50

終端選択値部分 (TERM\_SELECT) 56 とマルチビット終端値部分 (TERM\_VALUE) 57 を含む。低電力モードでは、端子 32 および 33 から受信機 RX\_16 を見た入力インピーダンスが比較的高くなるように、低インピーダンス終端がディセーブルされる。このインピーダンスは、導線 34 および第 2 の SerDes リンク 35 の他の部分の線路インピーダンスより大きくてよい。このより高い入力インピーダンスを使用することで、概して、悪い受信信号品質を引き起こす望ましくない信号反射が生じる。高電力モードでは、終端がイネーブルされ、受信機 RX\_16 の入力インピーダンスはより低い。一例では、受信機 RX\_16 を見たより低い入力インピーダンスが、導線 34 および第 2 の SerDes リンク 35 の線路インピーダンスに適合させられ、より高い受信機信号品質を生じる。入力インピーダンスの実効値は、マルチビット終端値部分 (TERM\_VALUE) 57 によって決定される。「-20%」の表記によって示されるように、受信機 RX\_16 は、高電力モードにおけるその消費電力と比較して、低電力モードにおいて約 20 パーセント少ない電力を消費する。

10

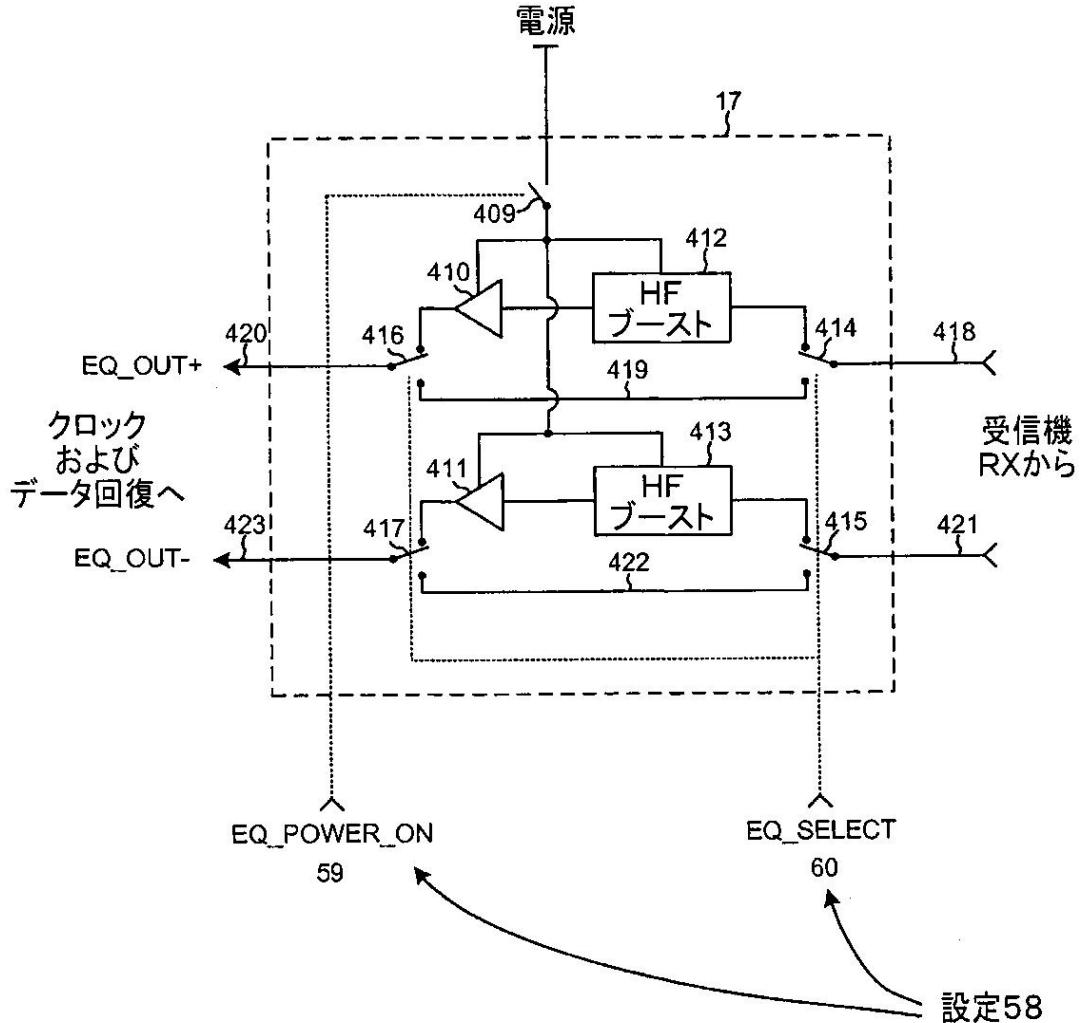

#### 【0019】

第 3 の設定は、イコライザ 17 に供給される設定 58 である。設定 58 は、イコライザ電力オン部分 (EQ\_POWER\_ON) 59 とイコライザ選択部分 (EQ\_SELECT) 60 を含む。低電力モードでは、イコライザオン部分は、イコライザが給電されないようにイコライザをターンオフさせる値を有する。高電力モードでは、イコライザオン部分は、イコライザをターンオンして給電させ、同じく高周波数ブースト機能を完全にイネーブルにさせる値を有する。高周波数ブーストは、イコライザ選択部分 60 の値に応じて、イネーブルされるかまたはディセーブルされる。「-50%」の表記によって示されるように、受信機イコライザ 17 は、高電力モードにおけるその消費電力と比較して、低電力モードにおいて約 50 パーセント少ない電力を消費する。

20

#### 【0020】

第 4 の設定は設定 61 である。設定 61 は、クロックおよびデータ回復 (CDR) 回路 18 に供給される。設定 61 は、2 次選択部分 (SECOND\_ORDER\_SELECT) 62 と細かさ選択部分 (FINE\_SELECT) 63 を含む。低電力モードでは、CDR 回路 18 内のループフィルタ 66 が、1 次のローパスフィルタとして構成されるのに対して、高電力モードでは、ループフィルタが、2 次のローパスフィルタとして構成される。ループフィルタ 66 が 1 次のフィルタとして構成されるかまたは 2 次のフィルタとして構成されるかは、2 次選択部分 62 の値によって決定される。低電力モードでは、クロックおよびデータ回復は、より少ない多相クロック信号（粗い）を使用して行われる。高電力モードでは、クロックおよびデータ回復は、より多い多相クロック信号（細かい）を使用して行われる。より少ない多相クロック信号が使用されるかまたはより多くの多相クロック信号が使用されるかは、細かさ選択部分 63 の値によって決定される。「-25%」の表記によって示されるように、クロックおよびデータ回復回路 18 は、高電力モードにおけるその消費電力と比較して、低電力モードにおいて約 25 パーセント少ない電力を消費する。

30

#### 【0021】

第 5 の設定は、PLL\_12 に供給される設定 64 である。設定 64 は、節電するために、PLL が CDR に対して駆動する多相クロック信号の数が、一定の条件の下で低減されることを可能にする。この特定の例において PLL\_12 に供給される設定 64 は、CDR 回路 18 に供給される設定 61 の細かさ選択部分 (FINE\_SELECT) 63 と同じであるが、他の例では、設定 64 は、PLL の他の部分を制御するために追加のデジタル制御ビットを含んでもよい。低電力モードでは、PLL は、より少ない多相クロック信号を CDR に対して駆動するのに対して、高電力モードでは、PLL は、より多くの多相クロック信号を CDR に対して駆動する。PLL が CDR に対してより少ない多相クロック信号を駆動するかまたはより多い多相クロック信号を駆動するかは、設定 64 の値によって決定される。「-25%」の表記によって示されるように、PLL\_12 は、高電力モードにおけるその消費電力と比較して、低電力モードにおいて約 25 パーセント少

40

50

ない電力を消費する。

**【0022】**

これらの設定 54、55、58、61 および 64 のすべては、コントローラ 6 から導線 65 を介して、図 3 に示す回路 15～18 および 12 のうちの様々な適切な回路に、合成消費電力設定 53 の形態で供給される。コントローラ 6 は、SerDes 送信機部 7 に供給される設定 54 の値を変えることによって、第 1 の SerDes リンク 31 の消費電力を増加または減少させることができる。コントローラ 6 は、SerDes 受信機部 8 に供給される設定 55、58、61 および 64 の値を変えることによって、第 2 の SerDes リンク 35 の消費電力を増加または減少させることができる。SerDes 回路のこれらの様々な部分において消費される電力量と、関連する SerDes リンクのビットエラーレートとの間には関連性がある。回路の部分への消費電力がますます低減されると、ある時点において回路の消費電力のさらなる低下が性能を低下させ始め、ビットエラーレートの増加として現れる。以下でさらに説明するように、SerDes 回路の消費電力設定は、SerDes 回路内で過剰な消費電力が発生しないように調整される。このことは、リンクのエラーレートが、エラーレート範囲の下限が実質的にゼロより大きい許容範囲内に維持されるように、SerDes リンクに対する回路の消費電力を制御することによって達成される。第 1 の SerDes リンク 31 および第 2 の SerDes リンク 35 のそれにおける消費電力は、このようにして制御される。

10

**【0023】**

図 4 は、第 1 の新規な態様による、図 1 のシステム 1 の動作の方法の図である。図 4 の円内の「1」は第 1 のステップを示す。プロセッサ集積回路 3 の SerDes デバイスは、メモリ集積回路 5 の SerDes デバイスから第 2 の SerDes リンクを介して第 1 の SerDes 通信を受信する。図 4 の円内の「2」は第 2 のステップを示す。プロセッサ集積回路 3 のコントローラ 6 内のエラー検出回路 21 は、SerDes 通信のデータペイロードを SerDes 通信の CRC 値と照合し、それにより 1 つまたは複数のビットエラーが発生したかどうかを判断する。図 4 の円内の「3」は第 3 のステップを示す。ビットエラーが発生したかどうかについて判断された情報は、第 2 の SerDes リンクに対するビットエラーレートを決定して更新するために使用される。このビットエラーレートは、レジスタ 23 内で保持される。次いで、第 2 の SerDes リンクに対して更新されたビットエラーレートが、第 2 の SerDes リンクに対する許容ビットエラーレート範囲内にあるかどうかが判断される。更新されたビットエラーレートが許容範囲内にある場合、消費電力設定 53 は調整されない。しかしながら、更新されたビットエラーレートがあまりに低くて許容範囲を下回る場合、プロセッサ集積回路 3 の SerDes 受信機部 8 内の消費電力を低減するように消費電力設定が調整され（図 4 の円内の「4」で示される第 4 のステップ）、それによりビットエラーレートが増大されて許容範囲に戻る。一方、ビットエラーレートがあまりに大きくて許容範囲を上回る場合、プロセッサ集積回路 3 の SerDes 受信機部 8 内の消費電力を増大させるように消費電力設定が調整され（第 4 のステップ）、それによりビットエラーレートが低減されて許容範囲に戻る。

20

30

**【0024】**

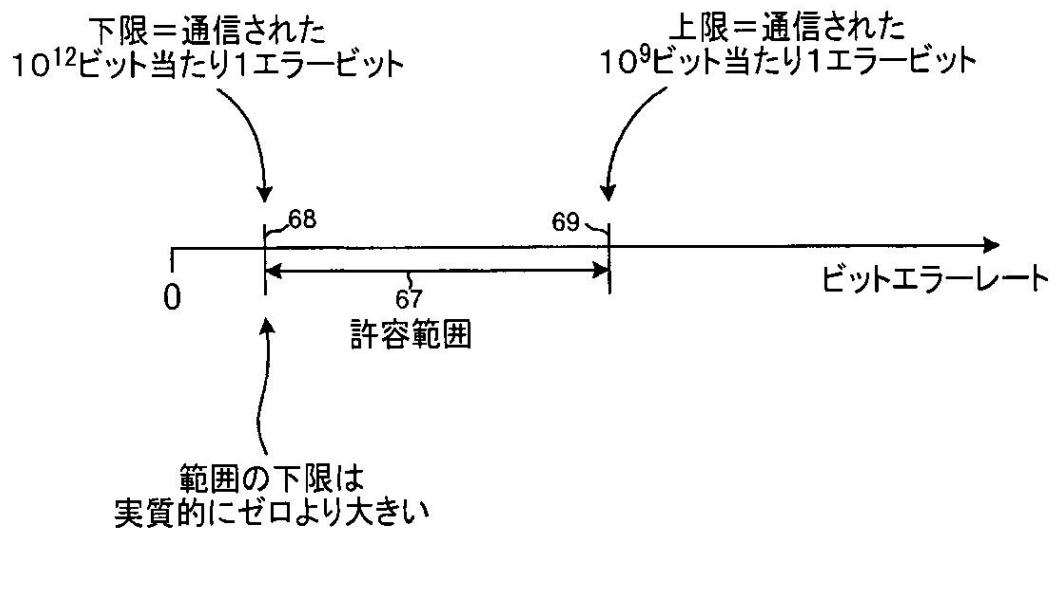

図 5 は、許容可能なビットエラーレート範囲 67 を示す図である。この場合の範囲 67 の下限 68 は、通信された  $10^{12}$  ビット当たりに 1 ビットのエラーである。この場合の範囲 67 の上限 69 は、通信された  $10^9$  ビット当たりに 1 ビットのエラーである。下限 68 は、実質的にゼロより大きいことに留意されたい。消費電力は、可能な最低のビットエラーレートにおいて第 2 の SerDes リンクを最大限高信頼にするために増大されることではなく、むしろ、消費電力は、ビットエラーレートを許容範囲内に保つように制御される。

40

**【0025】**

図 5 の上限および下限は、特定の実施形態に対する例であることを理解されたい。一例では、下限は、再送信を引き起こすタイプのエラー（たとえば、特定の実施形態における二重エラー）が、毎秒約 10 回より高い頻度で発生しないほど十分に低いという意味で、

50

実質的にゼロより大きい。したがって、この場合のビットエラーレートの実際の下限は、当該のSerDesリンクのチャネル特性、ならびに特定の実装形態のSerDes受信回路のエラー検出および訂正機能に依存する。

### 【0026】

図6は、第2の新規な態様による、図1のシステム1の動作の方法の図である。図6の円内の「1」は第1のステップを示す。プロセッサ集積回路3のSerDesデバイス2は、第1のSerDes通信を第1のSerDesリンクを介してメモリ集積回路5のSerDesデバイス4に送信する。図6の円内の「2」は第2のステップを示す。メモリ集積回路5のコントローラ9内のエラー検出回路43は、SerDes通信のデータペイロードをSerDes通信のCRC値と照合し、それにより1つまたは複数のビットエラーが発生したかどうかを判断する。図6の円内の「3」は第3のステップを示す。メモリ集積回路5内のSerDesデバイスは、第2のSerDes通信をプロセッサ集積回路3のSerDesデバイスに戻して送信し、このSerDes通信は、第1のSerDes通信内でどれだけ多くのビットエラーが検出されたかを示すエラー情報を含む。一例では、この第2のSerDes通信は、検出されたビットエラーの数を示すヘルスステータスフラグを含むキープアライブ同期パケットである。図6の円内の「4」は第4のステップを示す。プロセッサ集積回路3のSerDesデバイス内のコントローラ6は第2のSerDes通信を受信し、第1のSerDesリンクに対するビットエラーレートを決定して更新するために、第2のSerDes通信に含まれるエラー情報を使用する。一例では、コントローラ6は、それが、第1のSerDesリンクを介してメモリのSerDesデバイスに送信することを試みるビットの数の実行中の計数を維持する。加えて、コントローラ6は、キープアライブ同期パケット内の、SerDesデバイスによって報告されたビットエラーを合計することによって、第1のSerDesリンクを介して発生したビットエラーの数の実行中の計数を維持する。ビットエラーの総数を、送信を試みられたビットの総数で割った商が、ビットエラーレートである。更新された第1のSerDesリンクに対するビットエラーレートが、レジスタ24内に記憶される。次いで、この更新された第1のSerDesリンクに対するビットエラーレートが、第1のSerDesリンクに対する許容ビットエラーレート範囲内にあるかどうかが判断される。更新されたビットエラーレートが許容範囲内にある場合、第1のSerDesの回路の消費電力設定は調整されない。しかしながら、ビットエラーレートがあまりに低くて許容範囲を下回る場合、プロセッサ集積回路3のSerDesデバイスは、第3のSerDes通信を第1のSerDesリンクを介してメモリ集積回路5のSerDesデバイスに送信する(第5ステップ)。この第3のSerDes通信は、メモリ集積回路5のSerDesデバイス内の受信機回路が、その消費電力を低減することを引き起こす制御パケットまたは他の情報を含み、それにより第1のSerDesリンクのビットエラーレートが増加する。一例では、第3のSerDes通信は、メモリ集積回路5のSerDesデバイスが、受信機RX\_38の入力インピーダンスを増加することを引き起こす(第6ステップ)。このことは、第1のSerDesリンク全体の消費電力を減少させる効果を有し、ビットエラーレートを増加させる影響を有する。ビットエラーレートが第1のSerDesリンクに対して許容範囲内に入るまで、ビットエラーレートは、このようにして増加させられる。しかしながら、更新された第1のSerDesリンクのビットエラーレートが、(第1のSerDesリンクに対する許容範囲を超えて)あまりに大きいと判断される場合、プロセッサ集積回路3のSerDesデバイスは、第3のSerDes通信を第1のSerDesリンクを介してメモリ集積回路5のSerDesデバイスに送信するが、この第3のSerDes通信は、メモリ集積回路5のSerDesデバイスが、受信機RX\_38の入力インピーダンスを低減させることを引き起こす(第6のステップ)制御パケットまたは他の情報を含む。受信機RX\_38の入力インピーダンスを低減させることは、第1のSerDesリンクの消費電力を増加させる影響を有し、それによりビットエラーレートが減少する。第1のSerDesリンクのビットエラーレートは、ビットエラーレートが第1のSerDesリンクに対する許容範囲内に入るまで、このようにして低減される。

10

20

30

40

50

それに応じて、第1および第2のSerDesリンクに対するビットレートは、それらをそれらの許容ビットレート範囲内に維持するために、制御ループ内で制御される。

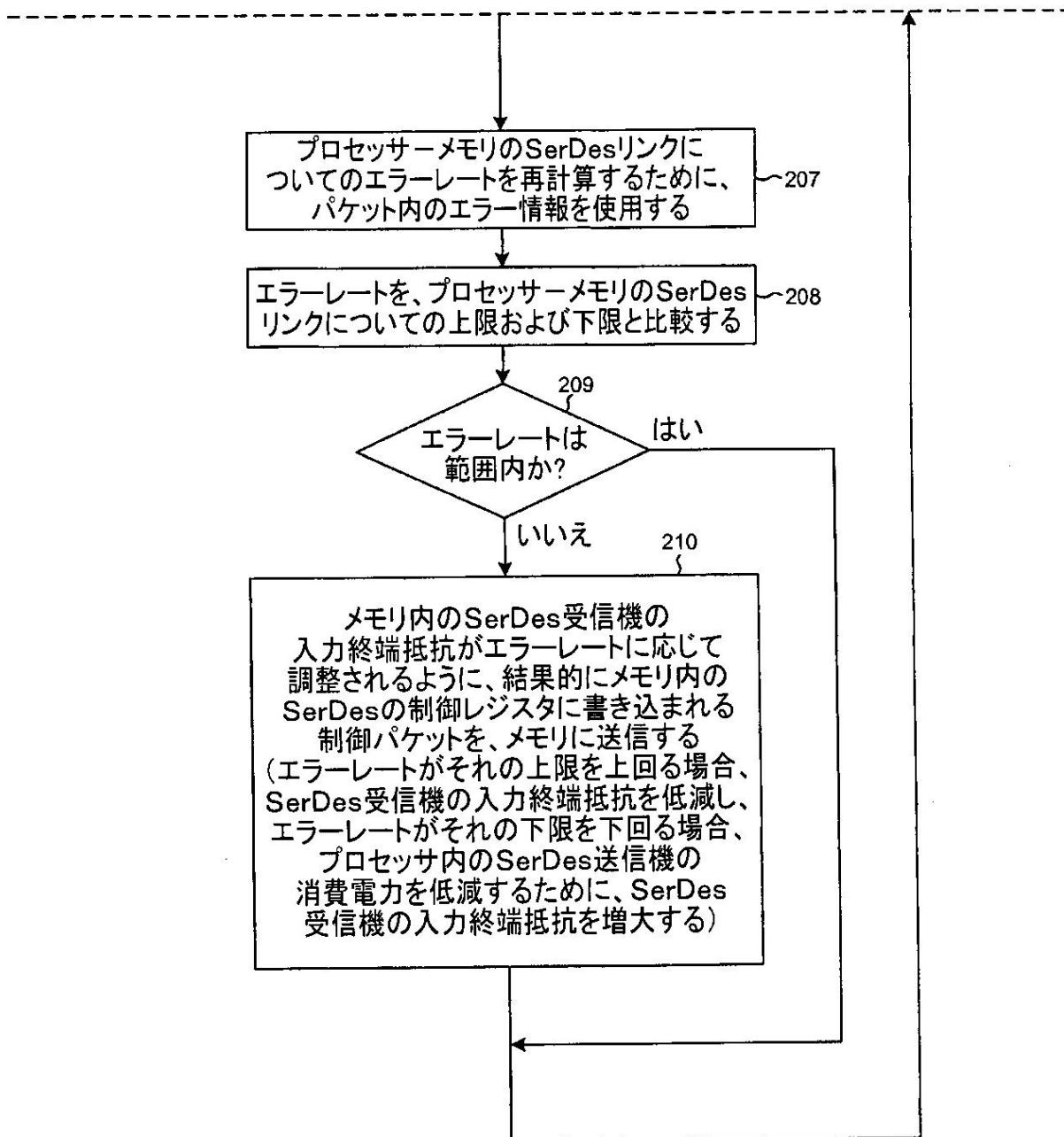

### 【0027】

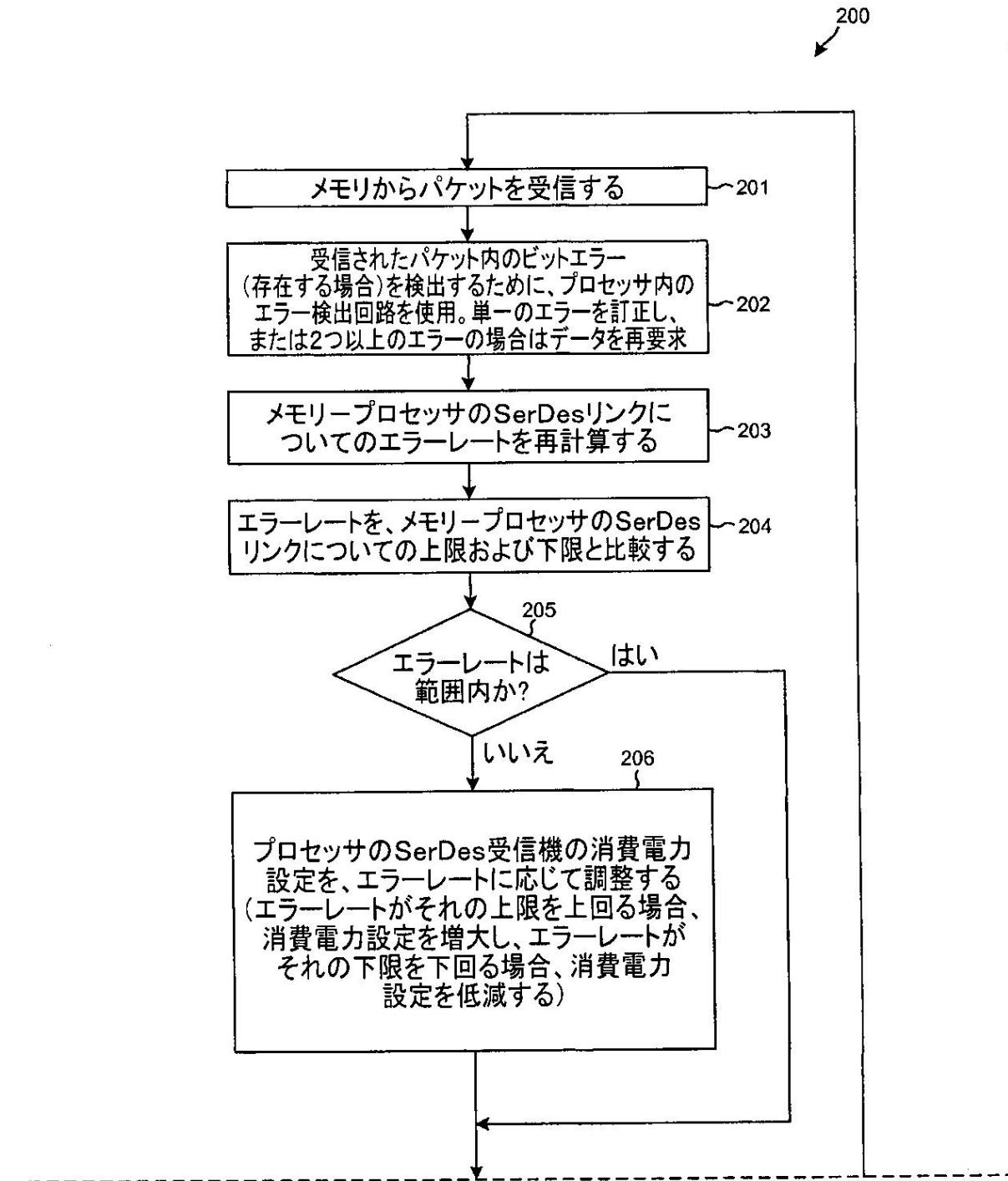

図7(図7Aおよび図7B)は、プロセッサ集積回路3内のSerDesデバイス2によって遂行される方法200のフローチャートである。方法は、第1のSerDesリンク31および第2のSerDesリンク35のビットエラーレートを制御することを伴う。第1に、パケットが、メモリ集積回路5から第2のSerDesリンクを介してプロセッサ集積回路3上で受信される(ステップ201)。プロセッサ集積回路3内のエラー検出回路が、受信されたパケット内のビットエラーの数を検出するために使用される(ステップ202)。データの完全性を維持するために、プロセッサ集積回路3に対するコントローラ6も同様に、パケット内の単一ビットエラーを訂正し、パケット内に2つ以上のエラーがある場合は、メモリからのデータを再要求する。受信されたビット数と検出されたビットエラー数に基づいて、第2のSerDesリンク35に対するビットエラーレートが再計算され(ステップ203)て更新される。次いで、プロセッサ集積回路3内のコントローラ6は、更新されたビットエラーレートを、第2のSerDesリンクに対する許容ビットエラーレート範囲の上限および下限と比較する(ステップ204)。更新されたビットエラーレートが範囲内にある場合(ステップ205)、ステップ206が省略されて、プロセッサ集積回路3のSerDes受信機部8に対する消費電力設定は変更されない。しかしながら、更新されたビットエラーレートが範囲内にない場合(ステップ205)、プロセッサ集積回路3のSerDes受信機部8に対する消費電力設定が、ビットエラーレートを範囲内に戻す方法などで調整される(ステップ206)。更新されたビットエラーレートがあまりに高い場合、この調整は、ビットエラーレートを制限しているSerDes受信機の一部の消費電力を増加させることを伴う。更新されたビットエラーレートがあまりに低い場合、SerDes受信機に対する消費電力は、ビットエラーレートが許容範囲内に戻るまで削減される。

### 【0028】

ステップ201における受信されたパケットは、第1のSerDesリンク31を介する以前のSerDes通信に関するメモリ集積回路5内のSerDesデバイスによって生成されたエラー情報を含む。エラー情報は、たとえば、第1のSerDesリンク31を介する以前のSerDes通信内でメモリ集積回路によって検出されていたビットエラーの数を示すことができる。ステップ207で、このエラー情報が、第1のSerDesリンクに対するエラーレートを再計算するために使用される。プロセッサ集積回路3内のコントローラ6は、第1のSerDesリンク31を介してメモリ集積回路5に転送されたビットの総数の合計を保持し、コントローラ6は、メモリ集積回路5によって検出されるにつれて、これらの通信内のビットエラーの総数の経過を追うために、エラー情報を使用する。次いで、得られた、更新された第1のSerDesリンク31に対するビットエラーレートは、第1のSerDesリンク31に対する許容エラーレート範囲の上限および下限と比較される(ステップ208)。更新されたビットエラーレートが範囲内にある場合(ステップ209)、ステップ210が省略されて、プロセッサ集積回路3が、メモリ集積回路5がSerDes受信機38の入力インピーダンスを変更することを引き起こさせることない。しかしながら、更新されたビットエラーレートが範囲内にない場合(ステップ209)、プロセッサ集積回路3のSerDesデバイスは、制御パケットを第1のSerDesリンク31を介してメモリ集積回路5のSerDesデバイスに送信し(ステップ210)、この制御パケットは、SerDes受信機38の入力インピーダンスが、ビットエラーレートを範囲内に戻す方法などで調整されることを引き起こす。更新されたビットエラーレートがあまりに高い場合、制御パケットは、入力インピーダンスが低減されることを引き起こし、それにより第1のSerDesリンク31の一部の消費電力が増加してビットエラーレートが減少する。更新されたビットエラーレートがあまりに低い場合、制御パケットは、入力インピーダンスが増大されることを引き起こし、それにより第1のSerDesリンク31の一部の消費電力が減少してビットエラーレートが増

10

20

30

40

50

加する。制御パケットは、たとえば、SerDes受信機38の制御レジスタ（図示せず）への書き込みを引き起こすことができ、制御レジスタ内の値がSerDes受信機38の入力インピーダンスを決定する。

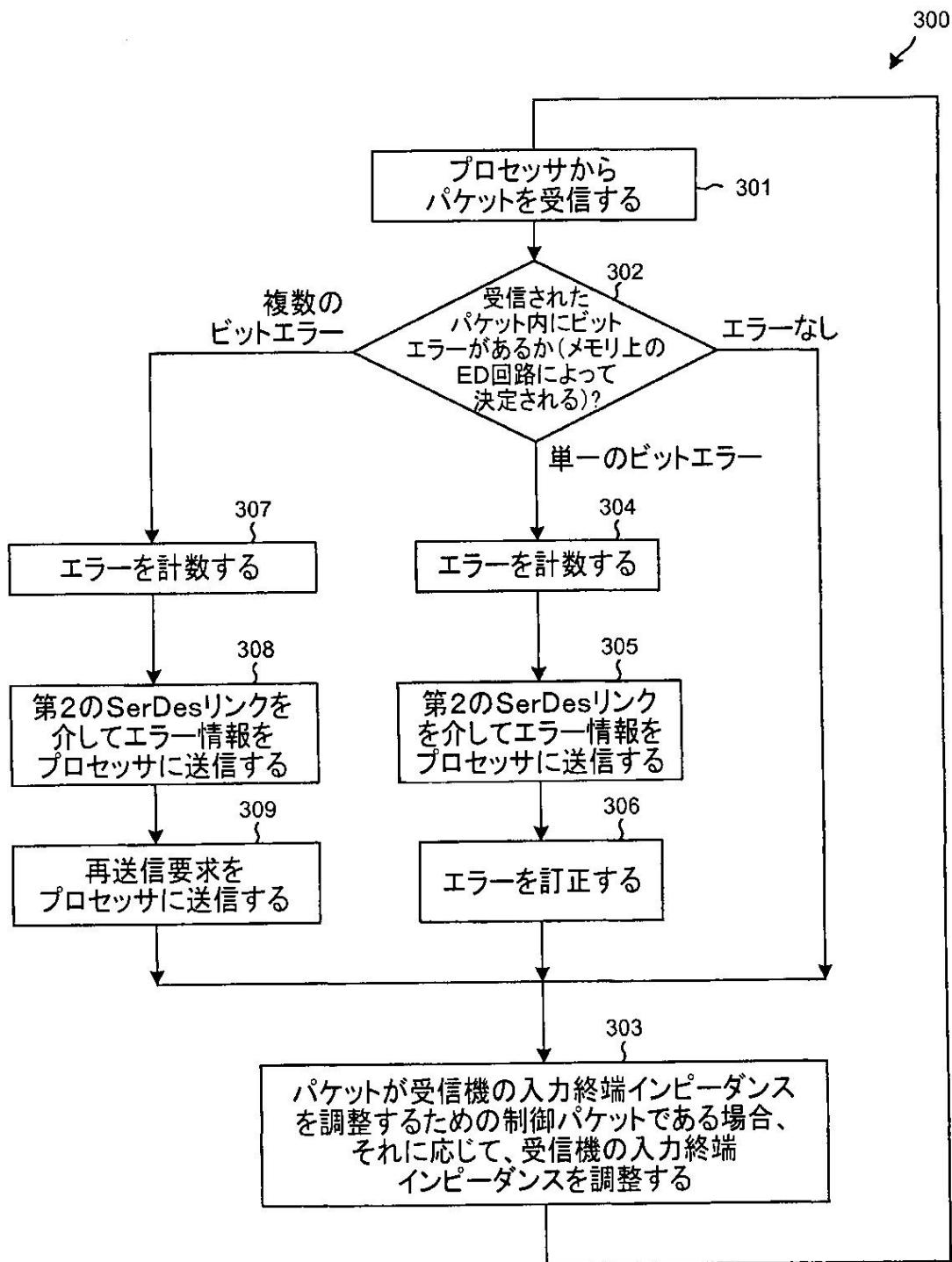

#### 【0029】

図8は、メモリ集積回路5内のSerDesデバイス4によって遂行される方法300のフローチャートである。パケットは、プロセッサ集積回路3から第1のSerDesリンク31を介して受信される。エラー検出回路43は、パケットの受信の中に1つまたは複数のビットエラーが存在するかどうかを判断するために、パケットのデータペイロードをパケット内で搬送されたCRCと照合する（ステップ302）。ステップ302でエラーが検出されなかった場合、処理は、直接ステップ303に進む。パケットが、SerDes受信機38の入力インピーダンスを調整するための制御パケットである場合、SerDes受信機の入力インピーダンスが、それに応じて調整される（ステップ303）。しかしながら、ステップ302で1つのエラーが検出された場合、コントローラ9は、第1のSerDesリンク31に対してコントローラ9上で保持されている（オプション）エラー回数の合計を増分し（ステップ304）、エラー情報を第2のSerDesリンク35を介してプロセッサ集積回路3内のSerDesデバイス2に送信し（ステップ305）、エラー情報は検出されたビットエラーの数を示す。エラー検出および訂正方式が使用され、着信パケットが単一のビットエラーを含む場合は、検出回路43が単一のエラーを検出してエラー訂正回路44がエラーを訂正するのに対して、着信パケットが2つのビットエラーを含む場合は、検出回路43が2つのエラーを検出するが、エラー訂正回路44は両エラーを訂正し得ない。したがって、ステップ306で、エラー訂正回路44は、着信パケット内の単一のビットエラーを訂正してデータペイロードを適宜に使用する。ステップ302で複数のエラーが検出された場合、処理は、直接ステップ307に進む。第1のSerDesリンク31に対するエラー回数の合計は、検出されたビットエラーの数だけ増分され（ステップ302）、メモリ集積回路5内のSerDesデバイスは、エラー情報を第2のSerDesリンク35を介してプロセッサ集積回路3内のSerDesデバイス2に送信し（ステップ308）、エラー情報は、検出されたビットエラーの数を示す。メモリ集積回路5内のSerDesデバイス4もまた、再送信要求を第2のSerDesリンク35を介してプロセッサ集積回路3内のSerDesデバイス2に送信し（ステップ309）、再送信要求は、複数のエラーを有することが検出されたパケットを再送信するための要求である。再送信要求は、ステップ308のエラー情報を含むパケットと同じパケットであってよく、または再送信要求は、異なるパケットであってよい。

#### 【0030】

図9は、SerDes受信機16の一例のより詳細な図である。この例におけるSerDes受信機38は、同一の構造である。端子RX+32および端末RX-33は、導線34から1ギガビット毎秒のビットレートの差動着信信号を受信する。終端入力インピーダンスオン／オフ信号TERM\_SELECT\_56は、1ビットのデジタル信号であり、かつ設定55の一部であり、マルチビットデジタル終端入力インピーダンス振幅制御信号TERM\_VALUE\_57も設定55の一部である。TERM\_SELECT\_56がデジタル論理低である場合、スイッチ401および402は図示のように開であるのに対して、TERM\_SELECT\_56がデジタル論理高である場合、スイッチ401および402は閉である。スイッチが開である場合、受信機RX\_16を見たインピーダンスは高く、抵抗器403および404の抵抗による影響を受けない。入力インピーダンスは、増幅器405および406の入力インピーダンスである。これは、比較的高い入力インピーダンスである。スイッチが閉である場合、受信機RX\_16を見たインピーダンスは低く、抵抗器403および404の抵抗、ならびにキャパシタ407および408のキャパシタンスによる影響を受ける。

#### 【0031】

図10は、イコライザ17の一例のより詳細な図である。その低電力モードまたは設定において、1ビットデジタル信号EQ\_POWER\_ON\_59は、デジタル論理低で

あり、スイッチ 409 は開であり、それによりアクティブ回路 410 ~ 413 は給電されない。1ビットデジタル信号 EQ\_SELECT\_60 もまたデジタル論理低であり、スイッチ 414 および 416 は、入力リード線 418 上の信号が、導線 419 を介してディセーブルされ、給電されないアクティブ回路 410 および 412 をバイパスし、出力リード線 420 に進むように設定される。同様に、スイッチ 415 および 417 は、入力リード線 421 上の信号が、導線 422 を介してディセーブルされ、給電されないアクティブ回路 411 および 413 をバイパスし、出力リード線 423 に進むように設定される。その高電力モードまたは設定において、EQ\_POWER\_ON\_59 はデジタル論理高であり、スイッチ 409 は閉であり、それによりアクティブ回路 410 ~ 413 は給電される。EQ\_SELECT\_60 はデジタル論理高であり、スイッチ 414 および 416 は図 10 に示す位置にある。入力リード線 418 上の信号は、高周波数ブースト回路 412 を通り、次いで増幅器 410 を通って出力リード線 420 に進む。入力リード線 421 上の信号は、高周波数ブースト回路 413 を通り、次いで増幅器 411 を通って出力リード線 423 に進む。高周波数ブースト回路 412 および 413 は、高周波数成分の信号が増幅される量と比較して、より少ない量の増幅（2dB 少ない利得）で処理された低周波数成分の信号を通す回路である。この例では、高周波数成分は、700MHz 以上の周波数の成分である。高周波数ブーストは、SersDes リンク 35 が帯域制限チャネルである状況において、受信機性能を改善する。制御信号 EQ\_POWER\_ON\_59 および EQ\_SELECT\_60 はともに、イコライザに供給される設定 58 を構成する。

## 【0032】

図 11 は、図 3 の CDR 回路 18 の 4 相サンプラ部 424 の簡略図である。図 11 の入力リード線 425 は、図 10 の出力リード線 420 に結合される。2 本のリード線は、同じ導線およびノードの部品である。同様に、図 11 の入力リード線 426 は、図 10 の出力リード線 423 に結合される。2 本のリード線は、同じ導線およびノードの部品である。信号 0°、90°、180° および 270° は、PLL 12 から受信される 4 相クロック信号である。これらの信号は、1 ギガビット毎秒の通信レートの半分の周波数である。スイッチ 427 ~ 434 の動作によって、比較器 435 ~ 438 は、入力リード線 425 および 426 上の差動信号をシングルエンドのデジタル信号に量子化する。この量子化は、0 度、90 度、180 度および 270 度の 4 つのサンプル時間において発生する。比較器 435 ~ 438 は、出力リード線 439 ~ 442 上に、シングルエンドのサンプル値データ信号 0°SD、90°SD、180°SD および 270°SD を出力する。

## 【0033】

図 12 は、図 3 の CDR 回路 18 のアーリーレート (early-late) 検出器部 443 の図である。アーリーレート検出器部の入力リード線 444 ~ 447 は、図 11 の 4 相のサンプラ部 424 の出力リード線 439 ~ 442 に結合される。着信するサンプル値データ信号 0°SD、90°SD、180°SD および 270°SD は、導線 452 上の信号 0° の立上りエッジのときに、フリップフロップ 448 ~ 451 によって記憶される。この信号「0°」は、図 15 の回路によって出力される、クロックを回復された信号である。表 453 は、参照用テーブル 455 による出力として、導線 454 上の 2 ビット値 H/R/A (停止 (Hold) / 遅延 (Retard) / 進める (Advance)) の意味を示す。2 ビット値 H/R/A は、データのサンプリングが理想的であるように、回復されたクロックが位相を進められるべきか、位相を調整すべきでないか、または位相を遅延されるべきかを示す。

## 【0034】

図 13 は、並列化器 19 の動作を示す図である。入力リード線 456 上の信号 0°SD および入力リード線 457 上の信号 180°SD は、データの偶数および奇数のサンプルを表す。信号 0°SD は、図 11 の出力リード線 439 上の信号である。信号 180°SD は、図 11 の出力リード線 441 上の信号である。並列化器 19 は、シフトレジスタと、制御回路と、マルチプレクサとを含む。0°SD 信号および 180°SD 信号の値は、前後に次々と交番方式でシフトレジスタ内にシフトされる。8 つのこれらのシフトイン動作の最後に得られた、シフトレジスタの 8 ビット並列出力が、導線 459 上の信号 458

10

20

30

40

50

である。これらの8ビット値の連続する値のそれぞれが、シフトレジスタの出力において真(valid)になると、それぞれは、コントローラ6内の先入れ先出し(FIFO)のエラスティックバッファ460に押し込まれる。CPUは、別のポートを介してFIFOのエラスティックバッファ460からデータを読み取る。並列化器19によるFIFO460への書き込みおよびCPUによるFIFO460からの読み取りは、互いに非同期であるが同じ公称レートを有する。(並列化器を出てコントローラ内に進む並列データおよびコントローラから直列化器内に進む並列データは、8ビット以外のビット数であってよいことを理解されたい。本明細書で説明する8ビット並列データは、単なる一例である。)

図14は、図3のCDR回路18内のループフィルタ66の図である。ループフィルタは、図12のアーリーレート検出器443からの2ビットデジタル値H/R/Aのストリームをフィルタリングするデジタルフィルタである。破線461内の回路だけが使用される場合、デジタルフィルタは、1次のローパスフィルタとなるように構成される。破線462内の全回路が使用される場合、デジタルフィルタは、2次のローパスフィルタとなるように構成される。ループフィルタ66が1次のローパスフィルタまたは2次のローパスフィルタのいずれに構成されるかにかかわらず、フィルタの出力は、導線463上の16ビット値のストリームとして現れる。入力リード線464上のSECOND\_ORDER\_SEL信号62は、図3のCDR回路18に供給される設定61の一部である。2次のフィルタがディセーブルされると、クロック信号CLKは、アキュムレータ466をクロッキングすることを(開であるスイッチ465で表されるように)阻止されるのに対して、2次のフィルタがイネーブルされると、クロック信号CLKはゲートオフされない。回路はデジタルであるので、消費電力は低減される。というのはデジタル回路の静的消費電力は低いからである。2次のフィルタがディセーブルされると、スイッチ467および468は図示の位置にあるのに対して、2次のフィルタがイネーブルされると、スイッチ467および468は図示と反対の位置にある。導線463上の16ビット信号は、ループフィルタのローパスフィルタリング効果によってゆっくりと変化する信号である。

#### 【0035】

図15は、図3のCDR18の4相クロック発生部469の図である。ループフィルタ66からの16ビット値のそれぞれの5つの最上位ビット470は、PLLから受信された500MHzのマスタークロック472の多相信号471のうちのいくつかの信号を選択するために使用される。矢印472は、低電力モードにおける500MHzマスタークロック信号のうちの4相か、または高電力モードにおける500MHzのマスタークロックのうちの8相のいずれかを表す。8つの信号導線があるが、低電力モードでは、導線のうちの4つの上で駆動される信号は存在しない。低電力モードでは、16の異なる多相信号471が存在する(16の導線の各ペアが、このモードにおいて異なる位相の信号を搬送する)のに対して、高電力モードでは、32の異なる多相信号471が存在する(32の導線のそれぞれが、このモードにおいて異なる位相の信号を搬送する)。

#### 【0036】

多相信号471のうちの適切な信号を選択するために、ループフィルタから受信された各16ビット値のうちの5つの最上位ビット470が、参照用テーブル473に供給される。参照用テーブル473の出力は、多相信号471のうちのどの1つが0°の信号としてマルチプレクサ474によって導線475に供給されるか、多相信号471のうちのどの1つが90°の信号としてマルチプレクサ476によって導線477に供給されるか、多相信号471のうちのどの1つが180°の信号としてマルチプレクサ478によって導線479に供給されるか、および多相信号471のうちのどの1つが270°の信号としてマルチプレクサ480によって導線481に供給されるかを判断する。参照用テーブル473は、0°、90°、180°および270°のそれぞれに対して選択された多相信号を進めるべきか、保持すべきか、または遅延すべきかを示す、着信する5ビット値470からのマッピングを提供する。マルチプレクサ474、476、478および480を制御する5ビット選択信号は、それらのそれぞれのマルチプレクサを選択し、それにより、マルチプレクサによって選択された多相信号のうちの信号が、位相を前にともにシフ

10

20

30

40

50

トするか、位相を保持するか、または位相を後ろにシフトされる。導線 475、477、479 および 481 上の 4 つの信号の位相のこの調整は、着信データの各ビット時間内に、サンプリング時間の位置の前進、保持または遅延のいずれかをもたらす。

#### 【0037】

4 相クロック発生器部 469 の 2 つのモード、細かいモードおよび粗いモードが存在する。細かいモードが高電力モードであるのに対して、粗いモードは低電力モードである。2 つのモードのうちのいずれのモードが使用されているかは、1 ビットの FINE SELECT 入力信号 63 によって決定される。細かいモードが選択される場合、32 の位相信号が必要であり、マルチブレクサ 474、476、478 および 480 は、32 位相のうちの 1 つを選択するように作られる。多相補間器 481 は、PLL から 8 位相 472 を受信し、より細かい位相分解能のために、それらから 32 位相を補間する。同様に、参照用テーブル 473 は、32 の可能な入力信号のうちの 1 つを選択するために、マルチブレクサのそれぞれを制御する。細かいモードでは、多相補間器 481 から来る 32 の導線のそれぞれが、異なる位相の信号を搬送する。粗いモードが選択される場合、マルチブレクサ 474、476、478 および 480 のそれぞれは、16 の異なる位相のうちの 1 つだけを選択する。多相補間器 481 は、PLL から 4 位相を受信し、マルチブレクサに供給するために、それらから 16 位相を補間する。粗いモードでは、多相補間器 481 から来る 32 の導線の連続するペアのそれぞれが、異なる位相の信号を搬送するので、16 だけの異なる位相が、多相補間器 481 によって提供される。

10

#### 【0038】

図 16 は、PLL 12 の簡略図である。PLL 12 は、位相検出器 482 と、ループフィルタ 483 と、8 位相 VCO 484 と、ループディバイダ 485 とを含む。到来する基準クロック REF\_FREQ は、たとえば、水晶発振器または他の高精度基準から得ることができる。VCO 484 は、制御された周波数の 1 つの信号を出力するだけではなく、VCO 484 は、8 バージョンの信号を 8 つの異なる、均等に離間した位相を出力する。これらの 8 つの信号は、クロックブロッキング回路 486 に供給される。FINE SELECT 信号 63 が細かいモードを選択している場合、8 バージョンのクロック信号は、すべて、クロックブロッキング回路 486 を通過して 8 つの導線 487 に乗る。細かいモードにおいて上記で説明したように、これらの 8 つの導線 487 は、8 バージョンのマスタークロックを図 15 の 4 相クロック発生器 469 に供給する。しかしながら、FINE SELECT 信号 63 が粗いモードを選択している場合、クロックブロッキング回路 486 から来る 8 つの導線 487 の 1 つおきの導線は、駆動されない。4 つの異なる位相信号だけがクロックブロッキング回路 486 から駆動され、したがって、8 つの導線のすべてが駆動される細かいモードの動作と比較して電力が節約される。

20

30

#### 【0039】

図 17 は、PLL 12 から導線 487 上に出力される信号を示す表である。チャートの中間列は、細かいモード動作を表す。8 つの導線のすべてが、クロック信号で駆動され、各信号は異なる位相を有する。チャートの右端の列は、粗いモード動作を表す。8 つの導線のうちの半分だけが、クロック信号で駆動される。

40

#### 【0040】

図 18 は、送信回路の簡略図である。コントローラ 6 は、送信のための 8 ビット並列データを供給する。8 ビット値は、125MHz のレートで供給される。直列化器 14 は、並列化器 19 に関して上記で説明した直並列変換動作の逆を実行する。直列化器 14 は、着信データストリームから偶数信号と奇数信号とを生成し、これらの偶数および奇数の信号が、次いで、データを单一の直列ストリーム内にアップサンプリングするために使用される。得られたアップサンプリングされたデータの直列ストリームは、1 ギガビット毎秒の出力データレートを有する。プリドライバ 488 は、着信するデジタルビットのシングルエンドストリームを取得するアナログ増幅器であり、このストリームから 2 つの異なるアナログ出力信号を生成する。1 つの信号は、導線 491 を介して出力ドライバ 489 に供給される。もう 1 つの信号は、導線 492 を介して出力ドライバ 490 に供給される。

50

出力ドライバ 489 および 490 は、デジタルに制御される出力インピーダンスを有する。出力インピーダンスが低いほど駆動される信号は強いが、より多くの電力が消費される。マルチビットデジタル信号 OUTPUT\_VALUE は、この出力インピーダンスを判断し、また図 3 に示された設定 54 である。

#### 【0041】

電流源記号 493 および 494 のそれぞれは、制御された電流源である。データ入力信号がデジタル論理 1 の値を有するときは、電流源はオンであり、電流制限された量の電流を供給しているが、データ入力信号がデジタル論理 0 の値を有するときは、電流源はオフであり、電流は供給されない。オンであるとき電流源が供給する電流の最大の量は、OUTPUT\_VALUE 信号によって判断される。端子 TX+ または TX- のうちの一方の信号が高に遷移すると、関連する電流源はその電流制限された量の電流を供給しようとする。このことが、出力端末の電圧を、電圧が電源電圧 (SUPPLY POWER) に達するまで上昇させ、その時点で電流源は電圧制限され、電流をほとんど供給しない。端子の信号が低に遷移すると、関連する電流源がターンオフされ、それにより出力端末の電圧が、送信機内および SerDes リンクの他端の受信機内のプルダウンインピーダンスによって接地電位にプルダウンされる。

#### 【0042】

図 19 は、SerDes 受信機の入力インピーダンスを下げることで、いかにして送信機の SerDes ドライバの消費電力が低減する結果が生じるかを示す図である。図 1 の SerDes 送信機 15 のバッファ 490 を、図 19 の左に示す。図 1 の SerDes 受信機 38 の半分 495 を、図 19 の右に示す。信号 DATA\_B がデジタル論理低に遷移すると、電流源 494 はターンオンされる。端子 TX- の電圧は、引き上げられて高に遷移する。電流源 494 によって供給される電流は、送信機内でインピーダンス 496 を通って接地に至る電流経路 497 と、受信機 495 内で抵抗器 404 を通って設置に至る電流経路 498 との間で分割される。電流源 494 は、電源導線 490A の固定電源電圧によって給電され、電流源 494 は比較的大量の電流を供給することができ、それゆえ、図 19 の回路内で、電流源 494 によって供給される電流の量は、実際には、送信機の抵抗 496 および受信機の抵抗 404 によって制限される。したがって、抵抗 404 を低減することで、送信機の電流源 494 からより多くの電流が引き出される。逆に、抵抗 404 を増加させることで、送信機の電流源 494 からより少ない電流が引き出される。受信機の入力インピーダンスを増加させることは、送信機での消費電力を減少させると言われている。導線 30 は、しばしば接地インピーダンスと呼ばれる対地インピーダンス（たとえば、対地 50 オーム）を有する。従来のように、送信機の出力インピーダンスと受信機の入力インピーダンスとを線路インピーダンスに整合させるのではなく、システム全体で消費電力を低減するために、受信機の入力インピーダンスが線路インピーダンスより故意に高くされる。ビットエラーレートを許容範囲内に保つために、不整合の程度が制御され、許容範囲の下限は、実質的にゼロより大きい。SerDes リンクはビットエラーを最小化するようには動作するのではないが、ビットエラーレートは許容可能であり、消費電力は、伝送線路が従来の方法で終端される状況と比較して低減される。単一ビットエラーを検出して訂正することができるエラー検出および訂正回路を SerDes 受信機内に設けることによって、許容可能なビットエラーレート範囲の下限が実質的にゼロより大になるように設定されているという事実にもかかわらず、SerDes リンクを介してデータを正常に通信するために再送信する必要性が、低減または排除される。

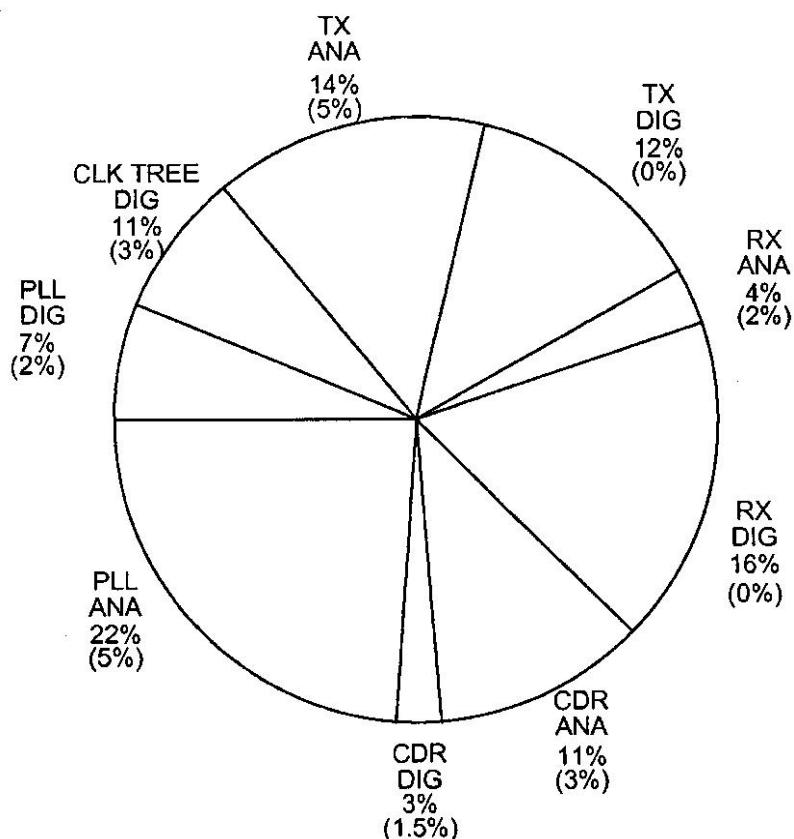

#### 【0043】

図 20 は、プロセッサ集積回路 3 内の SerDes デバイス 2 における消費電力の内訳を示すパイチャートである。チャートの各セクションに対して、丸括弧内にないパーセンテージ数が、高電力モードで動作しているときに消費される全消費電力のパーセンテージを示すのに対して、丸括弧で囲まれるパーセンテージ数が、低電力モードで動作することによって節約される全消費電力のパーセンテージを示す。たとえば、「RX\_ANA 4% (2%)」は、低電力モードにおいて SerDes 受信機 RX のアナログ部が（全 SerDes

10

20

30

40

50

r D e s デバイス 2 の ) 全消費電力の 4 パーセントを消費することを示す。 「 R X A N A 4 % ( 2 % ) 」 の 2 % は、低電力モードにおいて全体的な全消費電力 ( 全 S e r D e s デバイス 2 の全消費電力 ) の 2 パーセントが、 S e r D e s 受信機 R X を低電力モードで動作させることによってその受信機のアナログ部において節約されることを示す。チャートでは、「 D I G 」は、回路のデジタル部を意味し、「 A N A 」は回路のアナログ部を意味する。「 R X 」は S e r D e s 受信機 R X を意味し、「 C D R 」はクロックおよびデータ回復回路を意味し、「 P L L 」は位相ロックループを意味し、「 C L K T R E E 」は各クロック位相をそれらのそれぞれの宛先に分配するアクティブなクロックバッファおよび相互接続を意味し、「 T X 」は S e r D e s 送信機 T X を意味する。本実施形態では、 S e r D e s リンクの S e r D e s 送信機部内で可能であるよりも多くの消費電力の節約が、 S e r D e s リンクの S e r D e s 受信機内で可能である。

10

## 【 0 0 4 4 】

図 2 1 は、高電力モードおよび低電力モードにおける S e r D e s デバイス 2 の全消費電力を示す表である。低電力モードでイコライザオンに対する「 - 2 0 . 5 % 」の表記は、消費電力が、高電力モードにおけるよりも 2 0 . 5 % 少ないことを意味する。

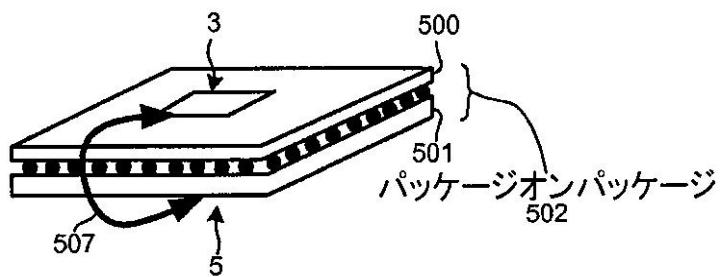

## 【 0 0 4 5 】

図 2 2 ~ 図 2 4 は、プロセッサ集積回路 3 とメモリ集積回路 5 との間の S e r D e s リンクが異なる量の帯域制限を有する例を示す。図 2 2 は、 S e r D e s リンクが広帯域チャネルである一例を示す。太い両矢印 5 0 7 は、広帯域チャネルを表す。プロセッサ集積回路 3 は第 1 のパッケージ 5 0 0 内にあり、メモリ集積回路 5 は P O P ( パッケージオンパッケージ ( Package-On-Package ) ) アセンブリ 5 0 2 の第 2 のパッケージ 5 0 1 内にある。チャネルは、一方の集積回路からそのパッケージを通り、 P O P のボンドボールを通って別のパッケージに入り、他方の集積回路まで延在する。チャネル内の帯域制限によるビットエラーレートは存在しない。したがって、均等化の高周波数ブーストはディセーブルされ、上記で説明したすべての他の節電特徴が、消費電力を低減するために動的に使用される。

20

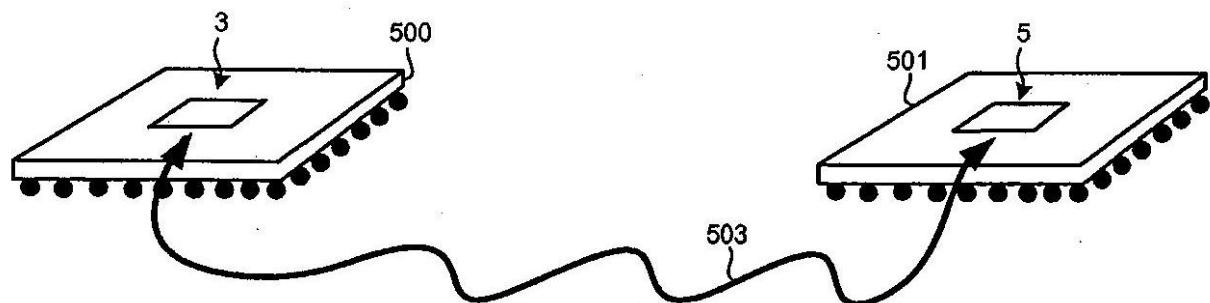

## 【 0 0 4 6 】

図 2 3 は、 S e r D e s リンクがわずかに帯域制限されたチャネルである一例を示す。集積回路 3 および 5 がパッケージングされ、パッケージ 5 0 0 および 5 0 1 が P C B ( プリント回路板 ) 上に搭載され、それにより S e r D e s リンクは、一方の集積回路からそのパッケージを通り、 P C B 上の配線および導線 5 0 3 を通り、別のパッケージを通って他方の集積回路まで延在する。したがって、均等化の高周波数ブーストはイネーブルされて動的に使用され、上記で説明したすべての他の節電特徴が、消費電力を低減するために動的に使用される。

30

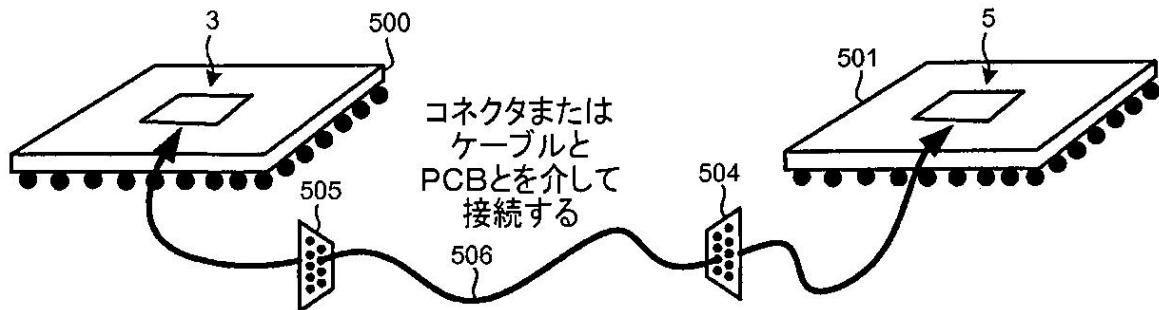

## 【 0 0 4 7 】

図 2 4 は、 S e r D e s リンクが実質的に帯域制限されたチャネルである一例を示す。メモリ集積回路 5 は、メモリスティックの一部であるパッケージ 5 0 1 内にある。メモリスティックは、マザーボード P C B 上のコネクタに差し込まれる。図中のコネクタ記号 5 0 4 は、このコネクタを表す。プロセッサ集積回路 3 はパッケージ 5 0 0 内にあり、このパッケージ 5 0 0 は、今度は P C B に搭載されるソケット内にある。ソケットは、コネクタ記号 5 0 5 で表される。 S e r D e s リンク 5 0 6 は、プロセッサ集積回路 3 からそのパッケージ 5 0 0 を通り、ソケット 5 0 5 を通り、 P C B を通り、 P C B 上のメモリスティックコネクタ 5 0 4 を通り、メモリスティックに入り、メモリ集積回路のパッケージ 5 0 1 を通り、メモリ集積回路 5 まで延在する。したがって、均等化の高周波数ブーストはイネーブルされて動的に使用され、上記で説明したすべての他の節電特徴が、消費電力を低減するために動的に使用される。

40

## 【 0 0 4 8 】

第 1 の例では、プロセッサ集積回路 3 の C P U 2 5 は、電源投入および初期化時に、構成情報 ( チャネルタイプおよび / または特性を示す情報 ) を読み取り、その構成情報からそのチャネル環境を決定する。それの決定された環境の知識に基づいて、 C P U 2

50

5は、適切な消費電力節約モード中にあるように、バス機構27を介してSerDesコントローラを構成する。記号27は、いくつかの特定のバス幅の単一の並列バスだけを表すのではなく、1つまたは複数のバスおよび他の回路を伴い得るバス機構を、より全体的に表す。第2の例では、CPUおよびSerDesコントローラは、チャネルタイプを検出し、検出されたチャネルタイプに対する適切な消費電力モード中にあるようにSerDes低電力回路を自動的に構成するために、検出されたビットエラーレートを使用する。この自動構成は、特別な構成情報を読み取る必要なしに、同じSerDesインターフェース設計が異なるタイプの製品およびシステムで使用されることを可能にする。この自動構成はまた、単一の製品の製造ばらつきにわたってユニットごとに最適化された性能（ビットエラーレートのトレードオフに対する最適な消費電力）を可能にする。ユニットは、時間とともに変化する動作パラメータに対応するため、およびユニットの動作環境における変化に対応するように、性能（ビットエラーレートのトレードオフに対する最適な消費電力）を最適化するように動作するので、單一ユニットのSerDesインターフェースは、時間とともにそれ自体を自動的に再構成することができる。

#### 【0049】

1つまたは複数の例示的な実施形態では、説明した機能はハードウェア、ソフトウェア、ファームウェア、またはそれらの任意の組合せで実装できる。ソフトウェアで実装する場合、機能は、1つまたは複数の命令またはコードとしてコンピュータ可読媒体上に記憶するか、あるいはコンピュータ可読媒体を介して送信することができる。コンピュータ可読媒体は、ある場所から別の場所へのコンピュータプログラムの転送を可能にする任意の媒体を含む、コンピュータ記憶媒体とコンピュータ通信媒体の両方を含む。記憶媒体は、コンピュータによってアクセスできる任意の利用可能な媒体でよい。限定ではなく例として、そのようなコンピュータ可読媒体は、RAM、ROM、EEPROM、CD-ROM、あるいは他の光ディスクストレージ、磁気ディスクストレージまたは他の磁気記憶デバイス、もしくは命令またはデータ構造の形態の所望のプログラムコードを搬送または記憶するために使用でき、コンピュータによってアクセスできる任意の他の媒体を備えることができる。さらに、いかなる接続もコンピュータ可読媒体と適切に呼ばれる。たとえば、ソフトウェアが、同軸ケーブル、光ファイバーケーブル、ツイストペア、デジタル加入者回線（DSL）、または赤外線、無線、およびマイクロ波などのワイヤレス技術を使用して、ウェブサイト、サーバ、または他のリモートソースから送信される場合、同軸ケーブル、光ファイバーケーブル、ツイストペア、DSL、または赤外線、無線、およびマイクロ波などのワイヤレス技術は、媒体の定義に含まれる。本明細書で使用するディスク（disk）およびディスク（disc）は、コンパクトディスク（disc）（CD）、レーザディスク（登録商標）（disc）、光ディスク（disc）、デジタル多用途ディスク（disc）（DVD）、フロッピー（登録商標）ディスク（disk）およびブルーレイディスク（disc）を含み、ディスク（disk）は、通常、データを磁気的に再生し、ディスク（disc）は、データをレーザで光学的に再生する。上記の組合せもコンピュータ可読媒体の範囲内に含めるべきである。一例では、プロセッサ実行可能命令のセットが、図1のメモリ26内にある。上記で説明したように、命令のそのセットを実行することで、コントローラ6は、ビットエラーレートと消費電力とのバランスをとるようにSerDes受信機8を構成することを引き起こす。別の例では、コントローラ6は、命令を記憶しているメモリを含む。コントローラ6内のプロセッサがこれらの命令を実行し、SerDes受信機の構成を引き起こす。

#### 【0050】

いくつかの特定の実施形態について説明の目的で上述したが、本特許文書の教示は、一般的な適用可能性を有し、上述した特定の実施形態に限定されない。低電力モードという用語および高電力モードという用語が、2つの可能性のある電力モードの例として上記で使用されたが、低電力モードと高電力モードとを有するものとして上記で説明したSerDes受信機およびSerDes送信機の各部は、実際には、多くの異なる電力モードを有することができ、低電力モードおよび高電力モードはそれらのうちの2つであるに過ぎ

10

20

30

40

50

ないことを理解されたい。全 S e r D e s 受信機または全 S e r D e s 送信機も同様に、低電力モードと高電力モードとを有すると言えるが、これらのそれぞれが、実際には、多数の異なる電力モードを有することができることを理解されたい。たとえば、S e r D e s 受信機 8において、消費電力設定 53 が S e r D e s 受信機の電力モードを決定する。したがって、説明した特定の実施形態の様々な特徴の様々な変更、適合、および組合せは、以下に記載する特許請求の範囲の範囲から逸脱することなく実施できる。

【図1】

図1

FIG. 1

【図2】

2

### SerDes受信機信号

**FIG. 2**

【図3】

図3

LLP-低減された位相精度(-25%)

HP-標準位相精度

LP-TXインピーダンス 高(-25%)

HP-TXインピーダンス 低

LP-1次のループフィルタ(-25%)

HP-2次のループフィルタ

LP-ディセーブルされる(-50%)

HP-イネーブルされたフルのHFブースト

LP-RX終端 高Z(-20%)

HP-RX終端 線路Z

より詳細なプロセッサ

FIG. 3

【図4】

図4

プロセッサが、そのSerDes受信機の消費電力設定を調整する

FIG. 4

【図 5】

図 5

ビットエラーレート範囲

FIG. 5

【図 6】

図 6

FIG. 6

【図 7A】

図 7A

プロセッサ内のSerDesデバイスの動作

FIG. 7A

【図 7B】

図 7B

プロセッサ内のSerDesデバイスの動作

FIG. 7B

|      |

|------|

| FIG. |

| 7A   |

| ---  |

| FIG. |

| 7B   |

KEY TO

FIG. 7

【図8】

図8

メモリ内のSerDesデバイスの動作

FIG. 8

【図9】

図9

受信機(RX)

FIG. 9

【図 10】

図 10

イコライザ

FIG. 10

【図 11】

図 11

4相サンプラー

FIG. 11

【図 12】

図 12

EARLY-LATE検出器

FIG. 12

【図 13】

図 13

並列化器およびFIFOバッファ

FIG. 13

【図 14】

図 14

ループフィルタ

(クロックおよびデータ回復回路のデジタルローパスフィルタ)

FIG. 14

【図 15】

図 15

4相クロック発生器

FIG. 15

【図 16】

図 16

位相ロックループ

FIG. 16

【図 17】

図 17

| 信号       | (細かい)<br>FINE_SELECT = 1 | (粗い)<br>FINE_SELECT = 0 |

|----------|--------------------------|-------------------------|

| $\Phi_0$ |                          |                         |

| $\Phi_1$ |                          | 非駆動－非トグリング              |

| $\Phi_2$ |                          |                         |

| :        | :                        | :                       |

| $\Phi_7$ |                          | 非駆動－非トグリング              |

PLL出力

FIG. 17

【図18】

図18

【図19】

図19

FIG. 19

【図 20】

図 20

プロセッサ SerDes 消費電力

(図は正確な尺度ではない)

FIG. 20

【図 21】

図 21

|                     |        |

|---------------------|--------|

| 高電力モード              | 100%   |

| 低電力モード<br>(イコライザオン) | -20.5% |

| 低電力モード<br>(イコライザオフ) | -22.5% |

プロセッサ SerDes 消費電力

FIG. 21

【図 22】

図 22

広帯域チャネル

FIG. 22

【図 23】

図 23

わずかに帯域制限されたチャネル

FIG. 23

【図 24】

図 24

適度に帯域制限されたチャネル

FIG. 24

【手続補正書】

【提出日】平成26年9月10日(2014.9.10)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

(a) 第1のSerDes(直列化器/並列化器)リンクのエラーレートを決定することであって、前記第1のSerDesリンクを介して進む情報がSerDes受信機によって受信されることと、

(b) 前記エラーレートがエラーレート下限とエラーレート上限との間に実質的に維持されるように、前記SerDes受信機の入力インピーダンス設定を制御することとを備え、

前記SerDes受信機によって受信された送信に対する前記エラーレートが前記エラーレート下限と前記エラーレート上限の範囲外のままであるとき、第1のSerDes受信機が別のSerDesデバイスにおける入力インピーダンスを変更する表示を前記別のSerDesデバイスへのSerDesリンクを介して送信するように構成される、方法。

【請求項2】

(a) における前記エラーレートを前記決定することが第1の集積回路上で実行され、前記SerDes受信機が第2の集積回路の一部である、請求項1に記載の方法。

【請求項3】

(a) における前記第1のSerDesリンクを介して進む前記情報が第1の集積回路のSerDes送信機によって出力され、(a)における前記情報を受信する前記SerDes受信機が第2の集積回路の一部であり、(a)の前記決定することおよび(b)の前記制御することが前記第1の集積回路によって実行される、請求項1に記載の方法。

【請求項4】

前記エラーレートを決定するために、第2のSerDesリンクを介して第1の集積回路上で受信されるパケット内のエラー情報を使用することをさらに備え、(a)の前記決定することが前記第1の集積回路によって実行され、前記SerDes受信機が前記第1の集積回路の一部ではない、請求項1に記載の方法。

【請求項5】

前記パケットがキープアライブ同期パケットである、請求項4に記載の方法。

【請求項6】

前記エラー情報が、(a)における前記第1のSerDesリンクを介して進む前記情報に関連する、請求項4に記載の方法。

【請求項7】

第2の集積回路内の回路が、(a)における前記SerDesリンクを介して進む前記情報内のエラーを検出し、前記エラーから前記エラー情報を生成し、前記第2の集積回路が前記エラー情報を前記パケットに組み込んで、前記パケットを前記第2のSerDesリンクを介して前記第1の集積回路に送信する、請求項4に記載の方法。

【請求項8】

前記第1の集積回路が、パケットを前記第1のSerDesリンクを介して前記第2の集積回路に送信することによって(b)の前記制御することを実行し、前記第2の集積回路に送信された前記パケットが前記入力インピーダンス設定を含み、前記入力インピーダンス設定が前記第2の集積回路の前記SerDes受信機に供給される、請求項2に記載の方法。

【請求項9】

前記パケットが制御パケットである、請求項8に記載の方法。

**【請求項 10】**

(a) の前記決定することおよび(b) の前記制御することが、SerDes送信機を含む第1の集積回路によって実行され、前記第1のSerDesリンクを介して進む前記情報が前記SerDes送信機から送信され、前記SerDes受信機が第2の集積回路の一部であり、前記第1の集積回路が中央処理装置(CPU)を含み、前記第2の集積回路がメモリを含み、前記第1の集積回路の前記CPUが前記第1のSerDesリンクを使用して前記第2の集積回路の前記メモリにアクセスする、請求項1に記載の方法。

**【請求項 11】**

(a) の前記決定することおよび(b) の前記制御することが、電池式ワイヤレスモバイル通信デバイス内の第1の集積回路によって実行される、請求項1に記載の方法。

**【請求項 12】**

(a) 第1のSerDes通信を第1のデバイスから第1のSerDesリンクを介して第2のデバイス上で受信することであって、前記第1のSerDes通信が前記第2のデバイスのSerDes受信機上で受信されることと、

(b) 前記第1のSerDes通信内でエラーが発生したことを前記第2のデバイス上で判断することと、前記判断することに応答して、前記第1のSerDes通信に存在する送信エラーの数を含む第2のSerDes通信を前記第2のデバイスから前記第1のデバイスに第2のSerDesリンクを介して送信することと、

(c) 前記第2のSerDes通信に基づくエラーレートが許容範囲外であるとき、第3のSerDes通信を前記第1のデバイスから前記第2のデバイスに前記第1のSerDesリンクを介して送信することと、

(d) 前記第2のデバイスの前記SerDes受信機の入力インピーダンス設定を調整するために、前記第3のSerDes通信内の情報を使用することと

を備える、方法。

**【請求項 13】**

前記エラーレートが、送信を試みられたビットの数で割ったエラーの総数を備える、請求項12に記載の方法。

**【請求項 14】**

(a)、(b)、(c) および(d) が第2の集積回路によって実行され、前記第1のSerDesリンクのエラーレートがエラーレート下限とエラーレート上限との間に実質的に維持されるように複数回繰り返される、請求項12に記載の方法。

**【請求項 15】**

第2のSerDesリンクを介して情報を受信するように適合された第1のSerDes受信機と、

第1のSerDesリンクを介して第2のSerDes受信機に情報を送信するように適合されたSerDes送信機と、

前記第1のSerDes受信機と前記SerDes送信機とに結合されたコントローラと

を備え、前記コントローラが、前記第1のSerDes受信機を介してエラー情報を受信し、前記第1のSerDesリンクのエラーレートを決定するために前記エラー情報を使用し、前記第1のSerDesリンクの前記エラーレートが許容可能な範囲外のままであるとき、前記コントローラが、前記第1のSerDesリンクの前記エラーレートがエラーレート下限とエラーレート上限との間に実質的に維持されるように、前記第2のSerDes受信機の入力インピーダンスを調整するために、前記SerDes送信機に制御パケットを送信させる、集積回路。

**【請求項 16】**

前記エラー情報が、キープアライブ同期パケットの一部として前記第2のSerDesリンクを介して前記集積回路上で受信される、請求項15に記載の集積回路。

**【請求項 17】**

前記第1のSerDesリンクおよび前記第2のSerDesリンクを介してメモリア

クセスを実行する中央処理装置（CPU）をさらに備える、請求項15に記載の集積回路。

【請求項 18】

エラーレートを有する第1のSerDesリンクを介して情報を受信するように適合されたSerDes受信機と、

第2のSerDesリンクを介して情報を送信するように適合されたSerDes送信機と、

第1のSerDes受信機と前記SerDes送信機とに結合されたコントローラと

を備え、前記コントローラが、前記第1のSerDesリンクを介した第1のSerDes通信に存在する送信エラーの数を決定し、前記コントローラが、前記第2のSerDesリンクを介して第2のSerDes通信内で前記送信エラーの数を通信させ、前記第2のSerDes通信に基づくエラーレートが許容範囲外であるとき、前記SerDes受信機が前記第1のSerDesリンクを介して第3のSerDes通信内の制御パケットを受信し、前記制御パケットに応答して、前記第1のSerDesリンクの前記エラーレートがエラーレート下限とエラーレート上限との間に実質的に維持されるように第2のSerDes受信機の入力インピーダンスが調整される、集積回路。

【請求項 19】

前記第2のSerDes通信がキープアライブ同期パケットの通信である、請求項18に記載の集積回路。

【請求項 20】

前記コントローラに結合され、前記第1のSerDesリンクおよび前記第2のSerDesリンクを使用して別の集積回路によってアクセスされ得るメモリをさらに備える、請求項18に記載の集積回路。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0050

【補正方法】変更

【補正の内容】

【0050】

いくつかの特定の実施形態について説明の目的で上述したが、本特許文書の教示は、一般的な適用可能性を有し、上述した特定の実施形態に限定されない。低電力モードという用語および高電力モードという用語が、2つの可能性のある電力モードの例として上記で使用されたが、低電力モードと高電力モードとを有するものとして上記で説明したSerDes受信機およびSerDes送信機の各部は、実際には、多くの異なる電力モードを有することができ、低電力モードおよび高電力モードはそれらのうちの2つであるに過ぎないことを理解されたい。全SerDes受信機または全SerDes送信機も同様に、低電力モードと高電力モードとを有すると言えるが、これらのそれぞれが、実際には、多数の異なる電力モードを有することができるることを理解されたい。たとえば、SerDes受信機8において、消費電力設定53がSerDes受信機の電力モードを決定する。したがって、説明した特定の実施形態の様々な特徴の様々な変更、適合、および組合せは、以下に記載する特許請求の範囲の範囲から逸脱することなく実施できる。

以下に、本願出願の当初の特許請求の範囲に記載された発明を付記する。

[C1]

SerDes(直列化器/並列化器)リンクを介した情報の通信においてSerDes回路を使用することであって、前記SerDes回路が、前記SerDesリンクを介して情報を送信するSerDes送信機と、前記SerDesリンクから情報を受信するSerDes受信機とからなる群から得られることと、

前記SerDesリンクのエラーレートが、実質的にゼロより大きいエラーレート下限とエラーレート上限との間に実質的に維持されるように、前記SerDes回路の消費電力を制御することと

を備え、前記制御することが行われる間、前記消費電力があるときは増大され、またあるときは低減される、方法。

[ C 2 ]

SerDes(直列化器／並列化器)リンクを介して情報を通信するように適合されたSerDes回路に動作可能に結合されたコントローラを備え、前記SerDesリンクのエラーレートが実質的にゼロより大きいエラーレート下限とエラーレート上限との間に実質的に維持されるように前記SerDes回路の消費電力を制御するように前記コントローラが適合され、前記制御することが行われる間、前記消費電力があるときは増大され、またあるときは低減される、装置。

[ C 3 ]

前記コントローラが第1のSerDesデバイスの一部であり、前記SerDes回路が第2のSerDesデバイスの一部であり、前記SerDesリンクが前記第1のSerDesデバイスと前記第2のSerDesデバイスとの間に延在する、C 2に記載の装置。

[ C 4 ]

前記コントローラおよび前記SerDes回路が第1のSerDesデバイスの一部であり、前記SerDesリンクが前記第1のSerDesデバイスと第2のSerDesデバイスとの間に延在する、C 2に記載の装置。

[ C 5 ]

(a) SerDes(直列化器／並列化器)リンクのエラーレートを決定することであって、前記SerDesリンクを介して進む情報がSerDes受信機によって受信されること、

(b) 前記エラーレートが実質的にゼロより大きいエラーレート下限とエラーレート上限との間に実質的に維持されるように前記SerDes受信機の消費電力設定を制御すること

を備え、(b)の前記制御することが、

前記エラーレートが前記エラーレート下限を下回っていると判断される場合、前記エラーレートが増加して実質的に前記エラーレート下限以上になるように、前記消費電力設定を前記SerDes受信機の消費電力が低減されるように調整することと、

前記エラーレートが前記エラーレート上限を上回っていると判断される場合、前記エラーレートが減少して実質的に前記エラーレート上限以下になるように、前記消費電力設定を前記SerDes受信機の前記消費電力が増加するように調整することとを併い、(b)の前記制御することが行われる間、あるときは前記消費電力が増大され、またあるときは低減される、方法。

[ C 6 ]

(a) の前記決定することおよび(b)の前記制御することが、電池式モバイル通信デバイス内で行われ、前記SerDesリンクが前記電池式モバイル通信デバイス内に配設される、C 5に記載の方法。

[ C 7 ]

前記SerDesリンクが、電池式モバイル通信デバイス内の第1の集積回路から前記電池式モバイル通信デバイス内の第2の集積回路まで延在する、C 5に記載の方法。

[ C 8 ]

(a) の前記決定することおよび(b)の前記制御することが前記SerDes受信機を含む第1の集積回路によって実行され、前記SerDesリンクを介して進む前記情報が、第2の集積回路の一部であるSerDes送信機から受信され、前記第1の集積回路が中央処理装置(CPU)を含み、前記第2の集積回路がメモリを含み、前記方法が、

前記SerDesリンクの前記SerDes受信機を使用して前記第2の集積回路の前記メモリにアクセスすることをさらに備え、前記第1の集積回路の前記CPUが前記アクセスすることを実行する、C 5に記載の方法。

[ C 9 ]

( a ) の前記決定することおよび( b ) の前記制御することが集積回路によって実行され、前記集積回路が前記 SerDes 受信機を含み、( a ) の前記決定することが、データ部分とエラー検出コード部分とを含む情報を前記 SerDes 受信機を介して受信することと、

前記エラー検出コード部分を使用して前記データ部分内の 1 つまたは複数のビットエラーを検出するために前記集積回路上のエラー検出回路を使用することとを伴う、C 5 に記載の方法。

[ C 10 ]

前記エラー検出コード部分が、エラー訂正コードと、エラー検出および訂正コードと、CRC (巡回冗長コード) コードとからなる群から得られる、C 9 に記載の方法。

[ C 11 ]

( a ) の前記決定することが、

検出されたビットエラーの数の合計を保持することと、

エラーなしで受信されたビットの数の合計を保持することとをさらに伴う、C 9 に記載の方法。

[ C 12 ]

前記 SerDes 受信機がループフィルタを含み、前記消費電力設定が前記ループフィルタの設定を備える、C 5 に記載の方法。

[ C 13 ]

前記 SerDes 受信機がデジタルフィルタを含み、前記消費電力設定が、デジタルクロック信号が前記デジタルフィルタの一部分に供給されるのを防止する設定である、C 5 に記載の方法。

[ C 14 ]

前記 SerDes 受信機がクロックとデータ回復回路とを含み、前記消費電力設定が前記クロックおよびデータ回復回路の設定を備える、C 5 に記載の方法。

[ C 15 ]

前記 SerDes 受信機がイコライザを含み、前記消費電力設定が前記イコライザの設定を備える、C 5 に記載の方法。

[ C 16 ]

前記 SerDes 受信機がイコライザを含み、前記消費電力設定が、前記イコライザの高周波数ブーストをイネーブルする設定を備える、C 5 に記載の方法。

[ C 17 ]

前記 SerDes 受信機が多相クロック信号を出力する位相ロックループ (PLL) を含み、前記消費電力設定が前記 PLL の設定を備える、C 5 に記載の方法。

[ C 18 ]

前記 SerDes 受信機が入力インピーダンスを有し、前記消費電力設定が前記 SerDes 受信機の前記入力インピーダンスを決定する設定を備える、C 5 に記載の方法。

[ C 19 ]

( a ) 第 1 の SerDes (直列化器 / 並列化器) リンクのエラーレートを決定することであって、前記第 1 の SerDes リンクを介して進む情報が SerDes 受信機によって受信されることと、

( b ) 前記エラーレートが実質的にゼロより大きいエラーレート下限とエラーレート上限との間に実質的に維持されるように、前記 SerDes 受信機の入力インピーダンス設定を制御することとを備え、( b ) の前記制御することが、

前記エラーレートが前記エラーレート下限を下回っていると判断される場合、前記エラーレートが増加して実質的に前記エラーレート下限以上になるように、前記入力インピーダンス設定を前記 SerDes 受信機の前記入力インピーダンスが増大されるように調整することと、

前記エラーレートが前記エラーレート上限を上回っていると判断される場合、前記エラーレートが減少して実質的に前記エラーレート上限以下になるように、前記入力インピーダンス設定を前記 SerDes 受信機の前記入力インピーダンスが低減されるように調整することと

を伴い、(b) の前記制御することが行われる間、前記 SerDes 受信機の入力インピーダンスがあるときは増大され、またあるときは低減される、方法。

[ C 2 0 ]

(a) における前記エラーレートを前記決定することが第1の集積回路上で実行され、前記 SerDes 受信機が第2の集積回路の一部である、C 1 9 に記載の方法。

[ C 2 1 ]

(a) における前記第1の SerDes リンクを介して進む前記情報が第1の集積回路の SerDes 送信機によって出力され、(a) における前記情報を受信する前記 SerDes 受信機が第2の集積回路の一部であり、(a) の前記決定することおよび(b) の前記制御することが前記第1の集積回路によって実行される、C 1 9 に記載の方法。

[ C 2 2 ]

前記エラーレートを決定するために、第2の SerDes リンクを介して第1の集積回路上で受信されるパケット内のエラー情報を使用することをさらに備え、(a) の前記決定することが前記第1の集積回路によって実行され、前記 SerDes 受信機が前記第1の集積回路の一部ではない、C 1 9 に記載の方法。

[ C 2 3 ]

前記パケットがキープアライブ同期パケットである、C 2 2 に記載の方法。

[ C 2 4 ]

前記エラー情報が、(a) における前記第1の SerDes リンクを介して進む前記情報に関連する、C 2 2 に記載の方法。

[ C 2 5 ]

第2の集積回路内の回路が、(a) における前記 SerDes リンクを介して進む前記情報内のエラーを検出し、前記エラーから前記エラー情報を生成し、前記第2の集積回路が前記エラー情報を前記パケットに組み込んで、前記パケットを前記第2の SerDes リンクを介して前記第1の集積回路に送信する、C 2 2 に記載の方法。

[ C 2 6 ]

前記第1の集積回路が、パケットを前記第1の SerDes リンクを介して前記第2の集積回路に送信することによって(b) の前記制御することを実行し、前記第2の集積回路に送信された前記パケットが前記入力インピーダンス設定を含み、前記入力インピーダンス設定が前記第2の集積回路の前記 SerDes 受信機に供給される、C 2 0 に記載の方法。

[ C 2 7 ]

前記パケットが制御パケットである、C 2 6 に記載の方法。

[ C 2 8 ]

(a) の前記決定することおよび(b) の前記制御することが、SerDes 送信機を含む第1の集積回路によって実行され、前記第1の SerDes リンクを介して進む前記情報が前記 SerDes 送信機から送信され、前記 SerDes 受信機が第2の集積回路の一部であり、前記第1の集積回路が中央処理装置(CPU)を含み、前記第2の集積回路がメモリを含み、前記第1の集積回路の前記 CPU が前記第1の SerDes リンクを使用して前記第2の集積回路の前記メモリにアクセスする、C 1 9 に記載の方法。

[ C 2 9 ]

(a) の前記決定することおよび(b) の前記制御することが、電池式ワイヤレスモバイル通信デバイス内の第1の集積回路によって実行される、C 1 9 に記載の方法。

[ C 3 0 ]

(a) 第1の SerDes 通信を第1のデバイスから第1の SerDes リンクを介して第2のデバイス上で受信することであって、前記第1の SerDes 通信が前記第2の

デバイスの SerDes 受信機上で受信されることと、

(b) 前記第1のSerDes通信内でエラーが発生したことを前記第2のデバイス上で判断することと、前記判断することに応答して、前記第1のSerDes通信に関連するエラー情報を含む第2のSerDes通信を前記第2のデバイスから前記第1のデバイスに第2のSerDesリンクを介して送信することと、

(c) 第3のSerDes通信を前記第1のデバイスから前記第1のSerDesリンクを介して前記第2のデバイス上で受信することと、

(d) 前記第2のデバイスの前記SerDes受信機の入力インピーダンス設定を調整するために、前記第3のSerDes通信内の情報を使用することとを備える、方法。

[C 3 1]

(c)において受信された前記第3のSerDes通信内の前記情報が、(b)における前記エラー情報の関数である、C 3 0 に記載の方法。

[C 3 2]

(a)、(b)、(c)および(d)が第2の集積回路によって実行され、前記第1のSerDesリンクのエラーレートが実質的にゼロより大きいエラーレート下限とエラーレート上限との間に実質的に維持されるように複数回繰り返される、C 3 0 に記載の方法。

[C 3 3]

SerDes受信機と、

前記SerDes受信機に結合されたコントローラとを備え、前記コントローラが、前記SerDes受信機を伴うSerDesリンクに対するエラーレートを決定し、前記コントローラが、前記エラーレートが実質的にゼロより大きいエラーレート下限とエラーレート上限との間に実質的に維持されるように、前記コントローラによって前記SerDes受信機に供給される消費電力設定を調整する、集積回路。

[C 3 4]

前記コントローラが、前記SerDesリンクを介して行われた通信内のエラーを検出するエラー検出回路を含み、前記コントローラが、前記SerDesリンクに対する前記エラーレートを決定するために、前記エラー検出回路によって生成されたエラー情報を使用する、C 3 3 に記載の集積回路。

[C 3 5]

前記SerDes受信機がループフィルタを含み、前記消費電力設定が前記ループフィルタの設定を備える、C 3 3 に記載の集積回路。

[C 3 6]

前記SerDes受信機がデジタルフィルタを含み、前記消費電力設定が、デジタルクロック信号が前記デジタルフィルタの一部分に供給されるのを防止する設定である、C 3 3 に記載の集積回路。

[C 3 7]

前記SerDes受信機がクロックおよびデータ回復回路を含み、前記消費電力設定が前記クロックおよびデータ回復回路の設定を備える、C 3 3 に記載の集積回路。

[C 3 8]

前記SerDes受信機がイコライザを含み、前記消費電力設定が前記イコライザの設定を備える、C 3 3 に記載の集積回路。

[C 3 9]

前記SerDes受信機がイコライザを含み、前記消費電力設定が、前記イコライザの高周波数ブーストをイネーブルする設定を備える、C 3 3 に記載の集積回路。

[C 4 0]

前記SerDes受信機が、多相クロック信号を出力する位相ロックループ(PLL)を含み、前記消費電力設定が前記PLLの設定を備える、C 3 3 に記載の集積回路。

[ C 4 1 ]

前記 SerDes 受信機が入力インピーダンスを有し、前記消費電力設定が、前記 SerDes 受信機の前記入力インピーダンスを決定する設定を備える、C 3 3 に記載の集積回路。

[ C 4 2 ]

第 2 の SerDes リンクを介して情報を受信するように適合された第 1 の SerDes 受信機と、

第 1 の SerDes リンクを介して第 2 の SerDes 受信機に情報を送信するように適合された SerDes 送信機と、

前記第 1 の SerDes 受信機と前記 SerDes 送信機とに結合されたコントローラと

を備え、前記コントローラが、前記第 1 の SerDes 受信機を介してエラー情報を受信し、前記第 1 の SerDes リンクのエラーレートを決定するために前記エラー情報を使用し、前記コントローラが、前記第 1 の SerDes リンクの前記エラーレートが実質的にゼロより大きいエラーレート下限とエラーレート上限との間に実質的に維持されるように前記第 2 の SerDes 受信機の入力インピーダンスを調整するために、前記 SerDes 送信機に制御パケットを送信させる、集積回路。

[ C 4 3 ]

前記エラー情報が、キープアライブ同期パケットの一部として前記第 2 の SerDes リンクを介して前記集積回路上で受信される、C 4 2 に記載の集積回路。

[ C 4 4 ]

前記第 1 の SerDes リンクおよび第 2 の SerDes リンクを介してメモリアクセスを実行する中央処理装置 (CPU) をさらに備える、C 4 2 に記載の集積回路。

[ C 4 5 ]

エラーレートを有する第 1 の SerDes リンクを介して情報を受信するように適合された SerDes 受信機と、

第 2 の SerDes リンクを介して情報を送信するように適合された SerDes 送信機と、

前記第 1 の SerDes 受信機と前記 SerDes 送信機とに結合されたコントローラと

を備え、前記コントローラが、前記第 1 の SerDes リンクを介した第 1 の SerDes 通信に関するエラー情報を生成し、前記コントローラが、前記第 2 の SerDes リンクを介して第 2 の SerDes 通信内で前記エラー情報を通信させ、前記コントローラが前記第 1 の SerDes リンクを介して第 3 の SerDes 通信内の制御パケットを受信し、前記制御パケットに応答して、前記第 1 の SerDes リンクの前記エラーレートが実質的にゼロより大きいエラーレート下限とエラーレート上限との間に実質的に維持されるように前記第 2 の SerDes 受信機の入力インピーダンスを調整する、集積回路。

[ C 4 6 ]

前記第 2 の SerDes 通信がキープアライブ同期パケットの通信である、C 4 5 に記載の集積回路。

[ C 4 7 ]

前記コントローラに結合され、前記第 1 の SerDes リンクおよび前記第 2 の SerDes リンクを使用して別の集積回路によってアクセスされ得るメモリをさらに備える、C 4 5 に記載の集積回路。

---

フロントページの続き

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100158805

弁理士 井関 守三

(74)代理人 100179062

弁理士 井上 正

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(72)発明者 デクスター・ティー・・チュン

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

(72)発明者 ジャック・ケー・・ウルフ

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

(72)発明者 ジュンウォン・スー

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

(72)発明者 ティアダッド・ソウラティ

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

F ターム(参考) 5B061 QQ01

5B077 NN02

【外國語明細書】

2015018564000001.pdf