(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-146920

(P2006-146920A)

(43) 公開日 平成18年6月8日(2006.6.8)

| (51) Int.C1.      | F 1              | テーマコード (参考)           |

|-------------------|------------------|-----------------------|

| <b>G06F 12/16</b> | <b>(2006.01)</b> | G06F 12/16 310C 5B005 |

| <b>G06F 12/08</b> | <b>(2006.01)</b> | G06F 12/16 320F 5B018 |

|                   |                  | G06F 12/08 543Z       |

|                   |                  | G06F 12/08 507Z       |

|                   |                  | G06F 12/08 531Z       |

審査請求 未請求 請求項の数 21 O L (全 18 頁)

(21) 出願番号 特願2005-330822 (P2005-330822)

(22) 出願日 平成17年11月15日 (2005.11.15)

(31) 優先権主張番号 10/992,056

(32) 優先日 平成16年11月17日 (2004.11.17)

(33) 優先権主張国 米国(US)

(71) 出願人 595034134

サン・マイクロシステムズ・インコーポレイテッド

Sun Microsystems, Inc.

アメリカ合衆国 カリフォルニア 95054, サンタクララ, ネットワークサークル 4150

(74) 代理人 100078282

弁理士 山本 秀策

(74) 代理人 100062409

弁理士 安村 高明

(74) 代理人 100113413

弁理士 森下 夏樹

最終頁に続く

(54) 【発明の名称】メモリエラーを分類するための方法および装置

## (57) 【要約】

【課題】コンピュータシステム内のメモリエラーの原因を正確に決定する装置を提供する。

【解決手段】本発明のシステムは、第1に、第1のプロセッサによってメインメモリにおけるメモリ位置へのアクセスの間、訂正可能なエラーを検出する(402)。訂正可能なエラーは、エラー検出および訂正回路によって検出される。次にシステムは、メモリ位置に関連されたキャッシュラインのためのタグビットを読み取る(408)。タグビットは、キャッシュラインのための一貫性プロトコル状態を示す状態情報だけでなく、キャッシュラインのアドレス情報をも含む。次いで、テスト結果を生成するために、第1のプロセッサに、メモリ位置に対する読み取りおよび書き込み動作を実行させることによって、メモリ位置をテストする。最後にシステムは、可能な場合、訂正可能なエラーの原因を決定する(418、430、432)ために、テスト結果およびタグビットを使用する。

【選択図】図4

**【特許請求の範囲】****【請求項 1】**

訂正可能なメモリエラーの原因を決定する方法であって、

第1のプロセッサによるメインメモリにおけるメモリ位置へのアクセスの間、エラー検出訂正回路によって検出される該訂正可能なエラーを検出することと、

該メモリ位置に関連されたキャッシュラインのためにタグビットを読み取ることであって、該タグビットは、該キャッシュラインのためのアドレス情報および、該キャッシュラインのための一貫性プロトコル状態を指示する状態情報を含む、ことと、

テスト結果を生成するために、該第1のプロセッサに、該メモリ位置に対する読み取り動作および書き込み動作を実行させることによって、該メモリ位置をテストすることと、10

可能である場合、該訂正可能なエラーの原因を決定するために、該テスト結果および該タグビットを利用することと

を包含する、方法。

**【請求項 2】**

前記メモリ位置をテストすることが、

前記訂正可能なエラーについての情報を含む、asynchronous fault status register (AFSR) および asynchronous fault address register (AFAR) をクリアすることと、

キャッシュから前記キャッシュラインをフラッシュすることと、

該メモリ位置を再度読み取ることであって、それによって、メインメモリから該キャッシュへ、該キャッシュラインが引き戻される、ことと、20

該AFSR および該AFAR レジスタを読み取り、クリアすることと、

前記エラー検出訂正回路に、該訂正可能なエラーを訂正させることと、

該キャッシュライン（エラーは訂正されている）をメインメモリへフラッシュして戻すことと

を包含する、請求項1に記載の方法。

**【請求項 3】**

前記メモリ位置を再度読み取ることが、前記キャッシュにおける修正された状態において前記キャッシュラインが存在することを保証するために、アトミックな比較およびスワップ (CAS) 動作を実行することを包含する、請求項1に記載の方法。30

**【請求項 4】**

前記メモリ位置を再度読み取ることが訂正可能なエラーを生じさせない場合、前記訂正可能なエラーの原因を決定することが、

前記読み取りタグビットを試験することと、

前記タグからのアドレスビットが、前記AFARからの訂正可能なエラーの読み取りのアドレスの対応するビットと一致する場合、および、キャッシュラインが該タグビットが読み取られた場合にキャッシュにおいて、共有された (S) 状態または排他的 (E) 状態であることを、該タグからの状態ビットが指示する場合、間欠エラーがあることを決定することと

を含む、請求項2に記載の方法。40

**【請求項 5】**

前記メモリ位置を再度読み取ることが訂正可能なエラーを生じさせる場合、前記方法が、

該メモリ位置をさらに再度読み取ることと、

前記AFSR および前記AFAR レジスタを再度読み取りおよびクリアすることとをさらに包含する、請求項2に記載の方法。

**【請求項 6】**

前記メモリをさらに再度読み取ることが訂正可能なエラーを生じさせない場合、前記方法が、

所定の時間間隔の後に前記メモリ位置を再度読み取ることと、50

該所定の時間間隔の後に該メモリ位置を再度読み取ることが、訂正可能なエラーを生じさせる場合、該メモリ位置がリーキーであることを決定することと、

さもなければ、該訂正可能なエラーが永続的エラーであることを決定することとをさらに包含する、請求項 5 に記載の方法。

#### 【請求項 7】

前記メモリ位置をさらに再度読み取ることが訂正可能なエラーを生じさせる場合、前記方法が、

第 2 のプロセッサに、該訂正可能なエラーを分類させることと、

該第 2 のプロセッサがエラーを検出しない場合、前記第 1 のプロセッサが不良な読み取り装置であると決定することと、10

該第 2 のプロセッサがスティックキーエラーでないエラーを検出する場合、該第 1 のプロセッサが不良な書き込み装置であると決定することと、

該第 2 のプロセッサがスティックキーエラーを検出する場合、該メモリ位置における少なくとも一つのビットがスタックしていると決定することと、

をさらに包含する、請求項 5 に記載の方法。

#### 【請求項 8】

コンピュータによって実行された場合、該コンピュータに、訂正可能なメモリエラーの原因を決定するための方法を実行させる命令を記憶するコンピュータ可読の記憶媒体であって、該方法は、

第 1 のプロセッサによるメインメモリにおけるメモリ位置へのアクセスの間、エラー検出訂正回路によって検出される訂正可能なエラーを検出することと、20

該メモリ位置に関連されたキャッシュラインのためにタグビットを読み取ることであって、該タグビットは、該キャッシュラインのためのアドレス情報および、該キャッシュラインのための一貫性プロトコル状態を指示する状態情報を含む、ことと、

テスト結果を生成するために、該第 1 のプロセッサに、該メモリ位置に対する読み取り動作および書き込み動作を実行させることによって、該メモリ位置をテストすることと、

可能である場合、該訂正可能なエラーの原因を決定するために、該テスト結果および該タグビットを利用することと、25

を包含する、コンピュータ可読の記憶媒体。

#### 【請求項 9】

前記メモリ位置をテストすることが、30

前記訂正可能なエラーについての情報を含む、asynchronous fault status register (AFSR) および asynchronous fault address register (AFAR) をクリアすることと、

キャッシュから前記キャッシュラインをフラッシュすることと、

該メモリ位置を再度読み取ることであって、それによって、メインメモリから該キャッシュへ、該キャッシュが引き戻される、ことと、

該 AFSR および該 AFAR レジスタを読み取り、およびクリアすることと、

前記エラー検出訂正回路に、訂正可能なエラーを訂正させることと、

該キャッシュライン (エラーは訂正されている) をメインメモリへフラッシュして戻すことと、40

を含む、請求項 8 に記載のコンピュータ可読の記憶媒体。

#### 【請求項 10】

前記メモリ位置を再度読み取ることが、前記キャッシュにおける修正された状態において、前記キャッシュラインが存在することを保証するために、アトミックな比較およびスワップ (CAS) 動作を実行することを包含する、請求項 8 に記載のコンピュータ可読の記憶媒体。

#### 【請求項 11】

前記メモリ位置を再度読み取ることが、訂正可能なエラーを生じさせない場合、該訂正可能なエラーの原因を決定することが、50

以前の読み取りタグビットを試験することと、

前記タグからのアドレスビットが前記 A F A R からの該訂正可能なエラー読み取りの前記アドレスに対応するビットと一致する場合、および、キャッシュラインが、該タグビットが読み取られた場合にキャッシュにおいて、共有された ( S ) 状態または排他的 ( E ) 状態であることを、該タグからの状態ビットが指示する場合、間欠エラーがあることを決定することと

を含む、請求項 9 に記載のコンピュータ可読の記憶媒体。

#### 【請求項 12】

前記メモリ位置を再度読み取ることが訂正可能なエラーを生じさせる場合、前記方法が

10

、該メモリ位置をさらに再度読み取ることと、

前記 A F S R および前記 A F A R レジスタを再度読み取り、クリアすることと

をさらに包含する、請求項 9 に記載のコンピュータ可読の記憶媒体。

#### 【請求項 13】

前記メモリ位置をさらに再度読み取ることが訂正可能なエラーを生じさせない場合、前記方法が、

所定の時間間隔の後に該メモリ位置を再度読み取ることと、

該所定の時間間隔の後に該メモリ位置を再度読み取ることが訂正可能なエラーを生じさせる場合、該メモリ位置がリーキーであることを決定することと、

20

さもなければ、該訂正可能なエラーが永続的エラーであることを決定することと

をさらに包含する、請求項 12 に記載のコンピュータ可読の記憶媒体。

#### 【請求項 14】

前記メモリ位置をさらに再度読み取ることが訂正可能なエラーを生じさせる場合、前記方法が、

第 2 のプロセッサに該訂正可能なエラーを分類させることと、

該第 2 のプロセッサがエラーを検出しない場合、前記第 1 のプロセッサが不良な読み取り装置であると決定することと、

該第 2 のプロセッサがステイックエラーでないエラーを検出する場合、該第 1 のプロセッサが不良な書き込み装置であると決定することと、

該第 2 のプロセッサがステイックエラーを検出する場合、該メモリ位置における少な

くとも一つのビットがスタッツしていると決定することと

30

をさらに包含する、請求項 12 に記載のコンピュータ可読の記憶媒体。

#### 【請求項 15】

前記訂正可能なメモリエラーの原因を決定する装置であって、

第 1 のプロセッサによるメインメモリにおけるメモリ位置へのアクセスの間、訂正可能なエラーを検出するように構成されたエラー訂正検出回路と、

該メモリ位置に関連されたキャッシュラインのためにタグビットを読み取るように構成された読み取りメカニズムであって、該タグビットは、該キャッシュラインのためのアドレス情報および、該キャッシュラインのための一貫性プロトコル状態を指示する状態情報を含む、読み取りメカニズムと、

40

テスト結果を生成するために、該第 1 のプロセッサに、該メモリ位置に対する読み取り動作および書き込み動作を実行させることによって、該メモリ位置をテストするように構成されたテストメカニズムと、

可能である場合、該訂正可能なエラーの原因を決定するために、該テスト結果および該タグビットを利用するために構成された、エラー分類メカニズムと

を備える、装置。

#### 【請求項 16】

前記テストメカニズムが、

前記訂正可能なエラーについての情報を含む、asynchronous fault status register ( A F S R ) および asynchronous fa

50

u l t a d d r e s s r e g i s t e r ( A F A R ) をクリアするように、

キャッシュから前記キャッシュラインをフラッシュするように、

該メモリ位置を再度読み取るようにであって、それによって、メインメモリから該キャッシュへ、該キャッシュラインが引き戻される、ように、

該 A F S R および該 A F A R レジスタを読み取り、クリアするように、

前記エラー検出訂正回路に、該訂正可能なエラーを訂正させるように、および、

該キャッシュライン（エラーは訂正されている）をメインメモリへフラッシュして戻す

ように、

構成される、請求項 15 に記載の装置。

## 【請求項 17】

10

前記メモリ位置を再度読み取る間、前記テストメカニズムは、前記キャッシュにおける修正された状態において前記キャッシュラインが存在することを保証するために、アトミックな比較およびスワップ（C A S）動作を実行するように構成されている、請求項 15 に記載の装置。

## 【請求項 18】

20

前記メモリ位置を再度読み取ることが訂正可能なエラーを生じさせない場合、エラー分類メカニズムが、

以前に読み取られたタグビットを試験するように、および、

前記タグからのアドレスビットが、前記 A F A R からの訂正可能なエラー読み取りのためのアドレスに対応するビットと一致する場合、および、キャッシュラインが、該タグビットが読み取られていた場合にキャッシュにおいて共有された（S）状態または排他的（E）状態であることを、該タグからの状態ビットが指示する場合、間欠エラーがあることを決定するように

構成される、請求項 16 に記載の装置。

## 【請求項 19】

30

前記メモリ位置を再度読み取ることが訂正可能なエラーを生じさせる場合、前記エラー分類メカニズムが、

該メモリ位置をさらに再度読み取るように、および、

前記 A F S R および前記 A F A R レジスタを再度読み取り、クリアするように

構成される、請求項 16 に記載の装置。

## 【請求項 20】

40

前記メモリをさらに再度読み取ることが訂正可能なエラーを生じさせない場合、前記エラー分類メカニズムが、

所定の時間間隔の後に前記メモリ位置を再度読み取るように、

該所定の時間間隔の後に該メモリ位置を再度読み取ることが訂正可能なエラーを生じさせる場合、該メモリ位置がリーキーであることを決定するように、および、

さもなければ、該訂正可能なエラーが永続的エラーであることを決定するように、

構成される、請求項 19 に記載の装置。

## 【請求項 21】

50

前記メモリ位置をさらに再度読み取ることが訂正可能なエラーを生じさせる場合、前記エラー分類メカニズムは、

第 2 のプロセッサに、該訂正可能なエラーを分類させるように、

該第 2 のプロセッサがエラーを検出しない場合、前記第 1 のプロセッサが不良な読み取り装置であると決定するように、

該第 2 のプロセッサがスティッキーエラーでないエラーを検出する場合、該第 1 のプロセッサが不良な書き込み装置であると決定するように、および、

該第 2 のプロセッサがスティッキーエラーを検出する場合、該メモリ位置における少なくとも一つのビットがスタッカしていると決定するように、

構成される、請求項 19 に記載の装置。

## 【発明の詳細な説明】

**【技術分野】****【0001】**

本発明は、コンピュータシステムにおけるエラーを扱うための技術に関する。より詳細には、本発明は、コンピュータシステムにおけるメモリエラーを分類するための方法および装置に関する。

**【背景技術】****【0002】**

コンピュタメモリは増加的に容量がより大きくなり、個々のメモリセルは進歩的により小さくなるにつれて、宇宙線のような自然現象のためにエラーが相当に発生し得るようになってきている。さらに、コンピュータシステムが速度を速め続けているので、データは、プロセッサとメモリとの間のより速い速度で転送されなければならない。これは、データエラーの別のソースを作成する。なぜならば、より速いデータ速度は、プロセッサとメモリとの間のデータを転送する一方でエラーが生じる可能性を増大させるからである。

**【0003】**

通常、コンピュータシステムは、メモリエラーを検出および訂正するためにエラー訂正コードを使用する。これは、普通、メモリにおけるそれぞれのデータワードに沿って、記憶されたエラー訂正コード(error-correcting code) (ECC) ビットを含み、次いで、データワードがメインメモリとプロセッサ(関連されたキャッシュメモリ)との間で転送された場合に、データワードに沿って ECC ビットを転送する。一般に使用されるエラー訂正コードは、通常、それぞれのデータワードのため、2 ビットエラー検出(double-error detection) および 1 ビットエラー訂正(single-error correction) をサポートする。それゆえ、コンピュータシステムは、通常、メインメモリから引き出されるデータワードにおける、2 ビットエラーおよび 1 ビットエラーを検出することができる。

**【0004】**

一部のコンピュータシステムは、さらに一ステップ進み、メモリエラーの原因を決定するためのメカニズムを提供する。例えば、メインメモリからデータワードを読み取る一方で、訂正可能なエラーに遭遇した場合、コンピュータシステムは、メモリエラーのその原因を決定するために、二回目の読み取る時にデータワードを読み取ることができる。エラーが、二回目の読み取りの間に発生しない場合、そのシステムは、エラーが「間欠エラー」であると決定することができ、例えば、それは、プロセッサとメインメモリとの間のデータライン上の一過性のノイズによって生じる。

**【0005】**

他方で、二回目の読み取りはまた、エラーに遭遇した場合、コンピュータシステムがデータワードを訂正し、メインメモリにそれを書き込むために、その ECC 回路を使用することができる。次いで、エラーの原因を決定するために、コンピュータシステムは、3 回目で、データワードを読み取ることができる。3 回目の読み取りはまた、エラーと遭遇した場合、システムは、エラーが「スティッキー(sticky) エラー」であること(「スティッキー エラー」は、例えば、メインメモリにおけるワードデータにおいて、「スタック(stuck)」ビットによって生じる)を決定することができる。他方で、三回目の読み取りが訂正されたデータワードを戻す場合、システムは、エラーが「永続的エラー」であったこと(メインメモリにおけるデータワードの状態における変化によって生じ得る)を決定することができる。

**【0006】**

残念ながら、メモリエラーの原因を決定するための上記に記載されたメカニズムは、キャッシュメモリの存在において非常に複雑になり得ている。キャッシュメモリがメインメモリへのアクセスを媒介することに注意したい。しかしながら、そうすることによって、キャッシュメモリは、誤った(errorant)メモリアクセスをリトライする企てを妨害し、それにより、メモリエラーの原因を決定するプロセスを妨害することができる。

**【0007】**

10

20

30

40

50

例えば、コンピュータシステムに、メモリ位置への二回目の読み取り動作を実行させるために、キャッシングからのメモリ位置に関連されたキャッシングラインを除去する( *f l u s h* )ことが第1に必要であり、その読み取り動作は実際に、キャッシングラインに、メインメモリから引き出させる。しかしながら、この除去が起こった場合で、キャッシングラインが汚れていた場合、その除去は、キャッシングラインをメモリへ記憶され戻させ、エラーを訂正し得る。それゆえ、メモリからの次の二回目の読み取りはエラーと遭遇し得ない。これは、エラーが実際には永続的エラーであった場合だとしても、間欠エラーとして診断されたエラーという結果になり得る( 誤診断エラーのこのタイプは「偽( *f a l s e* )間欠エラー」と呼ばれる)。

## 【0008】

10

さらに、既存の技術はメモリエラーの特定のタイプの間の差異を識別することができない。例えば、「リーキー( *l e a k y* )セル」状態は、メモリセルが負荷を持たない場合に起こり得る。この場合、上記に記載されたメカニズムは、そのエラーがリーキーセルである代わりに、永続的エラーであると誤って決定する。さらに、エラーは、マルチプロセッサシステムにおける特定のプロセッサが、「不良な読み取り装置( *b a d r e a d e r* )」または「不良な書き込み装置( *b a d w r i t e r* )」である場合、エラーは起こり得る。エラーのこれらのタイプは、既存の技術にては、どちらも診断され得ない。

## 【0009】

20

明らかに、メモリエラーの原因が正確に決定され得る場合に、効果的な矯正アクションが取られ得る。例えば、メモリエラーが正確に診断されてない場合、一部分が取り替えられる必要があるかどうか、その場合、どの部分が取り替えられる必要があるかどうかを、確かめることは不可能である。

## 【0010】

それゆえ、必要となるものは、上記に記載された問題なしで、コンピュータシステム内のメモリエラーの原因を正確に決定する方法および装置である。

## 【発明の開示】

## 【課題を解決するための手段】

## 【0011】

30

本発明における一実施形態は、訂正可能なメモリエラーの原因を決定するシステムを提供することである。第1に、システムは、第1のプロセッサによってメインメモリにおけるメモリ位置へのアクセスの間、訂正可能なエラーを検出する。その訂正可能なエラーは、エラー検出訂正回路によって検出される。次に、システムは、メモリ位置に関連されたキャッシングラインのためのタグビットを読み取る。そのタグビットは、キャッシングラインのための一貫性プロトコル状態( *c o h e r e n c y p r o t o c o l s t a t e* )を示す状態情報と、キャッシングラインのためのアドレス情報をも含む。次いでシステムは、テスト結果を生成するために、第1のプロセッサに、メモリ位置へ読み取り動作および書き込み動作を実行させることによって、メモリ位置をテストする。最後に、システムは、可能な場合、訂正可能なエラーの原因を決定するために、テスト結果およびタグビットを使用する。

## 【0012】

40

この実施形態での一つの変形において、メモリ位置をテストすることは、訂正可能なエラーについての情報を含む *a s y n c h r o n o u s f a u l t s t a t u s r e g i s t e r* (AFSR) および *a s y n c h r o n o u s f a u l t a d d r e s s r e g i s t e r* (AFAR) をクリアすることと、キャッシングからキャッシングラインをフラッシュする( *f l u s h* )ことと、キャッシングラインを、メインメモリからキャッシングに引き込ませられることで、メモリ位置を再度読み取ることと、AFSRおよびAFARレジスタを読み取り、クリアすることと、エラー検出訂正回路に、訂正可能なエラーを訂正させることと、メインメモリへキャッシングライン( エラーは訂正されている)をフラッシュして戻すこととを含む。

## 【0013】

50

さらなる変形において、メモリ位置を再度読み取ることは、キャッシングにおける修正された状態においてキャッシングラインが存在することを保証するために、微小の比較およびスワップ( C A S )動作の実行を含む。

【 0 0 1 4 】

さらなる変形において、メモリ位置を再度読み取ることが訂正可能なエラーを生じさせない場合、システムは、以前の読み取りタグビットを試験することによって訂正可能なエラーの原因を決定する。システムは、( 1 ) タグからのアドレスビットが、A F A R から訂正可能なエラー読み取りのためのアドレスに対応するビットと一致する場合、および、( 2 ) タグからの状態ビットが、タグビットが読み取られた場合、キャッシングラインがキャッシングにおいて、共有された状態、または排他的な状態のいずれかである場合、訂正可能なエラーが間欠エラーであると決定する。

【 0 0 1 5 】

さらなる変形において、メモリ位置を再度読み取ることが、訂正可能なエラーを生じさせる場合、システムは、さらに再度メモリ位置を読み取り、A F S R およびA F A R を読み取り、クリアする。

【 0 0 1 6 】

さらなる変形において、メモリ位置をさらに再度読み取ることが訂正可能なエラーを生じさせない場合、システムは、所定の時間間隔の後にメモリ位置を読み取る。所定の時間間隔の後にメモリ位置を読み取ることが訂正可能なエラーを生じさせる場合、システムは、メモリ位置がリーキーであることを決定する。さもなければ、システムは、訂正可能なエラーが永続的エラーであることを決定する。

【 0 0 1 7 】

この実施形態での一つの変形において、メモリ位置をさらに再度読み取ることが訂正可能なエラーを生じさせる場合、システムは、第 2 のプロセッサに、訂正可能なエラーを分類させる。第 2 のプロセッサがエラーを検出しない場合、システムは、第 1 のプロセッサが不良な読み取り装置であることを決定する。第 2 のプロセッサがステイックなエラーではないエラーを検出する場合、システムは第 1 のプロセッサが不良な書き込み装置であることを決定する。さもなければ、第 2 のプロセッサがステイックなエラーを検出する場合、システムは、メモリ位置における少なくとも一つのビットがスタックしている( i s   s t u c k ) ことを決定する。

【 0 0 1 8 】

本発明は、さらに以下の手段を提供する。

【 0 0 1 9 】

( 項目 1 )

訂正可能なメモリエラーの原因を決定する方法であって、

第 1 のプロセッサによるメインメモリにおけるメモリ位置へのアクセスの間、エラー検出訂正回路によって検出される該訂正可能なエラーを検出することと、

該メモリ位置に関連されたキャッシングラインのためにタグビットを読み取ることであって、該タグビットは、該キャッシングラインのためのアドレス情報および、該キャッシングラインのための一貫性プロトコル状態を指示する状態情報を含む、ことと、

テスト結果を生成するために、該第 1 のプロセッサに、該メモリ位置に対する読み取り動作および書き込み動作を実行させることによって、該メモリ位置をテストすることと、

可能である場合、該訂正可能なエラーの原因を決定するために、該テスト結果および該タグビットを利用することと

を包含する、方法。

【 0 0 2 0 】

( 項目 2 )

上記メモリ位置をテストすることが、

上記訂正可能なエラーについての情報を含む、a s y n c h r o n o u s   f a u l t s t a t u s   r e g i s t e r ( A F S R ) およびa s y n c h r o n o u s   f a

10

20

30

40

50

u l t a d d r e s s r e g i s t e r ( A F A R ) をクリアすることと、

キャッシュから上記キャッシュラインをフラッシュすることと、

該メモリ位置を再度読み取ることであって、それによって、メインメモリから該キャッシュへ、該キャッシュラインが引き戻される、ことと、

該 A F S R および該 A F A R レジスタを読み取り、クリアすることと、

上記エラー検出訂正回路に、該訂正可能なエラーを訂正させることと、

該キャッシュライン（エラーは訂正されている）をメインメモリへフラッシュして戻すことと

を包含する、項目 1 に記載の方法。

## 【0021】

(項目3)

上記メモリ位置を再度読み取ることが、上記キャッシュにおける修正された状態において上記キャッシュラインが存在することを保証するために、アトミックな比較およびスワップ（C A S）動作を実行することを包含する、項目 1 に記載の方法。

## 【0022】

(項目4)

上記メモリ位置を再度読み取ることが訂正可能なエラーを生じさせない場合、上記訂正可能なエラーの原因を決定することが、

上記読み取りタグビットを試験することと、

上記タグからのアドレスビットが、上記 A F A R からの訂正可能なエラーの読み取りのアドレスの対応するビットと一致する場合、および、キャッシュラインが該タグビットが読み取られた場合にキャッシュにおいて、共有された（S）状態または排他的（E）状態であることを、該タグからの状態ビットが指示する場合、間欠エラーがあることを決定することと

を含む、項目 2 に記載の方法。

## 【0023】

(項目5)

上記メモリ位置を再度読み取ることが訂正可能なエラーを生じさせる場合、上記方法が、

該メモリ位置をさらに再度読み取ることと、

上記 A F S R および上記 A F A R レジスタを再度読み取りおよびクリアすることとをさらに包含する、項目 2 に記載の方法。

## 【0024】

(項目6)

上記メモリをさらに再度読み取ることが訂正可能なエラーを生じさせない場合、上記方法が、

所定の時間間隔の後に上記メモリ位置を再度読み取ることと、

該所定の時間間隔の後に該メモリ位置を再度読み取ることが、訂正可能なエラーを生じさせる場合、該メモリ位置がリーキーであることを決定することと、

さもなければ、該訂正可能なエラーが永続的エラーであることを決定することとをさらに包含する、項目 5 に記載の方法。

## 【0025】

(項目7)

上記メモリ位置をさらに再度読み取ることが訂正可能なエラーを生じさせる場合、上記方法が、

第 2 のプロセッサに、該訂正可能なエラーを分類させることと、

該第 2 のプロセッサがエラーを検出しない場合、上記第 1 のプロセッサが不良な読み取り装置であると決定することと、

該第 2 のプロセッサがスティックエラーでないエラーを検出する場合、該第 1 のプロセッサが不良な書き込み装置であると決定することと、

10

20

30

40

50

該第2のプロセッサがスティックエラーを検出する場合、該メモリ位置における少なくとも一つのビットがスタックしていると決定することと

をさらに包含する、項目5に記載の方法。

## 【0026】

(項目8)

コンピュータによって実行された場合、該コンピュータに、訂正可能なメモリエラーの原因を決定するための方法を実行させる命令を記憶するコンピュータ可読の記憶媒体であって、該方法は、

第1のプロセッサによるメインメモリにおけるメモリ位置へのアクセスの間、エラー検出訂正回路によって検出される訂正可能なエラーを検出することと、10

該メモリ位置に関連されたキャッシュラインのためにタグビットを読み取ることであって、該タグビットは、該キャッシュラインのためのアドレス情報および、該キャッシュラインのための一貫性プロトコル状態を指示する状態情報を含む、ことと、

テスト結果を生成するために、該第1のプロセッサに、該メモリ位置に対する読み取り動作および書き込み動作を実行させることによって、該メモリ位置をテストすることと、20

可能である場合、該訂正可能なエラーの原因を決定するために、該テスト結果および該タグビットを利用することと

を包含する、コンピュータ可読の記憶媒体。

## 【0027】

(項目9)

上記メモリ位置をテストすることが、20

上記訂正可能なエラーについての情報を含む、asynchronous fault status register (AFSR) および asynchronous fault address register (AFAR) をクリアすることと、

キャッシュから上記キャッシュラインをフラッシュすることと、

該メモリ位置を再度読み取ることであって、それによって、メインメモリから該キャッシュへ、該キャッシュが引き戻される、ことと、

該AFSRおよび該AFARレジスタを読み取り、およびクリアすることと、

上記エラー検出訂正回路に、訂正可能なエラーを訂正させることと、

該キャッシュライン(エラーは訂正されている)をメインメモリへフラッシュして戻すことと30

を含む、項目8に記載のコンピュータ可読の記憶媒体。

## 【0028】

(項目10)

上記メモリ位置を再度読み取ることが、上記キャッシュにおける修正された状態において、上記キャッシュラインが存在することを保証するために、アトミックな比較およびスワップ(CAS)動作を実行することを包含する、項目8に記載のコンピュータ可読の記憶媒体。

## 【0029】

(項目11)

上記メモリ位置を再度読み取ることが、訂正可能なエラーを生じさせない場合、該訂正可能なエラーの原因を決定することが、40

以前の読み取りタグビットを試験することと、

上記タグからのアドレスビットが上記AFARからの該訂正可能なエラー読み取りの上記アドレスに対応するビットと一致する場合、および、キャッシュラインが、該タグビットが読み取られた場合にキャッシュにおいて、共有された(S)状態または排他的(E)状態であることを、該タグからの状態ビットが指示する場合、間欠エラーがあることを決定することと

を含む、項目9に記載のコンピュータ可読の記憶媒体。

## 【0030】

50

## (項目 1 2 )

上記メモリ位置を再度読み取ることが訂正可能なエラーを生じさせる場合、上記方法が

、該メモリ位置をさらに再度読み取ることと、

上記 A F S R および上記 A F A R レジスタを再度読み取り、クリアすることと

をさらに包含する、項目 9 に記載のコンピュータ可読の記憶媒体。

## 【0031】

## (項目 1 3 )

上記メモリ位置をさらに再度読み取ることが訂正可能なエラーを生じさせない場合、上記方法が、

所定の時間間隔の後に該メモリ位置を再度読み取ることと、

該所定の時間間隔の後に該メモリ位置を再度読み取ることが訂正可能なエラーを生じさせる場合、該メモリ位置がリーキーであることを決定することと、

さもなければ、該訂正可能なエラーが永続的エラーであることを決定することと

をさらに包含する、項目 1 2 に記載のコンピュータ可読の記憶媒体。

## 【0032】

## (項目 1 4 )

上記メモリ位置をさらに再度読み取ることが訂正可能なエラーを生じさせる場合、上記方法が、

第 2 のプロセッサに該訂正可能なエラーを分類させることと、

該第 2 のプロセッサがエラーを検出しない場合、上記第 1 のプロセッサが不良な読み取り装置であると決定することと、

該第 2 のプロセッサがステイックエラーでないエラーを検出する場合、該第 1 のプロセッサが不良な書き込み装置であると決定することと、

該第 2 のプロセッサがステイックエラーを検出する場合、該メモリ位置における少なくとも一つのビットがスタックしていると決定することと

をさらに包含する、項目 1 2 に記載のコンピュータ可読の記憶媒体。

## 【0033】

## (項目 1 5 )

上記訂正可能なメモリエラーの原因を決定する装置であって、

第 1 のプロセッサによるメインメモリにおけるメモリ位置へのアクセスの間、訂正可能なエラーを検出するように構成されたエラー訂正検出回路と、

該メモリ位置に関連されたキャッシュラインのためにタグビットを読み取るように構成された読み取りメカニズムであって、該タグビットは、該キャッシュラインのためのアドレス情報および、該キャッシュラインのための一貫性プロトコル状態を指示する状態情報を含む、読み取りメカニズムと、

テスト結果を生成するために、該第 1 のプロセッサに、該メモリ位置に対する読み取り動作および書き込み動作を実行させることによって、該メモリ位置をテストするように構成されたテストメカニズムと、

可能である場合、該訂正可能なエラーの原因を決定するために、該テスト結果および該タグビットを利用するように構成された、エラー分類メカニズムと

を備える、装置。

## 【0034】

## (項目 1 6 )

上記テストメカニズムが、

上記訂正可能なエラーについての情報を含む、asynchronous fault status register (AFSR) および asynchronous fault address register (AFAR) をクリアするように、

キャッシュから上記キャッシュラインをフラッシュするように、

該メモリ位置を再度読み取るようにであって、それによって、メインメモリから該キャ

10

20

30

40

50

ツシュへ、該キャッシュラインが引き戻される、ように、

該AFSRおよび該AFARレジスタを読み取り、クリアするように、

上記エラー検出訂正回路に、該訂正可能なエラーを訂正させるように、および、

該キャッシュライン（エラーは訂正されている）をメインメモリへフラッシュして戻すように、

構成される、項目15に記載の装置。

#### 【0035】

（項目17）

上記メモリ位置を再度読み取る間、上記テストメカニズムは、上記キャッシュにおける修正された状態において上記キャッシュラインが存在することを保証するために、アトミックな比較およびスワップ（CAS）動作を実行するように構成されている、項目15に記載の装置。 10

#### 【0036】

（項目18）

上記メモリ位置を再度読み取ることが訂正可能なエラーを生じさせない場合、エラー分類メカニズムが、

以前に読み取られたタグビットを試験するように、および、

上記タグからのアドレスビットが、上記AFARからの訂正可能なエラー読み取りのためのアドレスに対応するビットと一致する場合、および、キャッシュラインが、該タグビットが読み取られていた場合にキャッシュにおいて共有された（S）状態または排他的（E）状態であることを、該タグからの状態ビットが指示する場合、間欠エラーがあることを決定するように 20

構成される、項目16に記載の装置。

#### 【0037】

（項目19）

上記メモリ位置を再度読み取ることが訂正可能なエラーを生じさせる場合、上記エラー分類メカニズムが、

該メモリ位置をさらに再度読み取るように、および、

上記AFSRおよび上記AFARレジスタを再度読み取り、クリアするように

構成される、項目16に記載の装置。 30

#### 【0038】

（項目20）

上記メモリをさらに再度読み取ることが訂正可能なエラーを生じさせない場合、上記エラー分類メカニズムが、

所定の時間間隔の後に上記メモリ位置を再度読み取るように、

該所定の時間間隔の後に該メモリ位置を再度読み取ることが訂正可能なエラーを生じさせる場合、該メモリ位置がリーキーであることを決定するように、および、

さもなければ、該訂正可能なエラーが永続的エラーであることを決定するように、

構成される、項目19に記載の装置。 40

#### 【0039】

（項目21）

上記メモリ位置をさらに再度読み取ることが訂正可能なエラーを生じさせる場合、上記エラー分類メカニズムは、

第2のプロセッサに、該訂正可能なエラーを分類させるように、

該第2のプロセッサがエラーを検出しない場合、上記第1のプロセッサが不良な読み取り装置であると決定するように、

該第2のプロセッサがステイックエラーでないエラーを検出する場合、該第1のプロセッサが不良な書き込み装置であると決定するように、および、

該第2のプロセッサがステイックエラーを検出する場合、該メモリ位置における少なくとも一つのビットがスタックしていると決定するように、 50

構成される、項目 19 に記載の装置。

【0040】

(摘要)

本発明における一実施形態は、訂正可能なメモリエラーの原因を決定するシステムを提供する。第1に、システムは、第1のプロセッサによってメインメモリにおけるメモリ位置へのアクセスの間、訂正可能なエラーを検出する。その訂正可能なエラーは、エラー検出および訂正回路によって検出される。次に、システムは、メモリ位置に関連されたキャッシュラインのためのタグビットを読み取る。そのタグビットは、キャッシュラインのための一貫性プロトコル状態を示す状態情報だけでなく、キャッシュラインのためのアドレス情報をも含む。次いでシステムは、テスト結果を生成するために、第1のプロセッサに、メモリ位置へ読み取り動作および書き込み動作を実行させることによって、メモリ位置をテストする。最後に、システムは、可能な場合、訂正可能なエラーの原因を決定するために、テスト結果およびタグビットを使用する。

10

【発明を実施するための最良の形態】

【0041】

以下の記述は、当業者が本発明を作成または利用することができるよう示されており、特定の応用およびその必要に関連して提供される。開示された実施形態への様々な修正は、当業者にとって容易に明らかであり、ここにおいて定義される一般的な原理は、本発明の意図および範囲からそれることなく、他の実施形態および応用へ適応される。このように、本発明は、ここで示される実施形態に限定されるものではなく、ここにおいて開示された原理および特徴と一貫した、最も広い範囲に従うものである。

20

【0042】

この詳細な説明において記述されるデータ構造およびコードは、通常、コンピュータ可読記憶媒体上に記憶され、コンピュータシステムによる使用のためのコードおよび/またはデータを記憶することが可能な任意の装置または媒体であり得る。これはディスクドライブ、磁気テープ、CD（コンパクトディスク）、およびDVD（d i g i t a l v e r s a t i l e d i s c またはデジタルビデオディスク）などのような磁気および光学記憶装置、ならびに、伝送媒体（信号が変調される搬送波があってもなくても）において実施されるコンピュータ指示信号を含むが、それらに限定されるものではない。例えば、伝送媒体は、インターネットのような通信ネットワークを含み得る。

30

【0043】

(コンピュータシステム)

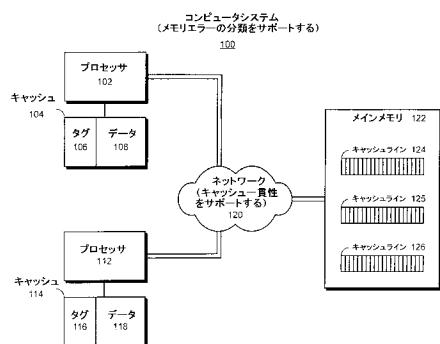

図1は、本発明における一実施形態にしたがったコンピュータシステム100を示す。コンピュータシステム100は、一般に、一つ以上のキャッシュおよび一つ以上のプロセッサを有するコンピュータシステムの任意のタイプを含み得る。これは、マイクロプロセッサに基づくコンピュータシステム、メインフレームコンピュータ、デジタル信号プロセッサ、ポータブルコンピュータ装置、パーソナルオーガナイザー、デバイス制御器、および電気機器を有する計算エンジンを含むが、それらに限定されるものではない。

【0044】

図1に示されるように、コンピュータシステム100は、プロセッサ102およびプロセッサ112を含み、それらは個々に、キャッシュ104およびキャッシュ114に関連される。キャッシュ104およびキャッシュ114は、メインメモリ122から引き出されるキャッシュラインのためのタグおよびデータを含む。メインメモリ122は、ランダムアクセスメモリの任意のタイプを含み、それは、コンピュータシステム100のためのコードおよびデータを記憶する。特に、メインメモリ122は、キャッシュライン124～126を含み、キャッシュラインと関連されたデータを記憶することができる。

40

【0045】

キャッシュライン124～126は、通信ネットワーク120を介して、メインメモリ122とキャッシュ104および114との間で転送され得、キャッシュ104および114におけるキャッシュラインのコピーが、メインメモリ122におけるキャッシュライ

50

ンのための対応するデータと一致され続けることを保証するためのキャッシュ貫性 ( cache-coherence ) プロトコルをサポートする。例えば、本発明における一実施形態において、コンピュータシステム 100 は、MOESI ( Modified-Owner-Exclusive-Shared-Invalid ) キャッシュ貫性プロトコルの一つの変形をサポートする。

#### 【0046】

コンピュータシステム 100 はまた、図 2 ~ 図 5 にて参照する以下のさらなる記述において記載されるように、メモリエラーを分類するためのサポートを提供する。

#### 【0047】

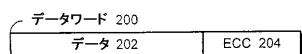

##### (データワード)

図 2 は、本発明の一実施形態にしたがうメインメモリ 122 におけるデータワード 200 を示す。データワード 200 は、ECC ビット 204 だけでなく、データ 202 をも含み、複合データワードのための 1 ビットエラー訂正および 2 ビットエラー検出をサポートし、データ 202 および ECC ビット 204 の両方を含む。

#### 【0048】

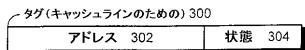

##### (キャッシュラインタグ)

図 3 は、本発明の一実施形態にしたがったキャッシュラインのためのタグ 300 を示す。タグ 300 は、対応するキャッシュラインのための、より上位のアドレスビット 302 を含む。タグ 300 はまた、状態ビット 304 を含み、その対応するキャッシュラインのための MOESI 状態を特定する。これらの状態ビット 304 はまた、対応するキャッシュラインが汚れているかいないかといった、その対応するキャッシュラインのための他の情報を示すことができる。

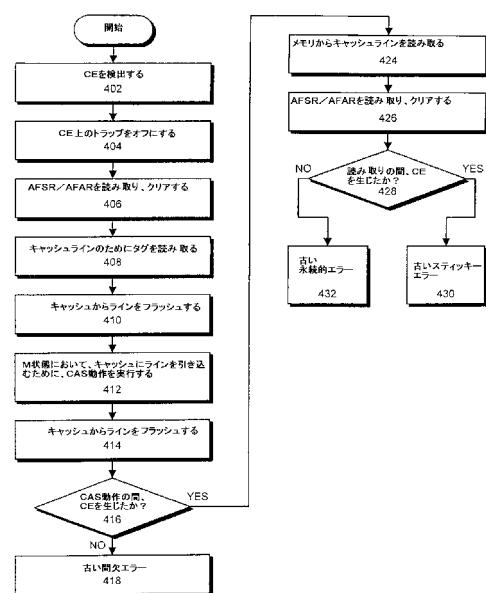

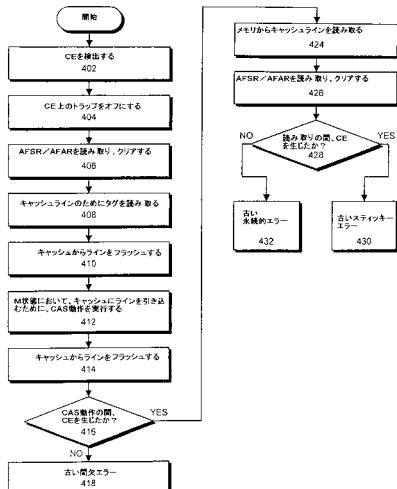

##### (メモリエラーの原因を診断するプロセス)

図 4 は、本発明の一実施形態にしたがうメモリエラーの原因を診断するプロセスを示すフローチャートの一部である。メインメモリ内の位置から読み取り動作間のプロセッサ内の ECC 回路によって、訂正可能なエラーが検出された場合、このプロセスは開始する (ステップ 402)。

#### 【0049】

この訂正可能なエラーに応答して、システムは多数のアクションを実行する。第 1 に、システムは、訂正可能なエラー (CE) のトラップをオフにし (ステップ 404)、AFSR / AFAR 登録を読み取り、クリアする (ステップ 406)。次に、システムは、メモリ位置に関連されたキャッシュラインからタグを読み取る (ステップ 408)。

#### 【0050】

システムは、次いで、キャッシュからキャッシュラインを除去する (ステップ 410)。これは、メモリ位置に指示された次の読み取り動作が、キャッシュラインにメインメモリから読み取りされることを保証する。次に、システムは、メインメモリからのキャッシュラインを修正された (M) 状態におけるキャッシュに引き込むために、比較およびスワップ (compare-and-swap) (CAS) 動作を実行する (ステップ 412)。この CAS 動作は、アトミックな (atomic) 動作であり、他のプロセス (またはプロセッサ) は、M 状態において、キャッシュラインをキャッシュに持ち込むプロセスを妨害することに注意したい。

#### 【0051】

次に、システムは、メインメモリへキャッシュからキャッシュラインを除去する (ステップ 414)。CAS 動作がまた CE を生じさせる場合、キャッシュラインが CAS 動作によるキャッシュにインストールされる以前に、エラー訂正回路は自動的にエラーを訂正することに注意したい。ゆえに、メインメモリへキャッシュラインを除去することは、訂正されたデータを、メモリに書き込みさせる。

#### 【0052】

次に、システムは、例えば、AFSR における CE ビットを試験することによって、先行する CAS 動作が CE を生じさせたかどうかを決定する (ステップ 416)。そうでな

い場合、システムは、古いエラータイプ（先行技術システムの下での）が間欠エラーであることを決定する（ステップ418）。

#### 【0053】

他方で、ステップ416で、システムは、先行するCAS動作がまた、CEを生じさせたと決定する場合、システムは、再度、メモリからキャッシュラインを読み取り（ステップ424）、次いで、AFSR/AFARを読み取り、クリアする（ステップ426）。

#### 【0054】

次に、システムは、読み取り動作がCEを生じさせたかどうかを決定する（ステップ428）。生じた場合、システムは、古いエラータイプがスティッキ-エラーであることを決定する（ステップ430）。生じない場合、システムは、古いエラータイプが永続的エラーであることを決定する（ステップ432）。

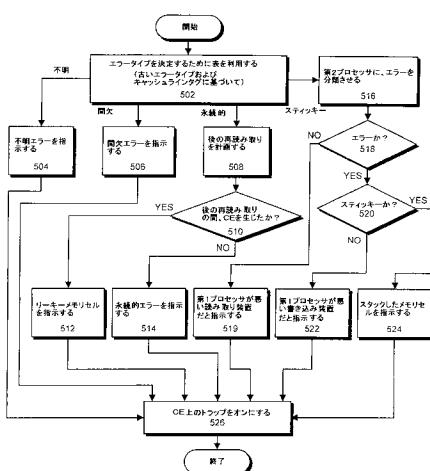

#### 【0055】

ついで、これらのありうる終端の状態、418、430、432のそれぞれから、システムは図5のフローチャートにおいて特定された動作を続行する。第1に、システムは古いエラータイプおよび以前の読み取りキャッシュラインタグからエラーの新しいタイプを決定するために、表1（下にある）を使う（ステップ502）。表1は、本発明における一実施形態にしたがつた、メモリエラーを分類するための表を表している。

#### 【0056】

##### 【表1】

10

20

| AFAR一致 | キャッシュライン状態 | 古いタイプ  | 新しいタイプ |

|--------|------------|--------|--------|

| No     | N/A        | 間欠     | 不明     |

| No     | N/A        | 永続性    | 永続性    |

| No     | N/A        | スティッキー | スティッキー |

| Yes    | I,M,O      | 間欠     | 不明     |

| Yes    | S,E        | 間欠     | 間欠     |

| Yes    | I,S,E      | 永続性    | 永続性    |

| Yes    | M,O        | 永続性    | スティッキー |

| Yes    | Any        | スティッキー | スティッキー |

30

次に、表1が、新しいエラータイプが「不明」を指示した場合、システムは不明エラー（ステップ504）を指示する。同様に、表1が、新しいエラータイプが「間欠」であると指示した場合、システムは、間欠エラーを指示する（ステップ506）。

#### 【0057】

表1を参照し、キャッシュライン状態がI、M、またはOだった場合（ステップ410におけるキャッシュラインの除去がメインメモリへの書き込みを生じていることを意味する）、および、古いエラータイプが間欠だった場合、新しいエラータイプは間欠の代わりに「不明」である。これは、偽間欠の診断を防ぐ。

#### 【0058】

次に、表1が、新しいエラータイプが「永続的」と指示する場合、システムは、後において、メモリ位置の再読み取りを計画し、次いで実行する（ステップ508）。再読み取りが完了した後、システムは、訂正可能なエラーが生じているかどうかを決定する（ステップ510）。生じていない場合、システムは永続的エラーを指示する（ステップ514）。さもなければ、訂正可能なエラーが再読み取りの間に生じた場合、システムは「リーキーメモリセル」を指示する（ステップ512）。（この場合、負荷は、再読み取りの間のエラーを生じさせるメモリセルをリークする。）

40

次に、表1が、新しいエラータイプが「スティッキー-」であると指示する場合、システムは、コンピュータシステムにおける第2のプロセッサに、メモリエラーを分類させる（ステップ516）。第2のプロセッサによってエラーが検出されない場合、システムは、

50

第1のプロセッサが不良な読み取り装置であることを指示する(ステップ519)。

【0059】

さもなければ、システムは、第2のプロセッサがそのエラーをスティックエラーとして分類したかどうかを決定する(ステップ520)。スティックエラーである場合、システムは、メモリセルがくつついでいることを指示する(ステップ524)。スティックエラーでない場合、システムは第1のプロセッサが不良な書き込み装置であると指示する(ステップ522)。

【0060】

最後に、システムが、状態504、506、512、514、519、522および524において、様々なエラー状態を指示した後、システムはCEのために、トラップをオンにする(ステップ526)。ここで、診断プロセスは完了する。

【0061】

本発明における実施形態の前述の記載は、図示および描写のためだけの目的で示されている。それらは網羅的であることを意図されているわけではなく、または、本発明を開示された形式に限定することを意図されているわけでもない。したがって、多くの修正や変化が当業の実施者にとって明らかである。追加的に、上記の開示は本発明を限定することを意図されていない。本発明の範囲は、添付された請求項によって限定される。

【図面の簡単な説明】

【0062】

【図1】本発明の一実施形態にしたがったコンピュータシステムである。

20

【図2】本発明の一実施形態にしたがったメモリにおけるデータワードである。

【図3】本発明の一実施形態にしたがったキャッシュラインのためのタグである。

【図4】本発明の一実施形態にしたがった、メモリエラーの原因を診断するプロセスのためのフローチャートの一部を示す。

【図5】本発明の一実施形態にしたがった、メモリエラーの原因を診断するプロセスのためのフローチャートの別の一部を示す。

【符号の説明】

【0063】

102 プロセッサ

104 キャッシュ

106 タグ

108 データ

112 プロセッサ

114 キャッシュ

116 タグ

118 データ

120 ネットワーク

122 メインメモリ

124、125、126 キャッシュライン

30

【図1】

【図2】

(従来技術)

【図3】

(従来技術)

【図4】

【図5】

---

フロントページの続き

(72)発明者 スティーブン エー. チェッシン

アメリカ合衆国 カリフォルニア 94040, マウンテン ビュー, ロイド ウェイ 14

26

(72)発明者 タリク ピー. ソイダン

アメリカ合衆国 マサチューセッツ 01720, アクトン, リバティ ストリート 74

(72)発明者 ルイス ワイ. チエン

アメリカ合衆国 マサチューセッツ 02472, ウォータータウン, グリーン ストリート

71

F ターム(参考) 5B005 JJ01 KK13 MM01 NN31 PP03 SS11 WV13 WV14 WV22 WW02

WW17

5B018 GA02 GA05 HA14 KA01 KA12 MA01 MA03 NA02 RA01 RA04

RA11