# ITALIAN PATENT OFFICE

Document No.

102008901686937A1

Publication Date

20100615

Applicant

STMICROELECTRONICS DESIGN AND APPLICATION S.R.O.

Title

REGOLATORE LINEARE DI TIPO LOW-DROPOUT E CORRISPONDENTE

PROCEDIMENTO

**DESCRIZIONE** dell'invenzione industriale dal titolo:

"Regolatore lineare di tipo low-dropout e corrispondente procedimento"

di: STMicroelectronics Design and Application s.r.o., nazionalità ceca, Pobrezni 620/3 - 186 00 Praha 8 - Repubblica Ceca

Inventore designato: Karel NAPRAVNIK

Depositata il: 15 dicembre 2008

\*\*\*\*\*

**TESTO DELLA DESCRIZIONE**

Campo dell'invenzione

La presente descrizione si riferisce ai regolatori lineari di tipo low-dropout (LDO). Gli LDO sono utilizzati in un'ampia gamma di applicazioni nel settore dell'elettronica al fine di applicare ad un carico un segnale regolato in funzione di un segnale di riferimento.

Descrizione della tecnica relativa

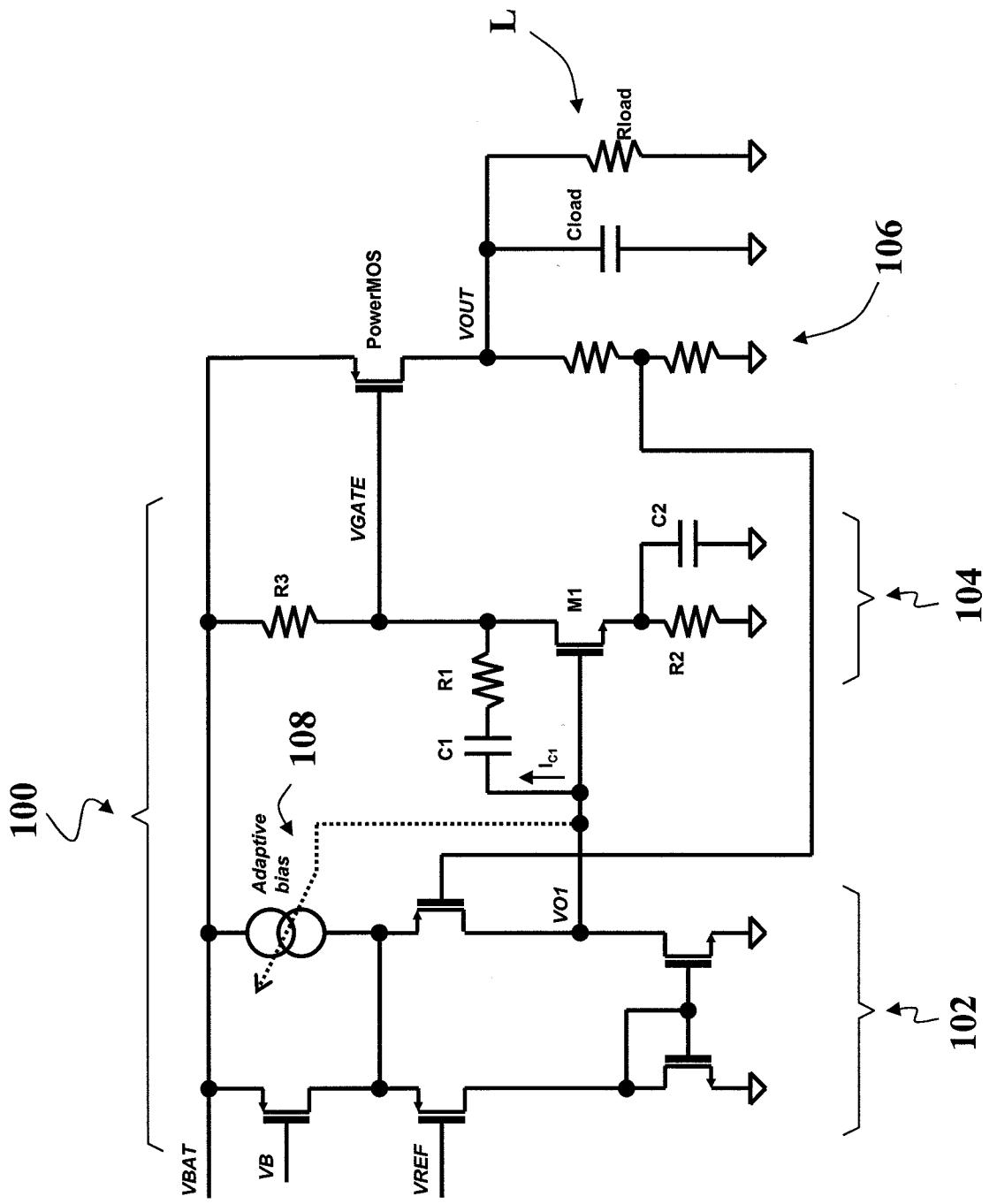

Lo schema della figura 1 è un esempio della configurazione circuitale di un regolatore lineare di tipo low-dropout di tipo convenzionale. L'LDO della figura 1 è sostanzialmente costituito da una disposizione in cascata di un amplificatore di errore 100 (a sua volta comprendente un amplificatore differenziale 102 che riceve un segnale di riferimento VREF seguito da uno stadio di guadagno 104) e di uno stadio di uscita 106. Lo stadio di uscita 106 comprende un MOS di potenza che riceve dallo stadio di guadagno 104 una tensione VGATE sul suo gate ed applica una tensione di uscita VOUT ad un carico comprendente una componente resistiva Rload ed una componente capacitiva Cload.

Un LDO può utilizzare nell'amplificatore differenziale 102 un bias adattativo 108 per ridurre la corrente di

quiescenza e migliorare in modo conseguente l'efficienza alle basse correnti. All'uscita (tensione V01) dell'amplificatore differenziale 102 sono normalmente collegati elementi di compensazione di frequenza (ad esempio uno stadio RC comprendente un resistore R1 ed un condensatore C1). Questo nodo è un nodo ad impedenza elevata e la compensazione è molto efficace.

La denominazione risposta ai transitori di carico (Load Transient Response) indica correntemente la risposta della tensione di uscita (VOUT) a rapidi cambiamenti della corrente nel carico. Rapidi cambiamenti della corrente del carico possono produrre sottoelongazioni e sovraelongazioni nella tensione di uscita (VOUT).

#### Scopo e sintesi dell'invenzione

Lo scopo dell'invenzione è quindi di eliminare questi effetti indesiderati dei rapidi cambiamenti della corrente nel carico.

Secondo la presente invenzione, tale scopo è ottenuto tramite una soluzione avente le caratteristiche esposte nelle rivendicazioni che seguono. L'invenzione riguarda anche un corrispondente procedimento.

Le rivendicazioni formano parte integrante dell'insegnamento qui somministrato in relazione all'invenzione.

In una forma di attuazione, un miglioramento della risposta ai transitori di carico in un regolatore di tipo low-dropout (LDO) è fornito sulla base di un miglioramento dello slew rate dell'uscita dell'amplificatore differenziale conseguita eliminando il carico capacitivo creato dagli elementi di compensazione in frequenza.

Una forma di attuazione di questo principio è particolarmente adatta per LDO con una coppia differenziale con bias adattativi.

Breve descrizione delle viste annesse

L'invenzione sarà ora descritta, a titolo di esempio non limitativo, con riferimento alle viste annesse, in cui:

- la figura 1 è già stata descritta in precedenza,

- la figura 2 è rappresentativa di una possibile forma di attuazione della soluzione qui descritta, e

- la figura 3 fornisce ulteriori dettagli sulla forma di attuazione della figura 2.

Descrizione particolareggiata di forme di attuazione

Nella seguente descrizione, sono illustrati vari dettagli specifici finalizzati ad un'approfondita comprensione delle forme di attuazione. Le forme di attuazione possono essere realizzate senza uno o più dei dettagli specifici, o con altri metodi, componenti, materiali, etc. In altri casi, strutture, materiali od operazioni noti non sono mostrati o descritti in dettaglio per evitare di rendere oscuri vari aspetti delle forme di attuazione.

Il riferimento ad "una forma di attuazione" nell'ambito di questa descrizione sta ad indicare che una particolare configurazione, struttura o caratteristica descritta in relazione alla forma di attuazione è compresa in almeno una forma di attuazione. Quindi, frasi come "in una forma di attuazione", eventualmente presenti in diversi luoghi di questa descrizione, non sono necessariamente riferite alla stessa forma di attuazione. Inoltre, particolari conformazioni, strutture, o caratteristiche, possono essere combinati in ogni modo adeguato in una o più forme di attuazione.

I riferimenti qui utilizzati sono soltanto per comodità e non definiscono dunque l'ambito di tutela o la portata delle forme di attuazione.

La forma di attuazione qui descritta è una modifica proposta della struttura generale di un LDO illustrata nella figura 1, di conseguenza la descrizione particolareggiata delle forme di attuazione qui descritte non ripeterà quegli elementi che sono comuni con la struttura della figura 1.

Si comprenderà altrimenti che, in tutte le viste qui annesse, componenti/elementi identici o equivalenti fra loro sono indicati con gli stessi riferimenti.

Si apprezzerà inoltre che la forma di attuazione qui descritta è applicabile a qualunque struttura di LDO comprendente un amplificatore di errore comprendente un amplificatore differenziale ed uno stadio di guadagno disposti in cascata ed aventi interposta fra loro una rete di compensazione di frequenza, in modo indipendente dai dettagli costruttivi di questi amplificatori, stadi e rete. Il fatto di riferirsi ai dettagli costruttivi della struttura di LDO della figura 1 ha pertanto solo scopi esemplificativi e non limitativi.

La forma di attuazione qui descritta è basata sul riconoscimento del fatto che un punto critico per la risposta ai transitori di carico in un LDO così come rappresentato nella figura 1 è costituito dal nodo di uscita V01 dell'amplificatore di errore 102.

Si presume che il condensatore di compensazione C1 collegato a questo nodo non crei un polo dominante; la sua capacità è quindi scelta ad un valore molto basso e non ha un'influenza marcata sulla larghezza di banda del regolatore (in un modello a piccoli segnali). Dall'altra

parte, il condensatore C1 è caricato da una corrente  $I_{C1}$  desunta dall'uscita dell'amplificatore differenziale 102 e questa corrente è limitata dalla corrente di bias del bias adattativo 108. Se la corrente di bias è molto piccola (una situazione comune, se si usa un bias adattativo), allora la carica del condensatore di compensazione C1 è molto lenta. Come risultato si riduce lo slew rate dell'amplificatore di errore 102 e si deteriora la risposta ai transitori sul carico (segnale ampio).

Osservando in modo sperimentale la risposta ai transitori di carico di un LDO in presenza ed in assenza del bias adattativo, si nota che la sottoelongazione della tensione di uscita è molto maggiore nel caso in cui è presente il bias adattativo. Questo si può spiegare notando che, poiché l'LDO è in uno stato di bassa corrente di bias prima di una transizione nella corrente di uscita  $I_{OUT}$ , allora tutte le risposte del regolatore sono lente. Un'analisi più dettagliata della sottoelongazione fa vedere che, dopo una transizione nella corrente di uscita  $I_{OUT}$ , la tensione di uscita  $V_{OUT}$  comincia a scendere (il coefficiente angolare è determinato dai valori di  $I_{OUT}$  e  $C_{LOAD}$ ). L'errore di regolazione determina un aumento della tensione di uscita  $V_{O1}$  dell'amplificatore differenziale 102 e la velocità di questo incremento è limitata dalla corrente di bias dell'amplificatore differenziale 102 che fluisce nel condensatore di compensazione C1 ( $I_{C1} \sim I_{BIAS} \sim dV_{O1}/dt$ ). Dal momento che un LDO con bias adattativo parte con una corrente di bias ridotta, il ritardo che si manifesta su  $V_{O1}$  determina una sottoelongazione maggiore.

La forma di attuazione qui descritta porta ad un miglioramento dei transitori sul carico aumentando lo slew rate dell'uscita dell'amplificatore differenziale 102.

Questo risultato può essere ottenuto eliminando l'influenza sull'uscita dell'amplificatore differenziale 102 del carico capacitivo creato dagli elementi di compensazione di frequenza. Questo principio di funzionamento è particolarmente adatto per LDO con una coppia differenziale con bias adattativo.

E' possibile ridurre l'effetto sulla rete di compensazione di frequenza nell'intervallo in cui la tensione di uscita  $V_{OUT}$  si trova al di fuori del campo desiderato di valori ed il regolatore è in uno stato con un errore di regolazione elevato.

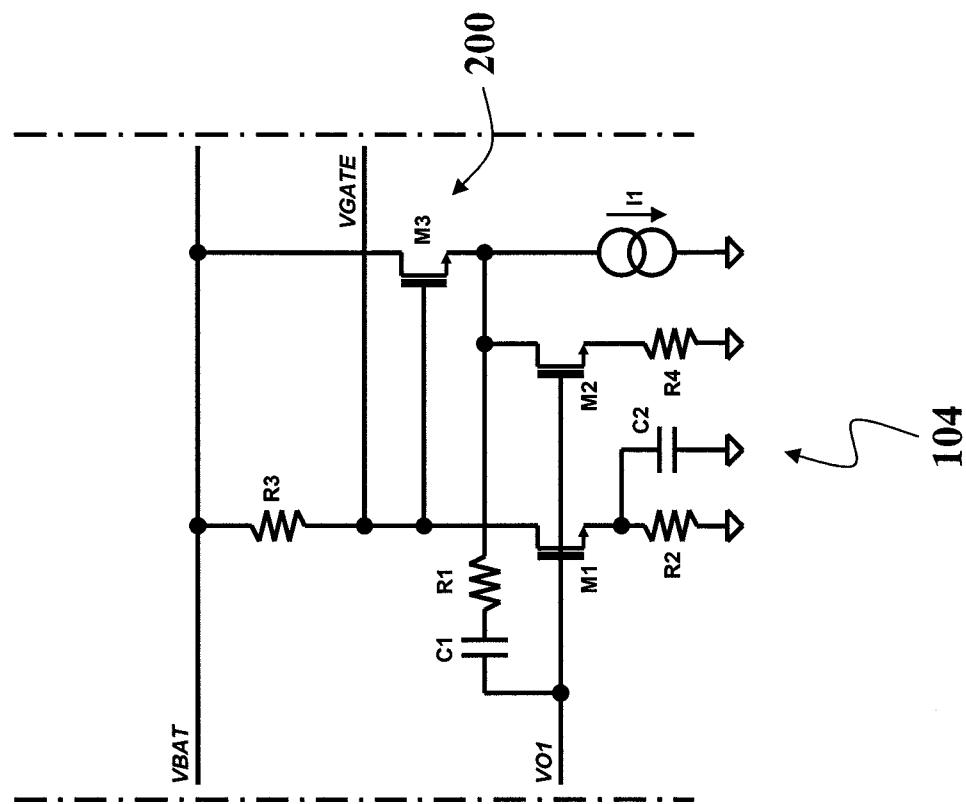

Così come illustrato nella figura 2, questo risultato può essere ottenuto inserendo un limitatore di corrente 200 nel cammino della corrente di carica  $I_{C1}$  che scorre attraverso la rete di compensazione in frequenza  $R1, C1$ . In questo modo, la rete di compensazione  $R1, C1$  funziona normalmente per piccoli segnali è di fatto scollegata per segnali elevati.

Durante un processo di transitorio di carico (segnale elevato) l'uscita dell'amplificatore differenziale (ossia il nodo  $V_{O1}$ ) è caricato soltanto dalla corrente in continua definita dal limitatore di corrente 200 e dalla capacità di ingresso dello stadio di guadagno 104 (il MOSFET  $M1$ , nella forma di attuazione esemplificativa qui considerata).

L'analisi sperimentale della risposta ai transitori di carico risultanti indica che, con la struttura della figura 2, il carico capacitivo più basso all'uscita dell'amplificatore differenziale 102 permette a  $V_{O1}$  di cambiare più rapidamente, mentre la corrente  $I_{C1}$  nella rete di compensazione, determinata dal limitatore di corrente 200, può essere regolata in modo da essere molto più bassa della corrente di bias minima della coppia differenziale.

Con la struttura della figura 2, il condensatore C1 è caricato da una corrente bassa, per cui la sua carica richiede un intervallo più lungo dell'intervallo di ricupero dopo un transitorio di carico. Come risultato, la rete di compensazione R1, C1 è infatti mantenuta inattiva mentre il regolatore si trova già nella condizione di errore di regolazione minimo (con un errore peraltro trascurabile sulla tensione  $V_{OUT}$  a causa dell'offset dell'amplificatore differenziale 102 causato dal carico di corrente su V01).

Qualunque potenziale problema di stabilità può essere tuttavia superato caricando più rapidamente C1 e portando la rete di compensazione R1, C1 in uno stato normale. Questo risultato può essere ottenuto utilizzando un regolatore di corrente adattativo in grado di tenere in conto il fatto che all'aumento della tensione V01 e della corrente di bias il nodo V01 può essere caricato con una corrente più elevata, accelerando così il processo di carica di C1 per cui il tempo di carica di C1 può essere effettivamente minimizzato conservando le prestazioni di transitorio di carico desiderate.

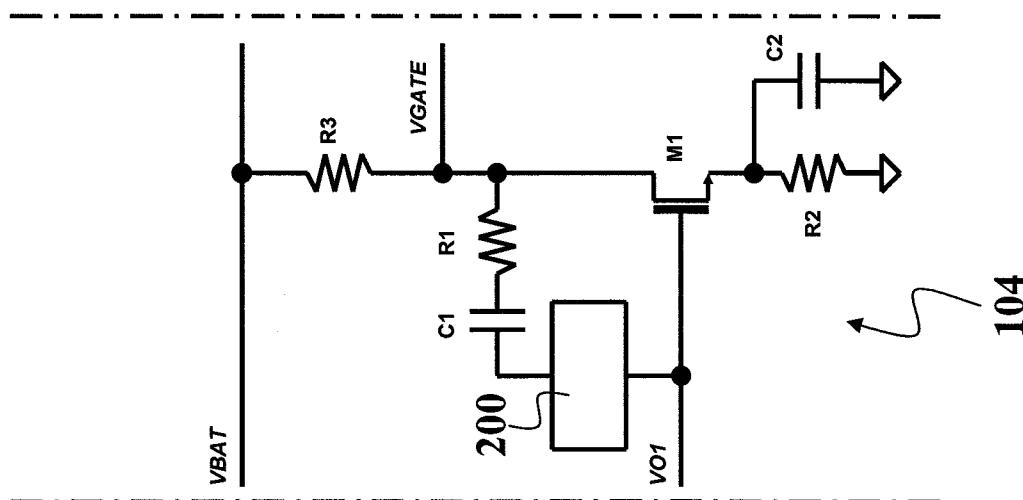

La figura 3 (dove elementi/componenti identici o equivalenti a quelli già descritti in relazione alle figure 1 e 2 sono indicati con gli stessi riferimenti che già appaiono in esse) è esemplificativo di una forma di attuazione di un tale limitatore di corrente adattativo. Essenzialmente, nella forma di attuazione della figura 3, un primo MOSFET M2 è accoppiato in una configurazione a gate comune con il MOSFET M1 dello stadio di guadagno 104 così da realizzare la funzione adattativa (rilevare l'aumento della tensione della corrente di bias su V01), mentre il MOSFET M3 funziona come buffer con una capacità

di corrente di uscita limitata che gradualmente "ripristina" la corrente di carico del condensatore C1 quando la tensione V01 e la corrente di bias aumentano, così come rilevato tramite il MOSFET M3 accelerando così il processo di carica di C1.

Fermo restando il principio dell'invenzione, i particolari di realizzazione e le forme di attuazione potranno essere variati anche in misura rilevante, rispetto a quanto qui illustrato a puro titolo di esempio non limitativo, senza per questo uscire dall'ambito di protezione della presente invenzione, così come definito dalle rivendicazioni annesse.

## RIVENDICAZIONI

**1.** Regolatore lineare di tipo low-dropout comprendente un amplificatore di errore (100) comprendente un amplificatore differenziale (102) ed uno stadio di guadagno (104) disposti in cascata ed aventi interposta fra loro una rete di compensazione di frequenza ( $R_1$ ,  $C_1$ ) attraversabile da una corrente di carica ( $I_{C1}$ ), il regolatore caratterizzato dal fatto che comprende un limitatore di corrente (200) inserito nel cammino di flusso della corrente di carica ( $I_{C1}$ ) di detta rete di compensazione ( $R_1$ ,  $C_1$ ).

**2.** Regolatore secondo la rivendicazione 1, comprendente detto limitatore di corrente (200) configurato per far sì che, durante un processo di transitorio sul carico sul regolatore, l'uscita di detto amplificatore differenziale (104) sia caricata da una corrente in continua definita dal limitatore di corrente (200) e dall'ingresso (M1) di detto stadio di guadagno (104).

**3.** Regolatore secondo una delle rivendicazioni 1 e 2, comprendente detto limitatore di corrente (200) sotto forma di un limitatore di corrente adattativo (200, M1, M2) per aumentare detta corrente di carica ( $I_{C1}$ ) di detta rete di compensazione ( $R_1$ ,  $C_1$ ) all'aumentare della tensione di uscita ( $V_{O1}$ ) di detto amplificatore differenziale (104).

**4.** Regolatore secondo la rivendicazione 3, in cui detto limitatore di corrente adattativo (200, M1, M2) comprende:

- un primo transistore (M2) per rilevare la tensione

di uscita (VO1) di detto amplificatore differenziale (104);

e

- un secondo transistore (M3) tampone accoppiato a detto primo transistore (M2) per aumentare detta corrente di carica ( $I_{C1}$ ) di detta rete di compensazione (R1, C1) quando la tensione di uscita (VO1) di detto amplificatore differenziale (104) cresce così come rilevato tramite detto primo transistore (M2).

**5.** Regolatore secondo la rivendicazione 4, in cui detto stadio di uscita (104) comprende un transistore di guadagno (M1) pilotato dall'uscita (VO1) di detto amplificatore differenziale (102) e detto primo transistore (M2) è accoppiato in una configurazione a gate comune con detto transistore di guadagno (M1) di detto stadio di guadagno (104).

**6.** Procedimento per migliorare la risposta ai transitori di carico di un regolatore lineare di tipo low-dropout comprendente un amplificatore di errore (100) comprendente un amplificatore differenziale (102) ed uno stadio di guadagno (104) collegati in cascata ed aventi fra loro interposta una rete di compensazione in frequenza (R1, C1) con un carico capacitivo (C1) in detta rete di compensazione in frequenza (R1, C1), il procedimento comprendendo l'aumentare lo slew rate dell'uscita (VO1) di detto amplificatore differenziale (102) eliminando detto carico capacitivo (C1) in detta rete di compensazione in frequenza (R1, C1) durante i transitori di carico di detto regolatore lineare di tipo low-dropout.

## CLAIMS

1. A low-dropout linear regulator including an error amplifier (100) including a cascaded arrangement of a differential amplifier (102) and a gain stage (104) having interposed therebetween a frequency compensation network (R1, C1) for a loading current ( $I_{C1}$ ) to flow therethrough, the regulator characterized in that it includes a current limiter (200) inserted the flowpath of said loading current ( $I_{C1}$ ) for said compensation network (R1, C1).

2. The regulator of Claim 1, including said current limiter (200) configured to cause the output of said differential amplifier (104) to be loaded during a load transient process on the regulator by a DC current defined by the current limiter (200) and by the input (M1) of said gain stage (104).

3. The regulator of either of Claims 1 or 2, including said current limiter (200) in the form of an adaptive current limiter (200, M1, M2) to increase said loading current ( $I_{C1}$ ) for said compensation network (R1, C1) as the output voltage (V01) of said differential amplifier (104) increases.

4. The regulator of Claim 3, wherein said adaptive current limiter (200, M1, M2) includes:

- a first transistor (M2) to sense the output voltage (V01) of said differential amplifier (104); and

- a second buffer transistor (M3) coupled to said first transistor (M2) to increase said loading current ( $I_{C1}$ ) for said compensation network (R1, C1) as the output

voltage (VO1) of said differential amplifier (104) increases as sensed via said first transistor (M2).

5. The regulator of Claim 4, wherein said gain stage (104) includes a gain transistor (M1) driven by the output (VO1) of said differential amplifier (102), and said first transistor (M2) is coupled in a common gate arrangement with said gain transistor (M1) of said gain stage (104).

6. A method of improving load transient response in a low-dropout linear regulator including an error amplifier (100) including a cascaded arrangement of a differential amplifier (102) and a gain stage (104) having interposed therebetween a frequency compensation network (R1, C1) with a capacitive load (C1) in said frequency compensation network (R1, C1), the method including increasing the slew rate of the output (VO1) of said differential amplifier (102) by dispensing with said capacitive load (C1) in said frequency compensation network (R1, C1) during load transients in said low-dropout linear regulator.

Fig. 1

2/2

Fig. 3

Fig. 2