(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4027434号

(P4027434)

(45) 発行日 平成19年12月26日(2007.12.26)

(24) 登録日 平成19年10月19日(2007.10.19)

(51) Int.C1.

F 1

HO3M 3/02 (2006.01)

HO3M 3/02

請求項の数 20 (全 11 頁)

|               |                              |

|---------------|------------------------------|

| (21) 出願番号     | 特願平11-500587                 |

| (86) (22) 出願日 | 平成10年5月26日(1998.5.26)        |

| (65) 公表番号     | 特表2002-502565(P2002-502565A) |

| (43) 公表日      | 平成14年1月22日(2002.1.22)        |

| (86) 國際出願番号   | PCT/SE1998/000990            |

| (87) 國際公開番号   | W01998/054840                |

| (87) 國際公開日    | 平成10年12月3日(1998.12.3)        |

| 審査請求日         | 平成17年5月17日(2005.5.17)        |

| (31) 優先権主張番号  | 9701986-3                    |

| (32) 優先日      | 平成9年5月27日(1997.5.27)         |

| (33) 優先権主張国   | スウェーデン(SE)                   |

|           |                                                                      |

|-----------|----------------------------------------------------------------------|

| (73) 特許権者 | テレフォンアクチーボラゲット エル エ<br>ム エリクソン<br>スウェーデン国エスー126 25 スト<br>ツクホルム(番地なし) |

| (74) 代理人  | 弁理士 浅村 譲                                                             |

| (74) 代理人  | 弁理士 浅村 肇                                                             |

| (74) 代理人  | 弁理士 林 銘三                                                             |

| (74) 代理人  | 弁理士 清水 邦明                                                            |

最終頁に続く

(54) 【発明の名称】シグマ・デルタ変調器内の周期雑音を低減するための装置並びに方法

## (57) 【特許請求の範囲】

## 【請求項 1】

周期雑音の低減を実行するシグマ・デルタ変調の方法であつて、

a) 第1の信号(209)の少なくとも第1の積分(200)を実行して、第1の積分信号を求め、前記第1の信号は出力信号(106)を予め定められた係数kと乗算しつつ変調器入力信号(103)を加算して形成し、

b) 第2の信号(211、411)の少なくとも第2の積分(201)を実行して、第2の積分信号(212、412)を求め、前記第2の信号は第1のディザイ生成器(216、215)からの第1の入力信号(218、417)に前記第1の積分信号(210)を加算することにより形成され、

c) 第3の信号(214、414)を量子化して、前記出力信号(106)を求め、前記第3の信号は第2のディザイ生成器(215、216)からの第2の入力信号(217、418)に前記第2の積分信号(212、412)を加算することにより形成される、方法において、

前記第1の入力信号(218、417)がそれ自体第1の周期にしたがって繰り返し、かつ前記第2の入力信号(217、418)がそれ自体第2の周期にしたがって繰り返し、前記第1の周期は前記第2の周期とはより異り、このうち、前記第1の入力信号(218)は前記第1の周期の特定ビットマップであり、かつ前記第2の入力信号(217)は前記第2の周期の擬似ランダム信号であることを特徴とする方法。

10

20

**【請求項 2】**

前記第1の入力信号(218)は前記第1の周期の1ビット離散時間シーケンスであり、前記第2の入力信号(217)の前記第2の周期に対して短く、かつ前記第2の入力信号(217)は前記第2の周期の1ビット時間離散シーケンスであることを特徴とする請求項1に記載の方法。

**【請求項 3】**

前記変調器入力信号(103)と前記第1の積分信号(210)Nビット時間離散信号であり、かつ前記出力信号(106)は1ビット時間離散信号であり、さらに、前記方法は、

前記第1の入力信号(218)を前記第1の積分信号(210)内の最上位ビットの一つに加算し、10

前記第2の入力信号(217)を前記第2の積分信号(212)内の最下位ビットに加算するステップを有することを特徴とする請求項2に記載の方法。

**【請求項 4】**

前記第1の入力信号(218)の前記第1の周期の周波数成分がシグマ・デルタ変調器の周波数範囲の外側にあり、かつ前記第2の入力信号(217)の前記第2の周期はシーケンスがそれ自体、人の耳に聞こえない周波数で繰り返すように十分長いことを特徴とする請求項2に記載の方法。

**【請求項 5】**

前記シグマ・デルタ変調器の周波数範囲は人の耳に聞こえ、かつ前記第1の入力信号(218)の前記第1の周期はそれ自体、人の耳に聞こえない周波数で繰り返すことを特徴とする請求項4に記載の方法。20

**【請求項 6】**

前記第1の入力信号(417)は前記第1の周期の1ビット時間離散シーケンスであり、かつ第2の入力信号(418)は、前記第1の入力信号の前記第1の周期に対して短い、前記第2の周期の1ビット時間離散シーケンスであることを特徴とする請求項1に記載の方法。

**【請求項 7】**

前記変調器入力信号(103)と前記第1の積分信号(210)はNビット時間離散信号であり、かつ前記出力信号(106)は1ビット時間離散信号であり、かつ前記方法は、さらに30

前記第1の入力信号(417)を前記第1の積分信号(210)内の最下位ビットに加算し、

前記第2の入力信号(418)を前記第2の積分信号(212)内の最上位ビットの一つに加算する、ことを特徴とする請求項6に記載の方法。

**【請求項 8】**

前記第1の入力信号(417)の前記第1の周期はシーケンスがそれ自体、人の耳に聞こえない周波数で繰り返すように十分長く、

前記第2の入力信号(418)の前記第2の周期の周波数成分は前記シグマ・デルタ変調器の周波数範囲の外側にあることを特徴とする請求項6に記載の方法。40

**【請求項 9】**

前記シグマ・デルタ変調器の周波数範囲は人の耳に聞こえ、かつ前記第2入力信号(417)の前記第2の周期はそれ自体、人の耳に聞こえない周波数で繰り返すことを特徴とする請求項8に記載の方法。

**【請求項 10】**

Nビット時間離散信号(101)を、前記時間離散信号(101)に対応しかつ低減された周期雑音を有するアナログ信号(108)に、ディジタル／アナログ変換する方法に含まれるシグマ・デルタ変調の方法であって、

特定サンプリング速度で前記Nビット時間離散信号(101)の補間フィルタリング(102)を実行して、一定のより高いサンプリング速度の時間離散信号(103)を求め、50

前記より高いサンプリング速度で前記時間離散信号(103)の前記シグマ・デルタ変調(104)を実行して、一定数の強度レベルを有する出力信号(106)を求め、前記出力信号(106)の低域フィルタリング(107)を実行して、前記Nビット時間離散信号(101)に対応の前記アナログ信号(108)を求める、ステップを有することを特徴とする請求項1に記載の方法。

【請求項11】

Nビット時間離散信号(101)を、前記時間離散信号(101)に対応しかつ低減された周期雑音を有するアナログ信号(108)に、ディジタル／アナログ変換する方法に含まれるシグマ・デルタ変調の方法であって、

特定サンプリング速度でNビット時間離散信号(101)の補間フィルタリング(102)を実行して、一定のより高いサンプリング速度の時間離散信号(103)を求め、

前記より高いサンプリング速度で前記時間離散信号(103)のシグマ・デルタ変調(104)を実行して、一定数の強度レベルを有する出力信号(106)を求め、

前記出力信号(106)の低域フィルタリング(107)を実行して、前記Nビット時間離散信号(101)に対応の前記アナログ信号(108)を求める、ステップを有することを特徴とする請求項1に記載の方法。

【請求項12】

シグマ・デルタ変調用の装置であって、

a) 第1の信号(209)の積分をして大の積分信号(210)を得るために少なくとも一つの第1の積分器(200)を有し、前記第1の信号は出力信号(106)と予め定められた係数kを乗算し、かつ変調器入力信号(103)を加算して形成し、

b) 第2の信号(211、411)の積分をして第の積分信号(212、412)を得るために少なくとも一つの第2の積分器(201)を有し、前記第2の信号は前記第1の積分信号を第1の入力信号(218、417)に加算して形成し、かつ

c) 第3の信号(214、414)を量子化して前記出力信号を得るために量子化器(202)を有し、前記第3の信号は前記第2の積分信号を第2の入力信号(217、418)に加算して形成する装置において、

第1のディザー生成器(216、215)を前記第1の入力信号(218、417)を生成するように配置し、前記第1の入力信号がそれ自体第1の周期にしたがって繰り返すようにし、かつ第2のディザー生成器(215、216)を前記第2の入力信号(217、418)を生成するように配置し、前記第2の入力信号がそれ自体第2の周期にしたがって繰り返すようにし、前記第1の周期は前記第2の周期とはより異なり、このうち、

前記第1のディザー生成器(216)は前記第1の周期の特定ビットマップを含み、さらに、前記第2のディザー生成器(215)は前記第2の周期の擬似ランダム信号を含むか

又は

前記第1のディザー生成器(215)は前記第1の周期の擬似ランダム信号を含み、さらに、前記第2のディザー生成器(216)は前記第2の周期の特定ビットマップを含む、ことを特徴とする装置。

【請求項13】

前記第1のディザー生成器(216)はメモリ装置を含み、さらに、前記第2のディザー生成器(215)は最大長シフトレジスタにより構成することを特徴とする請求項12に記載の装置。

【請求項14】

前記第1のディザー生成器(216)はシフトレジスタにより構成し、かつ前記第2のディザー生成器(215)は最大長シフトレジスタにより構成することを特徴とする請求項12に記載の装置。

【請求項15】

さらに、予め定められた係数1が乗算された前記出力信号(106)を前記第1の積分信号(210)に加算するための第1の加算器(204)と、

予め定められた係数が乗算された前記出力信号(106)を前記第2の積分信号(212) 50

)に加算するための第2の加算器(205)とを含むことを特徴とする請求項13または14に記載の装置。

**【請求項16】**

前記第1のディザイナー生成器(215)は最大長シフトレジスタにより構成し、かつ前記第2のディザイナー生成器(216)はメモリ装置を含むことを特徴とする請求項12に記載の装置。

**【請求項17】**

前記第1のディザイナー生成器(215)は最大長シフトレジスタにより構成し、かつ前記第2のディザイナー生成器(216)はシフトレジスタを含むことを特徴とする請求項12に記載の装置。

10

**【請求項18】**

さらに、予め定められた係数1が乗算された前記出力信号(106)を前記第1の積分信号(210)に加算するための第1の加算器(204)と、

予め定められた係数mが乗算された前記出力信号(106)を前記第2の積分信号(212)に加算するための第2の加算器(205)を含むことを特徴とする請求項16または17に記載の装置。

**【請求項19】**

Nビット時間離散信号(101)を、前記時間離散信号(101)に対応しかつ低減された周期雑音を有するアナログ信号(108)に、デジタル／アナログ変換する装置に含まれるシグマ・デルタ変調のための装置において、前記デジタル／アナログ変換(101)用の前記装置が、

20

一定サンプリング速度で前記Nビット時間離散信号(101)のフィルタリングをして一定のより高いサンプリング速度の時間離散信号(103)を得る補間フィルタ(102)と、

前記より高いサンプリング速度で前記時間離散信号(103)を変調して一定数の強度レベルを有する出力信号(106)を得る前記シグマ・デルタ変調(104)用の前記装置と、

前記出力信号(106)をフィルタリングして前記Nビット時間離散信号(101)に対応の前記アナログ信号(108)を得る前記出力信号(106)のフィルタリング用の低減フィルタ(107)を有することを特徴とする請求項12に記載のシグマ・デルタ変調用の装置。

30

**【請求項20】**

Nビット時間離散信号(101)を、前記時間離散信号(101)に対応しかつ低減された周期雑音を有するアナログ信号(108)に、デジタル／アナログ変換する装置に含まれるシグマ・デルタ変調のための装置において、前記デジタル／アナログ変換(101)用の前記装置が、

一定サンプリング速度で前記Nビット時間離散信号(101)のフィルタリングをして一定のより高いサンプリング速度の時間離散信号(103)を得る補間フィルタ(102)と、

前記より高いサンプリング速度で前記時間離散信号(103)を変調して一定数の強度レベルを有する出力信号(106)を得る前記シグマ・デルタ変調(104)用の前記装置と、

40

前記出力信号(106)をフィルタリングして前記Nビット時間離散信号(101)に対応の前記アナログ信号(108)を得る前記出力信号(106)のフィルタリング用の低減フィルタ(107)を有することを特徴とする請求項12に記載のシグマ・デルタ変調用の装置。

**【発明の詳細な説明】**

**技術分野**

本発明は周期雑音を低減したシグマ・デルタ変調の方法に関する。

**関連技術の説明**

50

その中でアナログ／デジタルまたはデジタル／アナログ変換が実行されている多くのオーディオ装置、例えば移動電話またはCDプレーヤでは、シグマ・デルタ変調器がアナログ／デジタルまたはデジタル／アナログ変換器で使用されている。

従来技術に基づくシグマ・デルタ変調器は多数の積分器、多数の増幅器および1つの量子化器を含む。これらはシグマ・デルタ変調器に特徴な方法で構成されている。シグマ・デルタ変調器の構成を以下に説明する。

シグマ・デルタ変調器ではその入力信号が低いか、一定であるかまたはゆっくりと変化しているとき、いわゆる周期雑音またはアイドリング雑音が生じる。周期雑音の強度は比較的小さいが人の耳には十分に聞こえる。この雑音は、従って聞こえないレベルまで低減されなければならない。

E P 0 7 0 9 9 6 9 A 2において、ディザー(Dither)信号により周期雑音を低減したシグマ・デルタ変調器が開示されている。ディザー信号はランダム信号であり、例えば疑似雑音コード(PNコード)である。このディザー信号がシグマ・デルタ変調器の1つまたは複数の場所で加算される。シグマ・デルタ変調器内の何処でディザー信号が加算されるかによって、この加算に先だって信号には特定のフィルタでフィルタ処理がなされる。

PNコードの好適な長さは、このPNコードの周期がシグマ・デルタ変調器で取り扱われる最低周波数の周期よりも十分に長いものである。PNコードは少なくとも21ビット長でなければならない。ディザー信号の整流されたAC電力はシグマ・デルタ変調器の次数に依存する。

この解決方法の1つの欠点は、ディザー信号を加算する場所を何処に選択されるかによって1つまたは複数のフィルターが必要とされることである。

シグマ・デルタ変調器内の周期雑音を低減するための別の共通の解決方法は、ディザー信号を積分器の1つの中に加算することである。ディザー信号はフィルタ処理無しで加算される。

この解決方法はまたシグマ・デルタ変調器の性能が低下するという欠点を有する。

シグマ・デルタ変調器内の信号／雑音比の低下は、シグマ・デルタ変調器の複雑さが増されなければならないことを意味する。これは希望するレベルの性能を維持するためにシグマ・デルタ変調器内で非常に多数の積分器が使用されなければならないことを意味する。シグマ・デルタ変調器がD/A変換器の中に含まれる場合、信号／雑音比の低下に対して別の解決方法がある。D/A変換器内の補間フィルタのオーバー・サンプリング速度を増加させたり、またはシグマ・デルタ変調器の出力部に構成されている低域濾波フィルタの複雑さを増したりすることが可能である。

しかしながら、上記の3つの解決方法は電力消費の増加やシグマ・デルタ変調器の複雑さにつながり、これは移動電話の様な無線通信装置に対しては好ましくない。

#### 発明の要約

本発明の目的はシグマ・デルタ変調器内の周期雑音(アイドル・トーン)を低減する問題を解決することである。

本発明で解決される別の問題は周期雑音を低減する際に、シグマ・デルタ変調器から信号を出力するための信号／雑音比をシグマ・デルタ変調器を複雑にすることなく維持することである。

本発明で解決される更に別の問題は周期雑音を低減する際に、シグマ・デルタ変調器に関する本発明の装置並びに本発明の方法がD/A変換器の中に含まれる場合、D/A変換器から信号を出力するための信号／雑音比をD/A変換器を複雑にすることなく維持することである。

従って本発明の1つの目的は、変調出力信号内の周期雑音が低減されたシグマ・デルタ変調器に関する装置並びに方法を提供することである。

別の目的は、周期雑音を低減する際に、変調処理を実行するシグマ・デルタ変調器の複雑さを増すことなくシグマ・デルタ変調器の出力信号の良好な信号／雑音比を維持することである。

上記の問題は本発明に基づき、シグマ・デルタ変調器に2つの異なる信号を追加すること

10

20

30

40

50

により解決されている。第一信号は比較的短い周期を有する。前記第一信号はシグマ・デルタ変調器の最上位ビットの1つに加算される。第二信号は前記第一信号に比較して長い周期を有する。第二信号はシグマ・デルタ変調器内に含まれる積分器の1つの最下位ビットに加算される。

本発明の装置並びに本発明の方法の1つの長所は、周期雑音の低減がシグマ・デルタ変調器からの出力信号の信号／雑音比の低下を引き起こさずに実行されることである。

本発明の別の長所は、周期雑音を低減する際に複雑さが低く保たれているので、比較的消費電力の小さなシグマ・デルタ変調器が得られる点である。

本発明を提出された実施例に基づき、添付図を参照して更に詳細に説明する。

#### 【図面の簡単な説明】

10

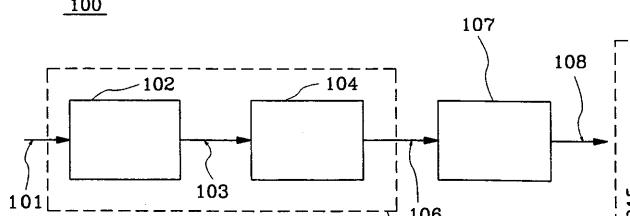

図1はシグマ・デルタ変調器を含むD/A変換器のブロック図。

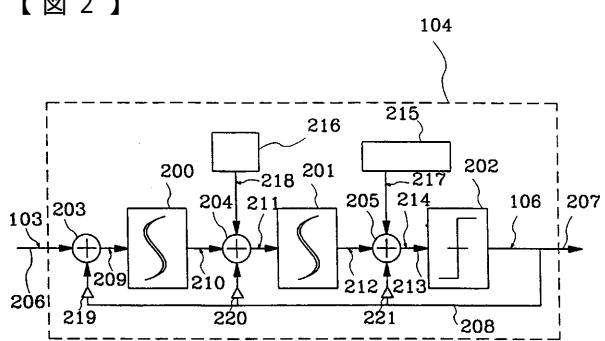

図2は本発明の装置並びに本発明の方法の1つの実施例を表すシグマ・デルタ変調器のブロック図。

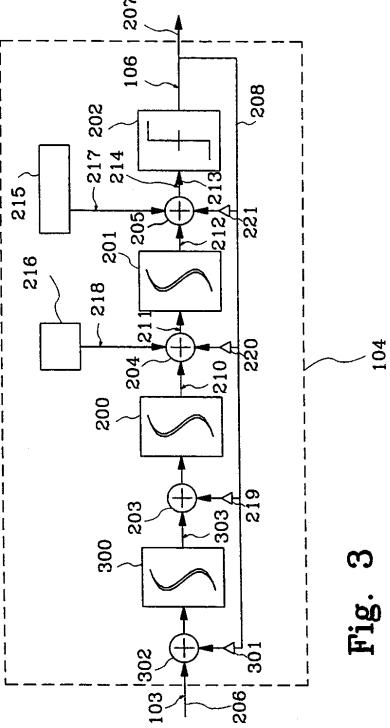

図3は本発明の装置並びに本発明の方法の別の実施例を表すシグマ・デルタ変調器のブロック図。

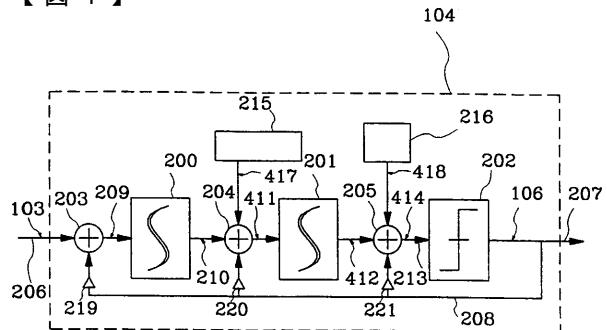

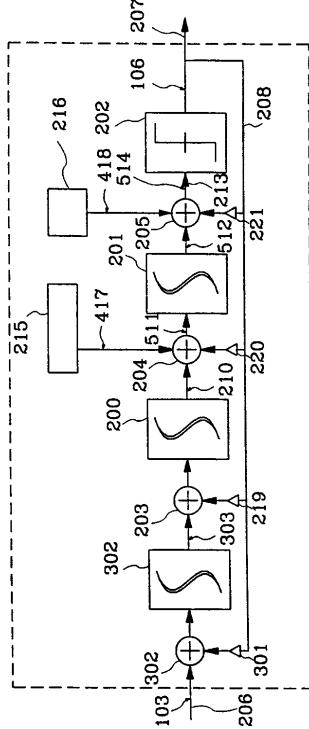

図4は本発明の装置並びに本発明の方法の更に別の実施例を表すシグマ・デルタ変調器のブロック図。

図5は本発明の装置並びに本発明の方法の更に別の実施例を表すシグマ・デルタ変調器のブロック図。

#### 実施例の詳細な説明

20

図1は従来技術に基づくD/A変換器100のブロック図である。D/A変換器100は離散時間補間フィルタ102を含み、多数のNビットを含む離散時間信号101を受信するように構成されている。例えば、D/A変換器100がGSM移動電話の中に構成されている場合、離散時間信号101はデジタル13ビット信号である。離散時間補間フィルタ102は受信された離散時間信号101のサンプリング速度を増して、より高いサンプリング速度を有する新たな離散時間信号103が得られるようにしている。このサンプリング速度の増加は、D/A変換器100から受信されるアナログ出力信号108内でより良い信号／雑音比を得るために実施される。高い方のサンプリング速度と低い方のサンプリング速度との間の比率を此処ではオーバー・サンプリング比率(OSR)と呼ぶ。新たな離散時間信号103はシグマ・デルタ変調器104に供給される。複数の積分器と量子化器とを含むシグマ・デルタ変調器104は、出力信号106を生成するように構成されている。出力信号106は事前に決定された数の強度レベルを仮定できる。前記出力信号106はしばしば2つの異なるレベルのみの1ビット信号である。この様な場合Nビットで表現された値から、2つの異なる強度値と仮定できる複数のサンプルへの変換が実行される。離散時間信号106は低域濾波フィルタ107に供給され、これは離散時間1ビット信号106を異なる強度値の間で平均化し、この方法でアナログ信号108を得るように構成されている。

A/D変換器は原理的に上述とは反対の方法で機能する。1つの違いはD/A変換器100が主としてデジタル・ハードウェア105で実現されるのに対し、A/D変換器は主としてアナログ構成要素で実現されている点である。

40

図2は発明の装置および発明の方法の1つの実施例を表すシグマ・デルタ変調器のブロック図である。シグマ・デルタ変調器104は前記シグマ・デルタ変調器の入力206に発生する離散時間信号103を受信し、出力信号106をシグマ・デルタ変調器の出力207として生成するように構成されている。出力信号106は離散時間信号103に依存する。シグマ・デルタ変調器104は2つの積分器200, 201、1つの量子化器202、3つの加算器203, 204, 205、第1ディザイナー信号218を生成するように意図された1つの第1ディザイナー生成器216そして第2ディザイナー信号217を生成するように意図された1つの第2ディザイナー生成器215を含む。

第1ディザイナー生成器216において、これは第1ディザイナー信号218が格納される、例えばメモリまたはシフト・レジスタであっても構わない。第1ディザイナー信号218は事前に

50

定義された強度の比較的短い周期を有する 1 ビット・シーケンスである。この比較的短い周期とは第 1 ディザー信号 218 が D/A 変換器 100 で意図されている周波数範囲のどの周波数成分をも含まないことを意味している。例えば、人の耳を意図しているオーディオ装置において、この周波数範囲は人の耳で知覚される周波数に対応する、すなわちほぼ 0 - 20 kHz に等しい周波数範囲である。第 1 ディザー信号の強度および周期をどのように選択するかを以下に説明する。

例えば最大長シフトレジスタである第 2 ディザー生成器 215 から、第 2 ディザー信号 217 が長周期、低強度で白色雑音に類似した統計的属性を具備して生成される。長さおよび強度をどのように選択するかを以下に説明する。第 2 ディザー信号 217 は 1 ビット・シーケンスであり、これは長さ 22 の最大長シフトレジスタで 4 秒より長い周期で生成された場合、白色雑音に類似した統計的属性が得られる。4 秒の周期は此処では顧客的長い周期とみなされる。このディザー信号は一義的に、第 1 ディザー信号 218 に依存してシグマ・デルタ変調器で意図されている周波数範囲内のトーンを有する出力信号を、シグマ・デルタ変調器が発生させないように意図するものである。

加算器 203 は離散時間信号 103 を出力信号 106 に加算するように構成されており、この出力信号 106 はフィードバック接続 208 により増幅器 219 を通してフィードバックされて、第 1 和信号 209 が得られる。増幅器 219 の増幅係数  $k$  は当業分野で知られている方法で選択される。 $k$  が  $k < 0$  として選択される場合、前記離散時間信号 103 から前記出力信号の引き算が実行される。前記第 1 和信号 209 は積分器 200 の中に積分されて、第 1 積分信号 210 が得られる。加算器 204 は前記第 1 積分信号 210 を出力信号 106 に加算するように構成されており、この出力信号 106 は増幅器 220 を通して先に説明したのと同じ方法でフィードバックされている。第 1 部分和がこの加算で得られる。加算器 204 は第 1 ディザー信号 218 を第一部分和の最上位ビットの 1 つに加算するように構成されている。この加算器の中で実行される加算はもちろん反対の順序でも実施できる。これにより第 2 和信号 211 が得られる。第 2 和信号 211 は積分器 201 の中に積分されて、第 2 積分信号 212 が得られる。加算器 205 は第 2 積分信号を、増幅器 221 にフィードバックされた出力信号 106 と、第 2 ディザー信号 218 とに加算するように構成されており、これにより第 3 和信号 214 が得られる。第 2 ディザー信号 218 は最下位ビットの 1 つに加算される。第 3 和信号は、出力信号 106 を生成するように構成されている量子化器 202 の入力 213 として発生する。出力信号 106 は 2 つのレベルの信号と仮定できる。

出力信号 106 は、それぞれの倍率係数  $k$ ,  $l$ ,  $m$  を具備した 3 つの増幅器 219, 220, 221 を通してフィードバックされる。倍率係数  $k$ ,  $l$ ,  $m$  は異なる方法で定められるはずである。しかしながら一般的に、雑音と信号に関する伝達関数の分析が行われなければならない。前記倍率係数をどのように決定するかは当業者には以前から知られている。

第 1 ディザー信号 218 は事前に決定されたスペクトル属性を有する 1 ビット信号である。第 1 ディザー信号は受信信号 101 の予め定められたサンプリング周波数  $f_s$  および決定された O S R ( オーバー・サンプリング比 ) に対して、D/A 変換器 100 に対して考えられている範囲  $f_B$  、これは例えば移動電話の基本帯域範囲内の周波数成分を含むべきではない。上記を満足させるために、第 1 ディザー信号 218 の長さは D/A 変換器に対して意図されている周波数範囲の最も高い周波数  $f_{BH}$  の周期よりも好適に短くなければならない。これは第 2 ディザー信号 217 が  $(1/f_{BH}) \times f_s \times O S R$  ビットよりも短ビットシーケンスで選択されると実現できる。人間の耳は 20 kHz 間でのトーンを知覚できるので、これが例えば移動電話機内に構成された場合、D/A 変換器の最高周波数を与える。例えば、サンプリング速度  $f_s = 8000 \text{ Hz}$  で O S R = 64 を使用すると、第 1 ディザー信号 218 が人の可聴周波数範囲内の周波数成分を含まないことという要求は、第 1 ディザー信号が 26 ビットよりも短く選択されると満たされる。これは上記の値を先に述べた式に代入して得られる： $(1/20000) \times 8000 \times 64 = 26$  ビット。第 1 ディザー信号の強度は好適に、フィードバックされた出力信号の強度よりも 4 - 3

10

20

30

40

50

2倍小さく選択される。第1ディザー信号強度の選択は、シグマ・デルタ変調器および第1ディザー信号が加算されるビットの構造に依存する。第1ディザー信号の強度はシグマ・デルタ変調器の構造が決定された後にシミュレートされる。

第2ディザー信号217は、白色雑音に相当する統計的属性を有するビットシーケンスである。これは例えば最大長シフト・レジスタで生成された疑似雑音(PN)コードである。このディザー信号の周期は好適に数秒の長さが必要である。例えば4秒の周期が望ましく、サンプリング速度 $f_s$ が8000Hzに等しくまたOSRが64に等しい場合、ビット・シーケンス、その周期は2048000ビット( $4 \times 8000 \times 64 = 2048000$ )よりも長くなければならない。このシーケンスは長さ22の最大長シフトレジスタを用いて得られるが、これは( $2^{22} - 1$ ) = 4194303の周期を与える。ある長さの最大長シフトレジスタの設計方法は当業者には良く知られている。10

第1ディザー信号の強度は、制御可能な強度を具備したディザー生成器216をシグマ・デルタ変調器内の加算器に接続することで決定できる。

この強度は出力信号108の中に周期雑音が見られなくなるまで増加される。これは種々の方法でチェック可能であり、例えば信号の周波数成分を蓄積するスペクトル分析器を、出力信号108を蓄積するように接続することでチェック出来る。

本実施例において、第1ディザー信号218を同様に加算器205に接続し、また第2ディザー信号217を加算器203, 204に接続することも可能である。上記と同じ結果が得られるであろう。

図3は本発明の装置並びに本発明の方法の第2の実施例を表すシグマ・デルタ変調器のブロック図である。図2に関連して説明した実施例と図3に示すものとの違いは、図3に示す実施例は追加の積分器300、従って3次シグマ・デルタ変調器と呼ばれる、と1つの加算器302と1つの增幅器301とを含むことである。20

入力信号103が、增幅器301で増幅された出力信号106と加算器302の中で加算され、これにより和信号が得られる。この和信号は積分器300の中で積分されて積分信号303を生成する。図2に関連して説明された入力信号103の代わりに、加算器203は入力信号303を得る。その他の全てに関してシグマ・デルタ変調器は図2に関連して先に説明したように機能する。

先に説明した2つの実施例の中で使用されている、ディザー信号217とディザー信号218はもちろん完全に同一の信号では無いが、先に説明した方法で調整されている。30

この実施例において第1ディザー信号218を同様に加算器203, 205の1つに接続し、第2ディザー信号217を加算器203, 204, 302の1つに接続することも可能である。上記と同じ結果が得られるであろう。

図4は本発明の装置および本発明の方法の別の実施例を表すシグマ・デルタ変調器のブロック図である。この実施例と図2に関連して説明したものとの間の違いは、ディザー生成器216, 216の位置が変化していることである。ディザー生成器215の1つで生成された第一ディザー信号417は第一積分信号210と増幅器220を通してフィードバックされた出力信号106に加算器204の中で、図2に関連してディザー信号217について記述したのと同様な方法で加算され、第2和信号411が得られる。和信号411は積分器201で積分され、これにより第2積分信号412が得られる。第2ディザー信号418が第2積分信号412と、増幅器221を通してフィードバックされた出力信号106に加算され、これにより第3和信号414が得られる。前記加算は図2に関連してディザー信号218について記述したのと同一の方法で実施される。出力信号106は出力106部に、先に記述したのと同様な方法で、第3和信号414を量子化202することにより得られる。40

図5は本発明のシグマ・デルタ変調器の更に別の実施例のブロック図である。図3に関連して説明したものとの間の違いは、ディザー生成器216, 215の位置が変化していることである。ディザー生成器215の1つで生成された第一ディザー信号417は第一積分信号210と増幅器220を通してフィードバックされた出力信号106に加算器204の中で、図3に関連してディザー信号217について記述したのと同様な方法で加算さ50

れ、第2和信号511が得られる。和信号511は積分器201で積分され、これにより第2積分信号512が得られる。第2ディザー信号418が第2積分信号512と、増幅器221を通してフィードバックされた出力信号106に加算され、これにより第3和信号514が得られる。前記加算は図3に関連してディザー信号218について記述したのと同一の方法で実施される。出力信号106は出力106部に、先に記述したのと同様な方法で、第3和信号414を量子化202することにより得られる。

本発明はもちろん先に記述され図に示されたものに制限されるものではなく、請求の範囲内で変更が可能である。

【 図 1 】

100

Fig. 1

【 図 2 】

Fig. 2

【 図 3 】

3

Ei**b**

【図4】

Fig. 4

【図5】

Fig. 5

---

フロントページの続き

(72)発明者 フラナゲン、マツ、オロフ

アメリカ合衆国 カリフォルニア、マウンテン ピュー、カルダロン アベニュー 151、ナン

バー 272

(72)発明者 フレムロット、ペル、ヘンリック

スウェーデン国 ルンド、カムナルスベーゲン 13、ディ 217

審査官 渡辺 未央子

(56)参考文献 特開平05-160736(JP,A)

特開平05-335964(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03M 3/02