(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6529712号

(P6529712)

(45) 発行日 令和1年6月12日(2019.6.12)

(24) 登録日 令和1年5月24日(2019.5.24)

(51) Int.Cl.

G01S 7/28 (2006.01)

G01S 13/28 (2006.01)

F 1

G01S 7/28 210

G01S 13/28 200

## 請求項の数 5 外国語出願 (全 13 頁)

(21) 出願番号 特願2013-184656 (P2013-184656)

(22) 出願日 平成25年9月6日 (2013.9.6)

(65) 公開番号 特開2014-95689 (P2014-95689A)

(43) 公開日 平成26年5月22日 (2014.5.22)

審査請求日 平成28年9月6日 (2016.9.6)

(31) 優先権主張番号 61/698, 903

(32) 優先日 平成24年9月10日 (2012.9.10)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 13/625, 767

(32) 優先日 平成24年9月24日 (2012.9.24)

(33) 優先権主張国 米国(US)

(73) 特許権者 500575824

ハネウェル・インターナショナル・インコ

ーポレーテッド

Honeywell Internati

onal Inc.

アメリカ合衆国ニュージャージー州O 7 9

5 0, モリス・プレインズ, ティバー・ロ

ード 1 1 5

1 1 5 Tabor Road Morr

is Plains NJ 07950

United States of Am

erica

(74) 代理人 100140109

弁理士 小野 新次郎

最終頁に続く

(54) 【発明の名称】 FM CWとFMパルス圧縮とを組み合わせるレーダー・システム及び方法

## (57) 【特許請求の範囲】

## 【請求項 1】

レーダーシステムであって、

アンテナと、

送信機と、

受信機と、

サーキュレータであって、

第1の信号を前記送信機から受信し、

前記第1の信号を前記アンテナに出力し、

前記アンテナから第2の信号を受信し、

前記第2の信号を前記受信機に出力する

サーキュレータと、

前記アンテナに前記送信機により提供される第1の信号のタイプ間の切り換えを行うた

めに、クロック信号及び前記レーダーシステム用の制御信号を生成するように構成された

コントローラと、

シンセサイザであって、

前記レーダーシステムの第1の信号経路に配置され、フラクショナルNシンセサイ

ザを備えた位相ロックループ(PLL)と、

前記レーダーシステムの第2の信号経路に前記第1の信号経路と並列に配置され、

パルス・ツー・パルス周波数ホッピングを提供するダイレクトデジタルシンセサイザ(D

10

20

D S ) と

を備えたシンセサイザと、

処理された第 2 の信号に包含されるターゲットの存否を判断するように構成された 1 又はそれ以上のプロセッサと、

前記ターゲットの存否の判断に基づいてプレゼンテーションを出力するように構成された出力デバイスと、

を備え、

前記第 1 の信号は、第 1 のモードにおいて生成される信号及び第 2 のモードにおいて生成される信号の中から選択され、

前記アンテナは、前記第 1 の信号を送信するよう構成され、

10

前記第 2 の信号は、前記送信された第 1 の信号に基づく反射リターン信号を包含し、

前記シンセサイザと前記送信機は、前記クロック信号及び前記制御信号に基づいて、前記第 1 のモード又は第 2 のモードにおいて前記第 1 の信号のタイプを生成するように構成され、

前記第 1 のモードにおける前記第 1 の信号のタイプは、周波数変調連続波 ( F M C W ) 信号又はストレッチパルス圧縮信号であり、前記第 2 のモードにおける前記第 1 の信号のタイプは、線形周波数変調 ( L F M ) パルス圧縮信号又は非線形周波数変調 ( N L F M ) パルス圧縮信号であり、

前記 レーダーシステム は、前記シンセサイザからの遅延信号に基づくとともに、前記クロック信号及び前記制御信号に基いて、前記第 1 のモードによって前記第 2 の信号を処理する、

20

ことを特徴とするシステム。

#### 【請求項 2】

前記送信機が、

可変減衰器と、

複数のアンプと、

変調器と、

低域フィルタと

を含み、

前記可変減衰器及び変調器が、生成された制御信号によって作動することを特徴とする請求項 1 に記載のシステム。

30

#### 【請求項 3】

前記シンセサイザが、第 1 のシンセサイザ ( 1 6 0 、 1 6 0 - 1 ) を有し、前記受信機が、

F M C W およびストレッチパルス圧縮信号を前処理するように構成された第 1 の受信機 ( 1 4 4 ) と、

L F M および N L F M パルス圧縮信号を前処理するように構成された第 2 の受信機 ( 1 4 6 ) と、

を備え、

前記システムが、更に、

40

前記第 2 のモードにおいて、第 1 の出力及び前記第 2 の受信機によって使用するための第 2 の出力を生成するように構成された第 2 のシンセサイザ ( 1 5 2 ) と、

ミキサ ( 1 4 0 ) と、

を備え、

前記ミキサ ( 1 4 0 ) が、

前記第 1 のモードにおいて、前記第 1 のシンセサイザからの遅延信号を前記第 2 の信号と混合し、混合された信号を前記第 1 の受信機 ( 1 4 4 ) に出力し、

前記第 2 のモードにおいて、前記第 2 のシンセサイザによって生成された前記第 1 の出力を前記第 2 の信号と混合する

ように構成され、

50

前記第2の受信機が、前記第2の出力を受信し、前記第1の出力と混合された第2の信号に関しI/Q復調を行うことを特徴とする、請求項1に記載のシステム。

【請求項4】

前記PLLは、更に、電圧制御発振器(VCO)を備え、

前記DDS(326)のフィルタリングされた出力は、第1の混合信号を生成するためにクロック信号と混合され、

前記PLLは、前記クロック信号及び前記制御信号に基づいてPLL出力信号を生成し、前記制御信号に基づいて調整されたパワー及び周波数となった後、前記PLL出力信号は、第2の混合信号を生成するために第1の混合信号と混合され、

10

前記第2の混合信号は、第3の混合信号を生成するために、フィルタリング(364)され、増幅(366)され、及び、パワー調整(342)がなされたPLL出力信号と混合され、

前記第3の混合信号は、増幅(372)され、フィルタリング(374)された後に前記送信機(380)に送信される、

ことを特徴とする請求項1に記載のシステム。

【請求項5】

レーダーシステムのコントローラで、前記レーダーシステムのアンテナにミキサを介して送信機により提供される信号のタイプ間の切り換えを行うために、クロック信号及び前記レーダーシステム用の制御信号を生成するステップと、

20

前記レーダーシステムのシンセサイザで、前記クロック信号及び前記制御信号に基いて、第1のモード又は第2のモードにおいて、信号を生成するステップと

前記送信機で、前記シンセサイザによって生成された前記信号を受信し、前記第1のモード又は前記第2のモードにおいて生成された前記信号に基づいて、レーダ送信信号を前記サーチュレータを介して前記アンテナに送信するステップと、

前記レーダーシステムの前記アンテナで、前記レーダ送信信号を送信するとともに、前記送信されたレーダ送信信号に基づいて反射リターン信号を受信するステップと、

前記レーダーシステムの受信機で、前記アンテナから前記反射リターン信号を受信するステップと、

前記レーダーシステムの1またはそれ以上のプロセッサで、前記クロック信号及び前記制御信号に基いて前記第1のモード又は第2のモードによって、受信された反射リターン信号を前処理し、前記前処理された反射リターン信号に含まれたターゲットの存否を判断するステップと、

30

前記レーダーシステムの出力デバイスで、前記ターゲットの存否の判断に基づいてプレゼンテーションを出力するステップと

を備え、

前記レーダーシステムの前記アンテナに前記送信機により提供される前記信号のタイプは、第1のモードにおいて生成される信号、及び、第2のモードにおいて生成される信号の中から選択され、

前記第1のモードにおける前記信号のタイプは、周波数変調連続波(FMCW)信号又はストレッチパルス圧縮信号であり、前記第2のモードにおける前記信号のタイプは、線形周波数変調(LFM)パルス圧縮信号又は非線形周波数変調(NLFM)パルス圧縮信号であり、

40

前記シンセサイザは、位相ロックループ(PLL)とダイレクトデジタルシンセサイザ(DDS)とを備え、前記PLLは、フラクショナルNシンセサイザを備えるとともに、前記レーダーシステムの第1の信号経路に配置され、前記DDSは、前記レーダーシステムの第2の信号経路に前記第1の信号経路と並列に配置され、パルス・ツー・パルス周波数ホッピングを提供する

ことを特徴とする方法。

【発明の詳細な説明】

50

## 【技術分野】

## 【0001】

同時係属出願

[0001] 本出願は、2012年9月10日に出願の米国特許出願第61/698,903号の利益を請求するものであり、また、2012年9月24日に出願の米国特許同時継続出願第13/625,785号と関連するものであり、これらの内容は、この参照によりここに組み入れられる。

## 【背景技術】

## 【0002】

[0002] 現在、非常に短い最小範囲（<10フィート（約3メートル））から中程度の範囲（5～7海里）で3～10フィート（約0.9～3メートル）程度の非常に高い分解能を提供することに加えて、長距離と中距離との組み合わせの分解能を提供する海洋と航空との双方の応用を可能にするレーダ装置は、存在しない。現在の商用の海用のレーダー・システムは、中範囲ないし高範囲の分解能を持つ中（～1NM）ないし長距離の能力のために、パルス方法またはパルス圧縮方法を採用する。その例は、Honeywell社のRDR4000非線形周波数変調（NLFM）パルス・コンプレッション・レーダー、ケルビン・ヒューズのLFMパルス・コンプレッション・マリン・レーダー、JRSのソリッド・ステート・マリン・レーダー、およびNGC/スペリーのマリン・ソリッドステート・パルス・コンプレッション・レーダー・システムを含む。海洋レーダーは、現在、パルス型のシステム（すべてのサブライヤー）、または周波数変調連続波（FMCW）型のシステム（Navico）である。

## 【発明の概要】

## 【課題を解決するための手段】

## 【0003】

[0003] 本発明は、近距離と遠距離との双方で動作するレーダー・システムを提供する。典型的なレーダー・システムは、クロック信号とモード信号とのうちの少なくとも1つを生成するコントローラと、シンセサイザを備えた送信機と、二重モード送信機とを含む。シンセサイザおよび二重モード送信機は、生成された少なくとも一つのクロック信号またはモード信号に基いて、第1のモードまたは第2のモード（周波数レンジ）の信号を生成する。システムはまた、

生成された信号を送信し、送信された信号に基づいてリターン信号を受信するアンテナと、

生成されたクロック信号またはモード信号のうちの少なくとも1つに基いて、第1又は第2のモードに従って、受信されたリターン信号を処理するレシーバ（受信機）と、

処理されたリターン信号に含まれているターゲットの存在を判定するプロセッサと、判定に基づいて、プレゼンテーションを出力する出力デバイス（表示装置など）とを含む。

## 【0004】

[0004] 第1のモードは、周波数変調連続波（FMCW）モードまたはストレッチ・パルス圧縮モードである。第2のモードは、線形または非線形周波数変調（LFM、NLFM）パルス圧縮モードである。

## 【0005】

[0005] 本発明のある態様では、シンセサイザはフラクショナルNシンセサイザまたはダイレクト・デジタル・シンセサイザ・ベースの位相ロック・ループである。

[0006] 本発明の別の態様では、二重モード送信機は、可変減衰器、複数の増幅器、変調器、およびローパス・フィルタを含む。二重モード送信機は、SおよびX周波数帯の信号を生成する。

## 【0006】

[0007] 本発明の更に別の態様では、受信機は、FMCWおよびストレッチ・パルス圧縮信号のための、およびLFMおよびNLFMパルス圧縮信号のための、別々の受信機を含む。

[0008] 本発明の更に別の態様では、システムは、以下のモードにおいて動作することができる：FMCW、パルス、周波数シフト・キーイング（FSK）パルス、LFMパルス、NLFMパ

10

20

30

40

50

ルス。NLFMのパルスは、DDSベースの位相ロックループ(PLL)変調を必要とし得る。

**【0007】**

[0009] 本発明の利点は、部品および製造費用の減少を含む。

[0010] 本発明の好適な及び代替の実施形態は、以下の図面を参照して以下に詳細に記載される。

**【図面の簡単な説明】**

**【0008】**

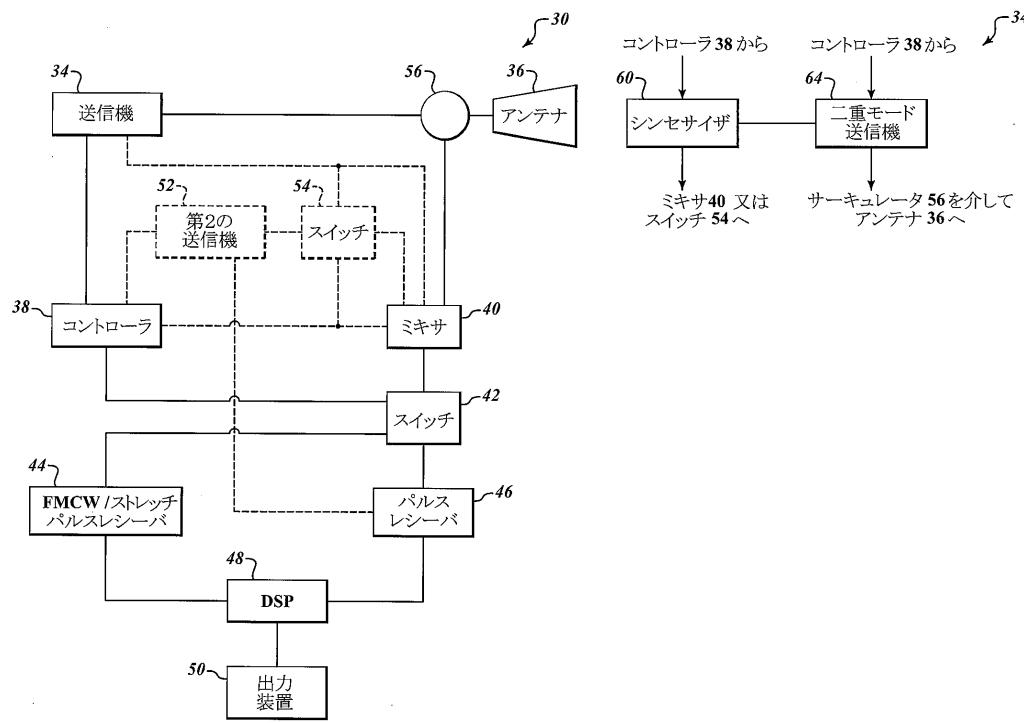

**【図1-1】**[0011] 図1-1は、本発明の実施形態に従って形成されるシステムのブロック図を例示する。

**【図1-2】**図1-2は、本発明の実施形態に従って形成されるシステムのブロック図を例示する。

10

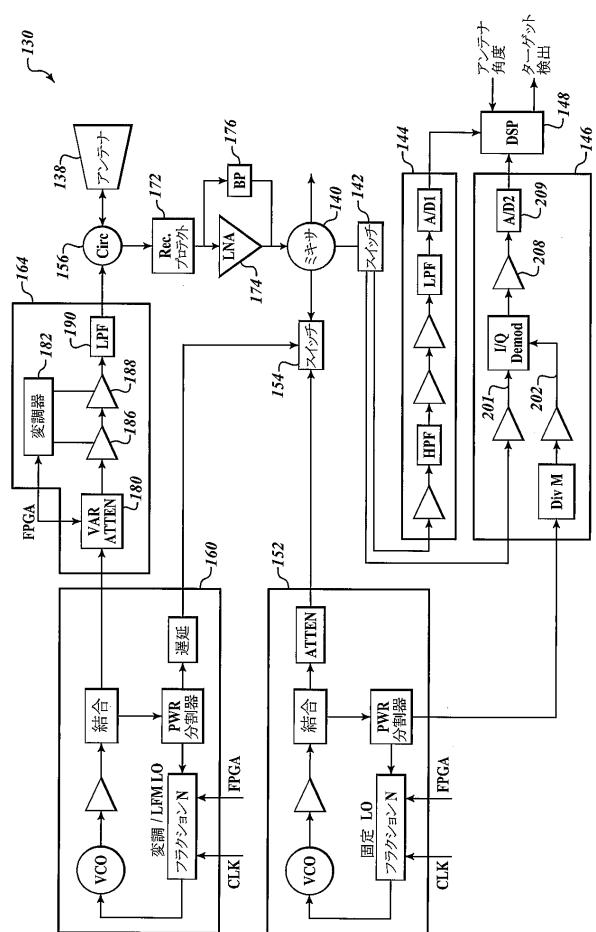

**【図2-1】**図2-1は、本発明の実施形態に従って形成されるシステムのブロック図を例示する。

**【図2-2】**図2-2は、本発明の実施形態に従って形成されるシステムのブロック図を例示する。

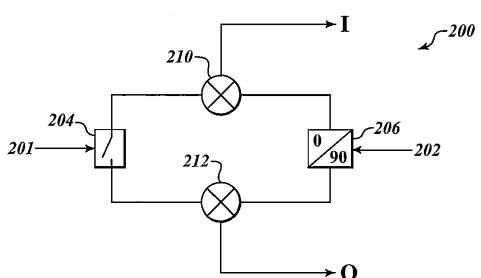

**【図3】**図3は、本発明の実施形態に従って形成されるシステムのブロック図を例示する。

。

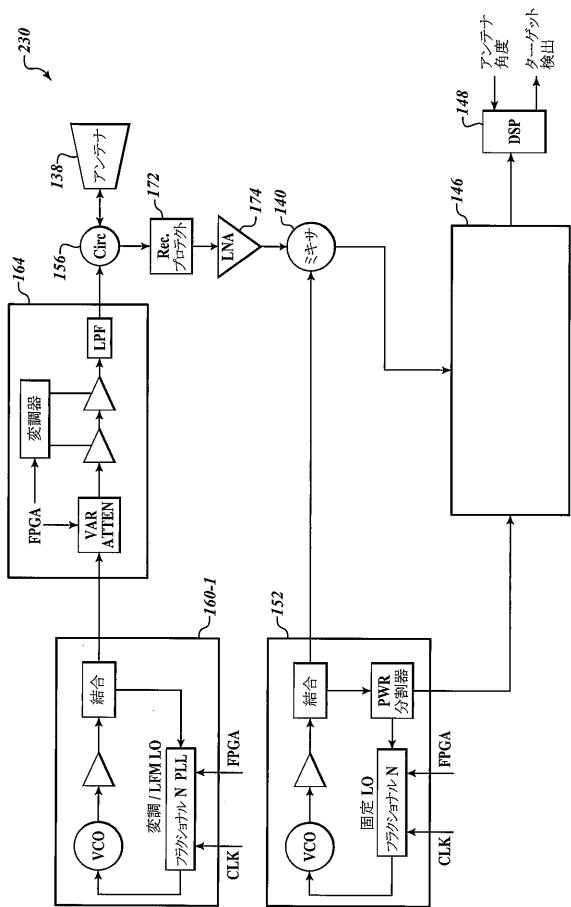

**【図4】**図4は、本発明の実施形態に従って形成されるシステムのブロック図を例示する。

。

**【図5-1】**図5-1は、本発明の実施形態に従って形成されるシステムのブロック図を例示する。

20

**【図5-2】**図5-2は、本発明の実施形態に従って形成されるシステムのブロック図を例示する。

**【発明を実施するための形態】**

**【0009】**

[0012] 本発明は、連続波(CW)ドライバ・ステージ(DPLLで周波数ロックを維持する)と、周波数変調連続波(FMCW)モードに対して低電圧で低電流のCW動作と高電圧/高電流のパルス動作との何れかを提供するデュアルモード変調器とを用いる窒化ガリウム(GaN)ハイパワー(すなわち、40Wピーク)送信機と関連して使用されるデジタル位相ロックループ(DPLL)ベースのシンセサイザまたはフラクショナルNシンセサイザを含む。

30

**【0010】**

[0013] 図1-1は、本発明の実施形態に従って形成される典型的なシステム30のブロック図を示す。システム30は、送信機34(上記のようなものなど)、アンテナ36、コントローラ38、ミキサー40、スイッチ42、FMCW/ストレッチ・パルス受信機44、非線形または線形周波数変調(NLFMまたはLFM)パルス圧縮受信機46、デジタル信号プロセッサ(DSP)48、出力装置50、サーチュレータ56、および、オプションとして、第2の送信機52および第2のスイッチ54を含む。

**【0011】**

[0014] コントローラ38は、送信機34、52およびスイッチ42、54へ制御信号および/またはクロック信号を送る。コントローラ38からの信号に基づいて、送信機34は、サーチュレータ56を介して、アンテナ36に、線形または非線形パルスまたはFMCW信号を出力する。アンテナ36によって受け取られた信号は、サーチュレータ56を介してミキサー40へ送られて、直接の又はスイッチ54を介しての第2のシンセサイザ52からの信号又は送信機34からの遅延信号のいずれかと混合される。

40

**【0012】**

[0015] スイッチ42は、コントローラ38からの信号(1以上)によって制御されて、受信機44、46のうちの1つへミキサー40の出力を送る。第2の送信機52が使われる場合、第2の送信機52は、パルス圧縮受信機46へ信号を送る。パルス圧縮受信機46へ送られた信号は、第2の送信機52がミキサー40へ送った信号に関連する。受信機44、46は、デジタル変

換を実行してデジタル化された信号(1以上)をDSP 48へ送信する前に、受け取った信号(1以上)に対してアナログ信号処理を実行する。DSP 48は、何れの受信機44、46が前処理を行ったかに応じて(コントローラ38からの信号を参照)、デジタル信号を周波数ドメインに変換するか、または、相関処理を実行する。DSP 48は、次に、プレゼンテーションのために出力装置50へ送られる出力を生成する。DSP 48によって実行される前処理および機能は、個別のFMCWシステムまたはパルス・システムを製造する者には知られている。

#### 【0013】

[0016] 図1-2は、送信機34の典型的なコンポーネントを示す。送信機34は、シンセサイザ60および二重モード送信機64を含む。シンセサイザ60は、コントローラ38から信号を受け取り、ベース周波数送信機信号を二重モード送信機64へ出力し、ベース周波数送信機信号の遅延をミキサー40または第2のスイッチ54に出力する。実施形態によっては、遅延信号は、生成されず、送られない。二重モード送信機64は、受け取ったベース周波数送信機信号およびコントローラ38からの信号に基づいて、レーダー送信を生成し、そのレーダー送信を、サーキュレータ56を介してアンテナ36へ送る。

#### 【0014】

[0017] シンセサイザ60は、DPLL(米国特許第7239266号または第7161527号に記載されているものであり、これらの文書は、この参照によりここに組み込まれる)と、内蔵LFM(LFMセグメントを備えた近似NLFM)を備えたフラクショナルNシンセサイザとのいずれかを含む。典型的なフラクショナルNシンセサイザは、「直接変調波形」機能(アナログ・デバイス)を有するADF4159 13GHzフラクショナルNシンセサイザ、またはヒッタイト自己完結型フラクショナルNシンセサイザ(HMC769LP6CE、9.05から10+GHzオペレーション)を含む。

#### 【0015】

[0018] フラクショナル・シンセサイザは、FMCWモードをインプリメントし、最低限で線形FMCWまたはLFMパルス圧縮を生成するために用いられる。適切な変更により、例えば、非線形FM変調は、正接関数の形態をとる。これは、いくつかの小さい線形FMセグメントで近似することができ、それらは、端と端とをつないで組み合わせたときに、必要とされる正接関数(または他の形状)を形成する。この近似は、比較的長い波形に対してのみ使えるものであり、短いパルスのみという制限では、DDSはNLFM波形を作成することができる。また、シンセサイザは、同様に、NLFMレーダー・システムを作成するために用いることができる。

#### 【0016】

[0019] フラクショナルNシンセサイザを使用して必要とされる波形を生成することは、110MHz以上の周波数で動作する内部位相周波数検出器(PFD)を提供するシンセサイザによってのみ可能である。

#### 【0017】

[0020] フラクショナルNシンセサイザを使用する場合、LFMの生成の間は非常に小さい周波数ステップ・サイズ(数百万のHzのうちのHzのオーダー)を用いてフラクショナルNシンセサイザのLFM周波数"階段(staircase)"に起因する受信スペクトル破損の問題を回避する。

#### 【0018】

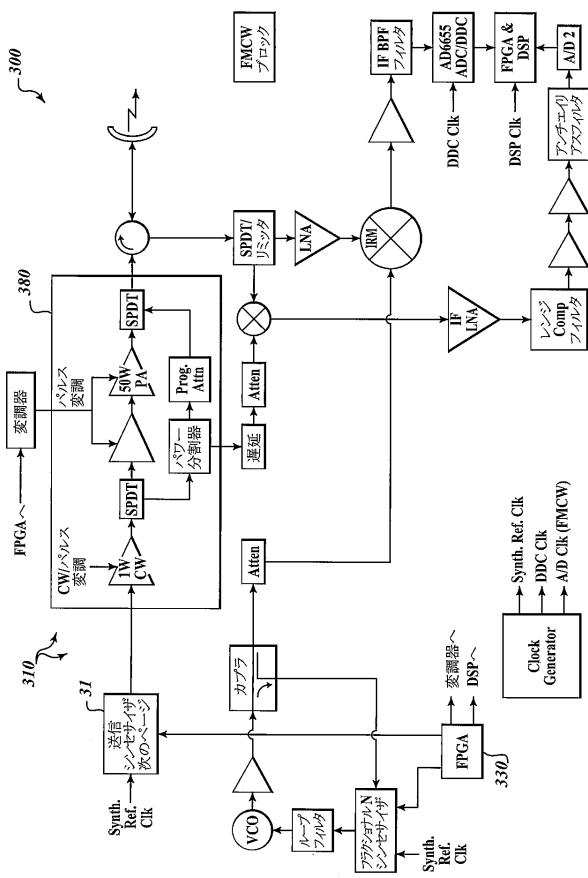

[0021] 図2-1および2-2は、LFMまたはNLFMを使用する二重モード(パルス、FMCW)動作を実行する、コントローラおよび出力装置を除外した典型的なシステム130の概略ブロック図を示す。システム130は、SおよびXバンドの信号を作ることができる。Sバンドは、2.9-3.1GHzである。Xバンドは、9.2乃至9.5GHzである。システム130は、13GHzまで信号を出力することができる。

#### 【0019】

[0022] システム130が、FMCWまたはLFMストレッチ圧縮モードで動作するように指令されると、スイッチ154は、コントローラ(すなわち、Hittite Microwave Corporationにより製造されるもののようなフィールド・プログラマブル・ゲート・アレイ(FPGA)、およ

10

20

30

40

50

び／または、クロック (clk) ) からの信号に基づいて、第 1 のシンセサイザ160が出力する信号に関連する分割（パワー）および遅延された信号がミキサー140へ送られることを、許容する。ミキサー140は、サーキュレータ156を介してのアンテナ138からの処理されたリターン信号と、分割および遅延された信号とを組み合わせる。サーキュレータ156から出力されたリターン信号は受信器保護装置172へ送られ、受信器保護装置172は、コントローラがLFMストレッチ圧縮モードを選択している場合には低雑音増幅器（LNA）174への出力を行い、FMCWが選択されている場合にはバイパス176への出力を行う。送信機164が始動すると、数ワットの電力がアンテナ138から反射し、受信機LNA174または受信機ミキサー140に到達して、それらを破壊し得る。そのため、PINダイオード（デバイス172）が、受信機の入力にシャントに配置される。送信パルスからの大きい電圧が現れるとすぐに、ダイオードが導通して、エネルギーが受信機から遠ざかるように反射する。バイパス176は、コントローラ38（例えばFPGA）によって制御される。

## 【0020】

[0023] リターン信号は、シンセサイザ160及びコントローラから受信した信号に応じて、送信機164によって出力されるFMCW又はLFMストレッチ圧縮信号に基づいている。ある実施形態では、送信機164は、可変減衰器180、変調器182、2つの増幅器186、188、およびローパワー・フィルタ（LPF）190を含む。可変減衰器180は、コントローラにより制御されて、2つのモードに関して送信機164に対してドライブ・レベルを設定する。ハイ・パワー・モードでは、減衰器180はゼロに設定され、それにより、ドライブ・パワーの全てが増幅器へ到達してフル・パワーに達する。FMCWモードでは、送信機バイアス・レベルは実質的に低減され、減衰器180は、送信機を0.1W出力レベルで駆動するレベルに設定される。FPGAからの制御信号は、上記のように減衰器を設定する。

## 【0021】

[0024] ストレッチLFMモード中に、送信機164がパルス・オフされると、減衰器は、PLの固定負荷として使用される。減衰器180は、FMCWモードにおけるHPA186および188の駆動レベルを調整して、自己ジャミングを防止するレベルに送信パワーを低減する。FMCWモードにおいて、HPAバイアスは、CW動作および更に低い電圧レベルに対して設定される。減衰器180は、適正な動作のためにHPAにおける最小利得/最小電圧を許容し、必要とされる最終的な低パワー出力を提供するように低ドライブ・レベルを設定する。減衰器180はまた、サーキュレータ156への入力のところにあるパワー検出器を有する閉ループ構成において用いられ、温度および製品の変動に対して、必要とされる固定の出力パワーを維持する。

## 【0022】

[0025] 減衰器180の出力は第1の増幅器186へ送られ、それから第2の増幅器188へ送られるが、双方とも変調器182により変調される。変調により、コンポーネントが所望の周波数帯の信号を作るようにさせる。変調器182は、増幅器186、188の送信パワーを制御するように、バイアス・レベルを調整する。ある実施形態では、増幅器186、188はGaN増幅器である。LPF 190は、第2の増幅器188から出力される信号を、サーキュレータ156を介してアンテナ138へ送る前に、フィルタリングする。ある実施形態において、送信パワーは距離の関数として調整される。パルスとCWの動作の間のパワー比は、最高26dBである。

## 【0023】

[0026] まだFMCW/ LFMストレッチ・モードにあるとき、スイッチ142は、FMCW/ストレッチ・レシーバ144にミキサー140の出力を送る。FMCW/ストレッチ受信機144は、知られているアナログ受信信号の前処理を行い、その処理の結果をデジタルにし、その後、そのデジタル信号をDSP 148へ送る。DSP 148は、受け取られたアンテナ角度情報（そして、コントローラの信号などの可能な他の情報）に基づいて、デジタル信号を周波数ドメインに変換するために、デジタル信号に対して高速フーリエ変換（FFT）を実行する。DSP148は、次に、周波数ドメイン信号から対象を識別し、その情報を出力装置又は他の車両システムへ送る。

## 【0024】

10

20

30

40

50

[0027] システム130がNLFMまたはLFMパルス圧縮モードで動作するよう命令されると、スイッチ154は、LNA 174からのリターン信号と混合するように、第2のシンセサイザ152からミキサー140へ、減衰された信号を送る。スイッチ142は、ミキサー140の出力をパルス受信機146へ送り、それはまた、第2のシンセサイザ152によって作られた信号の一部である信号を受け取る。パルス受信機146は、更に、第2のシンセサイザ152から直接受け取られる信号を分割し、スイッチ142からの信号および分割された信号に基づいて、I/Q復調を実行する。NLFMモードにおいて、周波数ステップ・レートを調整するために、FGAを用いてシンセサイザ160, 152により非線形波形が作成される。

#### 【0025】

[0028] パルス・モードでのチャーブ帯域幅は、第2の受信機146内のアナログ-デジタル変換器のクロック・レートによって設定される。FMCWモードのチャーブ帯域幅は、レーダーの距離分解能を設定する。IF帯域幅は、チャーブ帯域幅、チャーブの期間、およびレーダーの最大距離により決定される。チャーブ帯域幅は、DDSまたはフラクショナル・シンセサイザへの命令により決定される。シンセサイザによって発生する最大周波数は、クロック周波数の1/2より小さい。パルス・ストレッチLFMモードでのチャーブ帯域幅は、法定帯域幅および最大範囲でのIF帯域幅により設定される。法定帯域幅は、応用に対しての国際条約によって設定される。マリン・レーダーS帯域における最大許容帯域幅は、200 MHzおよびXバンドである。

#### 【0026】

[0029] 図2-2は、I/Q復調を行うための典型的なコンポーネント200を示す。コンポーネント200は、スイッチ142から受け取られるリターン信号201を分割するスプリッタ204を含む。デバイス206は、第2のシンセサイザ152から受け取った信号202を分割し、スプリット信号の一方を位相シフトする。デバイス206およびスプリッタ204からの出力は、I/Q信号を生成するためにコンバイン210、212へ送られる。生成されたI/Q信号は、その後、DSP 148へ送られる前に増幅されデジタル化される。DSP 148は、目標を検出するために、デジタル化されたI/Q信号に対して相關処理を行う。

#### 【0027】

[0030] FMCWモードにおいて、送信機164のバイアスは、低利得のためにモジュレータ182によって低減される。送信パワーは、~20 dBmに対して設定される。

[0031] LFMモードでは、送信機164はディスエーブルにされるが、ローカル発振器(LO)基準がストレッチ処理を用いるので、波形は継続する。送信機が停止した後もDPLLはまだ機能しているため、送信機が停止した後にも、ローカル発振器信号は、受信ミキサへ供給される。ストレッチ処理は、基準信号に、信号が受信機へ戻る時間の間は存在することを要求する。可変減衰器180は、フル・パワーに対して設定される。第2シンセサイザ/送信機152は、FMCWモードに対してのものと同じであることを必要としない。

#### 【0028】

[0032] NLFMモードにおいて、DSP 148は測距および圧縮を提供するが、それらはハネウェル社のRDR-4000によって行われるものと同様である。

[0033] LFMパルス・モードにおいて、DSP 148は測距および圧縮を提供する。

#### 【0029】

[0034] FSKパルス・モードおよびパルス・モードにおいて、第2のシンセサイザ/送信機152は、受信ができるようにするために固定周波数ローカル発振器信号を提供する。DSP 148は、測距とパルス・ツー・パルス(pulse-to-pulse)の統合を提供する。FSKは、干渉の軽減または距離分解能(LFMに対するパルス・ツー・パルス周波数ステップ近似)の改善のために使用される。

#### 【0030】

[0035] 図3は、FMCWやストレッチ・パルス圧縮のモードではなく、NLFMまたはLFMパルス圧縮のモードで動作するシステム230を示す。システム230が、FMCW/ストレッチ受信機144、第1または第2のスイッチ142、154、およびバイパス176を含まないことを除き、システム230は、システム130(図2-1)のものとすべて同じコンポー

10

20

30

40

50

ネットを含む。システム230は、パワー分割器や遅延装置を含まないシンセサイザ160-1を含む。

#### 【0031】

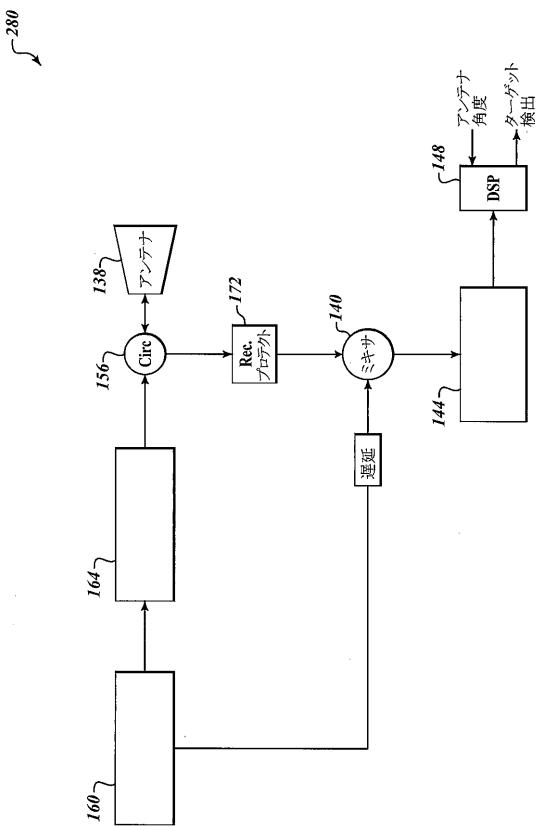

[0036] 図4は、FMCWまたはストレッチ・パルス圧縮のモードのみで動作するシステム280を示す。システム280は、第2のシンセサイザ152、スイッチ142、154、バイパス176、パルス・レシーバ146を含まない。

#### 【0032】

[0037] 全ての実施形態において、オプションとして、FPGAはDSPから信号を受け取る。

[0038] ある実施形態では、DPLLが使われるときには、フラクショナル・シンセサイザの代わりに、ダイレクト・デジタル・シンセサイザが使われる。典型的なDDS駆動DPLLは、2008年10月22日に出願の米国特許出願第12/256,392号、および2011年1月21日に出願の米国特許出願第13/011,771号に記載されており、これらの内容は、この参照によりここに組み入れられる。10

#### 【0033】

[0039] ある実施形態では、二重モード送信機64は、パルス送信機コンポーネントおよび低パワーFMCW/ストレッチ・パルス送信機コンポーネントの動作を制御するように構成されるハイブリッド・カプラを含む。このタイプのデュアルモード送信機の例は、米国特許の同時係属出願第13/625,785号に記載されており（代理人整理番号H000-1-1904）、その内容はこの参照によりここに組み込まれる。20

#### 【0034】

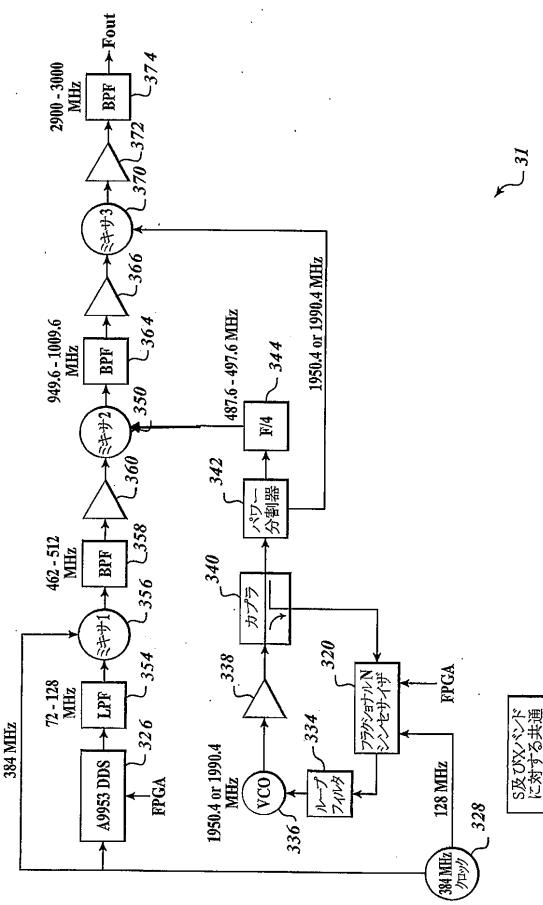

[0040] 図5-1および5-2は、送信機310を含むレーダー・システム300を例示する。送信機310は送信シンセサイザ314を含み、送信シンセサイザ314は、DDS326およびフラクショナルNシンセサイザ320を含み、これらの双方とも、クロック328（例えば、384 / 128 MHz クロック）からクロック信号を受け取り、かつコントローラ330（例えば、FPGA）から制御信号を受け取る。フラクショナルNシンセサイザ320の出力は、VCO336（例えば、1950.4または1990.4MHz）へ入力される前に、ループ・フィルタ334によりフィルタリングされ、VCO336は、出力を增幅器338へ送る。増幅された出力は、カプラ340を介してパワー分割器342に送られる。カプラ340は、フラクショナルNシンセサイザ320へ、増幅された出力の一部を戻す。周波数分割器344は、第1のミキサー350のための入力（例えば487.6-497.6MHz）を生成するために、電力分割器342の出力を所定のファクター（例えば、4）により分割する。30

#### 【0035】

[0041] DDS 326の出力は、クロック信号と混合するために、LPF354（例えば、72-128MHz）を介して第2のミキサー356へ送られる。BPF 358は、ミキサー356の出力をフィルタリングする（例えば462-512MHz）。次に、混合された信号は、周波数分割された出力と第1のミキサー350において混合される前に、増幅器360によって増幅される。BPF 364は、第1のミキサー350の出力をフィルタリングする（例えば949.6-1009.6MHz）。別のミキサー370は、パワー分割器342からの信号（例えば1950.4または1990.4MHz）と、BPF 364の増幅された出力（増幅器366により増幅）とを混合する。次に、ミキサー370の出力は増幅器372によって増幅され、その後、BPF 374（例えば2900-3000MHz）によってフィルタリングされる。BPF 374の出力は、送信機コンポーネント380へ送られる。40

#### 【0036】

[0042] フラクショナルNシンセサイザおよびDDSを使用すると、コストが低くなる。また、DDSは、より高性能である変調能力を提供する。

[0043] ある実施形態では、VCO336は、ヒッタイトによって作られた8-10 GHz VCOであり、VCOヒッタイト・プログラマブル1,3分周器を3に設定することにより3 GHzへと分割され下げられるものであり、Xバンドは分周器を1に設定し、カプラ-340は、SおよびXバンド周波数をカバーするための広帯域カプラである。従って、SおよびXバンド送信機/シンセサイザ組み合わせは、SバンドおよびXバンドに共通である周波数独立型モジュールに

10

20

30

40

50

なる。カプラ340は、二重帯域または広帯域の設計であり、ドライバ増幅器338は、3/9GHzをカバーする広帯域である。

### 【0037】

[0044] システム300は、N=4及び7377.6 GHzのVCO周波数を用いて、同様にして、9.3乃至9.4ギガヘルツ（または、他の100 MHz幅セグメント）からXバンドへと変換される。追加のVCO周波数を用いて、200MHzの帯域幅の方へ延ばすことが可能である。DDS 326は、高速変調能力および周波数ホッピング・パルス・ツー・パルスを提供する。低コストのフラクショナルNシンセサイザおよび周波数分割器は、マイクロ波信号およびローカル発振器信号（フラクショナルNシンセサイザ）を生成する。最後の二つのBPF364、374は、送信帯域幅能力の全体に対応している。10

### 【0038】

[0045] フラクショナルNシンセサイザのシフトが予め計画される限り、システム300は、50 MHzまでの広いチャーブおよび100MHzにわたる周波数ホッピングを許容し、従って、うまくおさまる。DDSではなくPLLに基づくシステムは、周波数ホップ後に、再ロックする時間を必要とする。周波数における大きいステップ変化が命令された場合、PLLはアンロックする。その後、「リングし(ring)」、最終的に新たな指令された周波数に定まるが、これには、周波数ステップ変化とPLLループ利得の設計に応じて数マイクロ秒からミリ秒を要し得る。20

### 【0039】

[0046] シンセサイザ314は、「共通の」電子回路の一部ではなくSまたはXバンド・ブロックの一部になることを必要とされる。クロックおよびDDSだけが、Sバンド・システムおよびXバンド・システムに共通であろう。典型的なフラクショナルNシンセサイザは、13 GHzの動作まで可能である。XおよびSの双方とも、FMCWおよびパルス・モード能力を有する。非共通の部分は、周波数に応じての特定的なものであり、例えば、HPA（高パワー増幅器または送信機）は、SバンドまたはXバンドに固有な設計である。それは、SおよびXのために使われるものではなく、特定のGaNトランジスタを用いるその帯域に固有な設計であろう。13

### 【0040】

[0047] ある実施形態では、システム314は、SまたはXバンドにわたって100MHzの動作に適応する。VCO 336は、最初の50MHzに対しては1950.4とし、第2の50MHzに対しては1990.4とするように命令される。100MHzの帯域は、周波数制限に対応するために、下部帯域と上部帯域とに割られる。これは、高調波を含まない周波数範囲でDDSが使用され得るように行われる。30

### 【0041】

[0048] 上記で、本発明の好ましい実施形態が例示され記載されたが、本発明の精神と範囲から逸脱することなく、多くの変更がなされ得る。したがって、本発明の範囲は、好ましい実施形態の開示によって制限されない。その代わりに、本発明は、請求の範囲を参考することにより全体を決定されるべきである。

### 【0042】

[0049] 排他的特権又は所有権が請求されている本発明の実施形態は、下記のように定められる。40

【 図 1 - 1 】

【図 1 - 2】

【 図 2 - 1 】

【図2-2】

【図3】

【図4】

【図5-1】

【図5-2】

31

S及BXバンド

に対する共通

プロセッサ

---

フロントページの続き

(74)代理人 100075270

弁理士 小林 泰

(74)代理人 100101373

弁理士 竹内 茂雄

(74)代理人 100118902

弁理士 山本 修

(74)代理人 100147681

弁理士 夫馬 直樹

(72)発明者 デーヴィッド・シー・ヴァキャンティ

アメリカ合衆国ニュージャージー州07962-2245, モーリスタウン, コロンビア・ロード

101, ピー・オー・ボックス 2245, ハネウェル・インターナショナル・インコーポレーテッド, パテント・サービス エム/エス エイビー/2ピー

審査官 渡辺 慶人

(56)参考文献 特開2011-191293(JP, A)

特開2006-029858(JP, A)

米国特許出願公開第2011/0298506(US, A1)

特開2007-225319(JP, A)

特開平07-094948(JP, A)

米国特許第07250823(US, B2)

米国特許第06486826(US, B1)

米国特許出願公開第2005/0285773(US, A1)

特開平11-258340(JP, A)

特表2009-516825(JP, A)

(58)調査した分野(Int.Cl., DB名)

I P C G 0 1 S 7 / 0 0 - 7 / 4 2

1 3 / 0 0 - 1 3 / 9 5