(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5553543号

(P5553543)

(45) 発行日 平成26年7月16日(2014.7.16)

(24) 登録日 平成26年6月6日(2014.6.6)

(51) Int.Cl.

B 41 J 2/05 (2006.01)

F 1

B 41 J 2/05

請求項の数 6 (全 11 頁)

(21) 出願番号 特願2009-151482 (P2009-151482)

(22) 出願日 平成21年6月25日 (2009.6.25)

(65) 公開番号 特開2010-30294 (P2010-30294A)

(43) 公開日 平成22年2月12日 (2010.2.12)

審査請求日 平成24年6月22日 (2012.6.22)

(31) 優先権主張番号 特願2008-169335 (P2008-169335)

(32) 優先日 平成20年6月27日 (2008.6.27)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 工藤 智子

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

(72) 発明者 古川 達生

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

最終頁に続く

(54) 【発明の名称】記録ヘッドおよび記録ヘッドを用いた記録装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の記録素子を複数のブロックに分けて時分割で駆動を行ってインクを吐出する記録ヘッドであって、

記録素子を駆動する駆動手段と、

1回のインクの吐出について、前記複数の記録素子の駆動を許可する期間を定める許可信号が入力される入力端子と、

前記入力端子を介して、前記許可信号と重畳して入力されるパルス信号に基づき、前記駆動手段の時分割駆動を制御する制御手段と、を備えることを特徴とする記録ヘッド。

## 【請求項 2】

前記制御手段は、グループ毎に記録素子の駆動タイミングを生成するタイミング生成手段を備えることを特徴とする請求項1に記載の記録ヘッド。

## 【請求項 3】

前記制御手段は、駆動する記録素子を選択する信号を生成する信号生成手段を備えることを特徴とする請求項1に記載の記録ヘッド。

## 【請求項 4】

前記制御手段は、前記許可信号で定められた期間にてパルス信号を検出するための検出手段を備えることを特徴とする請求項1に記載の記録ヘッド。

## 【請求項 5】

前記制御手段は、前記パルス信号の数をカウントするカウンタを備えることを特徴とす

10

20

る請求項 1 に記載の記録ヘッド。

【請求項 6】

請求項 1 に記載の記録ヘッドを用いて記録を行う記録装置であって、

前記許可信号を生成する生成手段と、

時分割の駆動のタイミングに同期して、前記生成手段によって生成された前記許可信号を前記記録ヘッドへ転送する転送手段と、を備えることを特徴とする記録装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、記録ヘッド及びその記録ヘッドを用いた記録装置に関する。 10

【背景技術】

【0002】

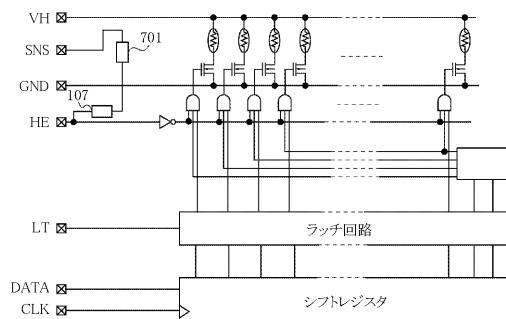

図 9 は、従来の記録ヘッド部の回路構成を示すブロック図である。スイッチング素子 102 は記録素子 101 を駆動する。シフトレジスタ 103 は、クロック信号 (CLK) に基づいてシリアル形式でデータ (DATA) を入力する。このデータは、ブロックを指定する情報と、画像データで構成されている。ラッチ信号 LT に同期して、ラッチ回路 106 は、シフトレジスタ 103 のデータをラッチする。

【0003】

デコーダ 114 は、ブロックを指定する情報をデコードする。デコーダ 1304 は、デコードした結果に基づいて AND 回路 104 へ信号が output する。これにより同時に駆動する記録素子が選択される。 20

【0004】

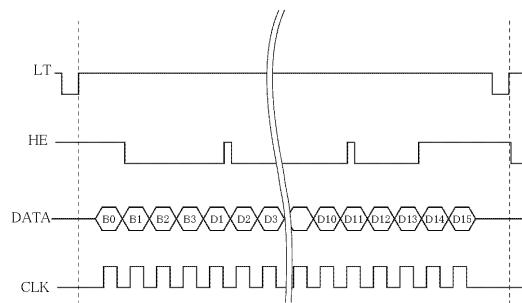

図 10 は、従来の記録素子を駆動するための信号のタイミングチャートである。クロック信号 (CLK) に同期してデータ (DATA) がシフトレジスタ 103 へ転送される。このデータは、ブロックを指定する 4 ビット (B0 ~ B3) の情報と、16 ビット (D0 ~ D15) の画像データで構成されている。ここで、1 ブロックあたり 16 個の記録素子にそれぞれ割当てるために、16 ビットのデータを転送している。また、記録ヘッドは、16 個のブロックを備えており、ブロックを指定するために 4 ビット (B0 ~ B3) の情報を転送する。

【0005】

ラッチ信号 (LT) が入力されると、データがラッチ回路 106 に保持される。ヒートイネーブル信号 (HE) が有効状態 (ロウレベル) で、スイッチング素子 102 をオンできる状態となる。VH は記録素子に印加する電圧である。GND はグランドの信号である。

【0006】

特許文献 1 には、ヒートイネーブル信号 (HE) とラッチ信号 (LT) を共用して、記録素子の駆動とラッチ回路の制御を行う記載がある。また、記録装置の記録動作の高速化、高画質化を実現するために制御として、特許文献 2 に、記録素子毎に異なるタイミングで、記録素子を駆動することが記載されている。

【先行技術文献】 40

【特許文献】

【0007】

【特許文献 1】特開 2005 - 161682 号公報

【特許文献 2】特開 2000 - 263770 号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

記録装置は、上述した装置の高速化や記録画像の高画質化だけでなく、放射ノイズを低減する要求も高まっている。しかし、このための機能を付加しようとすると、記録ヘッドに新たな信号を入力するための端子を追加することになる。この端子の追加は、配線接続

信頼性の低下や、チップ面積の増大などにつながるという課題があった。

【課題を解決するための手段】

【0009】

上述の課題を解決するために、本発明の記録ヘッドは、複数の記録素子を複数のプロックに分けて時分割で駆動を行ってインクを吐出する記録ヘッドであって、記録素子を駆動する駆動手段と、1回のインクの吐出について、前記複数の記録素子の駆動を許可する期間を定める許可信号が入力される入力端子と、前記入力端子を介して、前記許可信号と重畳して入力されるパルス信号に基づき、前記駆動手段の時分割駆動を制御する制御手段と、を備えることを特徴とする。

【発明の効果】

10

【0010】

本発明によれば、記録ヘッドに新たな信号を入力するための端子を追加することなく、放射ノイズを低減することができる。

【図面の簡単な説明】

【0011】

【図1】第1実施形態における記録ヘッドの駆動回路の説明図である。

【図2】第1実施形態における記録ヘッドの信号の説明図である。

【図3】第1実施形態におけるパルス検出回路の説明図である。

【図4】第1実施形態における記録ヘッドの信号の説明図である。

【図5】第2実施形態における記録ヘッドの制御回路の説明図である。

20

【図6】第2実施形態における記録ヘッドの信号の説明図である。

【図7】その他の実施形態における記録ヘッドの制御回路の説明図である。

【図8】実施例に適用するインクジェット記録装置のブロック図である。

【図9】従来の記録ヘッドの駆動回路の説明図である。

【図10】従来の記録ヘッドの信号の説明図である。

【発明を実施するための形態】

【0012】

(第1の実施例)

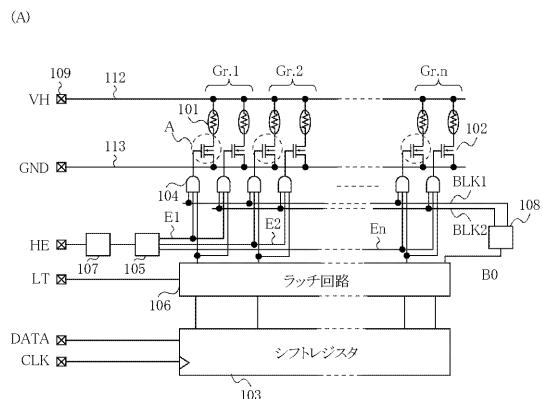

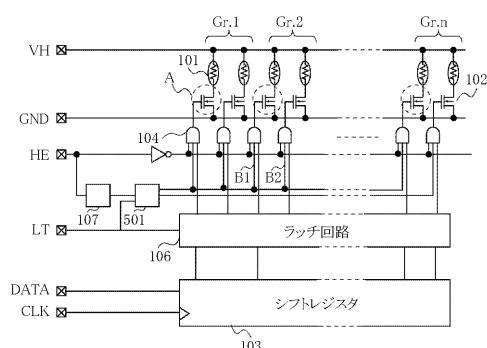

図1Aは、本発明のインクジェット記録ヘッドにおける第1の実施形態の等価回路を示すブロック図であり、基板上の回路ブロックレイアウトを模式的に示しているものである。

30

【0013】

図1Aにおいて、記録ヘッドは、記録素子として、複数( $2 \times n$ 個)の発熱抵抗素子(ヒータ)101を備えている。この発熱抵抗素子(ヒータ)101は熱エネルギーを発生する。駆動素子102は、記録素子101にそれぞれ駆動素子102が設けられている。駆動素子102として、スイッチング素子(MOSトランジスタ)102がヒータへの電流を供給のオン/オフの切替えを行う。この発熱抵抗素子(ヒータ)101は、グループ1(Gr.1)~グループn(Gr.n)までのn個のグループを構成している。この実施例では説明を簡単にするために、1つのグループは、2つのヒータで構成されている。全てのスイッチング素子102のうち、破線で囲まれた丸(Aで示す)のn個のスイッチング素子102は、同時に駆動するように制御線B1K1が接続されている。同様に、破線で囲まれていないn個のスイッチング素子102も、同時に駆動するように制御線B1K2が接続されている。このように、この実施形態では、記録ヘッドの時分割(時分割駆動)の数は2である。このため、記録ヘッドは2つのブロックを構成する。また、n個のグループに属する各記録素子は、ブロック1またはブロック2に割当てられる。つまり、1ブロックあたりn個の記録素子が割当てられる。

40

【0014】

シフトレジスタ103は、ブロック情報B0と発熱抵抗素子101へ出力する画像データを一時的に格納する。ラッチ回路106は、シフトレジスタ103からパラレルに出力された画像データとブロック情報を保持する。ラッチ信号LTが入力するとラッチ回路1

50

06は画像データとブロック情報をラッチする。ヒートイネーブル信号(HE)はヒータ101に駆動するために使用する信号である。デコーダ108は、ラッチ回路106からブロック情報B0を入力し、BLK1、BLK2の信号を生成する。駆動すべきブロックの選択は、BLK1、BLK2の信号に基づいている。

#### 【0015】

信号検出回路(信号生成回路)107は、ヒートイネーブル信号に重畠されているパルス信号を検出(抽出)する。信号検出回路107は、パルス信号の検出に同期して、所定幅のパルス信号NPを生成し、タイミング回路105へ出力する。記録ヘッドは、電力、ヒートイネーブル信号(HE)、ラッチ信号LT、データ信号DATA、クロック信号CLKを受けるために、複数のパッド109を備えている。

10

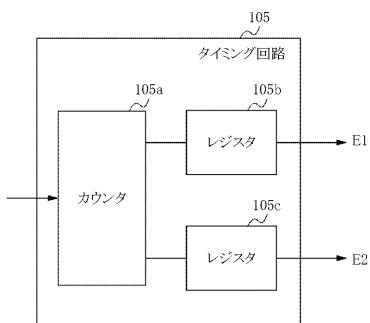

#### 【0016】

図1Bに示すように、タイミング回路105はカウンタ105aとレジスタ105b、105cを備えている。ここでは、説明を簡単にするために、グループの数が2である。カウンタ105aは、パルス検出回路107から出力されるパルス信号NPの数をカウントする。各レジスタは、グループそれぞれ対応している。レジスタ105b、105cは、カウンタ105の値を参照し、それぞれ予め決められたカウント値になれば許可信号E1、E2を出力する。このようにタイミング回路105は、許可信号のタイミング生成を行う。このために、レジスタ105b、105cは、それぞれ許可信号の出力開始、出力終了のカウント値(タイミング情報)を備えている。

#### 【0017】

20

従って、例えば、グループ数は8であれば、8つのレジスタを備え、許可信号はE1からE8を出力する構成とする。

#### 【0018】

図1Aの説明に戻ると、例えば、グループGr.1では、レジスタ105bから許可信号E1が出力する期間において、符号Aのスイッチング素子102のオンが可能となる。AND回路104は、BLK1、BLK2の信号と、ラッチ回路106からの出力された画像データと論理演算する。画像データが記録をすべきデータであれば、符号Aのスイッチング素子102はオン状態になる。グループGr.2～グループGr.nにおいても、同様である。

#### 【0019】

30

なお、電源ライン112は、所定の電圧VHをヒータ101に供給する。GNDライン113は、スイッチング素子102に接続されている。

#### 【0020】

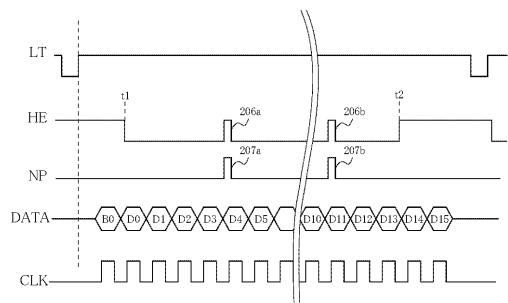

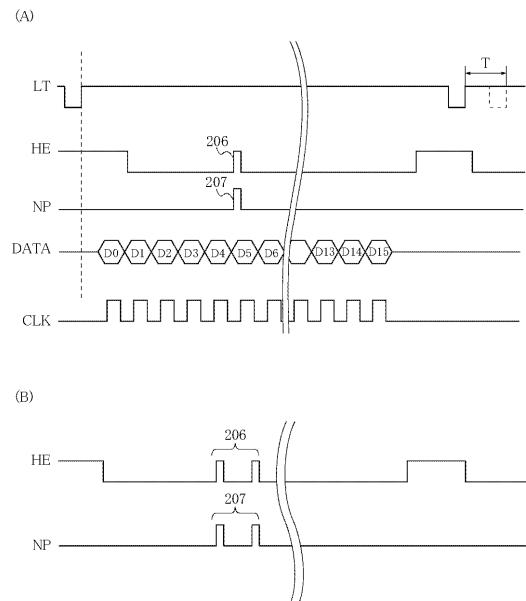

図2は、インクジェット記録ヘッドに入力される信号と内部で生成される信号のタイミングチャートである。図2では、グループの数nは16とする。記録装置から転送クロック(CLK)に同期して、データ(DATA)の転送がシリアルに行われる。このデータは、ブロックを指定する1ビット(B0)の情報と、16ビット(D0～D15)の画像データで構成されている。ここで、1ブロックあたり16個の記録素子にそれぞれ割当てるために、16ビットのデータを転送している。図2のタイミングチャートは、記録ヘッドは、2個のブロックを備えている。駆動するブロックは、ブロック情報B0により指定される。

40

#### 【0021】

画像データは、シフトレジスタ103に転送され、ラッチ信号(LT)203に同期してラッチ回路106に保持される。

#### 【0022】

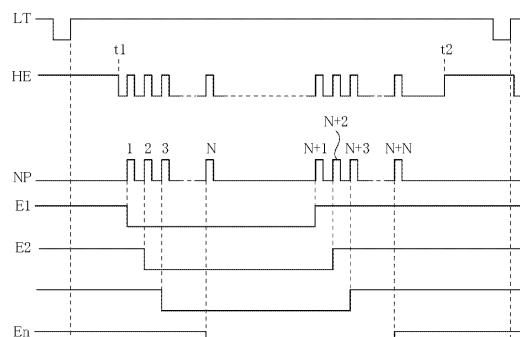

このラッチ信号(LT)によってシフトレジスタ104は、画像データをパラレル出力する。タイミングt1からt2の間のヒートイネーブル信号(HE)の論理レベルがロウレベル(有効)の状態において、スイッチング素子102の駆動が可能となる。これによりヒータ101に電流が流れ、ヒータの熱によりインクが発泡する。タイミングt1からt2の間に、スイッチング素子102の駆動することで、インクの発泡により各ノズルか

50

ら1回のインクの吐出が行われる。

#### 【0023】

この図2では、説明を簡単にするために、1つのグループ(G r . 1)について説明する。ヒートイネーブル信号HEに、パルス206aとパルス206bが重畠されている。パルス検出回路107は、パルス207aとパルス207bで示す信号NPを出力する。パルス207aは出力開始の信号、出力終了パルス207bは出力終了の信号である。この信号に基づき許可信号E1を出力する。

#### 【0024】

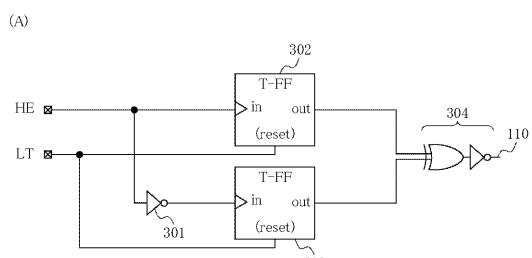

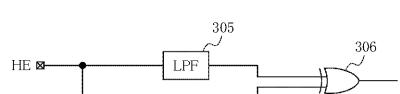

図3Aは、パルス検出回路107の構成を示す図である。図3において、Tフリップフロップ(T - FF)302は、ヒートイネーブル信号HEを入力する。Tフリップフロップ(T - FF)303は、インバータ回路301で論理反転したヒートイネーブル信号HEを入力する。Tフリップフロップ302、Tフリップフロップ303の出力を論理回路304で論理積をとる。論理回路304で論理積により制御信号NPを生成する。

10

#### 【0025】

なお、Tフリップフロップ302、303にはリセット信号としてラッチ信号LTが入力される。ラッチ信号LTが入力する毎に、Tフリップフロップはリセットされる。したがって、周期的にパルス信号の検出を行なうことができる。Tフリップフロップを用いた回路の構成を示したが、図3Bに示すように、ローパスフィルター305を用いてHE信号から短パルスを除いた信号とHE信号を論理回路306へ入力する。論理回路306によって排他的論理和をとることで制御信号NPを生成する形態でも構わない。

20

#### 【0026】

図4は、スイッチング素子102に供給する信号のタイミングを説明する図である。この図4では、記録ヘッドのグループ数はNである。タイミングt1からタイミングt2の期間は、記録ヘッドの記録素子の駆動を許可する期間である。ヒートイネーブル信号HEに重畠されている複数のパルス信号に応じて、パルス検出回路107が制御信号NPを複数出力する。パルス検出回路107は、ヒートイネーブル信号HEに重畠されているパルス信号の数と等しい数の制御信号NPを出力する。

#### 【0027】

許可信号E1は、第1のグループのヒートイネーブル信号である。許可信号E1は、1番目の制御信号NPの出力タイミングでヒートイネーブル信号が開始され、N+1番目の制御信号NPの出力タイミングでヒートイネーブル信号が終了する。つまり、グループ1に属する記録素子101のパルス幅は、1番目のパルスからN+1番目のパルスまでの期間に相当する。

30

#### 【0028】

許可信号E2は、グループ2のヒートイネーブル信号であり、2番目のパルスのタイミングでヒートイネーブル信号が開始され、N+2番目のパルスのタイミングでヒートイネーブル信号が終了する。つまり、グループ2に属する記録素子101のパルス幅は、2番目のパルスからN+2番目のパルスまでの期間に相当する。同様に、グループNに属する記録素子101のパルス幅は、N番目のパルスから2N(N+N)番目のパルスまでの期間に相当する。

40

#### 【0029】

以上のような構成により、グループ毎に、記録素子の駆動タイミングを設定できる。この設定により、グループ間の駆動タイミング異ならせることができ、ノイズのピークを低減させることができる。

#### 【0030】

##### (第2の実施例)

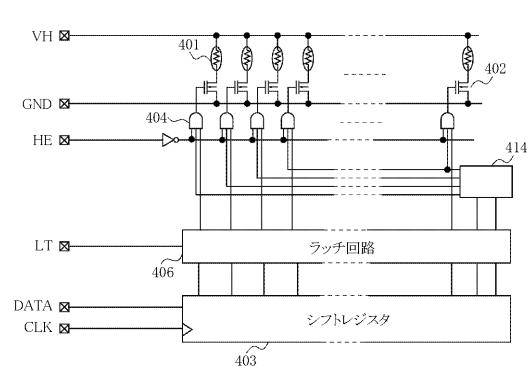

図5は、第2の実施形態の等価回路を示すブロック図である。図1と同様の内容は説明を省き、相違点について説明する。

#### 【0031】

パルス検出回路(パルス生成回路)107は、ヒートイネーブル信号に重畠している

50

パルス信号を検出し、所定幅のパルス信号N Pを出力する。デコーダ501は、パルス検出回路107から出力されるパルス信号N Pの数をカウントする。デコーダ501は、カウント値に応じて、ブロック選択信号を出力する。デコーダ501は、ラッチ信号L Tを入力する。デコーダ501は、ラッチ信号L Tに従ってブロック選択信号を出力する。図5では、説明を簡単にするために、時分割で駆動するタイミングの数を2とするために、記録ヘッドは2つのブロックを備える。従って、記録ヘッドは、各グループに2つのブロックを備えている。例えば、デコーダ501は、カウント値が1であればブロック1を選択する信号B 1を出力する。また、デコーダ501は、カウント値が2であればブロック2を選択する信号B 2を出力する。なお、時分割で駆動するタイミングの数を8とすれば、デコーダ501は、8つのブロックを選択できるように8つの信号B 1～B 8を出力する構成とする。

#### 【0032】

図6Aは、第2の実施形態におけるインクジェット記録ヘッドに入力される信号と内部で生成される信号のタイミングチャートである。図6Aにおいて、ヒートイネーブル信号には1個のパルス信号が重畠されているのを、パルス検出回路107は検知して、パルス信号207を1つ出力する。デコーダ501は、上述したように、ブロック1を選択する信号B 1を出力する。

#### 【0033】

同様に、図6Bにおいて、ヒートイネーブル信号には2個のパルス信号が重畠されているのを、パルス検出回路107は検知して、パルス信号207を2つ出力する。デコーダ501は、上述したように、ブロック2を選択する信号B 2を出力する。

#### 【0034】

第2の実施形態の構成により、先のラッチ信号L Tと次に入力するラッチ信号L Tとの間隔を短くすることができた。図6Aは、従来(図10)よりも時間T分短くなったことを示す。理由は、ブロックを指定する情報(B 0～B 3)を画像データ(D 0～D 15)とともに転送しない構成となつたためである。

#### 【0035】

なお、1つの記録素子列を構成するブロックの数が多ければ多いほど、ブロックを指定する情報のビット数が多くなるため、データの転送量を効果的に減らすと共に、発生するノイズの量を減らすことができる。

#### 【0036】

##### (インクジェット記録装置)

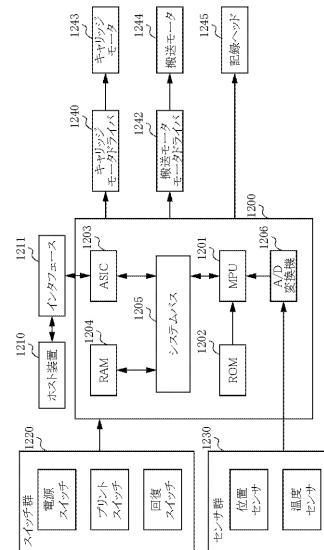

次に、上述した実施形態に適用するインクジェット記録装置の制御構成を説明する。インクジェット記録装置は、記録媒体に対して記録ヘッドを走査させ、記録媒体を搬送することで記録媒体に対して記録を行う。図8は、インクジェット記録装置の制御ブロック図である。コントローラ1200は、MPU1201、ROM1202、特殊用途集積回路ASIC1203、RAM1204、システムバス1205、A/D変換器1206などで構成される。ここで、ROM1202は後述する制御シーケンスに対応したプログラム、テーブル、その他の固定データを格納する。

#### 【0037】

ASIC1203は、転送クロック(CLK)やラッチ信号(L T)やヒートイネーブル信号(HE)を生成して、記録ヘッド1245へ転送する。ASIC1203は、ヒートイネーブル信号(HE)にパルス信号を重畠させる。また、ASIC1203は、RAM1204から画像データの読み出し、記録ヘッドに対して画像データを転送する。

#### 【0038】

ASIC1203は、キャリッジモータ1243を駆動するために、キャリッジモータドライバ1240へ制御信号を出力する。ASIC1203は、搬送モータ1244を駆動するために、搬送モータドライバ1242へ制御信号を出力する。キャリッジモータ1243は、記録ヘッドを走査させるための駆動源であり、搬送モータ1244は、記録媒体を搬送させるための駆動源である。

10

20

30

40

50

**【0039】**

RAM1204は、画像データの保持やプログラム実行のためのデータの保持に用いられる。MPU1201、ASIC1203、RAM1204は、システムバス1205を介して互いに接続されている。A/D変換器1206は以下に説明するセンサ群からのアナログ信号を入力してA/D変換し、デジタル信号をMPU1201に供給する。

**【0040】**

また、図8においてホスト装置1210は、コンピュータ或いは画像読み取り装置やデジタルカメラなどである。ホスト装置1210と記録装置との間ではインターフェース(I/F)1211を介して画像データ、コマンド、ステータス信号等を送受信する。この画像データは、例えば、ラスタ形式で入力される。1220はスイッチ群であり、電源スイッチ、プリントスイッチ、回復スイッチなどから構成される。1230は装置の状態を検出するためのセンサ群であり、位置センサ、温度センサ等から構成される。10

**【0041】****(その他の実施形態)**

図7は、その他の実施形態の等価回路を示すブロック図である。図5と同様の内容は説明を省き、相違点について説明する。

**【0042】**

この図7では、パルス検出回路(パルス生成回路)107は、ヒートイネーブル信号に重畠されているパルス信号を検出し、その信号を温度検知部(温度検出回路)701を制御する。温度検出部701からの電圧出力を信号SNSとして、記録装置へ出力する。このように、記録素子の駆動回路の他に温度検出回路の制御に使用しても構わない。20

**【0043】**

以上のように、記録ヘッド及び記録装置について説明したが、構成に関する数値は、上述した値に限定するものではない。例えば、1つのグループを構成する発熱抵抗素子(ヒータ)の数は2や16に限定するものではなく、8や32でも構わない。また、1つのブロックを構成する発熱抵抗素子(ヒータ)の数も、8や16に限定するものではない。

**【符号の説明】****【0044】**

- |     |                       |    |

|-----|-----------------------|----|

| 101 | 発熱抵抗素子(ヒータ)           |    |

| 102 | MOSトランジスタ(電界効果トランジスタ) | 30 |

| 103 | シフトレジスタ               |    |

| 106 | ラッチ回路                 |    |

| 105 | タイミング回路               |    |

| 107 | 検出回路(生成回路)            |    |

| 108 | デコーダ                  |    |

【図1】

【図2】

(B)

【図3】

(B)

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(72)発明者 平山 信之

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 葛西 亮

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 井上 智之

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

審査官 金田 理香

(56)参考文献 特開平05-104722(JP,A)

特開平09-300622(JP,A)

特開2003-291344(JP,A)

特開平06-191023(JP,A)

特開2005-161682(JP,A)

(58)調査した分野(Int.Cl., DB名)

|        |           |

|--------|-----------|

| B 41 J | 2 / 0 1   |

| B 41 J | 2 / 0 4   |

| B 41 J | 2 / 0 4 5 |

| B 41 J | 2 / 0 5   |

| B 41 J | 2 / 1 3 5 |

| B 41 J | 2 / 1 4   |