(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4877866号

(P4877866)

(45) 発行日 平成24年2月15日(2012.2.15)

(24) 登録日 平成23年12月9日(2011.12.9)

(51) Int.Cl.

H01L 29/786 (2006.01)

H01L 21/336 (2006.01)

F 1

H01L 29/78 623 A

H01L 29/78 627 C

請求項の数 18 (全 33 頁)

(21) 出願番号 特願2004-313315 (P2004-313315)

(22) 出願日 平成16年10月28日 (2004.10.28)

(65) 公開番号 特開2005-167212 (P2005-167212A)

(43) 公開日 平成17年6月23日 (2005.6.23)

審査請求日 平成19年9月4日 (2007.9.4)

(31) 優先権主張番号 特願2003-368141 (P2003-368141)

(32) 優先日 平成15年10月28日 (2003.10.28)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 肇平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 木村 肇

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 前川 慎志

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 中村 理

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

絶縁表面を有する基板上に、プラズマCVD法により、珪素からなる下地層を形成し、

前記下地層上に、液滴吐出法でゲート電極を形成し、

前記ゲート電極をマスクとして、前記下地層をエッチングし、

前記ゲート電極上に、ゲート絶縁層を形成し、

前記ゲート絶縁層上に、セミアモルファス半導体層を形成し、

前記ゲート電極と重なるように、前記セミアモルファス半導体層上にチャネル保護層を

形成し、

前記チャネル保護層上に、一導電型の不純物を含有する半導体層を形成し、

前記一導電型の不純物を含有する半導体層上に、液滴吐出法でマスクを形成し、

前記液滴吐出法で形成したマスクを用いて、前記セミアモルファス半導体層及び前記一導電型の不純物を含有する半導体層をエッチングし、

前記一導電型の不純物を含有する半導体層上に、液滴吐出法でソース配線及びドレイン配線を形成し、

前記ソース配線及び前記ドレイン配線をマスクとして、前記チャネル保護層上の前記一導電型の不純物を含有する半導体層をエッチングすることを特徴とする半導体装置の作製方法。

## 【請求項 2】

絶縁表面を有する基板上に、プラズマCVD法により、珪素からなる下地層を形成し、

10

20

前記下地層上に、液滴吐出法でゲート電極を形成し、

前記ゲート電極をマスクとして、前記下地層をエッチングし、

前記ゲート電極上に、ゲート絶縁層、セミアモルファス半導体層、及び絶縁層を積層して形成し、

前記ゲート電極と重なるように、前記絶縁層上に、液滴吐出法で第1のマスクを形成し、

前記第1のマスクを用いて、前記絶縁層をエッチングしてチャネル保護層を形成し、

前記チャネル保護層上に、一導電型の不純物を含有する半導体層を形成し、

前記一導電型の不純物を含有する半導体層上に、液滴吐出法で第2のマスクを形成し、

前記第2のマスクを用いて、前記セミアモルファス半導体層及び前記一導電型の不純物を含有する半導体層をエッチングし、

前記一導電型の不純物を含有する半導体層上に、液滴吐出法でソース配線及びドレイン配線を形成し、

前記ソース配線及び前記ドレイン配線をマスクとして、前記チャネル保護層上の前記一導電型の不純物を含有する半導体層をエッチングし、

前記ゲート絶縁層は少なくとも、第1の窒化珪素層、樹脂層、及び第2の窒化珪素層を有することを特徴とする半導体装置の作製方法。

**【請求項3】**

請求項2において、

前記ゲート絶縁層、前記セミアモルファス半導体層及び前記絶縁層は、大気に晒すことなく連続的に形成することを特徴とする半導体装置の作製方法。

**【請求項4】**

絶縁表面を有する基板上に、プラズマCVD法により、珪素からなる下地層を形成し、

前記下地層上に、液滴吐出法でゲート電極を形成し、

前記ゲート電極をマスクとして、前記下地層をエッチングし、

前記ゲート電極上に、ゲート絶縁層、セミアモルファス半導体層、及び一導電型の不純物を含有する半導体層を積層して形成し、

前記ゲート電極と重なるように、前記一導電型の不純物を含有する半導体層上に、液滴吐出法でマスクを形成し、

前記液滴吐出法で形成したマスクを用いて、前記セミアモルファス半導体層及び前記一導電型の不純物を含有する半導体層をエッチングし、

前記一導電型の不純物を含有する半導体層上に、液滴吐出法でソース配線及びドレイン配線を形成し、

前記ソース配線及び前記ドレイン配線をマスクとして、前記一導電型の不純物を含有する半導体層をエッチングすることを特徴とする半導体装置の作製方法。

**【請求項5】**

絶縁表面を有する基板上に、プラズマCVD法により、珪素からなる下地層を形成し、

前記下地層上に、液滴吐出法でゲート電極を形成し、

前記ゲート電極をマスクとして、前記下地層をエッチングし、

前記ゲート電極上に、ゲート絶縁層、セミアモルファス半導体層、及び一導電型の不純物を含有する半導体層を積層して形成し、

前記ゲート電極と重なるように、前記一導電型の不純物を含有する半導体層上に、液滴吐出法でマスクを形成し、

前記液滴吐出法で形成したマスクを用いて、前記セミアモルファス半導体層及び前記一導電型の不純物を含有する半導体層をエッチングし、

前記一導電型の不純物を含有する半導体層上に、液滴吐出法でソース配線及びドレイン配線を形成し、

前記ソース配線及び前記ドレイン配線をマスクとして、前記一導電型の不純物を含有する半導体層をエッチングし、

前記ゲート絶縁層は少なくとも、第1の窒化珪素層、樹脂層、及び第2の窒化珪素層を

有することを特徴とする半導体装置の作製方法。

**【請求項 6】**

請求項 1 乃至 請求項 5 のいずれか一項において、

前記ゲート電極は、銀、金、又は銅を含む材料を吐出して形成することを特徴とする半導体装置の作製方法。

**【請求項 7】**

請求項 1 乃至 請求項 5 のいずれか一項において、

前記セミアモルファス半導体層は、酸素濃度が  $5 \times 10^{-9}$  atoms / cm<sup>3</sup> 以下であることを特徴とする半導体装置の作製方法。

**【請求項 8】**

請求項 1 乃至 請求項 5 のいずれか一項において、

前記セミアモルファス半導体層は、酸素濃度が  $1 \times 10^{-9}$  atoms / cm<sup>3</sup> 以下であることを特徴とする半導体装置の作製方法。

**【請求項 9】**

請求項 1 乃至 請求項 5 のいずれか一項において、

前記セミアモルファス半導体層は、結晶粒が分散した非晶質半導体層であることを特徴とする半導体装置の作製方法。

**【請求項 10】**

請求項 1 乃至 請求項 5 のいずれか一項において、

前記セミアモルファス半導体層は、0.5 ~ 20 nm の結晶粒が分散した非晶質半導体層であることを特徴とする半導体装置の作製方法。

**【請求項 11】**

請求項 1 乃至 請求項 5 のいずれか一項において、

前記セミアモルファス半導体層は、珪化物気体を用いてプラズマ CVD 法により形成することを特徴とする半導体装置の作製方法。

**【請求項 12】**

請求項 1 乃至 請求項 5 のいずれか一項において、

前記セミアモルファス半導体層は、珪化物気体を希ガス元素で希釈した気体を用いてプラズマ CVD 法により形成することを特徴とする半導体装置の作製方法。

**【請求項 13】**

請求項 12 において、

前記希ガス元素は、水素、ヘリウム、アルゴン、クリプトン及びネオンから選ばれた 1 種又は複数種であることを特徴とする半導体装置の作製方法。

**【請求項 14】**

請求項 1 乃至 請求項 5 のいずれか一項において、

前記セミアモルファス半導体層は、珪化物気体に炭化物気体を混入させた気体を用いてプラズマ CVD 法により形成することを特徴とする半導体装置の作製方法。

**【請求項 15】**

請求項 14 において、

前記炭化物気体は、CH<sub>4</sub> 又はC<sub>2</sub>H<sub>6</sub> であることを特徴とする半導体装置の作製方法。

。

**【請求項 16】**

請求項 1 乃至 請求項 5 のいずれか一項において、

前記セミアモルファス半導体層は、珪化物気体にゲルマニウム化気体を混入させた気体を用いてプラズマ CVD 法により形成することを特徴とする半導体装置の作製方法。

**【請求項 17】**

請求項 16 において、

前記ゲルマニウム化気体は、GeH<sub>4</sub> 又はGeF<sub>4</sub> であることを特徴とする半導体装置の作製方法。

**【請求項 18】**

10

20

30

40

50

請求項 11 乃至請求項 17 のいずれか一項において、

前記珪化物気体は、 $\text{SiH}_4$ 、 $\text{Si}_2\text{H}_6$ 、 $\text{SiH}_2\text{Cl}_2$ 、 $\text{SiHCl}_3$ 、 $\text{SiCl}_4$ 、又は $\text{SiF}_4$ であることを特徴とする半導体装置の作製方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、液滴吐出法を用いた表示装置の作製方法、配線基板の作製方法及び半導体装置の作製方法に関する。

【背景技術】

【0002】

近年、インクジェット法に代表される液滴吐出法を用いたパターン形成は、フラットパネルディスプレイの分野に応用され、活発に開発が進められている。液滴吐出法は、直接描画するためにマスクが不要、大型基板への適用が容易、材料の利用効率が高い等の多くの利点を有するため、EL層やカラーフィルタ、プラズマディスプレイの電極等の作製に応用されている（例えば、非特許文献1参照。）。

【0003】

液滴吐出法で行う配線の形成は、ノズルの先端から組成物が吐出される際に電荷の偏りが生じて、吐出する組成物が帯電する現象が生じ、この現象に起因して、組成物が付着する薄膜が損傷したり破壊したりすることがある。また、粒子をナノオーダーにした組成物を用いて行うが、上記の組成物によって形成された薄膜は、下層の薄膜との密着性が低いためにその剥離性が高い。従って、半導体プロセスに必須である洗浄工程等のウェット工程を経ると、形成されたパターンが剥離してしまうことがある。

【0004】

一方、表示機能を有する半導体装置は、その価格が低下する傾向にあり、採算を維持できる製造ラインとして、第五世代以降のガラス基板のライン検討が進み、具体的には、第四世代（ $680 \times 880$ 、 $730 \times 920$ ）、第五世代（ $1000 \times 1200$ ）以降にまで変遷が進行している。

【非特許文献1】T. Shimoda, Ink-jet Technology for Fabrication Processes of Flat Panel Displays, SID 03 DIGEST, p1178 - p1181

【発明の開示】

【発明が解決しようとする課題】

【0005】

上記の実情を鑑み、本発明は、液滴吐出法で形成する組成物が帯電する現象に起因した静電破壊を防止する表示装置の作製方法の提供を課題とする。また、密着性、耐剥離性を向上させ、なおかつ組成物が付着する薄膜の損傷や破壊を防止する配線基板の作製方法の提供を課題とする。さらに本発明は、一辺が一メートル以上の大型基板に容易に適用することができる半導体装置の作製方法の提供を課題とする。

【課題を解決するための手段】

【0006】

上述した従来技術の課題を解決するために、本発明においては以下の手段を講じる。

【0007】

本発明の表示装置の作製方法は、基板上に半導体素子を複数含む画素領域及び保護回路を形成するステップ、前記基板上又は前記保護回路と接続されたテープにドライバICを実装するステップを有し、前記半導体素子のチャネル部として、非晶質半導体又はセミアモルファス半導体を形成する点を特徴とする。上記特徴により、結晶化の工程が必要ないため、基板の一辺が一メートル以上の大型基板への適用が容易であり、従って、10インチから50インチ程度の大型の表示画面を有する電子機器への適用が有用である。また、前記半導体素子が含む導電層は、導電性材料を含む組成物を吐出して形成する点を特徴とする。上記特徴により、材料の利用効率の向上、作製時間の短縮及び作製費用の低減を実

10

20

30

40

50

現する。さらに、前記保護回路として、高電位電源に接続された第1の電源線と低電位電源に接続された第2の電源線との間に配置されたクランプ回路を形成する点を特徴とする。上記特徴により、液滴吐出法で形成する組成物が帯電する現象に起因した静電破壊を防止する。

#### 【0008】

本発明の配線基板の作製方法は、プラズマCVD法により、珪素の酸化物又は窒化物からなる下地層を形成するステップ、前記下地層上に、導電性材料を含む組成物を吐出して、導電層を形成するステップを有することを特徴とする。下地層を形成したままだと、後に作成する素子や配線がショートする場合には、前記導電層をマスクとして、前記下地層をエッチングするステップを有することを特徴とする。また、前記組成物は、銀、金、銅又はインジウム錫酸化物を含むことを特徴とする。10

#### 【0009】

本発明は、非晶質半導体層（アモルファスシリコン、a-Si）を用いた、半導体装置の作製方法を提供することを特徴とする。非晶質半導体層は、プラズマCVD法やスパッタリング法等の公知の方法により作製する。

#### 【0010】

また本発明は、非晶質半導体の中に結晶粒が分散するように存在しているセミアモルファス半導体層（以下SASと表記）を用いた、半導体装置の作製方法を提供することを特徴とする。SASを用いたトランジスタは、その移動度が $2 \sim 10 \text{ cm}^2 / \text{V} \cdot \text{sec}$ と、非晶質半導体層を用いたトランジスタの $2 \sim 20$ 倍の電界効果移動度を有する。従って、駆動回路の一部または全体を、画素部と同じ基板上に一体形成することができる。つまり、システムオンパネル化を実現した表示装置の作製方法を提供することができる。20

#### 【0011】

SASは、非晶質と結晶構造（単結晶、多結晶を含む）の中間的な構造の半導体層である。この半導体層は、自由エネルギー的に安定な第3の状態を有する半導体層であって、短距離秩序を持ち格子歪みを有する結晶質なものであり、その粒径を $0.5 \sim 20 \text{ nm}$ として非単結晶半導体層中に分散させて存在せしめることができる。また、未結合手（ダンギングボンド）の中和剤として水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。さらに、ヘリウム、アルゴン、クリプトン、ネオンなどの希ガス元素を含ませて格子歪みをさらに助長させることで安定性が増し良好なSASが得られる。30

このようなSASに関する記述は、例えば、特許3065528号公報で開示されている。

#### 【0012】

また、SASは、価電子制御を目的とした不純物元素を意図的に添加しないときに弱いN型の電気伝導性を示す。これは、SAS中に含まれる不純物によるもので、代表的には酸素がN型の伝導性を付与するものとして考えられている。SASに含まれる酸素は、成膜時の高周波電力密度に応じても変化する。本発明においては、SASの酸素濃度は $5 \times 10^{19} \text{ atoms/cm}^3$ 以下、好ましくは $1 \times 10^{19} \text{ atoms/cm}^3$ 以下とすることが望ましい。勿論、この酸素の全てがドナーとして機能する訳ではないので、導電型を制御するには、それに応じた量の不純物元素を添加することとなる。40

#### 【0013】

ここで、トランジスタのチャネル形成領域を設けるSASに対しては、P型を付与する不純物元素を、この成膜と同時に、或いは成膜後に添加することで、しきい値制御することが可能となる。P型を付与する不純物元素としては、代表的には硼素であり、B<sub>2</sub>H<sub>6</sub>、BF<sub>3</sub>などの不純物気体を $1 \text{ ppm} \sim 1000 \text{ ppm}$ の割合で珪化物気体に混入させると良い。そしてボロンの濃度を $1 \times 10^{14} \sim 6 \times 10^{16} \text{ atoms/cm}^3$ とすると良い。

#### 【0014】

上記のSASは、多結晶半導体層と異なり、SASとして直接基板上に成膜することができる。具体的には、SiH<sub>4</sub>をH<sub>2</sub>で流量比 $2 \sim 1000$ 倍、好ましくは $10 \sim 100$ 倍50

に希釈して、プラズマCVD法を用いて成膜することができる。上記方法を用いて作製されたSASは、0.5nm～20nmの結晶粒を非晶質半導体層中に含む微結晶半導体層も含んでいる。よって、多結晶半導体層を用いる場合と異なり、半導体層の成膜後に結晶化の工程を設ける必要がない。そして、レーザ光を用いた結晶化のように、レーザビームの長軸の長さに限界があるために、基板の寸法に制限が生じるようなことがない。つまり、第5世代以降の基板上にも簡単に作製することができる。また、トランジスタの作製における工程数を削減することができ、その分、表示装置の歩留まりを高め、コストを抑えることができる。

なお本発明では、SASは、少なくともチャネル形成領域に用いていれば良い。またチャネル形成領域は、その膜厚方向において全てセミアモルファス半導体層である必要はなく、少なくとも一部にセミアモルファス半導体層を含んでいれば良い。10

#### 【0015】

非晶質半導体層又はセミアモルファス半導体を用いた半導体装置の作製方法を提供する本発明は、結晶化の工程が必要ないため、基板の一辺が一メートル以上の大型基板への適用が容易であり、従って、10インチから50インチ程度の大型の表示画面を有する電子機器への適用が有用である。

#### 【0016】

本発明の半導体装置の作製方法は、絶縁表面を有する基板上に、液滴吐出法でゲート電極を形成する第1の段階と、前記ゲート電極上に、ゲート絶縁層、半導体層、絶縁層を積層形成する第2の段階と、前記ゲート電極と重なる位置に、液滴吐出法で第1のマスクを形成する第3の段階と、前記第1のマスクにより、前記絶縁層をエッチングしてチャネル保護層を形成する第4の段階と、一導電型の不純物を含有する半導体層を形成する第5の段階と、前記ゲート電極を含む領域に、液滴吐出法で第2のマスクを形成する第6の段階と、前記第2のマスクにより、前記一導電型の不純物を含有する半導体層と、前記半導体層とをエッチングする第7の段階と、液滴吐出法でソース及びドレイン配線を形成する第8の段階と、前記ソース及びドレイン配線により、前記チャネル保護層上の前記一導電型の不純物を含有する半導体層をエッチングする第9の段階の各段階を含むことを特徴とする。20

#### 【0017】

本発明の半導体装置の作製方法は、絶縁表面を有する基板上に、液滴吐出法でゲート電極と、接続配線を形成する第1の段階と、前記ゲート電極上に、ゲート絶縁層、半導体層、絶縁層を積層形成する第2の段階と、前記ゲート電極と重なる位置に、液滴吐出法で第1のマスクを形成する第3の段階と、前記第1のマスクにより、前記絶縁層をエッチングしてチャネル保護層を形成する第4の段階と、一導電型の不純物を含有する半導体層を形成する第5の段階と、前記ゲート電極を含む領域に、液滴吐出法で第2のマスクを形成する第6の段階と、前記一導電型の不純物を含有する半導体層と、前記半導体層とをエッチングする第7の段階と、前記ゲート絶縁層を選択的にエッチングして、前記接続配線を露出させる第8の段階と、液滴吐出法で、ソース及びドレイン配線を形成すると共に、少なくとも一方の配線を前記接続配線と接続する第9の段階と、前記ソース及びドレイン配線により、前記チャネル保護層上の前記一導電型の不純物を含有する半導体層をエッチングする第10の段階の各段階を含むことを特徴とする。30

#### 【発明の効果】

#### 【0018】

上記構成を有する本発明は、液滴吐出法で形成する組成物が帯電する現象に起因した静電破壊を防止する表示装置の作製方法を提供することができる。密着性、耐剥離性を向上させ、なおかつ組成物が付着する薄膜の損傷や破壊を防止する配線基板の作製方法を提供することができる。一辺が一メートル以上の大型基板に容易に適用することができる半導体装置の作製方法を提供することができる。

#### 【発明を実施するための最良の形態】

#### 【0019】

10

20

30

40

50

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いる。

(実施の形態 1)

【0020】

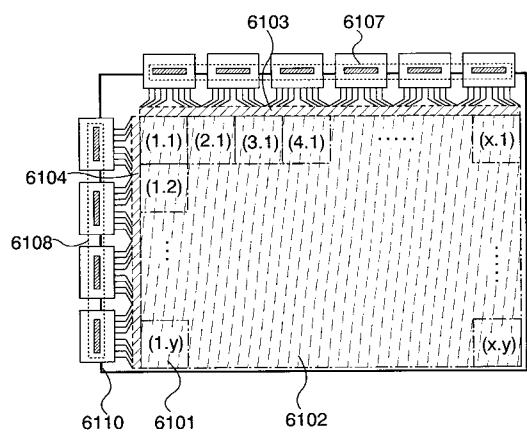

本発明の実施の形態について、図面を用いて説明する。本発明の表示装置の作製方法は、基板 6110 上に、半導体素子を複数含む画素領域（表示領域ともよばれる）6102 及び保護回路 6103、6104 を形成するステップ、保護回路 6103、6104 に接続されたテープにドライバIC 6107、6108 を実装するステップを有する（図3参照）。なお、図示する表示装置では、TAB方式が採用されているが、COG方式を採用してもよく、その場合には、基板 6110 上にドライバIC 6107、6108 を実装するステップを有する。画素領域 6102 には、複数の画素 6101 がマトリクス状に配置されるように形成する。また、画素領域 6102 と保護回路 6103、6104 には複数の半導体素子を形成する。

【0021】

なお、本実施の形態において説明する本発明の表示装置は、複数の半導体素子を含むため半導体装置ともよぶ。

【0022】

本発明は、半導体素子のチャネル部として、非晶質半導体又はセミアモルファス半導体を形成する点を特徴とする。上記特徴により、結晶化の工程が必要ないため、基板の一辺が一メートル以上の大型基板への適用が容易であり、従って、10インチから50インチ程度の大型の表示画面を有する電子機器への適用が有用である。また本発明は、前記半導体素子が含むゲート電極やソース・ドレイン配線等の導電層として、液滴吐出法により、導電性材料を含む組成物を吐出して形成することを特徴とする。上記特徴により、材料の利用効率の向上、作製時間の短縮及び作製費用の低減を実現する。なお、半導体素子が含む導電層に限らず、該半導体素子の活性層をパターニングする際のマスクや、該半導体素子に電気的に接続される表示素子の両電極等も、全て液滴吐出法により形成してもよい。さらに本発明は、前記保護回路 6103、6104 として、高電位電源（以下 VDD と表記）に接続された第1の電源線と、低電位電源（以下 VSS と表記）に接続された第2の電源線との間に配置されたクランプ回路を形成することを特徴とする。上記特徴により、液滴吐出法で形成する組成物が帯電する現象に起因した静電破壊を防止する。

【0023】

なお、半導体素子のチャネル部として、セミアモルファス半導体を形成する場合、走査線側の駆動回路も基板 6110 上に作り込み、信号線側にのみドライバIC 6107 を実装するとよい。これは、セミアモルファス半導体を活性層としたトランジスタは、その特性が非晶質半導体層を活性層としたトランジスタよりも良好であり、走査線側の駆動回路ならば構成可能であるからである。また、上記とは別の構成として、半導体素子のチャネル部として、セミアモルファス半導体を用いる場合、走査線側及び信号線側の駆動回路の一部を同一基板上に作り込み、一部をドライバIC で代用した構成でもよい。つまり、ドライバIC を実装するにあたり、その構成は様々であり、本発明はいずれの構成を用いてもよい。

【0024】

保護回路 6103、6104 は、画素領域 6102 とドライバIC 6107、6108 の間にのみ形成しているが、画素領域 6102 の内部、画素 6101 の内部に形成してもよい。また、基板 6110 上に走査線駆動回路を作り込む場合は、走査線駆動回路の内部に形成してもよいし、走査線駆動回路と画素領域 6102 の間に形成してもよい。

【0025】

続いて、保護回路 6103、6104 の構成について説明する。上述したように、前記

10

20

30

40

50

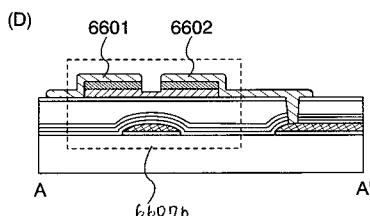

保護回路 6103、6104 は、VDD に接続された第 1 の電源線 6601 と、VSS に接続された第 2 の電源線 6602 の間にクランプ回路 6604 を有することを特徴とする（図 1（A）参照）。また、両電源線 6601、6602 の間には、画素領域 6102 等に相当する回路 6603、直列に接続されたダイオード 6605、6606 が設けられる。回路 6603 には、信号線 6607a を介して、信号が入力される。クランプ回路 6604 を配置する本発明は、静電気が発生しても、電流が流れる経路を増やすことができるため、開放されたノードの電位の急激な変動を防止して、回路 6603 の損傷や破壊を防止する。クランプ回路 6604 は、薄膜トランジスタ、容量素子及び抵抗素子から選択された一種又は複数種によって構成される。以下には、その構成について説明する。

## 【0026】

10

まず、クランプ回路 6604 として、ゲート電極とソース電極が接続されたトランジスタ 6607b を用いる場合について説明する（図 1（B）参照）。通常の状態では、トランジスタ 6607b は、そのゲート・ソース間電圧がゼロであるため、オフ状態にある。一方、静電気が発生して電荷が加えられると、トランジスタ 6607b はブレイクダウンして、オン状態になり、そのソース・ドレイン間に電流が流れる。このように、静電気が発生しても、クランプ回路 6604 の配置によって、電流が流れる経路が増えるため、電位の急激な変動を防止して、回路 6603 の損傷や破壊を防止する。図 1（C）は、クランプ回路 6604 として用いるトランジスタ 6607b のレイアウトであり、図 1（D）はレイアウトの A - A' における断面構造を示す。なお、トランジスタ 6607b の詳しい作製方法については、実施の形態 3 において説明するので、そちらを参考にするとよい。

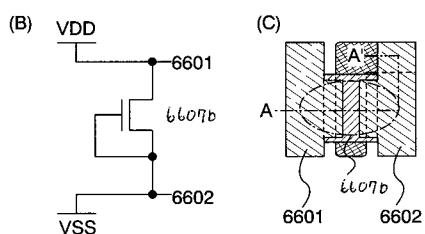

## 【0027】

20

次に、クランプ回路 6604 として、トランジスタ 6612、容量素子 6613 及び抵抗素子 6614 を用いる場合について説明する（図 2（A）参照）。通常の状態では、トランジスタ 6612 は、ゲート電極とソース電極の間に抵抗素子 6614 が接続されているため、オフ状態にある。一方、静電気が発生して電荷が加えられると、容量素子 6613 と抵抗素子 6614 に電流が流れる。そうすると、容量素子 6613 と抵抗素子 6614 の接点にゲート電極が接続されたトランジスタ 6612 はオン状態になって、そのソース・ドレイン間に電流が流れる。このように、静電気が発生しても、クランプ回路 6604 の配置によって、電流が流れる経路が増えるため、電位の急激な変動を防止して、回路 6603 の損傷や破壊を防止する。図 2（B）は、クランプ回路 6604 として用いるトランジスタ 6612、容量素子 6613 及び抵抗素子 6614 のレイアウトであり、図 2（C）はレイアウトの A - A'、B - B' における断面構造を示す。なお、トランジスタ 6612 の詳しい作製方法については、実施の形態 3 において説明するのでそちらを参考にするとよい。

30

図 2（C）では、抵抗素子 6614 を構成する導電層は、表示素子の画素電極と同じレイヤーで形成しているが、トランジスタ 6612 のゲート電極と同じレイヤーの導電層で形成してもよい。その場合、所望の抵抗値になるように、用いるノズルの吐出口を変えて、抵抗素子 6614 を構成する導電層のみ細く形成したり、ノズル又は基板の走査を工夫することで、抵抗素子 6614 を構成する導電層のみ、凹凸を有する形状に形成したりするよ。

40

## 【0028】

最後に、クランプ回路 6604 として、トランジスタ群 6608 を用いる場合について説明する（図 2（D）参照）。トランジスタ群 6608 は、n 個のトランジスタから構成され、各々のトランジスタのゲート電極とドレイン電極は接続されている。n は（VDD - VSS）<（Vth \* n）を満足する自然数であり、Vth は、トランジスタ群 6608 を構成するトランジスタのしきい値電圧である。なお、トランジスタ群 6608 を構成する複数のトランジスタの各々のしきい値電圧が大幅に異なる場合には、Vth は複数のトランジスタのしきい値電圧の平均値とするとよい。トランジスタ群 6608 は、通常の状態では非導通状態にある。一方、静電気が発生して、（VDD - VSS）>（Vth \*

50

n)を満たすようになると、トランジスタ群6608は導通状態になり、電流が流れる。このように、静電気が発生しても、クランプ回路6604の配置によって、電流が流れる経路が増えるため、電位の急激な変動を防止して、回路6603の損傷や破壊を防止する。上記のいずれかの構成を有する本発明は、液滴吐出法で形成する組成物が帯電する現象に起因した静電破壊を防止する表示装置の作製方法を提供することができる。

#### (実施の形態2)

##### 【0029】

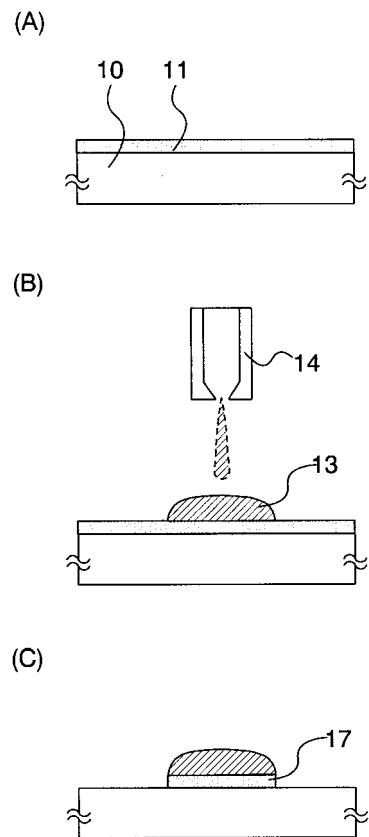

本発明の実施の形態について、図4を用いて説明する。バリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラス等からなるガラス基板、石英基板、シリコン基板、金属基板、ステンレス基板又は本作製工程の処理温度に耐えうる耐熱性を有するプラスチック基板等の基板10上に、下地層11を形成する(図4(A)参照)。下地層11は、CVD法により、半導体層と絶縁層の一方又は両方を単層又は積層して形成する。半導体層としては珪素からなる層を形成し、絶縁層としては珪素の酸化物又は窒化物からなる層を形成する。本発明は下地層11をCVD法により形成することを特徴とする。CVD法において用いるCVD装置は、スパッタリング装置と比較して、ターゲット交換の必要が無く、装置の管理が簡単であるという点、また、スパッタリング装置は、セルフクリーニングができない反面、CVD装置は、NF<sub>3</sub>などのガスを供給すれば、チャンバ内のクリーニングが簡単に行えるため、メンテナンス作業が少なくて済むという優位点を有する。

##### 【0030】

続いて、下地層11上に、導電性材料を含む組成物を吐出して、導電層13を形成する(図4(B)参照)。導電層13の形成は、液滴吐出手段14を用いて行う。液滴吐出手段14とは、組成物の吐出口を有するノズルや、1つ又は複数のノズルを具備したヘッド等の液滴を吐出する手段を有するものの総称とする。液滴吐出法において用いるノズルの径は、0.02~100μm(好適には30μm以下)に設定し、該ノズルから吐出される組成物の吐出量は0.001p1~100p1(好適には10p1以下)に設定する。液滴吐出法には、オンデマンド型とコンティニュアス型の2つの方式があるが、どちらの方式を用いてもよい。さらに液滴吐出法において用いるノズルには、圧電体の電圧印加により変形する性質を利用した圧電方式、ノズル内に設けられたヒータにより組成物を沸騰させ該組成物を吐出する加熱方式があるが、どちらの方式を用いてもよい。

##### 【0031】

被処理物とノズルの吐出口との距離は、所望の箇所に滴下するために、出来る限り近づけておくことが好ましく、0.1~3mm(好ましくは1mm以下)程度に設定する。ノズルと被処理物は、その相対的な距離を保ちながら、ノズル及び被処理物の一方が移動することで、所望のパターンを描画する。なお、ノズル及び被処理物は進行方向に対して両方とも平行でなくともよく、ノズル及び被処理物の一方を進行方向に対して任意の角度に回転させてもよい。また、組成物を吐出する前に、被処理物の表面にプラズマ処理を施してもよい。これは、プラズマ処理を施すと、被処理物の表面が親水性になったり、疎水性になったりすることを活用するためである。例えば、純水に対しては親水性になり、アルコールを溶媒したペーストに対しては疎水性になる。

##### 【0032】

吐出口から吐出する組成物は、導電性材料を溶媒に溶解又は分散させたものを用いる。導電性材料とは、Ag(銀)、Au(金)、Cu(銅)、W(タンゲステン)、Al(アルミニウム)等の金属、透光性を有するインジウム錫酸化物(ITO)、インジウム錫酸化物と酸化珪素からなるITO等に相当する。但し、吐出口から吐出する組成物は、比抵抗値を考慮して、金、銀、銅のいずれかの材料を用いることが好ましく、さらに好ましくは、低抵抗な銀、銅を用いるとよい。但し、銀、銅を用いる場合には、不純物対策のため、合わせてバリア膜を設けるとよい。溶媒は、酢酸ブチル等のエスチル類、イソプロピルアルコール等のアルコール類、アセトン等の有機溶剤等に相当する。表面張力と粘度は、溶媒の濃度を調整したり、界面活性剤等を加えたりして適宜調整し、表面張力は40mN/m以下、粘度は50mPa·s以下、好ましくは5~20mPa·sに設定する。

10

20

30

40

50

## 【0033】

組成物を吐出する工程は、減圧下で行うことが好適であり、これは、組成物を吐出して被処理物に着弾するまでの間に、該組成物の溶媒が揮発し、後の乾燥と焼成の工程を省略又は短くすることができるためである。組成物の吐出後は、常圧下又は減圧下で、レーザ光の照射や瞬間熱アニール、加熱炉等により、乾燥と焼成の一方又は両方の工程を行う。乾燥と焼成の工程は、両工程とも加熱処理の工程であるが、例えば、乾燥は100度で3分間、焼成は200～350度で15分間～120分間で行うもので、その目的、温度と時間が異なるものである。乾燥と焼成の工程を良好に行うためには、基板を加熱しておいてもよく、そのときの温度は、基板等の材質に依存するが、100～800度（好ましくは200～350度）とする。本工程により、組成物中の溶媒を揮発させたり、分散剤を除去したりして、周囲の樹脂が硬化収縮させ、融合と融着を加速する。雰囲気は、酸素雰囲気、窒素雰囲気又は空気で行い、特に制約はないが、好ましくは、金属元素を分解又は分散している溶媒が除去されやすい酸素雰囲気下で行う。

## 【0034】

レーザ光の照射は、連続発振またはパルス発振の気体レーザ又は固体レーザを用いれば良い。前者の気体レーザとしては、エキシマレーザ、YAGレーザ等が挙げられ、後者の固体レーザとしては、Cr、Nd等がドーピングされたYAG、YVO<sub>4</sub>等の結晶を使ったレーザ等が挙げられる。なお、レーザ光の吸収率の関係から、連続発振のレーザを用いることが好ましい。また、パルス発振と連続発振を組み合わせたハイブリッドのレーザ照射方法を用いてもよい。但し、基板の耐熱性に依っては、レーザ光の照射による加熱処理は、数マイクロ秒から数十秒の間で瞬間に行うとよい。瞬間熱アニール（RTA）は、不活性ガスの雰囲気下で、紫外光乃至赤外光を照射する赤外ランプやハロゲンランプなどを用いて、急激に温度を上昇させ、数マイクロ秒から数分の間で瞬間的に熱を加えて行う。この処理は瞬間的に行うために、実質的に最表面の薄膜のみを加熱することができ、下層の膜には影響を与えない。つまり、プラスチック基板等の耐熱性が弱い基板にも影響を与えない。

## 【0035】

液滴吐出手段14から組成物を吐出する際には、電荷の偏りが生じるために、組成物が正に帯電する傾向があり、この帯電した電荷によって、下層の薄膜の損傷や破壊が生じる可能性がある。しかしながら、導電層13の形成前に下地層11を形成する本発明は、そのような損傷や破壊を防止する。

## 【0036】

上記工程を経て、下地層11と導電層13が完成する。なお、下地層11として半導体層を形成した場合、そのままだと後に作製する素子や配線がショートする可能性がある。そのような可能性がある場合には、導電層13をマスクとして、下地層11をエッチングして、下地層17を形成する（図4（C）参照）。

## 【0037】

上記のように形成された導電層は配線として用いてもよいし、導電層13をゲート電極、下地層11をゲート絶縁膜として、薄膜トランジスタの一構成要素として用いてもよい。また、図示しないが、上記の工程を経て完成した導電層を覆うように保護膜を形成してもよい。このような保護膜は、バリア性を有する材料を用いて形成し、具体的には、緻密な膜質を有する窒化珪素膜を形成するとよい。

## 【0038】

上記のように、液滴吐出法で導電層13を形成する前に、下地層11を形成する本発明は、密着性、耐剥離性を向上させ、なおかつ下層の薄膜の損傷や破壊を防止した配線基板の作製方法を提供することができる。

## (実施の形態3)

## 【0039】

本発明の実施の形態として、チャネル保護型の薄膜トランジスタの作製方法、前記薄膜トランジスタを用いた表示装置の作製方法について、図面を用いて説明する。ガラス基板

10

20

30

40

50

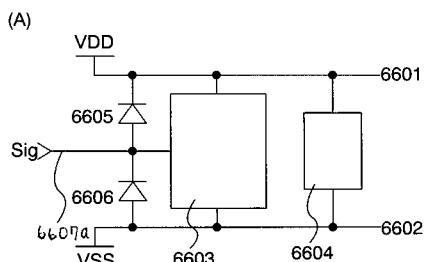

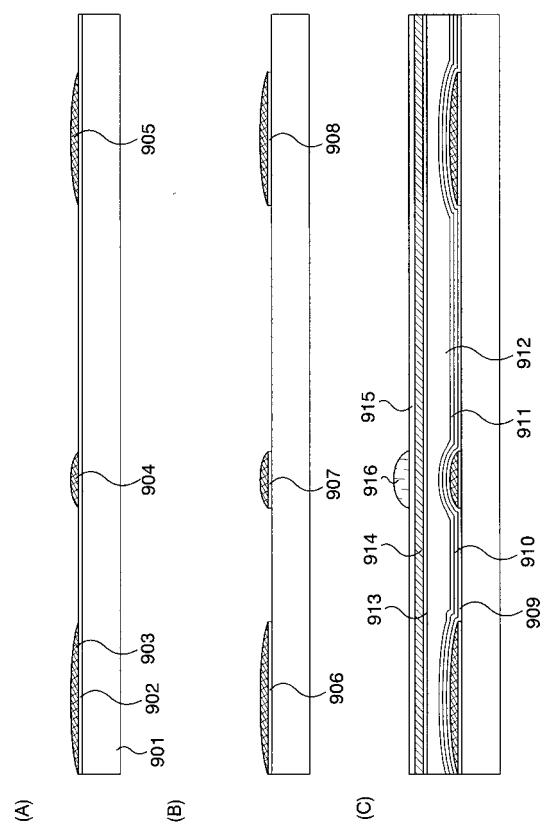

や石英基板等の基板 901 上に、下地層 902 を形成する（図 5（A）参照）。下地層 902 は、CVD 法により、半導体層と絶縁層の一方又は両方を単層又は積層して形成する。半導体層は、珪化物気体を用いて、珪素からなる層を形成する。絶縁層は、珪化物気体と酸素又は窒素を用いて、珪素の酸化物又は窒化物からなる層を形成するか、珪化物気体を用いて、珪素からなる層を形成後に、酸化処理又は窒化処理を行って形成する。ここでは、下地層 902 として珪化物気体を用いて、珪素からなる層を形成する。続いて、下地層 902 上に、導電性材料を含む組成物を吐出して、導電体層 903～905 を形成する。

#### 【0040】

次に、導電体層 903～905 をマスクとして、下地層 902 をエッチングして、下地層 906～908 を形成する（図 5（B）参照）。実施の形態 2 において説明したように、下地層 902 として絶縁層を形成した場合には、本工程を省略してもよい。

10

#### 【0041】

次に、プラズマ CVD 法、スパッタリング法、グロー放電分解法等の公知の方法を用いて、ゲート絶縁膜として機能する絶縁層を単層又は積層構造で形成する（図 5（C）参照）。ここでは、窒化珪素からなる絶縁層 909、酸化珪素からなる絶縁層 910、窒化珪素からなる絶縁層 911、樹脂材料や化合物材料等からなる絶縁層 912、窒化珪素からなる絶縁層 913 の積層体がゲート絶縁膜に相当する。上記構成により、所望の絶縁耐圧が得られる程度にゲート絶縁膜を厚く形成することができ、さらにトランジスタを構成する活性層とゲート電極間の容量を適当な値にすることができる。低い成膜温度でゲートトリーク電流の少ない緻密な絶縁膜を形成するには、アルゴンなどの希ガス元素を反応ガスに含ませ、形成される絶縁膜中に混入させると良い。

20

導電体層 903～905 に接する絶縁層 909 は、バリア性が良好な窒化珪素層を用いることが好ましく、そうすると、導電体層 903～905 からの不純物元素の侵入を防止することができる。窒化珪素層は、スパッタリング法やグロー放電分解法で形成可能であるが、大気中に浮遊する有機物や金属物、水蒸気などの汚染不純物の侵入を防ぐためのものであり、緻密な膜であることが要求される。この目的において、珪素をターゲットとして、珪素とアルゴンなどの希ガス元素を混合させたスパッタガスで高周波スパッタリングされた窒化珪素膜で、膜中の希ガス元素を含めることにより緻密化が促進されることとなる。また、グロー放電分解法においても、珪化物気体をアルゴンなどの不活性元素で 100 倍～500 倍に希釈して形成された窒化珪素膜は、100 度以下の低温において形成されたとしても膜質は緻密である。なお、必要があれば絶縁膜をさらに積層して形成してもよい。

30

#### 【0042】

絶縁層 912 は、エポキシ樹脂、アクリル樹脂、フェノール樹脂、ノボラック樹脂、メラミン樹脂、ウレタン樹脂等、透過性を有するポリイミド樹脂等の樹脂材料、シロキサン系ポリマー等の重合によってできた化合物材料、水溶性ホモポリマーと水溶性共重合体を含む材料を用いて、スピンドルコート法やディップ法、液滴吐出法により形成する。好ましくは液滴吐出法で形成し、そうすると、他の方法と比較して、材料の利用効率が格段に向上升る。絶縁層 912 として有機樹脂を用いる場合、図示するように、上層にバリア性が良好な窒化珪素からなる絶縁層 913 を形成すると、絶縁層 912 からの脱ガスを防止することができる。

40

#### 【0043】

続いて、絶縁層 913 上に、半導体層 914 を形成する。半導体層 914 は、非晶質構造又は非晶質と結晶構造（単結晶、多結晶を含む）の中間的な構造を有する。非晶質半導体層（アモルファスシリコン、a-Si）は、プラズマ CVD 法、スパッタリング法等の公知の方法により形成する。一方、非晶質と結晶構造の中間的な構造を有する半導体層は、自由エネルギー的に安定な第 3 の状態を有する半導体層であって、短距離秩序を持ち格子歪みを有する結晶質なものであり、その粒径を 0.5～20 nm として非単結晶半導体層中に分散させて存在せしめることが可能である。また、未結合手（ダンギングボンド

50

)の中和剤として水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。ここでは、このような半導体層をセミアモルファス半導体層(以下、SASと表記)と呼ぶ。SASは、ヘリウム、アルゴン、クリプトン、ネオンなどの希ガス元素を含ませて格子歪みをさらに助長させることで安定性が増す。

SASは珪化物気体をグロー放電分解することにより得ることができる。代表的な珪化物気体としては、SiH<sub>4</sub>であり、その他にもSi<sub>2</sub>H<sub>6</sub>、SiH<sub>2</sub>Cl<sub>2</sub>、SiHCl<sub>3</sub>、SiCl<sub>4</sub>、SiF<sub>4</sub>などを用いることができる。これら珪化物気体を水素、水素とヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または複数種の希ガス元素で希釈して用いることでSASの形成を容易なものとすることができます。希釈率は10倍～1000倍の範囲で珪化物気体を希釈する。また、Si<sub>2</sub>H<sub>6</sub>とGeF<sub>4</sub>のガス流量比をSi<sub>2</sub>H<sub>6</sub>:GeF<sub>4</sub>=20～40:0.9の範囲の条件下で形成すると、Siの組成比が80%以上である薄膜を得ることができる。勿論、グロー放電分解による被膜の反応生成は減圧下で行うが、圧力は概略0.1Pa～133Paの範囲で行えば良い。グロー放電を形成するための電源周波数は1MHz～120MHz、好ましくは13MHz～60MHzである。高周波電力は適宜設定すれば良い。基板加熱温度は300度以下が好ましく、100～200度の基板加熱温度が推奨される。また、珪化物気体中に、CH<sub>4</sub>、C<sub>2</sub>H<sub>6</sub>などの炭化物気体、GeH<sub>4</sub>、GeF<sub>4</sub>などのゲルマニウム化気体を混入させて、エネルギー bandwidth幅を1.5～2.4eV、若しくは0.9～1.1eVに調節しても良い。また、SASは、価電子制御を目的とした不純物元素を意図的に添加しないときに弱いN型の電気伝導性を示す。これは、SAS中に含まれる不純物によるもので、代表的には酸素がN型の伝導性を付与するものとして考えられている。SASに含まれる酸素は、成膜時の高周波電力密度に応じても変化する。次に、半導体層914上に、プラズマCVD法等の公知の方法で、珪素の酸化物又は窒化物からなる絶縁層915を形成する。10

以上、絶縁層909から絶縁層915までは大気に触れさせることなく連続して形成することが可能である。すなわち、大気成分や大気中に浮遊する汚染不純物元素に汚染されることなく各積層界面を形成することができるので、トランジスタの特性のばらつきを低減することができる。

#### 【0044】

次に、絶縁層915上に、組成物を選択的に吐出して、マスクとなる絶縁層916を形成する。このときに用いる組成物材料には、樹脂材料や化合物材料、感光剤を含む市販のレジスト材料を用いる。レジスト材料は、例えば、代表的なポジ型レジストである、ノボラック樹脂と感光剤であるナフトキノンジアジド化合物、ネガ型レジストであるベース樹脂、ジフェニルシランジオール及び酸発生剤などを用いる。いずれの材料を用いるとしても、その表面張力と粘度は、溶媒の濃度を調整したり、界面活性剤等を加えたりして適宜調整する。30

#### 【0045】

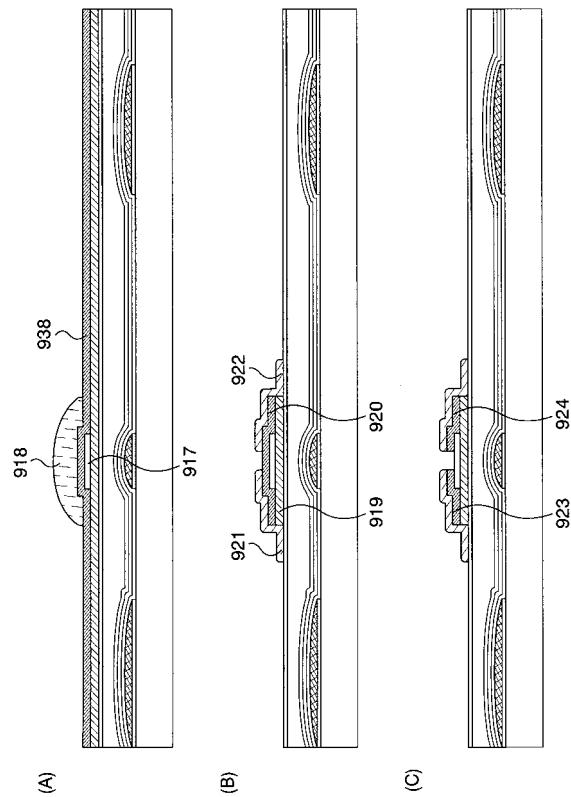

次に、絶縁層916をマスクとして、絶縁層915をエッチングして、チャネル保護層として機能する絶縁層917を形成する(図6(A)参照)。続いて、絶縁層916を除去後、半導体層914及び絶縁層917上に、一導電型が付与された半導体層938を形成する。一導電型が付与された半導体層938は、シランガスとフォスフィンガスを用いて形成したり、CVD法により半導体層を形成後に、ドーピング法により不純物元素を添加して形成したりする。次に、半導体層938上に、組成物を選択的に吐出して、絶縁層918を形成する。次に、絶縁層918をマスクとして、半導体層914及び一導電型が付与された半導体層938を同時にエッチングして、半導体層919と一導電型を有する半導体層920を形成する(図6(B)参照)。続いて、絶縁層918を除去後、導電性材料を含む組成物を選択的に吐出して、ソース配線及びドレイン配線として機能する導電層921、922を形成する。次に、導電層921、922をマスクとして、一導電型が付与された半導体層920をエッチングして、半導体層923、924を形成する(図6(C)参照)。40

#### 【0046】

50

20

30

40

50

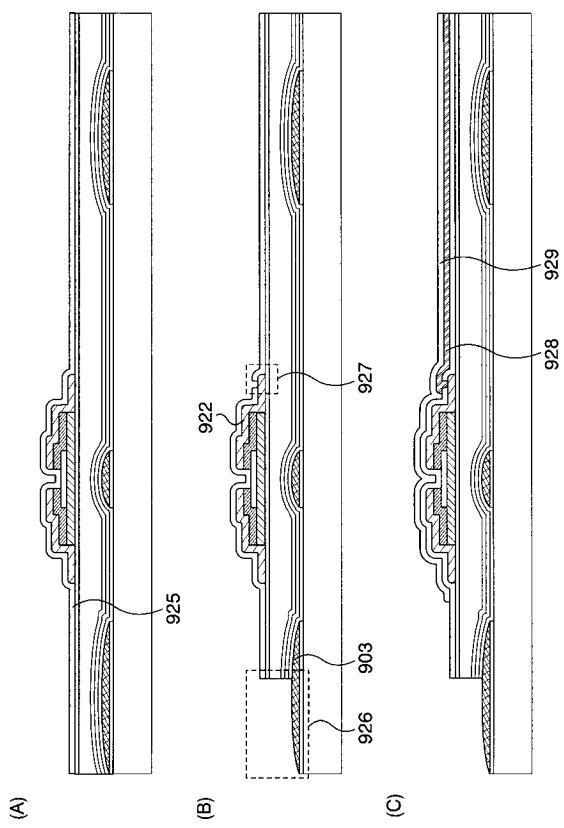

続いて、全面に絶縁層 925 を形成する（図 7（A）参照）。その後、導電体層 903、922 が露出するように、開口部 926、927 を形成する（図 7（B）参照）。開口部 926、927 は、大気圧放電によるエッティングや液滴吐出法、通常のフォトリソグラフィ法を用いて形成する。次に、導電層 922 と電気的に接続するように、導電性材料を含む組成物を選択的に吐出して、画素電極に相当する導電層 928 を形成する（図 7（C）参照）。なお図 4 では、導電層 928 を透光性材料で形成し、透過型の液晶表示装置を作製する例を示すが、光の反射率が高い導電材料を用いることで、反射型の液晶表示装置を作製してもよい。続いて、導電層 928 を覆うように、印刷法、スピンドルコート法、液滴吐出法等の方法により、配向膜として機能する絶縁層 929 を形成する。絶縁層 929 は、スクリーン印刷法や液滴吐出法を用いれば、図示するように、選択的に形成することができる。

10

#### 【0047】

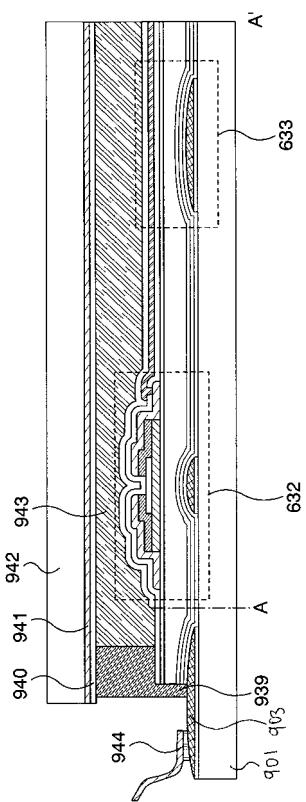

次に、シール材 939 を形成する（図 8 参照）。その後、配向膜として機能する絶縁層 940、対向電極として機能する導電層 941 が設けられた基板 942 と、基板 901 とをシール材 939 により貼り合わせ、その後、液晶 943 を注入する。なお、シール材 939 にはフィラーが混入されていても良く、また基板 942 には、カラーフィルタや、ディスクリネーションを防ぐための遮蔽膜（ブラックマトリクス）などが形成されていても良い。さらに、上述していないが、配向膜のラビング処理やスペーサの散布処理、偏光板を貼る処理等の適宜必要な処理は、必要なタイミングで行う。液晶 943 は、毛細管現象を利用した液晶注入だけでなく、ディスペンサ式（滴下式）を用いて形成してもよい。最後に、異方性導電層を介して、導電体層 903 と電気的に接続するように、接続端子（接続フィルム、接続テープ、フィルム、テープともよぶ）944 を貼り付ける。接続端子 944 は、外部からの信号や電位を伝達する役目を担う。そうすると、スイッチング用トランジスタ 632、容量素子 633 を含む表示装置が完成する。なお、図 8 に示す断面構造は、図 10 に示すレイアウト図の A-A' における断面構造に相当する。

20

#### 【0048】

上記の作製工程では、チャネル保護層として機能する絶縁層 925 を全面に形成しているが、絶縁層 925 を形成せずに、ソース・ドレイン配線として機能する導電層 922 に、画素電極として機能する導電層を直接形成してもよい。以下には、絶縁層 925 を形成しない工程について説明する。

30

#### 【0049】

ソース・ドレイン配線として機能する導電層 922 に接するように、導電性材料を含む組成物を吐出して、画素電極として機能する導電層 930 を形成する（図 9（A）参照）。次に、印刷法や液滴吐出法等により、配向膜として機能する絶縁層 931 を形成する。続いて、シール材 932 を形成する（図 9（B）参照）。その後、配向膜として機能する絶縁層 933、対向電極として機能する導電層 934 が設けられた基板 935 と、基板 901 とをシール材 932 により貼り合わせ、その後、液晶 936 を注入する。なお、上述したように、液晶は、ディスペンサ方式等の他の方法を用いて形成してもよい。

#### 【0050】

次に、大気圧又は大気圧近傍下で、エッティング処理により領域 945 の絶縁層 909～913 を選択的に除去する（図 9（C）参照）。この処理は、酸素ガスと、水素、 $\text{CF}_4$ 、 $\text{NF}_3$ 、 $\text{H}_2\text{O}$ 、 $\text{CHF}_3$  等から選択された一つ又は複数を用いて行う。本工程では、静電気による損傷や破壊を防止するために、封止後に行っているが、静電気による影響が少ない場合には、どのタイミングで行っても構わない。続いて、異方性導電層を介して、導電体層 903 と電気的に接続するように、接続端子 944 を設ける。上記工程を経て、スイッチング用トランジスタ 632、容量素子 633 を含む表示装置が完成する。なお、図 9（C）に示す断面構造は、図 10 に示すレイアウト図の A-A' における断面構造に相当する。

40

#### 【0051】

上記の作製工程では、導電層の形成や半導体層のパターニングに用いるマスクを液滴吐

50

出法により形成する点を特徴とし、上記特徴により、工程の簡略化による作製時間の短縮や作製費用の低減を実現する。また、結晶化の工程が必要ないため、基板の一辺が一メートル以上の大型基板への適用が容易であり、従って、10インチから50インチ程度の大型の表示画面を有する電子機器への適用が有用である。

(実施の形態4)

【0052】

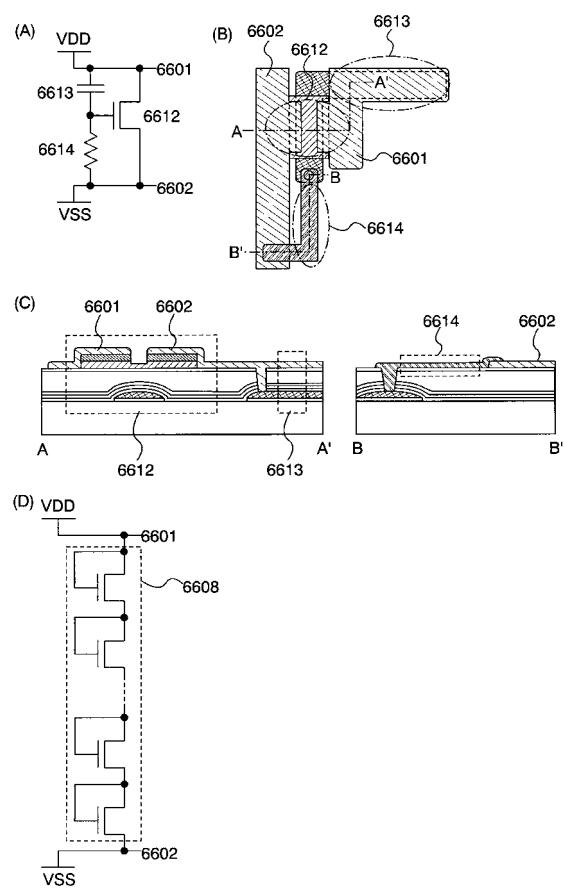

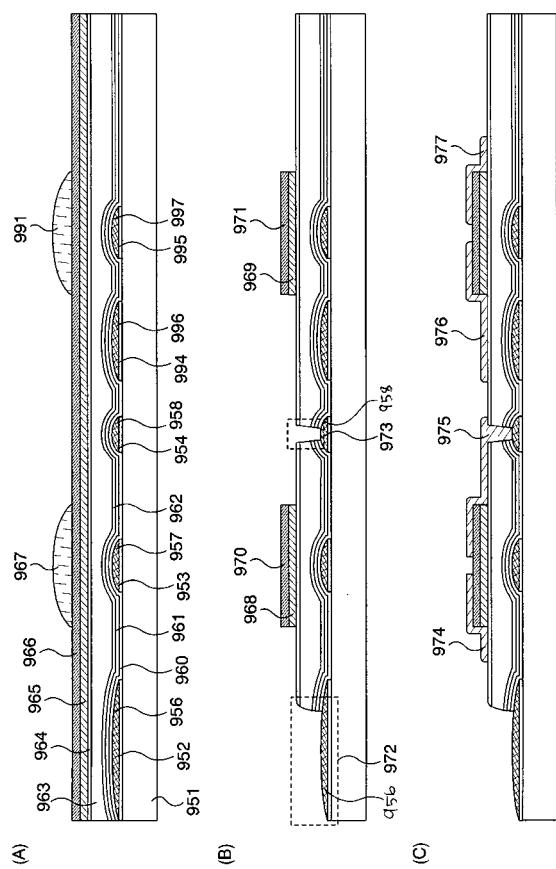

本発明の実施の形態として、チャネルエッチ型の薄膜トランジスタの作製方法、前記薄膜トランジスタを用いた表示装置の作製方法について図面を用いて説明する。ガラス基板、石英基板等の基板951上に、全面に下地層を形成する(図11(A)参照)。下地層は、CVD法により、半導体層と絶縁層の一方又は両方を単層又は積層して形成する。続いて、下地層上に、導電性材料を含む組成物を吐出して、ゲート電極、又は接続配線として機能する導電体層956～958、996、997を形成する。その後、導電体層956～958、996、997をマスクとして、下地層をエッティングして、下地層952～954、994、995を形成する。なお、実施の形態2において説明したように、下地層として絶縁層を形成した場合には、本工程を省略してもよい。次に、プラズマCVD法等の公知の方法を用いて、ゲート絶縁膜として機能する絶縁層を単層又は積層構造で形成する。ここでは、窒化珪素からなる絶縁層960、酸化珪素からなる絶縁層961、窒化珪素からなる絶縁層962、樹脂材料や化合物材料等からなる絶縁層963、窒化珪素からなる絶縁層964の積層体がゲート絶縁膜に相当する。

【0053】

続いて、絶縁層964上に、半導体層965を形成する。半導体層965は、非晶質構造又は非晶質と結晶構造(単結晶、多結晶を含む)の中間的な構造を有する。続いて、半導体層965上に、一導電型が付与された半導体層966を形成する。一導電型が付与された半導体層966は、シランガスとフォスフィンガスを用いて形成したり、CVD法により半導体層を形成後に、ドーピング法により不純物元素を添加して形成したりする。以上、絶縁層960から半導体層966までは大気に触れさせることなく連続して形成することが可能である。すなわち、大気成分や大気中に浮遊する汚染不純物元素に汚染されることなく各積層界面を形成することができる。トランジスタの特性のばらつきを低減することができる。次に、半導体層966上に、組成物を選択的に吐出して、マスクとして機能する絶縁層967、991を形成する。

【0054】

絶縁層967、991をマスクとして、半導体層965、966を同時にエッティングして、半導体層968、969と一導電型が付与された半導体層970、971を形成する(図11(B)参照)。次に、絶縁層967、991を除去後、大気圧放電を用いたエッティングや、液滴吐出法、フォトリソグラフィ法を用いて、導電体層956、958が露出するように、開口部972、973を形成する。次に、導電性材料を含む組成物を吐出して、ソース・ドレイン配線として機能する導電層974～977を形成する(図11(C)参照)。この際、導電層975は、開口部973が充填するように吐出する。

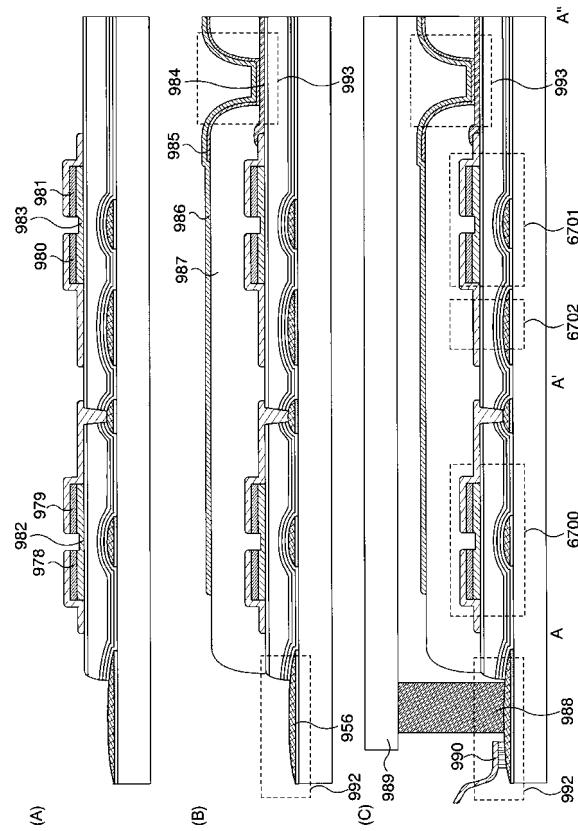

【0055】

次に、導電層974～977をマスクとして、一導電型が付与された半導体層970、971をエッティングして、半導体層978～981を形成する(図12(A)参照)。この際、図示するように、少しえッティングされた半導体層982、983が形成される。次に、導電性材料を含む組成物を選択的に吐出して、画素電極として機能する導電体層984を形成する(図12(B)参照)。次に、スピンドルコート法やディップ法を用いて、全面に絶縁層987を形成後、フォトリソグラフィ法や液滴吐出法等の公知の方法により開口部992、993を形成する。絶縁層987は、土手として機能するものであり、珪素を含む材料、アクリル等の有機材料、シロキサンポリマー等の化合物材料を用いて形成する。但し、アクリル、ポリイミド等の感光性、非感光性の材料を用いて形成すると、その側面は曲率半径が連続的に変化する形状となり、上層の薄膜が段切れせずに形成されるため好ましい。なお、有機材料を用いる場合には、脱ガス等の防止から、Ti等の金属膜、T

10

20

30

40

50

iN等の窒化膜、TiSi<sub>x</sub>等のシリサイド材料を用いて、単層又は積層構造のバリア膜を形成する。このバリア膜は、密着性を高め、埋め込み性を付与し、さらにコンタクト抵抗の低減と安定化をもたらす。さらに、開口部の形成は、液滴吐出法を用いて、ノズルから、ウエットエッチング液を吐出することで行ってもよい。但し、開口部のアスペクト比制御のため、水などの溶媒で適宜洗浄する工程を追加するとよい。勿論、この洗浄の工程も、液滴吐出法を用いて、ノズルから吐出する液滴を水に交換するか、または、溶液が充填されたヘッドを交換すると、同一の装置で連続処理が可能となり、処理時間の観点から好ましい。また、開口部の形成には、フォトリソグラフィ法を用いてもよいが、マスクとなる絶縁層の形成には、液滴吐出法を用いるとよい。そうすると、スピンドル法等に比較して、材料の利用効率が格段に向上する。上記のいずれかの方法によって開口部992、993を形成すると、導電体層956、984が露出した状態になる。

#### 【0056】

次に、導電体層984と電気的に接続するように、電界発光層985、対向電極となる導電体層986を形成する。そうすると、導電体層984、電界発光層985及び導電体層986の積層体に相当する発光素子が完成する。この発光素子の形成は、ノズルから吐出する組成物を変更するか、又は組成物が充填されたヘッドを変更することで、電界発光層985やその他の導電性を有する複数層の薄膜を連続的に作製することができる。そうすると、スループットが向上し、生産性が向上する。

#### 【0057】

続いて、シール材988を形成し、基板989を用いて封止する。その後、導電体層956に電気的に接続するように、異方性導電体を介して、接続端子990を取り付ける。

#### 【0058】

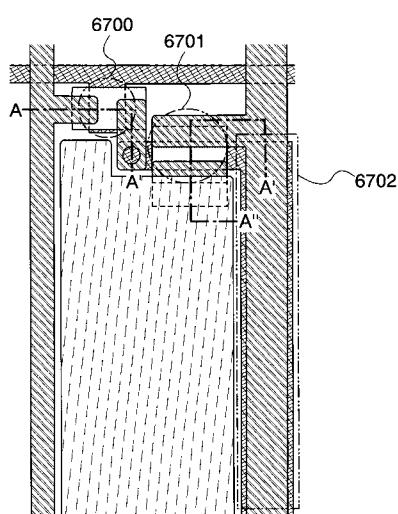

上記工程を経て、チャネル保護型のスイッチング用トランジスタ6700、駆動用トランジスタ6701及び容量素子6702を含む表示装置が完成する。図12(C)に示す断面構造は、図13に示すレイアウト図のA-A'-A'における断面構造に相当する。

#### 【0059】

上記構成では、導電体層984が陰極、導電体層986が陽極であり、上記工程を経ると、陰極/電界発光層/陽極の逆積み素子が完成する。この場合、発光素子から発せられる光は、基板989側に出射する。従って、上面出射を行う表示装置が完成する。但し基板951側に出射させたい場合には、導電体層986上に遮蔽体を設けるとよい。さらに、両面出射を行いたい場合には、陽極となる導電体層と陰極となる導電体層を透光性材料、又は光を透過する厚さで形成し、さらに透光性を有する基板を用いる。

#### 【0060】

陰極に相当する導電体層は、仕事関数が小さい材料を用いることが好ましく、例えば、Ca、Al、CaF、MgAg、AlLi等を用いる。電界発光層は、単層型、積層型、また層の界面がない混合型のいずれの型でもよく、シングレット材料、トリプレット材料又はそれらを組み合わせた材料や、低分子材料、高分子材料及び中分子材料を含む有機材料、電子注入性に優れる酸化モリブデン等に代表される無機材料、有機材料と無機材料の複合材料のいずれを用いてもよい。陽極に相当する導電層は光を透過する透明導電層で形成するか、又は光を透過する厚さで形成することが好ましく、例えばITO、ITSOの他、酸化インジウムに酸化亜鉛(ZnO)を混合した透明導電体を用いる。なお、陽極/電界発光層/陰極の順に形成する、順積み素子を形成する場合には、陽極の形成前に、酸素雰囲気中のプラズマ処理や真空雰囲気下での加熱処理を行うことが好ましく、これは、駆動電圧が低くなったり、寿命が向上したりする効果が得られるためである。また、発光素子から発せられる光が基板951側に向かう、下面出射を行う場合には、画素電極として機能する導電体層984は透光性を有することが必須である。この場合、導電体層984として、酸化珪素とITOからなるITSOを用いて、その下層には、窒化珪素からなる絶縁層964が形成してあるとよい。そうすると、導電体層984と絶縁層964との屈折率が近いために、発光素子から発せられる光の取り出し効率が向上する。

10

20

30

40

50

## 【0061】

また、透光性を有する導電体層と接する絶縁体層は、珪素(Si)と窒素(N)を含む層で形成することが好適であり、より具体的には窒素を10 atomic%以上、好適には25 atomic%以上含む層で形成するとよく、さらに具体的には窒化珪素膜(SiN)が挙げられる。また、窒素と酸素(O)を含み、窒素が酸素よりも多く含む層を形成するとよく、具体的には窒化酸化珪素膜(SiNO)が挙げられる。そして、透光性を有する導電体層と接する絶縁体層は、上記に挙げた構成の2つの薄膜を単層又は積層して形成する。上記構成とすると、電流効率を向上させ、同じ電流値でも輝度を向上させることで、明るい表示を得ることができる。

## 【0062】

10

上記の作製工程では、導電層の形成や半導体層のパターニングに用いるマスクを液滴吐出法により形成する点を特徴とし、上記特徴により、工程の簡略化による作製時間の短縮や作製費用の低減を実現する。また、結晶化の工程が必要ないため、基板の一辺が一メートル以上の大型基板への適用が容易であり、従って、10インチから50インチ程度の大型の表示画面を有する電子機器への適用が有用である。

## (実施の形態5)

## 【0063】

20

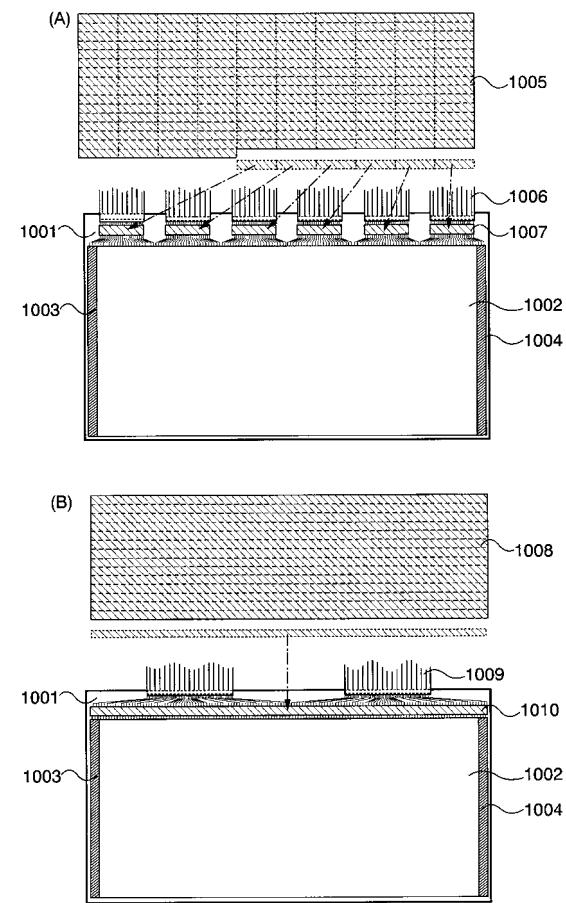

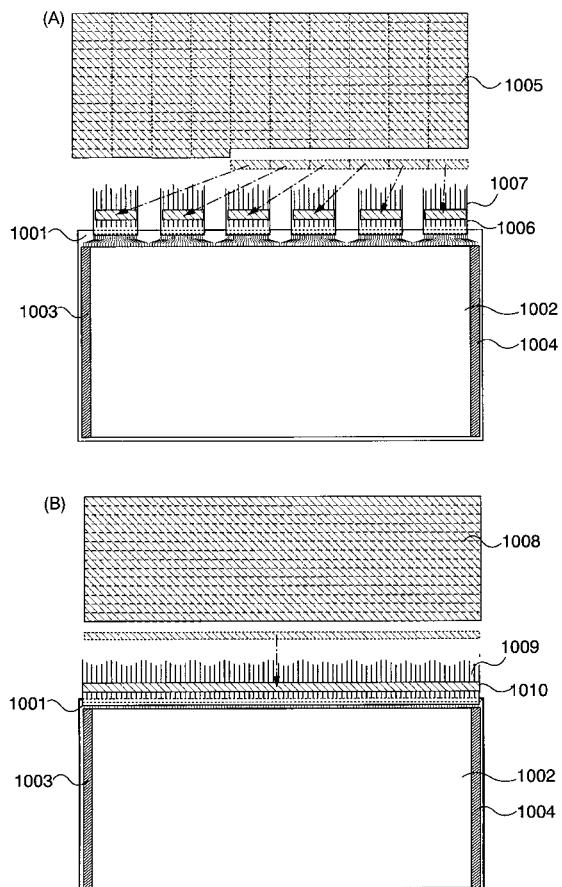

本発明の表示装置の作製方法について、図14、15を用いて説明する。まず、COG(Chip On Glass)方式を採用した表示装置について、図14を用いて説明する。基板1001上には、文字や画像などの情報を表示する画素領域1002、走査側の駆動回路1003、1004が設けられる。複数の駆動回路が設けられた基板1005、1008は、矩形状に分断され、分断後の駆動回路(以下ドライバICと表記)は、基板1001上に実装される。図14(A)は複数のドライバIC1007、該ドライバIC1007の先にテープ(フィルムともよぶ)1006を実装する形態を示す。図14(B)はドライバIC1010、該ドライバIC1010の先にテープ1009を実装する形態を示す。

## 【0064】

30

次に、TAB方式を採用した表示装置について、図15を用いて説明する。基板1001上には、画素領域1002、走査側の駆動回路1003、1004が設けられる。図15(A)は基板1001上に複数のテープ1006を貼り付けて、該テープ1006にドライバIC1007を実装する形態を示す。図15(B)は基板1001上にテープ1009を貼り付けて、該テープ1009にドライバIC1010を実装する形態を示す。後者を採用する場合には、強度の問題から、ドライバIC1010を固定する金属片等と一緒に貼り付けるとよい。

## 【0065】

40

ドライバICは、生産性を向上させる観点から、一辺が300mmから1000mm以上の矩形状の基板1005、1008上に複数個作り込むとよい。つまり、基板1005、1008上に駆動回路部と入出力端子を一つのユニットとする回路パターンを複数個形成し、最後に分割して取り出せばよい。ドライバICの長辺の長さは、完成する表示装置の解像度やその画面サイズに依存するが、図14(A)、図15(A)に示すように、長辺が15~80mm、短辺が1~6mmの矩形状に形成してもよいし、図14(B)、図15(B)に示すように、画素領域1002の一辺、又は画素領域1002の一辺と各駆動回路1003、1004の一辺とを足した長さに形成してもよい。

## 【0066】

50

ドライバICのICチップに対する外形寸法の優位性は長辺の長さにあり、長辺が15~80mmで形成されたドライバICを用いると、画素領域1002に対応して実装するのに必要な数がICチップを用いる場合よりも少なくて済み、製造上の歩留まりを向上させることができる。また、ガラス基板上にドライバICを形成すると、母体として用いる基板の形状に限定されないので生産性を損なうことがない。これは、円形のシリコンウエハからICチップを取り出す場合と比較すると、大きな優位点である。

## 【0067】

ドライバICは、基板上に形成された結晶質半導体により形成されることが好適であり、該結晶質半導体は連続発光のレーザ光を照射することで形成されることが好適である。従って、当該レーザ光を発生させる発振器としては、連続発光の固体レーザ又は気体レーザを用いる。連続発光のレーザを用いると、結晶欠陥が少なく、大粒径の多結晶半導体層を用いて、トランジスタを作成することが可能となる。また移動度や応答速度が良好なために高速駆動が可能で、従来よりも素子の動作周波数を向上させることができ、特性バラツキが少ないために高い信頼性を得ることができる。なお、さらなる動作周波数の向上を目的として、トランジスタのチャネル長方向とレーザ光の走査方向と一致させるとよい。これは、連続発光レーザによるレーザ結晶化工程では、トランジスタのチャネル長方向とレーザ光の基板に対する走査方向とが概ね並行（好ましくは $-30^\circ \sim 30^\circ$ ）であるときに、最も高い移動度が得られるためである。なおチャネル長方向とは、チャネル形成領域において、電流が流れる方向、換言すると電荷が移動する方向と一致する。このように作製したトランジスタは、結晶粒がチャネル方向に延在する多結晶半導体層によって構成される活性層を有し、このことは結晶粒界が概ねチャネル方向に沿って形成されていることを意味する。10

## 【0068】

レーザ結晶化を行うには、レーザ光の大幅な絞り込みを行うことが好ましく、そのビームスポットの幅は、ドライバICの短辺の同じ幅の $1 \sim 3\text{ mm}$ 程度とすることがよい。また、被照射体に対して、十分に且つ効率的なエネルギー密度を確保するために、レーザ光の照射領域は、線状であることが好ましい。但し、ここでいう線状とは、厳密な意味で線を意味しているのではなく、アスペクト比の大きい長方形もしくは長橈円形を意味する。例えば、アスペクト比が2以上（好ましくは $10 \sim 10000$ ）のものを指す。このように、レーザ光のビームスポットの幅をドライバICの短辺と同じ長さとすることで、生産性を向上させた表示装置の作製方法を提供することができる。20

## 【0069】

図14、15では、走査線駆動回路は画素部と共に一体形成し、信号線駆動回路としてドライバICを実装した形態を示した。しかしながら、本発明はこの形態に限定されず、走査線駆動回路及び信号線駆動回路の両方として、ドライバICを実装してもよい。その場合には、走査線側と信号線側で用いるドライバICの仕様を異なるものにするとよい。30

## 【0070】

画素領域1002は、信号線と走査線が交差してマトリクスを形成し、各交差部に対応してトランジスタが配置される。本発明は、画素領域1002に配置されるトランジスタとして、非晶質半導体又はセミアモルファス半導体をチャネル部としたTFTを用いることを特徴とする。非晶質半導体は、プラズマCVD法やスパッタリング法等の方法により形成する。セミアモルファス半導体は、プラズマCVD法で $300$ 以下の温度で形成することができあり、例えば、外寸 $550 \times 650\text{ mm}$ の無アルカリガラス基板であっても、トランジスタを形成するのに必要な膜厚を短時間で形成するという特徴を有する。このような製造技術の特徴は、大画面の表示装置を作製する上で有効である。また、セミアモルファスTFTは、SASでチャネル形成領域を構成することにより $2 \sim 10\text{ cm}^2/\text{V} \cdot \text{sec}$ の電界効果移動度を得ることができる。従って、このTFTを画素のスイッチング用素子や、走査線側の駆動回路を構成する素子として用いることができる。従って、システムオンパネル化を実現した表示装置を作製することができる。本実施の形態は、上記の実施の形態と自由に組み合わせることができる。40

## 【実施例1】

## 【0071】

本実施例では、ドライバICを実装する方法について、図16を用いて説明する。この実装方法としては、異方性導電材を用いた接続方法やワイヤボンディング方式等を採用すればよく、その一例について図16を用いて説明する。

## 【0072】

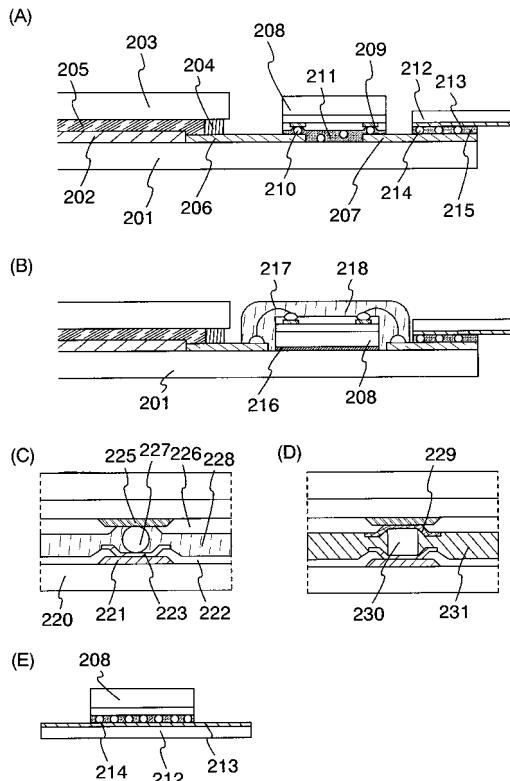

図16(A)は第1の基板201に、ドライバIC208が異方性導電材を用いて実装された例を示す。第1の基板201上には画素領域202、引出線206、接続配線及び入出力端子207を有する。第2の基板203は、シール材204で第1の基板201と接着されており、その間に液晶層205を有する。

#### 【0073】

接続配線及び入出力端子207の一方の端には、FPC212が異方性導電材で接着されている。異方性導電材は樹脂215と表面にAuなどがメッキされた数十~数百μm径の導電性粒子214から成り、導電性粒子214により接続配線及び入出力端子207とFPC212に形成された配線213とが電気的に接続される。ドライバIC208も、異方性導電材で第1の基板201に接着され、樹脂211中に混入された導電性粒子210により、ドライバIC208に設けられた入出力端子209と、引出線206又は接続配線及び入出力端子207と電気的に接続される。

10

#### 【0074】

この方式によるドライバIC208の実装方法について、図16(C)を用いて説明する。ドライバICには、入出力端子225が設けられ、その周辺部には保護絶縁膜226が形成される。第1の基板220には第1の導電層221と第2の導電層223及び絶縁層222が形成され、ここでは第1の導電層221と第2の導電層223とで引出線または接続配線を形成している。

#### 【0075】

第1の基板220に形成されるこれらの導電層及び絶縁層は画素領域の画素TFTと同じ工程で形成される。例えば、画素TFTが逆スタガ型で形成される場合、第1の導電層221はゲート電極と同じ層に形成され、Ta、Cr、Ti、Alなどの材料で形成される。通常ゲート電極上にはゲート絶縁膜が形成され、絶縁層222はこれと同じ層で形成されるものである。第1の導電層221上に重ねて設ける第2の導電層223は画素電極と同じ透明導電膜で形成されるものであり、導電性粒子227との接触を良好なものとする。樹脂228中に混入された導電性粒子227の大きさと密度を適したものとすることにより、このような形態でドライバICと第1の基板220とは電気的に接続する。

20

#### 【0076】

図16(D)は樹脂の収縮力を用いたCOG方式の例であり、ドライバIC側にTaやTiなどでバリア層229を形成し、その上に無電解メッキ法などによりAuを約20μm形成しバンプ230とする。そして、ドライバICと第1の基板との間に光硬化性絶縁樹脂231を介在させ、光硬化して固まる樹脂の収縮力を利用して電極間を圧接して電気的な接続を形成する。

30

#### 【0077】

また、図16(E)で示すように、FPC212上の配線213と、導電性粒子214を介してドライバIC208を設けてよい。この構成は、携帯端末等の筐体の大きさが限られた電子機器に用いる場合に大変有効である。

#### 【0078】

また、図16(B)で示すように、第1の基板201にドライバIC208を接着材216で固定して、Auワイヤ217によりドライバICの入出力端子と引出線または接続配線とを接続しても良い。そして封止樹脂218で封止する。なお、ドライバICの実装方法は、特に限定されるものではなく、公知のCOG方法やワイヤボンディング方法、或いはTAB方法を用いることができる。

40

#### 【0079】

ドライバICの厚さは、対向電極が形成された第2の基板と同じ厚さとすることで、両者の間の高さはほぼ同じものとなり、表示装置全体としての薄型化に寄与する。また、それぞれの基板を同じ材質のもので作製することにより、この表示装置に温度変化が生じても熱応力が発生することなく、TFTで作製された回路の特性を損なうことはない。その他にも、上記の実施形態で示すようにICチップよりも長尺のドライバICで駆動回路を実装することにより、1つの画素領域に対して、実装されるドライバICの個数を減らす

50

ことができる。本実施例は、上記の実施の形態と自由に組み合わせることができる。

**【実施例 2】**

**【0080】**

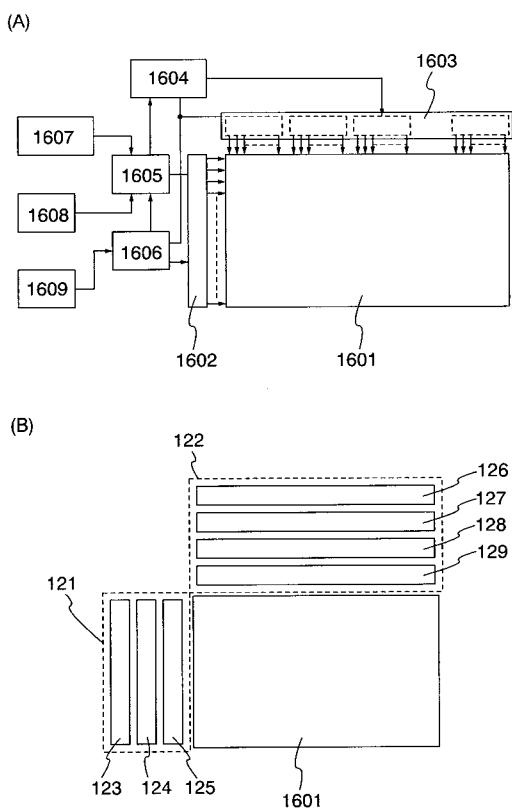

本実施例では、本発明の表示装置の構成について簡単に説明する。上述したように、ドライバICは、液晶表示装置やEL表示装置などの駆動回路として用いる。図17はそのような表示装置のブロック図である。画素領域1601は複数の走査線と信号線で形成され、TFTが設けられたアクティブマトリクス型であっても良いし、パッシブマトリクス型であっても良い。その周辺には、ドライバICに相当する走査線駆動回路1602及び信号線駆動回路1603が配置される。

**【0081】**

10

外部から入力されるクロック、スタートパルス1607と、映像信号1608は、ドライバICの入力仕様に変換するためのコントロール回路1605に入力され、それぞれのタイミング仕様に変換される。また、電源1609、オペアンプから成る電源回路1606は外付けの回路で賄われる。このコントロール回路1605と電源回路1606もTAB方式で実装すると、表示装置の小型化に有効である。

**【0082】**

コントロール回路1605からは、走査線と信号線にそれぞれ信号が出力されるが、信号線には信号分割回路1604が設けられ、入力デジタル信号をm個に分割して供給する。分割数mは2以上の自然数である。

**【0083】**

20

ドライバICの回路構成は、走査線側と信号線側とで異なる。図17(B)はその一例を示し、走査線側のドライバIC121は、シフトレジスタ回路123、レベルシフタ回路124、パッファ回路125からなる。一方、データ線側のドライバIC122は、シフトレジスタ回路126、ラッチ回路127、レベルシフタ回路128、D/A変換回路129からなる。なお、図12では、信号線側と走査線側の両方でドライバICを用いた形態を示したが、上述した通り、本発明はこれに限定されない。走査線側の駆動回路は、画素領域1601が形成された基板上に作り込んでもよい。本実施例は、上記の実施の形態、実施例と自由に組み合わせることができる。

**【実施例 3】**

**【0084】**

30

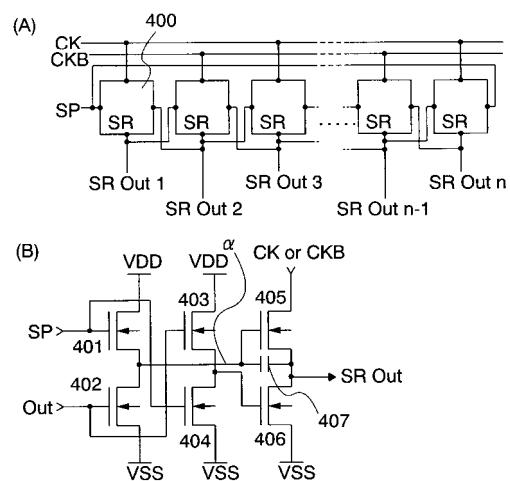

本発明の必須の構成要素として、セミアモルファス半導体層をチャネル部としたTFTが挙げられ、該TFTは各画素に具備される。このようなTFTを各画素に含む場合、同一基板上に形成する駆動回路もセミアモルファス半導体層をチャネル部としたTFTにより形成することが好適である。但し、セミアモルファス半導体層を含むTFTはN型TFTしか形成できない。本実施例は、N型TFTのみでシフトレジスタを構成する例について説明する。

**【0085】**

図18(A)において、ブロック400が1段分のサンプリングパルスを出力するパルス出力回路に相当し、シフトレジスタはn個のパルス出力回路により構成される。図18(B)は、パルス出力回路400の具体的な構成を示したものであり、N型のTFT401~406と、容量素子407を有する。このパルス出力回路は、ブートストラップ法を応用することで、N型TFTのみでの構成が可能となった回路である。詳しい動作については、特開2002-335153号公報に記載されているため、本公報を参考にするといい。本実施例は、上記の実施の形態、実施例と自由に組み合わせることができる。

40

**【実施例 4】**

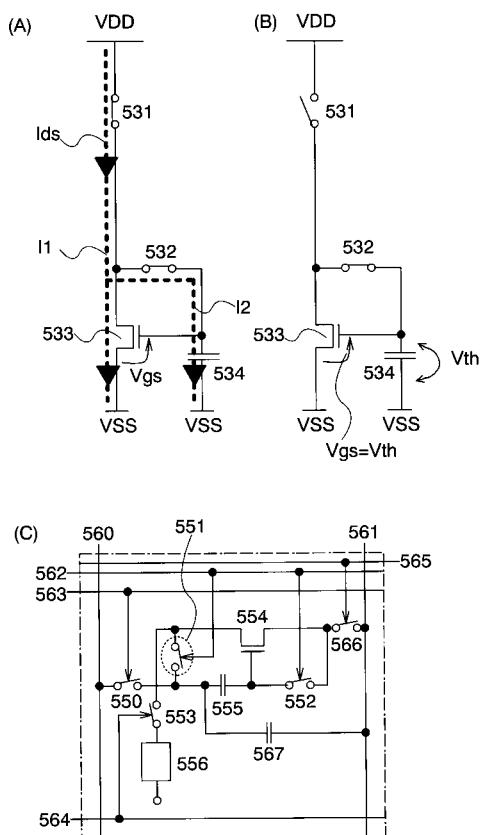

**【0086】**

本実施例では、しきい値電圧の補正回路について、図19を用いて説明する。この回路は、非晶質半導体をチャネル部とした薄膜トランジスタ(a-Si TFT)に対して有効であり、これは、a-Si TFTは、その電気特性(しきい値電圧、電界効果移動度等)が経時的に変化する性質を有するためである。図19(A)(B)は補正回路の等価

50

回路図を示し、トランジスタ等からなるスイッチ 531、532、トランジスタ 533、容量素子 534 を有する。この回路の動作について、以下に簡単に説明する。

#### 【0087】

まず、スイッチ 531、532 をオンにする（図 19 (A) 参照）。そうすると、スイッチ 531 からトランジスタ 533 の方向と、スイッチ 531 から容量素子 534 の方向に向かって電流  $I_{DS}$  が流れる。このとき、電流  $I_{DS}$  は  $I_1$  と  $I_2$  に分かれて流れ、 $I_{DS} = I_1 + I_2$  を満たす。電流が流れ始めた瞬間には、容量素子 534 に電荷は保持されず、トランジスタ 533 はオフである。従って、 $I_2 = 0$ 、 $I_{DS} = I_1$  である。しかしながら、徐々に容量素子 534 に電荷が蓄積されて、容量素子 534 の両電極間に電位差が生じ始め、その電位差がトランジスタ 533 のしきい値電圧になると、該トランジスタ 533 がオンになり、 $I_2 > 0$  となる。このとき、 $I_{DS} = I_1 + I_2$  を満たすので、 $I_1$  は次第に減少するが、以前電流は流れている。容量素子 534 では、その両電極間の電位差が VDD になるまで、電荷の蓄積が続けられるが、該容量素子 534 の両電極間の電位差が VDD になると、 $I_2$  は流れなくなり、 $I_{DS} = I_1$  となる。10

#### 【0088】

次に、スイッチ 531 をオフにする（図 19 (B) 参照）。そうすると、容量素子 534 に保持された電荷は、スイッチ 532 を介してトランジスタ 533 の方向に流れていき、放電する。この動作は、トランジスタ 533 がオフになるまで、つまり、容量素子 534 に保持された電荷が、トランジスタ 533 のしきい値電圧と同じ値になるまで行われる。上記構成を有する補正回路では、容量素子 534 の両電極間の電位差を、あるトランジスタのしきい値電圧と同じ値に設定することができる。つまり、トランジスタの  $V_{gs}$  をそのまま保持して、該トランジスタのゲート電極に信号電圧を入力することができる。そのため、トランジスタのゲート電極には、容量素子に保持されている  $V_{gs}$  に加えて、前記信号電圧を上乗せした値が入力される。従って、トランジスタ間のしきい値電圧にバラツキが生じていても、信号電圧が入力されるトランジスタは、常に該トランジスタのしきい値電圧と信号電圧を足した値が入力される。従って、トランジスタ間のしきい値電圧のバラツキの影響を抑制することができる。20

#### 【0089】

上記構成のしきい値補正回路を用いた画素回路の一例について、図 19 (C) を用いて説明する。図 19 (C) において、列方向に信号線 560、電源線 561、行方向に走査線 562 ~ 565 が配置され、これらの配線に囲まれた領域にスイッチ 550 ~ 553、566、トランジスタ 554、容量素子 555、567、発光素子 556 が設けられる。このように、しきい値補正回路を設けることで、発光素子を駆動する駆動用トランジスタのしきい値電圧のバラツキを抑制することができ、これらのバラツキに起因した輝度ムラを改善して、高画質の画像を表示する表示装置を提供することができる。本実施例は、上記の実施の形態、実施例と自由に組み合わせることができる。30

#### 【実施例 5】

#### 【0090】

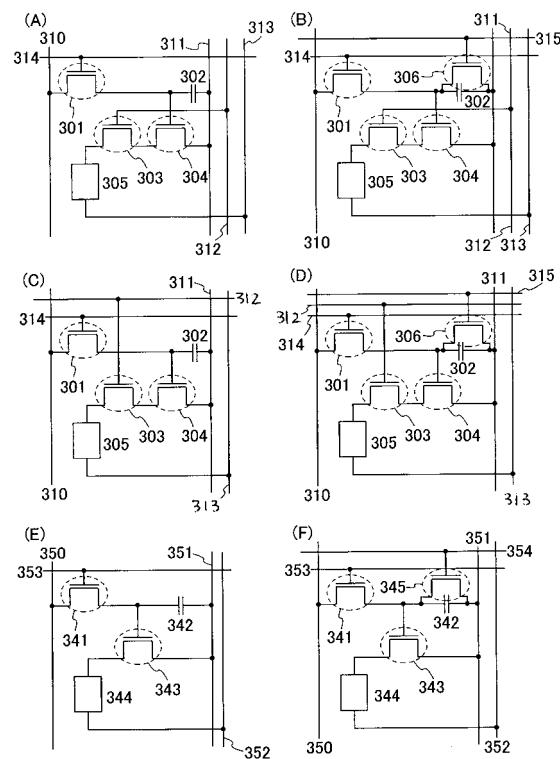

本発明は、セミアモルファス半導体層をチャネル部とした TFT、該 TFT を含む画素を複数有する表示装置を提供するものであり、ここでは、該画素の構成について、図 20 を用いて説明する。40

#### 【0091】

図 20 (A) に示す画素は、列方向に信号線 310 及び電源線 311 ~ 313、行方向に走査線 314 が配置される。また、スイッチング用 TFT 301、駆動用 TFT 303、電流制御用 TFT 304、容量素子 302 及び発光素子 305 を有する。

#### 【0092】

図 20 (C) に示す画素は、TFT 303 のゲート電極が、行方向に配置された電源線 312 に接続される点が異なっており、それ以外は図 20 (A) に示す画素と同じ構成である。つまり、図 20 (A) (C) に示す両画素は、同じ等価回路図を示す。しかしながら、行方向に電源線 312 が配置される場合（図 20 (A)）と、列方向に電源線 31250

が配置される場合(図20(C))では、各電源線は異なるレイヤーの導電体層で形成される。ここでは、駆動用TFT303のゲート電極が接続される配線に注目し、これらを作製するレイヤーが異なることを表すために、図20(A)(C)として分けて記載する。

#### 【0093】

図20(A)(C)に示す画素の特徴として、画素内にTFT303、304が直列に接続されており、TFT303のチャネル長 $L_3$ 、チャネル幅 $W_3$ 、TFT304のチャネル長 $L_4$ 、チャネル幅 $W_4$ は、 $L_3 / W_3 : L_4 / W_4 = 5 \sim 6000 : 1$ を満たすように設定される点が挙げられる。

#### 【0094】

TFT303は、飽和領域で動作し発光素子305に流れる電流値を制御する役目を有し、TFT304は線形領域で動作し発光素子305に対する電流の供給を制御する役目を有する。両TFTは同じ導電型を有していると作製工程上好ましい。またTFT303には、エンハンスマント型だけでなく、ディブリーション型のTFTを用いてもよい。上記構成を有する本発明は、TFT304が線形領域で動作するために、TFT304の $V_{GS}$ の僅かな変動は発光素子305の電流値に影響を及ぼさない。つまり、発光素子305の電流値は、飽和領域で動作するTFT303により決定される。上記構成を有する本発明は、TFTの特性バラツキに起因した発光素子の輝度ムラを改善して画質向上させた表示装置を提供することができる。

#### 【0095】

図20(A)～(D)に示す画素において、TFT301は、画素に対するビデオ信号の入力を制御するものであり、TFT301がオンして、画素内にビデオ信号が入力されると、容量素子302にそのビデオ信号が保持される。なお図20(A)(C)には、容量素子302を設けた構成を示したが、本発明はこれに限定されず、ビデオ信号を保持する容量がゲート容量などでもかなうことが可能な場合には、明示的に容量素子302を設けなくてもよい。

#### 【0096】

発光素子305は、2つの電極間に電界発光層が挟まれた構造を有し、順バイアス方向の電圧が印加されるように、画素電極と対向電極の間(陽極と陰極の間)に電位差が設けられる。電界発光層は有機材料や無機材料等の広汎に渡る材料により構成され、この電界発光層におけるルミネッセンスには、一重項励起状態から基底状態に戻る際の発光(蛍光)と、三重項励起状態から基底状態に戻る際の発光(リン光)とが含まれる。

#### 【0097】

図20(B)に示す画素は、TFT306と走査線315を追加している以外は、図20(A)に示す画素構成と同じである。同様に、図20(D)に示す画素は、TFT306と走査線315を追加している以外は、図20(C)に示す画素構成と同じである。

#### 【0098】

TFT306は、新たに配置された走査線315によりオン又はオフが制御される。TFT306がオンになると、容量素子302に保持された電荷は放電し、TFT306がオフする。つまり、TFT306の配置により、強制的に発光素子305に電流が流れない状態を作ることができる。従って、図20(B)(D)の構成は、全ての画素に対する信号の書き込みを待つことなく、書き込み期間の開始と同時又は直後に点灯期間を開始することができるため、デューティ比を向上することが可能となる。

#### 【0099】

図20(E)に示す画素は、列方向に信号線350、電源線351、352、行方向に走査線353が配置される。また、スイッチング用TFT341、駆動用TFT343、容量素子342及び発光素子344を有する。図20(F)に示す画素は、TFT345と走査線354を追加している以外は、図20(E)に示す画素構成と同じである。なお、図20(F)の構成も、TFT345の配置により、デューティ比を向上することが可能となる。本実施例は、上記の実施の形態、実施例と自由に組み合わせることができる。

10

20

30

40

50

## 【実施例 6】

## 【0100】

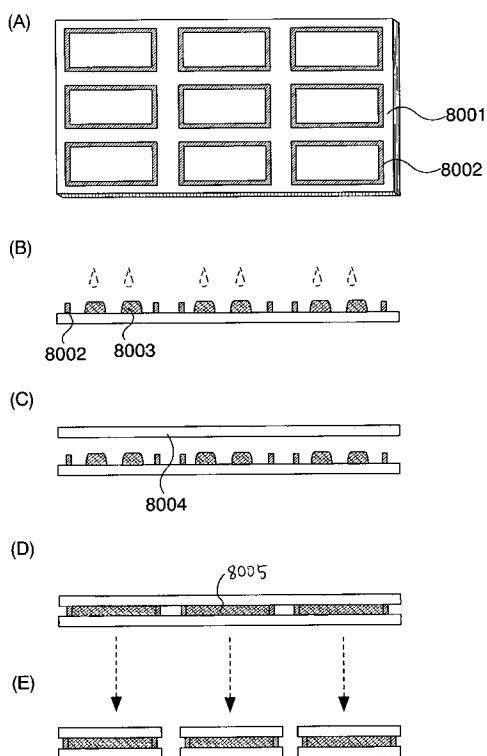

液晶を形成する方法として、液晶滴下方式を採用した場合について、図21を用いて説明する。まず、基板8001上に、TFT等の素子を形成し、次に、シール材として機能する閉ループ8002を形成する(図21(A)参照)。続いて、閉ループ8002の中にディスペンサにより液晶8003を滴下する(図21(B)参照)。その後、真空中で基板8001と基板8004とを貼り合わせる(図21(C)参照)。次に、UV硬化を行って、液晶8005が充填された状態となり(図21(D)参照)、続いてパネル毎に分断する(図21(E)参照)。本実施例は、上記の実施の形態と自由に組み合わせることができる。

10

## 【実施例 7】

## 【0101】

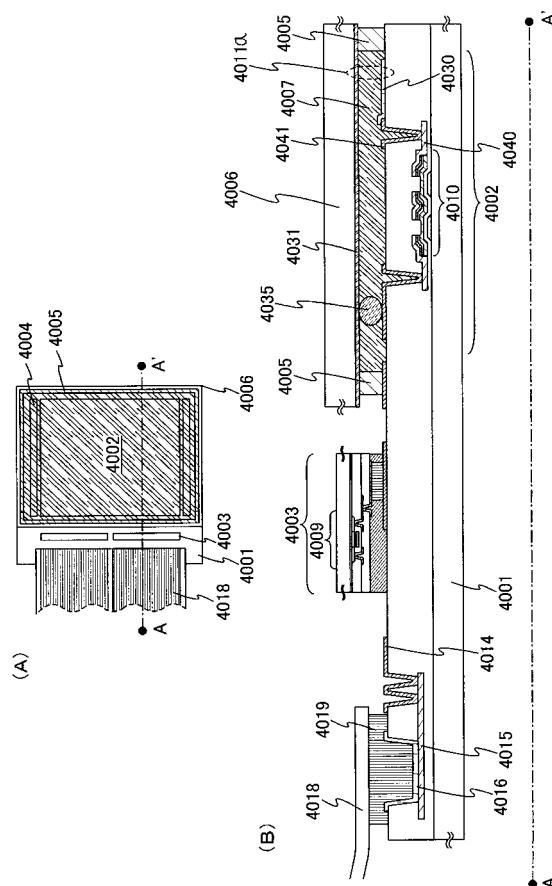

本実施例は、本発明の表示装置の一形態に相当するパネルの外観について、図22を用いて説明する。図22(A)は、第1の基板4001上に形成されたセミアモルファスTFT4010及び液晶素子4011aを、第2の基板4006との間にシール材4005によって封止した、パネルの上面図であり、図22(B)は、図22(A)のA-A'における断面図に相当する。

## 【0102】

第1の基板4001上に設けられた画素部4002と、走査線駆動回路4004とを囲むようにして、シール材4005が設けられる。また画素部4002と、走査線駆動回路4004の上に第2の基板4006が設けられる。よって画素部4002と、走査線駆動回路4004とは、第1の基板4001とシール材4005と第2の基板4006とによって、液晶4007aと共に封止される。また第1の基板4001上のシール材4005によって囲まれている領域とは異なる領域に、別途用意された基板上に多結晶半導体層で形成された信号線駆動回路4003が実装される。

20

## 【0103】

なお本実施例では、多結晶半導体層を用いたトランジスタを有する信号線駆動回路4003を、第1の基板4001に貼り合わせる例について説明するが、単結晶半導体層を用いたトランジスタで信号線駆動回路を形成し、貼り合わせてもよい。図22では、信号線駆動回路4003に含まれる、多結晶半導体層で形成されたトランジスタ4009を例示する。

30

また図22では、信号線駆動回路4003を別途形成し、第1の基板4001に実装している例を示しているが、本実施例はこの構成に限定されない。走査線駆動回路を別途形成して実装しても良いし、信号線駆動回路の一部または走査線駆動回路の一部のみを別途形成して実装しても良い。

## 【0104】

第1の基板4001上に設けられた画素部4002と、走査線駆動回路4004は、トランジスタを複数有し、図22(B)では、画素部4002に含まれるトランジスタ4010とを例示している。トランジスタ4010はセミアモルファス半導体層を用いたトランジスタに相当する。

40

また、液晶素子4011aが有する画素電極4030は、トランジスタ4010と配線4040、配線4041を介して電気的に接続されている。そして液晶素子4011aの対向電極4031は第2の基板4006上に形成される。画素電極4030、対向電極4031及び液晶4007aが重なっている部分が、液晶素子4011aに相当する。

球状のスペーサ4035は、画素電極4030と対向電極4031との間の距離(セルギャップ)を制御するために設けられている。なお絶縁膜をパターニングすることで得られるスペーサを用いていても良い。

また別途形成された信号線駆動回路4003と、走査線駆動回路4004または画素部4002に与えられる各種信号及び電位は、引き回し配線4014及び4015を介して、接続端子4016から供給されている。

50

**【0105】**

本実施例では、接続端子4016が、液晶素子4011aが有する画素電極4030と同じ導電膜から形成されている。また、引き回し配線4014は、配線4041と同じ導電膜で形成されている。また引き回し配線4015は、配線4040と同じ導電膜で形成されている。接続端子4016は、FPC4018が有する端子と、異方性導電膜4019を介して電気的に接続されている。

**【0106】**

なお図示していないが、本実施例に示した液晶表示装置は配向膜、偏光板を有し、更にカラーフィルタや遮蔽膜を有していても良い。本実施例は、上記の実施の形態、実施例と自由に組み合わせることができる。

10

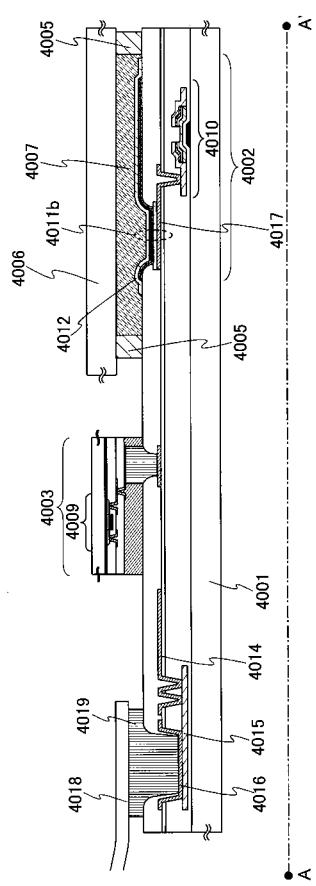

**【実施例8】****【0107】**

本実施例では、本発明の表示装置の一形態に相当するパネルの外観について、図23を用いて説明する。図23は、第1の基板上に形成されたセミアモルファストランジスタ及び発光素子を、第2の基板との間にシール材によって封止した、パネルの上面図であり、図23は、図22(A)のA-A'における断面図に相当する。

**【0108】**

第1の基板4001上に設けられた画素部4002と、走査線駆動回路4004は、トランジスタを複数有し、図23では、画素部4002に含まれるトランジスタ4010を例示している。なおトランジスタ4010はセミアモルファス半導体層を用いたトランジスタに相当する。

20

**【0109】**

発光素子4011bが有する画素電極は、トランジスタ4010のドレインと、配線4017を介して電気的に接続されている。そして、発光素子4011bの対向電極と透明導電膜4012が電気的に接続されている。なお発光素子4011bの構成は、発光素子4011bから取り出す光の方向や、トランジスタ4010の導電型などに合わせて、発光素子4011bの構成は適宜変えることができる。

**【0110】**

また、別途形成された信号線駆動回路4003と、走査線駆動回路4004または画素部4002に与えられる各種信号及び電位は、引き回し配線4014及び4015を介して、接続端子4016から供給されている。

30

**【0111】**

本実施例では、接続端子4016が、発光素子4011bが有する画素電極と同じ導電膜から形成されている。また、引き回し配線4014は、配線4017と同じ導電膜から形成されている。また引き回し配線4015は、トランジスタ4010が有するゲート電極と、同じ導電膜から形成されている。接続端子4016は、FPC4018が有する端子と、異方性導電膜4019を介して電気的に接続されている。

**【0112】**

充填材4007bとしては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂または熱硬化樹脂を用いることができ、PVC(ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコン樹脂、PVBl(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いることができる。本実施例では充填材として窒素を用いた。

40

**【0113】**

また充填材4007bを吸湿性物質(好ましくは酸化バリウム)もしくは酸素を吸着しうる物質にさらしておくために、第2の基板4006に凹部を設けて、該凹部に吸湿性物質または酸素を吸着しうる物質を配置するとよい。第2の基板4006は目の細かいメッシュ状にすると、空気や水分は通し、吸湿性物質または酸素を吸着しうる物質は通さない構成になっている。吸湿性物質または酸素を吸着しうる物質を設けることで、発光素子4011bの劣化を抑制できる。本実施例は、上記の実施の形態、実施例と自由に組み合わ

50

せることができる。

**【実施例 9】**

**【0114】**

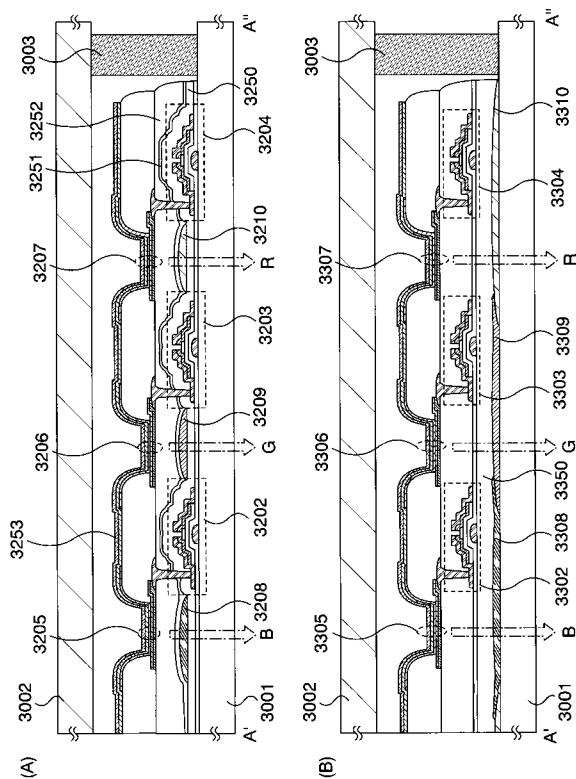

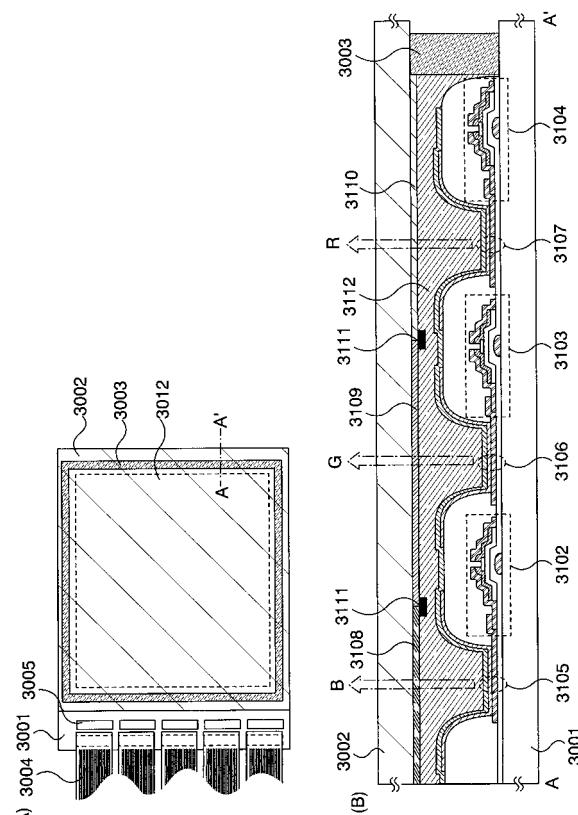

本発明の表示装置の一形態であるパネルについて、図24、25を用いて説明する。図24(A)はパネルの上面図、図24(B)と図25(A)(B)は図24(A)のA-A'における断面図である。第1の基板3001上には、画素部3012が設けられ、該画素部3012を囲むようにして、シール材3003が設けられる。第1の基板3001と第2の基板3002は、シール材3003により封止される(図24(A)(B)参照)。第1の基板3001上には、ドライバIC3005が設けられ、画素部3012とドライバIC3005には接続端子3004から各種信号や電位が供給される。

10

**【0115】**

図24(B)には、画素部3012が含むTFT3102～3104を例示する。TFT3102～3104は、本発明に従って形成された非晶質半導体又はセミアモルファス半導体をチャネル部としたTFTにより構成される。また、各TFT3102～3104に電気的に接続された発光素子3105～3107が設けられ、各発光素子3105～3107から発せられる光は、カラーフィルタ3108～3110を介して外部に出射される。各カラーフィルタ3108～3110の間には、ブラックマトリクス3111が設けられる。上記構成では、第1の基板3001と第2の基板3002間の密閉空間を樹脂3112により充填することで、水分等の発光素子3105～3107の劣化を促進する物質の侵入を防止し、寿命を向上させたパネルの提供を実現する。

20

**【0116】**

TFT3102～3104はN型TFTであり、該TFTに直接接続された導電体層が陰極に相当し、該導電体層と電界発光層を介して接続された導電体層が陽極に相当する。従って、発光素子3105～3107は、陰極/電界発光層/陽極の順に積層形成された逆積み素子に相当し、これらの素子から発せられる光は、第2の基板3002側に出射する。

**【0117】**

図25(A)には、画素部3012が含むTFT3202～3204を例示する。TFT3202～3204は、本発明に従って形成された非晶質半導体又はセミアモルファス半導体をチャネル部としたTFTにより構成される。また、各TFT3202～3204に電気的に接続された発光素子3205～3207が設けられ、各発光素子3205～3207から発せられる光は、カラーフィルタ3208～3210を介して外部に出射される。上記構成を有するパネルでは、まず、第1の基板3001上にTFT3202～3204を形成し、次に層間膜3250を形成し、続いて、カラーフィルタ3208～3210に相当する薄膜を形成する。その後、バリア膜として機能する絶縁膜3251と平坦化を目的とした絶縁膜3252を積層形成する。TFT3202～3204はN型TFTであり、発光素子3205～3207から発せられる光は、遮蔽体により反射して第1の基板3001側に出射する。従って、図示するパネルは、下面出射を行うパネルである。

30

**【0118】**

図25(B)は、画素部3012が含むTFT3302～3304を例示する。TFT3302～3304は、本発明に従って形成された非晶質半導体又はセミアモルファス半導体をチャネル部としたTFTにより構成される。また、各TFT3302～3304に電気的に接続された発光素子3305～3307が設けられ、各発光素子3305～3307から発せられる光は、カラーフィルタ3308～3310を介して外部に出射される。上記構成を有するパネルでは、まず、第1の基板3001上にカラーフィルタ3308～3310に相当する薄膜を形成し、該薄膜上に平坦化を目的とした絶縁膜3350を形成する。次に、絶縁膜3350上にTFT等の素子を形成する。

40

**【0119】**

上記構成において、発光素子から発せられる光は、RGBの各色を呈してもよいし、それ以外の色を呈していてもよい。また、カラーフィルタは、色変換層として用いてもよく

50

、その場合には、発光素子から発せられる光は1色でも構わない。発光素子から発せられる光をR G Bの各色とし、さらに、R G Bに対応したカラーフィルタを用いることで、高画質で階調再現性及び色再現性を向上したパネルを得ることが出来る。

#### 【0120】

なお上記パネルでは、発光素子を基板、又は基板及び樹脂により封止した場合を示すが、封止の処理は、発光素子を水分から保護するための処理であり、カバー材で機械的に封入する方法、熱硬化性樹脂又は紫外光硬化性樹脂で封入する方法、金属酸化物や窒化物等のバリア能力が高い薄膜により封止する方法のいずれかを用いる。カバー材としては、ガラス、セラミックス、プラスチックもしくは金属を用いることができるが、カバー材側に光を放射させる場合は透光性でなければならない。また、カバー材と上記発光素子が形成された基板とは熱硬化性樹脂又は紫外光硬化性樹脂等のシール材を用いて貼り合わせられ、熱処理又は紫外光照射処理によって樹脂を硬化させて密閉空間を形成する。この密閉空間の中に酸化バリウムに代表される吸湿材を設けることも有効である。さらに、カバー材と発光素子の形成された基板との空間を熱硬化性樹脂若しくは紫外光硬化性樹脂で充填することも可能である。この場合、熱硬化性樹脂若しくは紫外光硬化性樹脂の中に酸化バリウムに代表される吸湿材を添加しておくことは有効である。本実施例は、上記の実施の形態、実施例と自由に組み合わせることができる。10

#### 【実施例10】

#### 【0121】

本発明を用いた電子機器として、テレビ受像機（テレビ、テレビジョン、テレビジョン装置ともよぶ）、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、オーディオコンポ等）、ノート型パソコンコンピュータ、ゲーム機器、携帯情報端末（モバイルコンピュータ、携帯電話等）、記録媒体を備えた画像再生装置等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置）などが挙げられる。本発明は、結晶化の工程を設ける必要がないため、比較的パネルの大型化が容易である。従って、10～50インチの大型のパネルを用いた電子機器に非常に有用である。それら電子機器の具体例を図26に示す。20

#### 【0122】

図26（A）はテレビ受像機であり、筐体2001、表示部2003等を含む。図26（B）はパソコンコンピュータであり、筐体2202、表示部2203等を含む。図26（C）は記録媒体を備えた携帯型の画像再生装置であり、筐体2402、表示部A2403、表示部B2404等を含む。表示部A2403は主として画像情報を表示し、表示部B2404は主として文字情報を表示する。30

#### 【0123】

本発明は、表示部の作製に適用することができる。また本発明は上記電子機器に限定されず、適用範囲は極めて広く、あらゆる分野の電子機器に用いることが可能である。本実施例は、上記の実施の形態、実施例と自由に組み合わせることができる。

#### 【図面の簡単な説明】

#### 【0124】

- 【図1】本発明の表示装置の作製方法を説明する図（実施の形態1）。

- 【図2】本発明の表示装置の作製方法を説明する図（実施の形態1）。

- 【図3】本発明の表示装置の作製方法を説明する図（実施の形態1）。

- 【図4】本発明の配線基板の作製方法を説明する図（実施の形態2）。

- 【図5】本発明の半導体装置の作製方法を説明する図（実施の形態3）。

- 【図6】本発明の半導体装置の作製方法を説明する図（実施の形態3）。

- 【図7】本発明の半導体装置の作製方法を説明する図（実施の形態3）。

- 【図8】本発明の半導体装置の作製方法を説明する図（実施の形態3）。

- 【図9】本発明の半導体装置の作製方法を説明する図（実施の形態3）。

- 【図10】画素回路のレイアウト図（実施の形態3）。

4050

【図11】本発明の半導体装置の作製方法を説明する図（実施の形態4）。

【図12】本発明の半導体装置の作製方法を説明する図（実施の形態4）。

【図13】画素回路のレイアウト図（実施の形態4）。

【図14】ドライバICの実装方式（COG方式）を説明する図（実施の形態5）。

【図15】ドライバICの実装方式（TAB方式）を説明する図（実施の形態5）。

【図16】画素領域、テープ及びドライバICの接続を説明する図（実施例1）。

【図17】表示装置の構成を説明する図（実施例2）。

【図18】シフトレジスタを説明する図（実施例3）。

【図19】しきい値電圧の補正回路を説明する図（実施例4）。

【図20】表示装置の画素回路の一例を示す図（実施例5）。

10

【図21】ディスペンサ方式（液晶滴下方式）を説明する図（実施例6）。

【図22】本発明の表示装置の一形態であるパネルの上面図と断面図（実施例7）。

【図23】本発明の表示装置の一形態であるパネルの断面図（実施例8）。

【図24】本発明の表示装置の一形態であるパネルの上面図と断面図（実施例9）。

【図25】本発明の表示装置の一形態であるパネルの断面図（実施例9）。

【図26】本発明が適用される電子機器を示す図（実施例10）。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

### 【図 1 1】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図25】

【図24】

【図26】

---

フロントページの続き

審査官 綿引 隆

(56)参考文献 特開2003-098548(JP,A)

特開平08-201853(JP,A)

特開昭61-051878(JP,A)

国際公開第97/043689(WO,A1)

特開平11-340129(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/336

H01L 29/786