(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7664699号**

**(P7664699)**

(45)発行日 令和7年4月18日(2025.4.18)

(24)登録日 令和7年4月10日(2025.4.10)

(51)国際特許分類

|         |                 |     |         |        |         |

|---------|-----------------|-----|---------|--------|---------|

| G 0 9 F | 9/30 (2006.01)  | F I | G 0 9 F | 9/30   | 3 3 8   |

| G 0 9 G | 3/3233(2016.01) |     | G 0 9 F | 9/30   | 3 6 5   |

| G 0 9 G | 3/20 (2006.01)  |     | G 0 9 G | 3/3233 |         |

| H 1 0 D | 89/00 (2025.01) |     | G 0 9 G | 3/20   | 6 1 1 J |

| H 1 0 D | 1/68 (2025.01)  |     | G 0 9 G | 3/20   | 6 2 2 B |

請求項の数 5 (全20頁) 最終頁に続く

(21)出願番号 特願2020-214496(P2020-214496)

(22)出願日 令和2年12月24日(2020.12.24)

(65)公開番号 特開2022-100491(P2022-100491

A)

(43)公開日 令和4年7月6日(2022.7.6)

審査請求日 令和5年12月5日(2023.12.5)

(73)特許権者 520272868

武漢天馬微電子有限公司

中華人民共和国武漢市東湖新技術開発区

流芳園横路8号

(74)代理人 110001678

藤央弁理士法人

(72)発明者 松枝 洋二郎

神奈川県川崎市幸区鹿島田一丁目1番2

号 T i a n m a J a p a n 株式会社内

審査官 瀬戸井 綾菜

最終頁に続く

(54)【発明の名称】 表示装置

**(57)【特許請求の範囲】****【請求項1】**表示装置であつて、

複数の画素回路を含む表示領域と、

前記複数の画素回路に制御信号を出力するドライバと、

を含み、

前記表示領域は、第1領域と、前記第1領域よりも画素回路密度が低い第2領域とを含み、

前記ドライバは、複数の出力バッファを含み、

前記複数の出力バッファは、それぞれ、複数の画素回路に対して同時に制御信号を出力し、

前記複数の出力バッファは、第1出力バッファと、第2出力バッファとを含み、

前記第1出力バッファが制御信号を出力する画素回路の数は、前記第2出力バッファが制御信号を出力する画素回路の数より多く、

前記第1出力バッファの駆動トランジスタのチャネル幅は、前記第2出力バッファの駆動トランジスタのチャネル幅より大きく、

前記複数の出力バッファは、第3出力バッファをさらに含み、前記第3出力バッファが制御信号を出力する画素回路の数は、前記第2出力バッファが制御信号を出力する画素回路の数より少なく、前記第3出力バッファの駆動トランジスタのチャネル幅は、前記第2出力バッファの駆

10

20

動トランジスタのチャネル幅より小さく、

前記第1出力バッファは、前記第2領域を通過することなく前記第1領域を通過する制御線に接続された前記第1領域の画素回路を制御し、

前記第2出力バッファは、前記第1領域及び前記第2領域を通過する制御線に接続されている前記第1領域の画素回路及び前記第2領域の画素回路を制御し、

前記第3出力バッファは、前記第1領域及び前記第2領域を通過する制御線に接続されている前記第1領域の画素回路を制御し、

前記表示装置は、

前記第2出力バッファの出力に接続され、前記第1出力バッファの制御信号の遅延と前記第2出力バッファの制御信号の遅延の差を小さくする第1付加容量と、

前記第2出力バッファの出力に接続された前記第1付加容量より容量値が大きく、前記第3出力バッファの出力に接続された第2付加容量と、

をさらに含み、

前記第1付加容量及び前記第2付加容量は、前記表示領域の外側に配置され、

前記第1付加容量及び前記第2付加容量は、それぞれ、接続された複数導体層の電極をそれぞれ含む二つの容量電極及び前記複数導体層間の絶縁体を含む、

表示装置。

#### 【請求項2】

請求項1に記載の表示装置であって、

前記複数の出力バッファは、前記画素回路においてデータ信号を保持容量に書き込むトランジスタを制御する制御信号を出力する、

表示装置。

#### 【請求項3】

請求項1に記載の表示装置であって、

前記第1出力バッファからの制御信号の遅延、前記第2出力バッファからの制御信号の遅延及び前記第3出力バッファからの制御信号の遅延が等しい、

表示装置。

#### 【請求項4】

請求項1に記載の表示装置であって、

前記第1出力バッファの前記駆動トランジスタ、前記第2出力バッファの前記駆動トランジスタ及び前記第3出力バッファの前記駆動トランジスタは、前記チャネル幅を規定する半導体膜の幅を除いて、同一の構造を有している、

表示装置。

#### 【請求項5】

請求項1に記載の表示装置であって、

前記二つの容量電極に含まれる電極の導体層は、前記表示領域内の、ゲート電極、ソース/ドレイン電極及び他の導体層を含む、

表示装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本開示は、表示装置に関する。

##### 【背景技術】

##### 【0002】

OLE D (Organic Light-Emitting Diode) 素子は電流駆動型の自発光素子であるため、バックライトが不要となる上に、低消費電力、高視野角、高コントラスト比が得られるなどのメリットがあり、フラットパネルディスプレイの開発において期待されている。

##### 【0003】

OLE D 表示装置の表示領域が、画素密度が異なる領域を含むことがある。例えば、い

10

20

30

40

50

くつかのスマートフォンやタブレット型コンピュータなどの携帯端末において、表示領域の下に画像撮像用のカメラが配置される。カメラが外部からの光を受光するために、カメラは、周囲よりも画素密度が小さい領域の下に配置される。

**【先行技術文献】**

**【特許文献】**

**【0004】**

【文献】米国特許出願公開第2008/0036706号

【文献】米国特許出願公開第2008/0231560号

【文献】米国特許出願公開第2019/0057653号

**【発明の概要】**

10

**【発明が解決しようとする課題】**

**【0005】**

画素回路行は、それぞれ、画素回路を制御する制御線に接続される。表示領域が異なる画素密度の領域を含む表示装置において、制御線に接続される画素回路の数は、制御線の位置によって異なり得る。例えば、通常領域のみを通過する制御線に接続される画素回路数は、画素密度が小さい領域を通過する制御線に接続される画素回路数より多い。

**【0006】**

制御線に接続される画素回路の数が異なる場合、それら制御線の負荷が異なる。異なる負荷は、制御信号の異なる遅延を引き起こし、表示領域内の輝度差を発生させ得る。

**【課題を解決するための手段】**

20

**【0007】**

本開示の一態様に係る表示装置は、複数の画素回路を含む表示領域と、前記複数の画素回路に制御信号を出力するドライバと、を含む。前記表示領域は、第1領域と、前記第1領域よりも画素回路密度が低い第2領域とを含む。前記ドライバは、複数の出力バッファを含む。前記複数の出力バッファは、それぞれ、複数の画素回路に対して同時に制御信号を出力する。前記複数の出力バッファは、第1出力バッファと、第2出力バッファとを含む。前記第1出力バッファが制御信号を出力する画素回路の数は、前記第2出力バッファが制御信号を出力する画素回路の数より多い。前記第1出力バッファの駆動トランジスタのチャネル幅は、前記第2出力バッファの駆動トランジスタのチャネル幅より大きい。

**【発明の効果】**

30

**【0008】**

本開示の一態様によれば、画素密度が異なる領域を含む表示装置の表示品質を改善できる。

**【図面の簡単な説明】**

**【0009】**

【図1】OLED表示装置の構成例を模式的に示す。

【図2】画素回路の構成例を示す。

【図3】画素回路の他の構成例を示す。

【図4】表示領域を模式的に示す。

【図5】図4において一点鎖線で囲まれた領域の詳細を示す。

40

【図6】TFT基板上の制御配線のレイアウトを模式的に示す。

【図7】走査ドライバの一つの出力端子の出力バッファ650の回路構成例を示す。

【図8】出力バッファの信号のタイミングチャートを示す。

【図9】制御する画素回路数が異なる三つの出力バッファからの走査信号の時間変化を模式的に示す。

【図10】出力バッファのデバイス構造の一例を模式的に示す平面図である。

【図11】走査ドライバに含まれる、A種類、B種類及びC種類の出力バッファを模式的に示す平面図である。

【図12】出力バッファの出力線に付加された遅延調整用容量の例を示す。

【図13】出力バッファ及び出力バッファの遅延調整用付加容量の構造を模式的に示す平

50

面図である。

【図14】図13におけるXIV-XIV'切断線での断面構造を模式的に示す。

【発明を実施するための形態】

【0010】

以下、添付図面を参照して本開示の実施形態を説明する。本実施形態は本開示を実現するための一例に過ぎず、本開示の技術的範囲を限定するものではないことに注意すべきである。

【0011】

以下の説明において、画素は、表示領域における最小単位であり、单一色の光を発光する要素を示し、副画素とも呼ばれることがある。複数の異なる色の画素、例えば、赤、青及び緑の画素のセットが、一つのカラードットを表示する要素を構成し、主画素と呼ばれることがある。以下において、説明の明確化のために单一色表示を行う要素とカラー表示を行う要素を区別する場合に、それぞれ、副画素及び主画素と呼ぶ。なお、本明細書の特徴は、モノクロ表示を行う表示装置に適用することができ、その表示領域はモノクロ画素で構成されている。

10

【0012】

以下において、表示装置の構成例を説明する。表示装置の表示領域は、相対的に画素密度が小さい第2領域（低密度又は低解像度領域とも呼ぶ）と、相対的に画素密度が大きい第1領域（通常領域又は通常解像度領域とも呼ぶ）とを含む。通常領域よりも画素密度が低い複数の低密度領域が配置されてもよく、これらの画素密度が異なっていてもよい。以下に説明する例において、画素の発光素子は電流駆動型の素子であり、例えば、OLED（Organic Light-Emitting Diode）素子である。

20

【0013】

画素の輝度は、画素回路によって制御される。複数の画素からなる画素回路行は、それぞれ、画素回路を制御する制御線に接続される。制御線は、走査線や発光制御線を含み得る。表示領域が異なる画素密度の領域を含む表示装置において、制御線に接続される画素回路の数は、制御線の位置によって異なり得る。例えば、通常領域のみを通過する制御線に接続される画素回路数は、画素密度が小さい領域を通過する制御線に接続される画素回路数より多い。

【0014】

30

制御線に接続される画素回路の数が異なる場合、それら制御線の負荷が異なる。異なる負荷は、制御信号の異なる遅延を引き起こす。制御線出力の遅延は、画素間の輝度差を発生させ得る。特に、走査線の遅延時間の差は、画素回路内の駆動トランジスタのゲートソース電圧 $V_{gs}$ を変動させ得る。上述のように、通常領域のみを通過する制御線と低密度領域を通過する制御線の負荷が異なるため、輝度差が視認されやすく、その結果、通常領域と低密度領域の境界線を視認されやすくし得る。

【0015】

以下において、通常領域のみを通過する制御線を駆動する出力バッファ回路と、低密度領域を通過する制御線を駆動する出力バッファ回路のために、制御線間の負荷の相違による遅延の差を小さくする回路デバイス構造を説明する。制御信号の遅延差を低減するための構造は、表示領域外に実装される。

40

【0016】

本明細書の一実施形態において、通常領域のみを通過する制御線の出力バッファの駆動トランジスタのチャネル幅は、低密度領域を通過する制御線の出力バッファの駆動トランジスタのチャネル幅より大きい。これにより、二つの制御線の制御信号の遅延差を小さくすることができる。

【0017】

本明細書の一実施形態は、表示領域外において、低密度領域を通過する制御線に対して、通常領域のみを通過する制御線と比較して、遅延時間を調整するための容量を追加する。これにより、二つの制御線の制御信号の遅延差を小さくすることができる。チャネル幅

50

の異なる駆動トランジスタ及び表示領域外の追加容量の双方が一つの表示装置に実装されてもよい。これにより、より容易に制御線間の制御信号遅延差を小さくすることができる。

#### 【0018】

##### [表示装置の構成]

図1を参照して、本明細書の一実施形態に係る、表示装置の全体構成を説明する。なお、説明をわかりやすくするため、図示した物の寸法、形状については、誇張して記載している場合もある。以下において、表示装置の例として、OLED表示装置を説明する。

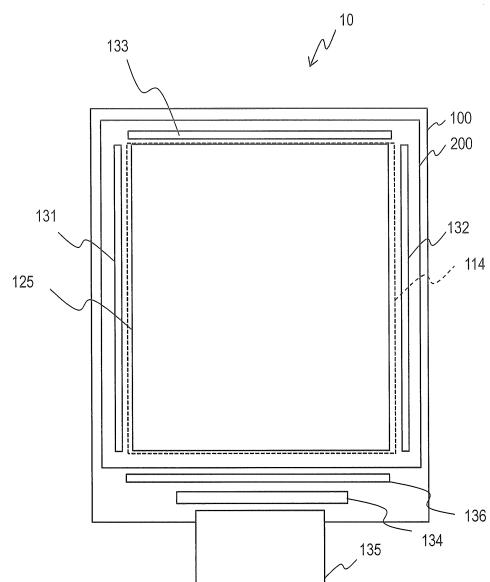

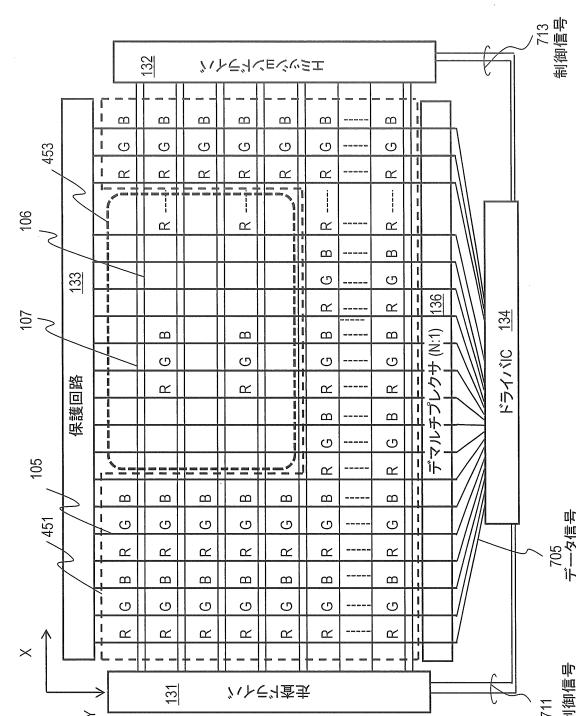

#### 【0019】

図1は、OLED表示装置10の構成例を模式的に示す。OLED表示装置10は、OLED素子(発光素子)が形成されるTFT(Thin Film Transistor)基板100と、OLED素子を封止する封止構造部200を含んで構成されている。TFT基板100の表示領域125の外側のカソード電極形成領域114の周囲に、制御回路が配置されている。具体的には、走査ドライバ131、エミッションドライバ132、静電気放電保護回路133、ドライバIC134、デマルチプレクサ136が配置されている。

10

#### 【0020】

ドライバIC134は、FPC(Flexible Printed Circuit)135を介して外部の機器と接続される。走査ドライバ131はTFT基板100の走査線を駆動する。エミッションドライバ132は、エミッション制御線を駆動して、各画素の発光を制御する。静電気放電保護回路133は、TFT基板における素子の静電破壊を防ぐ。ドライバIC134は、例えば、異方性導電フィルム(ACF:Anisotropic Conductive Film)を用いて実装される。

20

#### 【0021】

ドライバIC134は、走査ドライバ131及びエミッションドライバ132に電源、及び、タイミング信号を含む制御信号を与える。さらに、ドライバIC134は、デマルチプレクサ136に、電源及びデータ信号を与える。デマルチプレクサ136は、ドライバIC134の一つのピンの出力を、d本(dは2以上の整数)のデータ線に順次出力する。デマルチプレクサ136は、ドライバIC134からのデータ信号の出力先データ線を、走査期間内にd回切り替えることで、ドライバIC134の出力ピン数のd倍のデータ線を駆動する。

30

#### 【0022】

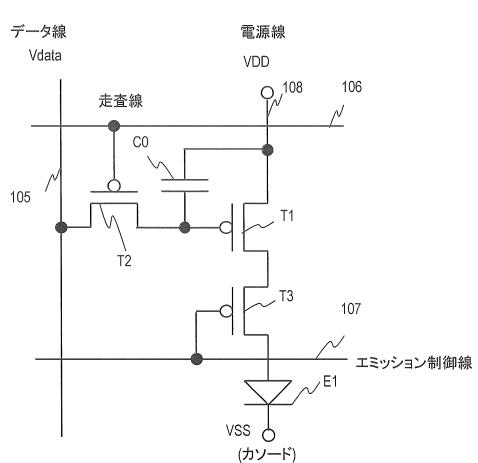

##### [画素回路構成]

TFT基板100上には、複数の副画素のアノード電極にそれぞれ供給する電流を制御する複数の画素回路が形成されている。図2は、画素回路の構成例を示す。各画素回路は、駆動トランジスタT1と、選択トランジスタT2と、エミッショントランジスタT3と、保持容量C0とを含む。画素回路は、OLED素子E1の発光を制御する。トランジスタは、TFTである。

#### 【0023】

図2の画素回路において、駆動トランジスタの閾値電圧を補償するための回路構成は省略されている。図2の画素回路は例であって、画素回路は他の回路構成を有してもよい。図2の画素回路はP型TFTを使用しているが、画素回路はNチャネル型TFTを使用してもよい。

40

#### 【0024】

選択トランジスタT2は副画素を選択するスイッチである。選択トランジスタT2はPチャネル型(P型)TFTであり、ゲート端子は、走査線106に接続されている。ソース端子は、データ線105に接続されている。ドレイン端子は、駆動トランジスタT1のゲート端子に接続されている。

#### 【0025】

駆動トランジスタT1はOLED素子E1の駆動用のトランジスタ(駆動TFT)である。駆動トランジスタT1はP型TFTであり、そのゲート端子は選択トランジスタT2

50

のドレイン端子に接続されている。駆動トランジスタT1のソース端子はアノード電源電位VDDを伝送する電源線108に接続されている。ドレイン端子は、エミッショントランジスタT3のソース端子に接続されている。駆動トランジスタT1のゲート端子とソース端子との間に保持容量C0が形成されている。

#### 【0026】

エミッショントランジスタT3は、OLED素子E1への駆動電流の供給と停止を制御するスイッチである。エミッショントランジスタT3はP型 TFTであり、ゲート端子はエミッション制御線107に接続されている。エミッショントランジスタT3のソース端子は駆動トランジスタT1のドレイン端子に接続されている。エミッショントランジスタT3のドレイン端子は、OLED素子E1に接続されている。OLED素子E1のカソードにはカソード電源電位VSSが与えられている。10

#### 【0027】

次に、画素回路の動作を説明する。走査ドライバ131が走査線106に選択パルスを出力し、選択トランジスタT2をオン状態にする。データ線105を介してドライバIC134から供給されたデータ電圧は、保持容量C0に格納される。保持容量C0は、格納された電圧を、1フレーム期間を通じて保持する。保持電圧によって、駆動トランジスタT1のコンダクタンスがアナログ的に変化し、駆動トランジスタT1は、発光階調に対応した順バイアス電流をOLED素子E1に供給する。

#### 【0028】

エミッショントランジスタT3は、駆動電流の供給経路上に位置する。エミッションドライバ132は、エミッション制御線107に制御信号を出力して、エミッショントランジスタT3のオンオフを制御する。エミッショントランジスタT3がオン状態のとき、駆動電流がOLED素子E1に供給される。エミッショントランジスタT3がオフ状態のとき、この供給が停止される。エミッショントランジスタT3のオンオフを制御することにより、1フレーム周期内の点灯期間（デューティ比）を制御することができる。20

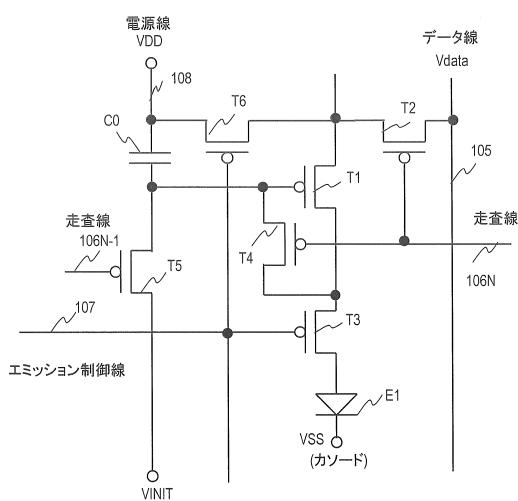

#### 【0029】

画素回路の構成は、図2の構成例に限定されない。図3は、画素回路の他の構成例を示す。画素回路は、駆動トランジスタT1、データ信号書き込みトランジスタT2及び発光制御トランジスタT3に加えて、トランジスタT4、T5及びT6を含む。トランジスタT1からT6は、全てP型 TFTである。トランジスタT2は、駆動トランジスタT1のソースとデータ線105との間に接続されている。30

#### 【0030】

トランジスタT4は、駆動トランジスタT1のゲートとドレインに接続されている。トランジスタT5は、駆動トランジスタT1のゲートと電源電位VINITを与える電源線とに接続されている。トランジスタT6は、駆動トランジスタT1のソースと電源電位VDDを与える電源線108とに接続されている。

#### 【0031】

走査線106N-1は、走査ドライバ131のN-1段目の出力端子から走査信号を伝送する。走査線106Nは、走査ドライバ131のN段目の出力端子から走査信号を伝送する。トランジスタT2及びT4は、走査線106Nの走査信号により制御される。トランジスタT5は、走査線106N-1の走査信号により制御される。トランジスタT6は、エミッション制御線107が伝送する発光制御信号により制御される。40

#### 【0032】

走査線106N-1が、ローレベルのパルスを画素回路に与えた後、走査線106Nが、ローレベルのパルスを画素回路に与える。これらパルスが与えられる期間において、エミッション制御線107が伝送する発光制御信号はハイレベルである。走査線106N-1のレベルがローである間、トランジスタT5はONであり、他のトランジスタはOFFである。このため、駆動トランジスタT1のゲートに初期電位VINITが与えられ、ゲート電位が初期化される。

#### 【0033】

10

20

30

40

50

次に、走査線 106N のレベルがローである間、トランジスタ T2 及び T4 が ON である。他のトランジスタは OFF である。トランジスタ T4 が ON であるので、駆動トランジスタ T1 はダイオード接続状態である。データ線 105 からデータ信号は、トランジスタ T2、T1 及び T4 を介して保持容量 C0 に書き込まれる。このとき、駆動トランジスタ T1 の閾値電圧が補償された電圧が、保持容量 C0 に書き込まれる。

#### 【0034】

その後、トランジスタ T2 及び T4 が OFF され、発光制御トランジスタ T3 及び T6 が ON される。駆動トランジスタ T1 からの駆動電流が OLED 素子 E1 に与えられ、OLED 素子 E1 が発光する。

#### 【0035】

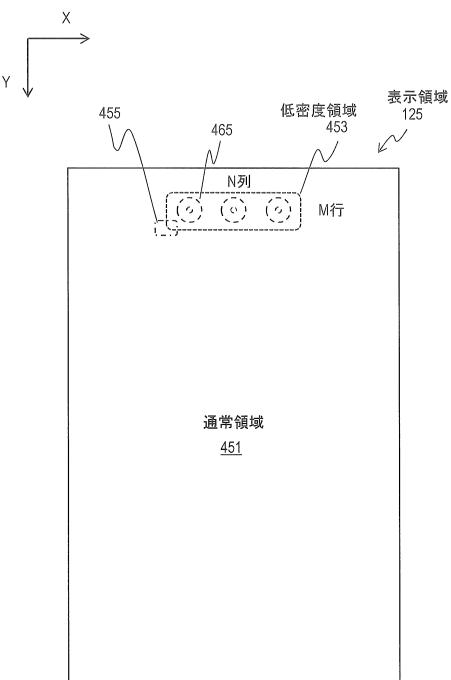

##### [画素レイアウト]

図 4 は、表示領域 125 を模式的に示す。OLED 表示装置 10 は、例えば、スマートフォンやタブレット端末のようなモバイル端末に実装される。表示領域 125 は、通常の画素密度を有する通常領域 451 と、通常領域 451 の画素密度（解像度）よりも低い画素密度（解像度）を有する低密度領域 453 を含む。1 又は複数のカメラ 465 が、低密度領域 453 の下に配置されている。図 4 において、複数のカメラのうちの一つが例として符号 465 で指示されている。以下において、表示領域 125 における副画素又は主画素を、表示副画素又は表示主画素と呼ぶことがある。

#### 【0036】

低密度領域 453 はカメラ 465 の視認側に配置されており、カメラ 465 は、低密度領域 453 と通過した光によって視認側の物体を撮影する。カメラ 465 による撮影を妨げないように、低密度領域 453 の画素密度は、周囲の通常領域 451 の画素密度より低い。不図示の制御装置は、例えば、カメラ 465 により撮像した画像のデータを OLED 表示装置 10 に送信する。なお、図 4 は、低密度領域の例として、カメラがその下に配置されている領域を示すが、本明細書における特徴は、他の目的のために画素密度が相対的に低い領域を含む表示装置に適用できる。

#### 【0037】

低密度領域 453 は、N 列 M 行の主画素で構成されている。主画素列は、図 4 における上下方向である Y 軸に沿って配列された主画素で構成されている。主画素行は、図 4 における左右方向である X 軸に沿って配列された主画素で構成されている。

#### 【0038】

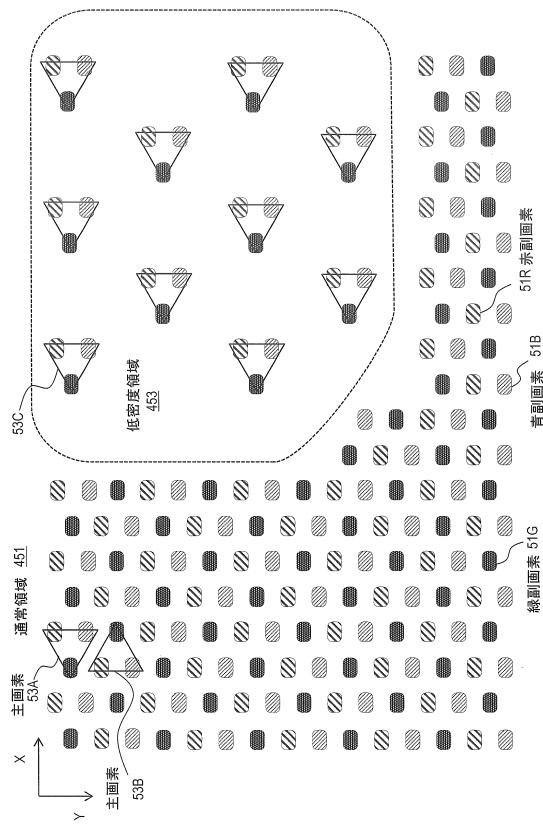

図 5 は、図 4 において一点鎖線で囲まれた領域 455 の詳細を示す。図 5 は、デルタナプラ配置（単にデルタ配置とも呼ぶ）の画素レイアウトを示す。なお、本実施形態における特徴は、他の画素レイアウトを有する表示装置に適用することができる。

#### 【0039】

領域 455 は、通常領域 451 と低密度領域 453 の一部の境界の近傍の領域である。図 5 に示す例において、低密度領域 453 の画素密度は、通常領域 451 の 1/4 である。低密度領域 453 の副画素は、同一の画像データに対して、通常領域 451 の副画素の 4 倍の輝度で発光するように制御される。

#### 【0040】

表示領域 125 は、面内に配置されている、複数の赤副画素 51R、複数の緑副画素 51G、及び複数の青副画素 51B で構成されている。図 5 において、一つの赤副画素、一つの緑副画素、及び一つの青副画素が、例として、符号で指示されている。図 5 において、同一のハッチングの（丸い角の）四角は、同一色の副画素を示す。図 5 において、副画素の形状は四角であるが、副画素の形状は任意であって、例えば、六角形又は八角形であつてもよい。

#### 【0041】

副画素列は、同一の X 軸位置の副画素からなる、Y 軸に沿って延びる配列である。副画素列において、赤副画素 51R、青副画素 51B 及び緑副画素 51G が、サイクリックに配列されている。例えば、副画素列の副画素は、同一のデータ線に接続される。副画素行

10

20

30

40

50

は、同一のY軸位置の同一色の副画素からなる、X軸に沿って延びる配列である。例えば、副画素行の副画素は、同一の走査線に接続される。

#### 【0042】

図5の構成例において、通常領域451は、マトリックス状に配置されている、第1種主画素53A及び第2種主画素53Bの、2種類の主画素を含む。図5において、一つの第1種主画素のみが、例として、符号53Aで指示されている。また、一つの第2種主画素のみが、例として、符号53Bで指示されている。なお、サブピクセルレンダリング技術が使用される場合、外部からの画像データの主画素とパネルの主画素とは一致しない。

#### 【0043】

図5において、第1種主画素53Aは、一つの頂点が左側にあり、二つの頂点が右側にある三角形で示されている。また、第2種主画素53Bは、一つの頂点が右側にあり、二つの頂点が左側にある三角形で示されている。

#### 【0044】

第1種主画素53Aにおいて、赤副画素51R及び青副画素51Bは、同一の副画素列において連続して配置されている。緑副画素51Gが含まれる副画素列は、赤副画素51R及び青副画素51Bが含まれる副画素列の左側に隣接している。緑副画素51Gは、Y軸位置において、赤副画素51Rと青副画素51Bの中央に位置している。

#### 【0045】

第2種主画素53Bにおいて、赤副画素51R及び青副画素51Bは、同一の副画素列において連続して配置されている。緑副画素51Gが含まれる副画素列は、赤副画素51R及び青副画素51Bが含まれる副画素列の右側に隣接している。緑副画素51Gは、Y方向において、赤副画素51Rと青副画素51Bの中央に位置している。

#### 【0046】

低密度領域453は、第1種主画素53Aと同一構成の主画素53Cで構成されている。図5は、5列4行の主画素53Cを示す。主画素53Cは規則的に配置されており、X軸及びY軸に沿った主画素間距離は一定である。また、隣接する主画素行は、互いに半ピッチだけずれている。

#### 【0047】

隣接する主画素53Cの間ならびに低密度領域453と通常領域451の間には、カメラ465によって撮像するため、視認側からカメラ465に光を取り込めるように透過領域（不図示）が、好適な配置で設けられている。

#### 【0048】

低密度領域453の副画素レイアウトは、通常領域451のレイアウトから一部の副画素を除いた構成を有している。低密度領域453の副画素は、通常領域の副画素と共に副画素行及び副画素列を構成する。低密度領域453の各副画素列は、通常領域451の対応する副画素列と共に一つの副画素列を構成し、同一のデータ線に接続される。低密度領域453の各副画素行は、通常領域451の対応する副画素行と共に一つの副画素行を構成し、同一の走査線に接続される。

#### 【0049】

##### [配線レイアウト]

以下において、OLED表示装置10の配線レイアウト例を説明する。図6は、TFT基板100上の制御配線のレイアウトを模式的に示し、図6の構成例において、通常領域451の画素回路のレイアウトは、ストライプ配置である。具体的には、Y軸に沿って延びる副画素列は、同一色の副画素で構成されている。X軸に沿って延びる副画素行は、サイクリックに配置された、赤副画素、緑副画素及び青副画素で構成されている。低密度領域453は、通常領域451の画素レイアウトから、一部の画素を間引いた構成を有している。低密度領域453における空白領域には、OLED素子を含む画素回路は形成されおらず、透過領域と配線のみが配置されている。

#### 【0050】

なお、透過領域に隣接する主画素53A、53Cの画素回路を構成する各トランジスタ

10

20

30

40

50

は適切に遮光（不図示）されている。その理由は、カメラでの撮影に伴って、透明領域には視認側から外光が入射するので、TFT基板100やOLED素子を形成する薄膜層を介して画素回路にも外光が入り、トランジスタに光アシスト効果が生じない様にするためである。光アシスト効果が生じると、トランジスタのしきい値電圧のシフトを引き起こすため、駆動電流が変化してしまう。

#### 【0051】

複数の走査線106が、走査ドライバ131からX軸に沿って延びている。また、複数のエミッション制御線107が、エミッションドライバ132からX軸に沿って延びている。図6は、例として、一つの走査線及び一つのエミッション制御線を、それぞれ符号106及び107で指示している。10

#### 【0052】

図6に示す構成例において、走査線106は、通常領域451及び低密度領域453の選択信号（走査信号とも呼ぶ）を伝送する。また、エミッション制御線107は、通常領域451及び低密度領域453のエミッション制御信号を伝送する。選択信号及びエミッション制御信号は、画素回路の制御信号である。

#### 【0053】

ドライバIC134は、配線711によって走査ドライバ131に制御信号を送信し、配線713によってエミッションドライバ132に制御信号を送信する。ドライバIC134は、外部からの画像データ（画像信号）に基づき、走査ドライバ131から走査信号（選択パルス）及びエミッションドライバ132のエミッション制御信号のタイミングを制御する。20

#### 【0054】

ドライバIC134は、配線705によって、通常領域451及び低密度領域453の副画素のデータ信号をデマルチプレクサ136に与える。図6は、1本の配線を例として、符号705で指示している。ドライバIC134は、外部からの映像データのフレーム内の1又は複数の副画素の階調レベルから、通常領域451及び低密度領域453の各副画素に対応する各画素回路のデータ信号を決定する。

#### 【0055】

デマルチプレクサ136は、ドライバIC134の一つの出力を、走査期間内にN本（Nは2以上の整数）のデータ線105に順次出力する。図6において、Y軸に沿って延びる複数のデータ線のうち、1本のデータ線が、例として符号105で指示されている。30

#### 【0056】

##### [出力バッファ]

以下において、走査ドライバ131からの制御信号遅延差を低減する構成を説明する。以下の説明は、エミッションドライバ132に対しても適用してもよい。図4から6を参照して説明したように、低密度領域453において走査線に接続される画素回路の密度は、通常領域451で走査線に接続される画素回路の密度より小さい。以下に説明する例において、走査線は、接続される画素回路数に応じて三つのグループに分けられるとする。

#### 【0057】

A種類の走査線は低密度領域453を通過することなく通常領域451のみを通過する。A種類の走査線に接続される画素回路は、通常領域451内の画素回路のみで構成されており、接続されている画素回路数は最も多い。40

#### 【0058】

B種類の走査線は、通常領域451及び低密度領域453を通過する。B種類の走査線に接続されている画素回路は、通常領域451及び低密度領域453の画素回路で構成されている。B種類の走査線に接続されている画素回路数は、A種類の走査線の画素回路数より少ない。

#### 【0059】

C種類の走査線は、通常領域451及び低密度領域453を通過する。C種類の走査線に接続されている画素回路は、通常領域451の画素回路のみで構成されている。つまり50

、C種類の走査線は、低密度領域453の画素回路が形成されていない非発光領域を通過する。C種類の走査線に接続されている画素回路数は、B種類の走査線の画素回路数より少ない、つまり、最も少ない。

#### 【0060】

図2の画素回路例に示すように、走査ドライバ131の出力端子は、一つの画素回路行のみに接続される場合や、図3の画素回路例に示すように、異なる画素回路行の異なる走査線に接続され、それらに同時に走査信号を出力する場合もある。以下に説明する例においては、走査ドライバ131の出力端子は、上記走査線の三つの種類と同様分類されるものとする。走査ドライバ131の一つの出力端子は、一つの出力バッファが対応する。なお、一つの出力バッファが制御する画素回路の数の種類は、上記3種類に限定されず、表示装置の設計に依存して、2種類又は4種類以上であり得る。10

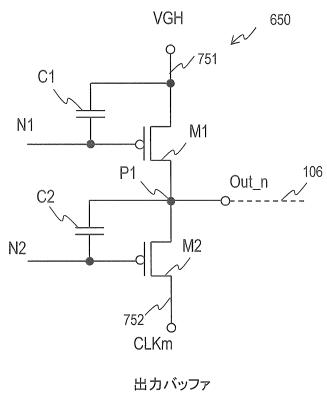

#### 【0061】

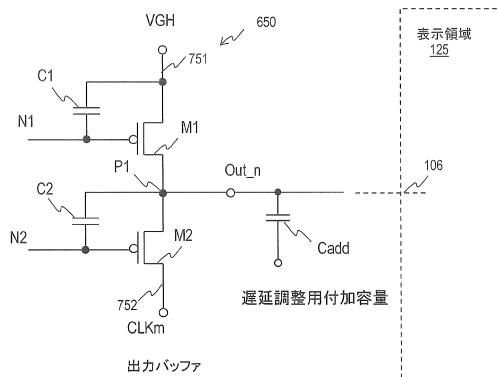

図7は、走査ドライバ131の一つの出力端子の出力バッファ650の回路構成例を示す。図7は、n段目の出力バッファを示す。出力バッファ650は、ハイレベル電位VGHを与える電源線751とクロック信号CLKmを与えるクロック線752との間ににおいて直列に接続された二つの駆動トランジスタM1及びM2を含む。

#### 【0062】

図7の構成例において、トランジスタM1及びM2はP型TFTであり、それらのゲートに信号N1及びN2がそれぞれ与えられる。出力バッファ650は、トランジスタM1及びM2の中間ノードP1から、走査信号(制御信号)Out\_nを走査線106に出力する。20

#### 【0063】

トランジスタM1のゲートとハイレベル電位VGHを与える電源線751との間に容量C1が接続されている。トランジスタM2のゲートと、トランジスタM1及びM2の中間ノードP1との間に容量C12が接続されている。

#### 【0064】

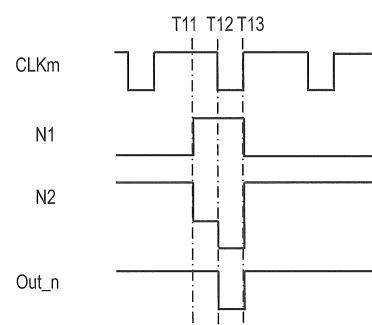

図8は、出力バッファ650の信号のタイミングチャートを示す。クロック信号CLKmは、一定周期でハイレベルとローレベルとの間で変化する。時刻T11において、信号N1がローレベルからハイレベルに変化し、信号N2がハイレベルからローレベルに変化する。クロック信号CLKmはハイレベルである。出力信号Out\_nは、基準のハイレベルである。30

#### 【0065】

時刻T12において、クロック信号CLKmがハイレベルからローレベルに変化し、信号N2はさらに低いレベルに変化する。出力信号Out\_nは、ハイレベルからローレベルに変化する。時刻T13において、クロック信号CLKmがローレベルからハイレベルに変化し、信号N1はハイレベルからローレベルに変化し、信号N2はハイレベルに変化する。出力信号Out\_nは、ローレベルからハイレベルに変化する。出力信号Out\_nの選択パルスは、時刻T12から時刻T13まで出力される。

#### 【0066】

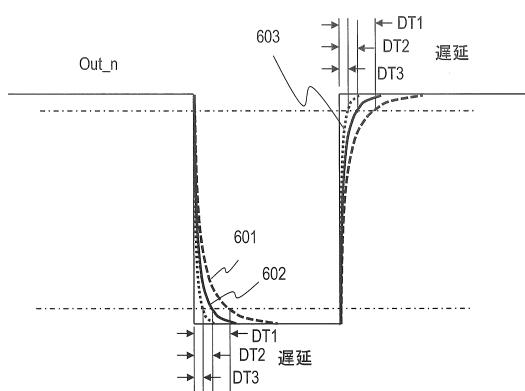

図9は、制御する画素回路数が異なる三つの出力バッファからの走査信号の時間変化を模式的に示す。横軸は時間を示し、縦軸は走査信号の電位レベルを示す。走査信号601の遅延DT1が最も大きい。走査信号602の遅延DT2は、走査信号601の遅延DT1よりも小さい。走査信号603の遅延DT3は最も小さい。40

#### 【0067】

遅延が最も大きい走査信号601は、通常領域451の画素回路のみを駆動し、駆動する画素回路数が最も多いA種類出力バッファの走査信号である。遅延が次に大きい走査信号602は、通常領域451及び低密度領域453の画素回路を駆動し、駆動する画素回路数が次に多いB種類出力バッファの走査信号である。遅延が最も小さい走査信号603、通常領域451及び低密度領域453の非発光領域を通過して通常領域451の画素回路のみを駆動し、駆動する画素回路数が最も少ないC種類出力バッファの走査信号である50

。 A 種類出力バッファ、B 種類出力バッファ及びC 出離出力バッファは、それぞれ、第1 出力バッファ、第2 出力バッファ及び第3 出力バッファである。

#### 【 0 0 6 8 】

図9に示すように、三種類の出力バッファの走査信号（駆動信号）の遅延は、それぞれ異なる。これら遅延の差を小さくすることで、画素の発光輝度の差を小さくすることができる。以下において、出力バッファの駆動トランジスタのチャネル幅を調整することで、遅延時間の差を小さくする手法を説明する。チャネル幅を最適化することで、遅延時間T1、T2 及びT3 の差をなくすことができる。

#### 【 0 0 6 9 】

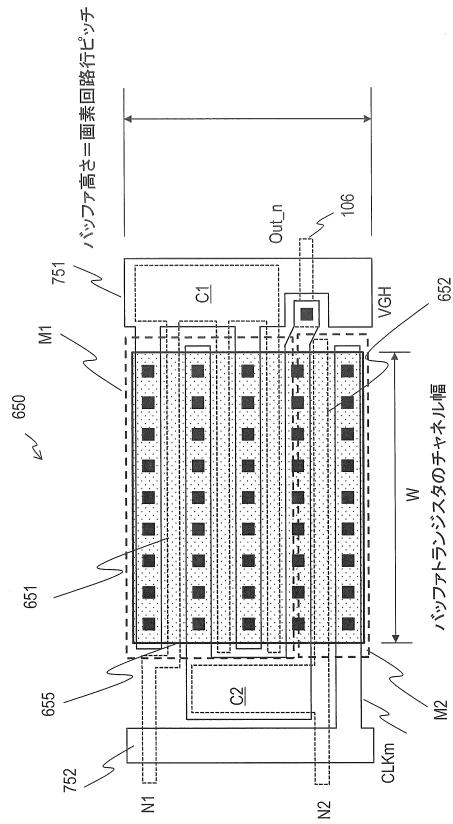

異なる種類の出力バッファの間の駆動トランジスタのチャネル幅について説明する前に、図7を参照して説明した出力バッファのデバイス構造を説明する。図10は、出力バッファ650のデバイス構造の一例を模式的に示す平面図である。図7に示すように、出力バッファ650は、トランジスタM1及びM2並びに容量C1及びC2を含む。出力バッファ650のバッファ高さは、画素回路行ピッチと一致する。バッファ高さは、図10における上下方向のサイズである。

10

#### 【 0 0 7 0 】

図10に示す構成例において、半導体膜655が最下層であり、ソース／ドレイン金属層（M2金属層）が最上層であり、ゲート電極層（M1金属層）がそれらの中間の層である。異なる層を示すため、それらは異なる様で示されている。半導体膜655は、ドットパターンで埋められた実線の矩形で示されている。ソース／ドレイン金属層は実線で示され、ゲート電極層は破線で示されている。

20

#### 【 0 0 7 1 】

ソース／ドレイン金属層は、表示領域125内のトランジスタのソース／ドレイン電極、トランジスタM1及びM2のソース／ドレイン電極、電源線751及びクロック信号線752を含む。ゲート電極層は、表示領域125内のトランジスタのゲート電極、トランジスタM1及びM2のゲート電極651、652及び容量C1、C2の下部電極を含む。電源線751は容量C1の上部電極を含み、クロック信号線752は容量C2の上部電極を含む。

#### 【 0 0 7 2 】

図10に示す構成例において、トランジスタM1は、半導体膜655と平面視において重なる三つのゲート電極651を含む。図10は、一つのゲート電極を例として符号651で示す。トランジスタM2は、半導体膜655と平面視において重なる一つのみのゲート電極652を含む。トランジスタM1のチャネル幅は、トランジスタM2のチャネル幅の3倍であり、トランジスタM1の駆動能力はトランジスタM2の駆動能力より高い。図10に示すように、半導体膜655の左右方向の寸法Wを変化させることで、トランジスタM1、M2のチャネル幅を変化させることができる。

30

#### 【 0 0 7 3 】

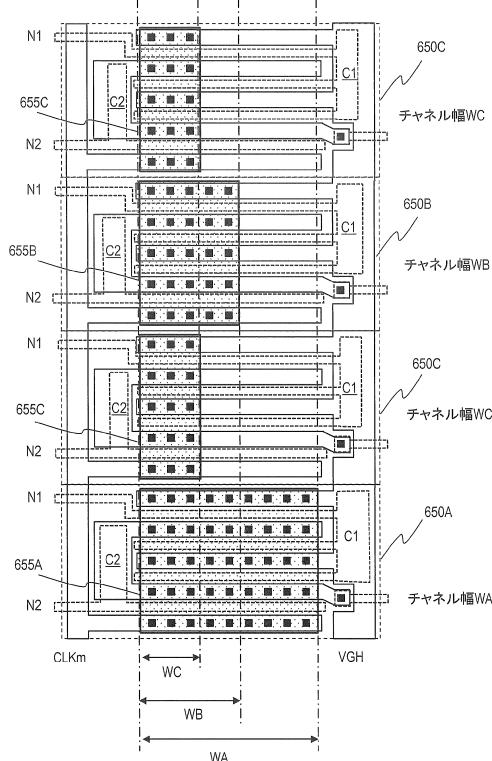

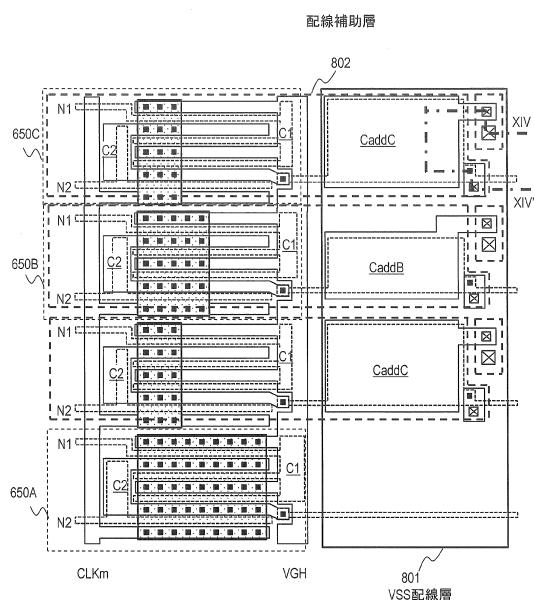

図11は、走査ドライバ131に含まれる、A種類、B種類及びC種類の出力バッファを模式的に示す平面図である。図11は、一つのA種類出力バッファ650A、一つのB種類出力バッファ650B、及び二つのC種類出力バッファ650Cを示す。

40

#### 【 0 0 7 4 】

A種類、B種類及びC種類出力バッファ650A、650B及び650Cは、それぞれ、チャネル幅WA、WB及びWCを有する。チャネル幅WA、WB及びWCは異なり、チャネル幅WAが最も大きく、チャネル幅WCが最も小さい。

#### 【 0 0 7 5 】

A種類出力バッファ650Aは、通常領域451のみを通過する走査線を駆動する。A種類出力バッファ650Aは、最も多くの画素回路を駆動する出力バッファであり、通常領域451の画素回路のみを駆動する。

#### 【 0 0 7 6 】

B種類出力バッファ650Bは、通常領域451及び低密度領域453を通過する走査

50

線を駆動する。B種類出力バッファ650Bは、次に多くの画素回路を駆動する出力バッファであり、通常領域451及び低密度領域453の画素回路を駆動する。

#### 【0077】

C種類出力バッファ650Cは、通常領域451及び低密度領域453を通過する走査線を駆動する。C種類出力バッファ650Cは、最も少ない画素回路を駆動する出力バッファであり、通常領域451の画素回路のみを駆動する。

#### 【0078】

上述のように、出力バッファ650A、650B、650Cが駆動する画素回路数に応じたチャネル幅WA、WB、WCを有することで、走査信号の遅延差を小さくすることができる。一例において、出力バッファ650A、650B、650Cからの信号の遅延が同等となるように、チャネル幅WA、WB、WCが決定されている。10

#### 【0079】

図11に示す構成例において、出力バッファ650A、650B、650Cは、異なる幅の半導体膜655A、655B、655Cを含む。半導体膜655A、655B、655Cの幅は、図11における左右方向のサイズである。半導体膜655A、655B、655Cの幅を大きくすることで、トランジスタM1及びM2のチャネル幅を大きくし、小さくすることで、トランジスタM1及びM2のチャネル幅を小さくできる。

#### 【0080】

出力バッファ650A、650B、650Cの間ににおいて、トランジスタM1及びM2のデバイス構造(積層構造)のパラメータは、半導体膜655A、655B、655Cの幅以外、共通である。つまり、出力バッファ650A、650B、650CのトランジスタM1及びM2において、半導体膜655A、655B、655Cの幅のみが異なる。このように、トランジスタがチャネル幅を規定する半導体膜の幅を除いて同一の構造を有することで、異なるチャネル幅のトランジスタを含む出力バッファを容易に設計できる。20

#### 【0081】

図11の構成例において、出力バッファ650A、650B、650Cは、異なる容量値の容量C1及びC2を含む。出力バッファ650Aの容量C1の容量値は、出力バッファ650B、650Cの容量C1の容量値より大きい。出力バッファ650Cの容量C1の容量値は、出力バッファ650A、650Bの容量C1の容量値より小さい。出力バッファ650Aの容量C2の容量値は、出力バッファ650B、650Cの容量C2の容量値より大きい。30出力バッファ650Cの容量C2の容量値は、出力バッファ650A、650Bの容量C2の容量値より小さい。図11の構成例において、容量C1、C2の異なる値は、ゲート電極層に含まれるこれらの下部電極の異なる面積で実現されている。

#### 【0082】

##### [遅延調整用付加容量]

次に、遅延調整用の容量を出力バッファの出力に付加することで、出力バッファの間の遅延差を低減する方法を説明する。図12は、出力バッファ650の出力線に付加された遅延調整用容量の例を示す。出力バッファ650の回路構成は、図7を参照して説明した通りである。

#### 【0083】

遅延調整用付加容量Caddは、表示領域125と出力バッファ650のトランジスタM1、M2との間の領域に配置される。遅延調整用付加容量Caddの一方端は出力バッファ650の出力に電気的に接続され、他端はいずれかの電源に電気的に接続される。遅延調整用付加容量Caddは、例えば、出力バッファ650の正電源、出力バッファ650の負電源、表示領域125のアノード電源、表示領域125のカソード電源のいずれかに接続することができる。40

#### 【0084】

例えば、B種類出力バッファ650Bの出力に、容量CaddBが追加され、C種類出力バッファ650Cの出力に容量CaddCが追加される。容量CaddBは第1付加容量であり、容量CaddCは第2付加容量である。A種類出力バッファ650Aのために50

付加容量は不要である。付加容量 CaddC は、付加容量 CaddB より大きい。付加容量 CaddB、CaddC の大きさを適切に選択することで、A 種類出力バッファ 650A、B 種類出力バッファ 650B、C 種類出力バッファ 650C の間の遅延差を小さくすることができる。

#### 【0085】

出力バッファ 650A、650B、650C それぞれの走査線容量を、CscanA、CscanB、CscanC とする。次の式が満たされる場合、出力バッファ 650A、650B、650C からの信号の遅延を同等のものとすることができます。

$$C_{\text{scan}}A = C_{\text{scan}}B + C_{\text{add}}B = C_{\text{scan}}C + C_{\text{add}}C$$

#### 【0086】

付加容量のみで遅延差を大きく低減するためには、付加容量のための大きな面積が必要となり、額縁領域を広げることになり得る。そのため、上述のような出力バッファのバッファサイズ（チャネル幅）の調整と付加容量の双方を採用して、出力バッファ 650A、650B、650C 間の信号遅延差を低減してもよい。

#### 【0087】

図 13 は、出力バッファ及び出力バッファの遅延調整用付加容量の構造を模式的に示す平面図である。図 11 に示す出力バッファに対して、さらに、付加容量が追加されている。出力バッファ 650A、650B 及び 650C の構造は、図 11 を参照して説明した通りである。

#### 【0088】

出力バッファ 650B の出力に、付加容量 CaddB が接続されている。また、出力バッファ 650C の出力に、付加容量 CaddC が接続されている。付加容量 CaddC の容量値は、付加容量 CaddB の容量値より大きい。図 13 の構造例において、付加容量 CaddC の面積が付加容量 CaddB の面積より大きい。他の容量パラメータの値は同一である。付加容量 CaddB は、出力バッファ 650B と表示領域 125 との間に配置され、付加容量 CaddC は、出力バッファ 650C と表示領域 125 との間に配置されている。

#### 【0089】

図 13 の構成例において、付加容量は、TFT 基板 100 上の複数の導体層及び絶縁体層で構成される。これにより、少ない面積で付加容量の容量値を大きくすることができる。図 13 の構成例において、ソース / ドレイン金属層、ゲート電極層、VSS 配線層 801 及び配線補助層 802 が、それぞれ、付加容量の電極の一部を含む。VSS 配線層 801 は、OLED 素子 E1 のカソード電位 VSS を伝送する。

#### 【0090】

配線補助層 802 はパネル周辺部において折り曲げ実装する部分の配線の耐久性を高めるために設けられる配線層であり、ソース / ドレイン電極配線層より上でアノード電極層より下の位置に設けられる。折り曲げ部分の配線補助層 802 以外の無機膜を総て除去することで、フレキシブル基板の耐久性を高めることができる。

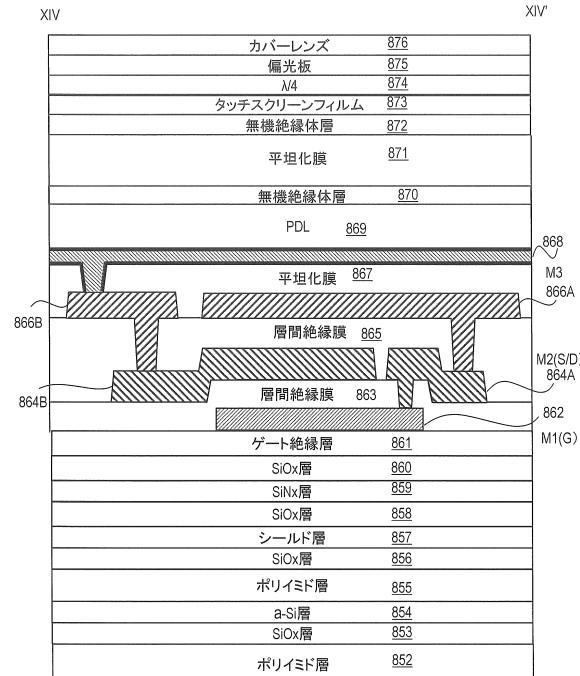

#### 【0091】

以下において、付加容量の構造の詳細を説明する。図 14 は、図 13 における XIV-XIV' 切断線での断面構造を模式的に示す。以下の説明において、上下は、図面における上下を示す。図 14 に示す積層構造を構成する層は、表示領域 125 内にも存在している。OLED 表示装置 10 は、下層から、ポリイミド層 852、シリコン酸化物層 (SiOx 層) 853、アモルファスシリコン層 (a-Si 層) 854、ポリイミド層 855 を含む。

#### 【0092】

OLED 表示装置 10 は、さらに、ポリイミド層 855 上に、下層から、シリコン酸化物層 856、シールド層 857、シリコン酸化物層 858、及びシリコン窒化物層 (SiNx 層) 859 を含む。

#### 【0093】

10

20

30

40

50

シリコン酸化物層 853 及びアモルファスシリコン層 854 は、二つのポリイミド層 852 及び 855 の密着性を改善する。シリコン酸化物層 853 及びアモルファスシリコン層 854 により、上層のポリイミド層 855 が下層のポリイミド層 852 から剥がれることを防ぐことができる。

#### 【0094】

シールド層 857 は、ポリイミド層 855 又は 852 に存在する電荷からの電界の影響を低減する導体層である。シールド層 857 は、ポリイミド層 855 の全面を覆うように形成されている。シールド層 857 は、例えば、ITO 及びIZO 等の透明アモルファス酸化物で形成される。

#### 【0095】

シリコン酸化物層 856 は、シールド層 857 のポリイミド層 855 に対する密着性を改善することができる。シリコン酸化物層 858 は、シールド層 857 とシリコン窒化物層 859 との密着性を改善するとともに、OLED 素子のための水分や酸素に対するバリア層である。シリコン窒化物層 859 もまたバリア層として働く。

#### 【0096】

シリコン窒化物層 859 上に、下層から、シリコン酸化物層 860 及びゲート絶縁層 861 が形成されている。ゲート絶縁層 861 は、例えば、シリコン酸化物、シリコン窒化物又はこれらの積層で形成されている。ゲート絶縁層 861 は、ドライバ 131、132 及び表示領域 125 内のトランジスタのゲート絶縁膜を含む。

#### 【0097】

ゲート絶縁層 861 上に、ゲート電極層 (M1 金属層) に含まれる電極 862 が配置されている。電極 862 は例えば Mo で形成できる。ゲート電極層 (M1 金属層) は、ドライバ 131、132 及び表示領域 125 内のトランジスタのゲート電極絶縁膜を含む。電極 862 を覆うように、層間絶縁膜 863 が形成されている。

#### 【0098】

層間絶縁膜 863 上に、ソース / ドレイン金属層 (M2 金属層) に含まれる電極 864A、864B が形成されている。ソース / ドレイン金属層は、例えば、高融点金属又はその合金で形成される。電極 864A は、層間絶縁膜 863 に形成されたコンタクトホールを介して電極 862 に接続されている。ソース / ドレイン金属層 (M2 金属層) は、ドライバ 131、132 及び表示領域 125 内のトランジスタのソース / ドレイン電極を含む。

#### 【0099】

ソース / ドレイン金属層の電極 864A、864B を覆うように、層間絶縁膜 865 が形成されている。層間絶縁膜 865 上に、配線補助層 (M3 金属層) に含まれる電極 866A、866B が形成されている。配線補助層は例えば Al で形成できる。電極 866A は、層間絶縁膜 865 に形成されたコンタクトホールを介して電極 864A に接続されている。電極 866B は、層間絶縁膜 865 に形成されたコンタクトホールを介して電極 864B に接続されている。

#### 【0100】

電極 866A、866B を覆うように、有機平坦化膜 867 が形成されている。平坦化膜 867 の上に、OLED 素子 E1 のアノード電極の層の含まれる電極 868 が形成されている。電極 868 は、アノード電極と同じ層構造を有し、例えば、中央の反射金属層と反射金属層を挟む透明導電層で構成される。電極 868 は、例えば、ITO / Ag / ITO 構造又は IZO / Ag / IZO 構造を有する。

#### 【0101】

本例において、電極 868 は、カソード電源電位 VSS を伝送する VSS 配線層 801 (図 13 参照) に含まれる。電極 868 は、平坦化膜 867 のコンタクトホールを介して電極 866B に接続されている。

#### 【0102】

電極 862 から電極 868 までの積層構造が、付加容量 Cadd を構成する。接続されている電極 862、864A、866A が、付加容量 Cadd の一方の容量電極を構成す

10

20

30

40

50

る。この容量電極は3層の導体層の電極で構成される。電極862が、出力バッファの出力(走査線)に接続される。接続されている電極864B、866B、868が、付加容量Caddの他方の容量電極を構成する。この容量電極は、3層の導体層の電極で構成されている。

#### 【0103】

これら電極間の絶縁体部が、付加容量Caddの絶縁体部を構成する。このように、層間接続された複数導体層の電極を含む容量電極と、導体層の間の絶縁体層により付加容量Caddを構成することで、少ない面積で大きい容量値を実現できる。なお、容量電極は3層以上の電極で構成することができる。各容量電極は1層の導体層の電極で構成されてもよい。二つの容量電極それぞれを構成する電極の層数は異なっていてもよく、一方の容量電極は複数導体層の電極で構成され、他方は1層の導体層の電極で構成されてもよい。

10

#### 【0104】

電極866を覆うように、OLED素子を分離する絶縁性の画素定義層(Pixel Defining Layer: PDL)に含まれる、絶縁体層869が形成されている。絶縁体層869は、例えば有機材料で形成される。

#### 【0105】

絶縁体層869上に、封止構造部200(図1参照)が形成されている。封止構造部200は、下層から、無機絶縁体層870、有機平坦化膜871、無機絶縁体(例えばSiNx、AlOx)層872を含む。無機絶縁体層870及び872は、それぞれ、信頼性向上のためのパッシベーション層である。

20

#### 【0106】

封止構造部200上に、下層から、タッチスクリーンフィルム873、/4板874、偏光板875、及び樹脂カバーレンズ876が積層されている。/4板874及び偏光板875は、外部から入射した光の反射を抑制する。なお、図14を参照して説明したOLED表示装置の積層構造は一例であり、図14に示す層の一部が省略されてもよく、図14に示されていない層が追加されてもよい。

#### 【0107】

以上、本開示の実施形態を説明したが、本開示が上記の実施形態に限定されるものではない。当業者であれば、上記の実施形態の各要素を、本開示の範囲において容易に変更、追加、変換することが可能である。ある実施形態の構成の一部を他の実施形態の構成に置き換えることが可能であり、ある実施形態の構成に他の実施形態の構成を加えることも可能である。

30

#### 【符号の説明】

#### 【0108】

100 TFT基板

106 走査線

107 エミッション制御線

131 走査ドライバ

132 エミッションドライバ

134 ドライバIC

40

451 通常領域

453 低密度領域

465 カメラ

650 出力バッファ

651、652 ゲート電極

655A、655B 半導体膜

801 VSS配線層

802 配線補助層

862、864A、864B、866A、866B 電極

863、865 層間絶縁膜

50

8 6 7 平坦化膜

8 6 8 電極

C a d d 付加容量

E 1 O L E D 素子

M 1、M 2 出力バッファの駆動トランジスタ

P 1、P 2 ノード

T 1 - T 6 画素回路のトランジスタ

【図面】

【図 1】

【図 2】

10

20

30

40

50

【図3】

【 図 4 】

10

20

【図5】

【図6】

30

40

50

【図 7】

【図 8】

10

【図 9】

【図 10】

20

30

40

50

【図 1 1】

【図 1 2】

10

20

【図 1 3】

【図 1 4】

30

40

50

## フロントページの続き

## (51)国際特許分類

|                          | F I     |       |         |

|--------------------------|---------|-------|---------|

| H 0 1 L 21/3205(2006.01) | G 0 9 G | 3/20  | 6 2 1 M |

| H 0 1 L 21/768(2006.01)  | G 0 9 G | 3/20  | 6 8 0 G |

| H 0 1 L 23/522(2006.01)  | G 0 9 G | 3/20  | 6 4 2 A |

| H 1 0 D 86/40 (2025.01)  | G 0 9 G | 3/20  | 6 2 4 B |

| H 1 0 D 84/83 (2025.01)  | H 1 0 D | 89/00 | 1 0 1 A |

| H 1 0 D 84/80 (2025.01)  | H 1 0 D | 89/00 | 1 0 1 F |

| H 1 0 D 89/10 (2025.01)  | H 1 0 D | 1/68  |         |

|                          | H 0 1 L | 21/88 | Z       |

|                          | H 1 0 D | 86/40 | 1 0 2   |

|                          | H 1 0 D | 84/83 | J       |

|                          | H 1 0 D | 84/80 | 1 0 1 A |

|                          | H 1 0 D | 89/10 | L       |

## (56)参考文献

中国特許出願公開第 1 1 0 4 4 4 1 2 5 ( C N , A )

特表 2 0 2 0 - 5 2 7 7 4 9 ( J P , A )

特表 2 0 1 8 - 5 3 4 6 1 3 ( J P , A )

中国特許出願公開第 1 1 1 2 6 1 6 4 1 ( C N , A )

中国特許出願公開第 1 0 9 4 6 1 4 1 2 ( C N , A )

## (58)調査した分野 (Int.Cl. , D B 名)

G 0 9 F 9 / 0 0 - 9 / 4 6

G 0 9 G 3 / 0 0 - 3 / 2 6

3 / 3 0 - 3 / 3 4

3 / 3 8

H 0 5 B 3 3 / 0 0 - 3 3 / 2 8

4 4 / 0 0

4 5 / 6 0

H 0 1 L 2 1 / 8 8 - 2 1 / 9 0

H 1 0 D 1 / 6 8

3 0 / 0 1

3 0 / 4 7

3 0 / 6 7

8 4 / 0 0 - 8 4 / 9 0

8 6 / 0 0 - 8 6 / 8 5

8 9 / 0 0 - 8 9 / 6 0

H 1 0 K 5 0 / 0 0 - 9 9 / 0 0