(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6494335号

(P6494335)

(45) 発行日 平成31年4月3日(2019.4.3)

(24) 登録日 平成31年3月15日(2019.3.15)

|                       |               |

|-----------------------|---------------|

| (51) Int.Cl.          | F 1           |

| HO4N 5/341 (2011.01)  | HO4N 5/341    |

| HO1L 27/146 (2006.01) | HO1L 27/146 A |

| HO4N 5/374 (2011.01)  | HO4N 5/374    |

| HO4N 5/378 (2011.01)  | HO4N 5/378    |

請求項の数 23 (全 28 頁)

(21) 出願番号 特願2015-43890 (P2015-43890)

(22) 出願日 平成27年3月5日 (2015.3.5)

(65) 公開番号 特開2016-163330 (P2016-163330A)

(43) 公開日 平成28年9月5日 (2016.9.5)

審査請求日 平成30年2月22日 (2018.2.22)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 戸塚 洋史

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

(72) 発明者 吉田 大介

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

最終頁に続く

(54) 【発明の名称】光電変換装置、光電変換装置の駆動方法、および、光電変換システム

## (57) 【特許請求の範囲】

## 【請求項 1】

光電変換素子と、

前記光電変換素子で発生した電荷に基づく信号を受けるゲートを含む増幅トランジスタと、

前記ゲートに接続された少なくとも1つのトランジスタと、

前記増幅トランジスタからの電流が流れる第1の経路に、前記増幅トランジスタに対して直列に配された選択トランジスタと、

前記第1の経路とは分離された第2の経路へ第1の基準電流を出力する第1の電流源と、

前記増幅トランジスタのソースおよびドレインのいずれか一方と電気的に接続された制御線の電圧を制御する電圧制御部と、

前記増幅トランジスタからの電流と前記第1の基準電流とを比較するための比較部と、を備え、

前記少なくとも1つのトランジスタが導通状態である期間に、前記選択トランジスタが非導通状態である、

ことを特徴とする光電変換装置。

## 【請求項 2】

前記少なくとも1つのトランジスタは、前記光電変換素子で発生した電荷を転送する転送トランジスタである、

ことを特徴とする請求項 1 に記載の光電変換装置。

【請求項 3】

前記少なくとも 1 つのトランジスタは、前記ゲートの電圧をリセットするリセットトランジスタである、

ことを特徴とする請求項 1 に記載の光電変換装置。

【請求項 4】

前記少なくとも 1 つのトランジスタは、前記光電変換素子で発生した電荷を転送する転送トランジスタ、および、前記ゲートの電圧をリセットするリセットトランジスタを含み、

前記リセットトランジスタが導通状態である期間、および、前記転送トランジスタが導通状態である期間のそれぞれにおいて、前記選択トランジスタが非導通状態である、

ことを特徴とする請求項 1 に記載の光電変換装置。

【請求項 5】

前記電圧制御部は、前記制御線と第 1 電圧を供給する第 1 電圧ノードとの間の経路に配されたスイッチ、および、前記制御線と第 2 電圧を供給する第 2 電圧ノードとの間の経路に配された第 2 の電流源を含む、

ことを特徴とする請求項 1 乃至請求項 4 のいずれか一項に記載の光電変換装置。

【請求項 6】

前記スイッチを導通状態にすることで、前記制御線の電圧を前記第 1 電圧に基づく電圧にリセットし、

前記スイッチを非導通状態にすることで、前記第 2 の電流源によって前記制御線の電圧を前記第 2 電圧に近づくように変化させる、

ことを特徴とする請求項 5 に記載の光電変換装置。

【請求項 7】

前記制御線の電圧がリセットされたとき、前記増幅トランジスタが非導通状態になり、前記電圧制御部が前記制御線の電圧を変化させた結果、前記増幅トランジスタが導通状態になる、

ことを特徴とする請求項 6 に記載の光電変換装置。

【請求項 8】

前記第 2 の電流源の出力する第 2 の基準電流の電流値が可変である、

ことを特徴とする請求項 5 乃至請求項 7 のいずれか一項に記載の光電変換装置。

【請求項 9】

前記電圧制御部は、前記制御線に接続された第 1 のノードを有する容量を含む、

ことを特徴とする請求項 5 乃至請求項 8 のいずれか一項に記載の光電変換装置。

【請求項 10】

前記容量の容量値が可変であること、

を特徴とする請求項 9 に記載の光電変換装置。

【請求項 11】

前記容量は、前記第 1 のノードとは別であって、第 3 電圧が供給された第 2 のノードを有し、

前記第 1 電圧は前記第 2 電圧と前記第 3 電圧との間の電圧である、

ことを特徴とする請求項 9 または請求項 10 に記載の光電変換装置。

【請求項 12】

前記容量は、前記第 1 のノードとは別であって、第 3 電圧が供給された第 2 のノードを有し、

前記第 3 電圧は、前記第 1 電圧と前記第 2 電圧との間の電圧であるか、または、前記第 2 電圧と等しい、

ことを特徴とする請求項 9 または請求項 10 に記載の光電変換装置。

【請求項 13】

前記増幅トランジスタのソースおよびドレインの他方に接続された第 3 の電流源を備え

10

20

30

40

50

る、

ことを特徴とする請求項 1 乃至請求項 1 2 のいずれか一項に記載の光電変換装置。

【請求項 1 4】

前記比較部は、カレントミラー回路を含み、

前記カレントミラー回路は、前記第 1 の経路に配された第 1 のトランジスタと、前記第 2 の経路に配された第 2 のトランジスタとを含み、

前記第 1 のトランジスタのゲートおよびドレインが互いに短絡されている、

ことを特徴とする請求項 1 乃至請求項 1 3 のいずれか一項に記載の光電変換装置。

【請求項 1 5】

前記第 2 のトランジスタのソースの側のノードと、前記第 2 のトランジスタのドレインの側のノードとを接続するトランジスタを備える、

ことを特徴とする請求項 1 4 に記載の光電変換装置。

【請求項 1 6】

前記第 2 の経路であって、前記第 2 のトランジスタと前記第 1 の電流源との間に配されたトランジスタを備える、

ことを特徴とする請求項 1 4 または請求項 1 5 に記載の光電変換装置。

【請求項 1 7】

前記電圧制御部が前記制御線の電圧を変化させている期間に、前記増幅トランジスタからの電流と前記第 1 の基準電流とを比較することにより、前記ゲートが受ける信号に対応するデジタル信号を生成する、

ことを特徴とする請求項 1 乃至請求項 1 6 のいずれか一項に記載の光電変換装置。

【請求項 1 8】

前記電圧制御部は、単位時間における前記制御線の電圧の変化量を切り替える、

ことを特徴とする請求項 1 乃至請求項 1 7 のいずれか一項に記載の光電変換装置。

【請求項 1 9】

前記選択トランジスタが非導通状態である期間が、前記少なくとも 1 つのトランジスタが導通状態である期間を包含する、

ことを特徴とする請求項 1 乃至請求項 1 8 のいずれか一項に記載の光電変換装置。

【請求項 2 0】

前記少なくとも 1 つのトランジスタが非導通状態から導通状態へ遷移するときに、前記選択トランジスタが非導通状態である、

ことを特徴とする請求項 1 乃至請求項 1 9 のいずれか一項に記載の光電変換装置。

【請求項 2 1】

前記光電変換素子、前記増幅トランジスタ、および、前記選択トランジスタをそれぞれが含む複数の画素を備え、

前記複数の画素のそれぞれの前記増幅トランジスタの前記ソースおよびドレインのいずれか一方が、前記制御線に電気的に接続される、

ことを特徴とする請求項 1 乃至請求項 2 0 のいずれか一項に記載の光電変換装置。

【請求項 2 2】

請求項 1 乃至請求項 2 1 のいずれか一項に記載の光電変換装置と、

前記光電変換装置からの信号を処理する信号処理装置と、を備えた光電変換システム。

【請求項 2 3】

光電変換素子と、

前記光電変換素子で発生した電荷に基づく信号を受けるゲートを含む増幅トランジスタと、

前記ゲートに接続された少なくとも 1 つのトランジスタと、

前記増幅トランジスタからの電流が流れる第 1 の経路に、前記増幅トランジスタに対して直列に配された選択トランジスタと、

前記第 1 の経路とは分離された第 2 の経路へ第 1 の基準電流を出力する第 1 の電流源と、

10

20

30

40

50

前記増幅トランジスタのソースおよびドレインのいずれか一方に電気的に接続された制御線の電圧を制御する電圧制御部と、

前記増幅トランジスタからの電流と前記第1の基準電流とを比較するための比較部と、を備える光電変換装置の駆動方法であって、

前記少なくとも1つのトランジスタが導通状態である期間に、前記選択トランジスタが非導通状態にする、

ことを特徴とする光電変換装置の駆動方法。

【発明の詳細な説明】

【技術分野】

【0001】

10

本発明は光電変換装置、光電変換装置の駆動方法、および、光電変換システムに関する。

【背景技術】

【0002】

特許文献1の図2には、光電変換によって発生した電荷の量に応じた電流信号を出力する画素(101)を有する光電変換装置が開示されている。当該電流信号は、画素の出力ノード(OUT)から出力される。特許文献1に記載された光電変換装置では、画素の出力ノードから出力される電流信号に基づいて、光電変換によって発生した電荷の量に応じたデジタル信号が生成される。

【先行技術文献】

20

【特許文献】

【0003】

【特許文献1】特開2013-146045号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献1に記載された光電変換装置においては、各画素が転送トランジスタ(204)、リセットトランジスタ(205)、および、選択トランジスタ(206、207)を含んでいる。また、特許文献1に記載の光電変換装置によれば、各画素から電流信号を読み出す期間(図11の時刻T1以降)において、選択トランジスタが常にオンしている。そのため、リセットトランジスタ、あるいは、転送トランジスタを駆動する駆動信号の変化によって、画素から出力される電流が変動する可能性がある。出力された電流の変動がセトリングするのに時間を要するため、高速な信号の読み出しが困難である。

30

【0005】

以上の課題に鑑み、本発明に係るいくつかの実施例は、光電変換装置の駆動の高速化を目的とする。

【課題を解決するための手段】

【0006】

本発明の1つの側面に係る実施例の撮像装置は、光電変換素子と、前記光電変換素子で発生した電荷に基づく信号を受けるゲートを含む増幅トランジスタと、前記ゲートに接続された少なくとも1つのトランジスタと、前記増幅トランジスタからの電流が流れる第1の経路に、前記増幅トランジスタに対して直列に配された選択トランジスタと、前記第1の経路とは分離された第2の経路へ第1の基準電流を出力する第1の電流源と、前記増幅トランジスタのソースおよびドレインのいずれか一方に電気的に接続された制御線の電圧を制御する電圧制御部と、前記増幅トランジスタからの電流と前記第1の基準電流とを比較するための比較部と、を備え、前記少なくとも1つのトランジスタが導通状態である期間に、前記選択トランジスタが非導通状態であることを特徴とする。

40

【発明の効果】

【0007】

本発明によれば、光電変換装置の駆動を高速化することができる。

50

## 【図面の簡単な説明】

## 【0008】

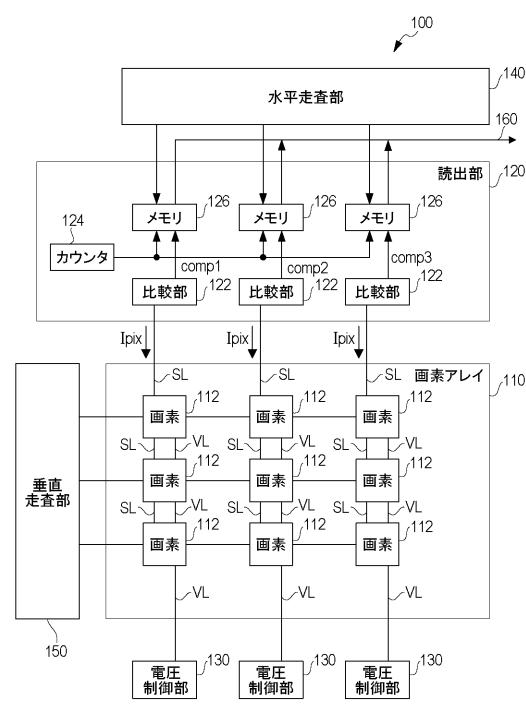

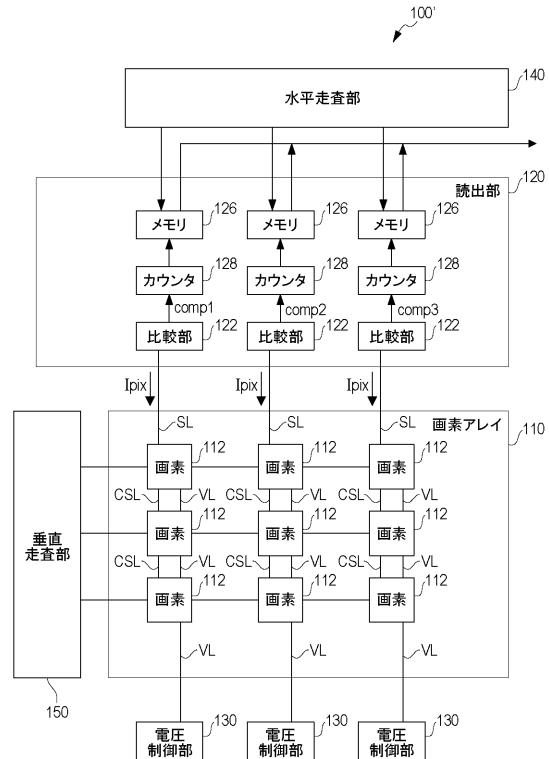

【図1】光電変換装置の構成を示す図。

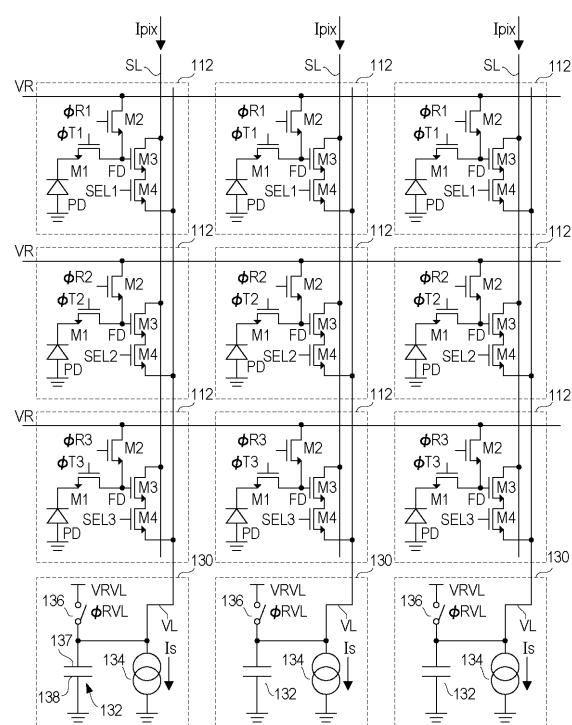

【図2】画素アレイおよび電圧制御部の構成例を示す図。

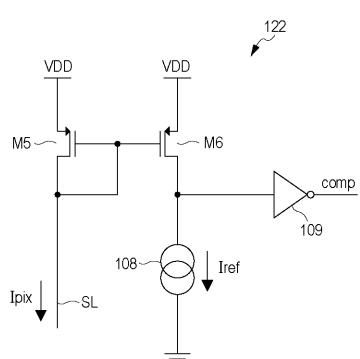

【図3】読み出部の構成例を示す図。

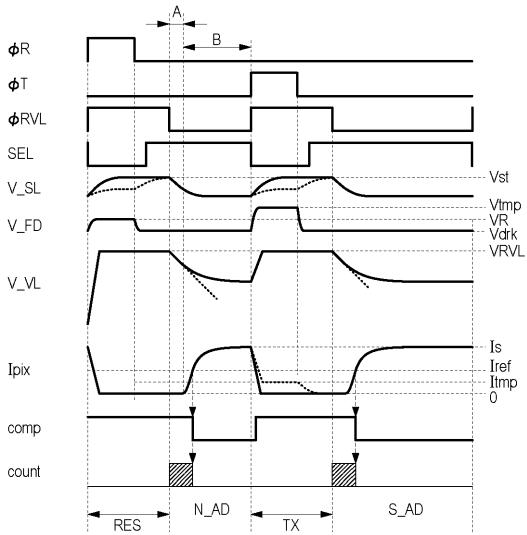

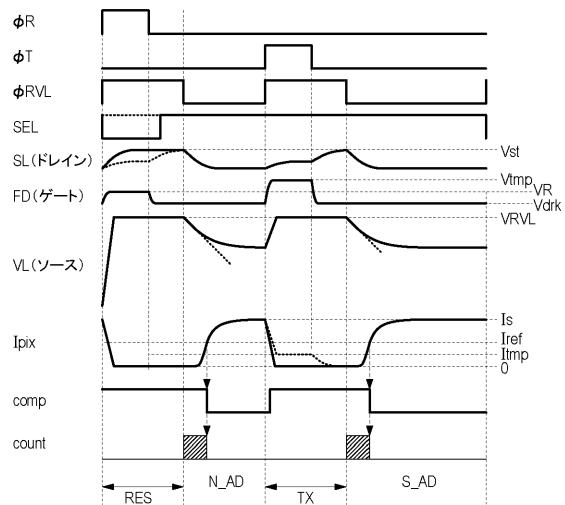

【図4】画素からの信号の読み出動作を示す図。

【図5】画素からの信号の読み出動作を示す図。

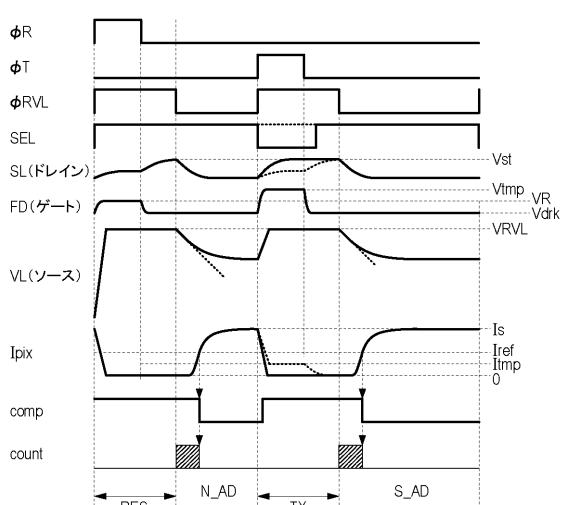

【図6】画素からの信号の読み出動作を示す図。

【図7】光電変換装置の構成を示す図。

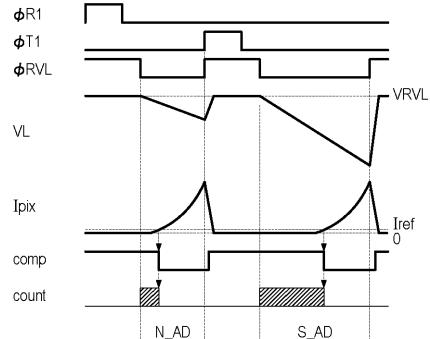

【図8】画素からの信号の読み出動作を示す図。

【図9】光電変換装置の電圧制御部の構成を示す図。

【図10】画素からの信号の読み出動作を示す図。

【図11】光電変換装置の構成を示す図。

【図12】光電変換装置の読み出動作を説明する図。

【図13】光電変換装置の読み出部の構成を示す図。

【図14】画素からの信号の読み出動作を示す図。

【図15】光電変換装置の読み出部の構成を示す図。

【図16】画素からの信号の読み出動作を示す図。

【図17】光電変換装置の読み出部の構成を示す図。

【図18】画素からの信号の読み出動作を示す図。

【図19】光電変換装置の読み出部の構成を示す図。

【図20】画素からの信号の読み出動作を示す図。

【図21】光電変換システムの構成を示す図。

## 【発明を実施するための形態】

## 【0009】

以下、添付図面を参照しながら本発明をその例示的な実施形態を通して説明する。

## 【実施例1】

## 【0010】

図1には、本発明の第1実施形態の光電変換装置100の構成が示されている。光電変換装置100は、少なくとも1つの画素112を有する。典型的には、光電変換装置100は、複数の画素112が1次元または2次元に配列された画素アレイ110を有する。複数の画素112を含む光電変換装置100は、撮像装置として用いられる。図1に示された例では、複数の画素112は、複数の行および複数の列を構成するように、即ち2次元状に配列されている。

## 【0011】

光電変換装置100は、画素112に接続された制御線VLへ制御電圧V\_VLを供給する電圧制御部130と、画素112からセンシング線SLを介して信号を読み出すための読み出部120とを備えている。ここで、画素アレイ110の各列に対して、1つの電圧制御部130および1つの読み出部120が設けられる。

## 【0012】

光電変換装置100は、更に、信号が読み出される画素112を選択するための垂直走査部(垂直選択部)150および水平走査部(水平選択部)140を含む。垂直走査部150は、画素アレイ110における複数の行のうち所定の行を選択し、選択された行の画素112の信号がセンシング線SLを介して読み出部120によって読み出される。水平走査部140は、読み出部120によって読み出された複数の列の画素112のデジタル信号のうち所定の列の画素112を選択し、当該画素112の信号を出力信号線160に出力させる。つまり、水平走査部140は、画素アレイ110における複数の列のうち読み出対象の列を選択する。

## 【0013】

電圧制御部130は、制御線VLの電圧V\_VLを変化させる。垂直走査部150によ

10

20

30

40

50

つて選択された行の各画素 112 は、光電変換によって発生した電荷の量に応じた電圧まで制御線 VL の電圧 V\_VL が変化した時点でセンシング線 SL に電流経路を形成し、画素電流 Ipix を流す。読出部 120 は、画素電流 Ipix に基づいて、光電変換によって発生した電荷の量に応じたデジタル信号を発生する。

#### 【0014】

読出部 120 は、比較部 122 と、カウンタ 124 と、メモリ 126 とを含む。比較部 122 は、画素電流 Ipix と基準電流 Iref とを比較する。本実施形態では、比較部 122 は、画素電流 Ipix の値が基準電流 Iref の値（閾値）を超えたことを検知する。カウンタ 124 は、所定のタイミングでカウント動作を開始する。メモリ 126 は、比較部 122 の比較結果信号 comp1、comp2、comp3 の遷移に応じて、カウンタ 124 のカウント値を画素 112 の信号に対応するデジタル信号として保持する。ここで、比較結果信号 comp1、comp2、comp3 における「1」、「2」、「3」は、画素アレイ 110 の複数の列にそれぞれ対応する複数の比較部 122 の比較結果信号 comp を相互に区別するための識別子である。10

#### 【0015】

図 2 には、画素アレイ 110 および電圧制御部 130 の構成例が示されている。図 3 には、読出部 120 の比較部 122 の構成例が示されている。図 1-3 を参照しながら光電変換装置 100 の構成および動作を更に詳細に説明する。

#### 【0016】

各画素 112 は、フォトダイオードなどの光電変換素子 PD と、増幅トランジスタ M3 とを少なくとも含む。増幅トランジスタ M3 のゲートは、光電変換素子 PD で発生した電荷に基づく信号を受ける。増幅トランジスタ M3 のソースおよびドレインの一方（本例ではソース）は、制御線 VL に電気的に接続される。各画素 112 は、増幅トランジスタ M3 のゲートに接続された電荷電圧変換部（フローティングディフュージョン）FD を含む。また、各画素 112 は増幅トランジスタ M3 のゲートに接続された少なくとも 1 つのトランジスタを含む。本実施形態では、各画素 112 は、増幅トランジスタ M3 のゲートに接続された転送トランジスタ M1 を含む。転送トランジスタ M1 は、光電変換素子 PD で発生した電荷を増幅トランジスタ M3 のゲートへ転送する。さらに、各画素 112 は、増幅トランジスタ M3 のゲートに接続されたリセットトランジスタ M2 を含む。リセットトランジスタ M2 は、増幅トランジスタ M3 のゲートの電圧をリセットする。各画素 112 は、更に、選択トランジスタ M4 を含む。選択トランジスタ M4 は、増幅トランジスタ M3 と制御線 VL との間の経路、または、増幅トランジスタ M3 とセンシング線 SL との間の経路に設けられる。つまり、選択トランジスタ M4 は、増幅トランジスタ M3 から出力される電流の経路において、増幅トランジスタ M3 に対して直列に配されている。選択トランジスタ M4 が増幅トランジスタ M3 と制御線 VL との間の経路に配された場合、増幅トランジスタ M3 のソースは、選択トランジスタ M4 を介して制御線 VL に電気的に接続される。2030

#### 【0017】

なお、増幅トランジスタ M3 のゲートと電荷電圧変換部 FD とは互いに接続されているため、両者は同一のノードである。そこで、本明細書においては、特に増幅トランジスタ M3 のゲートと電荷電圧変換部 FD とを区別する必要がない場合は、単に、当該ノードを電荷電圧変換部 FD と呼ぶ。40

#### 【0018】

転送トランジスタ M1 は、垂直走査部 150 によって転送信号 T ( T1, T2, T3 ) が活性化されることによってオンし、光電変換素子 PD の電荷を電荷電圧変換部 FD に転送する。ここで、転送信号 T1, T2, T3 における「1」、「2」、「3」は、画素アレイ 110 の複数の行に対する転送信号 T を相互に区別するための識別子である。リセットトランジスタ M2 は、リセット信号 R ( R1, R2, R3 ) が活性化されることによってオンし、電荷電圧変換部 FD の電圧をリセット電圧線の供給するリセット電圧 VR に応じた電圧にリセットする。ここで、リセット信号 R1, R50

2、R3における「1」、「2」、「3」は、画素アレイ110の複数の行に対するリセット信号Rを相互に区別するための識別子である。選択トランジスタM4は、選択信号SEL(SEL1、SEL2、SEL3)が活性化されることによってオンし、その選択信号SELが接続された画素112を選択状態にする。ここで、選択信号SEL1、SEL2、SEL3における「1」、「2」、「3」は、画素アレイ110の複数の行に対する選択信号SELを相互に区別するための識別子である。

#### 【0019】

ここで、本実施形態における画素112には、特許文献1に記載された光電変換装置のような差動增幅回路が設けられていない。したがって、本発明の第1実施形態における画素112は、特許文献1に記載された画素と比較して回路規模が小さく、多画素化に有利である。10

#### 【0020】

制御線VLの電圧V\_VLは、電圧制御部130によって制御される。本実施形態において、電圧制御部130は、増幅トランジスタM3のソース(第1主電極)に対する、増幅トランジスタM3のゲートの電圧が高くなる方向、即ち増幅トランジスタM3がオフ状態からオン状態になる方向に制御線VLの電圧を制御する。換言すると、第1実施形態では、電圧制御部130は、制御線VLの電圧V\_VLの電圧を降下させる。

#### 【0021】

電圧制御部130は、容量132と、スイッチ136と、電流源134とを含む。容量132は、制御線VLに接続される第1端子137と、所定電圧(この例では接地電圧)の供給される第2端子138とを有する。スイッチ136は、制御線VLと第1電圧VRVLが印加される第1電圧ノードとの間の経路に設けられている。そして、スイッチ136は、リセット信号RVLが活性化されたことに応じて容量132の第1端子137の電圧および制御線VLの電圧V\_VLを第1電圧VRVLに基づく電圧にリセットする。電流源134は、制御線VLと第2電圧(この例では接地電圧)が印加される第2電圧ノード(この例では接地ノード)との間に設けられる。リセット信号RVLが非活性化されると、容量132に蓄積された電荷が電流源134を介して電流値Isで放電される。これによって、制御線VLの電圧V\_VLは、第2電圧ノードの電圧に近づく方向に変化する。本実施形態では、制御線VLの電圧V\_VLは、線形的に降下する。20

#### 【0022】

なお、容量132は、制御線VLに付加的に設けるものに限られない。他の構成を変更することなく、容量132は制御線VLに付随する寄生容量で代替されうる。30

#### 【0023】

比較部122は、画素112の増幅トランジスタM3のドレイン(第2主電極)を通して流れる電流Ipixが基準電流Irrefの値(閾値)を超えたことを検知する。比較部122は、例えば、カレントミラー回路を構成するPMOSトランジスタなどのトランジスタM5、M6を含む。トランジスタM5のゲートとドレインとは互いに短絡され、かつ、センシング線SLに接続される。これにより、トランジスタM5は、増幅トランジスタM3からの電流の経路の一部を構成する。トランジスタM6は、基準電流Irrefを流す電流源108に接続される。これにより、トランジスタM6は、電流源108の出力する基準電流Irrefの経路の一部を構成する。トランジスタM5のゲートは、トランジスタM6のゲートに接続されている。トランジスタM6のドレインと電流源108との間のノードが、比較部122の出力ノードである。比較部122の出力ノードには、インバータ(反転アンプ)109が接続される。40

#### 【0024】

電流源108が流す基準電流Irrefは、比較部122における比較の基準(閾値)を定める。インバータ(反転アンプ)109は、比較結果信号compを出力する。メモリ126は、比較部122の比較結果信号comp1、comp2、comp3の遷移に応じて、カウンタ124のカウント値を画素112の信号に対応するデジタル信号として保持する。インバータ109は、出力回路の一例であり、ソース接地アンプ等の他の反転ア50

ンプで置き換えられてもよい。

**【0025】**

このような構成により、読出部120は、増幅トランジスタM3から流れる画素電流 $I_{pix}$ の電流値が基準電流 $I_{ref}$ の電流値(閾値)を超えるタイミングに応じて、画素112の電荷電圧変換部FDの電圧に対応するデジタル信号を生成する。

**【0026】**

本実施形態において、増幅トランジスタM3からの電流の経路(第1の経路)と、電流源108が出力する基準電流 $I_{ref}$ の経路(第2の経路)は、互いに分離されている。第1の経路は、トランジスタM5のソースが接続された電源ノード(VDD)から、電流源134が接続された第2電圧ノード(接地ノード)に至る。トランジスタM5、センシング線SLの一部、増幅トランジスタM3、選択トランジスタM4、制御線VLの一部、および、電流源134が、第1の経路を形成する。第2の経路は、トランジスタM5のソースが接続された電源ノード(VDD)から、電流源108が接続された接地ノードに至る。トランジスタM6、比較部122の出力ノードの一部、および、電流源108が第2の経路を形成する。上述の通り、第1の経路と第2の経路とは互いに共有する部分を有さない。つまり、第1の経路と第2の経路とは互いに分離されている。なお、互いに分離された第1の経路と第2の経路とが、電源ノードおよび接地ノードの一方もしくは両方を共有してもよい。一般に、電源ノードおよび接地ノードは複数の回路に共通だからである。

**【0027】**

図4には、本実施形態におけるある画素112の信号の読出動作が示されている。この読出動作は、ノイズレベルの読出動作N\_A\_Dと、光信号レベルの読出動作S\_A\_Dとを含んでいる。ノイズレベルの読出動作N\_A\_Dは、電荷電圧変換部FDをリセットした後に、電荷電圧変換部FDの電圧に応じた信号をデジタル信号として読み出す動作である。光信号レベルの読出動作S\_A\_Dは、電荷電圧変換部FDに光電変換素子PDの電荷を転送した後に、電荷電圧変換部FDの電圧に応じた信号をデジタル信号として読み出す動作である。

**【0028】**

まず、リセット信号Rが所定時間だけ活性化されることによってリセットトランジスタM2がオンする、つまり、導通状態になる。このとき、電荷電圧変換部FDの電圧V\_FDがリセットトランジスタM2を通してリセット電圧VRに応じた電圧にリセットされる。便宜的に、図4は、このときの電荷電圧変換部FDの電圧V\_FDがリセット電圧VRに等しい例を示している。電荷電圧変換部FDの電圧のリセットは、リセット信号Rの非活性化によって終了する。

**【0029】**

本実施形態においては、リセット信号Rが活性化されている期間は、選択信号SELが非活性化される。換言すると、リセットトランジスタM2がオンしている期間は、選択トランジスタM4がオフしている、つまり、非導通状態である。

**【0030】**

電荷電圧変換部FDの電圧のリセットと並行して、リセット信号RVLが所定時間だけ活性化される。これによって、スイッチ136がオンし、制御線VLの電圧V\_VLがスイッチ136を通して第1電圧VRVLに応じた電圧にリセットされる。便宜的に、図4は、このときの制御線VLの電圧V\_VLが第1電圧VRVLに等しい例を示している。制御線VLに接続された容量132の第1端子の電圧も、同じく第1電圧VRVLに応じた電圧にリセットされる。制御線VLの電圧V\_VLのリセットは、リセット信号RVLの非活性化によって終了する。

**【0031】**

ここで、第1電圧VRVL(第1電圧ノードの電圧)は、スイッチ136がオンすることによって制御線VLに設定される電圧が画素112の増幅トランジスタM3をオンさせない電圧であるように決定されている。すなわち、制御線VLの電圧V\_VLがリセット

10

20

30

40

50

されることにより、増幅トランジスタM3は非導通状態になる。

**【0032】**

リセット信号 RVL の非活性化によってノイズレベルの読み出動作 N\_A\_D が開始される。リセット信号 RVL の非活性化によって容量 132 に蓄積されていた電荷が電流源 134 によって電流値 Is で放電され、制御線 VL の電圧 V\_VL が線形的に降下する。制御線 VL の電圧 V\_VL が線形的に降下する期間が期間 A として示されている。また、リセット信号 RVL の非活性化に応じて、カウンタ 124 によるカウント動作が開始される。カウント動作は、図 4において、“count”として示されている。

**【0033】**

期間 A は、読み出対象の行の画素 112 の増幅トランジスタ M3 のゲートとソースとの間の電圧が増幅トランジスタ M3 の閾値を超えることによって終了し、期間 B に移行する。

10 制御線 VL の電圧 V\_VL は、期間 A において線形的に変化し、期間 B において非線形的に変化する。電圧まで制御線 VL の電圧 V\_VL が降下した結果、読み出対象の行の画素 112 の増幅トランジスタ M3 のゲートとソースとの間の電圧が増幅トランジスタ M3 の閾値を超えると、増幅トランジスタ M3 がオンして、画素電流 Ipix が流れ始める。画素電流 Ipix は、増幅トランジスタ M3 および選択トランジスタ M4 を介して制御線 VL に流れる。制御線 VL を流れることができる電流の値は、電流源 134 によって電流値 Is に制限される。よって、画素電流 Ipix が流れることによって容量 132 からの放電電流が小さくなり、そのため、制御線 VL の電圧 V\_VL の降下が非線形に変化する。

**【0034】**

画素電流 Ipix が流れ始めた後、画素電流 Ipix の値が基準電流 Iref の値（閾値）を超えると、それが比較部 122 によって検知される。つまり、比較結果信号 com\_p が活性化（反転）され、それに応じてカウンタ 124 によるカウント値が、ノイズレベルを示すデジタル信号として、メモリ 126 のノイズレベル保持用のメモリによって保持される。即ち、読み出部 120 は、容量 132 の充電後にスイッチ 136 がオフされた時点から画素 112 の増幅トランジスタ M3 のドレインを通して流れ込む画素電流 Ipix の値が基準電流 Iref の値を超える時点までの時間に応じたデジタル信号を生成する。

20

**【0035】**

リセット信号 RVL の非活性化から十分な時間が経過した後にノイズレベルの読み出動作 N\_A\_D が終了する。その後、転送信号 T が所定時間だけ活性化される。転送信号 T 1 が活性化されることによって光電変換素子 PD の電荷が電荷電圧変換部 FD に転送され、これにより電荷電圧変換部 FD の電圧が変化する。

30

**【0036】**

本実施形態においては、転送信号 T が活性化されている期間は、選択信号 SEL が非活性化される。換言すると、転送トランジスタ M1 がオンしている期間は、選択トランジスタ M4 がオフしている、つまり、非導通状態である。

**【0037】**

電荷の転送と並行して、リセット信号 RVL が所定時間だけ活性化される。リセット信号 RVL の活性化によって期間 B が終了する。リセット信号 RVL が所定時間だけ活性化されることによって、スイッチ 136 がオンし、制御線 VL の電圧 V\_VL がスイッチ 136 を通して第 1 電圧 VRVL に応じた電圧にリセットされる。制御線 VL の電圧 V\_VL のリセットは、リセット信号 RVL の非活性化によって終了する。

40

**【0038】**

リセット信号 RVL の非活性化によって光信号レベルの読み出動作 S\_A\_D が開始される。リセット信号 RVL の非活性化によって容量 132 に蓄積されていた電荷が電流源 134 によって電流値 Is で放電され、制御線 VL の電圧 V\_VL が線形的に降下する。以降の動作は、基本的には、ノイズレベルの読み出動作 N\_A\_D と同様であるが、読み出動作 S\_A\_D の読み出時間は、読み出動作 N\_A\_D よりも長く確保される。

**【0039】**

電圧まで制御線 VL の電圧 V\_VL が降下した結果、読み出対象の行の画素 112 の増幅

50

トランジスタM3のゲートとソースとの間の電圧が増幅トランジスタM3の閾値を超えると、増幅トランジスタM3がオンして画素電流 $I_{pix}$ が流れ始める。画素電流 $I_{pix}$ が流れ始めた後、画素電流 $I_{pix}$ の値が基準電流 $I_{ref}$ の値（閾値）を超えると、それが読出部120の比較部122によって検知される。つまり、比較結果信号compが活性化（反転）され、それに応じてカウンタ124によるカウント値が、光信号レベルを示すデジタル信号として、メモリ126の光信号レベル保持用のメモリによって保持される。即ち、読出部120は、容量132の充電後にスイッチ136がオフされた時点から画素112の増幅トランジスタM3のドレインを通して流れる画素電流 $I_{pix}$ の値が基準電流 $I_{ref}$ の値を超える時点までの時間に応じたデジタル信号を生成する。

## 【0040】

10

メモリ126によって保持されたノイズレベルを示すデジタル信号および光信号レベルを示すデジタル信号は、水平走査部140からの指令に応じて出力信号線160に出力される。ノイズレベルを示すデジタル信号および光信号レベルを示すデジタル信号は、それらの双方が光電変換装置100から出力されてもよいし、それらの差分が光電変換装置100から出力されてもよい。

## 【0041】

ここで、第1実施形態の光電変換装置100の特徴を、AD変換器を有する一般的な光電変換装置との比較において説明する。一般的な光電変換装置では、画素の信号は、画素に設けられた増幅トランジスタを介して列信号線に電圧信号の形態で出力され、これが列アンプによって増幅され、その後、AD変換器によってデジタル信号に変換される。このような方式では、列信号線の電圧がセトリングし、更に画素アレイ110の各列に設けられた列アンプの出力もセトリングした後に、AD変換器によるAD変換を開始する必要がある。

20

## 【0042】

一方、第1実施形態の光電変換装置100は、電荷電圧変換部FDの電圧に対応する信号をデジタル信号として出力するという点では広義のAD変換を行っている。しかし、第1実施形態の光電変換装置100は、電荷電圧変換部FDの電圧をアナログ電圧信号として読み出した後にそれをデジタル信号に変換するものではない。第1実施形態の光電変換装置100では、制御線VLの電圧 $V_{VL}$ の降下を開始するとともに、広義のAD変換が開始される。つまり、第1実施形態の光電変換装置100では、信号線の電圧のセトリングを待つ必要はない。よって、第1実施形態の光電変換装置100は、画素112から高速に信号を読み出すために有利である。

30

## 【0043】

本実施形態ではリセットトランジスタM2が導通状態である期間、および、転送トランジスタM1が導通状態である期間のそれぞれにおいて、選択信号SELが非導通状態である期間がある。このような構成によれば、光電変換装置100の駆動の高速化ができる。

## 【0044】

まず電荷電圧変換部FDの電圧 $V_{FD}$ がリセットされる期間について説明する。リセット信号R、 $R_{VL}$ が活性化され、電荷電圧変換部FDの電圧はリセット電圧VRに基づく電圧に、制御線VLの電圧は第1電圧 $V_{RVL}$ に基づく電圧にそれぞれリセットされる。このとき、増幅トランジスタM3のゲートとソースとの間の電圧は、 $VR - V_{RVL}$ で表される。

40

## 【0045】

選択信号SELが活性状態である場合、この時点で増幅トランジスタM3を非導通状態にしておくために、増幅トランジスタM3のゲートとソースとの間の電圧（ $VR - V_{RVL}$ ）が増幅トランジスタM3の閾値電圧より小さいことが好ましい。

## 【0046】

次にリセット信号Rが非活性化されると、リセットトランジスタM2のゲートと電荷電圧変換部FDの間のカップリングにより、電荷電圧変換部FDの電圧 $V_{FD}$ が、 $VR$

50

から  $V_{drk}$  に振り下げられる。増幅トランジスタ M3 のゲートとソースとの間の電圧は、 $V_{drk} - VRVL$  で表され、 $VR - VRVL$  より小さくなる。つまり、増幅トランジスタ M3 はより強いオフ状態となる。そのため、リセット信号  $RVL$  を非活性化して A/D 変換動作を開始すると、増幅トランジスタ M3 がオンするまでに長い時間がかかる。

#### 【0047】

一般に、リセットトランジスタ M2 のゲートと電荷電圧変換部 FD との間のカップリング容量に対して、電荷電圧変換部 FD の容量 CFD は 10 倍程度のため、 $VR$  と  $V_{drk}$  の差はリセット信号  $R$  の振幅の 1/10 程度になる。例えば、リセット信号  $R$  の振幅が 5 V であれば、 $VR$  と  $V_{drk}$  の差は数百 mV になる。なおこのカップリング容量には、リセットトランジスタ M2 のゲートとソースとの間の容量に加え、電荷電圧変換部 FD とりセット信号  $R$  を伝達する配線との間の寄生容量も含まれる。

10

#### 【0048】

本実施形態では、リセットトランジスタ M2 が導通状態である間に、選択信号 SEL が非活性化されている。そのため、その間は増幅トランジスタ M3 からの電流が流れる経路が遮断される。すなわち、リセットトランジスタ M2 が導通状態のときに増幅トランジスタ M3 に電流は流れない。したがって、リセットトランジスタ M2 が導通状態である間に、増幅トランジスタ M3 のゲートとソースとの間の電圧 ( $VR - VRVL$ ) が増幅トランジスタ M3 の閾値電圧より高くてよい。

#### 【0049】

そして、リセット信号  $R$  が非活性化され電荷電圧変換部 FD の電圧  $V_{FD}$  が  $V_{drk}$  に振り下げられた後に、選択信号 SEL が活性化される。この時に、増幅トランジスタ M3 のゲートとソースとの間の電圧 ( $V_{drk} - VRVL$ ) が、増幅トランジスタ M3 の閾値電圧より低ければよい。

20

#### 【0050】

したがって、先に説明した選択信号 SEL が活性化状態にある場合と比較して、第 1 電圧  $VRVL$  をより低い電圧に設定できる。つまり、本実施形態では、リセット信号  $RVL$  を非活性化して A/D 変換動作を開始してから増幅トランジスタ M3 がオンするまでの時間を短縮することが可能となる。結果として、光電変換装置 100 の駆動を高速化することができる。

#### 【0051】

30

続いて転送トランジスタ M1 が導通状態である期間について説明する。電荷を転送するため転送信号 T が活性化されるのと並行して、制御線 VL をリセットするためリセット信号  $RVL$  が活性化される。電荷電圧変換部 FD と転送トランジスタ M1 のゲートとのカップリングにより、転送信号 T が活性化した時に電荷電圧変換部 FD の電位  $V_{FD}$  が、 $V_{drk}$  から  $V_{tmp}$  に振り上げられる。

#### 【0052】

電荷電圧変換部 FD の電圧  $V_{FD}$  の振り上げにより増幅トランジスタ M3 がオンする可能性がある。したがって、電荷の転送時に選択トランジスタ M4 が導通状態のままの場合、第 1 電圧  $VRVL$  に高い電圧が用いられる。そのため、リセット信号  $RVL$  を非活性化して A/D 変換動作を開始してから増幅トランジスタ M3 がオンするまでの時間が長くなる。

40

#### 【0053】

また、電荷電圧変換部 FD の電位  $V_{FD}$  の振り上げにより増幅トランジスタ M3 がオンすることで、図 4 の点線で示したように増幅トランジスタ M3 に電流  $I_{tmp}$  が流れる。また、センシング線 SL の電圧  $V_{SL}$  は、A/D 変換動作を開始する初期電圧である電位  $V_{st}$  から、電流  $I_{tmp}$  に応じた電圧に降下する。この後、転送信号 T が非活性化されて電荷電圧変換部 FD の電位が  $V_{drk}$  に復帰することで、読み出し増幅トランジスタ M3 がオフすることで電流が流れなくなり、センシング線 SL は電位  $V_{st}$  にセトリングする。つまり、センシング線 SL の電圧  $V_{SL}$  がセトリングするのに時間がかかる。

#### 【0054】

50

本実施形態では、転送トランジスタM1が導通状態である間に、選択信号SELが非活性化されている。そのため、その間は増幅トランジスタM3からの電流が流れる経路が遮断される。すなわち、転送トランジスタM1が導通状態のときに、増幅トランジスタM3に電流は流れない。したがって、転送トランジスタM1が導通状態である間に、増幅トランジスタM3のゲートとソースとの間の電圧(VR - VRVL)が増幅トランジスタM3の閾値電圧より高くてよい。

#### 【0055】

そして、転送信号Tが非活性化され電荷電圧変換部FDの電圧V\_FDがVdrkに振り下げられた後に、選択信号SELが活性化される。この時に、増幅トランジスタM3のゲートとソースとの間の電圧(Vdrk - VRVL)が、増幅トランジスタM3の閾値電圧より低ければよい。10

#### 【0056】

したがって、先に説明した選択信号SELが活性化状態にある場合と比較して、第1電圧VRVLをより低い電圧に設定できる。つまり、本実施形態では、リセット信号RVLを非活性化してAD変換動作を開始してから増幅トランジスタM3がオンするまでの時間を短縮することが可能となる。結果として、光電変換装置100の駆動を高速化することができる。

#### 【0057】

また、増幅トランジスタM3がオンしなければ、センシング線SLの電圧V\_SLはVsにセトリングする。つまり本実施形態では選択信号SELを期間TXに非活性化することで、センシング線SLの電圧をより早くセトリングさせることができ、読み出しの高速化を実現できる。20

#### 【0058】

一般には、転送トランジスタM1のサイズ(チャネル幅)の方がリセットトランジスタM2のサイズ(チャネル幅)より大きい。そのため、VtmpとVdrkとの差は、VRとVdrkとの差より大きくなりうる。したがって、転送トランジスタM1がオンしている間に選択トランジスタM4をオフしておくが、リセットトランジスタM2の場合に比べて、高速化の効果は顕著である。なおこの場合のカップリング容量は、転送トランジスタM1のゲートとドレインとの間の容量に加えて、電荷電圧変換部FDと転送信号Tを供給する配線との間の寄生容量を含みうる。30

#### 【0059】

図4に示された駆動では、リセット信号Rの立ち上がりと、選択信号SELの立ち下がりとが同時刻である。しかし、リセット信号Rが活性化している期間の少なくとも一部において、選択信号SELが非活性化されれば、高速化の効果を得ることができる。リセット信号Rが非活性の状態から活性状態へ遷移するときに、選択信号SELが非活性化されていると、リセット信号Rの遷移による影響を低減でき、高速化の効果が高い。選択信号SELが非活性化している期間が、リセット信号Rが活性化している期間を包含していると、高速化の効果がより顕著に得られる。なお、リセット信号RVLの活性化している期間が、選択信号SELが非活性化している期間を包含していることが好ましい。40

#### 【0060】

また図4に示された駆動では、転送信号Tの立ち上がりと、選択信号SELの立下りとが同時刻である。しかし、転送信号Tが活性化している期間の少なくとも一部において、選択信号SELが非活性化されれば、高速化の効果を得ることができる。転送信号Rが非活性の状態から活性状態へ遷移するときに、選択信号SELが非活性化されていると、転送信号Rの遷移による影響を低減でき、高速化の効果が高い。選択信号SELが非活性化している期間が、転送信号Tが活性化している期間を包含していると、高速化の効果がより顕著に得られる。なお、リセット信号RVLの活性化している期間が、選択信号SELが非活性化している期間を包含していることが好ましい。

#### 【0061】

10

20

30

40

50

図4の例では、本実施形態ではリセットトランジスタM2が導通状態である期間、および、転送トランジスタM1が導通状態である期間のそれれにおいて、選択信号SELが非導通状態である期間がある。しかし、このような構成に限られない。画素112が転送トランジスタM1およびリセットトランジスタM2の両方を含む光電変換装置100において、リセットトランジスタM2が導通状態である期間にのみ、選択信号SELが非導通状態である期間があつてもよい。また、画素112が転送トランジスタM1およびリセットトランジスタM2の両方を含む光電変換装置100において、転送トランジスタM1が導通状態である期間にのみ、選択信号SELが非導通状態である期間があつてもよい。これらの実施形態を図5、および、図6を用いて説明する。

## 【0062】

10

図5には、本実施形態におけるある画素112の信号の読み出動作が示されている。この読み出動作は、ノイズレベルの読み出動作N<sub>—</sub>ADと、光信号レベルの読み出動作S<sub>—</sub>ADとを含んでいる。図4の動作との差異は、転送トランジスタM1が導通状態のときに、選択トランジスタM4が常時オンしていることである。それ以外の動作は、図4と同じなので説明を省略する。

## 【0063】

図5に示された動作によって、ノイズレベルの読み出動作N<sub>—</sub>ADにかかる時間を短縮することができる。したがって、光電変換装置100の駆動を高速化することができる。

## 【0064】

20

なお、別の実施形態では、光電変換装置の画素112が転送トランジスタM1を含まないよう、本実施形態が変更される。すなわち、光電変換素子PDが増幅トランジスタM3のゲートに直接接続される。当該実施形態において、図5に示された読み出動作が行われる。ただし、転送信号Tは用いられない。また、読み出動作は光信号レベルの読み出動作S<sub>—</sub>ADのみが行われてもよい。このような実施形態では、読み出動作S<sub>—</sub>ADに係る時間が短縮されるため、光電変換装置の駆動を高速化することができる。

## 【0065】

図6には、本実施形態におけるある画素112の信号の読み出動作が示されている。この読み出動作は、ノイズレベルの読み出動作N<sub>—</sub>ADと、光信号レベルの読み出動作S<sub>—</sub>ADとを含んでいる。図4の動作との差異は、リセットトランジスタM2が導通状態のときに、選択トランジスタM4が常時オンしていることである。それ以外の動作は、図4と同じなので説明を省略する。

30

## 【0066】

図6に示された動作によって、光信号レベルの読み出動作S<sub>—</sub>ADにかかる時間を短縮することができる。したがって、光電変換装置100の駆動を高速化することができる。

## 【0067】

なお、別の実施形態では、光電変換装置の画素112がリセットトランジスタM2を含まないよう、本実施形態が変更される。例えば、光電変換素子PDで生じた電流が光電流として増幅トランジスタM3から出力される場合、リセットトランジスタM2は用いられない。当該実施形態において、図6に示された読み出動作が行われる。ただし、リセット信号Rは用いられない。また、読み出動作は光信号レベルの読み出動作S<sub>—</sub>ADのみが行われてもよい。このような実施形態では、読み出動作S<sub>—</sub>ADに係る時間が短縮されるため、光電変換装置の駆動を高速化することができる。

40

## 【0068】

また、本実施形態では、増幅トランジスタM3のゲートに接続されたトランジスタの例として、転送トランジスタM1およびリセットトランジスタM2を説明した。しかし、増幅トランジスタM3のゲートに接続されたトランジスタは、これらに限られない。例えば、複数の画素112の電荷電圧変換部FDを互いに接続するためのトランジスタ、電荷電圧変換部FDの容量を変化させるためのトランジスタが挙げられる。増幅トランジスタM3のゲートに接続されたトランジスタが導通状態である期間に、選択トランジスタM4を非導通状態とすることで、高速化の効果を得ることができる。

50

**【0069】**

上記の各実施形態において、複数の画素で増幅トランジスタM3を共有する構成にしてもよい。すなわち、複数の光電変換素子が、互いに異なる転送トランジスタを介して、共通のフローティングディフィュージョンに接続されるように構成してもよい。

**【実施例2】****【0070】**

図7には、本発明の第2実施形態の光電変換装置100'の構成が示されている。第2実施形態として言及しない事項は、第1実施形態と同じである。本実施形態は、読出部120の構成が第1実施形態と異なる。具体的には、カウンタ128が列ごとに設けられている。即ち、読出部120は、画素アレイ110の1つの列について、1つの比較部122と、1つのカウンタ128と、1つのメモリ126とを含む。カウンタ128は、それに対応する比較部122からの比較結果信号compが遷移することによってカウント動作を停止し、メモリ126は、それに対応するカウンタ128によるカウント値を保持する。

10

**【0071】**

本実施形態の光電変換装置100'において、図4乃至図6のいずれかで示された画素からの信号の読出動作が行われる。その結果、光電変換装置100'の駆動を高速化することができる。

**【実施例3】****【0072】**

20

図8には、本発明の第3実施形態におけるある画素112からの信号の読出動作が示されている。第3実施形態として言及しない事項は、第1または第2実施形態と同じである。第3実施形態は、電圧制御部130は、可変電圧源を含み、該可変電圧源によって制御線VLの電圧VL\_Vを制御する。具体的には、電圧制御部130は、リセット信号R\_VLの非活性化に応答して制御線VLの電圧VL\_Vを線形的に降下させる。増幅トランジスタM3を流れる電流Ipixは、増幅トランジスタM3がオン状態になり始めとともに電流が流れ始め、制御線VLの電圧VL\_Vの変化が変化を停止するまで増大する。このように、制御線VLの電圧VL\_Vを線形的に変化させるための電圧制御部130の一例としては、ボルテージフォロワ等のバッファが考えられる。例えば、図2において、定電流源と容量132の第1端子137が接続されたノードの電圧を、ボルテージフォロワを介して制御線VLに供給する。

30

**【0073】**

なお、増幅トランジスタM3がオン状態からオフ状態になる方向に制御線VLの電圧を制御してもよい。このように、増幅トランジスタM3がオン状態からオフ状態になる方向に制御線VLの電圧を制御した場合に、画素電流Ipixの値が基準電流Irefの値よりも小さくなることも、画素電流Ipixが閾値を超えたと表現することができる。画素電流Ipixの値が基準電流Irefの値よりも小さくなること検知することも、画素電流Ipixと基準電流Irefとを比較することに含まれる。

**【0074】**

図8では選択信号SELの図示は省略されているが、本実施形態において、図4乃至図6のいずれかに示された選択信号SELが用いられる。その結果、光電変換装置の駆動を高速化することができる。

40

**【実施例4】****【0075】**

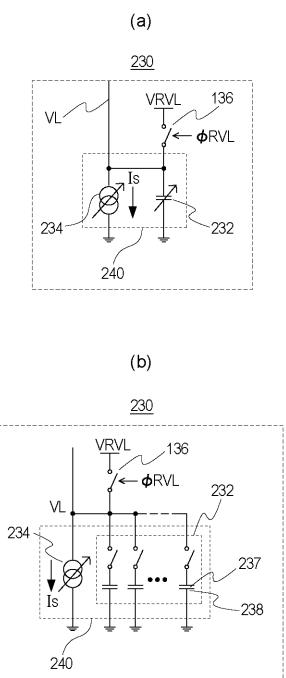

図9(a)を参照しながら本発明の第4実施形態の光電変換装置を説明する。第4実施形態は、電圧制御部130が電圧制御部230で置き換えられている点で第1乃至第3実施形態と異なる。第4実施形態として言及しない事項は、第1乃至第3実施形態のいずれかと同じである。

**【0076】**

電圧制御部230は、制御線VLの電圧VL\_Vを変化させる。電圧制御部230は、

50

可変容量 232 と、スイッチ 136 と、可変電流源 234 とを含む。可変容量 232 と可変電流源 234 とによってゲイン制御部 240 が構成されている。ゲイン制御部 240 は、不図示の制御信号に応じて、可変容量 232 の容量値および可変電流源 234 が output する電流の電流値  $I_s$  を決定することができる。

#### 【0077】

可変容量 232 の容量値を大きくすると、期間 A における制御線 VL の電圧  $V_{VL}$  の変化（傾き）を小さくすることができる。可変容量 232 の容量値を小さくすると、期間 A における制御線 VL の電圧  $V_{VL}$  の変化（傾き）を大きくすることができる。また、電流値  $I_s$  を大きくすると、図 4 の期間 A において、可変容量 232 からの放電電流が増加するため、制御線 VL の電圧  $V_{VL}$  の変化（傾き）を大きくすることができる。電流値  $I_s$  を小さくすると、期間 A における制御線 VL の電圧  $V_{VL}$  の変化（傾き）を小さくすることができる。

10

#### 【0078】

以上のように、ゲイン制御部 240 によって、期間 A における、単位時間あたりの制御線 VL の電圧  $V_{VL}$  の変化量（傾き）を変更することができる。これによって、以降で説明するように、AD 变換ゲイン（読み出部 120 による読み出のゲイン）を切替えることができる。この例では、可変容量 232 の容量値および可変電流源 234 の電流値  $I_s$  の双方を可変としているが、いずれか一方のみを可変とすることによっても AD 变換ゲインを変更することができる。

#### 【0079】

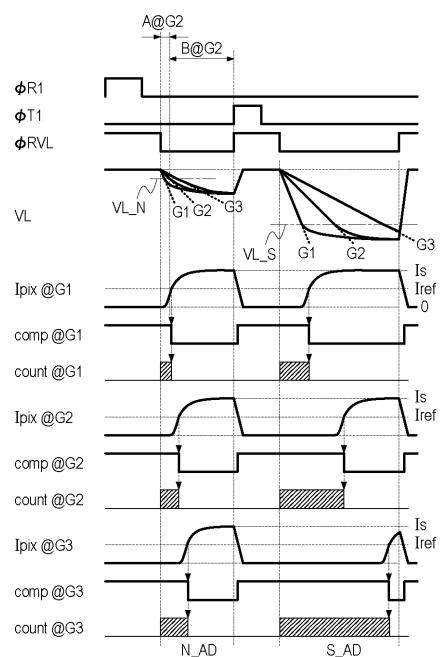

図 10 を参照しながら第 5 実施形態の光電変換装置における AD 变換ゲインの切り替えについて説明する。図 10 には、3 通りの AD 变換ゲイン G1、G2、G3 が示されている。ここでは、図 4 と同じ AD 变換ゲインを G2 とし、ゲイン G2 よりも制御線 VL の傾きを大きくした場合をゲイン G1、小さくした場合をゲイン G3 として示されている。前述のように、可変容量 232 の容量値および電流値  $I_s$  の少なくとも一方を変更することによって AD 变換ゲインを決定することができる。電荷電圧変換部 FD におけるリセット電圧、転送信号 T の活性化によって光電変換素子 PD から電荷電圧変換部 FD に転送される電荷量は、すべての AD 变換ゲインにおいて同じである。図 10 において、選択信号 SEL の図示は省略されている。選択信号 SEL は、図 4 乃至図 6 のいずれかの信号が用いられる。

20

#### 【0080】

まず、リセット信号 R1 が所定時間だけ活性化されることによってリセットトランジスタ M2 がオンし、電荷電圧変換部 FD の電圧がリセットトランジスタ M2 を通してリセット電圧 VR に応じた電圧にリセットされる。電荷電圧変換部 FD の電圧のリセットは、リセット信号 R1 の非活性化によって終了する。電荷電圧変換部 FD の電圧のリセットと並行して、リセット信号 RVL が所定時間だけ活性化されることによって、スイッチ 136 がオンし、制御線 VL の電圧  $V_{VL}$  がスイッチ 136 を通して第 1 電圧 VRVL に応じた電圧にリセットされる。制御線 VL に接続された可変容量 232 の第 1 端子 137 の電圧も、同じく第 1 電圧 VRVL に応じた電圧にリセットされる。制御線 VL の電圧  $V_{VL}$  のリセットは、リセット信号 RVL の非活性化によって終了する。ここで、第 1 電圧 VRVL（第 1 電圧ノードの電圧）は、スイッチ 136 がオンすることによって制御線 VL に設定される電圧が画素 112 の増幅トランジスタ M3 をオンさせない電圧であるように決定されている。

30

#### 【0081】

リセット信号 RVL の非活性化によってノイズレベルの読み出動作 N\_A D が開始され、AD 变換ゲイン G1、G2、G3 の設定に応じた傾きで制御線 VL の電圧  $V_{VL}$  が下降する。AD 变換ゲイン G1、G2、G3 のいずれが選択されている場合においても電荷電圧変換部 FD の電圧は同じであるため、制御線 VL の電圧  $V_{VL}$  が電圧  $V_{LN}$  になった時点で、増幅トランジスタ M3 がオンし、画素電流  $I_{pix}$  が流れ始める。AD 变換ゲイン G1 の傾きが最も大きいため、最も早い時刻で画素電流  $I_{pix}$  が流れ始め、最も

40

傾きの小さい A D 変換ゲイン G 3 の場合、最も遅い時刻で画素電流 I p i x が流れ始める。I p i x @ G 1、c o m p @ G 1、c o u n t @ G 1 は、A D 変換ゲインが G 1 である場合の I p i x 、 c o m p 、 c o u n t を示す。同様に、I p i x @ G 2、c o m p @ G 2、c o u n t @ G 2 は、A D 変換ゲインが G 2 である場合の I p i x 、 c o m p 、 c o u n t を示す。同様に、I p i x @ G 3、c o m p @ G 3、c o u n t @ G 3 は、A D 変換ゲインが G 3 である場合の I p i x 、 c o m p 、 c o u n t を示す。

#### 【 0 0 8 2 】

光信号レベルの読み出動作 S \_ A D においても、同様に、制御線 V L の電圧 V \_ V L が V L \_ S になった時点で、画素電流 I p i x が流れ始める。この場合も、A D 変換ゲイン G 1 の場合、画素電流 I p i x が流れ始める時刻が最も早く、A D 変換ゲイン G 3 の場合に最も遅い。各時刻及び各ゲインにおいて画素 I p i x の値が基準電流 I r e f の値を超えるタイミングで、比較結果信号 c o m p が反転し、その時点のカウント値であるデジタル信号がメモリ 1 2 6 に保持される。10

#### 【 0 0 8 3 】

A D 変換ゲインが G 1 である場合が最も早い時刻でカウント値を保持するということは、A D 変換ゲインが G 1 である場合のデジタル信号の値が最も小さいことを意味する。また、A D 変換ゲインが G 3 である場合が最も遅い時刻でカウント値を保持することは、A D 変換ゲインが G 3 である場合のデジタル信号の値が最も大きいことを意味する。A D 変換ゲインを（デジタル信号の値） / （電荷電圧変換部における電圧レベル）と定義すると、A D 変換ゲインと制御線 V L の電圧 V \_ B L の傾きは、以下の関係となる。20

G 1 ( ゲイン : 小、 傾き : 大 ) < G 2 ( ゲイン : 中、 傾き : 中 ) < G 3 ( ゲイン : 大、 傾き : 小 )

#### 【 0 0 8 4 】

つまり、ゲイン制御部 2 4 0 によって、読み出部 1 2 0 による A D 変換のゲインを切り替える機能が提供される。

#### 【 0 0 8 5 】

図 9 ( b ) には、ゲイン制御部 2 4 0 の具体的な構成例が示されている。図 9 ( b ) に示された例では、可変容量 2 3 2 は、複数のユニットの並列接続で構成され、各ユニットは、容量および選択スイッチの直列接続で構成されている。選択スイッチの状態（オン、オフ）を制御することによって可変容量 2 3 2 の容量値を決定することができる。つまり、選択スイッチの状態（オン、オフ）を制御することによって、複数の容量のうち制御線 V L の電圧制御のために使用される容量を選択することができる。30

#### 【 0 0 8 6 】

各ユニットの容量が、M O S 型キャパシタのように、シリコン拡散層を利用したデバイスで構成される場合、容量の 2 つの電極 2 3 7 および 2 3 8 のいずれかに拡散層 - ウエル間の寄生容量が生じる。各容量をスイッチと制御線 V L との間に配置した場合、スイッチの状態に関わらず、全ての容量の寄生容量が常に制御線 V L に対して付加されてしまう。この場合、ゲイン制御部 2 4 0 において A D 変換ゲインを設定する際に所望のゲインが得られない可能性がある。そこで、図 9 ( b ) に示された例のように、スイッチを容量と制御線 V L との間に挿入することで、オフしているスイッチが接続されている容量の寄生容量も制御線 V L から切り離される。したがって、このような構成によれば、寄生容量による誤差成分を小さくし、より正確な A D 変換ゲインの設定が可能になる。40

#### 【 0 0 8 7 】

また、本実施形態において、図 4 乃至図 6 のいずれかに示された選択信号 S E L が用いられる。その結果、光電変換装置の駆動を高速化することができる。

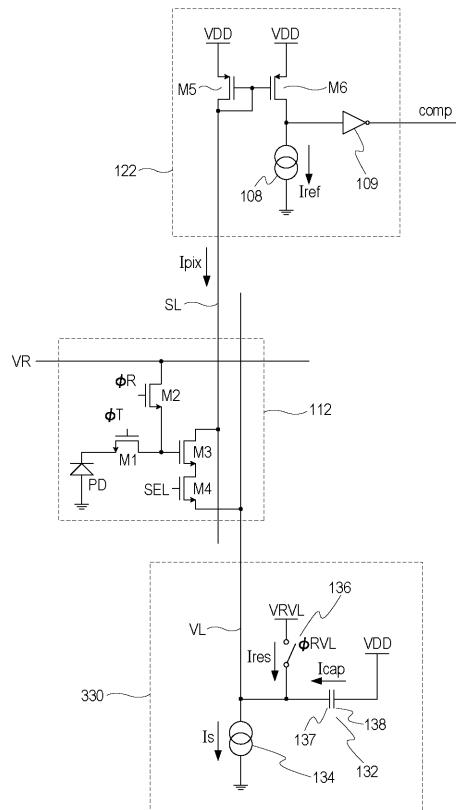

#### 【 実施例 5 】

#### 【 0 0 8 8 】

図 1 1 を参照しながら本発明の第 5 実施形態の光電変換装置を説明する。第 5 実施形態として言及しない事項は、第 1 乃至第 4 実施形態のいずれかと同じである。なお、図 1 1 では、簡略化のために、代表的に、1 つの列のための比較部 1 2 2 および電圧制御部 3 3

0と、当該列の1つの画素112が示されている。第5実施形態では、電圧制御部130が電圧制御部330で置き換えられている。

#### 【0089】

電圧制御部330は、容量132の第2端子138が第3電圧ノード（この例では、電源電圧VDDを供給する電源ノード）に接続されている点で、電圧制御部130と異なる。ここで、第3電圧ノードの電圧は、比較部122のトランジスタM5およびM6のソースに供給される電源電圧VDDと同じである。図11に示された電圧制御部330は、A/D変換ゲインを変更する機能を有しないが、第4実施形態のように、A/D変換ゲインを変更する機能を有してもよい。

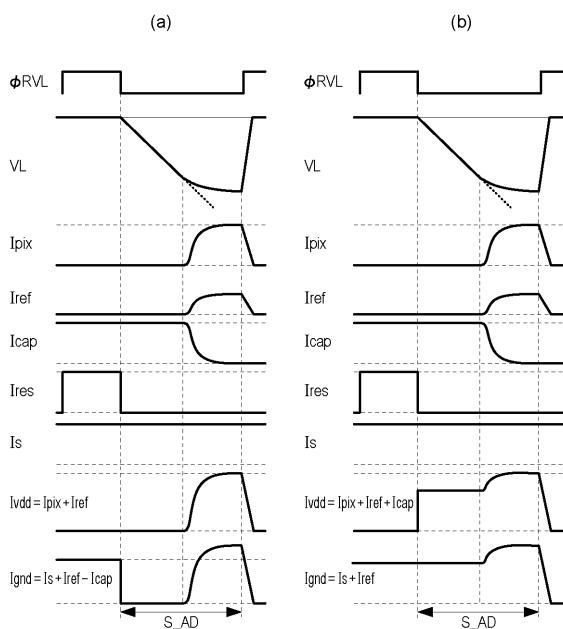

#### 【0090】

図12(a)には、第1乃至第4実施形態のように容量132の第2端子138が第2電圧ノード（接地ノード）に接続された構成における動作が示されている。図12(b)には、第5実施形態、即ち、第2端子138を第3電圧ノード（この例では、電源電圧VDDを供給する電源ノード）に接続された構成における動作が示されている。なお、図12において、選択信号SELの図示は省略されている。選択信号SELは、図4乃至図6のいずれかの信号が用いられる。

#### 【0091】

$I_{cap}$ は容量132から流れる電流、 $I_{res}$ はスイッチ136を流れる電流を示している。 $I_{cap}$ は容量132の第2端子138から第1端子137へ流れる方向を正の電流とする。ノイズレベルの読み出動作N\_A/Dにおける波形の基本的な動作は光信号レベルの読み出動作S\_A/Dと同様であるため、S\_A/Dのみが図示されている。

#### 【0092】

図12(a)において、第3電圧ノードから供給される電流 $I_{vdd}$ は、画素電流 $I_{pix}$ と基準電流 $I_{ref}$ の和である。 $I_{cap}$ は、RVLが非活性化された後における容量132からの放電電流であり、第2端子138を介して第2電圧ノード（接地ノード）から供給される。したがって、第2電圧ノードに流れ込む電流 $I_{gnd}$ は、電流源電流 $I_s$ と $I_{ref}$ の和から $I_{cap}$ を引いたものである。図12(a)から明らかなように、A/D変換を行っているS\_A/Dの期間において、 $I_{vdd}$ および $I_{gnd}$ が大きく変動していることが分かる。第2電圧ノードおよび第3電圧ノードは相応のインピーダンスを持つため、これらの電流変動が接地電圧および電源電圧の変動を引き起こす。図11では1列の回路のみが示されているが、複数の列からなる光電変換装置の場合、自列がA/D変換を行っている最中に他の列が引き起こす接地電圧および電源電圧変動がノイズ要因となる。

#### 【0093】

図12(b)の場合、容量132の第2端子138は第3電圧ノードに接続されているため、 $I_{vdd}$ は、 $I_{pix}$ 、 $I_{ref}$ と $I_{cap}$ の和となり、 $I_{gnd}$ は、 $I_s$ と $I_{ref}$ の和となる。 $I_{cap}$ と $I_{pix}$ とは逆相の関係にあるため、両者を足すことで電流変動を打ち消すことが可能となり、 $I_{vdd}$ の変動を抑制できる。また、 $I_{gnd}$ は変動の大きい $I_{cap}$ と相関を有しないので、 $I_{gnd}$ の変動も抑制できる。したがって、複数の列で構成された光電変換装置において、自列のA/D変換期間中の他列の動作に起因する接地電圧および電源電圧の変動が抑圧される。これにより、容量132の第2端子138を第2電圧ノードに接続した場合と比較して、ノイズによる画質劣化を低減することができる。

#### 【0094】

以上のように、制御線VLに接続される容量132の第2端子138を、比較部122のトランジスタM5、M6が接続されている第3電圧ノードと接続することで、ノイズによる画質の劣化を低減することができる。

#### 【実施例6】

#### 【0095】

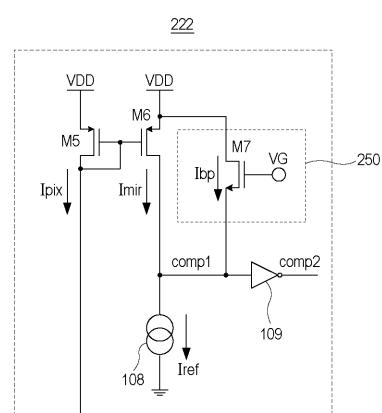

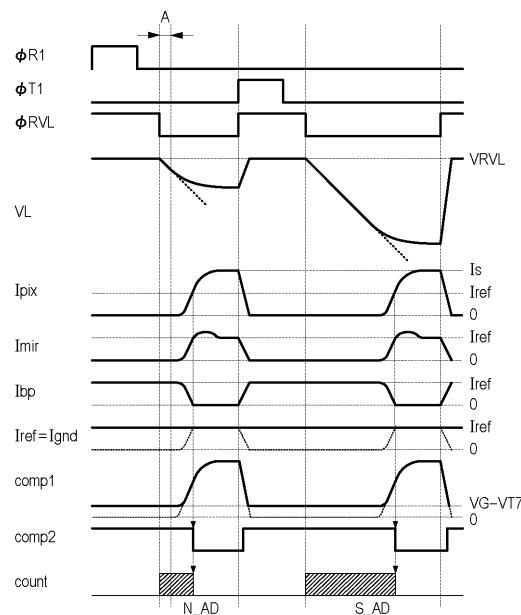

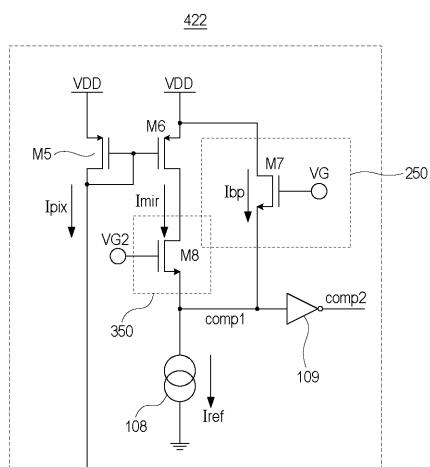

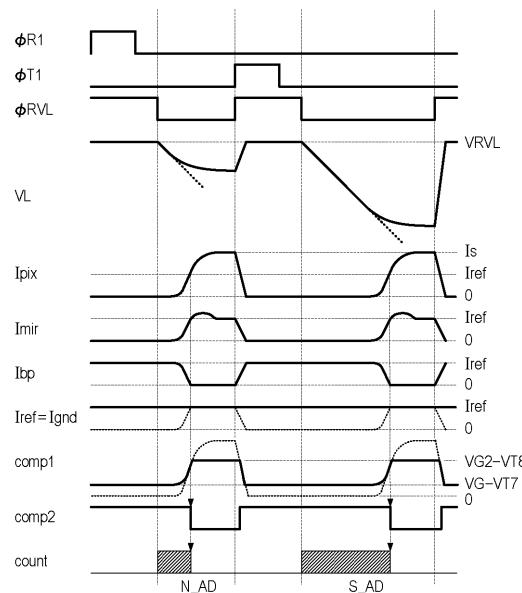

図13を参照しながら本発明の第6実施形態の光電変換装置を説明する。第6実施形態

では、第1乃至第5実施形態における比較部122が比較部222で置き換えられている。比較部222は、比較部122の構成に対してバイパス経路250を追加した構成を有する。バイパス経路250は、トランジスタM6のソースの側のノードとドレインの側のノードとの間の経路をバイパスするように、即ち、トランジスタM6に対して並列に設けられている。バイパス経路250は、例えば、ゲートに所定電圧VGが印加され、ドレインが第3電圧ノード(この例では、電源電圧VDDを供給する電源ノード)に接続され、ソースが電流源108(ノードcomp1)に接続されたNMOSトランジスタM7で構成される。comp1は、インバータ109の入力ノード、comp2は、インバータ109の出力ノードを示している。

## 【0096】

10

次に、図14を参照しながら、図4に示された動作とは異なる点を中心として、第6実施形態の光電変換装置の動作を説明する。ImirはトランジスタM6に流れる電流、IbpはトランジスタM7(バイパス経路250)に流れる電流、Irefは電流源108に流れる参照電流である。なお、図14では選択信号SELの図示は省略されている。選択信号SELは、図4乃至図6のいずれかの信号が用いられる。

## 【0097】

読み出動作N\_A\_Dの期間Aにおいて、制御線VLの電圧V\_VLが線形的に降下するが、読み出対象の行の画素112の増幅トランジスタM3がオフしているため、画素電流Ipixは流れない。トランジスタM5とトランジスタM6は、カレントミラー回路を構成しているので、期間Aにおいては、電流Imirも流れない。トランジスタM7がオンするように所定電圧VGを設定することで、トランジスタM7を介して、電流Ibpが電流源108の基準電流Irefとして流れる。この時、ノードcomp1の電圧は、おおよそ所定電圧VGからトランジスタM7の閾値電圧VT7を引いた電圧である。電圧VG - VT7が接地電圧より高く、インバータ109の反転閾値より低くなるように所定電圧VGが設定されることが好ましい。

20

## 【0098】

制御線VLの電圧V\_VLが降下し続けると、やがて増幅トランジスタM3がオンし、画素電流Ipixが流れ始める。これにより、トランジスタM5とトランジスタM6のサイズ比に応じた電流ImirがトランジスタM6を通して流れる。トランジスタM6、M7は共に電流源108に接続されており、トランジスタM6、M7を流れる電流の合計がIrefである。よって、電流Ibpは減少ていき、ノードcomp1の電圧は上昇していく。そして、画素電流Ipixが大きくなり、電流Imirが基準電流Irefに等しくなる時点で電流Ibpはゼロとなる。その後、電流Imirが基準電流Irefより一時的に大きくなり、ImirとIrefの差分の電荷がノードcomp1の寄生容量に充電されることでノードcomp1の電圧が上昇していく。ノードcomp1の電圧が上昇していくと、トランジスタM6のドレイン・ソース間電圧が小さくなることで、徐々に電流Imirが減少ていき、基準電流Irefと同じ値になるところで釣り合う。

30

## 【0099】

ノードcomp1の電圧が上昇していく期間においてインバータ109の反転閾値を超えた時点でノードcomp2の電圧が反転し、その時点のカウント値countがメモリ126によって保持される。その後、読み出動作N\_A\_Dの終了し、リセット信号RVLが活性化されることで、増幅トランジスタM3がオフし、電流Ipixが流れなくなる。この時、Imirも同様に流れなくなり、代わりに電流Ibpが電流源108の電流を供給し、ノードcomp1の電圧はVG - VT7に戻る。以降、読み出動作S\_A\_Dにおける動作は、N\_A\_Dと同様であるため、説明を省略する。

40

## 【0100】

画素電流Ipixが流れない期間にバイパス経路250(トランジスタM7)を介して電流Ibpを流すことで、接地ノードに流れる電流が一定となる。また、ノードcomp1の低電圧側の電圧を接地電圧より高いVG - VT7とすることで、ノードcomp1における電圧変化の振幅が制限される。複数の列を有し、かつ列間のピッチが数ミクロン以

50

下と狭い光電変換装置においては、クロストークによって他列の大振幅信号が自列に影響を及ぼし、これがノイズとなって画質劣化を引き起こしうる。つまり、ノードcomp1における電圧変化の振幅を制限することで、画質劣化を抑制することができる。

#### 【0101】

図14には、バイパス経路250がない場合の基準電流Iref(即ち、接地ノードに流れる電流Ign)とノードcomp1における電圧の波形が点線で示されている。バイパス経路250がないために、AD変換を行っている読出動作N\_A DおよびS\_A Dの期間に接地ノードに流れる電流が変動していることが分かる。接地ノードは、相応のインピーダンスを持つため、この電流変動が接地電圧の変動を引き起こす。複数の列を有する光電変換装置においては、自列がAD変換を行っている最中に他の列が引き起こす接地電圧変動がノイズ要因となり、画質劣化を引き起こしうる。つまり、接地ノードに流れる電流変動をバイパス経路によって抑制することで、画質劣化を抑制することができる。10

#### 【実施例7】

#### 【0102】

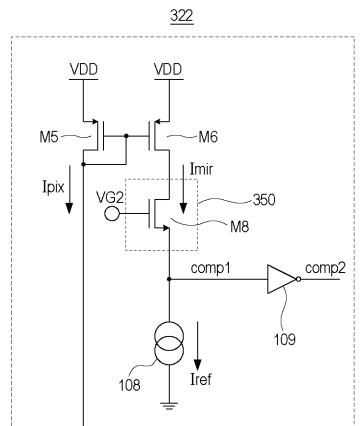

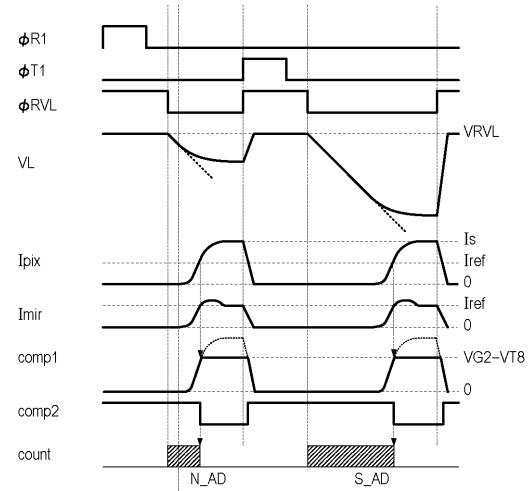

図15を参照しながら本発明の第7実施形態の光電変換装置を説明する。第7実施形態では、第1ないし第5実施形態における比較部122が比較部322で置き換えられている。比較部322は、比較部122の構成に対して振幅制限部350を追加した構成を有する。振幅制限部350は、ノードcomp1における電圧の振幅を制限する。振幅制限部350は、例えば、ゲートに電圧VG2が印加され、ドレインがトランジスタM6のドレイン、ソースが電流源108に接続されたNMOSトランジスタM8で構成されうる。トランジスタM8は、電流源108が出力する基準電流Irefの経路の一部を構成する。つまり、トランジスタM8は、基準電流Irefの経路において、トランジスタM6と電流源108の間に配されている。20

#### 【0103】

次に、図16を参照しながら、図4に示された動作と異なる点を中心として、第7実施形態の光電変換装置の動作を説明する。なお、図16では選択信号SELの図示は省略されている。選択信号SELは、図4乃至図6のいずれかの信号が用いられる。

#### 【0104】

読出動作N\_A Dが開始され、読出対象行の画素112の増幅トランジスタM3がオンし、画素電流Ipixが流れ出すところまでは図4と同様である。画素電流Ipixが流れると、トランジスタM5とトランジスタM6のサイズ比に応じた電流Imirが流れる。これによってノードcomp1の電圧が上昇していくが、トランジスタM8の閾値をVT8とすると、ノードcomp1の電圧は、およそVG2 - VT8となり、ノードcomp1の高電圧側の電圧が抑えられる。つまり、ノードcomp1の電圧の振幅が制限される。複数の列を有し、かつ列間のピッチが数ミクロン以下と狭い光電変換装置においては、クロストークによって他列の大振幅信号が自列に影響を及ぼし、これがノイズとなって画質劣化を引き起こしうる。つまり、ノードcomp1の電圧の振幅を制限することで、画質劣化を抑制することができる。電圧VG2は、インバータ109が反転するよう、VG2 - VT8がインバータ109の反転閾値より高くなるよう設定される。30

#### 【0105】

図15に示された例では、トランジスタM8のゲートに電圧VG2が印加されるが、トランジスタM8のゲートには、比較部322を動作状態または非動作状態に制御するイネーブル信号線が接続されてもよい。イネーブル信号が活性(ハイレベル)の時は、比較部322を動作させ、非活性(ローレベル)の時は比較部322の電流経路を遮断することで比較部322を非動作状態とすることで、消費電力を抑制することができる。40

#### 【実施例8】

#### 【0106】

図17を参照しながら本発明の第8実施形態の光電変換装置を説明する。第8実施形態では、第1ないし第5実施形態における比較部122が比較部422で置き換えられている。比較部422は、第6実施形態のバイパス経路250と第7実施形態の振幅制限部3

1020304050

50の双方が組み込まれた構成を有する。

**【0107】**

図18には、第8実施形態の光電変換装置の動作が示されている。図18では選択信号SELの図示は省略されている。選択信号SELは、図4乃至図6のいずれかの信号が用いられる。

**【0108】**

バイパス経路250および振幅制限部350を有することで、接地ノードを流れる電流 $I_{gnd}$ を一定にすると共に、ノードcomp1における電圧の振幅をVG2-VT8~VG-VT7に制限することができる。つまり、複数の列を有する光電変換装置において、接地電圧変動による画質劣化と、大振幅信号のクロストークによる画質劣化の双方を抑制することができる。10

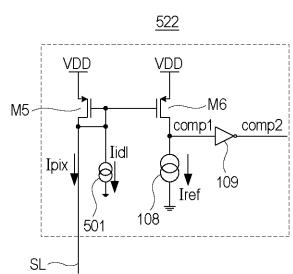

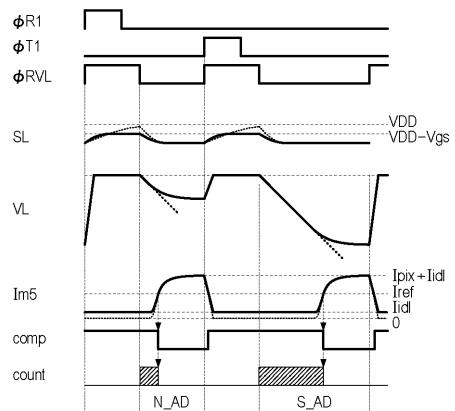

**【実施例9】**

**【0109】**

図19を参照しながら本発明の第9実施形態の光電変換装置を説明する。第9実施形態では、第1ないし第5実施形態における比較部122が比較部522で置き換えられている。比較部522は、比較部122に対してアイドル電流 $I_{idle}$ を流すアイドル電流源501を追加した構成を有する。アイドル電流源501は、センシング線SLを介して、増幅トランジスタM3のソースおよびドレインの他方（本例ではドレイン）に接続される。20

**【0110】**

次に、図20を参照しながら、図4に示された動作と異なる点を中心として、第10実施形態の光電変換装置の動作を説明する。図20では選択信号SELの図示は省略されている。選択信号SELは、図4乃至図6のいずれかの信号が用いられる。

**【0111】**

リセット信号RVLが活性化されることで、増幅トランジスタM3がオフ状態となるため、電流 $I_{pix}$ が流れなくなり、トランジスタM5を流れる電流はアイドル電流 $I_{idle}$ のみとなる。この状態で、センシング線SLの電圧は、センシング線SLの寄生容量がアイドル電流 $I_{idle}$ で充電されることで上昇していく、トランジスタM5のゲートソース間電圧をVgsとするとき、VDD-Vgsにセトリングする。また、トランジスタM6には、アイドル電流 $I_{idle}$ に対して、トランジスタM5に対するM6のサイズ比M( $= (M6のゲート幅) / (M5のゲート幅)$ )を乗じた大きさの電流が流れる。制御線VLおよびセンシング線SLの電圧がセトリングし、且つ画素のリセット動作或いは転送動作が完了した後に、リセット信号RVLが非活性状態にされることでAD変換動作が開始される。以降の動作はこれまで説明した実施形態と同様のため、その説明を省略する。30

**【0112】**

ここで、アイドル電流 $I_{idle}$ は、以下の関係式を満たす電流値である必要がある。

$$I_{idle} < I_{ref}/M$$

**【0113】**

図20には、アイドル電流源501が無い場合のセンシング線SLの電圧波形とトランジスタM5に流れる電流波形Im5が点線で示されている。アイドル電流源501が無いために、リセット信号RVLを活性化すると、トランジスタM5のゲートソース間電圧Vgsで決まる電流がトランジスタM5より供給され、センシング線SLの寄生容量を充電することで、センシング線SLの電圧が上昇していく。センシング線SLの電圧が上昇していくに連れて、ゲートソース間電圧は減少していくため、トランジスタM5より供給される電流も減少し、センシング線SLの電圧の上昇速度も低下する。VgsがトランジスタM5の閾値電圧以下になると、トランジスタM5はサブスレッシュホールド領域に入るため、トランジスタM5より供給される電流量は指数関数的に減少していく。センシング線SLのセトリングには、トランジスタM5の電流が無くなりセトリング線SLの電圧がVDDに到達する必要があるため、長時間掛ることが明らかである。40

**【0114】**

10

20

30

40

50

センシング線 S L が十分にセトリングしていない状態で A D 変換動作を開始する場合、毎回の A D 変換動作の初期状態における増幅トランジスタ M 3 のソースドレイン間電圧が異なる可能性がある。このため、A D 変換結果において、リニアリティ劣化、固定パターンノイズ、ランダムノイズの増加といった問題を引き起こし、画質が劣化しうる。したがって、良好な画質を得るためにには、センシング線 S L が十分にセトリングする時間を確保する必要がある。

#### 【 0 1 1 5 】

つまり、第 10 実施形態のようにアイドル電流源 501 を追加することで、センシング線 S L のセトリング時間を短縮することが可能となり、光電変換装置の読み出し時間の更なる高速化を実現することができる。

10

#### 【実施例 10】

#### 【 0 1 1 6 】

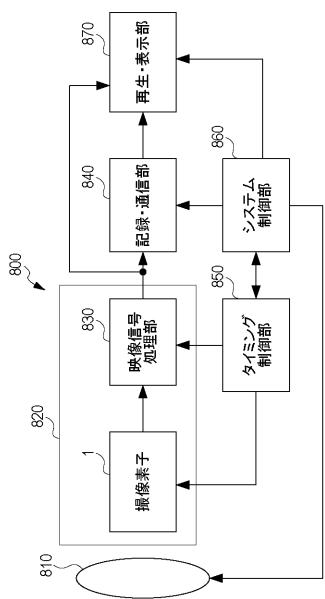

図 21 には、本発明の 1 つの実施形態の光電変換システムの構成が示されている。光電変換システム 800 は、例えば、光学部 810、撮像素子 1、映像信号処理部 830、記録・通信部 840、タイミング制御部 850、システム制御部 860、及び再生・表示部 870 を含む。撮像装置 820 は、撮像素子 1 及び映像信号処理部 830 を有する。撮像素子 1 には、上記の実施形態で説明された光電変換装置 100、100'、100" が用いられる。

#### 【 0 1 1 7 】

レンズ等の光学系である光学部 810 は、被写体からの光を撮像素子 1 の、複数の画素が 2 次元状に配列された画素部 10 に結像させ、被写体の像を形成する。撮像素子 1 は、タイミング制御部 850 からの信号に基づくタイミングで、画素部 10 に結像された光に応じた信号を出力する。撮像素子 1 から出力された信号は、映像信号処理部である映像信号処理部 830 に入力され、映像信号処理部 830 が、プログラム等によって定められた方法に従って信号処理を行う。映像信号処理部 830 での処理によって得られた信号は画像データとして記録・通信部 840 に送られる。記録・通信部 840 は、画像を形成するための信号を再生・表示部 870 に送り、再生・表示部 870 に動画や静止画像を再生・表示させる。記録・通信部 840 は、また、映像信号処理部 830 からの信号を受けて、システム制御部 860 と通信を行うほか、不図示の記録媒体に、画像を形成するための信号を記録する動作も行う。

20

#### 【 0 1 1 8 】

システム制御部 860 は、撮像システムの動作を統括的に制御するものであり、光学部 810、タイミング制御部 850、記録・通信部 840、及び再生・表示部 870 の駆動を制御する。また、システム制御部 860 は、例えば記録媒体である不図示の記憶装置を備え、ここに撮像システムの動作を制御するのに必要なプログラム等が記録される。また、システム制御部 860 は、例えばユーザの操作に応じて駆動モードを切り替える信号を撮像システム内に供給する。具体的な例としては、読み出す行やりセットする行の変更、電子ズームに伴う画角の変更や、電子防振に伴う画角のずらし等である。タイミング制御部 850 は、システム制御部 860 による制御に基づいて撮像素子 1 及び映像信号処理部 830 の駆動タイミングを制御する。

30

#### 【 符号の説明】

#### 【 0 1 1 9 】

112 画素、

P D 光電変換素子

M 1 転送トランジスタ

M 2 リセットトランジスタ

M 3 増幅トランジスタ

M 4 選択トランジスタ

V L 制御線

S L センシング線

40

50

1 3 0 電圧制御部

1 2 2 比較部

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

---

フロントページの続き

(72)発明者 松野 靖司

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 武藤 隆

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 小泉 徹

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

審査官 橋 高志

(56)参考文献 特開2001-346102(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/341

H01L 27/146

H04N 5/374

H04N 5/378