(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5907686号

(P5907686)

(45) 発行日 平成28年4月26日(2016.4.26)

(24) 登録日 平成28年4月1日(2016.4.1)

(51) Int.Cl.

F 1

|               |           |               |

|---------------|-----------|---------------|

| HO 1 L 21/205 | (2006.01) | HO 1 L 21/205 |

| HO 1 L 21/338 | (2006.01) | HO 1 L 29/80  |

| HO 1 L 29/778 | (2006.01) | H             |

| HO 1 L 29/812 | (2006.01) |               |

請求項の数 10 (全 17 頁)

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2011-191264 (P2011-191264) |

| (22) 出願日     | 平成23年9月2日(2011.9.2)          |

| (65) 公開番号    | 特開2012-54559 (P2012-54559A)  |

| (43) 公開日     | 平成24年3月15日(2012.3.15)        |

| 審査請求日        | 平成26年8月6日(2014.8.6)          |

| (31) 優先権主張番号 | 12/807,336                   |

| (32) 優先日     | 平成22年9月2日(2010.9.2)          |

| (33) 優先権主張国  | 米国(US)                       |

|           |                                                                                                                                               |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 591150672<br>ナショナル セミコンダクター コーポレーション<br>NATIONAL SEMICONDUCTOR CORPORATION<br>アメリカ合衆国 カリフォルニア州 95051 サンタクララ エム/エス ディー3-579 セミコンダクター ドライブ 2900 |

| (74) 代理人  | 100098497<br>弁理士 片寄 恭三                                                                                                                        |

| (74) 代理人  | 100076185<br>弁理士 小橋 正明                                                                                                                        |

最終頁に続く

(54) 【発明の名称】大面積シリコン基板及びその他の基板上の多層III族窒化物バッファの成長

## (57) 【特許請求の範囲】

## 【請求項1】

半導体基板の上に第1のエピタキシャル層を形成することと、複数の分離された第1のエピタキシャル領域を形成するために前記第1のエピタキシャル層をエッチングすることと、前記エッチングされた第1のエピタキシャル層の上に第2のエピタキシャル層を形成することであって、前記エピタキシャル層の各々が少なくとも1つのIII族窒化物を含み、前記エピタキシャル層が集合的にバッファを形成する、前記第2のエピタキシャル層を形成することと、

前記バッファの上にデバイス層を形成することと、

前記デバイス層を用いる半導体デバイスを製作することと、

前記第2のエピタキシャル層を形成する前に、前記第1のエピタキシャル領域の上及び回りに第1の誘電体材料を堆積し、前記第1の誘電体材料と前記第1のエピタキシャル領域を平坦化することと、

複数の分離された第2のエピタキシャル領域を形成するために前記第2のエピタキシャル層をエッチングすることと、

前記第2のエピタキシャル領域の上及び回りに第2の誘電体材料を堆積し、前記第2の誘電体材料と前記第2のエピタキシャル領域とを平坦化することと、

を含む、方法。

## 【請求項2】

10

20

シリコン、サファイア又は炭化シリコンの一群から選択される材料で構成される半導体基板を提供することと、

窒化アルミニウムで構成される核形成層を前記基板の上に形成することと、

前記核形成層の上に第1のエピタキシャル層を形成することと、

前記第1のエピタキシャル層をエッチングして複数の分離された第1のエピタキシャル領域を形成することであって、前記複数の分離された第1のエピタキシャル領域が転移を最小化するように構造化された開始表面を提供するように構成される、前記エッチングすることと、

前記エッチングされた第1のエピタキシャル層の直上に第2のエピタキシャル層を形成することであって、前記エピタキシャル層の各々が少なくとも1つのIII族窒化物を含み、前記エピタキシャル層が集合的にバッファを形成し、前記バッファが前記第1のエピタキシャル層と前記第2のエピタキシャル層との複数の分離されたバッファ領域を構成する、前記第2のエピタキシャル層を形成することと、

デバイス層又はデバイス層の一部を形成することであって、前記デバイス層又は前記デバイス層の一部に半導体デバイスの少なくとも一部分が形成され、前記デバイス層が前記バッファの上の個別の層として又は前記バッファの一部分として形成される、前記デバイス層又は前記デバイス層の一部を形成することと、

トランジスタのソース、ドレイン又は他の領域を形成するために前記デバイス層を1つ又はそれ以上のドーパントでドープすることと、

前記デバイス層の上に1つ又はそれ以上の導電層を形成し、ソース及びドレンインコンタクトを形成するためにパターニング及びエッチングすることと、

を含む、方法。

#### 【請求項3】

請求項2に記載の方法であって、

前記デバイス層が少なくとも1つのIII族窒化物を含み、前記デバイス層が前記バッファの一部分としての複数の分離された第2のエピタキシャル領域を含み、前記第2のエピタキシャル領域が実質的に前記第1のエピタキシャル領域上のみに形成される、方法。

#### 【請求項4】

請求項2に記載の方法であって、

前記第2のエピタキシャル層を形成することが、前記第1のエピタキシャル領域と前記基板とを前記第2のエピタキシャル層で覆うことを含む、方法。

#### 【請求項5】

請求項4に記載の方法であって、

前記第2のエピタキシャル層をエッチングして複数の分離された第2のエピタキシャル領域を形成することを更に含む、方法。

#### 【請求項6】

請求項2に記載の方法であって、

前記デバイス層を形成することが、前記第2のエピタキシャル層の一部分として前記デバイス層を形成することを含む、方法。

#### 【請求項7】

請求項2に記載の方法であって、

前記半導体デバイスを分離することを更に含む、方法。

#### 【請求項8】

請求項2に記載の方法であって、

前記基板が少なくとも6インチの直径を有するシリコンウエハを含み、

前記少なくとも1つのIII族窒化物が、窒化ガリウム(GaN)、アルミニウム窒化ガリウム(AlGaN)、インジウム窒化アルミニウム(InAlN)、インジウムアルミニウム窒化ガリウム(InAlGaN)、窒化アルミニウム(AlN)、窒化インジウム(InN)及びインジウム窒化ガリウム(InGaN)の内の1つ又はそれ以上を含み、

10

20

40

50

前記第1のエピタキシャル層が1μm乃至3μmの厚さを有し、

前記第2のエピタキシャル層が1μm乃至3μmの厚さを有する、方法。

**【請求項9】**

シリコン、サファイア又は炭化シリコンの一群から選択される材料で構成される半導体基板と、

窒化アルミニウムで構成され、前記基板の上に形成される核形成層と、

前記核形成層の上に形成され、複数の分離された第1のエピタキシャル領域を含む、バッファ層であって、前記複数の分離された第1のエピタキシャル領域が転移を最小化するように構造化された開始表面を提供するように構成される、前記バッファ層と、

前記バッファ層の上に形成される少なくとも1つのIII族窒化物の第2のエピタキシャル層であって、前記第2のエピタキシャル層が半導体デバイスの一部分を有するデバイス層を形成するように構成され、前記第2のエピタキシャル層が複数の分離された第2のエピタキシャル領域を含む、前記第2のエピタキシャル層と、

トランジスタのソース、ドレイン又は他の領域を形成するために前記デバイス層の一部をドープする1つ又はそれ以上のドーパントと、

前記デバイス層の上に形成され、ソース及びドレインコンタクトを形成するためにパターニング及びエッチングされる1つ又はそれ以上の導電層と、

前記第1のエピタキシャル領域を互いに電気的に分離し、前記第2のエピタキシャル領域を互いに電気的に分離する、複数の誘電体領域と、

を含む、システム。

**【請求項10】**

シリコン、サファイア又は炭化シリコンの一群から選択される材料で構成される半導体基板と、

前記基板の上に形成され、窒化アルミニウムで構成される、核形成層と、

前記核形成層の上に形成され、複数の分離された第1のエピタキシャル領域を含む、第1のエピタキシャル層と、

前記第1のエピタキシャル層の上に形成される第2のエピタキシャル層であって、複数の分離された第2のエピタキシャル領域を含む、前記第2のエピタキシャル層と、

前記第1のエピタキシャル領域を互いに電気的に分離し、前記第2のエピタキシャル領域を互いに電気的に分離する、複数の誘電体領域と、

を含み、

前記エピタキシャル層の各々が少なくとも1つのIII族窒化物を含み、前記エピタキシャル層が集合的に少なくとも1つのIII族窒化物半導体デバイス用のバッファを形成する、装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本開示は、大略、集積回路に関するものである。更に、詳細には、本開示は、大面積シリコン基板及びその他の基板上の多層III族窒化物バッファの成長に関するものである。

**【背景技術】**

**【0002】**

窒化ガリウム(GaN)及びその他の「III族窒化物」は、高速又は高パワー集積回路装置を製造する場合に使用することが可能である。標準のシリコン装置と比較して、窒化ガリウムは高い動作温度に耐えることが可能であり且つ高いブレークダウン電圧を提供することが可能であるので、窒化ガリウムがしばしば望ましいものである。窒化ガリウムは、又、典型的に、良好な高周波数性能を提供し且つ一層低いオン抵抗を提供することが可能である。

**【0003】**

通常、天然の窒化ガリウム基板は入手可能なものではない。その代わりに、しばしば、<111>シリコンウェハなどのシリコンをベースとした基板上に窒化ガリウムエピタキ

10

20

30

40

50

シャル層が形成される。しかしながら、しばしば、大きなシリコン基板上に厚く高品質の窒化ガリウムエピタキシャル層を形成することは困難である。そのことは、大きな熱膨張係数の不一致及びウエハの曲がりを含む多数の要因に起因している。より詳細には、下側に存在するシリコン基板と比較して、窒化ガリウムエピタキシャル層は、冷却された場合に、約2倍も早く収縮する場合がある。このことは、窒化ガリウムエピタキシャル層内に引っ張り応力を発生させ、そのことがウエハの曲がりとなる場合があり且つエピタキシャル層内に亀裂を発生する場合がある。これらの問題は、6インチ以上の直径を有するシリコンウエハなどの一層大きな基板の場合により深刻である。

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0004】**

厚く高品質の窒化ガリウム層を形成することが不可能であることは、電界効果トランジスタ(FET)、高電子移動度トランジスタ(EMT)，又は窒化ガリウム層を使用して形成されるその他の装置のブレークダウン電圧を減少させる場合がある。又、典型的に、一層大きな基板の上に回路を製造することが望ましい。何故ならば、同じ処理ステップを使用して一層多数の回路を基板上に形成することが可能であり、回路当たりの製造コストの低下となるからである。一層大きな基板上に厚く高品質の窒化ガリウム層を形成することが不可能であるということは、これらのコスト低下を制限するか又は除去する場合があり、一層コスト高の回路とさせることとなる。更に、ウエハの曲がり及びエピタキシャル層の亀裂は、実際に、或る窒化ガリウムをベースとした回路の製造可能性を制限する場合がある。

**【課題を解決するための手段】**

**【0005】**

本発明の第1の側面によれば、

半導体基板上に第1エピタキシャル層を形成し、

該第1エピタキシャル層をエッチングして複数の分離された第1エピタキシャル領域を形成し、

該エッチングした第1エピタキシャル層上に第2エピタキシャル層を形成し、該エピタキシャル層の各々は少なくとも一つのIII族窒化物を有しており、該エピタキシャル層は一緒にになって1個のバッファを形成し、

該バッファ上に装置層を形成し、

該装置層を使用して半導体装置を製造する、

ことを特徴とする方法が提供される。

**【0006】**

好適には、該第2エピタキシャル層を形成する場合に、実質的に該第1エピタキシャル領域上にのみ第2エピタキシャル領域を選択的に形成する。

**【0007】**

好適には、該第2エピタキシャル層を形成する場合に、該第1エピタキシャル領域及び該基板を該第2エピタキシャル層で被覆する。

**【0008】**

好適には、更に、

該第2エピタキシャル層をエッチングして複数の分離された第2エピタキシャル領域を形成する、

ことを包含している。

**【0009】**

好適には、更に、

該第2エピタキシャル層を形成する前に、該第1エピタキシャル領域の上及び回りに第1誘電体物質を付着し且つ該第1誘電体物質及び該第1エピタキシャル領域を平坦化し、

該第2エピタキシャル層をエッチングして複数の分離された第2エピタキシャル領域を形成し、

10

20

30

40

50

該第2エピタキシャル領域の上及び回りに第2誘電体物質を付着し且つ該第2誘電体物質及び該第2エピタキシャル領域を平坦化させる、

ことを包含している。

【0010】

好適には、該装置層を形成する場合に、該第2エピタキシャル層を形成するために使用するのと同じ操作期間中に該装置層を形成する。

【0011】

好適には、更に、

該半導体装置を分離させる、

ことを包含している。

10

【0012】

好適には、

該基板が少なくとも6インチの直径を有するシリコンウエハを有しており、

該少なくとも1個のIII族窒化物が、窒化ガリウム(GaN)、アルミニウム窒化ガリウム(AlGaN)、インジウム窒化アルミニウム(InAlN)、インジウムアルミニウム窒化ガリウム(InAlGaN)、窒化アルミニウム(AlN)、窒化インジウム(InN)、及びインジウム窒化ガリウム(InGaN)の内の一つ又はそれ以上を有しており、

該第1エピタキシャル層が1μm乃至3μmの厚さを有しており、

該第2エピタキシャル層が1μm乃至3μmの厚さを有している、

ことを包含している。

20

【0013】

本発明の別の側面によれば、

半導体基板が設けられており、

該基板上の第1エピタキシャル層であって、複数の分離された第1エピタキシャル領域を有している第1エピタキシャル層が設けられており、

該第1エピタキシャル層上に第2エピタキシャル層が設けられており、

該エピタキシャル層の各々は少なくとも1個のIII族窒化物を有しており、該エピタキシャル層は一緒になって1個のバッファを形成しており、

該バッファ上に装置層が設けられており、

該装置層内又は上に半導体装置が設けられている、

ことを特徴とするシステムが提供される。

30

【0014】

好適には、該第2エピタキシャル層が複数の分離された第2エピタキシャル領域を有しており、該第2エピタキシャル領域が実質的に該第1エピタキシャル領域上にのみ設けられている。

【0015】

好適には、該第2エピタキシャル層が、該第1エピタキシャル領域及び該基板の少なくとも一部を被覆するエピタキシャル物質を有している。

【0016】

40

好適には、

該第2エピタキシャル層が複数の分離された第2エピタキシャル領域を有しており、

本システムが、更に、該第1エピタキシャル領域を互いに電気的に分離しており且つ該第2エピタキシャル領域を互いに電気的に分離している複数の誘電体領域を有している、

ことを包含している。

【0017】

好適には、更に、

分離領域が該装置層及び該バッファの少なくとも一部内に設けられており、該分離領域は該半導体装置を分離する形態とされている、

ことを包含している。

50

## 【0018】

好適には、

該基板は少なくとも6インチの直径を有するシリコンウエハを有しており、

該少なくとも1個のIII族は、窒化ガリウム(GaN)、アルミニウム窒化ガリウム(AlGaN)、インジウム窒化アルミニウム(InAlN)、インジウムアルミニウム窒化ガリウム(InAlGaN)、窒化アルミニウム(AlN)、窒化インジウム(InN)、及びインジウム窒化ガリウム(InGaN)の内の一つ又はそれ以上を有しており、

該第1エピタキシャル層が1μm乃至3μmの厚さを有しており、

該第2エピタキシャル層が1μm乃至3μmの厚さを有している、

ことを包含している。

10

## 【0019】

本発明の更に別の側面によれば、

半導体基板、

該基板上に設けられており複数の分離された第1エピタキシャル領域を有している第1エピタキシャル層、

該第1エピタキシャル層上に設けられている第2エピタキシャル層、

を有しており、該エピタキシャル層の各々が少なくとも1個のIII族窒化物を有しており、該エピタキシャル層が一緒にになって少なくとも1個のIII族窒化物半導体装置用のバッファを形成していることを特徴とする装置が提供される。

## 【0020】

20

好適には、該第2エピタキシャル層が複数の分離された第2エピタキシャル領域を有しており、該第2エピタキシャル領域が実質的に該第1エピタキシャル領域上にのみ設けられている。

## 【0021】

好適には、該第2エピタキシャル層が複数の分離された第2エピタキシャル領域を有しており、該第2エピタキシャル領域は該第1エピタキシャル領域及び該第1エピタキシャル領域に隣接した該基板の部分を被覆しており、該第2エピタキシャル領域は該基板のその他の部分を被覆するものではない。

## 【0022】

30

好適には、該第2エピタキシャル層が該第1エピタキシャル領域を被覆しているエピタキシャル物質を有している。

## 【0023】

好適には、

該第2エピタキシャル層が複数の分離された第2エピタキシャル領域を有しており、

本装置が、更に、該第1エピタキシャル領域を互いに電気的に分離し且つ該第2エピタキシャル領域を互いに電気的に分離している複数の誘電体領域を有している、ことを包含している。

## 【0024】

好適には、

該基板が少なくとも6インチの直径を有しているシリコンウエハを有しており、

40

該少なくとも1個のIII族窒化物が、窒化ガリウム(GaN)、アルミニウム窒化ガリウム(AlGaN)、インジウム窒化アルミニウム(InAlN)、インジウムアルミニウム窒化ガリウム(InAlGaN)、窒化アルミニウム(AlN)、窒化インジウム(InN)、及びインジウム窒化ガリウム(InGaN)の内の一つ又はそれ以上を有しており、

該第1エピタキシャル層が1μm乃至3μmの厚さを有しており、

該第2エピタキシャル層が1μm乃至3μmの厚さを有している、ことを包含している。

## 【図面の簡単な説明】

## 【0025】

50

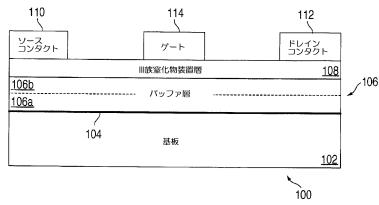

【図1】本開示に基く多層III族窒化物バッファを具備する例示的な半導体構成体を例示した概略図。

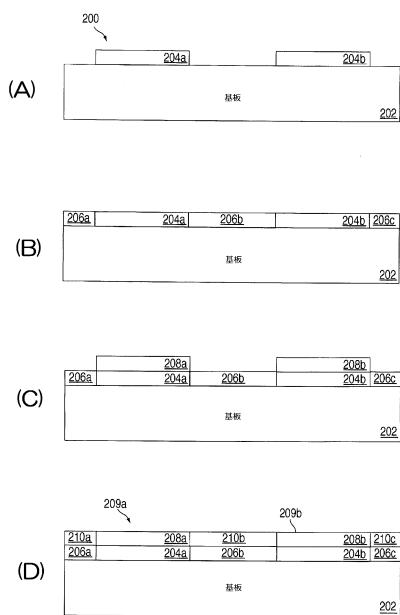

【図2】(A)乃至(D)は本開示に基いて多層III族窒化物バッファを具備する半導体構成体を形成するための第1の例示的な技術を例示した各概略図。

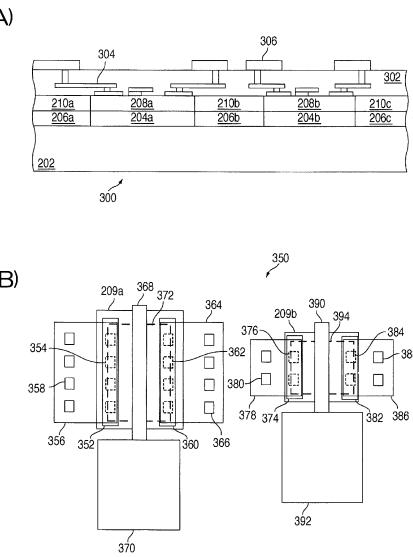

【図3】(A)及び(B)は、夫々、本開示に基いて図2(A)乃至(D)において形成された半導体構成体の側面図及び平面図。

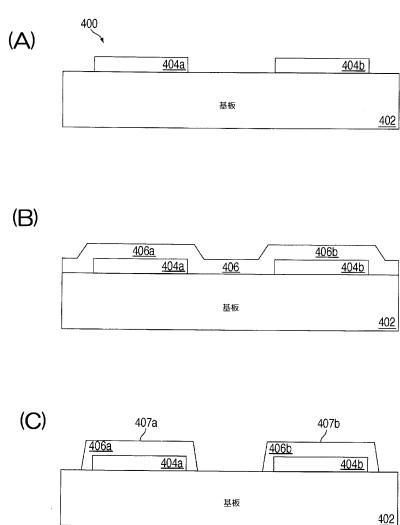

【図4】(A)乃至(C)は本開示に基く多層III族窒化物バッファを具備する半導体構成体を形成するための第2の例示的な技術を例示した各概略図。

【図5】(A)乃至(C)は本開示に基く多層III族窒化物バッファを具備する半導体構成体を形成するための第3の例示的な技術を例示した各概略図。 10

【図6】本開示に基く多層III族バッファを具備する半導体構成体を形成するための例示的な方法を例示したフローチャート。

#### 【発明を実施するための形態】

##### 【0026】

本特許文書において本発明の原理を説明するために以下に説明する図1乃至6及び種々の実施例は、単に例示的なものであって、本発明の範囲を制限するようないかなる様様でも解釈されるべきものではない。当業者が理解するように、本発明の原理は、任意のタイプの適宜構成された装置又はシステムにおいて実現することが可能である。

##### 【0027】

図1は、本開示に基く多層III族窒化物バッファを具備している例示的な半導体構成体100を例示している。図1に示した如く、半導体構成体100は基板102を含んでいる。基板102は、任意の適宜の半導体基板を表しており、それは半導体構成体100のその他の構成要素を支持又は担持する。基板102は、例えば、シリコン、サファイア、又は炭化シリコン基板を表すことが可能である。特定の実施例においては、基板102は、少なくとも6インチの直径を有する<111>シリコンウエハなどの大面積基板を表すことが可能である。基板102上に核形成層104を形成する。その核形成層104は、窒化アルミニウム等の任意の適宜の物質から形成することが可能である。 20

##### 【0028】

核形成層104の上にバッファ層106を形成する。このバッファ層106は、典型的に、半導体構成体100内の他の構成要素を基板102から分離させることを助け且つ形成される1個又はそれ以上のIII族窒化物装置に対して良好な開始表面（最小の転位）を提供するために使用される層を表している。バッファ層106は、III族窒化物等の任意の適宜の物質から形成することが可能である。「III族窒化物」とは、窒素と少なくとも一つのIII族元素とを使用して形成される化合物のことを意味している。例示的なIII族元素は、窒化ガリウム(GaN)、アルミニウム窒化ガリウム(AlGaN)、インジウム窒化アルミニウム(InAlN)、インジウムアルミニウム窒化ガリウム(InAlGaN)、窒化アルミニウム(AlN)、窒化インジウム(InN)、及びインジウム窒化ガリウム(InGaN)を包含している。バッファ層106は、有機金属成長法(MOCVD)又は分子線エピタキシ(MBE)技術を使用するによるなどの任意の適宜の態様で形成することが可能である。注意すべきことであるが、バッファ層106の形成は、核形成層104によって容易化せることが可能である。しかしながら、バッファ層106は、核形成層104を必要とするとの無い態様で形成することが可能であり、且つ核形成層104を省略することが可能である。 30

##### 【0029】

少なくとも一つのIII族窒化物装置層108がバッファ層106上に形成される。III族窒化物装置層108は、窒化ガリウムをベースとした電界効果トランジスタ(FET)又は高電子移動度トランジスタ(HEMT)等の少なくとも一つの半導体装置の一部を形成するために使用される。III族窒化物装置層108は、その他の又は付加的な集積回路構成要素を包含することが可能である。III族窒化物装置層108は、任意の適宜のIII族窒化物物質から形成することが可能である。III族窒化物装置層108は、又、バッファ層 40

106を形成するために使用されるものと同じ操作（MOCVD又はMBEのような）の期間中などの、任意の適宜の態様で形成することが可能である。一般的に、「装置層」とは、その中に半導体装置の少なくとも一部が形成される層の全て又は一部のことを意味している。装置層は、個別的な層として、又は別の層（エピタキシャル層など）の一部として形成することが可能である。

#### 【0030】

少なくとも一つのIII族窒化物装置の形成は、III族窒化物装置層108を使用して完成することが可能である。例えば、バッファ層106の上部部分又は装置層108の一部を一つ又はそれ以上のドーパントでドープしてソース、ドレイン、又はその他のトランジスタ領域を形成することが可能である。一つ又はそれ以上のメタル又はその他の導電層をパターン化し且つエッチングしてソース及びドレインコンタクト110-112を形成することが可能である。該構成体における活性領域は、メサエッチング又はイオン注入などにより、互いに分離させることが可能である。エッチング、誘電体付着、及びメタル又はその他の導電性物質の付着によってゲート114を形成することが可能である。その他の装置又は回路要素への接続は、コンタクト110-112及びゲート114を使用して構成することが可能である。

#### 【0031】

バッファ層106の厚さを増加させることを助けるために、バッファ層106は多層構成体として製造する。バッファ層106の第一部106a（第一III族窒化物エピタキシャル層など）は、基板102上に形成することが可能である。バッファ層106の第一部106aは、分離されたエピタキシャル領域を形成するために第一部106aをエッチングする等によって、処理することが可能であり、そのことは、バッファ層106の第一部106a上の応力を緩和させることを助ける。バッファ層106の第二部分106b（第二III族窒化物エピタキシャル層など）をバッファ層106の第一部106a上に形成し、且つバッファ層106の第二部分106bを処理することが可能である。所望により、この時点において、バッファ層106の一つ又はそれ以上の付加的な部分を形成することが可能である。

#### 【0032】

これらの異なる部分は一緒にになって、上述した従来の技術を使用して得られるものよりも一層厚いバッファ層106を形成することが可能である。例えば、バッファ層106を形成する各エピタキシャル層は厚さが1μmと3μmとの間とすることが可能であり（6インチ及び8インチ直径の<111>シリコン基板の場合）、最大で6μmの全体的な厚さを与える。一般的に、バッファ層106を形成する各エピタキシャル層は、熱膨張係数不一致、ウエハの曲がり、又は格子不一致等からのストレスに起因するエピタキシャル層に亀裂が表われる最小厚さのことを意味する「亀裂」厚さにおけるか又はそれ以下の厚さを有することが可能である。一層厚いバッファ層106の結果として、装置層108を使用して形成されるIII族窒化物装置は、従来のIII族窒化物装置と比較して、一層高いブレーカダウン電圧を有している。更に、多層III族窒化物装置を製造するために一層大きなシリコンウェハ又はその他の基板102を使用することが可能であり、製造される装置当たりのコストを低下させる。多層III族窒化物バッファ層106を形成するための種々の技術を以下に説明する。注意すべきことであるが、バッファ層106における異なる部分又は層は同一の厚さ又は異なる厚さを有することが可能であり、且つバッファ層106における異なる部分又は層は同一の物質から又は異なる物質から形成することが可能である。

#### 【0033】

図1は多層III族窒化物バッファを有する半導体構成体100の一つの例を例示しているが、図1に対して種々の変更を行うことが可能である。例えば、半導体構成体100の種々の層又はその他の構成体を形成するために任意のその他の物質及びプロセスを使用することが可能である。又、図1における構成要素の寸法及び形状及び図1におけるこれらの構成要素の配置は例示のために過ぎない。

#### 【0034】

10

20

30

40

50

図2(A)乃至(D)は、本開示に基いて多層III族窒化物バッファを有する半導体構成体を形成するための第1の例示的技術200を例示している。図2(A)に示したように、基板202が製造されるか又は提供される。基板202は6インチ又はそれ以上の直径を有するシリコンウエハなどの任意の適宜の半導体基板を表すことが可能である。注意すべきことであるが、炭化シリコン又はサファイアウエハ又は一層小さなシリコンウエハなどの任意のその他の適宜の基板を使用することが可能である。

#### 【0035】

エピタキシャル領域204a-204bを基板202上に形成する。エピタキシャル領域204a-204bは、1個又はそれ以上のIII族窒化物等の任意の適宜の物質から形成することが可能である。エピタキシャル領域204a-204bは、又、1μm乃至3μmなどの任意の適宜の厚さを有することが可能である(それは、典型的に、亀裂無しで、6インチ及び8インチ直径の<111>シリコン基板のような一層大きな基板上に形成することが可能である)。エピタキシャル領域204a-204bは、更に、MOCVD, MBE、又はパターン化され且つエッチングされるエピタキシャル層を形成するためのその他の技術を使用することなどによって、任意の適宜の技術を使用して形成することが可能である。該エピタキシャル層は、基板202上に核形成層(不図示)を使用して形成することが可能である。エピタキシャル領域204a-204bは、半導体装置が形成されるべき箇所のエピタキシャル層の区域を表すことが可能である。エピタキシャル層の除去される部分(エピタキシャル領域204a-204bの回り及び間)は、半導体装置が形成されることの無い箇所のエピタキシャル層の非活性区域を表すことが可能である。

#### 【0036】

図2(B)に示されているように、誘電体領域206a-206cはエピタキシャル領域204a-204bの間及び回りに形成される。誘電体領域206a-206cはエピタキシャル領域204a-204bを電気的に分離させることを助ける。誘電体領域206a-206cは、二酸化シリコン(SiO<sub>2</sub>)等の任意の適宜の物質から形成することが可能である。又、誘電体領域206a-206cは、エピタキシャル領域204a-204bの上及び間に誘電体層を形成し、次いで化学的機械的研磨(CMP)操作を実施することによるなどの任意の適宜の態様で形成することが可能である。このことはエピタキシャル領域204a-204bの上方の誘電体層を除去し且つエピタキシャル領域204a-204b及び誘電体領域206a-206cを平坦化させる。

#### 【0037】

図2(C)に示されているように、エピタキシャル領域208a-208bを該構成体の上に形成する。エピタキシャル領域208a-208bは、一つ又はそれ以上のIII族窒化物等の任意の適宜の物質から形成することが可能である。エピタキシャル領域208a-208bも1μm乃至3μm等の任意の適宜の厚さを有することが可能である。エピタキシャル領域208a-208bは、更に、MOCVD又はMBEを使用しての選択的付着又は成長等の任意の適宜の技術を使用して形成することが可能である。選択的付着又は成長とは、エピタキシャル領域208a-208bがほぼ露出されているエピタキシャル領域204a-204bの上に形成され、従ってエピタキシャル領域208a-208bがエピタキシャル領域204a-204bと実効的に自己整合されることを意味している。該選択的操作期間中に或るアモルファス又はその他の物質を誘電体領域206a-206c上に付着又は成長させることができるとあるが、この物質は除去するか又は形成される半導体装置の動作に悪影響を与えるものではない場合には残存させることが可能である。

#### 【0038】

図2(D)に示されているように、誘電体領域210a-210cをエピタキシャル領域208a-208bの間及び回りに形成し、そのことはエピタキシャル領域208a-208bを電気的に分離させることを助ける。誘電体領域210a-210cはSiO<sub>2</sub>等の任意の適宜の物質から形成することが可能である。又、誘電体領域210a-210cは、エピタキシャル領域208a-208bの上及び間に誘電体層を付着させ、次いで

10

20

30

40

50

CMP操作を実施することによるなどにより任意の適宜の態様で形成することが可能である。このことは、エピタキシャル領域208a - 208bの上方から該誘電体層を除去し且つエピタキシャル領域208a - 208b及び誘電体領域210a - 210cを平坦化させる。

#### 【0039】

エピタキシャル領域204a及び208aはバッファ層209aを形成し、その中又は上に少なくとも1個のトランジスタ装置又はその他の集積回路装置を製造することが可能である（領域208aの一部として又はその上に装置層が形成されることを仮定）。同様に、エピタキシャル領域204b及び208bはバッファ層209bを形成し、その中又は上に、少なくとも1個の別のトランジスタ装置又はその他の集積回路装置を製造することが可能である（領域208bの一部として又はその上に装置層が形成されることを仮定）。この時点において、エピタキシャル領域208a - 208b上にIII族窒化物装置層又は装置の形成などの付加的な処理ステップを行うことが可能である。これの1例が図3(A)及び(B)に示されている。10

#### 【0040】

図3(A)及び(B)は、この開示に基いて図2(A)乃至(D)で形成される半導体構成体の側面図及び平面図を夫々示している。特に、図3(A)は該半導体構成体の側面図300を示しており、一方図3(B)は該半導体構成体の平面図350を示している。

#### 【0041】

図3(A)に示したように、少なくとも1個の層間誘電体(ILD)層又は他の誘電体層302が図2(D)の半導体構成体の上に形成する。このことは、III族窒化物装置層及び装置が図2(D)の半導体構成体の上に形成した後に、行うことが可能である。又、誘電体層302内に種々の構成体304を形成することが可能である。誘電体層302は、任意の適宜の誘電体物質から形成した任意の適宜の数の層を包含している。構成体304は、ソース、ドレイン、及びゲートコンタクト、メタル相互接続、及び導電性プラグ等のトランジスタ装置又はその他の装置へ結合するための任意の適宜の構成体を包含することが可能である。更に、導電性構成体306は、外部信号線に対しての電気的接続を与えるために誘電体層302上に形成することが可能である。導電性構成体306は、各バッファ209a - 209b上にソース及びドレインボンドパッドを形成するためにメタル層を付着させ且つエッチングする等の任意の適宜の物質を使用して任意の適宜の態様で形成することが可能である。これらの構成要素304 - 306は、従来の相補的金属酸化物半導体(CMOS)バックエンド製造操作を使用するなどの任意の適宜の態様で製造することが可能である。2030

#### 【0042】

図3(B)において、ソースコンタクト352はエピタキシャル領域208aに形成されているソースと電気的に接触する。1個又はそれ以上の導電性プラグ354がソースコンタクト352を、1個又はそれ以上の導電性プラグ358によって別の構成要素（ソースボンドパッド306）へ電気的に結合されている導電性相互接続356へ、電気的に結合させる。同様に、ドレインコンタクト360はエピタキシャル領域208aに形成されているドレインと電気的に接触している。1個又はそれ以上の導電性プラグ362がドレインコンタクト360を、1個又はそれ以上の導電性プラグ366によって別の構成要素（ドレインボンドパッド306）へ電気的に結合されている導電性相互接続364へ、電気的に結合させる。ゲート368がエピタキシャル領域208aの上に形成されている。ゲート368はゲートボンドパッド370と電気的に接触している。該ボンドパッドは、一層大きな装置における他の回路へ電気的に接続させることができる。エピタキシャル領域208aに形成される半導体装置のトレンチ端部における高電圧を回避することを助けるために本構成体の領域372の外側に分離注入（窒素を使用するものなど）を実施することが可能である。装置層を介してエッチングし且つ半導体装置が形成される区域の回りのバッファ層の一部をエッチングするなどのその他の技術を使用して、形成中の半導体装置の分離を助けることが可能である。4050

## 【0043】

同様の態様で、ソースコンタクト 374 がエピタキシャル領域 208b に形成されているソースと電気的に接触する。1個又はそれ以上の導電性プラグ 376 が、ソースコンタクト 374 を、1個又はそれ以上の導電性プラグ 380 によって別の構成要素（第2ソースボンドパッド 306）へ電気的に結合されている導電性相互接続 378 へ電気的に結合させる。ドレインコンタクト 382 がエピタキシャル領域 208b に形成されているドレインと電気的に接触する。1個又はそれ以上の導電性プラグ 384 が、ドレインコンタクト 386 を1個又はそれ以上の導電性プラグ 388 によって別の構成要素（第2ドレインボンドパッド 306）へ電気的に結合されている導電性相互接続 386 へ電気的に結合させる。ゲート 390 がエピタキシャル領域 208b の上に形成される。ゲート 390 はゲートボンドパッド 392 と電気的に接触している。該ボンドパッドは一層大きな装置における他の回路へ電気的に接続することが可能である。エピタキシャル領域 208b に形成される半導体装置のトレンチ端部における高電圧を回避することを助けるために本構成体の領域 394 の外側に分離注入を実施することが可能である。その他の分離技術を使用することも可能である。10

## 【0044】

これらの構成要素 352 - 394 の各々は、任意の適宜の物質から且つ任意の適宜の技術を使用して形成することが可能である。この例において、異なる寸法のトランジスタ装置がバッファ 209a - 209b を使用して形成されるが、任意の数の装置を同一の又は同様の態様で製造することが可能であり且つ任意の適宜の寸法を有することが可能である。20

更に、エピタキシャル領域 204a - 204b 及び 208a - 208b は、一緒になって、顕著なウエハの曲げ又は亀裂無しで、6 μm 又はそれ以上のバッファ等の一層厚いバッファ 209a - 209b を形成する。バッファ 209a - 209b は一層厚いので、ここで形成されるトランジスタ装置は著しく一層高いブレークダウン電圧を有することが可能である。更に、このことは、6 インチ又は一層大きなシリコンウエハのような大型の半導体基板を使用しても達成することが可能であり、そのことは顕著なコストの節約を与える。

## 【0045】

図 2 (A) 乃至 (D) は多層 III 族窒化物バッファを有する半導体構成体を形成するための技術 200 の 1 例を例示しており且つ図 3 (A) 乃至 (B) は該半導体構成体の概略図を例示しているが、図 2 (A) 乃至 (D) 及び 3 (A) 及び (B) に対して種々の変更を行うことが可能である。例えば、該構成体における各要素は、任意の適宜の物質及び任意の適宜の技術を使用して製造することが可能である。又、該構成体における要素の相対的な寸法及び形状は特定の必要性に従って修正することが可能である。更に、核形成層又は単一のバッファを形成するために結合される 2 個を超えるエピタキシャル領域などの附加的な構成要素を該半導体構成体内に形成することが可能である。30

## 【0046】

図 4 (A) 乃至 (C) は、本開示に従って多層 III 族窒化物バッファを有する半導体構成体を形成するための第 2 の例示的な技術 400 を例示している。図 4 (A) に示したように、基板 402 を製造又は提供する。6 インチ又はそれ以上の直径を有するシリコンウエハなどの任意の適宜の半導体基板を使用することが可能である。基板 402 上にエピタキシャル領域 404a - 404b を形成する。エピタキシャル領域 404a - 404b は、1 個又はそれ以上の III 族窒化物等の任意の適宜の物質から形成することが可能である。エピタキシャル領域 404a - 404b も 1 μm 乃至 3 μm 等の任意の適宜の厚さを有することが可能である。エピタキシャル領域 404a - 404b は、MOCVD、MBE、又はパターン化され且つエッチングされるエピタキシャル層を形成するためのその他技術を使用することなどの任意の適宜の技術を使用して形成することが可能である。該エピタキシャル層は、基板 402 上に形成される核形成層（不図示）を使用して形成することが可能である。該エピタキシャル層をエッチングすることは、エピタキシャル層 404 におけるストレスを緩和させることを助けることが可能である。4050

## 【0047】

図4(B)に示したように、エピタキシャル層406及び基板402上にエピタキシャル層406を形成する。エピタキシャル層406は、1個又はそれ以上のIII族窒化物等の任意の適宜の物質から形成することが可能である。エピタキシャル層406も1μm乃至3μm等の任意の適宜の厚さを有することが可能である。エピタキシャル層406は、更に、MOCVD又はMBE等の任意の適宜の技術を使用して形成することが可能である。

## 【0048】

エピタキシャル層406は、図4(C)に示したように、エピタキシャル層406のエピタキシャル領域406a-406bを分離させるためにエッチングさせることが可能である。該エッチングは、エピタキシャル層406内のストレス即ち応力を緩和させることを助けることが可能である。エピタキシャル領域404a-404b及びエピタキシャル領域406a-406bはバッファ407a-407bを形成することが可能である。トランジスタ装置又はその他の集積回路構成要素をバッファ407a-407b内又は上に形成することが可能である(装置層がエピタキシャル領域406a-406bの一部として又はその上に形成されることを仮定)。エピタキシャル領域404a-404b及びエピタキシャル領域406a-406bの結合厚さはこれらの装置に対して一層高いブレークダウン電圧を提供することが可能である。何故ならば、その結合厚さは単一の成長のみにより可能な最大厚さを超えるものだからである。代替的に、エピタキシャル層406が非常に厚く成長されるものではない場合には(1μm乃至3μm)、処理コストを低下させるためにエッチングしないままとさせることが可能である。

## 【0049】

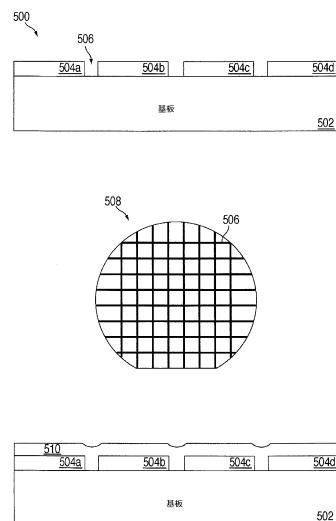

図5(A)乃至(C)は、本開示に基く多層III族窒化物バッファを有する半導体構成体を形成する3番目の例示的な技術500を示している。図5(A)に示したように、半導体構成体502を製造するか又は供給する。エピタキシャル領域504a-504dを基板502の上に形成する。エピタキシャル領域504a-504dは任意の適宜の物質から且つ任意の適宜の態様で形成することが可能である。例えば、エピタキシャル領域504a-504dはIII族窒化物エピタキシャル層をエッチングすることにより形成することが可能である。該エッチングはエピタキシャル領域504a-504dの間にトレーニングチ506を形成することが可能であり、それはエピタキシャル領域504a-504d上のストレス即ち応力を緩和させることを助ける。該エッチングは、図5(B)に示したように発生させることができ、該図はグリッドパターン508を形成するトレーニングチ506を示している。

## 【0050】

図5(C)に示したように、エピタキシャル層510をトレーニングチ506内及びエピタキシャル領域504a-504d及び基板502の上に形成する。エピタキシャル層510は任意の適宜の物質から且つ任意の適宜の態様で形成することが可能である。図示していないが、エピタキシャル層510の異なる領域を分離させるためにエピタキシャル層510をエッチングすることが可能である。該エッチングもエピタキシャル層510上のストレスを緩和させることを助けることが可能である。エピタキシャル層510がエッチングされるか否かに拘わらずに、エピタキシャル層510の領域内及び上にトランジスタ装置又はその他の集積回路構成要素を形成することが可能である(装置層をエピタキシャル層510の一部として又はその上に形成することを仮定)。エピタキシャル領域502a-502d及びエピタキシャル層510の結合厚さはこれらの装置に対して一層高いブレークダウン電圧を与えることが可能である。何故ならば、その結合厚さは単一の成長のみにより可能な最大厚さを超えるものだからである。

## 【0051】

図4(A)乃至5(C)は多層III族窒化物バッファを有する半導体構成体を形成するための技術の2つの付加的な例を例示しているが、図4(A)乃至5(C)に対して種々の変更を行うことが可能である。例えば、該構成体における各要素は、任意の適宜の物質

10

20

30

40

50

及び任意の適宜の技術を使用して製造することが可能である。又、該構成体における要素の相対的寸法及び形状は、特定の必要性に応じて修正することが可能である。更に、核形成層又は単一のバッファを形成するために結合される2個を越えるエピタキシャル領域等の付加的な構成要素を該半導体構成体内に形成することが可能である。

#### 【0052】

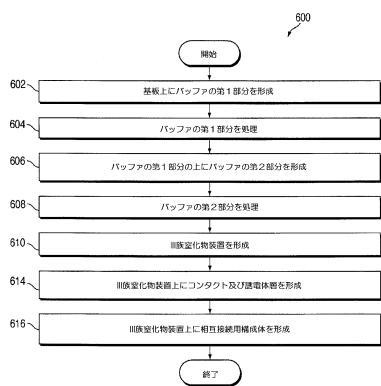

図6は、本開示に基いて多層III族窒化物バッファを有する半導体構成体を形成するための例示的な方法600を示している。説明の便宜上、方法600を図2(A)乃至(D)に示した技術に関して説明する。

#### 【0053】

図6に示したように、ステップ602において、基板上にバッファの第一部分を形成し、且つステップ604において、該バッファの第一部分を処理する。このことは、例えば、基板202上にエピタキシャル領域204a-204bを形成することを包含することができる。特定の例として、このことは、基板202上にエピタキシャル層を形成し、エピタキシャル領域204a及び204bとなるべき箇所の上にマスクをパターン化し、且つエピタキシャル領域204a-204bを形成するために該マスクによって保護されていない区域におけるエピタキシャル層をエッチングすることを包含することができる。このことは、又、エピタキシャル領域204a-204bの回りに分離用の誘電体領域206a-206cを形成することを包含することが可能である。注意すべきことであるが、単一のエピタキシャル層又は複数のエピタキシャル層を使用して該バッファの第一部分を形成することが可能である。これらの層は同一又は異なるものとすることが可能であり、且つ各層は一様であるか又はグレード付き(graded)即ち勾配を有するものとすることが可能である。分離されている領域を有する該バッファの第一部分を形成するための別の技術は米国特許出願第12/577,576号に開示されており、それを引用により本明細書内に取り込む。

10

20

30

40

#### 【0054】

ステップ606において、該バッファの第二部分を該バッファの第一部分の上に形成し、且つステップ608において、該バッファの第二部分を処理する。このことは、例えば、エピタキシャル領域204a-204bの上にエピタキシャル領域208a-208bを形成することを包含することができる。特定の例として、このことは、エピタキシャル領域204a-204bの上にエピタキシャル層を形成し、エピタキシャル領域208a及び208bとなるべき箇所の上にマスクをパターン化し、且つエピタキシャル領域208a-208bを形成するためにマスクされていないエピタキシャル層をエッチングすることを包含することができる。別の特定の例として、このことは、エピタキシャル領域204a-204bの上にエピタキシャル領域208a-208bを選択的に形成することを包含することができる。これは、又、エピタキシャル領域208a-208bの回りに分離用の誘電体領域210a-210cを形成することを包含することができる。注意すべきことであるが、何らかの装置をエピタキシャル領域208a-208b内に形成すべき場合には、エピタキシャル領域208a-208bはバッファ及び装置を表すことが可能である。エピタキシャル領域204a-204b及び208a-208bは、一体となって、著しい亀裂を蒙ることが無いか又は著しいウエハの曲がりを発生することの無い一層厚いバッファを形成する。注意すべきことであるが、単一のエピタキシャル層又は複数個のエピタキシャル層を該バッファの第二部分を形成するために使用することができる。それらの層は、同一のもの又は異なるものとすることが可能であり、且つ各層は一様であるか又はグレード付き即ち勾配が付けられているものとすることが可能である。

50

#### 【0055】

ステップ610において、1個又はそれ以上のIII族窒化物装置を該バッファ上に形成する。このことは、例えば、エピタキシャル領域208a-208b内又はエピタキシャル領域208a-208b上に形成されている装置層108内にソース、ドレイン、及びその他の装置構成体を形成することを包含することができる。ステップ614におい

50

て、III族窒化物装置上にコンタクト及び1個又はそれ以上の誘電体層を形成する。このことは、例えば、III族窒化物装置上にソース、ドレイン、及びゲートコンタクトを形成することを包含することが可能である。このことは、又、III族窒化物装置上及び該ソース、ドレイン、及びゲートコンタクト上にILD層又はその他の誘電体層302を形成することを包含することも可能である。ステップ616において、III族窒化物装置上に相互接続構成体を形成する。このことは、例えば、該ソース、ドレイン、及びゲートコンタクトをボンドパッド又はその他の構成体へ結合させるために導電性相互接続及び導電性プラグを形成することを包含することが可能である。

#### 【0056】

図6は多層III族窒化物バッファを有する半導体構成体を形成する方法600の1例を示しているが、図6に対して種々の変更を行うことが可能である。例えば、一連のステップとして示してあるが、図6に示した種々のステップはオーバーラップするか、並列に発生するか、異なる順番で発生するか、又は複数回発生することが可能である。

10

#### 【0057】

本特許文書において使用されている或る単語及び用語の定義について説明しておくことが有益的である。「結合」という用語及びその派生語は、互いに物理的に接触しているか否かに拘わらずに、2個又はそれ以上の構成要素の間の任意の直接的又は間接的なコミュニケーション即ち通信のことを意味している。「包含する」及び「有する」という用語及びそれらの派生語は、制限無しで包含することを意味している。「又は」という用語は包括的であり、及び／又はを意味している。「と関連する」及び「それと関連する」という用語及びそれらの派生語は、包含する、その中に包含されている、それと相互接続する、含有する、その中に含有されている、それへ又はそれと接続する、それへ又はそれと結合する、それと通信可能である、それと共同する、インタリープする、並置する、それに近接している、それへ又はそれと結合されている、持っている、その特性を持っている、それへ又はそれと関係を持っている等を意味する場合がある。

20

#### 【0058】

以上、本発明の具体的実施の態様について詳細に説明したが、本発明はこれらの具体的実施例に制限されるべきものではなく、本発明の技術的範囲を逸脱すること無しに種々の変形が可能であることは勿論である。

30

#### 【符号の説明】

#### 【0059】

- 100：半導体構成体

- 102：基板

- 104：核形成層

- 106：バッファ層

- 108：III族窒化物装置層

- 110 - 112：コンタクト

- 114：ゲート

【図1】

【図2】

【図4】

【図3】

【図5】

【図6】

---

フロントページの続き

(72)発明者 サンディープ アール. バール

アメリカ合衆国， カリフォルニア 94306， パロ アルト， エドリー アベニュー 2

97

(72)発明者 ジャマール ラムダニ

アメリカ合衆国， メイン 04074， スカボロー， パイン レッジ ドライブ 20

審査官 正山 旭

(56)参考文献 特開2009-130010(JP,A)

特開2009-231561(JP,A)

特開2000-286450(JP,A)

特表2003-514392(JP,A)

米国特許第06342404(US,B1)

(58)調査した分野(Int.Cl., DB名)

H01L 21/205

H01L 21/338

H01L 29/778

H01L 29/812