(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5192163号

(P5192163)

(45) 発行日 平成25年5月8日(2013.5.8)

(24) 登録日 平成25年2月8日(2013.2.8)

(51) Int.Cl.

F 1

**H01L 21/3205 (2006.01)**

**H01L 21/768 (2006.01)**

**H01L 23/522 (2006.01)**

**H01L 21/60 (2006.01)**

H01L 21/88 T

H01L 21/60 301P

請求項の数 9 (全 12 頁)

(21) 出願番号 特願2007-75858 (P2007-75858)

(22) 出願日 平成19年3月23日 (2007.3.23)

(65) 公開番号 特開2008-235728 (P2008-235728A)

(43) 公開日 平成20年10月2日 (2008.10.2)

審査請求日 平成22年3月19日 (2010.3.19)

(73) 特許権者 000154325

住友電工デバイス・イノベーション株式会

社

神奈川県横浜市栄区金井町1番地

(74) 代理人 100087480

弁理士 片山 修平

(74) 復代理人 100137615

弁理士 横山 照夫

(74) 復代理人 100134511

弁理士 八田 俊之

(72) 発明者 五十嵐 武司

山梨県中巨摩郡昭和町大字紙漉阿原100

○番地 ユーディナデバイス株式会社内

審査官 崎間 伸洋

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

化合物半導体層上に設けられ、A1を含み、かつボンディング領域を避けて設けられた配線接続部を有するパッドと、

前記パッドの前記配線接続部に電気的に接続されたAuを含む配線層と、

前記配線接続部と前記配線層との間に設けられたバリア層と、

前記配線層の端部において、前記配線層と前記パッドとの間に設けられた第1絶縁層と

を具備し、

前記パッドの前記配線接続部上には、前記配線層および前記バリア層が延在し、前記パッドの前記ボンディング領域上には、前記配線層および前記バリア層が延在していないことを特徴とする半導体装置。

## 【請求項 2】

前記半導体装置の使用上限温度は200以上であることを特徴とする請求項1記載の半導体装置。

## 【請求項 3】

前記ボンディング領域に接続されるべきボンディングワイヤの太さは100μm以上であることを特徴とする請求項1記載の半導体装置。

## 【請求項 4】

前記パッドの端部において、前記配線層と前記パッドとの間に設けられた第2絶縁層を

10

20

具備することを特徴とする請求項1記載の半導体装置。

**【請求項 5】**

前記パッドは第1層と該第1層上の第2層とからなり、

前記配線層は前記第1層上に延在することにより前記パッドに接続され、

前記ボンディング領域は前記第2層に設けられていることを特徴とする請求項1記載の半導体装置。

**【請求項 6】**

前記第2層は前記配線層上に第3絶縁層を介し延在することを特徴とする請求項5記載の半導体装置。

**【請求項 7】**

前記バリア層は、TiN、TiWN、WN、WSiN及びTaNのいずれかを含むことを特徴とする請求項1記載の半導体装置。

**【請求項 8】**

前記バリア層の厚さは100nmから200nmであることを特徴とする請求項1記載の半導体装置。

**【請求項 9】**

前記ボンディングワイヤはAlを含むことを特徴とする請求項3記載の半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、半導体装置に関し、特にAuを含む配線層とAlを含むボンディングパッドとを有する半導体装置に関する。

**【背景技術】**

**【0002】**

インバータ、コンバータやスイッチングレギュレータのスイッチに用いられる高電力用半導体装置には主にシリコン基板を用いた半導体装置が用いられている。この半導体装置においては、半導体チップに接続されるボンディングワイヤに大電流が流れるため、ボンディングワイヤは抵抗率の小さなAl(アルミニウム)が用いられている。一方、シリコン基板を用いた半導体チップ上に形成される配線層は一般的にAlを用いている。よって、Alを主に含むボンディングパッド(以下、Alパッド)に、Alを主に含むボンディングワイヤ(以下、Alワイヤ)をボンディングすることとなる。

**【0003】**

近年、GaN(窒化ガリウム)等のII-V族化合物半導体層を有する半導体装置を用いた高電力用半導体装置の開発が進められている。II-V族化合物半導体層を用いた半導体チップにおいては、Au(金)を主に含む配線層(以下、Au配線層)が用いられる。これは、半導体層に接触するオームック電極あるいはゲート電極等の電極としてAuを含む電極が用いられるためである。

**【0004】**

AlとAuは200程度になると反応し金属間化合物を形成する。この化合物は抵抗率が高いため、AlとAuとの接触箇所の電気抵抗が大きくなってしまう。この課題はパープルプレーグ(AuAl<sub>2</sub>の生成)として知られている。そこで、特許文献1のように、Alを主に含む配線層(Al配線層)にAuを主に含むボンディングワイヤ(Auワイヤ)を接続する際は、Al配線層上にバリア層を介しAuを主に含むパッド(Auパッド)を形成し、Auパッド上にAuワイヤを接続する。また、特許文献2及び3のように、Al配線層とAu配線層との間にバリア層を形成する。これにより、AlとAuとの反応を抑制することができる。

**【特許文献1】特開昭59-210656号公報**

**【特許文献2】特開平11-162996号公報**

**【特許文献3】特開2006-173386号公報**

**【発明の開示】**

10

20

30

40

50

**【発明が解決しようとする課題】****【0005】**

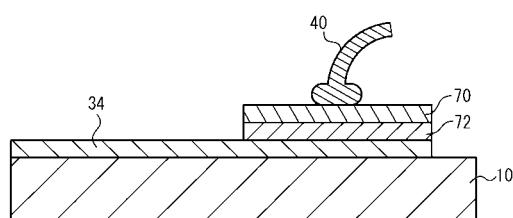

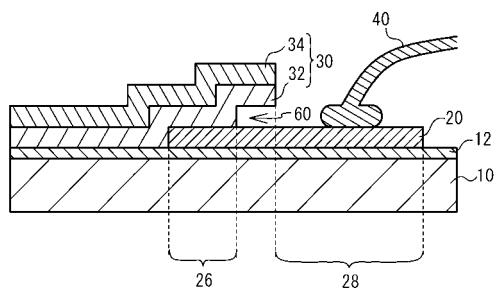

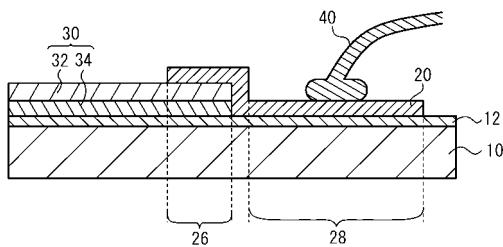

しかしながら、図1のように、化合物半導体の基板10上に形成されたAu層34(Au配線層)にバリア層72を介しAlパッド70を形成し、Alパッド70にAlワイヤ40を接続すると、後述するがAlとAuとの反応が生じてしまうことがわかった。

**【0006】**

本発明は、上記課題に鑑みなされたものであり、Alパッド上にボンディングワイヤを形成することによる、AlパッドとAu配線層との反応を抑制することを目的とする。

**【課題を解決するための手段】****【0007】**

本発明は、化合物半導体層上に設けられ、Alを含み、かつボンディング領域を避けて設けられた配線接続部を有するパッドと、前記パッドの前記配線接続部に電気的に接続されたAuを含む配線層と、前記配線接続部と前記配線層との間に設けられたバリア層と、前記配線層の端部において、前記配線層と前記パッドとの間に設けられた第1絶縁層と、

を具備し、前記パッドの前記配線接続部上には、前記配線層および前記バリア層が延在し、前記パッドの前記ボンディング領域上には、前記配線層および前記バリア層が延在していないことを特徴とする半導体装置である。本発明によれば、パッドにボンディングワイヤが接続されるべきボンディング領域を避けて設けられた配線接続部において、配線層がバリア層を介しパッドに接続されている。これにより、ワイヤボンディングにより、パッドと配線層とが反応することを抑制できる。

20

**【0008】**

上記構成において、前記半導体装置の使用上限温度は200以上である構成とすることができます。この構成によれば、AlとAuとが反応する温度である200以上においても、AlとAuとの反応を抑制することができる。

**【0009】**

前記ボンディング領域に接続されるべきボンディングワイヤの太さは100μm以上である構成とすることができます。この構成によれば、ボンディングの際パッドに加わる圧力が大きい場合も、AlとAuとの反応を抑制することができる。

**【0011】**

上記構成において、前記パッドの端部において、前記配線層と前記パッドとの間に設けられた第2絶縁層を具備する構成とすることができます。この構成によれば、パッドの端部におけるAuとAlが反応を抑制することができる。

30

**【0012】**

上記構成において、前記パッドは第1層と該第1層上の第2層とからなり、前記配線層は前記第1層上に延在することにより前記パッドに接続され、前記ボンディング領域は前記第2層に設けられている構成とすることができます。この構成によれば、パッド端部のAlとAuとの反応を抑制し、かつボンディング領域に接続されるべきボンディングワイヤとパッドとの密着強度を保つことができる。

**【0013】**

上記構成において、前記第2層は前記配線層上に第3絶縁層を介し延在する構成とすることができます。

40

**【0014】**

上記構成において、前記バリア層は、TiN、TiWN、WN、WSiN及びTaNのいずれかを含む構成とすることができます。

**【0015】**

上記構成において、前記バリア層の厚さは100nmから200nmである構成とすることができます。

**【0016】**

上記構成において、前記ボンディングワイヤはAlを含む構成とすることができます。この構成によれば、ボンディングワイヤとパッドとの間での金属間反応を抑制することができます

50

きる。

**【発明の効果】**

**【0017】**

本発明によれば、パッドにボンディングワイヤが接続されるべきボンディング領域を避けて設けられた配線接続部において、配線層がバリア層を介しパッドに接続されている。これにより、ワイヤボンディングにより、パッドと配線層とが反応することを抑制できる。

**【発明を実施するための最良の形態】**

**【0018】**

まず、図1に係る構造において、A1パッド70とAu層34とが反応する原因について調査した。その結果、A1ワイヤ40をA1パッド70にワイヤボンディングした際に、バリア層72が破壊されることが原因であることがわかった。ワイヤボンディングする場合は、半導体チップに加える熱及び超音波並びにワイヤツールがパッドに加える圧力の寄与により、ボンディングワイヤとパッドとを機械的及び電気的に接続する。AuワイヤをAuパッドにボンディングする場合は、熱と超音波が主に寄与する(超音波熱圧着)。これに対しA1ワイヤをA1パッドにボンディングする場合は、圧力が主に寄与する。このため、A1ワイヤを用いる場合は、Auワイヤに比べ大きな圧力が必要となる。このため、特許文献1のような配線層上にバリア層を介しパッドが形成される構造では、バリア層が破壊されるものと考えられる。そこで、バリア層の破壊を抑制する実施例を以下に説明する。

**【実施例1】**

**【0019】**

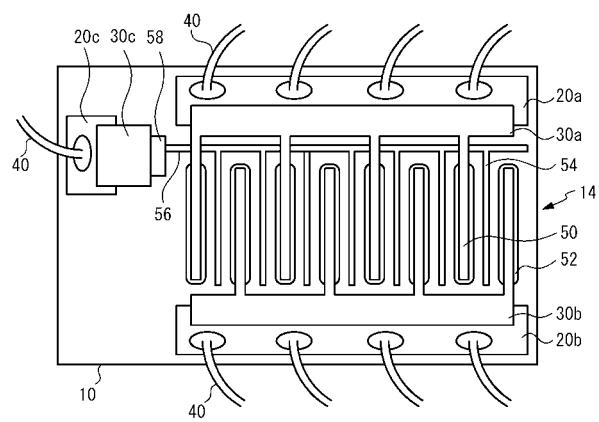

実施例1は、GaNを用いたFET(Field Effect Transistor)の例である。図2は実施例1に係る半導体装置内の半導体チップの平面図である。サファイア基板またはSiC(炭化シリコン)等の基板10上にGaNを含む半導体層であるGaN系半導体層が形成されている。GaN系半導体層上には、上からAl/Ti(チタン)からなるソース電極50及びドレイン電極52、上からAu/Ni(ニッケル)からなるゲート電極54が形成されている。ソース電極50、ドレイン電極52及びゲート電極54はフィンガを形成している。FET14は複数のフィンガで構成されている。すなわち、マルチフィンガ構造を有している。ソース電極50及びドレイン電極52上にはそれぞれ配線層30a及び30bが形成されている。配線層30a及び30bは櫛型をしており、フィンガがバスバーに接続されている。配線層30aのバスバーがA1パッド20a上に延在することにより、配線層30aとA1パッド20aとが電気的に接続されている。配線層30bとA1パッド20bにおいても同様である。各ゲート電極54はバスバー56を介しゲートパッド58に接続される。ゲートパッド58とA1パッド20cとは配線層30cを介し接続される。各配線層30aから30cは、バリア層とAu層とから構成される。各A1パッド20aから20cには、1または複数のA1ワイヤ40が接続されている。

**【0020】**

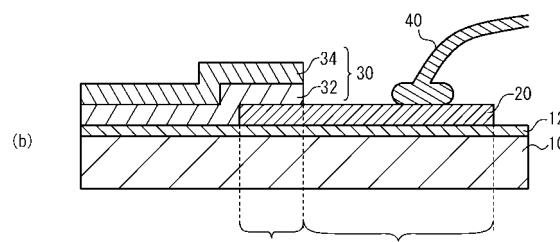

図3(a)及び図3(b)は基板10上に設けられたA1パッド20と配線層30とからなるパッド構造を示す平面図及び断面図である。図3(a)及び図3(b)を参照に、基板10上にGaN系半導体層である化合物半導体層12が設けられている。化合物半導体層12上にA1パッド20及び配線層30が形成されている。なお、化合物半導体層12上に層間絶縁膜や保護膜等の絶縁膜を介しA1パッド20及び配線層30が形成されていてもよい。また、A1パッド20及び配線層30の一部は、化合物半導体層12を介さず基板10上に設けられていてもよい。A1パッド20上に配線層30が延在することにより、配線層30とA1パッド20とが電気的に接続されている。

**【0021】**

A1パッド20は膜厚が例えば2μmである。A1パッド20上には太さが200μmから300μmのA1ワイヤ40が接続されている。配線層30は、バリア層32とバリ

10

20

30

30

40

50

ア層32上のAu層34(Auを含む配線層、Au配線層)とからなる。バリア層32は、例えば膜厚が50nmから300nm、好ましくは100から200nmのTiN(窒化チタン)やTiWN(窒化チタンタングステン)等である。バリア層32として、他にWN(窒化タングステン)、WSiN(窒化珪化タングステン)またはTaN(窒化タンタル)等を用いることもできる。バリア層32の膜厚が薄すぎると膜厚のばらつき等によりより薄い箇所が生じるためバリア性が小さくなってしまう。一方、膜厚が厚すぎると、バリア層32をエッチングする際のオーバーエッチング時間が長くなり、バリア層32下の下地(実施例1では化合物半導体層12)がエッチングされてしまう。また、処理時間も長くなってしまう。よって、バリア層32の膜厚は例えば50nmから300nmであり、好ましくは100nmから200nmである。Au層34の膜厚は例えば5μmから10μmである。

10

#### 【0022】

実施例1によれば、A1パッド20にA1ワイヤ40が接続される領域外において、配線層30がA1パッド20に電気的に接続している。つまり、A1パッド20は、A1ワイヤ40が接続すべき領域であるボンディング領域28と、Au層34が接続されている配線接続部26と、を有しており、配線接続部26はボンディング領域28を避けて設けられている。このように、A1ワイヤ40をA1パッド20に接続しているため、A1ワイヤ40とA1パッド20とでは金属間反応は生じない。また、A1パッド20と配線層30とは、A1ワイヤ40が接続されるボンディング領域28以外で接続している。よって、図1の比較例のように、A1ワイヤ40のボンディングにより、A1パッド70と配線層30とが反応することを抑制できる。このように、A1パッド20上にA1ワイヤ40を形成することによる、A1パッド20と配線層30との反応を抑制することができる。

20

#### 【0023】

また、パッド20の配線接続部26とAu層34(Au配線層)との間にバリア層32が設けられている。これにより、A1パッド20と配線層30とが接触している領域におけるA1パッド20と配線層30との反応を抑制することができる。バリア層32はTiN、TiWN等例示した材料以外にも、AlとAuとの反応を抑制する材料であればよい。また、バリア層32とAu層34との間またはバリア層42の下に密着層等の別の導電層が設けられていてもよい。

30

#### 【0024】

実施例1に係る半導体装置によれば、使用上限温度は200以上とすることができる。A1パッドとAuワイヤとの接合強度はパープルプレーグにより150～200以上で劣化することが知られている。AuパッドにA1ワイヤを接合した場合も同様であると考えられる。よって、半導体装置の使用上限温度が200以上の場合、実施例1のパッド構造が有効である。なお、半導体装置の使用上限温度は、半導体装置を動作させる際、信頼性を保証される温度であり半導体装置ごとに定められた温度である。

#### 【0025】

また、AlとAuとの接触部に不純物が存在するとAlとAuとによる金属間化合物の生成が加速すると考えられている。半導体チップを樹脂封止する場合、封止樹脂のガラス転位温度は一般的に150～200である。ガラス転位温度を越えると封止樹脂の熱膨張係数が増加する。よって、150～200以上では樹脂と半導体チップとの間に隙間が生じる。この隙間を介し侵入した酸素が封止樹脂を酸化し、酸化物の分解生成物がAlとAuの接合部に不純物として供給される。以上により、樹脂封止された半導体装置においては、使用上限温度が200以上の場合、特にAlとAuの反応が起こりやすい。よって、実施例1のパッド構造が特に有効である。

40

#### 【0026】

さらに、高電力用途の半導体装置においては、供給される電流が大きく発热量が大きいため、使用環境温度は実質的に200以上となる。よって、高電力用途の半導体装置の場合、実施例1に係る構成を用いることが好ましい。

50

**【0027】**

A1ワイヤ40の太さは100μm以上であることが好ましい。高電力用途の半導体装置に用いられるA1ワイヤは、大電流を流すため太線ワイヤとよばれ、100μm以上500μm以下の太さを有している。高出力用途の半導体装置以外に用いられるA1ワイヤの太さは50μm以下であり、太線ワイヤとはその用途が異なっている。A1ワイヤ40が太い場合は、ワイヤボンディングする際、A1パッド20に加わる圧力が大きくなる。よって、太線ワイヤを用いる場合バリア層32が破壊され易く、実施例1に係るパッド構造を用いることが好ましい。なお、例えば、太さ25μmのAuワイヤをAuパッド上にボンディングする場合の荷重は0.5N程度であるが、太さ250μmのA1ワイヤをA1パッド上にボンディングする場合の荷重は5N程度である。このように、ワイヤの種類と太さが異なることにより1桁大きい圧力がパッドに加わる。10

**【0028】**

コンバータ、インバータまたはスイッチングレギュレータのスイッチに用いる高出力用途の半導体装置は、印加される電圧の2.5倍の耐圧が要求される。よって、日本における100Vの交流に用いる場合は、耐圧は250V以上が求められる。さらに、各国に使用するため240Vの交流にも用いられる場合は、600V以上の耐圧が求められる。よって、高出力用途の半導体装置とは、例えば、耐圧が250V以上であり、好ましくは600V以上である。

**【0029】**

高出力用途の半導体装置において求められる耐圧は、FETの場合はドレイン耐圧である。バイポーラトランジスタまたは（絶縁ゲートバイポーラトランジスタ）の場合はコレクタ耐圧である。20

**【0030】**

実施例1は、化合物半導体層12として、GaN系半導体層の例であったが、GaAs系半導体層であってもよい。GaAsを用いた半導体装置においても、Au配線層が一般的に用いられており、A1ワイヤをワイヤボンディングする場合は、実施例1に係るパッド構造を適用することが好ましい。このように、化合物半導体層12はII-V族化合物半導体層であることが好ましい。

**【0031】**

GaN系半導体層を用いる場合、ソース電極50及びドレイン電極52は上からA1/Ta（タンタル）、A1/Pd（パラジウム）/Ta、またはMo（モリブデン）/Taを用いることができる。ゲート電極54としては、上から（Au、Cu（銅）またはA1）/TiWN、（Au、CuまたはA1）/（TiWNまたはPd）/（Ni、TiまたはIr（イリジウム））を用いることができる。化合物半導体層上に形成される電極は、特にこれらに限られないが、いずれかの電極がAuを含む場合、Au配線層を用いることが多い。よって、化合物半導体層上に形成された電極はAuを含むことが好ましい。30

**【実施例2】****【0032】**

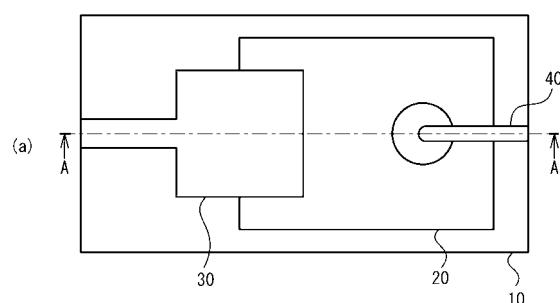

図4は、実施例2のパッド構造を示す図である。図4を参照に、実施例2においては、A1パッド20上の配線層30の端部（ボンディング領域28と配線接続部26との間）において、配線層30がA1パッド20から離間している。その他の構成は実施例1の図3（b）と同じであり説明を省略する。実施例2のように、配線層30の端部において、配線層30はA1パッド20から離間していてもよい。40

**【実施例3】****【0033】**

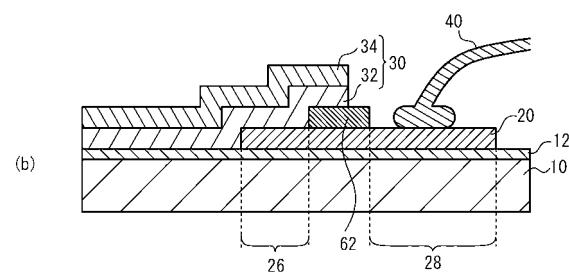

図5（a）及び図5（b）は、実施例3のパッド構造を示す図である。図5（a）及び図5（b）を参照に、実施例3においては、例えば酸化シリコンまたは窒化シリコンからなる第1絶縁層62が、A1パッド20上の配線層30の端部（ボンディング領域28と配線接続部26との間）において、配線層30とA1パッド20との間に設けられている。その他の構成は実施例1の図3（a）及び図3（b）と同じであり説明を省略する。実50

施例 3 によれば、A 1 パッド 2 0 上の配線層 3 0 の端部において、製造工程中に A u と A 1 とが接触することを抑制することができる。さらに、半導体装置の動作に伴うイオンマイグレーション等により A u または A 1 がバリア層 3 2 表面を移動し、A u と A 1 とが反応することを抑制することができる。

**【実施例 4】**

**【0 0 3 4】**

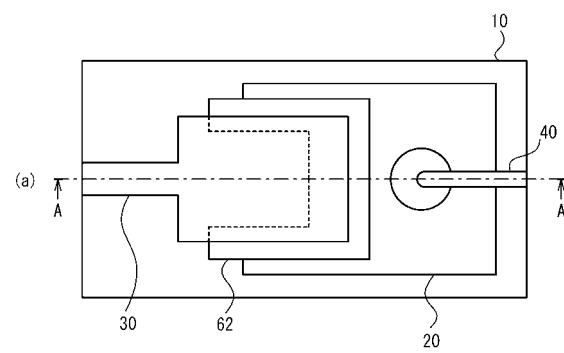

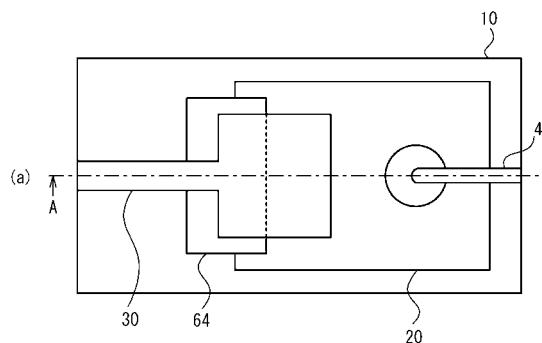

図 6 ( a ) 及び図 6 ( b ) は、実施例 4 のパッド構造を示す図である。図 6 ( a ) 及び図 6 ( b ) を参照に、実施例 4 においては、A 1 パッド 2 0 の端部において、配線層 3 0 と A 1 パッド 2 0 との間に第 2 絶縁層 6 4 が設けられている。その他の構成は実施例 1 の図 3 ( a ) 及び図 3 ( b ) と同じであり説明を省略する。配線層 3 0 が A 1 パッド 2 0 上に乗り上げる段差においては、バリア層 3 2 の被覆性劣化等により、A u と A 1 が反応することが起こりうる。実施例 4 によれば、A 1 パッド 2 0 の端部における A u と A 1 が反応を抑制することができる。10

**【実施例 5】**

**【0 0 3 5】**

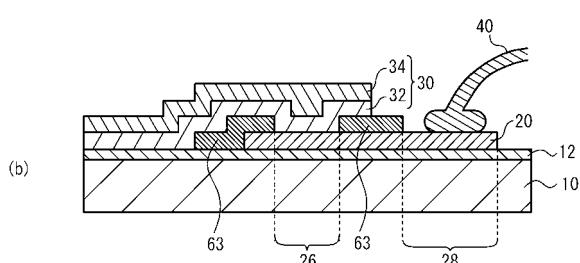

図 7 ( a ) 及び図 7 ( b ) は、実施例 5 のパッド構造を示す図である。図 7 ( a ) 及び図 7 ( b ) を参照に、実施例 5 においては、絶縁層 6 3 が、実施例 3 の第 1 絶縁層と実施例 4 の第 2 絶縁層とを有し、環状をなしている。その他の構成は実施例 1 の図 3 ( a ) 及び図 3 ( b ) と同じであり説明を省略する。実施例 5 によれば、A 1 パッド 2 0 上の配線層 3 0 の端部及び A 1 パッド 2 0 端部の配線層 3 0 の乗り上げ部分における A u と A 1 との反応を抑制することができる。20

**【実施例 6】**

**【0 0 3 6】**

図 8 は、実施例 6 のパッド構造を示す図である。図 8 を参照に、実施例 6 においては、A 1 パッド 2 0 は A 1 からなる第 1 層 2 2 と第 1 層 2 2 上の A 1 からなる第 2 層 2 4 とかなる。配線層 3 0 は第 1 層 2 2 上に延在することにより A 1 パッド 2 0 に接続される。A 1 ワイヤ 4 0 は第 2 層 2 4 上に接続されている。その他の構成は実施例 1 の図 3 ( b ) と同じであり説明を省略する。A 1 パッド 2 0 の膜厚は A 1 ワイヤ 4 0 と A 1 パッド 2 0 との密着強度を保つため、2 μm 以上あることが好ましい。一方、A 1 パッド 2 0 の膜厚が大きいと、実施例 4 において説明したように、A 1 パッド 2 0 端部の配線層 3 0 の乗り上げ部分において、A u と A 1 とが反応しやすい。実施例 6 によれば、第 1 層 2 2 の膜厚を小さくすることにより、A 1 パッド 2 0 端部の配線層 3 0 の乗り上げ部分の段差を小さくすることができる。これにより、A 1 と A u との反応を抑制することができる。一方、第 2 層 2 4 を厚くすることにより、A 1 ワイヤ 4 0 と A 1 パッド 2 0 との密着強度を保つことができる。30

**【実施例 7】**

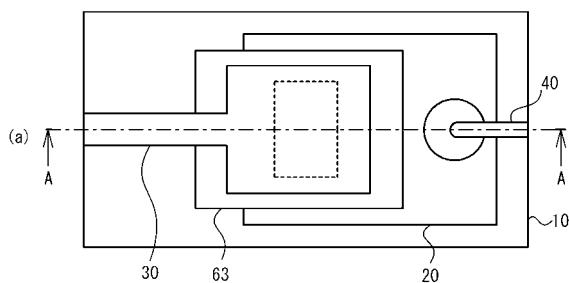

**【0 0 3 7】**

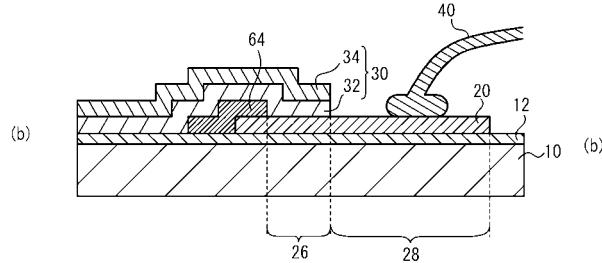

図 9 ( a ) 及び図 9 ( b ) は、実施例 7 のパッド構造を示す図である。図 9 ( a ) 及び図 9 ( b ) を参照に、実施例 7 においては、第 2 層 2 4 が配線層 3 0 上に第 3 絶縁層 6 6 を介し延在している。その他の構成は実施例 6 の図 8 ( a ) 及び図 8 ( b ) と同じであり、説明を省略する。実施例 7 によれば、配線層 3 0 の端部を第 3 絶縁層 6 6 及び第 2 層 2 4 が覆っているため、A 1 ワイヤ 4 0 が配線層 3 0 に接触することを抑制することができる。40

**【実施例 8】**

**【0 0 3 8】**

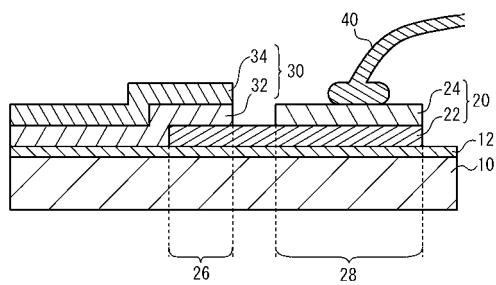

図 10 ( a ) 及び図 10 ( b ) は、実施例 8 のパッド構造を示す図である。図 10 ( a ) 及び図 10 ( b ) を参照に、実施例 8 においては、第 1 絶縁層 6 2 が、第 1 層 2 2 上の配線層 3 0 の端部において、配線層 3 0 と第 1 層 2 2 との間に設けられている。その他の構成は実施例 7 の図 9 ( a ) 及び図 9 ( b ) と同じであり説明を省略する。実施例 8 によれば、第 1 絶縁層 6 2 により、第 1 層 2 2 上の配線層 3 0 の端部において A u と A 1 が反50

応することを抑制することができる。また、第3絶縁層66及び第2層24によりA1ワイヤ40が配線層30に接触することを抑制することができる。

【実施例9】

【0039】

図11は、実施例9のパッド構造を示す図である。図11を参照に、実施例9においては、A1パッド20は配線層30上に延在することにより配線層30と接続している。配線層30はAu層34上にバリア層32が形成されている。つまり、Au層34とA1パッド20との間にバリア層32が設けられている。その他の構成は実施例1の図3(b)と同じであり説明を省略する。

【実施例10】

10

【0040】

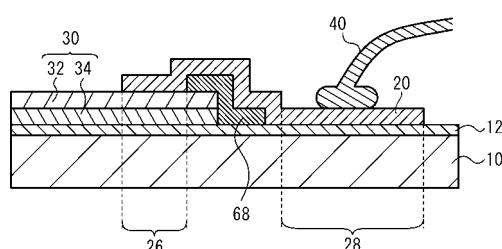

図12は、実施例10のパッド構造を示す図である。図12を参照に、実施例10においては、配線層30の端部において、配線層30とA1パッド20との間に第4絶縁層68が設けられている。その他の構成は実施例9の図11と同じであり説明を省略する。実施例10によれば、第4絶縁層68により、配線層30の端部におけるA1とAuの反応を抑制することができる。

【0041】

GaNを用いたFETでは、ソース電極50及びドレイン電極52はA1/Ti等のA1を含む電極が一般的に用いられる。実施例1から実施例8によれば、このようなA1を含む電極を形成する際にA1パッド20を同時に形成することができる。また、A1を含む電極を用いない場合は、A1パッド20を形成した後に配線層30を形成してもよいが、実施例9及び実施例10のように、配線層30を形成した後にA1パッド20を形成することができる。このように、A1を含む電極を用いる場合及び、用いない場合のいずれの場合も、実施例1から実施例8並びに実施例9及び実施例10のいずれの構造も選択することができる。

20

【0042】

以上、発明の好ましい実施例について詳述したが、本発明は係る特定の実施例に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

【図面の簡単な説明】

30

【0043】

【図1】図1は比較例のパッド構造の断面図である。

【図2】図2実施例1の半導体チップの平面図である。

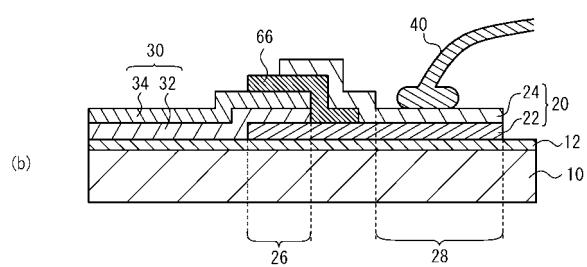

【図3】図3(a)は、実施例1のパッド構造の平面図、図3(b)は図3(a)のA-A断面図である。

【図4】図4は実施例2のパッド構造の断面図である。

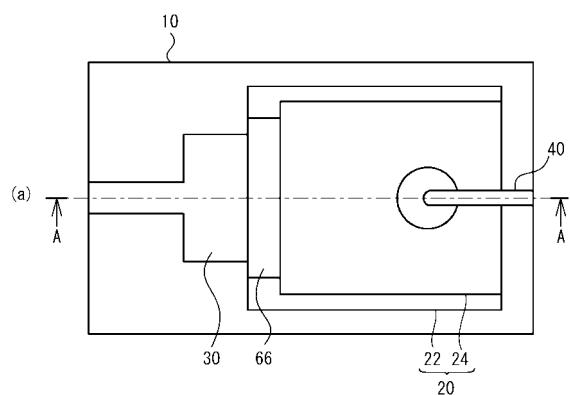

【図5】図5(a)は、実施例3のパッド構造の平面図、図5(b)は図5(a)のA-A断面図である。

【図6】図6(a)は、実施例4のパッド構造の平面図、図6(b)は図6(a)のA-A断面図である。

40

【図7】図7(a)は、実施例5のパッド構造の平面図、図7(b)は図7(a)のA-A断面図である。

【図8】図8は実施例6のパッド構造の断面図である。

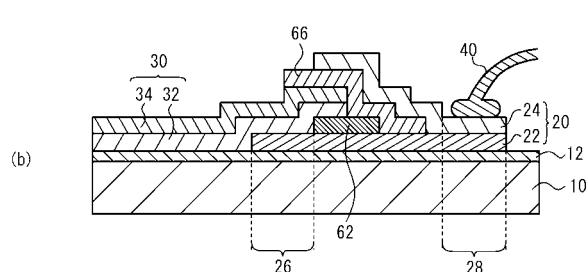

【図9】図9(a)は、実施例7のパッド構造の平面図、図9(b)は図9(a)のA-A断面図である。

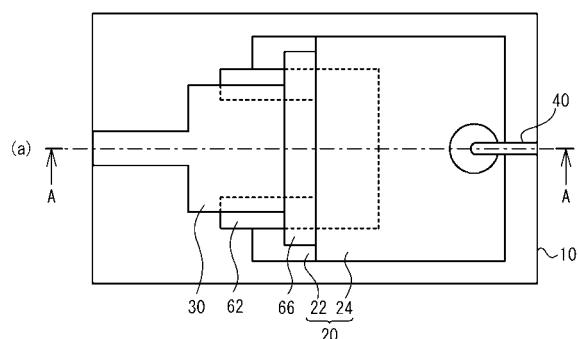

【図10】図10(a)は、実施例8のパッド構造の平面図、図10(b)は図10(a)のA-A断面図である。

【図11】図11は実施例9のパッド構造の断面図である。

【図12】図12は実施例10のパッド構造の断面図である。

【符号の説明】

50

## 【0044】

|     |         |

|-----|---------|

| 1 0 | 基板      |

| 1 2 | 化合物半導体層 |

| 2 0 | A 1 パッド |

| 2 2 | 第 1 層   |

| 2 4 | 第 2 層   |

| 3 0 | 配線層     |

| 3 2 | バリア層    |

| 3 4 | A u 層   |

| 4 0 | A 1 ワイヤ |

| 6 2 | 第 1 絶縁層 |

| 6 3 | 絶縁層     |

| 6 4 | 第 2 絶縁層 |

| 6 6 | 第 3 絶縁層 |

| 6 8 | 第 4 絶縁層 |

10

【図 1】

【図 2】

【図 3】

【図4】

【図5】

【図6】

【図7】

【図 8】

【図 9】

【図 10】

【図 11】

【図 12】

---

フロントページの続き

(56)参考文献 特開昭61-220462(JP,A)

特開平04-102358(JP,A)

特開昭59-210656(JP,A)

特開2002-118121(JP,A)

特開2002-231748(JP,A)

特開平10-189649(JP,A)

特表2003-514380(JP,A)

特開2006-245379(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L21/3205

H01L21/3213

H01L21/768

H01L23/52 - H01L23/522

H01L21/60