(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6249868号

(P6249868)

(45) 発行日 平成29年12月20日(2017.12.20)

(24) 登録日 平成29年12月1日(2017.12.1)

(51) Int.Cl.

F 1

H01L 21/338 (2006.01)

H01L 29/80

H

H01L 29/778 (2006.01)

H01L 29/812 (2006.01)

請求項の数 7 (全 12 頁)

(21) 出願番号 特願2014-86397 (P2014-86397)

(22) 出願日 平成26年4月18日 (2014.4.18)

(65) 公開番号 特開2015-207624 (P2015-207624A)

(43) 公開日 平成27年11月19日 (2015.11.19)

審査請求日 平成28年11月11日 (2016.11.11)

(73) 特許権者 000106276

サンケン電気株式会社

埼玉県新座市北野3丁目6番3号

(73) 特許権者 000190149

信越半導体株式会社

東京都千代田区大手町二丁目2番1号

(74) 代理人 100102532

弁理士 好宮 幹夫

(72) 発明者 佐藤 憲

埼玉県新座市北野3丁目6番3号 サンケン電気株式会社内

(72) 発明者 鹿内 洋志

埼玉県新座市北野3丁目6番3号 サンケン電気株式会社内

最終頁に続く

(54) 【発明の名称】半導体基板及び半導体素子

## (57) 【特許請求の範囲】

## 【請求項 1】

基板と、

前記基板上の窒化物系半導体からなり、炭素を含むバッファ層と、

前記バッファ層上の窒化物系半導体からなり、炭素を含む高抵抗層と、

前記高抵抗層上の窒化物系半導体からなるチャネル層と

を有する半導体基板であって、

前記高抵抗層は、

前記バッファ層よりも炭素濃度が低い第1の領域と、

前記第1の領域と前記チャネル層との間に設けられ、前記第1の領域よりも炭素濃度 10

が高い第2の領域と

を有し、

前記第1の領域が遷移金属を含み、前記第1の領域の遷移金属濃度が前記第2の領域の遷移金属濃度より高いことを特徴とする半導体基板。

## 【請求項 2】

前記第1の領域の遷移金属濃度が、 $1 \times 10^{17}$  atoms/cm<sup>3</sup>以上、 $1 \times 10^{20}$  atoms/cm<sup>3</sup>以下であることを特徴とする請求項1に記載の半導体基板。

## 【請求項 3】

前記第1の領域の遷移金属濃度が、 $1 \times 10^{18}$  atoms/cm<sup>3</sup>以上、 $1 \times 10^{21}$  atoms/cm<sup>3</sup>以下であることを特徴とする請求項2に記載の半導体基板。

## 【請求項 4】

前記第1の領域が遷移金属を含み、前記第1の領域の厚さが3nm以上、3000nm以下であることを特徴とする請求項1から請求項3のいずれか一項に記載の半導体基板。

## 【請求項 5】

前記第1の領域は、前記バッファ層と接していることを特徴とする請求項1から請求項4のいずれか一項に記載の半導体基板。

## 【請求項 6】

前記第1の領域の炭素濃度が $1 \times 10^{18}$ atoms/cm<sup>3</sup>未満であり、前記第2の領域の炭素濃度が $1 \times 10^{18}$ atoms/cm<sup>3</sup>以上、 $1 \times 10^{19}$ atoms/cm<sup>3</sup>以下であることを特徴とする請求項1から請求項5のいずれか一項に記載の半導体基板

10

。

## 【請求項 7】

請求項1から請求項6のいずれか一項に記載の半導体基板を用いて作製された半導体素子であって、前記チャネル層上に電極が設けられているものであることを特徴とする半導体素子。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、半導体基板及びこの半導体基板を用いて作製された半導体素子に関する。

## 【背景技術】

## 【0002】

窒化物半導体を用いた半導体基板は、高周波かつ高出力で動作するパワー素子等に用いられている。特に、マイクロ波、準ミリ波、ミリ波等の高周波帯域において増幅を行うのに適したものとして、例えば高電子移動度トランジスタ(High Electron Mobility Transistor: HEMT)等が知られている。

## 【0003】

窒化物半導体を用いた半導体基板として、Si基板上に、バッファ層、GaN層、AlGaNからなるバリア層が順次積層された半導体基板が知られている。

GaN層のうち下部の層(高抵抗層)は、縦方向及び横方向の電気抵抗を高めることで、トランジスタのオフ特性向上、縦方向リーキの抑制により高耐圧化が可能となる。そのためGaN層に炭素をドープし、GaN結晶中に深い準位を形成し、n型の伝導を抑制させる。

20

一方、GaN層のうち上部の層は、チャネル層として機能し、キャリアをトラップさせる準位が形成されると電流コラプス(出力電流特性の再現性が劣化する現象)の要因となりうるため、炭素等の濃度を十分低下させる必要がある(特許文献1-3参照)。

## 【0004】

また、特許文献4には、GaN層にFeを添加することで高抵抗化を図ることが開示され、Feのエネルギー準位を安定化させるために炭素をさらに添加することも開示されている。

また、特許文献5には、寄生容量を低減させるとともに高耐圧化させるために、GaN層にFeを添加することが開示されている。

30

## 【先行技術文献】

## 【特許文献】

## 【0005】

【特許文献1】特許第5064824号公報

【特許文献2】特開2006-332367号公報

【特許文献3】特開2013-070053号公報

【特許文献4】特開2012-033646号公報

【特許文献5】特開2010-123725号公報

## 【発明の概要】

40

50

## 【発明が解決しようとする課題】

## 【0006】

上述のように、高抵抗層は炭素濃度を高くすることで、デバイスの縦方向（厚み方向）リーケ電流を抑制し、トランジスタのオフ特性を向上させるために用いているが、炭素濃度の高い高抵抗層の結晶性について本発明者らは調べた。

## 【0007】

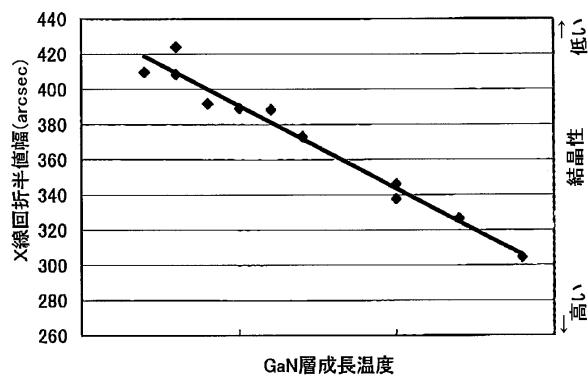

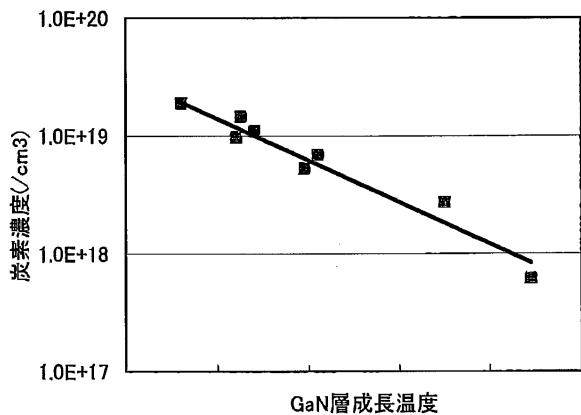

図9に高抵抗層の結晶性の成長温度依存性を示し、図10に高抵抗層の炭素濃度の成長温度依存性を示す。

図9-10からわかるように、成長温度を下げると高抵抗層の炭素濃度を増加させることができるが、逆に高抵抗層の結晶性が低くなっている。

10

## 【0008】

高抵抗層の結晶性が低くなると、リーケ電流が増加するとともに、その上に形成されるチャネル層の結晶性も低くなることによって、チャネル層における電子移動度の低下や電流コラプスを引き起こすという問題がある。

## 【0009】

本発明は、上記問題点に鑑みてなされたものであって、高抵抗層の高抵抗を維持しながら結晶性を高くすることでリーケ電流を低減させるとともに、その上に形成されるチャネル層の結晶性も高くすることでチャネル層における電子移動度の低下や電流コラプスの発生を抑制できる半導体基板及び半導体素子を提供することを目的とする。

## 【課題を解決するための手段】

20

## 【0010】

上記目的を達成するために、本発明は、基板と、前記基板上の窒化物系半導体からなり、炭素を含むバッファ層と、前記バッファ層上の窒化物系半導体からなり、炭素を含む高抵抗層と、前記高抵抗層上の窒化物系半導体からなるチャネル層とを有する半導体基板であって、前記高抵抗層は、前記バッファ層よりも炭素濃度が低い第1の領域と、前記第1の領域と前記チャネル層との間に設けられ、前記第1の領域よりも炭素濃度が高い第2の領域とを有することを特徴とする半導体基板を提供する。

## 【0011】

このように、高抵抗層が、バッファ層よりも炭素濃度が低い第1の領域と、第1の領域とチャネル層との間にあって、第1の領域よりも炭素濃度が高い第2の領域とを有することで、高抵抗層の高抵抗を維持しながら結晶性を高くすることができ、それによってリーケ電流を低減させるとともに、その上に形成されるチャネル層の結晶性も高くすることでチャネル層における電子移動度の低下や電流コラプスの発生を抑制できる。

30

## 【0012】

このとき、前記第1の領域が遷移金属を含み、前記第1の領域の遷移金属濃度が前記第2の領域の遷移金属濃度より高いことが好ましい。

第1の領域が第2の領域の遷移金属濃度より高い濃度で遷移金属を含むことで、炭素濃度の低い第1の領域において縦方向リーケ電流の増加を抑制することができるとともに、第1の領域の結晶性をさらに高くすることができ、これにより第1の領域より上に形成される窒化物系半導体の結晶性をさらに改善することができる。

40

## 【0013】

このとき、前記第1の領域の遷移金属濃度が、 $1 \times 10^{17}$  atoms/cm<sup>3</sup>以上、 $1 \times 10^{20}$  atoms/cm<sup>3</sup>以下、特に $1 \times 10^{18}$  atoms/cm<sup>3</sup>以上、 $1 \times 10^{19}$  atoms/cm<sup>3</sup>以下であることが好ましい。

第1の領域の遷移金属濃度がこのような濃度範囲であれば、第1の領域における縦方向リーケ電流の増加を確実に抑制することができ、第1の領域より上に形成される窒化物系半導体の結晶性を確実に改善することができる。

## 【0014】

このとき、前記第1の領域が遷移金属を含み、前記第1の領域の厚さが3nm以上、300nm以下であることが好ましい。

50

第1の領域が遷移金属を含む場合に、第1の領域の厚さがこのような範囲であれば、第1の領域の高抵抗を維持しながら、第1の領域より上に形成される窒化物系半導体の結晶性を改善することができる。

【0015】

このとき、前記第1の領域が遷移金属を含まず、前記第1の領域の厚さが3nm以上、500nm以下であることが好ましい。

第1の領域が遷移金属を含まない場合に、第1の領域の厚さがこのような範囲であれば、縦方向リーク電流の抑制を維持しながら、第1の領域より上に形成される窒化物系半導体の結晶性を改善することができる。

【0016】

このとき、前記第1の領域は、前記バッファ層と接していることが好ましい。

このように結晶性の高い第1の領域をよりバッファ層側に（すなわち、より基板側に）設けることにより、第1の領域より上に形成される窒化物系半導体の結晶性をより効果的に改善することができる。

【0017】

このとき、前記第1の領域の炭素濃度が $1 \times 10^{18}$ atoms/cm<sup>3</sup>未満であり、前記第2の領域の炭素濃度が $1 \times 10^{18}$ atoms/cm<sup>3</sup>以上、 $1 \times 10^{19}$ atoms/cm<sup>3</sup>以下であることが好ましい。

第1の領域及び第2の領域の炭素濃度として、このような濃度範囲を好適に用いることができる。

【0018】

また、本発明は、上記の半導体基板を用いて作製された半導体素子であって、前記チャネル層上に電極が設けられているものであることを特徴とする半導体素子を提供する。

【0019】

このような本発明の半導体基板を用いて作製された半導体素子であれば、高抵抗層の高抵抗を維持しながら結晶性を高くすることができ、それによってリーク電流を低減させるとともに、その上に形成されるチャネル層の結晶性も高くすることでチャネル層における電子移動度の低下や電流コラプスの発生を抑制できる。

【発明の効果】

【0020】

以上のように、本発明によれば、高抵抗層の高抵抗を維持しながら結晶性を高くすることができ、それによってリーク電流を低減させるとともに、その上に形成されるチャネル層の結晶性も高くすることでチャネル層における電子移動度の低下や電流コラプスの発生を抑制できる。

【図面の簡単な説明】

【0021】

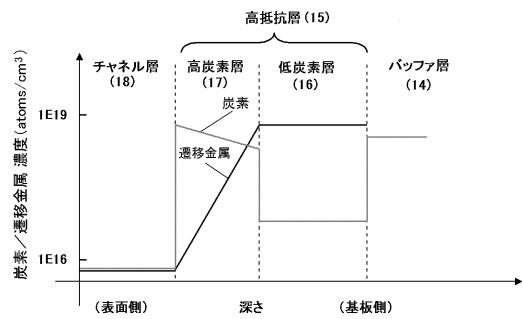

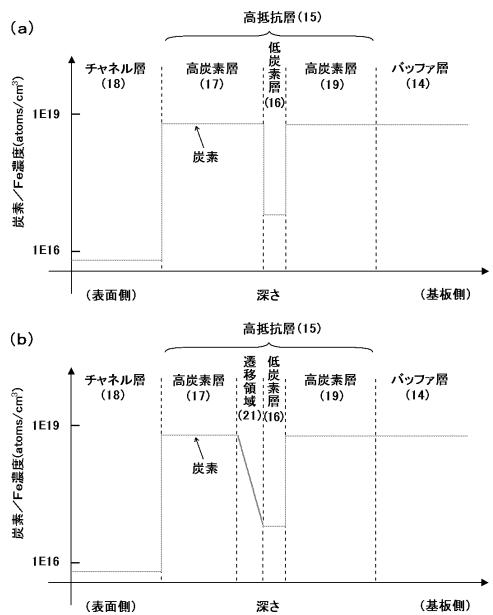

【図1】本発明の実施態様の一例を示す半導体基板の深さ方向の濃度分布を示す図である。

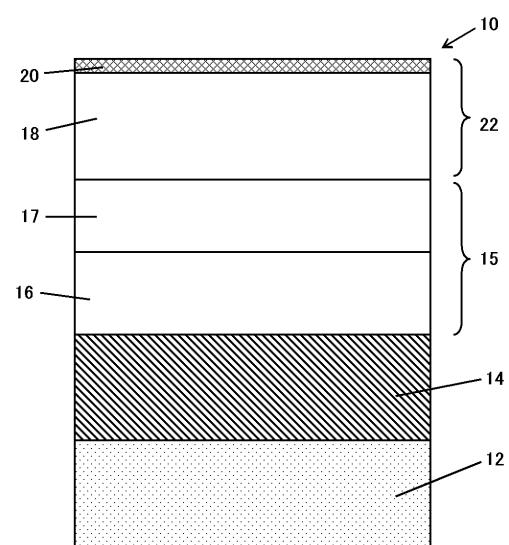

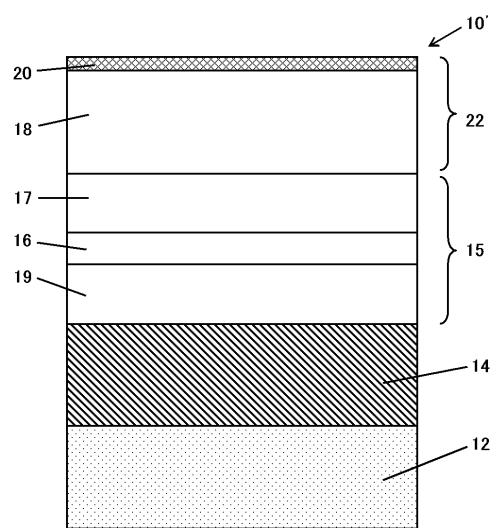

【図2】本発明の実施態様の一例を示す半導体基板の断面図である。

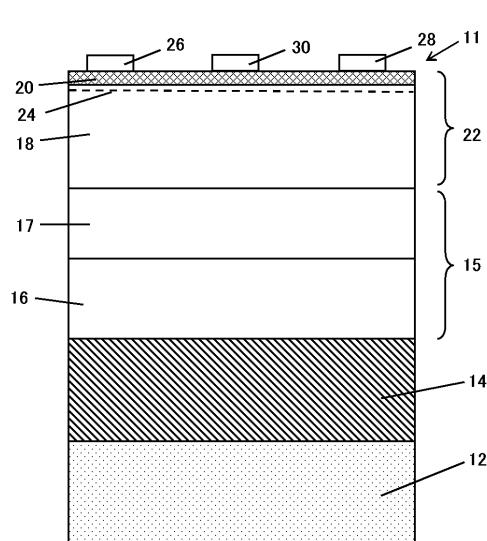

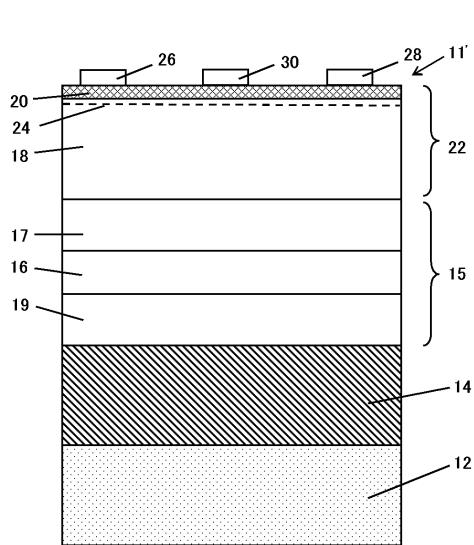

【図3】本発明の実施態様の一例を示す半導体素子の断面図である。

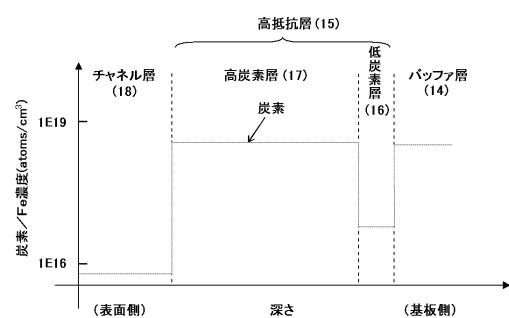

【図4】実施例2の半導体基板の深さ方向の不純物濃度分布を示す図である。

【図5】実施例5の半導体基板の深さ方向の不純物濃度分布を示す図である。

【図6】実施例5の半導体基板の断面図である。

【図7】実施例5の半導体素子の断面図である。

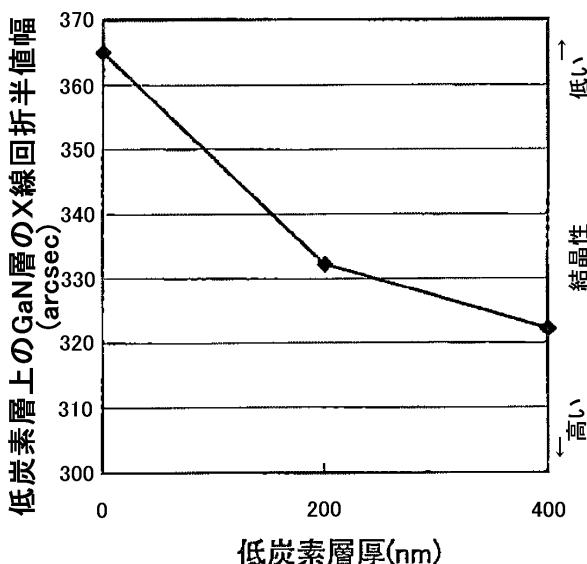

【図8】低炭素層上のGaN層の結晶性の低炭素層の膜厚依存性を示す図である。

【図9】高抵抗層の結晶性の成長温度依存性を示す図である。

【図10】高抵抗層の炭素濃度の成長温度依存性を示す図である

【発明を実施するための形態】

【0022】

前述のように、高抵抗層は炭素濃度を高くすることで、デバイスの縦方向リーク電流を

抑制し、トランジスタのオフ特性を向上させるために用いているが、炭素濃度を高くすると高抵抗層の結晶性が低くなる。高抵抗層の結晶性が低くなると、リーク電流が増加するとともに、その上に形成されるチャネル層の結晶性も低くなることによって、チャネル層における電子移動度の低下や電流コラプスを引き起こすという問題があった。

【0023】

そこで、本発明者らは、高抵抗層の高抵抗を維持しながら結晶性を高くすることでリーク電流を低減させるとともに、その上に形成されるチャネル層の結晶性も高くすることでチャネル層における電子移動度の低下や電流コラプスの発生を抑制できる半導体基板について鋭意検討を重ねた。その結果、高抵抗層中に、バッファ層よりも炭素濃度が低い第1の領域と、第1の領域とチャネル層との間に設けられ第1の領域よりも炭素濃度が高い第2の領域とを設けることで、高抵抗層の高抵抗を維持しながら結晶性を高くすることができ、それによってリーク電流を低減させるとともに、その上に形成されるチャネル層の結晶性も高くすることでチャネル層における電子移動度の低下や電流コラプスの発生を抑制できることを見出し、本発明をなすに至った。

【0024】

以下、本発明について、実施態様の一例として、図を参照しながら詳細に説明するが、本発明はこれに限定されるものではない。

【0025】

まず、本発明の実施態様の一例を示す半導体基板について、図1-2を参照しながら説明する。

図1は本発明の実施態様の一例を示す半導体基板の深さ方向の濃度分布を示した図であり、図2は本発明の半導体基板の断面図である。

【0026】

図2に示す本発明の実施態様の一例を示す半導体基板10は、基板12と、基板12上に設けられたバッファ層14と、バッファ層14上に設けられた窒化物系半導体（例えば、GaN）からなり、遷移金属及び炭素を不純物として含む高抵抗層15と、高抵抗層15上に設けられた能動層22を有している。

ここで、基板12は、例えば、Si又はSiCからなる基板である。また、バッファ層14は、例えば、窒化物系半導体からなる第一の層と、第一の層と組成の異なる窒化物系半導体からなる第二の層とが繰り返し積層された積層体で構成されるバッファ層である。

第一の層は例えば、 $Al_y Ga_{1-y} N$ からなり、第二の層は例えば、 $Al_x Ga_{1-x} N$  ( $0 < x < 1$ ) からなる。

具体的には、第一の層はAlNとすることことができ、第二の層はGaNとすることができる。

【0027】

能動層22は、窒化物系半導体からなるチャネル層18と、チャネル層18上に設けられた窒化物系半導体からなるバリア層20とを有している。チャネル層18は例えば、GaNからなり、バリア層20は例えば、AlGaNからなる。

【0028】

高抵抗層15は、炭素濃度がバッファ層14より低く遷移金属の濃度が一定である低炭素層（第1の領域）16と、低炭素層16とチャネル層18との間に設けられ炭素濃度が低炭素層16より高く遷移金属が低炭素層16側からチャネル層18側に向かって減少している高炭素層（第2の領域）17とを含んでいる。

なお、図1において、高抵抗層15が遷移金属を含んでいる場合を示しているが、高抵抗層15は遷移金属を含んでいなくてもよい。

高抵抗層15が、バッファ層14よりも炭素濃度が低い低炭素層16と、低炭素層16とチャネル層18との間に設けられ低炭素層16よりも炭素濃度が高い高炭素層17とを有することで、高抵抗層15の高抵抗を維持しながら結晶性を高くすることができ、それによってリーク電流を低減させるとともに、その上に形成されるチャネル層18の結晶性も高くすることでチャネル層における電子移動度の低下や電流コラプスの発生を抑制でき

10

20

30

40

50

る。

【0029】

半導体基板10において、遷移金属をFeとすることができます。

このように、遷移金属としてFeを好適に用いることができる。なお、遷移金属としてSc、Ti、V、Cr、Mn、Co、Ni、Cu、Zn等を用いることもできる。

【0030】

炭素の添加は、窒化物系半導体層をMOVPE(有機金属気相成長)法によって成長させるとときに、原料ガス(TMГ(トリメチルガリウム)等)に含まれる炭素が膜中に取り込まれることによって行われるものであるが、プロパン等のドーピングガスによって行うこともできる。

10

【0031】

半導体基板10において、低炭素層16が遷移金属を含む場合、低炭素層16の遷移金属濃度が高炭素層17の遷移金属濃度より高いことが好ましい。

低炭素層16が高炭素層17より高い濃度で遷移金属を含むことで、炭素濃度の低い低炭素層16において縦方向リーケ電流の増加を抑制することができるとともに、低炭素層16の結晶性をさらに高くすることができ、これにより第1の領域より上に形成される窒化物系半導体の結晶性をさらに改善することができる。

【0032】

低炭素層16の遷移金属濃度が、 $1 \times 10^{17}$  atoms/cm<sup>3</sup>以上、 $1 \times 10^{20}$  atoms/cm<sup>3</sup>以下、特に $1 \times 10^{18}$  atoms/cm<sup>3</sup>以上、 $1 \times 10^{19}$  atoms/cm<sup>3</sup>以下であることが好ましい。

20

低炭素層16の遷移金属濃度がこのような濃度範囲であれば、低炭素層16における縦方向リーケ電流の増加を確実に抑制することができ、低炭素層16より上に形成される窒化物系半導体の結晶性を確実に改善することができる。

【0033】

半導体基板10において、低炭素層16が遷移金属を含む場合、低炭素層16の厚さが3nm以上、3000nm以下であることが好ましく、5nm以上、2000nm以下であることが特に好ましい。

低炭素層16が遷移金属を含む場合に、低炭素層16の厚さがこのような範囲であれば、低炭素層16の高抵抗を維持しながら、低炭素層16より上に形成される窒化物系半導体の結晶性を改善することができる。

30

【0034】

半導体基板10において、低炭素層16が遷移金属を含まない場合、低炭素層16の厚さが3nm以上、500nm以下であることが好ましく、5nm以上、200nm以下であることが特に好ましい。

低炭素層16が遷移金属を含まない場合に、低炭素層16の厚さがこのような薄い範囲であれば、縦方向リーケ電流の抑制を維持しながら、低炭素層16より上に形成される窒化物系半導体の結晶性を改善することができる。

【0035】

半導体基板10において、低炭素層16は、バッファ層14と接していることが好ましい。

40

このように結晶性の高い低炭素層16をよりバッファ層14側(すなわち、より基板12側に)設けることにより、低炭素層16より上に形成される窒化物系半導体の結晶性をより効果的に改善することができる。

【0036】

ここで、低炭素層16の炭素濃度が $1 \times 10^{18}$  atoms/cm<sup>3</sup>未満であり、前記第2の領域の炭素濃度が $1 \times 10^{18}$  atoms/cm<sup>3</sup>以上、 $1 \times 10^{19}$  atoms/cm<sup>3</sup>以下であることが好ましい。

第1の領域及び第2の領域の炭素濃度として、このような濃度範囲を好適に用いることができる。

50

## 【0037】

次に、本発明の実施態様の一例を示す半導体素子について、図3を参照しながら説明する。

図3は本発明の実施態様の一例を示す半導体素子の断面図である。

半導体素子11は、本発明の半導体基板10を用いて作製されたものであり、能動層22上に設けられた第一電極26、第二電極28、制御電極30を有している。

半導体素子11において、第一電極26及び第二電極28は、第一電極26から、チャネル層18内に形成された二次元電子ガス層24を介して、第二電極28に電流が流れるように配置されている。

第一電極26と第二電極28との間に流れる電流は、制御電極30に印可される電位によってコントロールすることができる。 10

## 【0038】

半導体素子11は、本発明の実施態様の一例を示す半導体基板10を用いて作製されたものであり、高抵抗層の高抵抗を維持しながら結晶性を高くすることができます、それによってリーク電流を低減させるとともに、その上に形成されるチャネル層の結晶性も高くすることでチャネル層における電子移動度の低下や電流コラプスの発生を抑制できる。

## 【実施例】

## 【0039】

以下、実施例及び比較例を示して本発明をより具体的に説明するが、本発明はこれらに限定されるものではない。 20

## 【0040】

## (実施例1)

図1に示す深さ方向の濃度分布を有する図2に示すような半導体基板を作製した。ただし、遷移金属としてFeを用い、低炭素層16における炭素濃度は、 $5 \times 10^{17}$  atoms / cm<sup>3</sup>とし、高炭素層17における炭素濃度は $2 \times 10^{18}$  atoms / cm<sup>3</sup>とし、低炭素層16におけるFeの濃度は、 $3 \times 10^{18}$  atoms / cm<sup>3</sup>とした。また、低炭素層16の厚さは500nmとし、高炭素層17の厚さは1600nmとした。

作製された半導体基板を用いて図3に示すような半導体素子を作製した。

## 【0041】

## (実施例2)

図4に示す深さ方向の濃度分布を有する図2に示すような半導体基板を作製した。ただし、高抵抗層15には遷移金属を添加せず、低炭素層16における炭素濃度は、 $3 \times 10^{17}$  atoms / cm<sup>3</sup>とし、高炭素層17における炭素濃度は $2 \times 10^{18}$  atoms / cm<sup>3</sup>とした。また、低炭素層16の厚さは100nmとし、高炭素層17の厚さは1600nmとした。

作製された半導体基板を用いて図3に示すような半導体素子を作製した。 30

## 【0042】

## (実施例3)

実施例2と同様にして半導体基板を作製した。ただし、低炭素層16の厚さは200nmとし、高炭素層17の厚さは1500nmとした。 40

作製した半導体基板において、低炭素層16上の0002方向のGaN層（高炭素層17を含む）の結晶性をX線回折を用いて測定した。その結果を図8に示す。

作製された半導体基板を用いて図3に示すような半導体素子を作製した。

## 【0043】

## (実施例4)

実施例2と同様にして半導体基板を作製した。ただし、低炭素層16の厚さは400nmとし、高炭素層17の厚さは1300nmとした。

作製した半導体基板において、低炭素層16上の0002方向のGaN層（高炭素層17を含む）の結晶性をX線回折を用いて測定した。その結果を図8に示す。

作製された半導体基板を用いて図3に示すような半導体素子を作製した。 50

## 【0044】

## (比較例)

実施例2と同様にして半導体基板を作製した。ただし、低炭素層16は形成せずに、高炭素層17の厚さは1700nmとした。

作製した半導体基板において、高炭素層17を含む0002方向のGaN層の結晶性をX線回折を用いて測定した。その結果を図8に示す。

作製された半導体基板を用いて図3に示すような半導体素子(ただし、低炭素層16は形成されていない)を作製した。

## 【0045】

## (実施例5)

図5(a)に示す深さ方向の濃度分布を有する図6に示すような半導体基板を作製した。

図5-6に示す半導体基板10'は、高抵抗層15がさらに、炭素濃度が低炭素層16より高い高炭素層(第3の領域)19をバッファ層14と低炭素層16との間に含んでいることを除いて、図4、図2に示す半導体基板10と同様の構成となっている。ただし、高抵抗層15には遷移金属を添加せず、低炭素層16における炭素濃度は、 $3 \times 10^{17}$  atoms/cm<sup>3</sup>とし、高炭素層17における炭素濃度は $2 \times 10^{18}$  atoms/cm<sup>3</sup>とし、高炭素層19における炭素濃度は $2 \times 10^{18}$  atoms/cm<sup>3</sup>とした。また、低炭素層16の厚さは100nmとし、高炭素層17の厚さは800nmとし、高炭素層19の厚さは800nmとした。

なお、図5(b)に示すように、低炭素層16と高炭素層17との間に炭素濃度が徐々に増加する遷移領域21を設けてよい。

作製された半導体基板を用いて図7に示すような半導体素子を作製した。

図7に示す半導体素子11'は、高抵抗層15がさらに、炭素濃度が低炭素層16より高い高炭素層(第3の領域)19をバッファ層14と低炭素層16との間に含んでいることを除いて、図3の半導体素子11と同様の構成となっている。

## 【0046】

図8からわかるように、低炭素層16の膜厚が増加するとともに、低炭素層16上のGaN層の結晶性が高くなっている。すなわち、低炭素層16を形成しない比較例と比較して、低炭素層16を形成した実施例3-4の半導体基板の低炭素層16上のGaN層(高炭素層17を含む)の結晶性は高くなっている。低炭素層16の膜厚の厚い実施例4では低炭素層16の膜厚の薄い実施例3と比較して結晶性がより高くなっている。

さらに、実施例1-5の半導体素子において、比較例の半導体素子と比較して縦方向リーケ電流が減少し、チャネル層において電子移動度の低下や電流コラプスの発生が抑制されていることが確認できた。

## 【0047】

なお、本発明は、上記実施形態に限定されるものではない。上記実施形態は、例示であり、本発明の特許請求の範囲に記載された技術的思想と実質的に同一な構成を有し、同様な作用効果を奏するものは、いかなるものであっても本発明の技術的範囲に包含される。

例えば、各実施形態において、低炭素層16、高炭素層17、19の各層のいずれか1つが基板12側からチャネル18側に向かって炭素濃度が徐々に増加してもよい。

## 【符号の説明】

## 【0048】

10, 10' ... 半導体基板、 11, 11' ... 半導体素子、 12 ... 基板、

14 ... バッファ層、 15 ... 高抵抗層、 16 ... 低炭素層(第1の領域)、

17 ... 高炭素層(第2の領域)、 18 ... チャネル層、

19 ... 高炭素層(第3の領域)、 20 ... バリア層、 21 ... 遷移領域、

22 ... 能動層、 24 ... 二次元電子ガス層、 26 ... 第一電極、 28 ... 第二電極、

30 ... 制御電極。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(72)発明者 後藤 博一

埼玉県新座市北野3丁目6番3号 サンケン電気株式会社内

(72)発明者 篠宮 勝

群馬県安中市磯部二丁目13番1号 信越半導体株式会社 半導体磯部研究所内

(72)発明者 萩本 和徳

群馬県安中市磯部二丁目13番1号 信越半導体株式会社 半導体磯部研究所内

(72)発明者 土屋 慶太郎

群馬県安中市磯部二丁目13番1号 信越半導体株式会社 半導体磯部研究所内

審査官 棚田 一也

(56)参考文献 特開2011-082494 (JP, A)

特開2014-049674 (JP, A)

特開2008-205146 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/337-338

H01L 27/095-098

H01L 29/778

H01L 29/80-812