## (12) 发明专利

(10) 授权公告号 CN 109585472 B

(45) 授权公告日 2023.10.03

(21) 申请号 201811113385.7

(51) Int.CI.

(22) 申请日 2018.09.25

H01L 27/146 (2006.01)

(65) 同一申请的已公布的文献号

H04N 25/70 (2023.01)

申请公布号 CN 109585472 A

(56) 对比文件

(43) 申请公布日 2019.04.05

CN 103107176 A, 2013.05.15

(30) 优先权数据

US 2011175187 A1, 2011.07.21

2017-188985 2017.09.28 JP

CN 1898409 A, 2007.01.17

(73) 专利权人 佳能株式会社

CN 101640210 A, 2010.02.03

地址 日本东京

US 2015214269 A1, 2015.07.30

(72) 发明人 广田克范 佐佐木圭一 丹下勉

US 2015104954 A1, 2015.04.16

田中芳荣 大谷章

US 2011108836 A1, 2011.05.12

审查员 孙宁宁

(74) 专利代理机构 中国贸促会专利商标事务所

有限公司 11038

权利要求书2页 说明书14页 附图9页

(54) 发明名称

成像装置、成像装置的制造方法以及设备

(57) 摘要

本申请涉及成像装置、成像装置的制造方法以及设备。一种成像装置，包括：基板，包括光电转换部分；以及氮化硅层，被布置为覆盖光电转换部分的至少一部分。氮化硅层包含氯。氮化硅层中的N/Si组成比不小于1.00且小于1.33。

1. 一种成像装置,其特征在于,包括:

基板,包括光电转换部分;以及

氮化硅层,布置为覆盖光电转换部分的至少一部分,

其中氮化硅层包含氯,以及

氮化硅层中的N/Si原子组成比不小于1.00且小于1.2,

其中氮化硅层中的氯浓度不小于0.3原子%且不大于6原子%,并且

其中氮化硅层包含硅、氮、氢和氯,以及

氮化硅层中的氯的原子组成比低于硅、氮和氢中的每一个的原子组成比。

2. 如权利要求1所述的装置,还包括晶体管的栅极电极,用于转移存储在光电转换部分中的电荷,

其中氮化硅层的覆盖光电转换部分的那部分的下表面与基板的表面之间的距离短于栅极电极的上表面与基板的表面之间的距离。

3. 如权利要求2所述的装置,其中氮化硅层还覆盖栅极电极的上表面和侧表面。

4. 如权利要求1所述的装置,还包括氧化硅层,该氧化硅层被布置为与氮化硅层接触并位于光电转换部分和氮化硅层之间,

其中氮化硅层的厚度不小于氧化硅层的厚度。

5. 如权利要求1所述的装置,其中氮化硅层用作抗反射层。

6. 如权利要求1所述的装置,其中基板包括放大元件,并且氮化硅层从光电转换部分上方的一部分延伸到放大元件上方的一部分。

7. 一种结合成像装置的设备,其特征在于,包括:

如权利要求1-6中任一项所述的成像装置;以及

处理器,被配置为处理从成像装置输出的信号。

8. 一种制造成像装置的方法,其特征在于,包括:

在基板中形成光电转换部分;以及

通过使用化学气相沉积来形成覆盖光电转换部分的至少一部分的氮化硅层,

其中氮化硅层包含氯,以及

氮化硅层中的N/Si原子组成比不小于1.00且小于1.2,并且

其中氮化硅层中的氯浓度不小于0.3原子%且不大于6原子%,

氮化硅层包含硅、氮、氢和氯,以及

氮化硅层中的氯的原子组成比低于硅、氮和氢中的每一个的原子组成比。

9. 如权利要求8所述的方法,其中通过使用包含六氯乙硅烷的工艺气体来形成氮化硅层。

10. 如权利要求9所述的方法,其中,

工艺气体还包含氨,以及

工艺气体中的氨/六氯乙硅烷体积比不小于60且小于120。

11. 一种制造成像装置的方法,其特征在于,包括:

在基板中形成光电转换部分;以及

形成覆盖光电转换部分的至少一部分的氮化硅层,

其中通过使用包含六氯乙硅烷和氨的工艺气体通过使用化学气相沉积来形成氮化硅

层,以及

工艺气体中的氨/六氯乙硅烷体积比不小于60且小于120,

其中氮化硅层包含氯,

氮化硅层中的N/Si原子组成比不小于1.00且小于1.2,并且

其中氮化硅层中的氯浓度不小于0.3原子%且不大于6原子%,并且

其中氮化硅层包含硅、氮、氢和氯,以及

氮化硅层中的氯的原子组成比低于硅、氮和氢中的每一个的原子组成比。

## 成像装置、成像装置的制造方法以及设备

### 技术领域

[0001] 本发明涉及成像装置、成像装置的制造方法以及设备。

### 背景技术

[0002] 已知一种在光电转换部分上方形成用作抗反射层的氮化硅以高效地使用进入光电转换部分的光的方法。日本专利公开No. 2013-84693描述了通过使用六氯乙硅烷(HCD)作为源气体通过低压CVD(LP-CVD)在光电转换部分上方形成氮化硅的方法。

### 发明内容

[0003] 发明人已经发现,当诸如太阳光之类的强光照射光电转换部分时像素的暗输出的变化量根据在光电转换部分上形成的氮化硅层的组成而有所不同。本发明的一方面提供有利于改善成像装置的特性的技术。

[0004] 根据一些实施例,提供了一种成像装置,包括:基板,包括光电转换部分;以及氮化硅层,布置为覆盖光电转换部分的至少一部分,其中氮化硅层包含氯,并且氮化硅层中的N/Si组成比不小于1.00且小于1.33。

[0005] 根据一些其它实施例,提供了一种制造成像装置的方法,包括:在基板中形成光电转换部分;以及形成覆盖光电转换部分的至少一部分的氮化硅层,其中氮化硅层包含氯,并且氮化硅层中的N/Si组成比不小于1.00且小于1.33。

[0006] 根据还有一些其它实施例,提供了一种制造成像装置的方法,包括:在基板中形成光电转换部分;以及形成覆盖光电转换部分的至少一部分的氮化硅层,其中氮化硅层是通过使用包含六氯乙硅烷和氨的工艺气体形成的,并且工艺气体中氨/六氯乙硅烷比不小于60且小于120。

[0007] 从以下(参考附图)对示例性实施例的描述,本发明的其它特征将变得清楚。

### 附图说明

[0008] 图1A和图1B是用于解释根据实施例的成像装置的配置示例以及在成像装置中形成的像素的电路配置示例的视图;

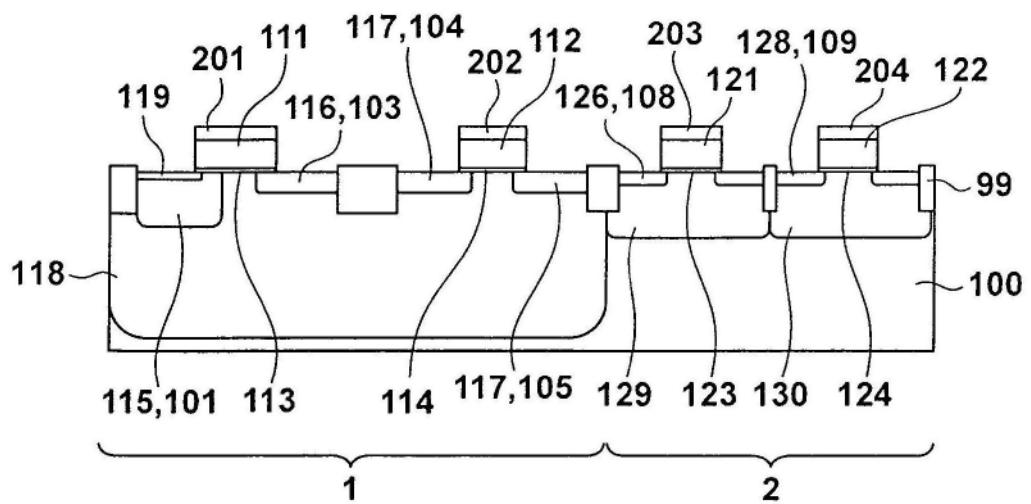

[0009] 图2A和图2B是示出第一实施例的成像装置的配置示例的平面图和截面图;

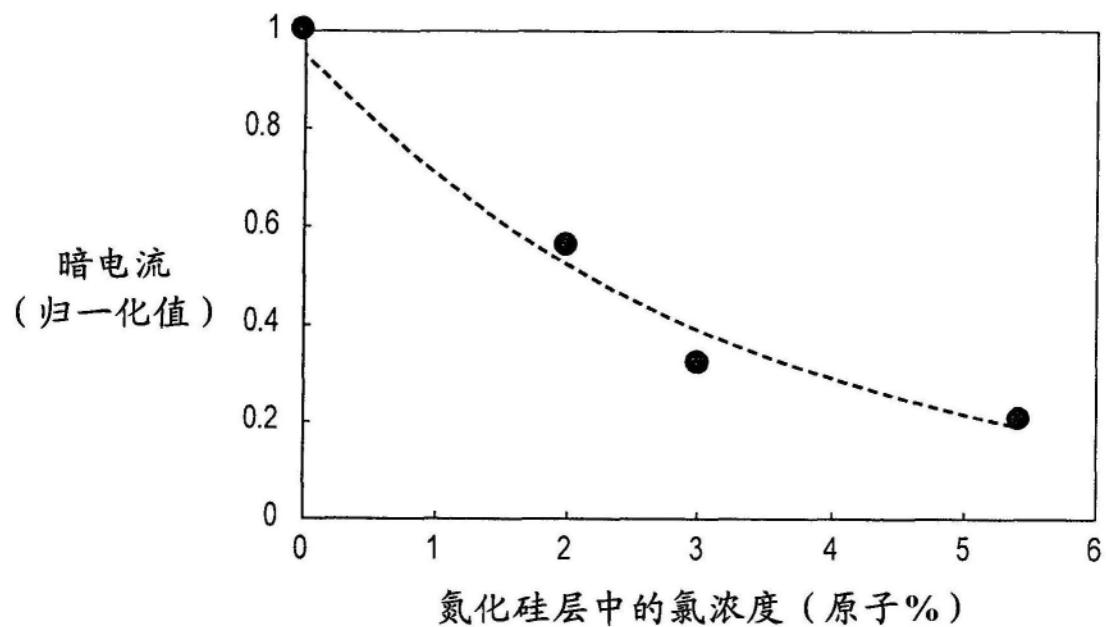

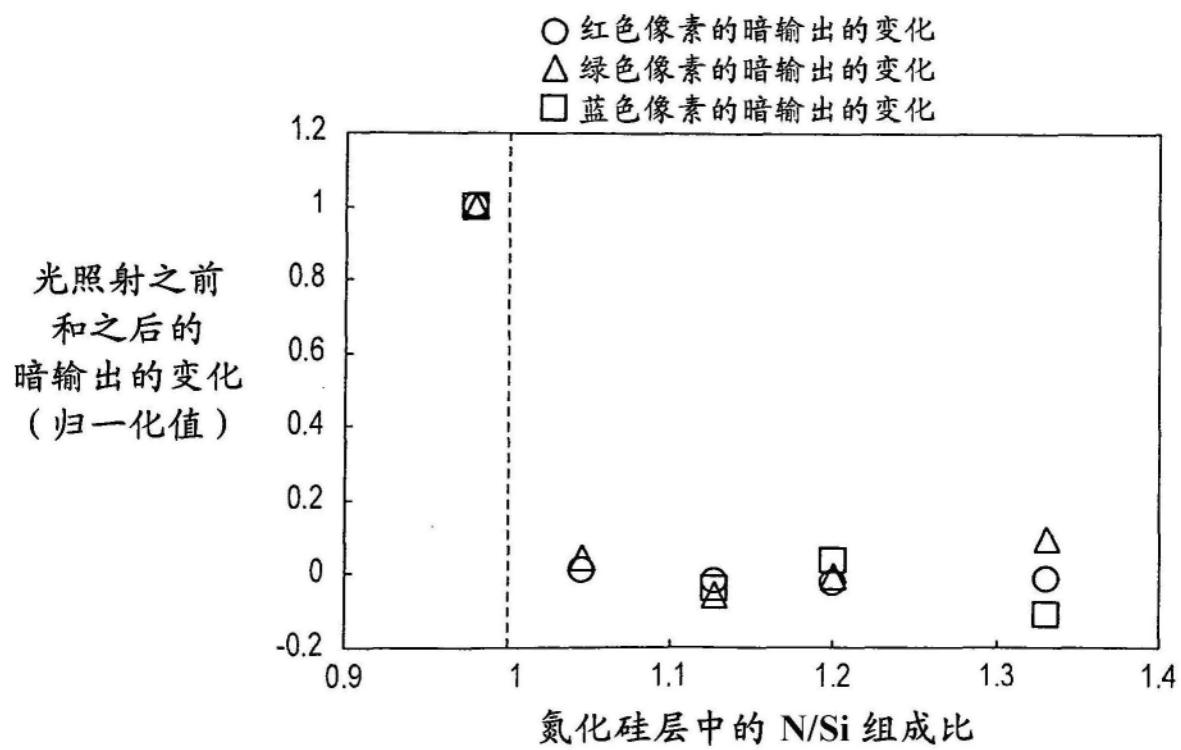

[0010] 图3A和图3B是用于解释氮化硅层中的氯浓度与暗电流之间的关系以及氮化硅层中的N/Si组成比与暗输出的变化量之间的关系的视图;

[0011] 图4A至图4C是示出制造第一实施例的成像装置的方法的示例的截面图;

[0012] 图5A至图5C是示出制造第一实施例的成像装置的方法的示例的截面图;

[0013] 图6A至图6C是示出制造第一实施例的成像装置的方法的示例的截面图;

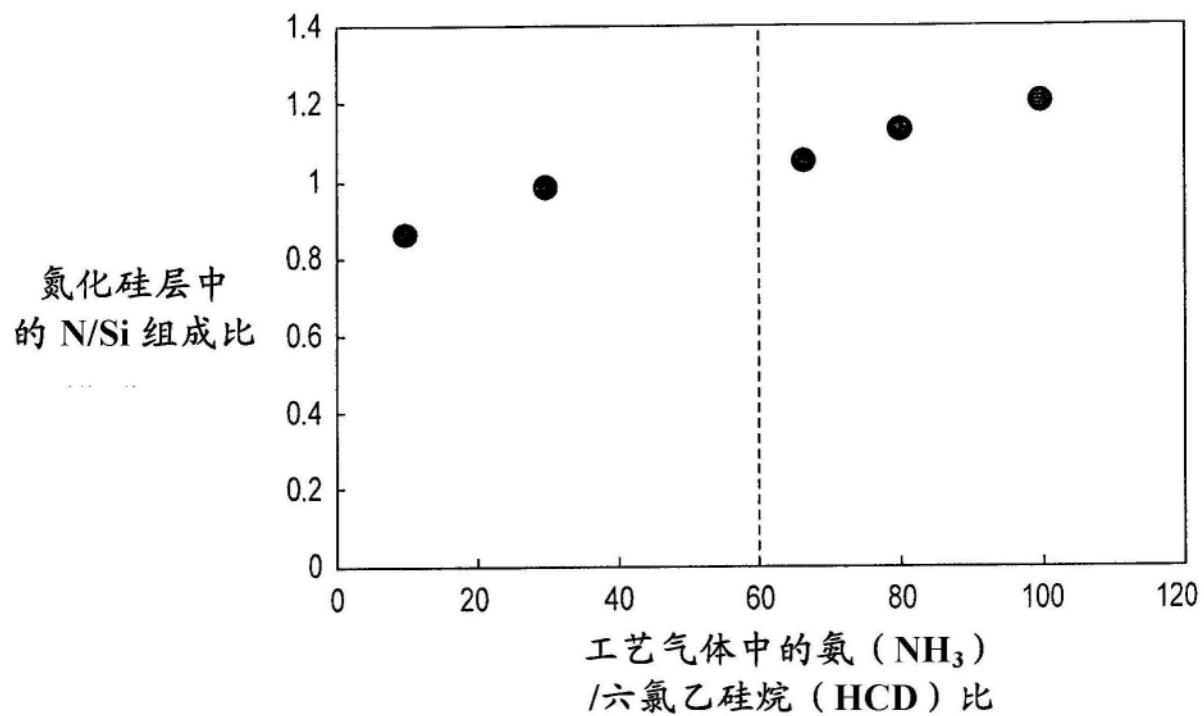

[0014] 图7是用于解释氮化硅层的沉积条件中的工艺气体中的氨/六氯乙硅烷比与氮化硅层中的N/Si组成比之间的关系的视图;以及

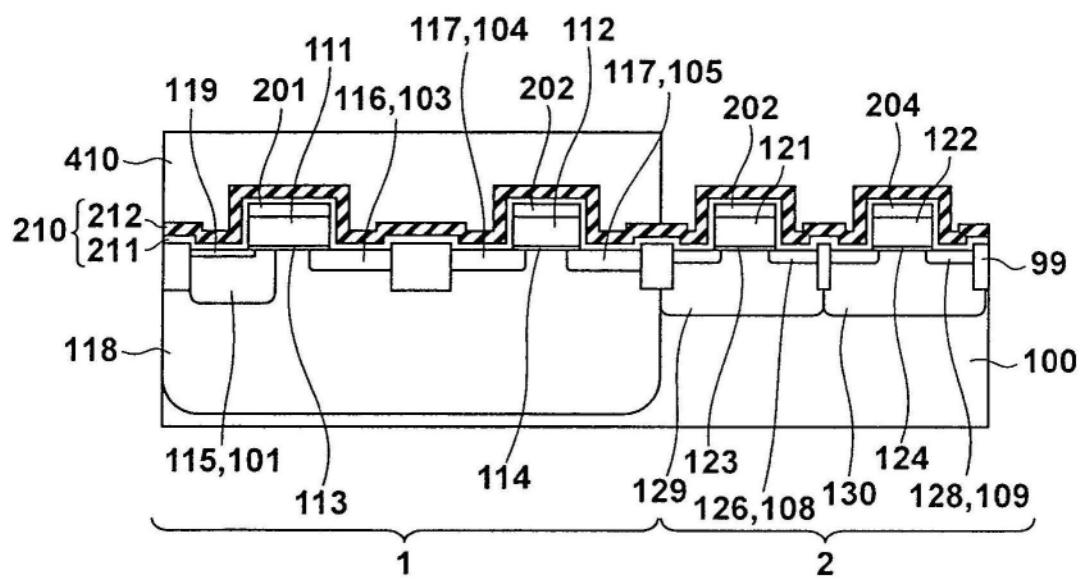

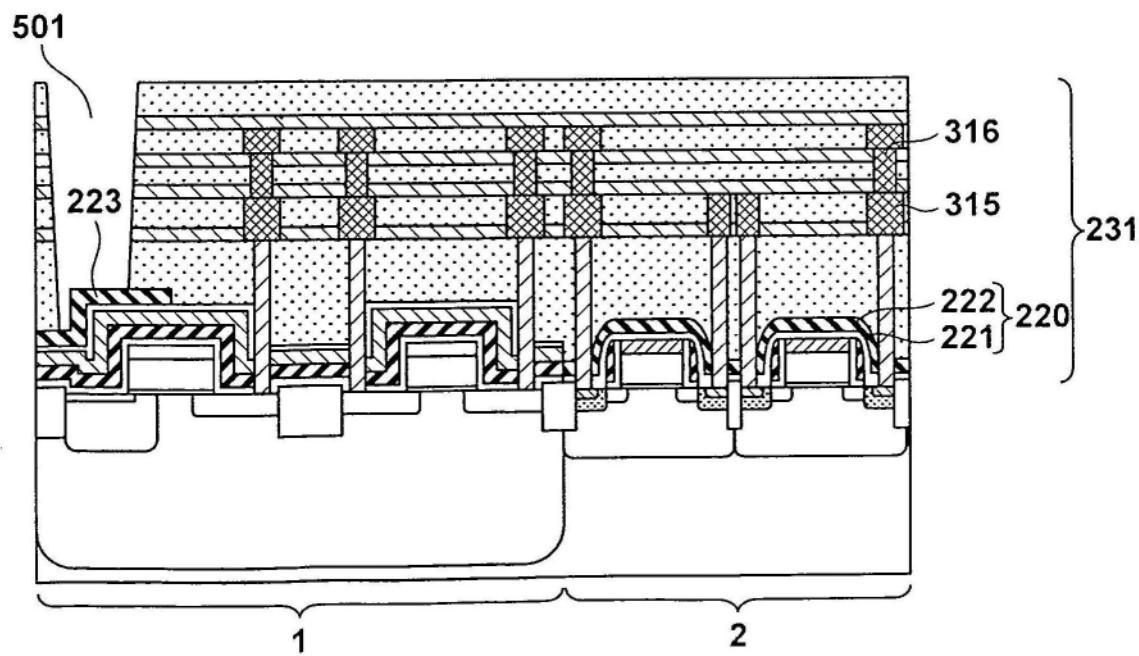

[0015] 图8是第二实施例的成像装置的截面图。

## 具体实施方式

[0016] 下面将参考附图解释根据本发明的成像装置的第一实施例和示例。在以下解释和附图中,相同的附图标记贯穿多个附图表示相同的部件。因此,将通过参考多个附图解释相同的部件,并且将省略由相同的附图标记表示的部件的解释。

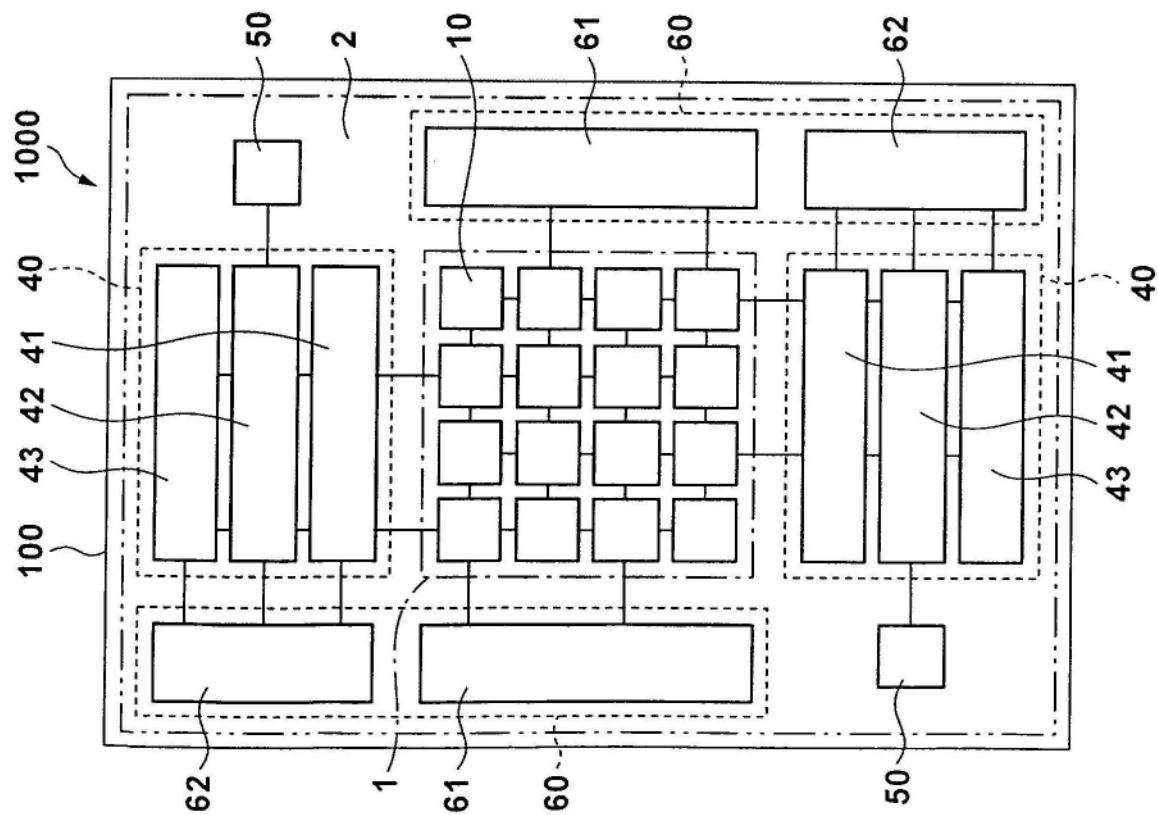

[0017] 将参考图1A至图6C来解释根据本发明第一实施例的成像装置的布置及其制造方法。图1A是示出根据本发明第一实施例的成像装置1000的配置示例的视图。成像装置1000包括:像素区域1,其中布置有多个像素10;以及外围电路区域2,其中布置有用于例如处理从像素10输出的信号的外围电路。像素区域1和外围电路区域2在单个基板100上形成。基板100是由例如硅制成的半导体基板。参考图1A,由单点划线围绕的区域是像素区域1,以及单点划线和双点划线之间的区域是外围电路区域2。外围电路区域2可以被说成是位于像素区域1周围,并且也可以被说成是位于像素区域1和基板100的边缘之间。图1A中示出的像素区域1是其中以二维阵列的形式布置有多个像素10的区域传感器的示例。像素区域1也可以是在一维方向上布置多个像素10的线性传感器。

[0018] 图1B是示出布置在像素区域1中的单独像素10的电路配置示例的视图。像素10包括光电转换部分11、转移元件12、电容元件13、放大元件15、复位元件16和选择元件17。光电转换部分11将入射光转换成电信号。在这个实施例中,在基板100中形成的光电二极管用作光电转换部分11。

[0019] 在基板100上形成的晶体管被用作放大元件15、复位元件16和选择元件17。在本说明书中,布置在像素10中的每个晶体管将被称为像素晶体管。MISFET(金属-绝缘体-半导体场效应晶体管)被用作这种像素晶体管。还可以使用例如使用氧化硅作为MISFET的栅极绝缘膜的MOSFET(金属-氧化物-半导体场效应晶体管)。但是,栅极绝缘膜不限于此,也可以是氮化硅等。栅极绝缘膜也可以是所谓的高介电常数(permittivity)栅极绝缘膜,诸如氧化铪。此外,栅极绝缘膜可以通过堆叠这些材料形成,并且也可以是诸如氮氧化硅之类的复合物。

[0020] 转移元件12具有MOS型栅极结构。因此,当使用转移元件12作为栅极、光电转换部分11作为源极并且电容元件13作为漏极时,这种结构可以被视为晶体管。因而,光电转换部分11、转移元件12和电容元件13可以被称为像素晶体管。

[0021] 转移元件12将在光电转换部分11中生成的信号电荷转移到电容元件13。电容元件13用作电荷-电压转换元件,其生成与电容和节点14中的信号电荷量对应的电压。放大元件15的栅极经由节点14连接到电容元件13。放大元件15的漏极连接到电力线21,并且放大元件15的源极经由选择元件17连接到输出线22。电容元件13和放大元件15的栅极经由复位元件16连接到电力线21。节点14的电位通过接通复位元件16被复位成与电力线21的电位对应的电位。而且,与节点14的电位对应的信号通过接通选择元件17从放大元件15输出到输出线22。像素10的布置不限于图1B中所示的布置,由光电转换部分11根据入射光生成的电信号仅需要输出到外围电路区域2。

[0022] 在这个实施例中,具有n沟道的MOSFET(nMOSFET)用作每个像素晶体管,但是具有p沟道的pMOSFET也可以被包括。像素晶体管还可以包括除MISFET以外的晶体管。例如,放大元件15也可以是JFET(结型FET)或双极晶体管。

[0023] 在本说明书的以下解释中,与在像素区域1中将作为信号电荷被处理的电荷用作

多数载流子的导电类型匹配的导电类型将被称为第一导电类型,与将作为信号电荷被处理的电荷用作少数载流子的导电类型匹配的导电类型将被称为第二导电类型。例如,当使用电子作为信号电荷时,n型是第一导电类型,p型是第二导电类型。

[0024] 下面将再次参考图1A解释外围电路区域2。外围电路区域2包括用于处理由像素10生成的电信号的信号处理单元40。外围电路区域2还包括用于将由信号处理单元40处理后的信号输出到成像装置1000的外部的输出单元50,以及用于控制其中布置有多个像素10的像素区域1以及信号处理单元40的控制单元60。信号处理单元40、输出单元50和控制单元60可以被称为外围电路。

[0025] 在这个实施例中,信号处理单元40包括具有多个列放大器的放大电路41、具有多个A/D转换器的转换电路42,以及用于选择性地从转换电路42向输出单元50输出信号的水平扫描电路43。信号处理单元40可以执行相关双采样(CDS)处理、并行-串行转换处理、模数转换处理等。输出单元50包括电极垫和保护电路。控制单元60包括垂直扫描电路61和定时生成电路62。外围电路区域2的布置不限于此,并且仅需要适当地处理由像素区域1的每个像素10生成的电信号,并将处理后的信号输出到成像装置1000的外部。

[0026] 外围电路可以通过使用多个晶体管(例如,如像素晶体管的MISFET)来形成,并且可以通过CMOS(互补MOS)电路来配置,该CMOS电路包括nMOSFET和pMOSFET。在本说明书中,形成外围电路的晶体管将被称为外围晶体管,并且在指定导电类型时将被称为外围nMOSFET和外围pMOSFET。除了诸如晶体管和二极管之类的有源元件之外,外围电路还可以包括诸如电阻元件和电容元件之类的无源元件。

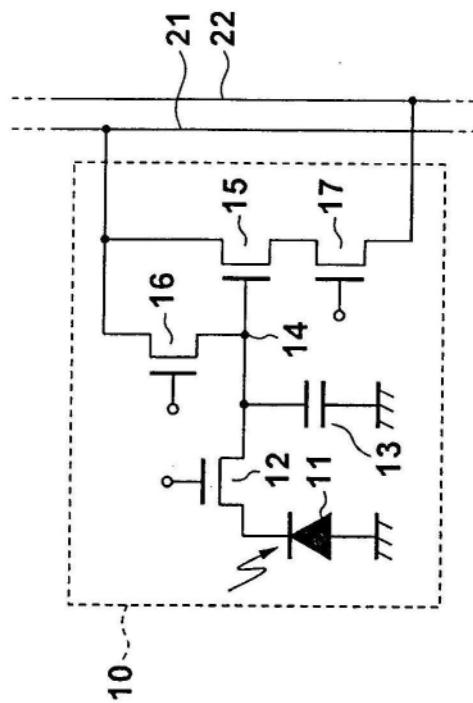

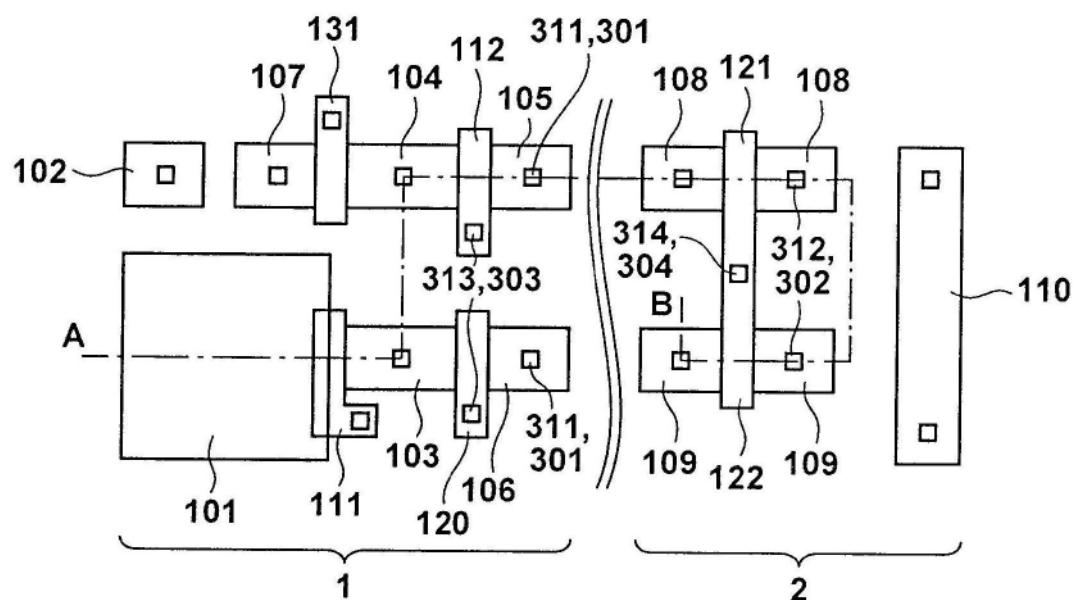

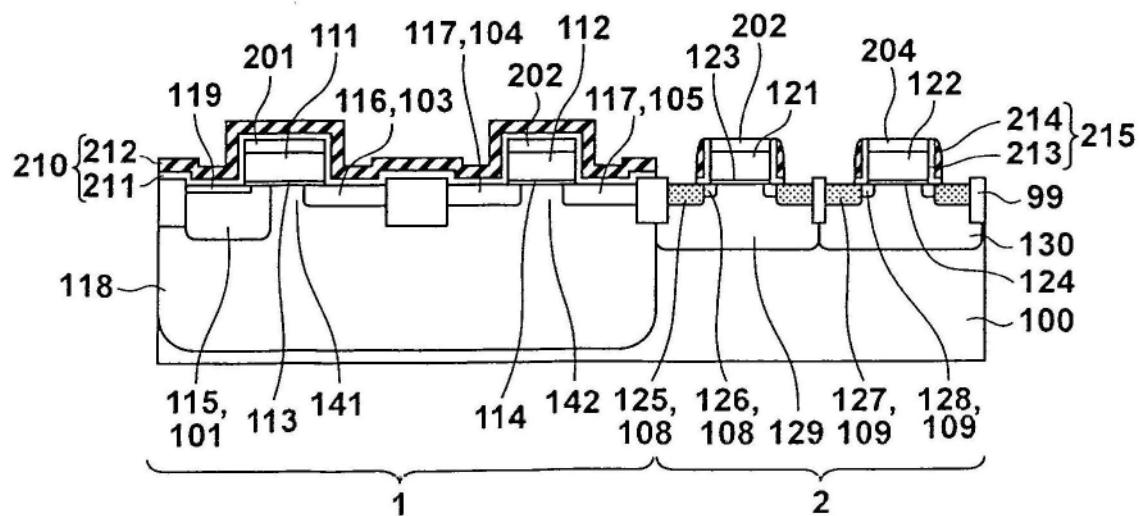

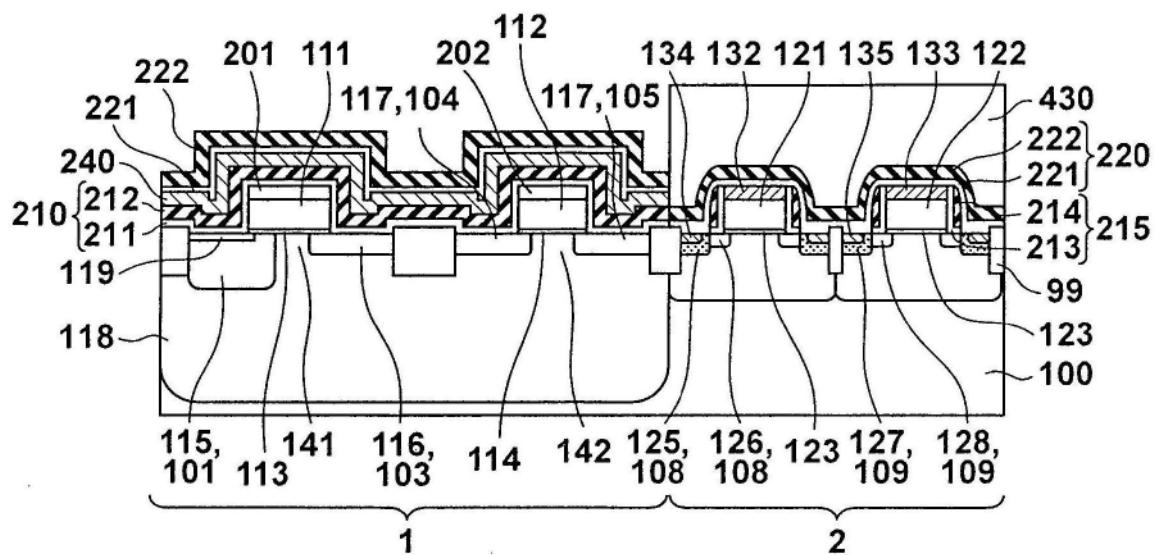

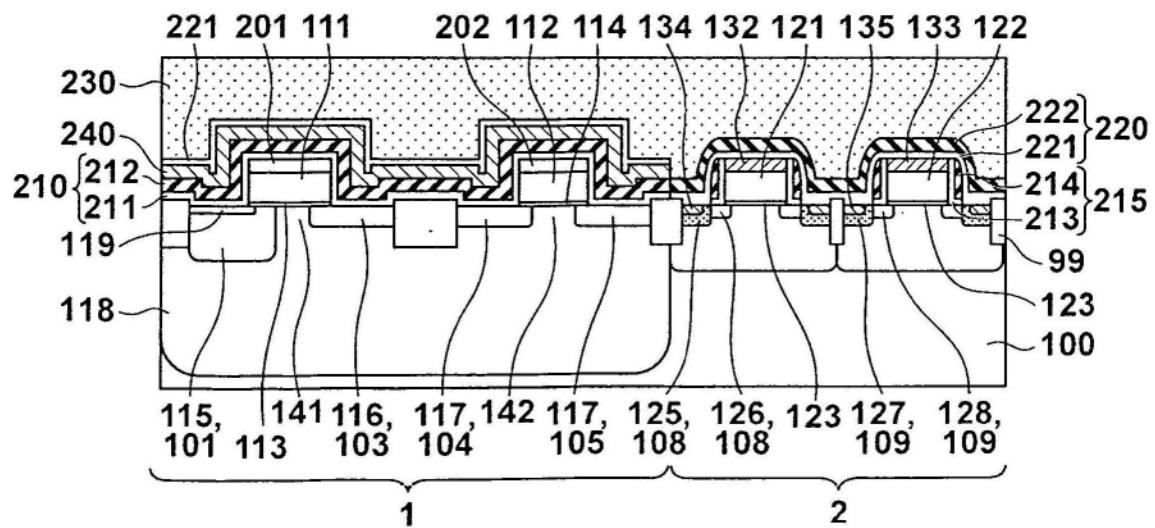

[0027] 下面将参考图2A和图2B解释这个实施例的成像装置1000的结构。图2A和图2B分别是示出像素区域1和外围电路区域2的部分的平面图和截面图。

[0028] 参考图2A,区域101等同于光电转换部分11,区域103等同于电容元件13和用于检测电荷的节点14,并且区域106等同于复位元件16的漏极区域。区域104等同于放大元件15的源极区域,区域105等同于放大元件15的漏极区域,并且区域107等同于选择元件17的源极。区域103还用作复位元件16的源极,并且区域104还用作选择元件17的漏极区域。栅极电极111等同于转移元件12的栅极,栅极电极120等同于复位元件16的栅极,栅极电极112等同于放大元件15的栅极,并且栅极电极131等同于选择元件17的栅极。区域108和区域109分别等同于外围nMOSFET或外围pMOSFET的源极/漏极区域。栅极电极121和栅极电极122分别等同于外围nMOSFET或外围pMOSFET的栅极。在这个实施例中,每个栅极电极由多晶硅(polycrystalline silicon)形成。而且,在这个实施例中,栅极电极121和栅极电极122是一体的,但它们也可以彼此独立地形成。栅极电极以及等同于源极/漏极区域的区域103至109经由埋在接触孔301、302、303和304中的导电构件311、312、313和314连接到互连件(未示出)。

[0029] 参考图2A,像素10的参考接触区域102可以在像素区域1中形成。参考接触区域102经由互连件(未示出)向像素10供给诸如接地电位之类的参考电位。通过在像素区域1中布置多个参考接触区域102,可以抑制像素区域1中参考电位的变化,并且抑制捕获图像中阴影的发生。

[0030] 此外,电阻元件110可以在图2A中示出的外围电路区域2中形成。电阻元件110是在基板100中形成的杂质区域。通过在这个杂质区域的两端中形成触点,可以获得与杂质浓

度、触点之间的距离以及杂质区域的宽度对应的电阻。在这个实施例中,电阻元件110的杂质区域是在具有p型作为第二导电类型的阱中形成的具有n型作为第一导电类型的杂质区域。替代地,电阻元件110的杂质区域也可以是在n型阱中形成的p型杂质区域。此外,由n型杂质区域形成的电阻元件和由p型杂质区域形成的电阻元件也可以共存。外围电路区域2还可以包括除电阻元件110以外的其它无源元件,例如,具有由多晶硅形成的MOS结构的电阻元件或电容元件。

[0031] 在这个实施例中,区域101和103、等同于像素晶体管的源极/漏极区域的区域104、105、106和107、参考接触区域102以及等同于外围nMOSFET的源极/漏极区域的区域108是n型杂质区域。等同于外围pMOSFET的源极/漏极区域的区域109是p型杂质区域。

[0032] 图2B是沿图2A中示出的线A-B截取的截面图。基板100是诸如如上所述的硅之类的半导体基板。基板100被元件隔离区域99分成多个有源区域。元件隔离区域99可以由通过浅沟槽隔离(STI)、选择性氧化(LOCOS)等形成的、用于元件隔离的绝缘体制成。在每个有源区域中形成杂质区域,并且每个杂质区域形成半导体元件。因此,可以形成用于p-n结隔离的杂质区域(例如,p型杂质区域)作为元件隔离区域。

[0033] 在基板100的有源区域中形成具有与元件的导电类型对应的导电类型的阱。在像素区域1中形成p型阱118,并且在外围电路区域2中形成p型阱129和n型阱130。此外,在图2A中示出的参考接触区域102中形成杂质浓度高于p型阱118的杂质浓度的p型杂质区域。连接到参考接触区域102的互连件经由参考接触区域102向阱118供给参考电位。

[0034] 现在将参考图2B解释像素区域1和外围电路区域2的截面结构。为了便于解释,图2B和图4A至图6(将稍后描述)将像素区域1和外围电路区域2描绘为彼此相邻。首先,将解释像素区域1的截面结构。在区域101中,形成光电转换部分11的n型存储区域115被形成。存储区域115与p型阱118一起形成p-n结,并且用作光电转换部分11的光电二极管。用于获得光电转换部分11作为钉扎(pinned)光电二极管的p型表面区域119被形成在存储区域115和基板100的表面之间。在区域103中,形成电容元件13的杂质区域116被形成。杂质区域116是浮置扩散区域。N型杂质区域117被形成为放大元件15、复位元件16和选择元件17的源极/漏极区域。图2B示出了放大元件15的截面,但是复位元件16和选择元件17可以具有相同的结构。

[0035] 棚极绝缘膜113和棚极绝缘膜114以及诸如像素10的其它像素晶体管之类的元件的棚极绝缘膜主要由氧化硅制成,并且这个氧化硅可以包含少量(例如,少于10%)通过等离子体氮化或热氧氮化形成的氮。含氮的氧化硅的介电常数高于纯氧化硅的介电常数,因此能够改善晶体管的驱动能力。但是,棚极绝缘膜的布置不限于此,并且棚极绝缘膜也可以是纯氧化硅或氮化硅。还可以使用诸如如上所述的氧化铪之类的高介电常数材料,或这些材料的复合物或多层膜。在基板100上的棚极绝缘膜113和棚极绝缘膜114上形成的棚极电极111和棚极电极112的上表面覆盖有包含氧化硅或氮化硅的绝缘层201和绝缘层202。

[0036] 在像素区域1上形成包括氧化硅层211和氮化硅层212(第一氮化硅层)的绝缘膜210。绝缘膜210覆盖棚极电极111和棚极电极112的上表面(有绝缘层201和绝缘层202插入其间),并且还覆盖棚极电极111和棚极电极112的侧表面(没有绝缘层201和绝缘层202)。即,氮化硅层212从在光电转换部分11上方的一部分延伸到在放大元件15上方的一部分。氮化硅层212(将稍后描述)不仅有利于改善光电转换部分11的特性,而且还有利于改善放大元件15的特性。虽然未在图2B中示出,但是绝缘膜210类似地覆盖棚极电极120和棚极电极

131的上表面和侧表面。绝缘膜210还覆盖形成光电转换部分11的区域101,以及等同于像素晶体管的源极/漏极区域的区域103至107。在这种情况下,基板100的表面与氮化硅层212的覆盖形成光电转换部分11的区域101的部分的下表面之间的距离短于基板100的表面与像素晶体管的栅极电极的上表面之间的距离。氮化硅层212与基板100之间的距离越短,氮化硅层212的组成的影响越大。氮化硅层212与基板100之间的距离可以如上所述的通过与栅极电极的上表面相比来相对地定义。氮化硅层212与基板100之间的距离通常小于100nm,并且还可以小于50nm或小于25nm。

[0037] 绝缘膜210是氧化硅层211和氮化硅层212的多层膜。氧化硅层211和氮化硅层212具有彼此接触的界面。在这个实施例中,氧化硅层211与栅极电极111、112、120和131的侧表面接触,但是其它层也可以插入在氧化硅层211和栅极电极111、112、120和131的侧表面之间。而且,氧化硅层211与形成光电转换部分11的区域101接触,并且与等同于像素晶体管的源极/漏极区域的区域103至107接触,由此相对于基板100形成界面。但是,也可以在它们之间插入其它层。

[0038] 作为氧化硅层211和氮化硅层212的多层膜,绝缘膜210覆盖形成光电转换部分11的区域101,其中氧化硅层211相对于波长为633nm的光具有1.4至1.5的折射率,氮化硅层212相对于相同的光具有1.9至2.1的折射率。因此,绝缘膜210可以用作抵抗光进入光电转换部分11的抗反射层。为了获得良好的抗反射特性,氮化硅层212的厚度可以等于或大于氧化硅层211的厚度。此外,氮化硅层212的厚度可以大于氧化硅层211的厚度。

[0039] 在绝缘膜210上形成保护膜240以覆盖绝缘膜210。保护膜240可以是绝缘体(诸如氧化硅或氮化硅)的单层膜或多层膜。在保护膜240上形成氧化硅层221以覆盖保护膜240。在氧化硅层221上形成绝缘膜230以覆盖氧化硅层221。绝缘膜230可以是诸如BPSG、BSG或PSG之类的硅酸盐玻璃,或者氧化硅。绝缘膜230的上表面是平坦表面,该平坦表面基本上不反映底层表面的不平坦。

[0040] 接触孔301和303被形成为延伸穿过绝缘膜230、氧化硅层221、保护膜240和绝缘膜210。用于电连接互连件(未示出)和像素晶体管的导电构件311和313在接触孔301和303中形成。在图2A中示出的这种布置中,导电构件311连接到等同于像素晶体管的源极/漏极区域的区域103至107以及参考接触区域102,并且导电构件313连接到栅极电极111、112、120和131。导电构件311和313是主要由诸如钨之类的金属制成的接触插塞。

[0041] 下面将解释绝缘膜210的氮化硅层212中包含的氯的浓度。本发明人通过实验已经发现,成像装置的特性根据氮化硅层212中包含的氯的浓度而改变。更具体而言,由于含氯的氮化硅层212覆盖区域101,因此氮化硅层212中包含的氯终止光电转换部分11的悬空键(dangling bond),因此可以减小成像装置1000的暗电流。由于氮化硅层212减小了用氮化硅层212覆盖的放大元件15中晶体管的沟道的界面状态,因此可以改善放大元件15的噪声特性。

[0042] 下面将参考图3A解释氮化硅层212中的氯浓度与暗电流之间的关系。在图3A中,横坐标指示氮化硅层212中的氯浓度,并且纵坐标指示暗电流的值。纵坐标的值被归一化,使得当氯浓度为0原子%时,暗电流的值为1。图3A示出了光电转换部分11的暗电流随着氮化硅层212中的氯浓度增加而减小。因而,与氮化硅层212中不含氯的情况相比,通过使氮化硅层212包含氯,可以降低暗电流的水平。因此,在这个实施例中,氮化硅层212包含氯。当氮化

硅层212显著包含氯时,氯浓度通常为0.1原子%或更多,更通常为0.3原子%或更多。氮化硅层212中的氯浓度也可以小于1原子%。为了减小暗电流,氮化硅层212中的氯浓度可以是1原子%或更多、2原子%或更多以及3原子%或更多中的任何一个。如果氮化硅层212中的氯浓度极度增加,那么稳定性和透射率降低。因此,氮化硅层212中的氯浓度可以是10原子%或更少或6原子%或更少。尤其是当氯浓度高于3原子%时,波长450nm处的入射光的光吸收系数(k值)增加,因此氯浓度可以是3原子%或更少。

[0043] 下面将解释绝缘膜210的氮化硅层212中氮和硅的组成比(即,N/Si组成比)。本发明人通过实验已经发现,成像装置的特性根据绝缘膜210的氮化硅层212中的N/Si组成比而改变。更具体而言,当氮化硅层212中的N/Si组成比小于1.00时,光的短波长侧的光吸收系数(k值)增加。因而,当覆盖区域101的氮化硅层212中的N/Si组成比小于1.00时,氮化硅层212吸收入射光,因此接收已进入光电转换部分11的光的区域的特性劣化。因此,在稍后的成像中,成像装置1000的暗输出在光照射之前和之后改变。氮化硅( $\text{Si}_3\text{N}_4$ )的化学计量组成比为N/Si=1.33,因此N/Si组成比小于1.00的氮化硅具有富硅组成比。

[0044] 图3B是用于解释氮化硅层212中的N/Si组成比与光照射之前和之后的暗电流的变化量之间的关系的图。在图3B中,横坐标指示N/Si组成比,并且纵坐标指示通过从光照射之后的暗输出(电流值)减去光照射之前的暗输出(电流值)而获得的值。将纵坐标的值归一化,使得当N/Si组成比为0.98时,变化量为1。圆形图(plot)指示红色像素(即,用于检测红光的像素;这类似地适用于其它颜色)的暗输出的变化量,三角形图指示绿色像素的暗输出的变化量,并且方形图指示蓝色像素的暗输出的变化量。图3B揭示,当氮化硅层212中的N/Si组成比为1.00或更大时,与使用具有小于1.00的N/Si组成比的氮化硅层的情况相比,暗输出的变化量大大减少。更具体而言,假设当N/Si组成比为0.98时暗电流的变化量为1,则当N/Si组成比为1或更大且1.2或更小时,暗电流的变化量几乎为0。此外,当N/Si组成比增加到1.33时,暗电流的变化量增加。因此,在这个实施例中,氮化硅层212中的N/Si组成比可以是1.00或更大且小于1.33。此外,氮化硅层212中的N/Si组成比可以是1.10或更大且1.30或更小,并且还可以是1.15或更大且1.25或更小。当氮化硅层212中的N/Si组成比是1.15或更大且1.25或更小时,氮化硅层212中的氯浓度例如是0.5原子%或更大且0.7原子%或更小。

[0045] 下面将解释外围电路区域2的截面结构。在等同于外围nMOSFET的源极/漏极区域的区域108中形成n型杂质区域125、n型杂质区域126和硅化物层134。杂质区域125的杂质浓度高于杂质区域126的杂质浓度。硅化物层134覆盖杂质区域125。在等同于外围pMOSFET的源极/漏极区域的区域109中形成p型杂质区域127、p型杂质区域128和硅化物层135。杂质区域127的杂质浓度高于杂质区域128的杂质浓度。硅化物层135覆盖杂质区域127。因此,外围晶体管通过重掺杂的杂质区域125和127和轻掺杂的杂质区域126和128形成LDL(轻掺杂漏极)结构。

[0046] 棚极电极121和122形成在基板100上,棚极绝缘膜123和124插入在棚极电极121和122与基板100之间。在这个实施例中,如在像素10的像素晶体管中那样,棚极绝缘膜主要由氧化硅制成,并且这种氧化硅包含少量(例如,少于10%)通过等离子体氮化或热氧氮化形成的氮。外围晶体管的棚极绝缘膜123和棚极绝缘膜124的厚度可以等于或小于像素晶体管的棚极绝缘膜113和棚极绝缘膜114的厚度。例如,棚极绝缘膜113和棚极绝缘膜114的厚度

可以是5.0nm或更大且10nm或更小,以及栅极绝缘膜123和栅极绝缘膜124的厚度可以是1.0nm或更大且5.0nm或更小。通过使像素晶体管和外围晶体管的栅极绝缘膜的厚度彼此不同,可以增加像素晶体管的击穿电压和外围晶体管的驱动速度二者。形成栅极电极121和栅极电极122的部分的硅化物层132和硅化物层133在栅极电极121和栅极电极122的上表面上形成。因此,外围晶体管可以具有其中形成硅化物层132、133、134和135的SALICIDE(自对准硅化物)结构。可以使用钛、镍、钴、钨、钼、钽、铬、钯、铂等作为形成硅化物层的金属成分。

[0047] 外围晶体管的栅极电极121和栅极电极122的侧表面覆盖有侧壁215。侧壁215还覆盖区域108和区域109的轻掺杂的杂质区域126和128。在这个实施例中,侧壁215具有包括氧化硅层213和氮化硅层214的多层结构。氧化硅层213位于氮化硅层214与栅极电极121和栅极电极122之间,以及氮化硅层214与区域108和区域109之间。氧化硅层213和氮化硅层214具有彼此接触的界面。

[0048] 在外围电路区域2上形成包括氧化硅层221和氮化硅层222(第二氮化硅层)的绝缘膜220。在这个实施例中,绝缘膜220是氧化硅层221和氮化硅层222的多层膜。氧化硅层211和氮化硅层212具有彼此接触的界面。但是,绝缘膜220也可以是氮化硅层222的单层膜。氧化硅层221位于氮化硅层214与氮化硅层222之间。氮化硅层214和氧化硅层221具有彼此接触的界面。即,侧壁215和绝缘膜220具有彼此接触的界面。此外,绝缘膜220覆盖区域108和区域109中的硅化物层134和硅化物层135。绝缘膜220与区域108和区域109中的硅化物层134和硅化物层135具有彼此接触的界面。虽然在这个实施例中形成硅化物层134和硅化物层135,但是不需要总是形成硅化物层134和硅化物层135。在这种情况下,绝缘膜220覆盖重掺杂的杂质区域125和127。绝缘膜220和重掺杂的杂质区域125和127具有彼此接触的界面。如在像素区域1中那样,绝缘膜230在绝缘膜220上形成。接触孔302和接触孔304被形成为延伸通过绝缘膜230以及包括氧化硅层221和氮化硅层222的绝缘膜220。用于电连接互连件(未示出)与作为外围晶体管的源极/漏极区域的区域108以及栅极电极121和栅极电极122的导电构件312和314在接触孔302和接触孔304中形成。如同导电构件311和导电构件313,导电构件312和导电构件314是主要由诸如钨之类的金属制成的接触插塞。

[0049] 在绝缘膜230上形成布线图案(未示出),布线图案包括要连接到导电构件311、312、313和314的互连件。这种布线图案可以通过堆叠多个布线图案来获得,层间介电膜被插入它们之间。布线图案可以由诸如铝或铜之类的金属制成。此外,可以在基板100的接收光的光接收表面上形成滤色器(未示出)和微透镜(未示出)。这些部件可以通过使用现有技术形成,因此将省略其解释。成像装置1000容纳在封装等中,并且可以构造诸如结合这种封装的设备或信息终端之类的成像系统。

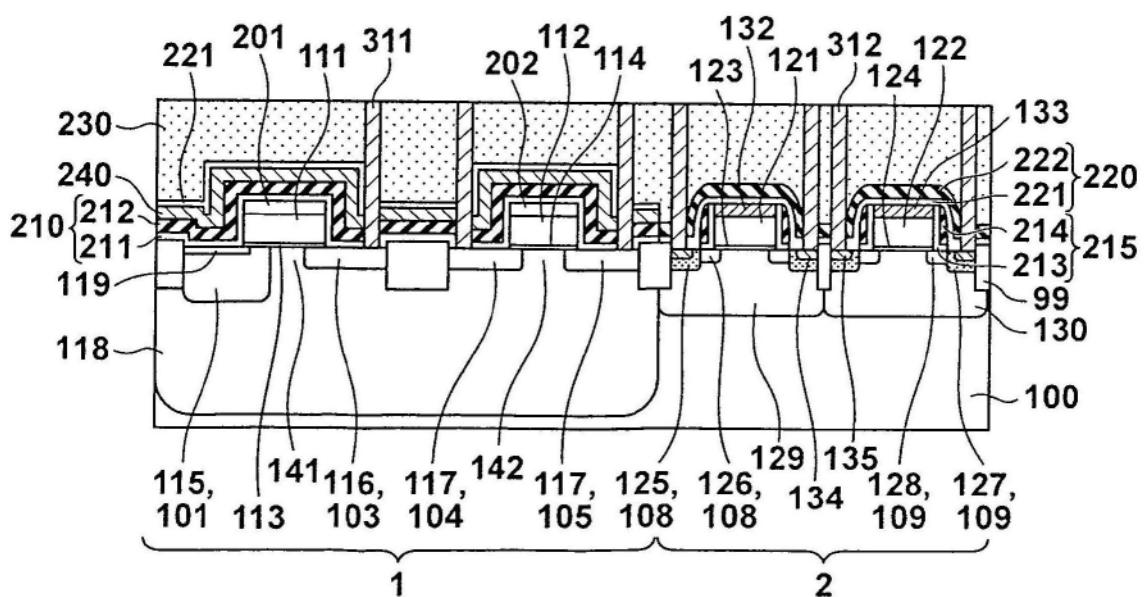

[0050] 接下来,将参考图4A至图6C解释制造成像装置1000的方法。图4A至图6C是成像装置1000的制造步骤的截面图。首先,如图4A中所示,形成像素晶体管和外围晶体管。在形成像素晶体管和外围晶体管的这个步骤中,通过使用STI、LOCOS等在基板100中形成元件隔离区域99。基板100可以是从硅锭切出的硅晶片,也可以是通过在硅晶片上外延生长单晶硅层而获得的晶片。在形成元件隔离区域99之后,形成具有第二导电类型(p型)的阱118和129以及具有第一导电类型(n型)的阱130。

[0051] 在形成阱118、129和130之后,形成栅极绝缘膜113、114、123和124,并且在栅极绝缘膜113、114、123和124上沉积多晶硅。栅极绝缘膜113、114、123和124可以同时在像素区域

1和外围电路区域2中形成。可替代地,如前所述,也可以通过使用不同的步骤在像素区域1和外围电路区域2中形成这些栅极绝缘膜,以便获得不同的膜厚度。然后,根据对应晶体管的导电类型,通过离子注入等在多晶硅的要成为栅极电极的每个部分中注入杂质。在这种杂质注入之后,在多晶硅的将用作栅极电极111、112、121和122的那些部分上形成用作硬掩模的绝缘层201、202、203和204。之后,通过使用绝缘层201、202、203和204作为掩模,蚀刻开口中的多晶硅。在这个步骤中,形成n型栅极电极111、112和121以及p型栅极电极122。

[0052] 随后,形成n型存储区域115和p型表面区域119。而且,形成区域103中的杂质区域116和用作像素晶体管的源极/漏极区域的具有单个漏极结构的n型杂质区域117。此外,形成具有外围晶体管的LDD结构的轻掺杂的n型杂质区域126和p型杂质区域128。当形成像素10的杂质区域116和117时,剂量可以是 $5 \times 10^{12}$ 至 $5 \times 10^{14}$ (离子/cm<sup>2</sup>),并且也可以是 $1 \times 10^{13}$ 至 $1 \times 10^{14}$ (离子/cm<sup>2</sup>)。当形成具有LDD结构的轻掺杂的杂质区域126和128时,剂量可以是 $5 \times 10^{12}$ 至 $5 \times 10^{14}$ (离子/cm<sup>2</sup>),并且也可以是 $1 \times 10^{13}$ 至 $1 \times 10^{14}$ (离子/cm<sup>2</sup>)。因而,杂质区域116和117以及杂质区域126的杂质注入也可以并行进行。此外,存储区域115、杂质区域116、117、126和128以及表面区域119的杂质注入的次序可以是任意次序。

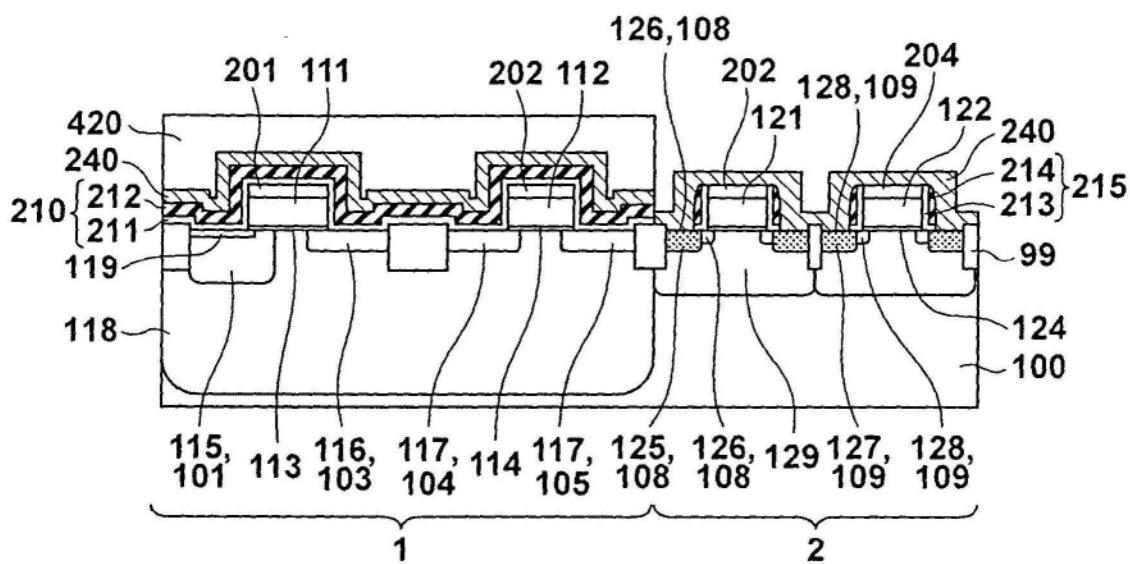

[0053] 然后,如图4B中所示,形成包括氧化硅层211和氮化硅层212的绝缘膜210。绝缘膜210覆盖栅极电极111、112、121和122的上表面和侧表面,以及用作像素晶体管和外围晶体管的源极/漏极区域的区域103、104、105、108和109,以及区域101。通过图4A中示出的步骤,杂质区域116、117、126和128在源极/漏极区域中形成,因此绝缘膜210覆盖杂质区域116、117、126和128。

[0054] 绝缘膜210是氧化硅层211和氮化硅层212的多层膜,并且氧化硅层211和氮化硅层212被形成为彼此接触。形成绝缘膜210的步骤包括形成氧化硅层211的步骤和形成氮化硅层212的步骤。如前所述,绝缘膜210覆盖至少用作光电转换部分11的区域101,以便用作抗反射层,并且氮化硅层212的厚度可以等于或大于氧化硅层211的厚度,以便获得良好的抗反射特性。例如,氧化硅层211的厚度可以是5nm或更大且20nm或更小,并且氮化硅层212的厚度可以是20nm或更大且100nm或更小。

[0055] 在这个实施例中,通过使用CVD(化学气相沉积)来形成氧化硅层211和氮化硅层212。通过使用LPCVD(低压CVD)作为热CVD来形成氧化硅层211,在LPCVD中,包含源气体(诸如TEOS)的工艺气体的压力(沉积压力)为20Pa或更大且200Pa或更小。在这个步骤中,沉积温度(基板温度)可以是500°C或更高且800°C或更低。本文提到的工艺气体是指沉积室中的全部气体,其包含至少源气体并包含按照需要添加的载气。可以使用稀有气体(诸如氩气或氪气)或氮气作为这种载气。而且,沉积压力是指沉积室中的工艺气体的压力(总压力)。

[0056] 通过使用包含例如氨(NH<sub>3</sub>)和六氯乙硅烷(HCD)作为源气体的工艺气体,通过使用LPCVD形成氮化硅层212。在这个步骤中,工艺气体的压力(沉积压力)可以是20Pa或更大且200Pa或更小,并且沉积温度(基板温度)可以是500°C或更高且800°C或更低。

[0057] 在如前所述的这个实施例中,为了减小暗电流和暗输出的变化量,要用作抗反射层的氮化硅层212的N/Si组成比为1.00或更大且小于1.33,并且氮化硅层212包含氯。图7是用于解释氮化硅层212的沉积条件的工艺气体中的氨/六氯乙硅烷比(下文中将称为NH<sub>3</sub>/HCD比)与氮化硅层212中的N/Si组成比之间的关系的视图。在图7中,横坐标指示NH<sub>3</sub>/HCD比,并且纵坐标指示氮化硅层212中的N/Si组成比。图7示出N/Si组成比随NH<sub>3</sub>/HCD比增加而

增加。在这个实施例中,  $\text{NH}_3/\text{HCD}$  比被设定为60或更大, 使得氮化硅层212中的N/Si组成比变为1.00或更大。而且,  $\text{NH}_3/\text{HCD}$  比被设定为小于120, 使得氮化硅层212中的N/Si组成比小于1.33。

[0058] 作为氮化硅层212中的N/Si组成比变为大约1.00的氮化硅层212的沉积条件, 可以采用例如以下条件。

[0059] 沉积温度: 550°C至650°C

[0060] HCD: 20sccm至40sccm

[0061]  $\text{NH}_3$ : 1300sccm至2700sccm

[0062] 沉积压力: 20Pa至30Pa

[0063] 作为氮化硅层212中的N/Si组成比变为大约1.10的氮化硅层212的沉积条件, 可以采用例如以下条件。

[0064] 沉积温度: 550°C至650°C

[0065] HCD: 15sccm至35sccm

[0066]  $\text{NH}_3$ : 1200sccm至2800sccm

[0067] 沉积压力: 20Pa至30Pa

[0068] 作为氮化硅层212中的N/Si组成比变为大约1.20的氮化硅层212的沉积条件, 可以采用例如以下条件。

[0069] 沉积温度: 550°C至650°C

[0070] HCD: 10sccm至30sccm

[0071]  $\text{NH}_3$ : 1000sccm至3000sccm

[0072] 沉积压力: 20Pa至30Pa

[0073] 可以通过增加/减少工艺气体中HCD和 $\text{NH}_3$ 的流速来改变氮化硅层212中的N/Si组成比。

[0074] 如在日本专利公开No.2013-84693中所公开的, 通过使用包含六氯乙硅烷(HCD)和氨( $\text{NH}_3$ )作为源气体的工艺气体形成的氮化硅层212除了硅、氮和氯还包含大量的氢。因此, 氮化硅层212可以用作用于终止像素晶体管的悬空键的氢供应源。而且, 当形成至少氮化硅层212时, 氮化硅层212中的氯的组成比可以低于氮和氢的组成比。换句话说, 氮化硅层212中的氢的组成比可以高于氮化硅层212中的氯的组成比。氮化硅层212中的氢的组成比可以高于或低于氮化硅层212中的硅和氮的组成比。由于氢是轻元素, 因此氮化硅层212中的氢不需要在氮化硅层212的化学计量组成中被考虑。

[0075] 在形成绝缘膜210之后, 在外围晶体管的栅极电极121和栅极电极122的侧表面上形成侧壁215。首先, 如图4B中所示, 通过使用光致抗蚀剂等在绝缘膜210上形成掩模图案410。掩模图案410被形成为覆盖像素区域1中用作光电转换部分11的区域101的至少一部分。由于掩模图案410覆盖区域101的至少一部分, 因此氮化硅层212在区域101的至少一部分上具有1.00或更大且小于1.33的N/Si组成比并且包含氯的残留物。在这个实施例中, 掩模图案410覆盖包括区域101、103、104和105的像素区域1, 并且在外围电路区域2中具有开口。然后, 蚀刻(回蚀刻)掩模图案410的开口中的绝缘膜210。通过在蚀刻之后移除掩模图案410, 形成覆盖外围晶体管的栅极电极121和122的侧表面的侧壁215, 如图4C中所示。侧壁215可以是氧化硅层213和氮化硅层214(第三氮化硅层)的堆叠。氧化硅层213是绝缘膜210

的氧化硅层211的一部分，并且氮化硅层214是绝缘膜210的氮化硅层212的一部分。因此，氮化硅层214和氮化硅层212在N/Si组成比和氯浓度方面彼此相等。

[0076] 形成侧壁215的蚀刻使区域108中将要形成杂质区域125和127的区域暴露。而且，在这个蚀刻步骤中，用于形成图2A中示出的电阻元件110的区域暴露。

[0077] 在形成侧壁215的蚀刻期间，因为掩模图案410覆盖区域101，所以绝缘膜210在区域101上方的一部分保留。这抑制了对光电转换部分11的蚀刻损坏，并且使得可以减少在光电转换部分11中产生的噪声。而且，由于掩模图案410覆盖栅极电极111和112以及区域103和104，因此在沟道区域141和142以及像素晶体管的源极/漏极区域上方形成的绝缘膜210保留。这抑制了对像素晶体管的蚀刻损坏，并且使得可以减少像素晶体管中产生的噪声。

[0078] 在形成侧壁215的蚀刻中，在区域108中用于形成杂质区域125和127的区域暴露之后，沿着侧壁215的侧表面形成自对准的重掺杂的杂质区域125和127。形成覆盖像素区域1和外围pMOSFET的掩模图案，并且通过使用这个掩模图案以及栅极电极121和侧壁215作为掩模，通过离子注入等注入n型杂质。因此，形成外围nMOSFET的杂质区域125。此外，形成覆盖像素区域1和外围nMOSFET的掩模图案，并且通过使用这个掩模图案以及栅极电极122和侧壁215作为掩模，通过离子注入等注入p型杂质。因此，形成外围pMOSFET的杂质区域127。杂质区域125和杂质区域127的形成次序是任意次序。当形成具有LDD结构的重掺杂的杂质区域125和127时，剂量可以是 $5 \times 10^{14}$ 至 $5 \times 10^{16}$  (离子/cm<sup>2</sup>)，并且也可以是 $1 \times 10^{15}$ 至 $1 \times 10^{16}$  (离子/cm<sup>2</sup>)。形成杂质区域125和127时的剂量高于形成上述杂质区域126和128时的剂量。因此，杂质区域125和127中的杂质浓度变得高于杂质区域126和128中的杂质浓度。

[0079] 当形成杂质区域125和杂质区域127中的至少一个时，可以同时将杂质注入到用于形成电阻元件110的区域中。因此，形成作为扩散电阻的电阻元件110。形成杂质区域126和128时的剂量降低杂质浓度，因此可能无法将电阻元件110的电阻值降低到实用范围。另一方面，形成杂质区域125和127时的剂量可以形成具有实际电阻值的电阻元件110的杂质区域。因此，通过形成侧壁215的蚀刻来暴露用于形成电阻元件110的区域，并且在将杂质注入到杂质区域125或127中的同时形成电阻元件110的杂质区域。

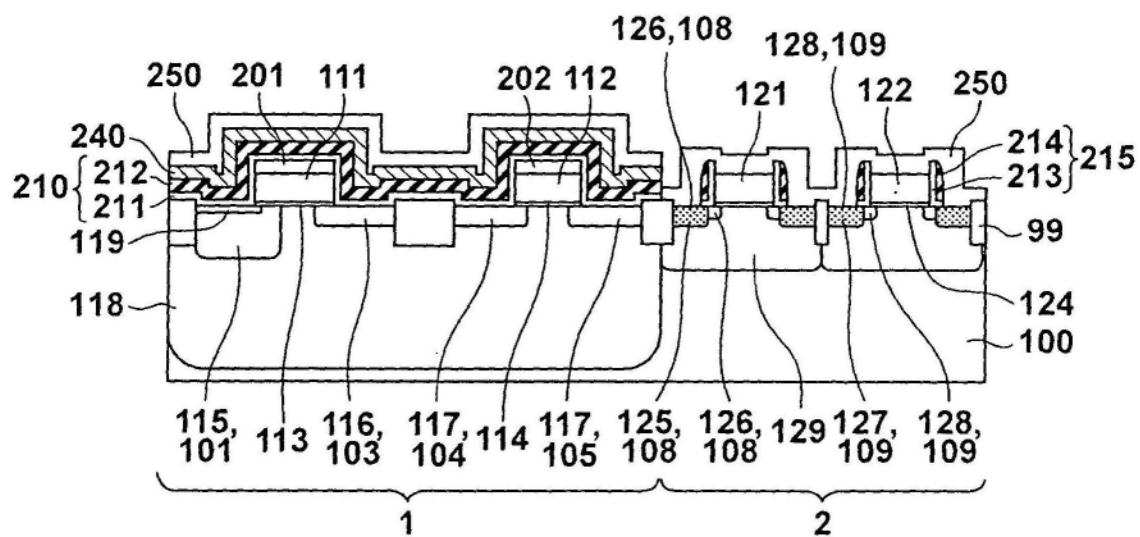

[0080] 在形成外围晶体管的LDD结构之后，如图5A中所示，保护膜240被形成为覆盖像素区域1和外围电路区域2。保护膜240由氧化硅等制成，并且具有大约30nm或更大且130nm或更小的厚度。在形成保护膜240之后，通过使用光致抗蚀剂等形成覆盖像素区域1的掩模图案420。在形成掩模图案420之后，蚀刻掩模图案420的开口中的保护膜240。这种蚀刻移除保护膜240的位于区域108和109上方的那些部分，以及保护膜240的位于栅极电极121和栅极电极122上方的那些部分。在这个步骤中，保护膜240的位于像素区域1和电阻元件110上方的那些部分留下。在蚀刻保护膜240之后，覆盖栅极电极121和栅极电极122的上表面的绝缘层203和绝缘层204被移除。绝缘层203和204的这种蚀刻可以与保护膜240的蚀刻同时或独立地执行。在蚀刻保护膜240以及绝缘层203和204之后移除掩模图案420。

[0081] 随后，如图5B中所示，通过溅射或CVD形成金属膜250以覆盖基板100。金属膜250被形成为与栅极电极121和栅极电极122以及区域108和区域109的上表面接触，并且包含将栅极电极121和栅极电极122以及区域108和区域109的上表面硅化的金属。金属膜250与未被硅化的电阻元件110和像素区域1上方的保护膜240接触。金属膜250可以具有包含用于硅化的金属和抑制金属氧化的金属化合物的多层结构。例如，金属膜250也可以是钴和用于抑制

钴的氧化的氮化钛的多层膜。

[0082] 在形成金属膜250之后,通过将基板100加热到大约500℃,使金属膜250与和金属膜250接触的栅极电极121和栅极电极122以及区域108和区域109反应。因此,形成处于单硅化物(monosilicide)状态的硅化物层132、133、134和135。之后,移除位于保护膜240和侧壁215上的未反应的金属膜250。而且,如果在金属膜250中形成用于抑制金属氧化的金属化合物层,那么也移除这个金属化合物层。在移除未反应的金属膜250之后,将基板100加热到大约800℃,这个温度高于第一硅化中使用的温度,由此将硅化物层132、133、134和135从单硅化物状态改变为二硅化物(disilicide)状态。在这个实施例中,在不同温度下执行两次加热。但是,也可以通过执行一次加热来形成硅化物层132、133、134和135。可以根据例如用于形成硅化物的金属的类型适当地选择硅化条件。

[0083] 在硅化步骤中,没有硅化物层在保护膜240保留的电阻元件110和像素区域1中形成,因为金属膜250不与基板100和栅极电极接触。保护膜240因此用作硅化物块。由于硅化物层可以在像素区域1中造成噪声,因此在硅化期间像素区域1覆盖有保护膜240。特别地,不对用作光电转换部分11的区域101、用作用于检测电荷的节点14的区域103以及用作放大元件15的源极/漏极区域的区域104和105执行硅化。电阻元件110也受到保护膜240的保护,因为电阻值可能变得太小。在形成硅化物层132、133、134和135之后,可以移除保护膜240。但是,保护膜240也可以保留,以便避免对像素区域1的不必要的损坏。在这个实施例中,保护膜240留下,如图5C中所示。

[0084] 在形成硅化物层132、133、134和135之后,如图6A中所示,形成包括氧化硅层221和氮化硅层222的绝缘膜220。绝缘膜220覆盖栅极电极111、112、121和122的上表面、侧壁215、用作像素晶体管和外围晶体管的源极/漏极区域的区域103、104、105、108和109,以及区域101。

[0085] 绝缘膜220是氧化硅层221和氮化硅层222的多层膜。氧化硅层221和氮化硅层222被形成为彼此接触。形成绝缘膜220的步骤包括形成氧化硅层221的步骤和形成氮化硅层222的步骤。氮化硅层222的厚度可以等于或大于氧化硅层221的厚度。氮化硅层222的厚度可以是氧化硅层221的厚度的两倍或更多。例如,氧化硅层221的厚度可以是10nm或更大且30nm或更小,并且氮化硅层222的厚度可以是20nm或更大且100nm或更小。

[0086] 氧化硅层221通过其中工艺气体的压力(沉积压力)是200Pa或更大且600Pa或更小的亚大气压CVD(SA-CVD)作为热CVD形成,其中工艺气体包含诸如TEOS之类的源气体。在这个步骤中,沉积温度(基板温度)可以是400℃或更高且500℃或更低。因此,氧化硅层211和221都可以通过热CVD形成。

[0087] 氮化硅层222通过使用包含例如氨( $NH_3$ )和六氯乙硅烷(HCD)作为源气体的工艺气体通过LPCVD形成。在这个步骤中,工艺气体的压力(沉积压力)是20Pa或更大且200Pa或更小,并且沉积温度(基板温度)可以是500℃或更高且800℃或更低。

[0088] 氮化硅层222还可以用作氯供应源,用于向外围晶体管稳定地供应氯。厚氮化硅层222可以包含大量的氯,并且薄氧化硅层221可以适当地传送(transmit)氯。而且,如上所述的通过使用包含六氯乙硅烷(HCD)和氨( $NH_3$ )作为源气体的工艺气体形成的氮化硅层222包含大量的氯。这使得可以形成具有优异噪声特性的外围晶体管。

[0089] 在形成绝缘膜220之后,如图6A中所示,通过使用光致抗蚀剂等形成掩模图案430,

以覆盖绝缘膜220的位于外围电路区域2中的那部分。然后,通过掩模图案430的开口移除氮化硅层212的布置在像素区域1中的那些部分。氮化硅层212的待移除部分包括氮化硅层212的位于光电转换部分11、转移元件12、电容元件13、放大元件15、复位元件16和选择元件17上方的那些部分。在这个步骤中,氧化硅层221可以用作在蚀刻掉覆盖像素区域1的氮化硅层222时的蚀刻停止件。氧化硅层221还可以用作保护像素区域1免受蚀刻损坏的保护层。布置在像素区域1中的至少光电转换部分11上方的氮化硅层222被移除。

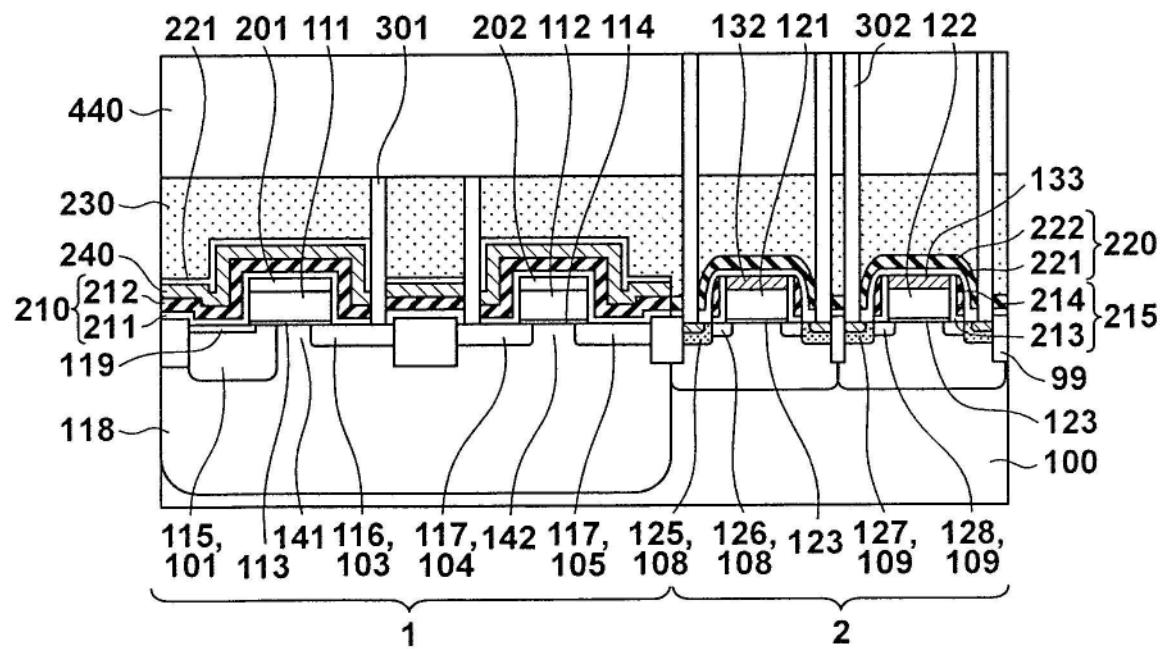

[0090] 随后,形成绝缘膜230以覆盖像素区域1和外围电路区域2。绝缘膜230是通过诸如HDP(高密度等离子体)CVD之类的等离子体CVD沉积的单层氧化硅膜。绝缘膜230可以由诸如BPSG膜、BSG膜或PSG膜之类的任意材料形成。此外,绝缘膜230不限于单层膜,并且可以是多层膜。

[0091] 然后,如图6B中所示,绝缘膜230的表面被平坦化。作为平坦化方法,可以使用例如CMP(化学机械抛光)、回流或回蚀。也可以通过组合这些方法来使用它们。平坦化之前的绝缘膜230的厚度可以是例如200nm或更大且1700nm或更小。在这个实施例中,通过上述步骤移除氮化硅层222的位于像素区域1上方的那些部分,并且这减小了绝缘膜230下方的像素区域1和外围电路区域2的高度之间的差异。因而,平坦化的绝缘膜230的厚度可以减小到1000nm或更小。例如,绝缘膜230的厚度也可以是450nm或更大且850nm或更小。通过减小绝缘膜230的厚度,可以减小电阻并增加接触插塞的灵敏度。平坦化的绝缘膜230的厚度也可以大于绝缘膜210和绝缘膜220的厚度。

[0092] 在绝缘膜230的平坦化之后,形成用于将像素晶体管和外围晶体管电连接到互连件的导电构件311、312、313和314。首先,在像素区域1中,通过覆盖绝缘膜230的掩模图案(诸如光致抗蚀剂)的开口,通过各向异性蚀刻在绝缘膜230中形成孔,由此形成用于形成导电构件311的接触孔301。当形成接触孔301时,绝缘膜210的氮化硅层212可以被用作像素区域1中的蚀刻停止件。接触孔301被形成为延伸通过绝缘膜230、氧化硅层221、保护膜240、氮化硅层212和氧化硅层211。接触孔301暴露电容元件13、放大元件15、复位元件16和选择元件17的源极/漏极区域,以及参考接触区域102。

[0093] 与形成接触孔301并行地,形成用于暴露电容元件13、放大元件15、复位元件16和选择元件17的栅极电极的接触孔303。用于形成导电构件313的接触孔303延伸通过绝缘膜230、氧化硅层221、保护膜240、氮化硅层212和氧化硅层211。用于形成导电构件313的接触孔进一步延伸通过绝缘层201和202。为了减小接触插塞的接触电阻,还可以通过接触孔将杂质注入到基板100的杂质区域和栅极电极中。

[0094] 在形成接触孔301之前,如上所述,移除位于像素区域1上方的氮化硅层222。因此,在氮化硅层212上方没有将用作蚀刻停止件的氮化硅层。因此,当形成接触孔301时,可以抑制除氮化硅层212以外的氮化硅层以防止阻止形成接触孔301。

[0095] 然后,如图6C中所示,在外围电路区域2中,通过使用覆盖绝缘膜230并且在用于形成接触孔302和304的区域中具有开口的掩模图案440,通过各向异性干法蚀刻在绝缘膜230中形成孔。因此,形成用于形成导电构件312和314的接触孔302和304。当形成接触孔302时,绝缘膜220的氮化硅层222可以用作外围电路区域2中的蚀刻停止件。接触孔302和304被形成为延伸通过绝缘膜230、氮化硅层222和氧化硅层221。接触孔302暴露位于用作外围晶体管的源极-漏极区域的区域108和109中的硅化物层134和135。与形成接触孔302并行地,形

成了形成导电构件314并暴露栅极电极121和栅极电极122的硅化物层132和硅化物层133的接触孔304。

[0096] 在形成接触孔301、302、303和304之后,通过在接触孔301、302、303和304中填充诸如金属之类的导体来形成用作接触插塞的导电构件311、312、313和314。这些导电构件可以立即填充在接触孔301、302、303和304中。

[0097] 在像素区域1中形成接触孔301和303并填充导电构件311和313的步骤以及在外围电路区域2中形成接触孔302和304并填充导电构件312和314的步骤也可以是不同的步骤。通过在像素区域1和外围电路区域2中使用不同的接触插塞形成步骤,可以抑制包含在硅化物层132、133、134和135中的金属经由接触孔301和303污染像素区域1中的杂质区域。形成接触孔和通过填充导电构件形成接触插塞的步骤可以首先在像素区域1或外围电路区域2中的任一个中执行。

[0098] 通过上述步骤获得图2A和图2B中示出的结构。之后,通过形成布线图案、滤色器、微透镜等来完成成像装置1000。在外围晶体管覆盖有绝缘膜220的状态下,还可以添加用于促进对像素晶体管和外围晶体管的氢供应的氢退火过程。氢退火过程意指通过在氢气气氛中加热基板100来在基板100的表面上执行氢终止(termination)的过程。也可以在形成导电构件311、312、313和314之后形成布线图案之后执行氢退火过程。

[0099] 以上已经解释了根据本发明的第一实施例,但是本发明当然不限于第一实施例,并且可以在不脱离本发明的精神和范围的情况下对上述第一实施例进行适当的改变和组合。例如,在上述第一实施例中,已经以半导体装置的成像装置为例解释了本发明。但是,本发明不限于成像装置,并且可应用于包括绝缘栅型场效应晶体管的任何半导体装置,诸如算术运算装置、存储装置、控制装置、信号处理装置、检测装置和显示装置。

[0100] 下面将解释结合成像装置1000的设备,作为根据上述第一实施例的成像装置的应用示例。设备的概念不仅包括诸如主要目的是成像的相机之类的电子设备,而且还包括作为辅助功能包括成像功能的设备(例如,个人计算机、诸如便携式终端之类的电子设备,以及诸如汽车、轮船或飞机之类的运输设备)。当在运输设备中使用根据本发明实施例的成像装置1000时,可以减少针对诸如太阳光之类的强光的特性的变化。因而,在设计、制造和销售运输设备时,使用根据本发明实施例的成像装置在增加运输设备的价值方面是有效的。结合成像装置1000的设备包括根据本发明、被例示为上述第一实施例的成像装置1000,以及用于基于从成像装置1000输出的信号处理信息的处理单元。这个处理单元可以包括用于处理作为图像数据的数字数据的处理器。处理器可以基于来自成像装置1000的具有焦点检测功能的像素的信号来计算散焦量,并且基于计算结果执行控制成像透镜的聚焦的处理。用于生成上面提到的图像数据的A/D转换器可以安装在基板100上。还可以将包括A/D转换器的基板堆叠在基板100上并使用这个堆叠作为成像装置1000,或者与成像装置1000独立地形成A/D转换器。在结合成像装置1000的设备中,从成像装置1000获得的数据可以显示在设备的显示装置上或存储在设备的存储装置中。此外,在结合成像装置1000的设备中,可以基于从成像装置1000获得的数据来驱动设备的诸如马达之类的机械装置。

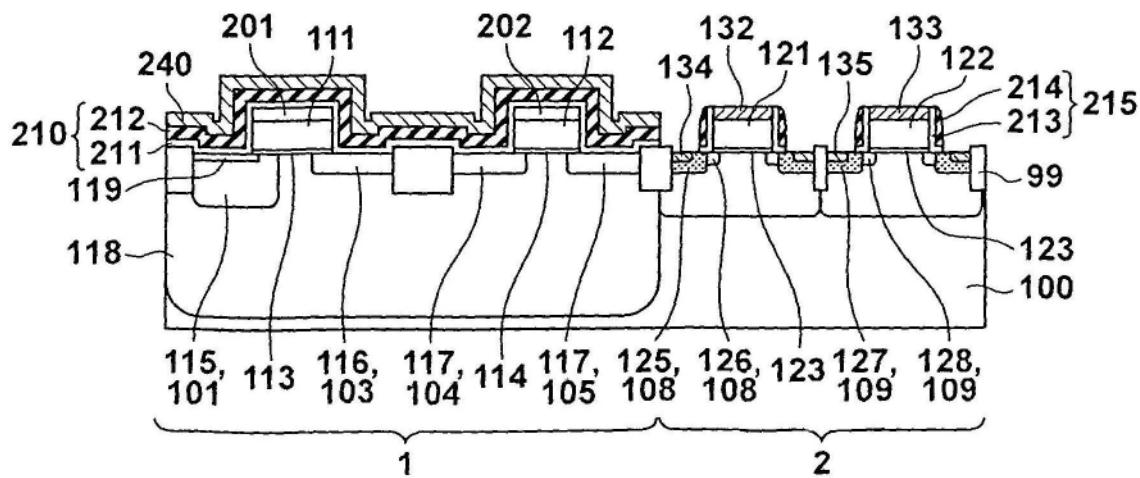

[0101] 下面将参考图8解释本发明第二实施例的制造方法。第二实施例与第一实施例的不同之处在于使用波导来增加进入光电转换部分11的光量,第二实施例在其它方面与第一实施例相同。在第二实施例中,在光电转换部分11上留下氮化硅层222,并且使用氮化硅层

223作为用于形成波导的蚀刻停止膜。

[0102] 在形成绝缘膜220之后,通过使用光致抗蚀剂等形成掩模图案,以覆盖绝缘膜220的位于像素区域1的一部分上方的那部分,以及绝缘膜220的位于外围电路区域2上方的那部分。然后,通过掩模图案的开口蚀刻掉氮化硅层212的位于像素区域1上方的那部分。因此,氮化硅层223被形成为位于像素区域1中的至少光电转换部分11的上方。

[0103] 然后,形成多个层间介电膜231、接触插塞、包括通孔插塞的第一互连件层315和第二互连件层316。通过交替堆叠氧化硅层和氮化硅层来形成多个层间介电膜231。多个层间介电膜231可用作波导的包层。第一互连件层315和第二互连件层316可以通过使用包含铜作为主要成分的材料通过镶嵌(damascene)方法形成,但是也可以通过使用诸如铝之类的另一种材料来形成。

[0104] 随后,在多个层间介电膜231中形成开口501。例如,通过在多个层间介电膜231上形成在与光电转换部分11对应的区域中具有开口的掩模图案并通过使用掩模图案作为掩模蚀刻多个层间介电膜231来形成开口501。这种蚀刻是例如各向异性蚀刻。更具体而言,对多个层间介电膜231执行等离子体蚀刻,直到露出氮化硅层223。氮化硅层223是用于在蚀刻期间减少对光电转换部分11的等离子体损坏的膜,并且还可以用作蚀刻停止膜。

[0105] 然后,在开口501中填充折射率高于作为包层的多个层间介电膜231的折射率的透明材料,由此形成将成为用于将光引导到光电转换部分11的波导的芯(core)的部分。在这个实施例中,在开口501中形成折射率高于作为多个层间介电膜231的主要材料的氧化硅的折射率的氮化硅,但是也可以使用氧化硅。更具体而言,通过HDP-CVD(高密度等离子体-CVD)在整个表面上沉积氮化硅,由此在开口501中填充氮化硅。在除开口501以外的部分中形成的氮化硅可以通过例如CMP(化学机械抛光)或等离子体蚀刻被移除。之后,通过形成布线图案、滤色器、微透镜等来完成成像装置。

[0106] 虽然已经参考示例性实施例描述了本发明,但是应当理解的是,本发明不限于所公开的示例性实施例。所附权利要求的范围应被赋予最广泛的解释,以便涵盖所有这种修改以及等同的结构和功能。

图1A

图1B

图2A

图2B

图3A

图3B

图4A

图4B

图4C

图5A

图5B

图5C

图6A

图6B

图6C

图7

图8