(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-32541

(P2006-32541A)

(43) 公開日 平成18年2月2日(2006.2.2)

| (51) Int.CI.                  | F 1        | テーマコード (参考) |

|-------------------------------|------------|-------------|

| <b>HO1L 29/78 (2006.01)</b>   | HO1L 29/78 | 301G 5FO33  |

| <b>HO1L 21/8247 (2006.01)</b> | HO1L 29/78 | 371 5FO83   |

| <b>HO1L 29/792 (2006.01)</b>  | HO1L 27/10 | 434 5F1O1   |

| <b>HO1L 29/788 (2006.01)</b>  | HO1L 21/90 | C 5F140     |

| <b>HO1L 27/115 (2006.01)</b>  |            |             |

審査請求 未請求 請求項の数 4 O L (全 9 頁) 最終頁に続く

|           |                              |          |                                                 |

|-----------|------------------------------|----------|-------------------------------------------------|

| (21) 出願番号 | 特願2004-207205 (P2004-207205) | (71) 出願人 | 503121103<br>株式会社ルネサステクノロジ<br>東京都千代田区丸の内二丁目4番1号 |

| (22) 出願日  | 平成16年7月14日 (2004.7.14)       | (74) 代理人 | 100082175<br>弁理士 高田 守                           |

|           |                              | (74) 代理人 | 100106150<br>弁理士 高橋 英樹                          |

|           |                              | (72) 発明者 | 角野 潤<br>東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内        |

|           |                              | (72) 発明者 | 清水 悟<br>東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内        |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【要約】

【課題】 酸化膜と窒化膜の多層膜よりなるサイドウォールを有する半導体装置において、サイドウォールを構成する酸化膜がコントラクトエッチングの際にエッチングされてゲート電極の側面が露出するのを防ぐことができる半導体装置を得る。

【解決手段】 半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極上に形成された第1の窒化膜と、ゲート電極及び第1の窒化膜の側面に順番に形成された第1の酸化膜、第2の窒化膜、第2の酸化膜及び第3の窒化膜からなるサイドウォールとを有し、第1の窒化膜は、上部の外径が下部の外径よりも小さく、第1の酸化膜のゲート電極の側面にある部分は、上面から見て第2の窒化膜で覆われ、第2の酸化膜のゲート電極の側面にある部分は、上面から見て第3の窒化膜で覆われている。

【選択図】 図3

**【特許請求の範囲】****【請求項 1】**

半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成されたゲート電極と、

前記ゲート電極上に形成された第1の窒化膜と、

前記ゲート電極及び前記第1の窒化膜の側面に順番に形成された第1の酸化膜、第2の窒化膜、第2の酸化膜及び第3の窒化膜からなるサイドウォールとを有し、

前記第1の窒化膜は、上部の外径が下部の外径よりも小さく、

前記第1の酸化膜の前記ゲート電極の側面にある部分は、上面から見て前記第2の窒化膜で覆われ、

前記第2の酸化膜の前記ゲート電極の側面にある部分は、上面から見て前記第3の窒化膜で覆われていることを特徴とする半導体装置。

**【請求項 2】**

前記第1の窒化膜は、上面の角が丸まっていることを特徴とする請求項1に記載の半導体装置。

**【請求項 3】**

前記第1の窒化膜は、上方にいくほど外径が小さくなるテーパー形状であることを特徴とする請求項1に記載の半導体装置。

**【請求項 4】**

前記第1の窒化膜は、上部の外径が下部の外径に比べて階段状に小さくなることを特徴とする請求項1に記載の半導体装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、多層膜よりなるサイドウォールを有する半導体装置に関するものである。

**【背景技術】****【0002】**

近年、トランジスタやメモリセル等の半導体装置において、微細化に伴い、ゲート電極とコンタクトの間隔を狭くする傾向にある。このため、ゲート電極上にコンタクトが乗り上げるSAC (Self Aligned Contact) 構造が用いられる。このSAC構造では、酸化膜からなる層間絶縁膜との選択比を確保するため、ゲート上のハードカバーやサイドウォールに窒化膜を用いる。

**【0003】**

また、フラッシュメモリでは、ゲート - コンタクト間に約20Vの高い電圧が印加されるため、耐圧向上が課題となっている。特に、サイドウォールとして窒化膜のみを用いた場合、ゲートを負バイアスにすると、ゲート近傍の窒化膜にホールが蓄積され、実効的な耐圧が低下するという問題があった。

**【0004】**

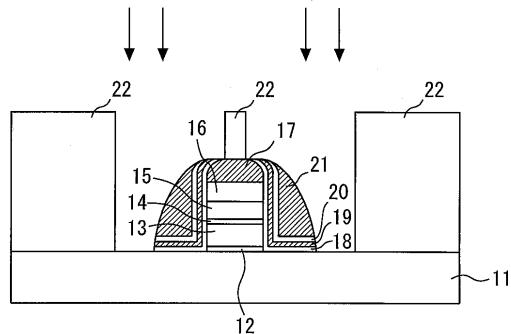

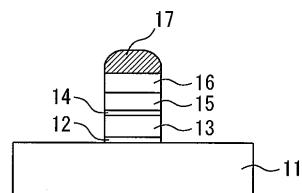

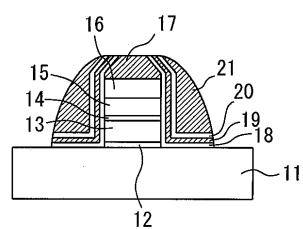

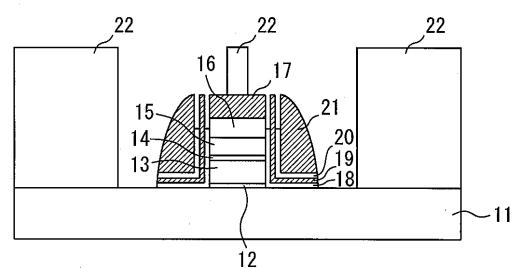

そこで、ゲートとサイドウォールの窒化膜の間にONO膜を設けた半導体装置が提案されている（例えば、特許文献1参照）。この従来の半導体装置の断面図を図9に示す。半導体基板11上にゲート絶縁膜12が形成されている。そして、ゲート絶縁膜12上に、ゲート電極として、ポリシリコン膜13、ONO膜14、ポリシリコン膜15、WSi膜16が形成されている。また、ゲート電極上にSiN膜17が形成され、ゲート電極及びSiN膜17の側壁には、順番に形成されたSiO<sub>2</sub>膜18、SiN膜19、SiO<sub>2</sub>膜20及びSiN膜21からなるサイドウォールが形成されている。

**【0005】**

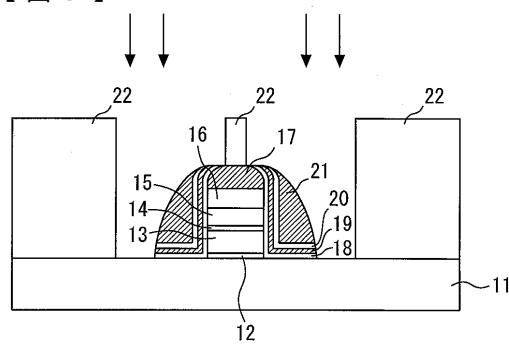

従来の半導体装置を用いてコンタクトエッチングを行った状態を図10に示す。半導体装置を覆うようにSiO<sub>2</sub>からなる層間絶縁膜22を形成し、この層間絶縁膜22をフォトリソグラフィ等により異方性エッチングする。この際、エッチングの選択性を持たせることでSiN膜21はエッチングされないようにする。これにより、ゲート電極上にコン

タクトが乗り上げた S A C 構造を形成することができる。

【 0 0 0 6 】

【特許文献 1】特開 2 0 0 2 - 2 5 2 2 3 2 号公報

【発明の開示】

【発明が解決しようとする課題】

【 0 0 0 7 】

しかし、従来の半導体装置では、サイドウォールを構成する酸化膜と窒化膜の多層膜が垂直に形成されているため、サイドウォールを構成する酸化膜がコンタクトエッチングの際にエッチングされて、ゲート電極の側面が露出するという問題があった。

【 0 0 0 8 】

本発明は、上述のような課題を解決するためになされたもので、その目的は、酸化膜と窒化膜の多層膜よりなるサイドウォールを有する半導体装置において、サイドウォールを構成する酸化膜がコンタクトエッチングの際にエッチングされてゲート電極の側面が露出するのを防ぐことができる半導体装置を得るものである。

【課題を解決するための手段】

【 0 0 0 9 】

本発明に係る半導体装置は、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極上に形成された第 1 の窒化膜と、ゲート電極及び第 1 の窒化膜の側面に順番に形成された第 1 の酸化膜、第 2 の窒化膜、第 2 の酸化膜及び第 3 の窒化膜からなるサイドウォールとを有し、第 1 の窒化膜は、上部の外径が下部の外径よりも小さく、第 1 の酸化膜のゲート電極の側面にある部分は、上面から見て第 2 の窒化膜で覆われ、第 2 の酸化膜のゲート電極の側面にある部分は、上面から見て第 3 の窒化膜で覆われている。本発明のその他の特徴は以下に明らかにする。

【発明の効果】

【 0 0 1 0 】

本発明により、酸化膜と窒化膜の多層膜よりなるサイドウォールを有する半導体装置において、サイドウォールを構成する酸化膜がコンタクトエッチングの際にエッチングされてゲート電極の側面が露出するのを防ぐことができる。

【発明を実施するための最良の形態】

【 0 0 1 1 】

実施の形態 1 .

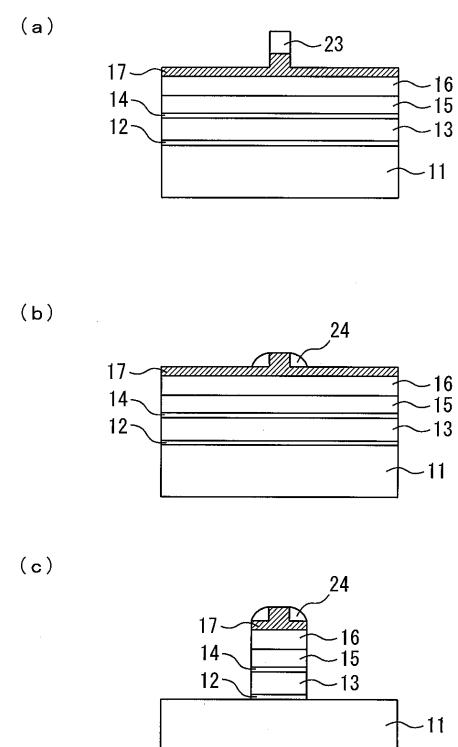

本発明の実施の形態 1 に係る半導体装置の製造工程について図 1 及び図 2 を用いて説明する。

【 0 0 1 2 】

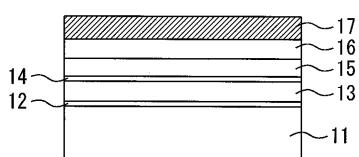

まず、図 1 ( a ) に示すように、半導体基板 1 1 上に、ゲート絶縁膜 1 2 、ポリシリコン膜 1 3 、 O N O 膜 1 4 、ポリシリコン膜 1 5 、 W S i 膜 1 6 、及び、第 1 の窒化膜である S i N 膜 1 7 を順番に形成する。

【 0 0 1 3 】

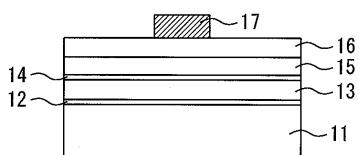

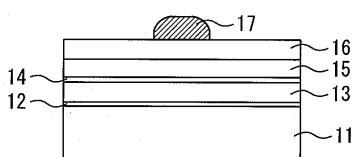

次に、図 1 ( b ) に示すように、 S i N 膜 1 7 をフォトリソグラフィ等によりパターニングする。そして、図 1 ( c ) に示すように、エッチングにより S i N 膜 1 7 の上面の角を丸くする。

【 0 0 1 4 】

次に、図 2 ( a ) に示すように、 S i N 膜 1 7 をマスクにして、 W S i 膜 1 6 、ポリシリコン膜 1 5 、 O N O 膜 1 4 、ポリシリコン膜 1 3 及びゲート絶縁膜 1 2 を異方性エッチングする。これにより、ポリシリコン膜 1 3 、ポリシリコン膜 1 5 及び W S i 膜 1 6 からなるゲート電極が形成される。より具体的には、ポリシリコン膜 1 3 がフローティングゲートであり、ポリシリコン膜 1 5 がコントロールゲートである。

【 0 0 1 5 】

次に、図 2 ( b ) に示すように、全面に、第 1 の酸化膜である S i O<sub>2</sub> 膜 1 8 、第 2 の窒化膜である S i N 膜 1 9 、第 2 の酸化膜である S i O<sub>2</sub> 膜 2 0 、及び、第 3 の窒化膜で

10

20

30

40

50

ある SiN 膜 21 を順番に形成する。ここで、SiO<sub>2</sub> 膜 18 及び SiO<sub>2</sub> 膜 20 として、TEOS 膜又は熱酸化膜を用いることができる。また、SiN 膜 19 及び SiN 膜 21 は CVD 法により形成することができる。なお、SiO<sub>2</sub> 膜 18 を形成する前に、ゲート電極の側壁を保護するために、熱酸化又はラジカル酸化によりゲート電極の側壁に酸化膜を形成してもよい。ただし、ラジカル酸化は酸化力が強く、ゲート電極全体と半導体基板 11 を酸化膜で覆うように酸化膜を形成できるため、SiO<sub>2</sub> 膜 18 及び SiO<sub>2</sub> 膜 20 をラジカル酸化により形成してもよい。

#### 【0016】

次に、図 2(c) に示すように、全面エッチバックにより、ゲート電極及び SiN 膜 17 の側壁にサイドウォールを形成する。このサイドウォールは、SiO<sub>2</sub> 膜 18、SiN 膜 19、SiO<sub>2</sub> 膜 20 及び SiN 膜 21 からなる。10

#### 【0017】

このように、ゲート電極と、サイドウォールの SiN 膜 21 との間に、SiO<sub>2</sub> 膜 18、SiN 膜 19 及び SiO<sub>2</sub> 膜 20 からなる ONO 膜を設ける。この ONO 膜により、ゲート電極に負バイアスを印加した場合でも、窒化膜中の電気伝導を支配している正孔の流れを阻止し、ゲート電極の特に WSi 膜 16 近傍の窒化膜にホールが蓄積されるのを防ぎ、実効的な耐圧の低下を防ぐことができる。

#### 【0018】

ただし、ゲート電極 コンタクト間に電圧が印加された場合でも FN(Fowler-Nordheim) トンネルが起こらないように、ゲート電極側にある SiO<sub>2</sub> 膜 18 の膜厚は 50 以上、好ましくは 70 以上に設定する必要がある。20

#### 【0019】

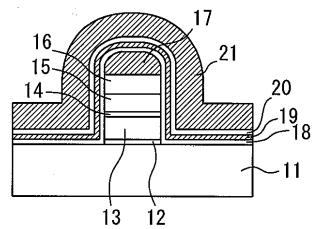

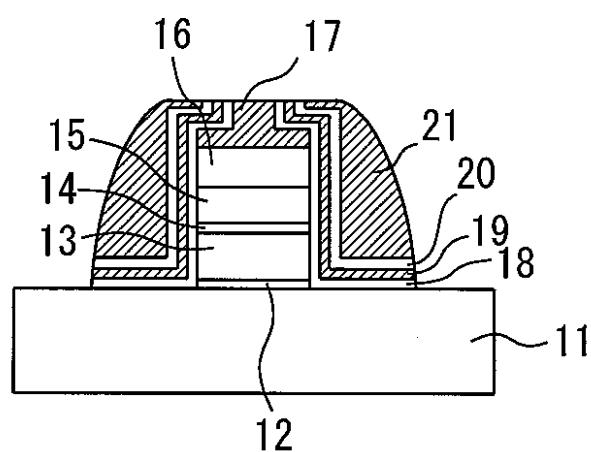

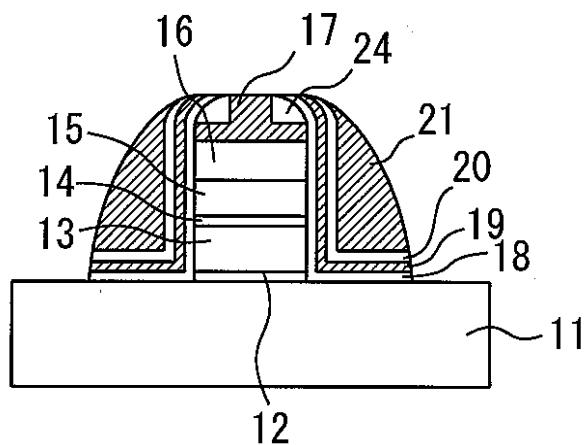

実施の形態 1 に係る半導体装置を用いてコンタクトエッティングを行った状態を図 3 に示す。半導体装置を覆うように SiO<sub>2</sub> からなる層間絶縁膜 22 を形成し、この層間絶縁膜 22 をフォトリソグラフィ等により異方性エッティングする。この際、エッティングの選択性を持たせることで SiN 膜 21 はエッティングされないようにする。これにより、ゲート電極上にコンタクトが乗り上げた SAC 構造を形成することができる。

#### 【0020】

このコンタクトエッティングでは、酸化膜を選択的に異方性エッティングするため、サイドウォールを構成する SiO<sub>2</sub> 膜 18 及び SiO<sub>2</sub> 膜 20 もエッティングされる。しかし、SiN 膜 17 は、上面の角が丸まっていて、上部の外径が下部の外径よりも小さいため、SiO<sub>2</sub> 膜 18 のゲート電極の側面にある部分は、上面から見て SiN 膜 19 で覆われ、SiO<sub>2</sub> 膜 20 のゲート電極の側面にある部分は、上面から見て SiN 膜 21 で覆われている。これにより、コンタクトエッティングにおいて、SiO<sub>2</sub> 膜 18 及び SiO<sub>2</sub> 膜 20 は、ゲート電極の側面にある部分まではエッティングされない。30

#### 【0021】

従って、本実施の形態 1 に係る半導体装置ならば、サイドウォールを構成する酸化膜がコンタクトエッティングの際にエッティングされてゲート電極の側面が露出するのを防ぐことができる。

#### 【0022】

なお、フラッシュメモリの構造を例に挙げて説明したが、本発明は、MOS ドランジスタ等に使用しても同様の効果を奏する。40

#### 【0023】

実施の形態 2 .

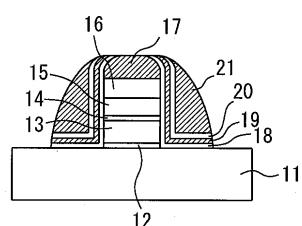

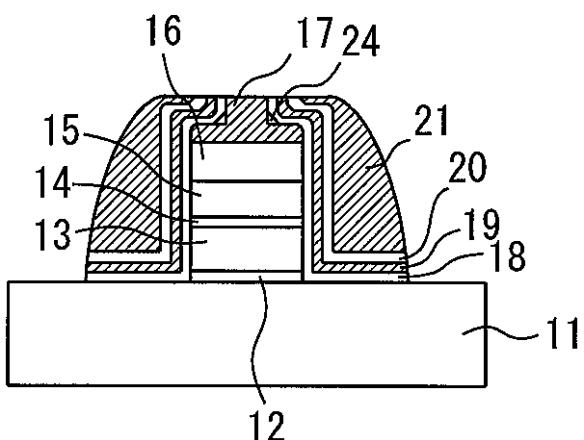

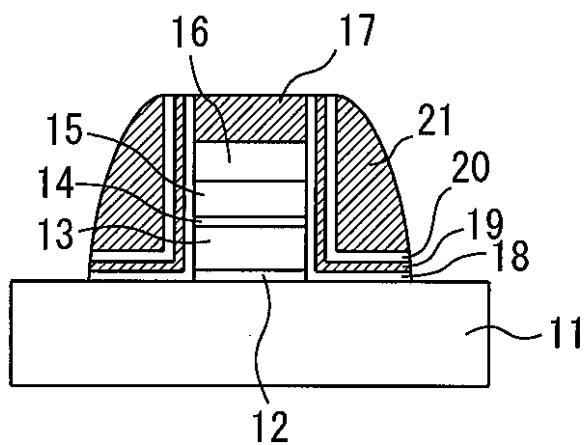

図 4 は、本発明の実施の形態 2 に係る半導体装置を示す断面図である。図 1 及び 2 と同様の構成要素には同じ番号を付し、説明を省略する。

#### 【0024】

実施の形態 2 に係る半導体装置では、第 1 の窒化膜である SiN 膜 17 が、上方にいくほど外径が小さくなるテーパー形状であり、上部の外径が下部の外径よりも小さくなっている。このため、SiO<sub>2</sub> 膜 18 のゲート電極の側面にある部分は、上面から見て SiN 50

膜 19 で覆われ、 $\text{SiO}_2$  膜 20 のゲート電極の側面にある部分は、上面から見て  $\text{SiN}$  膜 21 で覆われている。これにより、コンタクトエッチングにおいて、 $\text{SiO}_2$  膜 18 及び  $\text{SiO}_2$  膜 20 は、ゲート電極の側面にある部分まではエッチングされない。

#### 【0025】

従って、実施の形態 2 に係る半導体装置ならば、サイドウォールを構成する酸化膜がコンタクトエッチングの際にエッチングされてゲート電極の側面が露出するのを防ぐことができる。

#### 【0026】

##### 実施の形態 3 .

本発明の実施の形態 3 に係る半導体装置の製造工程について図 5 を用いて説明する。図 10 1 及び 2 と同様の構成要素には同じ番号を付し、説明を省略する。

#### 【0027】

まず、図 5 (a) に示すように、半導体基板 11 上に、ゲート絶縁膜 12、ポリシリコン膜 13、 $\text{ONO}$  膜 14、ポリシリコン膜 15、 $\text{WSi}$  膜 16、及び、第 1 の窒化膜である  $\text{SiN}$  膜 17 を順番に形成する。そして、フォトレジスト 23 により  $\text{SiN}$  膜 17 の一部を覆った状態で、 $\text{SiN}$  膜 17 を途中まで異方性エッチングする。これにより、 $\text{SiN}$  膜 17 には凸部が形成される。

#### 【0028】

次に、図 5 (b) に示すように、 $\text{SiN}$  膜 17 の上に  $\text{TEOS}$  膜 24 を形成し、全面エッチバックにより、 $\text{SiN}$  膜 17 の凸部の側壁のみに  $\text{TEOS}$  膜 24 が残るようにしてサイドウォールを形成する。図 20

#### 【0029】

次に、図 5 (c) に示すように、 $\text{SiN}$  膜 17 をエッチングして凸部及び  $\text{TEOS}$  膜 24 で覆われた部分以外を除去する。そして、残った  $\text{SiN}$  膜 17 及び  $\text{TEOS}$  膜 24 をマスクにして、 $\text{WSi}$  膜 16、ポリシリコン膜 15、 $\text{ONO}$  膜 14、ポリシリコン膜 13 及びゲート絶縁膜 12 を異方性エッチングする。これにより、ポリシリコン膜 13、ポリシリコン膜 15 及び  $\text{WSi}$  膜 16 からなるゲート電極が形成される。

#### 【0030】

そして、APM (ammonia-peroxide-mixture) 等によるウェットエッチングにより  $\text{TEOS}$  膜 24 を完全に除去して、実施の形態 1 と同様にサイドウォールを形成すると、図 6 に示すような実施の形態 3 に係る半導体装置が形成される。ただし、図 7 に示すように  $\text{TEOS}$  膜 24 を少しだけ残すか、ウェットエッチングをしないで図 8 に示すように  $\text{TEOS}$  膜 24 をそのまま残してもよい。図 30

#### 【0031】

この実施の形態 3 に係る半導体装置では、第 1 の窒化膜は、上部の外径が下部の外径に比べて階段状に小さくなっているノッチ形状であり、上部の外径が下部の外径よりも小さいため、 $\text{SiO}_2$  膜 18 のゲート電極の側面にある部分は、上面から見て  $\text{SiN}$  膜 19 で覆われ、 $\text{SiO}_2$  膜 20 のゲート電極の側面にある部分は、上面から見て  $\text{SiN}$  膜 21 で覆われている。これにより、コンタクトエッチングにおいて、 $\text{SiO}_2$  膜 18 及び  $\text{SiO}_2$  膜 20 は、ゲート電極の側面にある部分まではエッチングされない。図 40

#### 【0032】

従って、実施の形態 3 に係る半導体装置ならば、サイドウォールを構成する酸化膜がコンタクトエッチングの際にエッチングされてゲート電極の側面が露出するのを防ぐことができる。

#### 【図面の簡単な説明】

#### 【0033】

【図 1】本発明の実施の形態 1 に係る半導体装置の製造工程を示す断面図 (1) である。

【図 2】本発明の実施の形態 1 に係る半導体装置の製造工程を示す断面図 (2) である。

【図 3】本発明の実施の形態 1 に係る半導体装置を用いてコンタクトエッチングを行った状態を示す断面図である。

【図4】本発明の実施の形態2に係る半導体装置を示す断面図である。

【図5】本発明の実施の形態3に係る半導体装置の製造工程を示す断面図である。

【図6】本発明の実施の形態3に係る半導体装置を示す断面図である。

【図7】本発明の実施の形態3に係る半導体装置の別の例を示す断面図である。

【図8】本発明の実施の形態3に係る半導体装置の更に別の例を示す断面図である。

【図9】従来の半導体装置の断面図を示す断面図である。

【図10】従来の半導体装置を用いてコンタクトエッチングを行った状態を示す断面図である。

#### 【符号の説明】

##### 【0034】

- 11 半導体基板

- 12 ゲート絶縁膜

- 13 ポリシリコン膜(ゲート電極)

- 15 ポリシリコン膜(ゲート電極)

- 16 WSi膜(ゲート電極)

- 17 SiN膜(第1の窒化膜)

- 18 SiO<sub>2</sub>膜(サイドウォール)

- 19 SiN膜(サイドウォール)

- 20 SiO<sub>2</sub>膜(サイドウォール)

- 21 SiN膜(サイドウォール)

10

20

【図1】

(a)

(b)

(c)

【図2】

(a)

(b)

(c)

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

**H 0 1 L 21/768 (2006.01)**

F ターム(参考) 5F033 HH04 HH28 KK01 MM07 MM08 MM15 QQ08 QQ09 QQ10 QQ16

QQ19 QQ28 QQ31 QQ37 RR04 RR06 TT08 VV06 VV16 XX31

5F083 EP23 EP55 EP56 JA04 JA35 JA53 MA03 MA19

5F101 BA07 BA29 BA36 BB05 BB08 BD50

5F140 AA26 AC32 BF04 BF14 BF21 BF28 BF35 BG10 BG12 BG14

BG22 BG38 BG39 BG50 BG52 BG53 BJ28 BK27 CA07 CC03

CE20