(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-222296

(P2004-222296A)

(43) 公開日 平成16年8月5日(2004.8.5)

(51) Int.Cl.<sup>7</sup>H03K 5/00

G06F 1/06

F 1

H03K 5/00

G06F 1/04J

310A

テーマコード(参考)

5B079

審査請求 未請求 請求項の数 1 O L (全 12 頁)

(21) 出願番号 特願2004-7252 (P2004-7252)

(22) 出願日 平成16年1月14日 (2004.1.14)

(31) 優先権主張番号 10/346689

(32) 優先日 平成15年1月15日 (2003.1.15)

(33) 優先権主張国 米国(US)

(71) 出願人 399117121

アジレント・テクノロジーズ・インク

AGILENT TECHNOLOGIE

S, INC.

アメリカ合衆国カリフォルニア州パロアル

ト ページ・ミル・ロード 395

395 Page Mill Road

Palo Alto, California

U. S. A.

(74) 代理人 100075513

弁理士 後藤 政喜

(74) 代理人 100084537

弁理士 松田 嘉夫

最終頁に続く

(54) 【発明の名称】クロック信号発生システム

## (57) 【要約】

【課題】一のクロック信号の周波数の分数である周波数を有するクロック信号を広範囲に発生するシステム。

【解決手段】本発明によるシステムは、第1のクロック信号に応答して符号化信号の第1の組を発生する第1の回路(212)と、前記第1のクロック信号に応答して符号化信号の第2の組を発生する第2の回路(214)と、前記符号化信号の第1の組と前記符号化信号の第2の組とに応答して、第1、第2のパルス信号を発生する第3の回路(216)と、前記第1、第2のパルス信号に応答して、第2のクロック信号を発生する第4の回路(218)とを具備する。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

第1のクロック信号を受信し、前記第1のクロック信号の正エッジに応答して、符号化信号の第1の組を発生するように構成された第1の回路と、

前記第1のクロック信号を受信し、前記第1のクロック信号の負エッジに応答して、符号化信号の第2の組を発生するように構成された第2の回路と、

前記符号化信号の第1の組及び前記符号化信号の第2の組を受信し、前記符号化信号の第1の組及び前記符号化信号の第2の組に応答して、第1のパルス信号及び第2のパルス信号を発生するように構成されている第3の回路と、

前記第1のパルス信号及び前記第2のパルス信号を受信し、前記第1のパルス信号及び前記第2のパルス信号に応答して、第2のクロック信号を発生するように構成されている第4の回路とを具備する、

クロック信号発生システム。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、一般に、ディジタル回路要素に関するものであり、とりわけ、クロック分周回路に関するものである。

**【背景技術】****【0002】**

ディジタル・システムの構成要素は、一般に、システム・クロックを用いて動作する。システム・クロックによって、構成要素内のディジタル回路の同期がとられ、ディジタル回路による情報の生成及び処理が可能になる。それぞれ異なる時間に、ディジタル・システム内の異なる構成要素によって、異なる周波数及び／またはデューティ・サイクルのクロック信号が利用される可能性がある。異なる周波数及び／またはデューティ・サイクルのクロック信号を発生するため、システムに複数クロックを組み込むことも可能であるが、システムに複数クロックを設けるのは、システム設計にとってコスト、複雑性、または、物理的スペースの増大につながる可能性がある。結果として、ディジタル・システムにおいて、複数クロックを用いて、異なる周波数及び／またはデューティ・サイクルでクロック信号を発生するのは望ましくない。

**【0003】**

さまざまなアナログまたはディジタル回路を用いて、クロック信号の周波数またはデューティ・サイクルを変更することが可能である。しかし、これらの回路では、特定のディジタル・システムにとって望ましい周波数及び／またはデューティ・サイクルのクロック信号を発生することができない。例えば、これらの回路では、分周クロック信号の周波数が、システム・クロックの周波数の奇数分の1（例えば、1/3、1/5、1/7等）である場合、デューティ・サイクルが50%の分周クロック信号を発生することができない。さらに、これらの回路は、それぞれ異なる時間に、クロック信号の周波数を変更することができるように、プログラムすることが不可能である。

**【発明の開示】****【発明が解決しようとする課題】****【0004】**

本発明の目的は、一のクロック信号の周波数の分数である周波数を有するクロック信号を広範囲に発生することにある。

**【課題を解決するための手段】****【0005】**

本発明によれば、第1のクロック信号に応答して、符号化信号の第1の組を発生するように構成された第1の回路と、第1のクロック信号に応答して、符号化信号の第2の組を発生するように構成された第2の回路を含むシステムが得られる。このシステムには、符号化信号の第1の組及び符号化信号の第2の組に応答して、第1のパルス信号及び第2の

10

20

30

40

50

パルス信号を発生するように構成された第3の回路と、第1のパルス信号及び第2のパルス信号に応答して、第2のクロック信号を発生するように構成された第4の回路も含まれている。

【発明を実施するための最良の形態】

【0006】

望ましい実施態様に関する下記の詳細な説明では、その一部をなしている、本発明の実施が可能な特定の実施態様を例証するために示された添付の図面を参照する。もちろん、他の実施態様を利用することも可能であり、あるいは、本発明の範囲を逸脱することなく、構造または論理上の変更を加えることも可能である。従って、以下の詳細な説明は、制限の意味にとるべきではなく、本発明の範囲は付属の請求項によって定義される。

10

【0007】

本明細書では、クロック分周回路が解説され、例示される。クロック分周回路は、システム・クロック信号のような第1のクロック信号を受信し、第1のクロック信号を用いて、第2のクロック信号を発生する。第2のクロック信号は、デューティ・サイクルが50%で、周波数が、第1のクロック信号の周波数の $1/n$ であるが、ここで、nは1以上の整数である。すなわち、nを3、5、または、7のような奇数にして、第2のクロック信号の周波数を、それぞれ、第1のクロック信号の $1/3$ 、 $1/5$ 、または、 $1/7$ にすることが可能である。一部の実施態様では、nの値を経時変化させるように、クロック分周回路をプログラムできる。

20

【0008】

下記の図には、ハードウェア論理素子を用いたクロック分周回路の実施態様が例示されている。本明細書に示されていない他の実施態様には、ソフトウェア、または、ハードウェアとソフトウェアの組合せを用いて、クロック分周回路の1つ以上の機能を実施することが可能なものもある。

【0009】

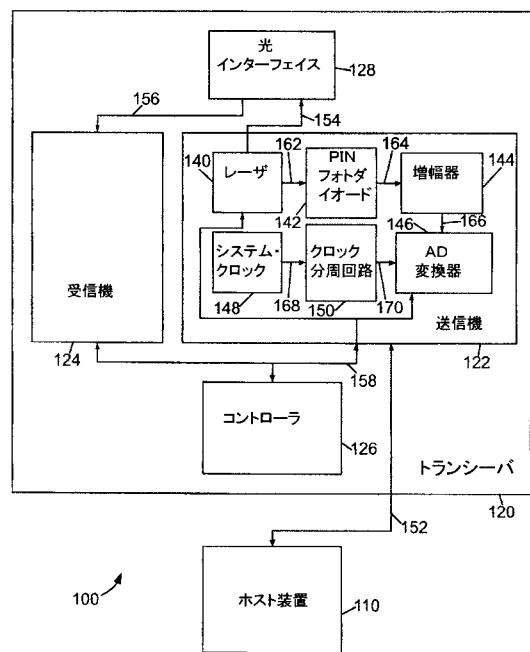

図1は、クロック分周回路150を含むシステム100の実施態様を例示したブロック図である。図示のように、図1には、トランシーバ120に結合されたホスト装置110が含まれている。トランシーバ120には、送信機122、受信機124、コントローラ126、及び、光インターフェイス128が含まれている。送信機122には、レーザ140、PINフォトダイオード142、増幅器144、アナログ・デジタル変換器(ADC変換器)146、システム・クロック148、及び、クロック分周回路150が含まれている。

30

【0010】

ホスト装置110は、トランシーバ120と連係動作するように構成された任意のタイプの有線または無線装置とすることが可能である。こうした装置の例には、サーバ・コンピュータ・システム、パーソナル・コンピュータ・システム、ラップ・トップ・コンピュータ・システム、ハンド・ヘルド・コンピュータ・システム、携帯端末、及び、携帯電話が含まれている。

【0011】

トランシーバ120には、電気的接続152を用いて、デジタル信号を送受信することにより、ホスト装置110との通信を行うように構成された光トランシーバが含まれている。電気的接続152によって、ホスト装置110と送信機122が結合されるが、電気的接続152は、任意の適合する直列または並列接続とすることが可能である。適合する接続の1つは、Philips Semiconductorsから入手可能なI2C-Bus Specificationに規定されている、I2C接続ということになる。トランシーバ120は、光インターフェイス128を用いて光信号を送受信することによって、別の装置(不図示)とも通信を行う。光インターフェイス128は、光ファイバ・チャネル・インターフェイスまたは別のタイプの光インターフェイスとすることが可能である。

40

【0012】

50

実施態様の1つでは、トランシーバ120は、SFP(小形差込可能)トランシーバに関するSFF-8074i規格に適合している。SFF-8074i規格は、<http://www.sffcommittee.com>、または、<http://ftp.seagate.com/sff/>で入手可能である。他の実施態様では、トランシーバ120は、他の規格に適合可能である。

#### 【0013】

送信機122は、図1に示されていない接続を用いて、ホスト110からデジタル出力信号を受信し、デジタル・アナログ変換器(不図示)を用いて、デジタル出力信号をアナログ出力信号に変換し、アナログ出力信号をレーザ140に供給する。レーザ140は、アナログ出力信号に応答して、光出力信号を発生し、光出力信号を光インターフェイス128に供給する。10

#### 【0014】

受信機124は、接続156を用いて、光インターフェイス128から光入力信号を受信し、アナログ・デジタル変換器(不図示)を用いて、光入力信号をデジタル入力信号に変換し、図1には示されていない接続を用いて、デジタル入力信号をホスト110に供給する。

#### 【0015】

コントローラ126は、接続158を用いて、送信機122及び受信機124に制御信号を送り、それらからフィードバック信号を受信する。接続158は、任意の適合する直列または並列接続とすることが可能である。適合する接続の1つは、Philips Semiconductorsから入手可能なI2C-Bus Specificationに規定されている、I2C接続ということになる。コントローラ126には、制御信号を発生して、フィードバック信号を受信する、マイクロコントローラ、ファームウェア、及び、メモリ(不図示)が含まれる。20

#### 【0016】

動作時、PINフォトダイオード142は、接続162を用いて、レーザ140から光信号を受信する。PINフォトダイオード142は、光信号をアナログ信号に変換し、接続164を介して、アナログ信号を増幅器144に供給する。増幅器144は、アナログ信号を増幅し、接続166を介して、増幅信号をアナログ・デジタル変換器146に供給する。アナログ・デジタル変換器146には、アナログ信号をデジタル信号に変換し、接続158を介して、デジタル信号をコントローラ126に供給するように構成されたシグマ・デルタ変調器が含まれている。コントローラ126は、デジタル信号の受信に応答し、接続158を介して、制御信号をレーザ140に供給する。PINフォトダイオード142、増幅器144、及び/または、アナログ・デジタル変換器146は、モニタ回路を構成している。30

#### 【0017】

システム・クロック148は、接続168を用いて、システム・クロック信号をクロック分周回路150に供給する。クロック分周回路150は、システム・クロック信号を受信し、システム・クロック信号を用いて、分周クロック信号を発生する。クロック分周回路150は、接続170を用いて、分周クロック信号をアナログ・デジタル変換器146に供給する。40

#### 【0018】

分周クロック信号の周波数は、システム・クロック信号の周波数の1/nであるが、ここで、nは1以上の整数である。nは、1を超える奇整数を含む、1以上の任意の整数とすることが可能である。ある特定の実施態様の場合、nは3であり、従って、分周クロック信号の周波数は、システム・クロック信号の周波数の1/3になる。

#### 【0019】

図1の実施態様の場合、クロック分周回路150は、システム・クロック信号の周波数に基づいて設定された周波数の分周クロック信号を発生するように構成されている。換言すれば、n値は、3のような特定の値に設定され、プログラム可能ではない。下記の図750

に関連して後述する別の実施態様の場合、n値は、クロック分周回路が、異なる時間に、それぞれ異なるn値に応答して、分周クロック信号を発生することができるよう、プログラム可能である。

#### 【0020】

図1の実施態様の場合、送信機122には、システム・クロック148及びクロック分周回路150が含まれている。他の実施態様には、システム・クロック148及びクロック分周回路150をトランシーバ120の他の部分に含むことが可能なものもある。

#### 【0021】

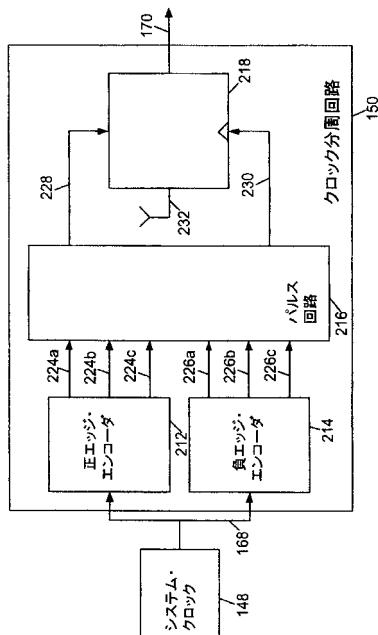

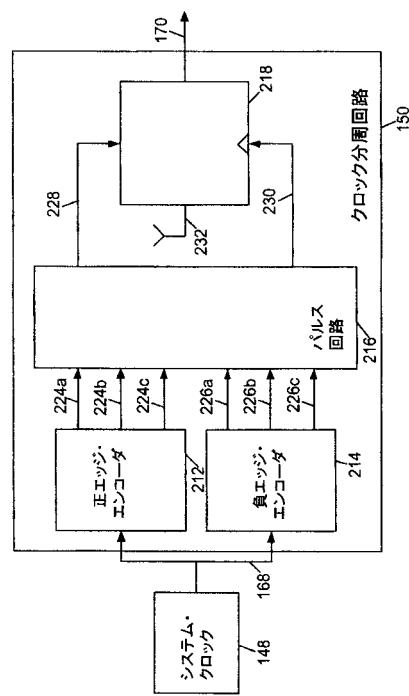

図2は、クロック分周回路150の実施態様のさらなる詳細を例示したブロック図である。クロック分周回路150には、正エッジ・エンコーダ212、負エッジ・エンコーダ214、パルス回路216、及び、クロックト・Dフリップ・フロップ218が含まれている。システム・クロック148から受信するシステム・クロック信号は、接続168を用いて、正エッジ・エンコーダ212及び負エッジ・エンコーダ214に供給される。正エッジ・エンコーダ212は、システム・クロック信号の正エッジすなわち上昇エッジに応答して、符号化信号を1組発生し、接続224a、224b、及び、224cを用いて、この1組の信号をパルス回路216に供給する。正エッジ・エンコーダ212は、3ビット幅の環状シフト・レジスタまたは3ビット幅エンコーダとすることが可能である。負エッジ・エンコーダ214は、システム・クロック信号の負エッジすなわち下降エッジに応答して、符号化信号を1組発生し、接続226a、226b、及び、226cを用いて、この1組の信号をパルス回路216に供給する。負エッジ・エンコーダ214は、3ビット幅の環状シフト・レジスタまたは3ビット幅エンコーダとすることが可能である。パルス回路216は、これらの複数組の符号化信号に応答して、第1及び第2のパルス信号を発生し、接続228及び230を用いて、クロックト・Dフリップ・フロップ218に供給する。接続228は、クロックト・Dフリップ・フロップ218のCLEAR入力に結合され、接続230は、クロックト・Dフリップ・フロップ218のCLOCK入力に結合されている。クロックト・Dフリップ・フロップ218のD入力は、高に結合される、すなわち、論理1すなわち高レベルに設定される。クロックト・Dフリップ・フロップ218は、第1及び第2のパルス信号を受信し、第1及び第2のパルス信号を用いて、分周クロック信号を発生し、Q出力から接続170に分周クロック信号を送り出す。

#### 【0022】

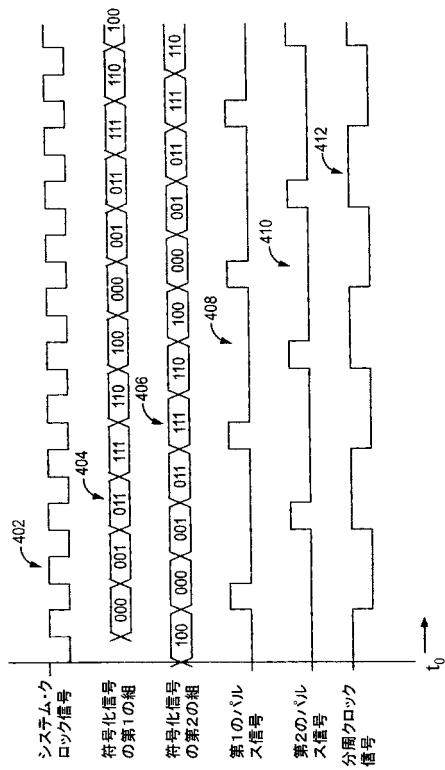

図4は、図2に示すクロック分周回路150によって発生する信号の実施態様を例示したタイム・チャートである。図4には、システム・クロック信号402、符号化信号の第1の組404、符号化信号の第2の組406、第1のパルス信号408、第2のパルス信号410、及び、分周クロック信号412が含まれている。

#### 【0023】

図2及び4を参照すると、正エッジ・エンコーダ212は、システム・クロック148からクロック信号402を受信して、符号化信号の第1の組404を発生する。図4に示すように、符号化信号の第1の組404は、000から始まり、システム・クロック信号402の正エッジに応答して、001、011、111、110、100、000等の順に続く。符号化信号の第1の組404の場合、最上位ビットは、接続224aに対応し、2番目に上位のビットは、接続224bに対応し、最下位ビットは、接続224cに対応する。

#### 【0024】

負エッジ・エンコーダ214は、システム・クロック148からシステム・クロック信号402を受信し、符号化信号の第2の組406を発生する。符号化信号の第2の組406は、システム・クロック信号の負の各エッジ402毎に変化する。符号化信号の第2の組406は、000で始まり、システム・クロック信号402の負エッジに応答して、001、011、111、110、100、000等の順に続く。符号化信号の第2の組406の場合、最上位ビットは、接続226aに対応し、2番目に上位のビットは、接続226bに対応し、最下位ビットは、接続226cに対応する。

10

20

30

40

50

## 【0025】

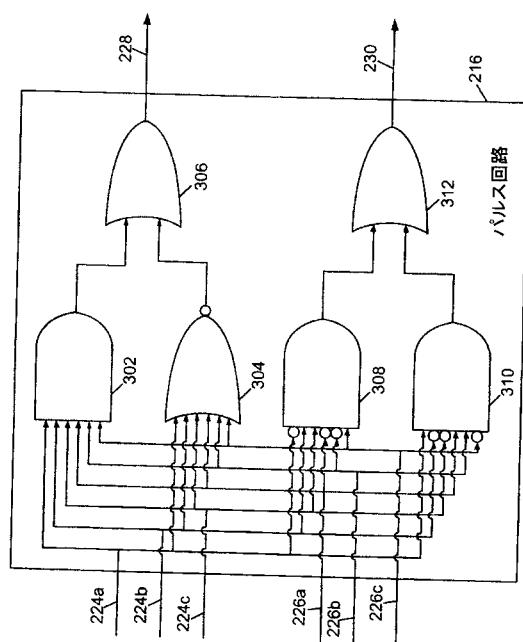

図2に示すように、組をなす符号化信号404及び406は、接続224a、224b、224c、226a、226b、及び、226cを用いて、パルス回路216に供給される。図3は、パルス回路216の実施態様を例示した回路図である。図3の場合、接続224a、224b、224c、226a、226b、及び、226cは、図示のように、ANDゲート302、NORゲート304、ANDゲート308、及び、ANDゲート310に結合されている。ANDゲート302及びNORゲート304の出力は、ORゲート306に供給されて、接続228に第1のパルス信号408が生じる。ANDゲート308及びANDゲート310の出力は、ORゲート312に供給されて、接続230に第2のパルス信号410が生じる。同じかまたは異なる数の入力を備えた、他のタイプ及び/または数のゲートを用いて、第1及び第2のパルス信号を発生する多くの回路バリエーションが可能であるので、図3の回路は、例証のために示されたものということになる。

## 【0026】

図2及び4を参照すると、第1のパルス信号408は、クロックト・Dフリップ・フロップ218のCLEAR入力に供給され、第2のパルス信号410は、クロックト・Dフリップ・フロップ218のCLK入力に供給される。図示のように、D入力が高に結合されると、分周クロック信号412は、クロックト・Dフリップ・フロップ218のQ出力によって送り出される。第1のパルス信号408からの各パルスによって、Q出力がクリアされ、すなわち、論理低レベルに遷移し、第2のパルス信号からの各パルスによって、高レベルのD入力がQ出力に刻時出力され、論理高レベルを生じることになる。結果として、分周クロック信号412は、周波数が、システム・クロック信号の周波数を3で割ったすなわち $1/3$ としたものになり、デューティ・サイクルは50%になる。

## 【0027】

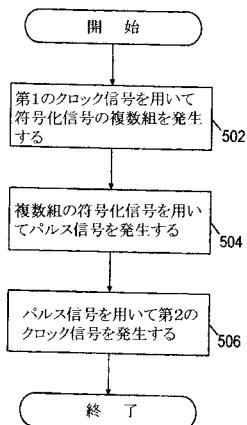

図5は、分周クロック信号を発生する方法の実施態様を例示したフローチャートである。図5において、ブロック502に示すように、第1のクロック信号を用いて、符号化信号を複数組発生する。2組の符号化信号を発生することが可能であり、各組毎に、nに等しい数の信号が含まれるが、ここで、nは1以上の整数である。符号化信号の組は、それぞれ、第1のクロック信号の異なる部分を用いて発生することが可能である。例えば、符号化信号の第1の組は、第1のクロック信号の正エッジを用いて発生することが可能であり、符号化信号の第2の組は、第1のクロック信号の負エッジを用いて発生することが可能である。ブロック504に示すように、これら符号化信号の複数組を用いて、パルス信号を発生する。これら複数組の符号化信号に応答して、2つのパルス信号を発生することが可能である。ブロック506に示すように、これらのパルス信号を用いて、第2のクロック信号を発生する。第2のクロック信号は、デューティ・サイクルが50%で、n分周された周波数を有するが、ここで、nは符号化信号の各組における信号数に等しい。従って、第2のクロック信号は、分周クロック信号をなしている。例えば、nが3の場合、第2のクロック信号の周波数は、第1のクロック信号の周波数の $1/3$ になる。

## 【0028】

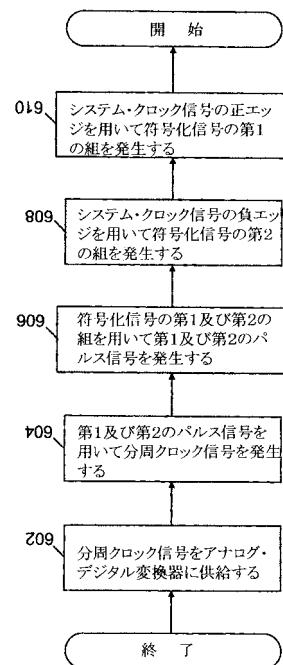

図6は、トランシーバにおいて分周クロック信号を発生する方法の実施態様を例示したフローチャートである。図6において、ブロック602に示すように、システム・クロックの正エッジを用いて、符号化信号の第1の組を発生する。第1の組の信号には、nに等しい数の信号が含まれるが、ここで、nは1以上の整数である。ブロック604に示すように、システム・クロックの負エッジを用いて、符号化信号の第2の組を発生する。第2の組の信号には、nに等しい数の信号が含まれる。ブロック606に示すように、符号化信号の第1及び第2の組を用いて、第1及び第2のパルス信号を発生する。ブロック608に示すように、第1及び第2のパルス信号を用いて、分周クロック信号を発生する。分周クロック信号は、デューティ・サイクルが50%で、周波数がシステム・クロック信号の周波数の $1/n$ である。ブロック610に示すように、分周クロック信号は、アナログ・ディジタル変換器に供給される。

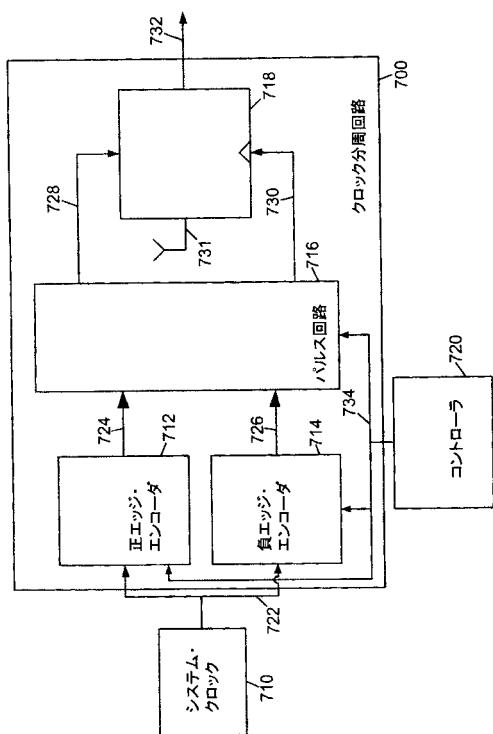

## 【0029】

図7は、システム・クロック710及びコントローラ720に結合されたプログラマブル・クロック分周回路700の実施態様を例示したブロック図である。クロック分周回路700には、正エッジ・エンコーダ712、負エッジ・エンコーダ714、パルス回路716、及び、クロックト・Dフリップ・フロップ718が含まれている。システム・クロック710からシステム・クロック信号を受信すると、接続722を用いて、正エッジ・エンコーダ712及び負エッジ・エンコーダ714に供給される。正エッジ・エンコーダ712は、システム・クロック信号の正エッジすなわち上昇エッジに応答して、符号化信号を1組発生し、1組の接続724を用いて、この1組の符号化信号をパルス回路716に供給する。正エッジ・エンコーダ712は、nビット幅の環状シフト・レジスタまたはnビット幅エンコーダとすることが可能であるが、ここで、nは1以上の整数である。負エッジ・エンコーダ714は、システム・クロック信号の負エッジすなわち下降エッジに応答して、符号化信号を1組発生し、1組の接続726を用いて、この1組の符号化信号をパルス回路716に供給する。負エッジ・エンコーダ714は、nビット幅の環状シフト・レジスタまたはnビット幅エンコーダとすることが可能であるが、ここで、nは1以上の整数である。パルス回路716は、これらの複数組の符号化信号に応答して、第1及び第2のパルス信号を発生し、接続728及び730を用いて、クロックト・Dフリップ・フロップ718に供給する。接続728は、クロックト・Dフリップ・フロップ718のCLEAR入力に結合され、接続730は、クロックト・Dフリップ・フロップ718のLOCK入力に結合されている。クロックト・Dフリップ・フロップ718のD入力は、記号731で示すように、高に結合される、すなわち、論理1すなわち高レベルに設定される。クロックト・Dフリップ・フロップ718は、第1及び第2のパルス信号を受信し、第1及び第2のパルス信号を用いて、分周クロック信号を発生し、Q出力から接続732に分周クロック信号を送り出す。

10

20

## 【0030】

クロック分周回路700には、コントローラ720からクロック分周信号を受信するよう構成されたプログラマブル・クロック分周回路が含まれている。クロック分周回路700は、クロック分周信号に応答して、周波数がシステム・クロック信号の周波数の $1/n$ である分周クロック信号を生じさせるが、ここで、nは1以上の整数であり、クロック分周信号に基づいて決定される。すなわち、コントローラ720からクロック分周回路700に加えられるクロック分周信号によって、分周クロック信号の周波数が設定される。

30

## 【0031】

コントローラ720は、クロック分周信号を発生するために用いられる情報を記憶するか、または、アクセスする。クロック分周信号は、分周クロック信号の周波数を決定する整数nを指示する。コントローラ720は、クロック分周信号を発生し、接続734を用いて、正エッジ・エンコーダ712、負エッジ・エンコーダ714、及び、パルス回路716に加える。

## 【0032】

正エッジ・エンコーダ712は、クロック分周信号に応答して、符号化信号の第1の組を発生する。符号化信号の第1の組には、クロック分周信号によって指示されるn値に等しい数の信号が含まれている。同様に、負エッジ・エンコーダ714は、クロック分周信号に応答して、符号化信号の第2の組を発生する。符号化信号の第2の組には、クロック分周信号によって指示されるn値に等しい数の信号が含まれている。例えば、クロック分周信号によって、nが5であると指示されると、符号化信号の第1、第2の組のそれぞれには、それぞれ、5つの信号が含まれることになる。

40

## 【0033】

パルス回路716は、クロック分周信号及び符号化信号の第1及び第2の組に応答して、第1及び第2のパルス信号を発生し、クロックト・Dフリップ・フロップ718に供給する。上述の図2の実施態様と同様、クロックト・Dフリップ・フロップ718は、第1及び第2のパルス信号に応答して、システム・クロック信号の周波数の $1/n$ の周波数を

有する分周クロック信号を発生する。従って、クロック分周信号によって、例えば、 $n$  が 5 であると指示される場合、分周クロック信号は、その周波数がシステム・クロック信号の周波数の  $1/5$  になり、デューティ・サイクルが 50 % になる。

#### 【0034】

望ましい実施態様の説明のため、特定の実施態様について例示し、解説してきたが、当該分野の技術者には明らかなように、本発明の範囲を逸脱することなく、図示及び解説の特定の実施態様の代わりに、同じ目的を実現することを意図した多種多様な代替及び/または同等実施例を用いることも可能である。化学、機械、電気機械、電気、及び、コンピュータの技術者にはすぐ分るように、本発明は、以下に一部をさらに例示するが、多種多様な実施態様で実施可能である。本出願は、本明細書において論述の望ましい実施態様に関するいかなる改変または変更をも網羅することを意図したものである。従って、明らかに、本発明は、請求項及びその同等物による制限しか受けないことを意図したものである。10

#### 【0035】

##### (実施態様 1)

第 1 のクロック信号を受信し、前記第 1 のクロック信号の正エッジに応答して、符号化信号の第 1 の組を発生するように構成された第 1 の回路 (212 / 712) と、

前記第 1 のクロック信号を受信し、前記第 1 のクロック信号の負エッジに応答して、符号化信号の第 2 の組を発生するように構成された第 2 の回路 (214 / 714) と、前記符号化信号の第 1 の組及び前記符号化信号の第 2 の組を受信し、前記符号化信号の第 1 の組及び前記符号化信号の第 2 の組に応答して、第 1 のパルス信号及び第 2 のパルス信号を発生するように構成されている第 3 の回路 (216 / 716) と、前記第 1 のパルス信号及び前記第 2 のパルス信号を受信し、前記第 1 のパルス信号及び前記第 2 のパルス信号に応答して、第 2 のクロック信号を発生するように構成されている第 4 の回路 (218 / 718) とを具備する、クロック信号発生システム。20

#### 【0036】

##### (実施態様 2)

前記第 1 の回路に第 1 の環状シフト・レジスタが含まれることと、前記第 2 の回路に第 2 の環状シフト・レジスタが含まれる、実施態様 1 に記載のシステム。

#### 【0037】

##### (実施態様 3)

前記第 1 の回路に第 1 のエンコーダが含まれることと、前記第 2 の回路に第 2 のエンコーダが含まれる、実施態様 1 に記載のシステム。

#### 【0038】

##### (実施態様 4)

前記第 4 の回路に、クロックト・D フリップ・フロップが含まれる、実施態様 1 に記載のシステム。

#### 【0039】

##### (実施態様 5)

前記第 1 のパルス信号が、前記クロックト・D フリップ・フロップのクリア入力に加えられることと、前記第 2 のパルス信号が、前記クロックト・D フリップ・フロップのクロック入力に加えられることと、前記クロックト・D フリップ・フロップの D 入力が高に結合されることと、前記第 2 のクロック信号が、前記クロックト・D フリップ・フロップの Q 出力から送り出される、実施態様 4 に記載のシステム。40

#### 【0040】

##### (実施態様 6)

前記符号化信号の第 1 の組と前記符号化信号の第 2 の組に、それぞれ、 $n$  の符号化信号が含まれることと、前記第 2 のクロック信号の周波数が、前記第 1 のクロック信号の周波数の  $1/n$  であることと、 $n$  が 1 以上の整数である、実施態様 1 に記載のシステム。

#### 【0041】

**(実施態様 7 )**

$n$  が 1 を超える奇整数である、実施態様 6 に記載のシステム。

**【0042】****(実施態様 8 )**

前記第 1 の回路と前記第 2 の回路が、それぞれ、整数  $n$  を表わすクロック分周信号(734)を受信するように構成されている、実施態様 6 に記載のシステム。

**【0043】**

(実施態様 9) : 第 1 のクロック信号を用いて、符号化信号の複数組を発生するステップと、前記符号化信号の複数組を用いて、複数のパルス信号を発生するステップと、前記複数のパルス信号を用いて、第 2 のクロック信号を発生するステップとを有する、クロック信号発生方法。10

**【0044】**

(実施態様 10) : 前記クロック信号を用いて、前記符号化信号の複数組を発生するステップに、さらに、前記クロック信号の正エッジを用いて、前記符号化信号の複数組のうち符号化信号の第 1 の組を発生するステップと、前記クロック信号の負エッジを用いて、前記符号化信号の複数組のうち符号化信号の第 2 の組を発生するステップとを有する、実施態様 9 に記載の方法。

**【0045】**

(実施態様 11) : 前記符号化信号の複数組が、各組毎に、奇数の信号を備えることを特徴とする、実施態様 9 に記載の方法。20

**【0046】**

(実施態様 12) : さらに、クロック分周信号を受信するステップと、前記クロック分周信号に関連した周波数で前記第 2 のクロック信号を発生するステップとを有する、実施態様 9 に記載の方法。

**【図面の簡単な説明】****【0047】**

【図 1】クロック分周回路を含むシステムの実施態様を例示したブロック図である。

【図 2】クロック分周回路の実施態様を例示したブロック図である。

【図 3】パルス回路の実施態様を例示した回路図である。

【図 4】クロック分周回路によって発生する信号の実施態様を例示したタイム・チャート30を示す図である。

【図 5】分周クロック信号を発生する方法の実施態様を例示したフローチャートである。

【図 6】トランシーバにおいて分周クロック信号を発生する方法の実施態様を例示したフローチャートを示す図である。

【図 7】プログラマブル・クロック分周回路の実施態様を例示したブロック図である。

**【符号の説明】****【0048】**

- 212 第 1 の回路

- 214 第 2 の回路

- 216 第 3 の回路

- 218 第 4 の回路

- 712 第 1 の回路

- 714 第 2 の回路

- 716 第 3 の回路

- 718 第 4 の回路

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(72)発明者 タカシ ヒダイ

アメリカ合衆国 カリフォルニア 94303 パロ・アルト ルイス・ロード 3683

F ターム(参考) 5B079 DD03