### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2009-54860 (P2009-54860A)

(43) 公開日 平成21年3月12日(2009.3.12)

| (51) Int.Cl. |              |           | F I  |       |         | テーマコード(参考) |  |

|--------------|--------------|-----------|------|-------|---------|------------|--|

| HO1L         | 23/12        | (2006.01) | HO1L | 23/12 | W       | 5 F O 4 1  |  |

| HO1L         | <i>33/00</i> | (2006.01) | HO1L | 33/00 | N       | 5 F O 4 4  |  |

| HO1L         | 21/60        | (2006.01) | HO1L | 21/60 | 3 O 1 A |            |  |

#### 審査請求 未請求 請求項の数 8 〇1. (全 9 頁)

|                       |                                                        | 普宜請為                                     | K 木請水 請水項の数 δ U L (至 9 貝)<br> |

|-----------------------|--------------------------------------------------------|------------------------------------------|-------------------------------|

| (21) 出願番号<br>(22) 出願日 | 特願2007-221416 (P2007-221416)<br>平成19年8月28日 (2007.8.28) | (71) 出願人                                 | 000131430 シチズン電子株式会社          |

|                       |                                                        | /_ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | 山梨県富士吉田市上暮地1丁目23番1号           |

|                       |                                                        | (74)代理人                                  | 100085280                     |

|                       |                                                        |                                          | 弁理士 高宗 寬暁                     |

|                       |                                                        | (72)発明者                                  | 門谷 典和                         |

|                       |                                                        |                                          | 山梨県富士吉田市上暮地1丁目23番1号           |

|                       |                                                        |                                          | シチズン電子株式会社内                   |

|                       |                                                        | (72) 発明者                                 | 菊池 悟                          |

|                       |                                                        |                                          | 山梨県富士吉田市上暮地1丁目23番1号           |

|                       |                                                        |                                          | シチズン電子株式会社内                   |

|                       |                                                        | (72) 発明者                                 | 深沢 孝一                         |

|                       |                                                        |                                          | 山梨県富士吉田市上暮地1丁目23番1号           |

|                       |                                                        |                                          | シチズン電子株式会社内                   |

|                       |                                                        |                                          | 最終頁に続く                        |

## (54) 【発明の名称】チップ型半導体装置

## (57)【要約】

【課題】 ボールボンディングで行う場合に、フィルドビア上のパターンにも問題なくワイヤを打つことができるチップ型半導体装置。

【解決手段】 LED1の基板2は、絶縁層2aを挟んで表面側電極であるダイボンドパターン2b及び2ndボンディングパターン2cと裏面側電極である端子電極2d、2dとをそれぞれ対向配置させ、スルーホール内に導電剤を充填して形成したフィルドビア2eによって表裏電極を導通させている。ダイボンドパターン2bにはLED素子3が接合され、金ワイヤ4によってLED素子3の電極と2ndボンディングパターン2cとが接続されている。LED素子3とワイヤ4とは封止樹脂5によって封止されている。2ndボンディングパターン2cにおけるフィルドビア2eがボンディングポイントから離れた、キャピラリの先端径と垂直方向に重ならない位置に形成されているところに特徴がある。

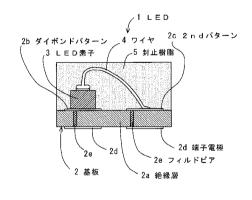

【選択図】 図1

#### 【特許請求の範囲】

### 【請求項1】

絶縁層の両面に銅箔が張られ、表面側には半導体素子を実装するダイボンドパターンとワイヤボンディングされる2ndボンディングパターンとを有し、裏面側には前記両パターンの端子電極となる裏パターンを有し、表裏の前記パターンが絶縁層を貫通して導通している実装基板と、前記実装基板上に固着された半導体素子と、前記半導体素子と前記2ndボンディングパターンとをボールボンディングにより接続する金属線とから成り、前記半導体素子および前記金属線を封止する絶縁樹脂で前記実装基板の表面側全面を覆ったチップ型半導体装置において、前記フィルドビアと、前記キャピラリ先端とが垂直方向に重ならないように、2ndボンディングがなされていることを特徴とするチップ型半導体装置。

#### 【請求項2】

前記裏パターン側から前記ダイボンドパターンあるいは前記 2 n d ボンディングパターンの銅箔に達する穴をレーザー処理により設け、メッキにより表裏のパターンを導通し、さらに穴全体を塞ぎフィルドビアを形成したことを特徴とする請求項 1 記載のチップ型半導体装置。

### 【請求項3】

前記フィルドビア径は、ワイヤボンディングのキャピラリ先端径よりも小であることを 特徴とする請求項1又は請求項2記載のチップ型半導体装置。

#### 【請求項4】

前記フィルドビアは、ダイボンドパターン側に複数形成されていることを特徴とする請求項1乃至請求項3のいずれかに記載のチップ型半導体装置。

#### 【請求項5】

絶縁層の両面に銅箔が張られ、表面側には半導体素子を実装するダイボンドパターンとワイヤボンディングされる2ndボンディングパターンとを有し、裏面側には前記両パターンの端子電極となる裏パターンを有し、表裏の前記パターンが絶縁層を貫通して導通している実装基板と、前記実装基板上に固着された半導体素子と、前記半導体素子と前記2ndボンディングパターンとをボールボンディングにより接続する金属線とから成り、前記半導体素子および前記金属線を封止する絶縁樹脂で前記実装基板の表面側全面を覆ったチップ型半導体装置において、前記フィルドビアは、2ndボンディングパターン側に複数形成されており、前記キャピラリ先端と前記複数のフィルドビアの少なくとも2つ以上とが垂直方向に重なるように2ndボンディングがなされていることを特徴とするチップ型半導体装置。

## 【請求項6】

前記裏パターン側から前記ダイボンドパターンあるいは前記 2 n d ボンディングパターンの銅箔に達する穴をレーザー処理により設け、メッキにより表裏のパターンを導通し、さらに穴全体を塞ぎフィルドビアを形成したことを特徴とする請求項 5 記載のチップ型半導体装置。

## 【請求項7】

前記フィルドビア径は、ワイヤボンディングのキャピラリ先端径よりも小であることを 特徴とする請求項5又は請求項6記載のチップ型半導体装置。

#### 【請求項8】

前記フィルドビアは、ダイボンドパターン側に複数形成されていることを特徴とする請求項5万至請求項7のいずれかに記載のチップ型半導体装置。

#### 【発明の詳細な説明】

## 【技術分野】

## [ 0 0 0 1 ]

本発明は、チップ型半導体装置に関し、更に詳しくは、半導体素子がワイヤボンディングによって実装されたチップ型半導体装置に関する。

## 【背景技術】

50

40

10

20

#### [00002]

近年の電子機器の小形・薄形化傾向に伴って、回路基板へ表面実装が可能な電子部品、即ちチップ型半導体装置の需要が急速に増加している。チップ型半導体装置は、通常は直方体ブロックに近い形状をしており、絶縁基板の表面側にそれぞれ一対の電極を備え、裏面または裏面に近い側面に一対の端子電極が形成されている。そして、表裏面の電極同士はスルーホールによって導通する一方、表面側電極の一方に半導体素子を実装し、該半導体素子と他方の表面側電極とを金属細線によってワイヤボンディングしたのち、これらの半導体素子及び金属細線を透光性樹脂によって封止したものである。このようなチップ型半導体装置は、回路基板上の配線パターンと所定の端子電極とが接触するように回路基板上に配設して、半田などの導電性接着剤で回路基板上に固着する。

[0003]

このようなチップ型半導体装置において、基板の表面側に半導体素子を接合するダイボンドパターン及び 2 n d ボンディングパターンと裏面側の端子電極とを絶縁層を挟んで対向配置させることによって、装置の小型化を追求したものが知られている(例えば、特許文献 1、特許文献 2 及び特許文献 3 参照。)。

[0004]

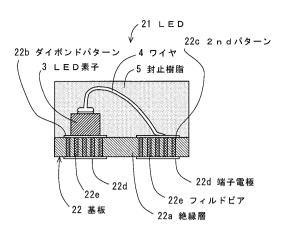

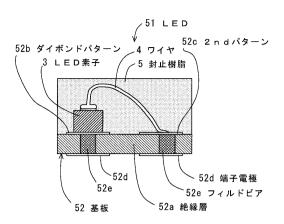

図4は従来のこのようなチップ型半導体装置の一例である発光ダイオード(以下LEDと略記する)の断面図を示している。LED51の基板52は、絶縁層52aを挟んで表面側電極であるダイボンドパターン52b及び2ndボンディングパターン52cと裏面側電極である端子電極52d、52dとをそれぞれ対向配置させ、絶縁層52aを貫通するレーザーで開けた穴内に導電剤を充填して形成したフィルドビア52eによって表裏電極を導通させている。フィルドビア52eはレーザーによって穴開けを行う都合上、基板52はプリント配線板やフレキシブル基板等の薄いものである。ダイボンドパターン52bにはLED素子3が接合され、金ワイヤ4(径20~30μm)によってLED素子3の電極と2ndボンディングパターン52cとが接続されている。LED素子3と金ワイヤ4とは封止樹脂5によって封止されている。LED51ではフィルドビア51eの径がキャピラリの先端径より大きいのでキャピラリの片当たりが起きない。

[0005]

【特許文献1】特開2001-102638号公報

【特許文献2】特開平09-181359号公報

【特許文献3】特開2003-017754号公報

【発明の開示】

【発明が解決しようとする課題】

[0006]

しかし、ワイヤボンディングをウェッジボンディングで行った場合には、2ndボンディング側においてより広いスペースを必要とする。また、キャピラリの構造上、同じ方向にしかワイヤのループを張れない。そこでボールボンディングで行おうとすると、フィルドビアの径がワイヤボンダーのキャピラリの先端径より小さい場合には、キャピラリの片当たりが発生する。この場合には超音波が基材部分には伝わり難くなるのでワイヤが2ndボンディング位置で押しつぶしに不具合が生じやすく、ワイヤが引っ張られたときに接続部が剥がれたり、剥がれやすくなるという問題があった。

[0007]

本発明は、上記問題を解決して、ワイヤボンディングをボールボンディングで行った場合に、フィルドビアの径がワイヤボンダーのキャピラリの先端径より小さい場合にもフィ

10

20

30

40

ルドビア上のパターンに問題なくワイヤを打つことができるチップ型半導体装置を提供することを目的としている。

## 【課題を解決するための手段】

#### [00008]

前述した目的を達成するための本発明の手段は、絶縁層の両面に銅箔が張られ、表面側には半導体素子を実装するダイボンドパターンとワイヤボンディングされる2ndボンディングパターンとを有し、裏面側には前記両パターンの端子電極となる裏パターンを有し、表裏の前記パターンが絶縁層を貫通して導通している実装基板と、前記実装基板上に固着された半導体素子と、前記半導体素子と前記2ndボンディングパターンとをボールボンディングにより接続する金属線とから成り、前記半導体素子および前記金属線を封止する絶縁樹脂で前記実装基板の表面側全面を覆ったチップ型半導体装置において、前記フィルドビアと、前記キャピラリ先端とが垂直方向に重ならないように、2ndボンディングがなされていることを特徴とする。

## [0009]

また、前記裏パターン側から前記ダイボンドパターンあるいは前記 2 n d ボンディングパターンの銅箔に達する穴をレーザー処理により設け、メッキにより表裏のパターンを導通し、さらに穴全体を塞ぎフィルドビアを形成したことを特徴する。

#### [0010]

また、前記フィルドビアの径がワイヤボンディングのキャピラリ先端径よりも小であることを特徴する。

[0011]

また、前記フィルドビアは、ダイボンドパターン側に複数形成されていることを特徴する。

#### [0012]

また、前述した目的を達成するための本発明の他の手段は、絶縁層の両面に銅箔が張られ、表面側には半導体素子を実装するダイボンドパターンとワイヤボンディングされる2ndボンディングパターンとを有し、裏面側には前記両パターンの端子電極となる裏パターンを有し、表裏の前記パターンが絶縁層を貫通して導通している実装基板と、前記実装基板上に固着された半導体素子と、前記半導体素子と前記2ndボンディングパターンとをボールボンディングにより接続する金属線とから成り、前記半導体素子および前記金属線を封止する絶縁樹脂で前記実装基板の表面側全面を覆ったチップ型半導体装置において、前記フィルドビアは、2ndボンディングパターン側に複数形成されており、前記キャピラリ先端と前記複数のフィルドビアの少なくとも2つ以上とが垂直方向に重なるように2ndボンディングがなされていることを特徴とするチップ型半導体装置。

[0013]

また、前記裏パターン側から前記ダイボンドパターンあるいは前記2ndボンディングパターンの銅箔に達する穴をレーザー処理により設け、メッキにより表裏のパターンを導通し、さらに穴全体を塞ぎフィルドビアを形成したことを特徴とする。

#### [0014]

また、前記フィルドビア径は、ワイヤボンディングのキャピラリ先端径よりも小である ことを特徴とする。

[0015]

また、前記フィルドビアは、ダイボンドパターン側に複数形成されていることを特徴と する。

### 【発明の効果】

## [0016]

本発明によれば、絶縁層の両面に銅箔が張られ、表面側には半導体素子を実装するダイボンドパターンとワイヤボンディングされる2 n d ボンディングパターンとを有し、裏面側には前記両パターンの端子電極となる裏パターンを有し、表裏の前記パターンが絶縁層を貫通して導通している実装基板と、前記実装基板上に固着された半導体素子と、前記半

10

20

30

40

10

20

30

40

50

[0017]

また、前記裏パターン側から前記ダイボンドパターンあるいは前記 2 n d ボンディングパターンの銅箔に達する穴をレーザー処理により設け、メッキにより表裏のパターンを導通し、さらに穴全体を塞ぎフィルドビアを形成したので、パターン側の熱を効率よく端子電極側へ放熱することができる。

[0018]

また、前記フィルドビアの径がワイヤボンディングのキャピラリ先端径よりも小であるので、キャピラリの片当たりが発生せず、ボールボンディングの不良発生を防ぐことができる。

[0019]

また、前記フィルドビアは、ダイボンドパターン側に複数形成されているので、素子実装部直下のフィルドビアを経由して端子電極から放熱し易くなるので放熱性を向上させることができる。

[0020]

また、前記フィルドビアと、前記キャピラリ先端とが垂直方向に重ならないように、 2 n d ボンディングがなされているので、 2 n d ボンディングの際に、フィルドビアの影響を受けず、ボールボンディングの不良発生を未然に防ぐことができる。

[0021]

また、前述した目的を達成するための本発明の他の手段は、絶縁層の両面に銅箔が張っための本発明の他の手段は、絶縁層の両面に銅箔が張っための本発明の他の手段は、絶縁層の両面に銅箔が張っための本発明には半導体素子を実装するダイボンドパターンとワイヤボンディングである裏面側には前記である実装基板と、前記パターンが絶縁層を貫通している実装基板と、前記パターンが絶縁層を貫通している実装基板と、前記半導体素子と、前記半導体素子と、前記半導体素子の成り、前記半導体素子とをボールボンディングにより接続する金属線とから成り、前記半導体素子およりではよりで前記に表現のでで前記で前記に変数のである金属線とからでで表してものででがでするとでがです。また、小が発生を重ながパターン側に複数形成されておりではいるのではではでである。また、小さなフィルドビアとが重なるのではいってもが発生を表別にいてできる。また、小さなフィルドビアの何れかとがディングの不良発生を未然にでのできる。また、小さなフィルドビアが、複数ある合わせることで、多少位置が記とができるので、ボンディング条件をフィルドビアと基板との混成部に合わせることで、多少位置が記さても、混成部の範囲内ならばどこでも同じ条件でボンディングできるので、ボンディとが発生しない。

【発明を実施するための最良の形態】

[0022]

以下、本発明を実施するための最良の形態であるチップ型半導体装置を図面に基づいて

詳細に説明する。図1は本発明の第1の実施の形態であるLEDの断面図である。

### [0023]

まず、本発明の第1の実施の形態であるLEDの構成について説明する。図1において、LED装置1は、従来技術で説明したものと同様であるが、ボンディング位置ズレが起きたとしても、2ndボンディングパターン2cにおけるフィルドビア2eが、ボンディングポイントから離れた位置であるキャピラリの先端と垂直方向に重ならない位置に形成されているところに特徴がある。

### [0024]

次に、本発明の第1の実施の形態であるLEDの効果について説明する。LED1において、端子電極2dが絶縁層2aを介してダイボンドパターン2b及び2ndボンディングパターン2cと対向配置されており、LED1の小型化に寄与している。フィルドビアやスルーホール形成に必要だったスペースを有効利用できるので、パターン面積を増やすことによって素子数増加(LED素子の場合には高輝度化)が可能になる。また、製品小型化に伴い基板取り個数の向上による低コスト化が可能である。また、LED素子3の直下にフィルドビア2eがあるので、端子電極2dへ放熱されるのでLED素子3の放熱性がよくなる。また、ワイヤボンディングをボールボンディングで行う場合に、2ndボンディングにおいてフィルドビア2eがボンディングポイントから離れているために、フィルドビア2eの影響を受けないでボンディング不良の発生を未然に防止できる。

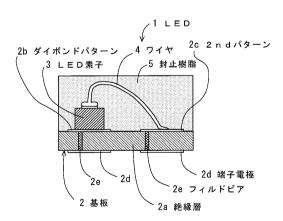

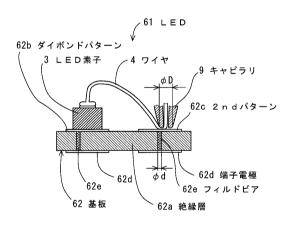

#### [0025]

次に、本発明の第2の実施の形態であるLEDの構成について説明する。図2において、LED装置11には、2ndボンディングパターン12cにおいて複数のフィルドビア12eが縦横に形成されており、ボールボンディングにおいてキャピラリの先端は必ず複数のフィルドビアの少なくとも2つ以上が垂直方向に重なるように2ndボンディングされている。このように複数のフィルドビアの周辺に基材が存在する構成、即ちフィルドビアと基材との混成部では、キャピラリの先端部は複数(2つ以上)のフィルドビアにかかることになるので、片当たりは起きず、ボンディング不良を発生させない。

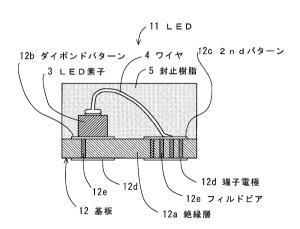

## [0026]

次に、本発明の第3の実施の形態であるLEDの構成について説明する。図3において、LED装置21は、第2の実施の形態のLED11と同様であり、ダイボンドパターン22bにおけるフィルドビア22eが複数形成されているところに特徴がある。これにより、LED素子3の放熱性をLED1やLED11よりも更に向上させることができる。

## 【図面の簡単な説明】

- [0027]

- 【図1】本発明の第1の実施の形態であるLEDの断面図である。

- 【図2】本発明の第2の実施の形態であるLEDの断面図である。

- 【図3】本発明の第3の実施の形態であるLEDの断面図である。

- 【図4】従来のLEDを示す断面図である。

- 【図5】他の従来のLEDの2ndボンディングを示す断面図である。

## 【符号の説明】

- [0028]

- 1, 11, 21 LED

- 2、12、22 基板

- 2 a、12 a、22 a 絶縁層

- 2 b 、 1 2 b 、 2 2 b ダイボンドパターン

- 2 c 、 1 2 c 、 2 2 c 2 n d ボンディングパターン

- 2 d、1 2 d、2 2 d 端子電極

- 2 e、12 e、22 e フィルドビア

- 3 LED素子

20

10

30

40

- 4 金ワイヤ

- 5 封止樹脂

# 【図1】

## 【図2】

## 【図3】

## 【図4】

## 【図5】

# フロントページの続き

F ターム(参考) 5F041 AA25 AA47 DA07 DA12 DA19 DA35 DA43 DB09 5F044 AA05