### (19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第4565815号 (P4565815)

(45) 発行日 平成22年10月20日(2010.10.20)

(24) 登録日 平成22年8月13日(2010.8.13)

| (10) (11) [ [ [ 10]                                                   | F 10/3 20 11 (20 10: 10: 20)                                                           | ,                                    |                                  | (2±) ± 35 H                                                    | 1 /3/22   0/110 | рд (2010.0.10) |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------|----------------------------------|----------------------------------------------------------------|-----------------|----------------|

| (51) Int.Cl.  GO9G 3/36  GO2F 1/133  GO9G 3/20  GO9G 3/30  G11C 19/00 | (2006.01)                                                                              | G09G<br>G02F<br>G09G<br>G09G<br>G09G | 3/20<br>3/20                     | 550<br>611A<br>622E<br>623H<br>請求項の数8                          | (全 30 頁)        | 最終頁に続く         |

| (21) 出願番号<br>(22) 出願日<br>(65) 公開番号<br>(43) 公開日<br>審査請求日               | 特願2003-185263 (P200平成15年6月27日 (2003特開2005-17908 (P2005平成17年1月20日 (2006平成18年6月20日 (2006 | . 6. 27)<br>-17908A)<br>. 1. 20)     | (73) 特許権<br>(74) 代理人<br>(72) 発明者 | 三洋電機株式:<br>大阪府守口市:<br>100104433<br>弁理士 宮園<br>千田 みちる<br>大阪府守口市: | 京阪本通2丁目         | 5番5号           |

|                                                                       |                                                                                        |                                      | 審查官                              | 〉安藤 達哉                                                         | 最               | ŧ終頁に続く         |

### (54) 【発明の名称】表示装置

## (57)【特許請求の範囲】

## 【請求項1】

第1電位側にドレインが接続され、クロック信号に応答してオンする第1導電型の第1トランジスタと、第2電位側にソースが接続され、前記第1トランジスタのソースにドレインが接続された第1導電型の第2トランジスタと、前記第1トランジスタのゲートと前記第2電位との間に直列に接続され、互いに電気的に接続された2つのゲート電極を有する第1導電型の第3トランジスタとを含む第1回路部を複数有し、一の第1回路部における前記第1トランジスタのソースと前記第2トランジスタのドレインとの間に設けられたノードが、他の第1回路部における前記第2トランジスタ及び前記第3トランジスタのゲートに接続されることによって、前記第1回路部が複数接続されたシフトレジスタ回路を備え、

前記シフトレジスタ回路における一の第1回路部の前記第2トランジスタ及び前記第3トランジスタのゲートに接続されていないノードの電位が前記シフトレジスタ回路の出力信号として出力され、

前記シフトレジスタ回路における一の第1回路部のノードに接続されていない前記第2トランジスタ及び前記第3トランジスタのゲートに前段のシフトレジスタ回路の出力信号が 入力信号として入力されることを特徴とする表示装置。

#### 【請求項2】

前記第1回路部は、前記第1トランジスタのゲートと、前記クロック信号を供給するクロック信号線との間に接続され、互いに電気的に接続された2つのゲート電極を有するダイ

オード接続された第4トランジスタをさらに含むことを特徴とする請求項1に記載の表示装置。

### 【請求項3】

前記第1回路部は、前記第1トランジスタのゲートと、前記クロック信号を供給するクロック信号線との間に接続され、前記第3トランジスタのオン状態の期間と重ならないオン状態の期間が得られる信号に応答してオンする第4トランジスタをさらに含むことを特徴とする請求項1に記載の表示装置。

### 【請求項4】

前記第1回路部は、前記<u>第1トランジスタのゲートにソース</u>が接続され、第1の信号に応答してオンする第4トランジスタと、前記第4トランジスタ<u>のドレインにソースが接続され、</u>前記第1電位<u>にドレインが</u>接続され、前記第1の信号が入力される第4トランジスタのオン状態の期間と重ならないオン状態の期間が得られる第2の信号に応答してオンする第5トランジスタとをさらに含むことを特徴とする請求項1に記載の表示装置。

## 【請求項5】

前記第1トランジスタのゲートとソースとの間には、容量が接続されていることを特徴と する請求項1~4のうちいずれか1項に記載の表示装置。

### 【請求項6】

前記第3トランジスタは、前記第2トランジスタがオン状態のときに、前記第1トランジスタをオフ状態にする機能を有することを特徴とする請求項1~5のうちいずれか1項に記載の表示装置。

### 【請求項7】

少なくとも前記第1トランジスタ、前記第2トランジスタおよび前記第3トランジスタは、p型の電界効果型トランジスタであることを特徴とする請求項1~6のうちいずれか1項に記載の表示装置。

#### 【請求項8】

前記シフトレジスタ回路は、ドレイン線を駆動するためのシフトレジスタ回路、および、 ゲート線を駆動するためのシフトレジスタ回路の少なくとも一方に適用されていることを 特徴とする請求項1~7のうちいずれか1項に記載の表示装置。

### 【発明の詳細な説明】

### [0001]

#### 【発明の属する技術分野】

この発明は、表示装置に関し、特に、シフトレジスタ回路を有する表示装置に関する。

#### [0002]

## 【従来の技術】

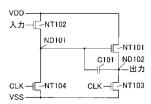

従来、ブートストラップ型のインバータ回路が知られている(たとえば、特許文献 1 参照 )。

#### [0003]

図19は、従来のブートストラップ型のインバータ回路を示した回路図である。図19を参照して、従来のブートストラップ型のインバータ回路は、nチャネルトランジスタNT101、NT102、NT103およびNT104と、容量C101とを含んでいる。トランジスタNT101のソースはノードND102に接続されているとともに、ドレインは正側電位VDDに接続されている。このトランジスタNT101のゲートはノードND101に接続されている。そして、容量C101はトランジスタNT101のゲートとソースとの間に接続されている。また、トランジスタNT102のソースはノードND101に接続されているとともに、ドレインは正側電位VDDに接続されている。このトランジスタNT102のゲートには入力信号が供給される。

#### [0004]

また、トランジスタNT103のソースは、負側電位VSSに接続されているとともに、ドレインはノードND102に接続されている。トランジスタNT104のソースは負側電位VSSに接続されているとともに、ドレインはノードND101に接続されている。

10

20

30

40

20

30

40

50

そして、トランジスタNT103およびNT104のゲートにはクロック信号CLKが供給される。

### [0005]

図19に示した従来のブートストラップ型のインバータ回路の動作としては、まず、入力信号がHレベルになるとともに、クロック信号CLKがLレベルになると、トランジスタNT102がオン状態になるとともに、トランジスタNT103およびNT104がオフ状態になる。これにより、ノードND101の電位がHレベル(VDD)に上昇するので、トランジスタNT101がオン状態になる。このため、ノードND102の電位はVDD側に上昇する。この場合、ノードND101の電位(トランジスタNT101のゲート電位)は、容量C101によって、トランジスタNT101のゲート・ソース間電圧が維持されるように、ノードND102の電位(トランジスタNT101のソース電位)の上昇に伴って上昇する。これにより、ノードND102の電位が上昇していくときにトランジスタNT101が常時オン状態に維持されるので、ノードND102の電位がVDDまで上昇する。その結果、Hレベル(VDD)の出力信号が出力される。なお、この場合のノードND101の電位はVDDよりも大きくなる。

### [0006]

この後、入力信号がLレベルになるとともに、クロック信号CLKがHレベルになると、トランジスタNT102がオフ状態になるとともに、トランジスタNT103およびNT104がオン状態になる。これにより、ノードND102の電位はLレベルに低下する。その結果、Lレベル(VSS)の出力信号が出力される。

#### [0007]

そして、上記のようなブートストラップ型のインバータ回路を直列に複数接続することによって、液晶表示装置や有機 EL(Electroluminescence)表示装置のゲート線やドレイン線を駆動するシフトレジスタ回路として用いることが可能となる。

#### [00008]

#### 【特許文献1】

特許第2921510号公報(IPC:H03K 19/094)

#### 【発明が解決しようとする課題】

しかしながら、図19に示した従来のブートストラップ型のインバータ回路では、上記したように、ノードND101の電位がVDDよりも大きくなるので、負側電位VSSに接続されたトランジスタNT104に印加されるバイアス電圧が、VDDとVSSとの電位差よりも大きくなるという不都合があった。このため、トランジスタNT104の特性が劣化しやすくなるという不都合があった。

その結果、上記した従来のブートストラップ型のインバータ回路を含むシフトレジスタ回路を、液晶表示装置や有機 EL表示装置のゲート線やドレイン線を駆動する回路に用いた場合には、液晶表示装置や有機 EL表示装置のスキャン特性が低下するという問題点があった。

### [0009]

この発明は、上記のような課題を解決するためになされたものであり、この発明の 1 つの目的は、スキャン特性が低下することを抑制することが可能な表示装置を提供することである。

#### [0010]

### 【課題を解決するための手段および発明の効果】

上記目的を達成するために、この発明の一の局面による表示装置は、第1電位側に接続され、クロック信号に応答してオンする第1導電型の第1トランジスタと、第2電位側に接続された第1導電型の第2トランジスタと、第1トランジスタのゲートと第2電位との間に接続され、互いに電気的に接続された2つのゲート電極を有する第1導電型の第3トランジスタとを含む第1回路部が複数接続されたシフトレジスタ回路を備えている。

####

この一の局面による表示装置では、上記のように、第1トランジスタのゲートと第2電位

20

30

40

50

との間に接続された第3トランジスタを、互いに電気的に接続された2つのゲート電極を有するように構成することによって、第3トランジスタに印加される電圧は2つのゲート電極により各ゲート電極に対応するソース・ドレイン間に分配されるので、第3トランジスタの各ゲート電極に対応するソース・ドレイン間には、第1電位と第1電位との電位差よりも大きい場合に対応するソース・ドレイン間には、第1電位と第1電位との電位差よりも大きいがでする。これにより、第3トランジスタに第1電位と第2電位との電位差よりも大きいバイアス電圧が印加されることに起因して、第3トランジスタの特性が劣化することが抑制されるので、シフトレジスタ回路を含む表示装置のスキャン特性が低下することを抑制することができる。また、第1トランジスタ、第2トランジスタおよび第3トランジスタを第1導電型に形成することによって、2種類の関数およびイオン注入マスクの枚数を減少させることができる。これにより、製造プロ数およびイオン注入マスクの枚数を減少させることができる。これにより、製造プスを簡略化することができるとともに、製造コストを削減することができる。

### [0012]

上記一の局面による表示装置において、好ましくは、第1回路部は、第1トランジスタのゲートと、クロック信号を供給するクロック信号線との間に接続され、互いに電気的に接続された2つのゲート電極を有するダイオード接続された第4トランジスタをさらっク信号線と第1トランジスタのゲートとの間で電流が逆流するのが防止されるので、確実に、第1トランジスタのゲートとの間で電流が逆流するのが防止されるので、確実に、第1トランジスタをオン状態に保持することができる。また、ジスタを2つのゲート・関を有するように構成することができる。また、ジジスタを2つのゲート電極により各ゲート電極に対応するソース・ドレインジスタを2つのゲート電極により各ゲート電極に対応するソース・ドレイン間に対応されるので、第4トランジスタに印かされるバイアス電圧が印かされる。この電位差よりも大きい場合にも、第4トランジスタの各ゲート電極に対応する。これにいり、第4トランジスタに第1電位と第2電位との電位差よりも大きいバイアス電圧が印かされるので、第4トランジスタの特性が劣化することが抑制されるので、カーレジスタ回路を含む表示装置のスキャン特性が低下することを抑制することができる。

## [0013]

上記一の局面による表示装置において、好ましくは、第1回路部は、第1トランジスタのゲートと、クロック信号を供給するクロック信号線との間に接続され、第3トランジスタのオン状態の期間と重ならないオン状態の期間が得られる信号に応答してオンする第4トランジスタをさらに含む。このように構成すれば、第3トランジスタと第4トランジスタとが同時にオン状態になることがないので、第3トランジスタと第4トランジスタとを介して第2電位とクロック信号線との間に貫通電流が流れることを防止することができる。その結果、第3トランジスタの特性が劣化することに起因するスキャン特性の低下を抑制しながら、消費電力が増加することを抑制することが可能な表示装置を得ることができる

### [0014]

上記一の局面による表示装置において、好ましくは、第1回路部は、第1トランジスタのゲートに接続され、第1の信号に応答してオンする第1導電型の第4トランジスタと、第4トランジスタと第1電位との間に接続され、第1の信号が入力される第4トランジスタのオン状態の期間が得られる第2の信号に応答してオンする第5トランジスタとをさらに含む。このように構成すれば、第4トランジスタおよび第5トランジスタのどちらか一方は、常にオフ状態になるので、第2電位に接続された第3トランジスタがオン状態である場合にも、第3トランジスタ、第4トランジスタおよび第5トランジスタを介して、第1電位と第2電位との間に貫通電流が流れることを抑制することができる。その結果、第3トランジスタの特性が劣化することに起因するスキャン特性の低下を抑制しながら、消費電力が増加することを抑制することが可能な表示装置を得る

ことができる。

### [0015]

上記一の局面による表示装置において、好ましくは、第1トランジスタのゲートとソースとの間には容量が接続されている。このように構成すれば、容易に、容量が接続された第1トランジスタのゲート・ソース間電圧を維持するように、第1トランジスタのソース電位の上昇または低下に伴って、第1トランジスタのゲート電位を上昇または低下させることができる。これにより、容易に、第1トランジスタを常時オン状態に維持することができる。その結果、第1回路部の出力信号(第1トランジスタのソース電位)を第1電位になるまで上昇または低下させることができる。特に、この場合には、第1トランジスタのゲート電位の上昇または低下により、第3トランジスタのバイアス電圧は第1電位と第2電位との電位差よりも大きくなるので、上記した2つのゲート電極を有する第3トランジスタによる電圧の分配によって、第3トランジスタの特性が劣化することを有効に抑制することができる。

## [0016]

上記一の局面による表示装置において、好ましくは、第 3 トランジスタは第 2 トランジスタがオン状態のときに第 1 トランジスタをオフ状態にする機能を有する。このように構成すれば、第 1 トランジスタと第 2 トランジスタとが同時にオン状態になることがないので、第 1 トランジスタと第 2 トランジスタとを介して第 1 電位と第 2 電位との間に貫通電流が流れるのを防止することができる。

## [0017]

上記一の局面による表示装置において、好ましくは、少なくとも第1トランジスタ、第2トランジスタおよび第3トランジスタは、p型の電界効果型トランジスタである。このように構成すれば、p型の電界効果型トランジスタは、n型の電界効果型トランジスタと異なり、LDD(Lightly Doped Drain)構造にする必要がないので、製造プロセスをより簡略化することができる。

### [0018]

上記一の局面による表示装置において、好ましくは、シフトレジスタ回路は、ドレイン線を駆動するためのシフトレジスタ回路、および、ゲート線を駆動するためのシフトレジスタ回路の少なくとも一方に適用されている。このように構成すれば、ドレイン線を駆動するためのシフトレジスタ回路を含む表示装置において、容易に、スキャン特性の低下を抑制することができるとともに、ゲート線を駆動するためのシフトレジスタ回路を含む表示装置において、容易に、スキャン特性の低下を抑制することができる。また、ドレイン線を駆動するためのシフトレジスタ回路との両方に適用すれば、表示装置のスキャン特性の低下をより抑制することができる。

## [0019]

### 【発明の実施の形態】

以下、本発明の実施形態を図面に基づいて説明する。

### [0020]

## (第1実施形態)

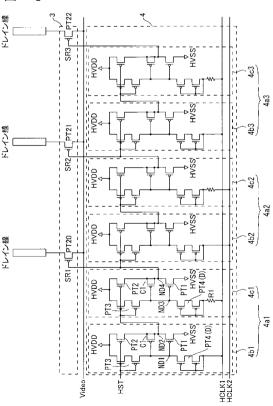

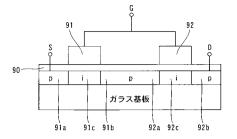

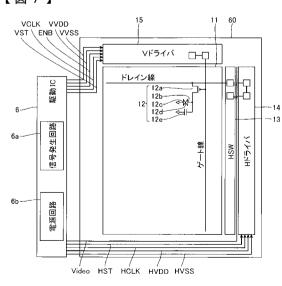

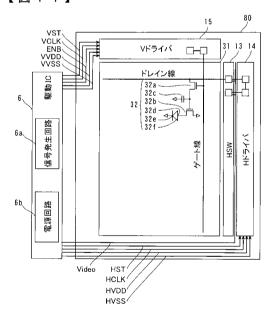

図1は、本発明の第1実施形態による液晶表示装置を示した平面図である。図2は、図1に示した第1実施形態による液晶表示装置のHドライバを構成するシフトレジスタ回路の回路図である。図3は、2つのゲート電極を有するpチャネルトランジスタの構造を説明するための模式図である。

## [0021]

まず、図1を参照して、この第1実施形態では、基板50上に、表示部1が設けられている。なお、図1の表示部1には、1画素分の構成を示している。この表示部1には、画素2がマトリクス状に配置されている。各々の画素2は、pチャネルトランジスタ2a、画素電極2b、画素電極2bに対向配置された各画素2に共通の対向電極2c、画素電極2bと対向電極2cとの間に挟持された液晶2d、および、補助容量2eによって構成されている。そして、pチャネルトランジスタ2aのソースは、ドレイン線に接続されている

10

20

30

40

20

30

40

50

とともに、ドレインは、画素電極2bおよび補助容量2cに接続されている。このpチャネルトランジスタ2aのゲートは、ゲート線に接続されている。

### [0022]

#### [0023]

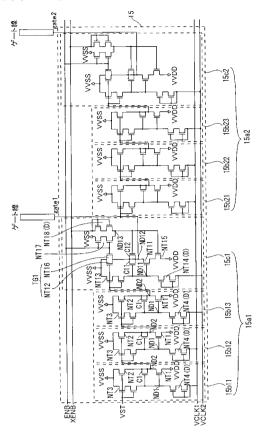

また、図2に示すように、Hドライバ4の内部には、複数段のシフトレジスタ回路4a1、4a2および4a3が設けられている。なお、図2では、図面の簡略化のため、3段のシフトレジスタ回路4a1、4a2および4a3のみ図示しているが、実際は画素の数に応じた段数が設けられている。また、1段目のシフトレジスタ回路4a1は、1つ目の第1回路部4b1および2つ目の第1回路部4c1によって構成されている。1つ目の第1回路部4b1は、pチャネルトランジスタPT1、PT2およびPT3と、ダイオード投続されたpチャネルトランジスタPT4と、pチャネルトランジスタのソース・ドレーンジスタPT1、PT2、PT3およびPT4は、それぞれ、本発明の「第1トランジスタ」、「第2トランジスタ」、「第3トランジスタ」および「第4トランジスタ」の一例である。また、2つ目の第1回路部4c1は、1つ目の第1回路部4b1と同様、pチャネルトランジスタPT1、PT2、PT3およびPT4と、容量C1とを含んでいる。また、2つ目の第1回路部4c1は、1つ目の第1回路部4b1と異なり、高抵抗R1をさらに含んでいる。

#### [0024]

ここで、第1実施形態では、1つ目の第1回路部4b1および2つ目の第1回路部4c1に設けられたpチャネルトランジスタPT1~PT4と、容量C1を構成するpチャネルトランジスタとは、すべてp型のMOSトランジスタ(電界効果型トランジスタ)からなるTFT(薄膜トランジスタ)によって構成されている。以下、pチャネルトランジスタPT1~PT4と称する。

### [0025]

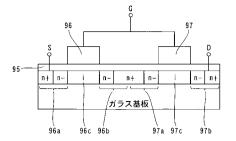

また、第1実施形態では、トランジスタPT3およびPT4は、図3に示すように、それぞれ、互いに電気的に接続された2つのゲート電極91および92を有するように形成されている。具体的には、一方のゲート電極91および他方のゲート電極92は、それぞれ、一方のチャネル領域91cおよび他方のチャネル領域92c上に、ゲート絶縁膜90を介して形成されている。そして、一方のチャネル領域91cは、一方のソース領域91aと一方のドレイン領域91bとに挟まれるように形成されており、他方のチャネル領域92cは、他方のソース領域92aと他方のドレイン領域92bとに挟まれるように形成されている。また、ドレイン領域91bとソース領域92aとは、共通の不純物領域により構成されている。

### [0026]

そして、図2に示すように、1つ目の第1回路部4b1において、トランジスタPT1の

20

30

40

50

ソースはノードND2に接続されているとともに、ドレインは負側電位HVSSに接続されている。このトランジスタPT1のゲートはノードND1に接続されているとともに、トランジスタPT1のゲートにはクロック信号HCLK1が供給される。トランジスタPT2のソースは正側電位HVDDに接続されているとともに、ドレインはノードND2に接続されている。このトランジスタPT2のゲートにはスタート信号HSTが供給される

#### [0027]

ここで、第1実施形態では、トランジスタPT3は、トランジスタPT1のゲートと正側電位HVDDとの間に接続されている。このトランジスタPT3のゲートにはスタート信号HSTが供給される。そして、トランジスタPT3はトランジスタPT2がオン状態のときにトランジスタPT1をオフ状態にするために設けられている。これにより、トランジスタPT2とトランジスタPT1とが同時にオン状態になることが抑制される。

#### [0028]

また、第1実施形態では、容量 C 1 はトランジスタ P T 1 のゲートとソースとの間に接続されている。またトランジスタ P T 4 はトランジスタ P T 1 のゲートとクロック信号線(H C L K 1 )との間に接続されている。このトランジスタ P T 4 により、クロック信号 H C L K 1 の H レベルのパルス電圧が、クロック信号線(H C L K 1 )から容量 C 1 へ逆流することが抑制される。

#### [0029]

また、2つ目の第1回路部4c1における回路構成は、基本的に1つ目の第1回路部4b1の回路構成と同様である。ただし、2つ目の第1回路部4c1では、トランジスタPT1のソースおよびトランジスタPT2のドレインは、それぞれノードND4に接続されているとともに、トランジスタPT1のゲートはノードND3に接続されている。また、高抵抗R1はトランジスタPT4とクロック信号線(HCLK1)との間に接続されている

### [0030]

そして、ノードND4(出力ノード)からは、1段目のシフトレジスタ回路4a1の出力信号SR1が出力される。この出力信号SR1は水平スイッチ3に供給される。

### [0031]

水平スイッチ3は、複数のトランジスタPT20、PT21およびPT22を含んでいる。なお、図2では、図面の簡略化のため、3つのトランジスタPT20、PT21およびPT22のみを図示しているが、実際は画素の数に応じた数だけ設けられている。トランジスタPT20、PT21およびPT22のゲートは、それぞれ、1段目~3段目のシフトレジスタ回路4a1~4a3の出力SR1、SR2およびSR3に接続されている。また、トランジスタPT20~PT22のドレインは、それぞれ、各段のドレイン線に接続されている。また、pチャネルトランジスタPT20、PT21およびPT22のソースは、それぞれ、1本のビデオ信号線(Video)に接続されている。また、1段目のシフトレジスタ回路4a1のノードND4(出力ノード)には、2段目のシフトレジスタ回路4a2が接続されている。

### [0032]

2 段目のシフトレジスタ回路 4 a 2 は、1つ目の第1回路部4b2および2つ目の第1回路部4c2によって構成されている。この2 段目のシフトレジスタ回路4a2の1つ目の第1回路部4b2および2つ目の第1回路部4c2の回路構成は、それぞれ、上記した1段目のシフトレジスタ回路4a1の1つ目の第1回路部4b1および2つ目の第1回路部4c1の回路構成と同様である。また、2段目のシフトレジスタ回路4a2の出力ノードからは出力信号SR2が出力される。また、2段目のシフトレジスタ回路4a2の出力ノードには3段目のシフトレジスタ回路4a3が接続されている。シフトレジスタ回路4a1~4a3の出力SR1~SR3は、ビデオ信号線の数(たとえば、赤(R)、緑(G)および青(B)の3種類のビデオ信号Videoが入力される場合は3本になる)に応じて設けられた水平スイッチ3のソースに入力される。

20

30

40

50

### [0033]

3 段目のシフトレジスタ回路4a3は、1つ目の第1回路部4b3および2つ目の第1回路部4c3によって構成されている。この3段目のシフトレジスタ回路4a3の1つ目の第1回路部4b3および2つ目の第1回路部4c3の回路構成は、それぞれ、上記した1段目のシフトレジスタ回路4a1の1つ目の第1回路部4b1および2つ目の第1回路部4c1の回路構成と同様である。また、3段目のシフトレジスタ回路4a3の出力ノードからは出力信号SR3が出力される。また、3段目のシフトレジスタ回路4a3の出力ノードには、4段目のシフトレジスタ回路(図示せず)が接続されている。

### [0034]

4 段目以降のシフトレジスタ回路の回路構成は、上記した1段目~3段目のシフトレジスタ回路4a1~4a3の回路構成と同様である。なお、上記した2段目のシフトレジスタ回路4a2には、クロック信号線(HCLK2)が接続されている。また、上記した3段目のシフトレジスタ回路4a1と同様、クロック信号線(HCLK1)が接続されている。このように、複数段のシフトレジスタ回路には、交互にクロック信号線(HCLK1)とクロック信号線(HCLK2)とが接続されている。また、後段のシフトレジスタ回路は前段のシフトレジスタ回路の出力ノードに接続されるように構成されている。

#### [0035]

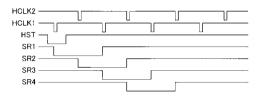

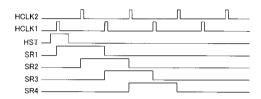

図4は、図2に示した第1実施形態による液晶表示装置のHドライバのシフトレジスタ回路のタイミングチャートである。なお、図4において、SR1、SR2、SR3およびSR4は、それぞれ、1段目、2段目、3段目および4段目のシフトレジスタ回路からの出力信号を示している。次に、図2および図4を参照して、第1実施形態による液晶表示装置のHドライバのシフトレジスタ回路の動作について説明する。

#### [0036]

まず、初期状態として、Hレベル(HVDD)のスタート信号HSTが、1段目のシフトレジスタ回路4a1の1つ目の第1回路部4b1に入力されている。

これにより、1つ目の第1回路部4b1のトランジスタPT2およびPT3がオフ状態になるとともに、トランジスタPT1がオン状態になるため、ノードND2の電位はLレベルとなっている。このため、2つ目の第1回路部4c1において、トランジスタPT2およびPT3はオン状態になる。これにより、ノードND3の電位がHレベルになるので、トランジスタPT1はオフ状態になる。このように、2つ目の第1回路部4c1において、トランジスタPT2がオン状態になるとともに、トランジスタPT1がオフ状態になるので、ノードND4の電位はHレベルになる。これにより、初期状態では、1段目のシフトレジスタ回路4a1からHレベルの出力信号SR1が出力されている。

### [0037]

1段目のシフトレジスタ回路4a1からHレベルの出力信号SR1が出力されている状態で、Lレベル(HVSS)のスタート信号HSTが入力されると、1つ目の第1回路部4b1において、トランジスタPT2およびPT3はオン状態になる。これにより、ノードND1およびND2の電位が共にHレベルになるので、トランジスタPT1はオフ状態に保持される。そして、ノードND2の電位がHレベルになることにより、2つ目の第1回路部4c1において、トランジスタPT2およびPT3はオフ状態になる。このとき、ノードND3の電位がHレベルの状態で保持されるので、トランジスタPT1は、オフ状態のまま保持される。このため、ノードND4の電位がHレベルのまま保持されるので、1段目のシフトレジスタ回路4a1からHレベルの出力信号SR1が出力される。

#### [0038]

次に、1つ目の第1回路部4b1において、トランジスタPT4を介してLレベル(HVSS)のクロック信号HCLK1が入力される。この際、トランジスタPT3がオン状態になっているので、ノードND1の電位はHレベルのまま保持される。これにより、トランジスタPT1はオフ状態のまま保持される。なお、クロック信号HCLK1がLレベルの期間中、トランジスタPT4およびPT3を介してクロック信号線(HCLK1)と正

20

30

40

50

側電位HVDDとの間に貫通電流が流れる。

### [0039]

一方、 2 つ目の第 1 回路部 4 c 1 においても、高抵抗 R 1 およびトランジスタ P T 4 を介して L レベル ( H V S S ) のクロック信号 H C L K 1 が入力される。

この際、トランジスタPT3がオフ状態になっているので、ノードND3の電位がLレベルになることによりトランジスタPT1はオン状態になる。この際、高抵抗R1によりトランジスタPT1がオン状態になるときの応答速度が遅くなる。

## [0040]

このとき、2つ目の第1回路部4c1において、トランジスタPT2がオフ状態になっているので、オン状態のトランジスタPT1を介してノードND4の電位はHVSS側に低下する。この場合、ノードND3の電位(トランジスタPT1のゲート電位)は、容量C1によって、トランジスタPT1のゲート・ソース間電圧が維持されるように、ノードND4の電位(トランジスタPT1のソース電位)の低下に伴って低下する。また、トランジスタPT3がオフ状態であるとともに、ダイオード接続されたトランジスタPT4には、クロック信号線(HCLK1)からのHレベルの信号がノードND3側に逆流することはないので、容量C1の保持電圧(トランジスタPT1のゲート・ソース間電圧)は維持される。これにより、ノードND4の電位が低下していくときにトランジスタPT1が常時オン状態に維持されるので、ノードND4の電位はHVSSまで低下する。

その結果、1段目のシフトレジスタ回路4a1からLレベルの出力信号SR1が出力される。

#### [0041]

なお、2つ目の第1回路部4c1において、ノードND4の電位がHVSSまで低下したときのノードND3の電位はHVSSよりも低くなっている。このため、正側電位HVDDに接続されたトランジスタPT3に印加されるバイアス電圧はHVDDとHVSSとの電位差よりも大きくなる。また、クロック信号HCLK1がHレベル(HVDD)なった場合には、クロック信号線(HCLK1)に接続されたトランジスタPT4に印加されるバイアス電圧も、HVDDとHVSSとの電位差よりも大きくなる。

### [0042]

次に、1つ目の第1回路部4b1において、Hレベル(HVDD)のスタート信号HSTが入力されると、トランジスタPT2およびPT3がオフ状態になる。この場合には、ノードND1およびND2はHレベルに保持された状態でフローティング状態になる。このため、他の部分へ影響が与えられることはないので、1段目のシフトレジスタ回路4a1からはLレベルの出力信号SR1が維持される。

## [0043]

次に、1つ目の第1回路部4b1において、再度、トランジスタPT4を介してLレベル(HVSS)のクロック信号HCLK1が入力される。これにより、トランジスタPT1がオン状態になるのでノードND2の電位はHVSS側に低下する。この場合、ノードND1の電位は、容量C1によってトランジスタPT1のゲート・ソース間電圧が維持されるように、ノードND2の電位の低下に伴って低下する。また、トランジスタPT3がオフ状態であるとともに、ダイオード接続されたトランジスタPT4にはクロック信号線(HCLK1)からのHレベルの信号がノードND1側に逆流することはないので容量C1の保持電圧は維持される。これにより、ノードND2の電位が低下していくときにトランジスタPT1が常時オン状態に維持されるので、ノードND2の電位はHVSSまで低下する。このため、2つ目の第1回路部4c1のトランジスタPT2およびPT3はオン状態になる。なお、ノードND2の電位がHVSSまで低下したときのノードND1の電位は、HVSSよりも低くなっている。

## [0044]

この際、第1実施形態では、2つ目の第1回路部4c1において、トランジスタPT3に よってトランジスタPT1がオフ状態にされるので、トランジスタPT1とトランジスタ

20

30

40

50

PT2とが同時にオン状態になることが抑制される。これにより、トランジスタPT1およびPT2を介して正側電位HVDDと負側電位HVSSとの間に貫通電流が流れることが抑制される。

#### [0045]

そして、2つ目の第1回路部4c1において、トランジスタPT2がオン状態になるとともに、トランジスタPT1がオフ状態になることにより、ノードND4の電位はHVSSからHVDDに上昇してHレベルになる。このため、1段目のシフトレジスタ回路4a1からHレベルの出力信号SR1が出力される。

#### [0046]

以上のように、第1実施形態によるシフトレジスタ回路4a1では、1つ目の第1回路部4b1にLレベルのスタート信号HSTが入力されているときに、Lレベルのクロック信号HCLK1が入力されると、2つ目の第1回路部4c1からLレベルの出力信号SR1が出力される。そして、1つ目の第1回路部4b1にHレベルの出力信号SR1が出力されている状態で、再度、Lレベルのクロック信号HCLK1が入力されると、2つ目の第1回路部4c1からの出力信号SR1はHレベルになる。

#### [0047]

なお、1段目のシフトレジスタ回路4a1の2つ目の第1回路部4c1からの出力信号SR1は、2段目のシフトレジスタ回路4a2の1つ目の第1回路部4b2に入力される。2段目のシフトレジスタ回路4a2では、1つ目の第1回路部4b2に1段目のシフトレジスタ回路4a1のLレベルの出力信号SR1が入力されている場合に、Hレベルのクロック信号HCLK2が入力されると、2つ目の第1回路部4c2からLレベルの出力信号SR2が出力される。さらに、3段目のシフトレジスタ回路4a3では、1つ目の第1回路部4b3に2段目のシフトレジスタ回路4a2のLレベルの出力信号SR2が入力されている場合に、Lレベルのクロック信号HCLK1およびHレベルのクロック信号HCLK2が入力されると、3つ目の第1回路部4c3からLレベルの出力信号SR3が出力される。このように、前段のシフトレジスタ回路からLレベルになるタイミングが互いにずれたクロック信号HCLK1およびHCLK2が、各段のシフトレジスタ回路からLレベルの出力信号が出力される。これにより、各段のシフトレジスタ回路からLレベルの出力信号が出力されるタイミングがシフトする。

#### [0048]

タイミングがシフトしたLレベルの信号が水平スイッチ3のトランジスタPT20、PT21およびPT22のゲートに入力されることにより、トランジスタPT20、PT21およびPT22は、順次、オン状態になる。これにより、各段のドレイン線にビデオ信号線Videoからビデオ信号が供給されるので、各段のドレイン線は、順次、駆動(走査)される。そして、1本のゲート線に繋がる全ての段のドレイン線の走査が終了すると、次のゲート線が選択される。そして、再び各段のドレイン線が順次走査された後、次のゲート線が選択される。この動作が最後のゲート線に繋がる各段のドレイン線の走査が終了する。されるまで繰り返されることによって一画面の走査が終了する。

### [0049]

第1実施形態では、上記のように、トランジスタPT1のゲートと正側電位HVDDとの間に接続されたトランジスタPT3を、互いに電気的に接続された2つのゲート電極91および92を有するように構成することによって、トランジスタPT3に印加される電圧は、一方のゲート電極91に対応するソース・ドレイン間と他方のゲート電極92に対応するソース・ドレイン間とに概ね半分程度ずつ(電圧の分配比率はトランジスタサイズなどによって変動)分配される。このため、トランジスタPT3に印加されるバイアス電圧がHVSSとHVDDとの電位差よりも大きくなった場合にも、トランジスタPT3の一方のゲート電極91に対応するソース・ドレイン間および他方のゲート電極92に対応するソース・ドレイン間には、それぞれ、HVSSとHVDDとの電位差よりもが印加される。これにより、トランジスタPT3にHVSSとHVDDとの電位差よりも

大きいバイアス電圧が印加されることに起因して、 p チャネルトランジスタ P T 3 の特性が劣化することが抑制されるので、シフトレジスタ回路 4 a 1 ~ 4 a 3 を有する H ドライバ 4 を含む液晶表示装置のスキャン特性が低下することを抑制することができる。

#### [0050]

また、第1実施形態では、PチャネルトランジスタPT1のゲートとクロック信号線(HCLK)との間のトランジスタPT4においても、互いに電気的に接続された2つのゲート電極91および92を有するように構成しているので、上記したトランジスタPT3と同様、トランジスタPT4に印加されるバイアス電圧がHVSSとHVDDとの電位差よりも大きくなった場合にも、トランジスタPT4の特性が劣化することが抑制される。その結果、トランジスタPT4の特性が劣化することに起因して、シフトレジスタ回路4a1~4a3を含む液晶表示装置のスキャン特性が低下することをも抑制することができる

10

#### [0051]

また、第1実施形態では、1つ目の第1回路部4b1および2つ目の第1回路部4c1に設けられたトランジスタPT1~PT4と、容量C1を構成するトランジスタとを、すべてp型のMOSトランジスタ(電界効果型トランジスタ)からなるTFT(薄膜トランジスタ)で構成することによって、2種類の導電型のトランジスタを含むシフトレジスタ回路を形成する場合に比べてイオン注入工程の回数およびイオン注入マスクの枚数を減少させることができる。これにより、製造プロセスを簡略化することができるとともに、製造コストを削減することができる。また、p型の電界効果型トランジスタは、n型の電界効果型トランジスタと異なり、LDD(Lightly Doped Drain)構造にする必要がないので、製造プロセスをより簡略化することができる。

20

### [0052]

### (第2実施形態)

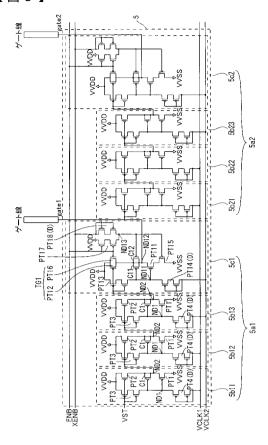

図5は、本発明の第2実施形態による液晶表示装置のVドライバを構成するシフトレジスタ回路の回路図である。図5を参照して、この第2実施形態では、上記第1実施形態と異なり、ゲート線を駆動(走査)するためのVドライバに本発明を適用する場合について説明する。

[0053]

30

すなわち、この第2実施形態による液晶表示装置のVドライバ5では、図5に示すように 、複数段のシフトレジスタ回路5a1および5a2が設けられている。なお、図5では、 図面の簡略化のため2段のシフトレジスタ回路5a1および5a2のみ図示している。ま た、 1 段目のシフトレジスタ回路 5 a 1 は、 1 つ目の第 1 回路部 5 b 1 1 、 2 つ目の第 1 回路部5 b 1 2 および3 つ目の第1 回路部5 b 1 3 と、第2 回路部5 c 1 とによって構成 されている。1つ目の第1回路部5b11は、トランジスタPT1、PT2およびPT3 と、ダイオード接続されたトランジスタPT4と、トランジスタのソース・ドレイン間を 接続することにより形成された容量C1とを含んでいる。また、第2回路部5c1は、上 記した1つ目の第1回路部5b11のトランジスタPT1、PT2、PT3およびPT4 と、容量C1とにそれぞれ対応するトランジスタPT11、PT12、PT13およびP T14と、容量C11とを含んでいる。なお、トランジスタPT11、PT12、PT1 3 および P T 1 4 は、それぞれ、本発明の「第 1 トランジスタ」、「第 2 トランジスタ」 「第3トランジスタ」および「第4トランジスタ」の一例である。また、第2回路部5 c 1 は、上記した 1 つ目の第 1 回路部 5 b 1 1 と異なり、トランジスタ P T 1 5 、 P T 1 6 およびPT17と、ダイオード接続されたトランジスタPT18と、トランジスタのソ ース・ドレイン間を接続することにより形成された容量 C 1 2 とをさらに含んでいる。

40

## [0054]

20

30

40

50

[0055]

また、第2実施形態では、トランジスタPT3、PT4、PT13、PT14、PT17 およびPT18は、それぞれ、図3に示した第1実施形態と同様、互いに電気的に接続された2つのゲート電極を有するように形成されている。

[0056]

そして、図5に示すように、1つ目の第1回路部5b11において、トランジスタPT1のソースはノードND2に接続されているとともに、ドレインは負側電位 VVSSに接続されている。このトランジスタPT1のゲートはノードND1に接続されているとともに、トランジスタPT1のゲートにはクロック信号 VCLK1が供給される。トランジスタPT2のソースは正側電位 VVDDに接続されているとともに、ドレインはノードND2に接続されている。このトランジスタPT2のゲートにはスタート信号 VSTが供給される。

[0057]

ここで、第2実施形態では、トランジスタPT3はトランジスタPT1のゲートと正側電位VVDDとの間に接続されている。このトランジスタPT3のゲートにはスタート信号VSTが供給される。そして、トランジスタPT3はトランジスタPT2がオン状態のときにトランジスタPT1をオフ状態にするために設けられている。これにより、トランジスタPT2とトランジスタPT1とが同時にオン状態になることが抑制される。

[0058]

また、第2実施形態では、容量 C 1 はトランジスタ P T 1 のゲートとソースとの間に接続されている。また、トランジスタ P T 4 はトランジスタ P T 1 のゲートとクロック信号線(V C L K 1)との間に接続されている。このトランジスタ P T 4 により、クロック信号 V C L K 1 の H レベルのパルス電圧が、クロック信号線(V C L K 1)から容量 C 1 へ逆流することが抑制される。

[0059]

また、2つ目の第1回路部5 b 1 2 および3つ目の第1回路部5 b 1 3の回路構成は、上記した1つ目の第1回路部5 b 1 1 の回路構成と同様である。そして、1つ目の第1回路部5 b 1 3 は直列に接続されている。そして、第2回路部5 c 1 は3つ目の第1回路部5 b 1 3のノードND2に接続されている。

[0060]

また、第2回路部5 c 1 において、トランジスタPT11、PT12、PT13およびPT14、および、容量C11は、それぞれ、基本的に1つ目の第1回路部5 b 1 1 のトランジスタPT1、PT2、PT3およびPT4、および、容量C1に対応した位置に接続されている。ただし、第2回路部5 c 1 では、トランジスタPT11のソースおよびトランジスタPT12のドレインは、それぞれ、ノードND12に接続されているとともに、トランジスタPT11のゲートはノードND11に接続されている。

[0061]

また、トランジスタPT15は負側電位VVSSとトランジスタPT11との間に接続されている。このトランジスタPT15のゲートはノードND13に接続されているとともに、トランジスタPT15のゲートには反転イネーブル信号XENBが供給される。そして、容量C12はトランジスタPT15のゲートとソースとの間に接続されている。トランジスタPT16はトランジスタPT12とともに、トランスファゲートTG1を構成している。

[0062]

また、トランジスタPT17のソースは正側電位VVDDに接続されているとともに、ドレインはノードND13に接続されている。このトランジスタPT17のゲートにはイネーブル信号ENBが供給される。トランジスタPT18はトランジスタPT15のゲートと反転イネーブル信号線(XENB)との間に接続されている。

[0063]

20

30

40

50

また、ノードND12(出力ノード)から1段目のシフトレジスタ回路5a1の出力信号gate1が出力される。このノードND12にはゲート線が接続されている。また、ノードND12には2段目のシフトレジスタ回路5a2が接続されている。

#### [0064]

2 段目のシフトレジスタ回路 5 a 2 は、1つ目の第1回路部 5 b 2 1、2つ目の第1回路部 5 b 2 2 および 3 つ目の第1回路部 5 b 2 3 と、第2回路部 5 c 2 とによって構成されている。この2 段目のシフトレジスタ回路 5 a 2 の 1 つ目の第1回路部 5 b 2 1、2 つ目の第1回路部 5 b 2 2 ない3つ目の第1回路部 5 b 2 1、2つ目の第1回路部 5 b 2 2 ない3つ目の第1回路部 5 b 2 1、2つ目の第1回路部 5 b 2 1、2つ目の第1回路部 5 b 2 1、2 口目の第1回路部 5 b 2 1、2 回日の第1回路部 5 b 2 1、2 同日の第1回路部 5 b 2 1、2 同日の第1回路部 5 b 2 1、2 同日のシフトレジスタ回路 5 a 2 の第2 回路部 5 c 2 は、上記した 1 段目のシフトレジスタ回路 5 a 2 の出力ノードにはゲート線が接続されている。また、2 段目のシフトレジスタ回路 5 a 2 の出力ノードには 3 段目のシフトレジスタ回路 6 に 2 に 1 段目のシフトレジスタ回路 7 に は 3 段目のシフトレジスタ回路 8 a 1 の回路構成と同様である。

### [0065]

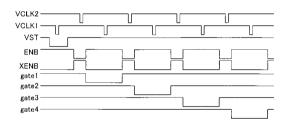

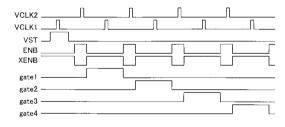

図6は、図5に示した第2実施形態による液晶表示装置のVドライバのシフトレジスタ回路のタイミングチャートである。なお、図6において、gate1、gate2、gate3 およびgate4は、それぞれ、1段目、2段目、3段目および4段目のシフトレジスタ回路からゲート線に出力される出力信号を示している。次に、図5および図6を参照して、第2実施形態による液晶表示装置のVドライバのシフトレジスタ回路の動作について説明する。

#### [0066]

図5に示した第2実施形態の1段目のシフトレジスタ回路5 a 1 の1つ目の第1回路部5 b 1 1 および2つ目の第1回路部5 b 1 2 の構成は、図2に示した第1実施形態の1段目のシフトレジスタ回路4 a 1 の1つ目の第1回路部4 b 1 および2つ目の第1回路部4 c 1 から高抵抗R 1 を除いた構成に相当する。したがって、第2実施形態の1段目のシフトレジスタ回路5 a 1 の1つ目の第1回路部5 b 1 1 および2つ目の第1回路部5 b 1 2 のスタート信号 V S T およびクロック信号 V C L K 1に応答して行われる動作は、図2に示した第1実施形態の1段目のシフトレジスタ回路4 a 1 の 1 つ目の第1回路部4 b 1 および2つ目の第1回路部4 c 1 のスタート信号 H S T およびクロック信号 H C L K 1 に応答して行われる動作に相当する。

## [0067]

すなわち、まず、初期状態として、Hレベル(VVDD)のスタート信号VSTが1段目のシフトレジスタ回路5a1の1つ目の第1回路部5b11に入力される。これにより、上記した第1実施形態のHドライバ4と同様の動作により、2つ目の第1回路部5b12からはHレベルの信号が出力される。このHレベルの信号は、3つ目の第1回路部5b13のトランジスタPT2およびPT3がオフ状態になるので、3つ目の第1回路部5b13からはLレベルの信号が出力される。

#### [0068]

この3つ目の第1回路部5 b 1 3 からの L レベルの信号は、第2回路部5 c 1 のトランジスタ P T 1 3 のゲートおよびトランスファゲート T G 1 の一方のゲートに入力される。これにより、第2回路部5 c 1 のトランジスタ P T 1 3 およびトランスファゲート T G 1 がオン状態になるので、ノード N D 1 2 の電位は H レベルになる。このため、初期状態では、1段目のシフトレジスタ回路5 a 1 からゲート線へ H レベルの出力信号 g a t e 1 が出力されている。

#### [0069]

この状態で、Lレベル(VVSS)のスタート信号VSTが入力されると、上記した第1

20

30

40

50

実施形態のHドライバ4と同様の動作により、2つ目の第1回路部5b12からHレベルの信号が出力されるので、初期状態と同様、1段目のシフトレジスタ回路5a1からゲート線へHレベルの出力信号gate1が続けて出力される。

#### [0070]

次に、Lレベル(VVSS)のクロック信号VCLK1が入力されると、上記した第1実施形態のHドライバ4と同様の動作により、2つ目の第1回路部5b12からはLレベルの信号が出力される。このLレベルの信号が3つ目の第1回路部5b13のトランジスタPT2およびPT3はオン状態になる。このとき、3つ目の第1回路部5b13のトランジスタPT1がオフ状態であるので、3つ目の第1回路部5b13のトランジスタPT1がオフ状態であるので、3つ目の第1回路部5b13からHレベルの信号が出力される。このHレベルの信号は、第2回路部5c1のトランジスタPT13のゲートおよびトランスファゲートTG1の一方のゲートに入力される。このとき、イネーブル信号ENBがHレベル(VVDD)に保持されているので、トランスファゲートTG1はオフ状態になる。また、ノードND11がHレベルに保持された状態でフローティング状態になるので、トランジスタPT11もオフ状態のまま維持される。これにより、1段目のシフトレジスタ回路5a1からゲート線へHレベルの出力信号gate1が続けて出力される。

### [0071]

次に、Hレベル(VVDD)のスタート信号VSTが入力された場合にも、上記した第1 実施形態のHドライバ4と同様の動作により、2つ目の第1回路部5b12からは、Lレベルの信号が続けて出力される。これにより、1段目のシフトレジスタ回路5a1からゲート線へHレベルの出力信号gate1が続けて出力される。

#### [0072]

次に、イネーブル信号 E N B が L レベル( V V S S )になるとともに、反転イネーブル信号 X E N B が H レベル( V V D D )になる。これにより、第 2 回路部 5 c 1 において、 L レベルのイネーブル信号 E N B が入力されるトランスファゲート T G 1 はオン状態になる。また、 L レベルのイネーブル信号 E N B がトランジスタ P T 1 7 のゲートにも入力されるので、トランジスタ P T 1 7 はオン状態になる。これにより、ノード N D 1 3 の電位が H レベルになるので、ノード N D 1 3 にゲートが接続されたトランジスタ P T 1 5 はオフ 状態になる。これにより、ノード N D 1 2 の電位が H レベルになるので、 1 段目のシフトレジスタ回路 5 a 1 からゲート線へ H レベルの出力信号 g a t e 1 が続けて出力される。

[0073]

次に、イネーブル信号ENBがLレベル(VVSS)の状態で、3つ目の第1回路部5b13のトランジスタPT4を介して、Lレベル(VVSS)のクロック信号VCLK2が入力される。このとき、3つ目の第1回路部5b13のトランジスタPT2およびPT3がオン状態であるので、3つ目の第1回路部5b13のノードND1の電位はHレベルに保持される。これにより、3つ目の第1回路部5b13のトランジスタPT1がオフ状態になるので、3つ目の第1回路部5b13のトランジスタPT1がオフ状態になるので、3つ目の第1回路部5b13からはHレベルの信号が出力される。このHレベルの信号は、第2回路部5c1のトランジスタPT13のゲートおよびトランスファゲートTG1の一方のゲートに入力される。これにより、トランジスタPT13はオフ状態に保持される。これに対して、トランスファゲートTG1はオン状態に保持される。

### [0074]

一方、第2回路部5 c 1 にも、トランジスタPT14を介してLレベル(VVSS)のクロック信号VCLK2が入力される。これにより、ノードND11の電位がLレベルになるので、トランジスタPT11はオン状態になる。ただし、この場合、イネーブル信号ENBがLレベルであるので、pチャネルトランジスタPT17はオン状態に保持される。このため、トランジスタPT15がオフ状態に保持されるので、結局、ノードND12はHレベルに保持される。これにより、この状態では、1段目のシフトレジスタ回路5 a 1からゲート線へHレベルの出力信号gate1が保持される。

20

30

40

50

#### [0075]

この後、イネーブル信号 ENB が H レベル( V V D D )になるとともに、反転イネーブル信号 X ENB が L レベル( V V S S )になることによって、トランスファゲートTG 1 およびトランジスタ P T 1 7 はオフ状態になる。また、トランジスタ P T 1 8 を介してゲートに L レベルの反転イネーブル信号 X E N B が入力されるトランジスタ P T 1 5 はオン状態になる。

#### [0076]

なお、このときのノードND13の電位は、容量C12の機能により、VVSSよりも低くなっている。このため、正側電位VVDDに接続されたトランジスタPT17に印加されるバイアス電圧は、VVDDとVVSSとの電位差よりも大きくなる。また、反転イネーブル信号XENBがHレベル(VVDD)になった場合には、反転イネーブル信号線( XENB)に接続されたトランジスタPT18に印加されるバイアス電圧も、VVDDとVVSSとの電位差よりも大きくなる。

## [0077]

これにより、トランジスタPT11およびPT15がオン状態になるとともに、トランスファゲートTG1がオフ状態になるので、ノードND12の電位は容量C11およびC12の機能によりVVSSまで低下しLレベルになる。このため、1段目のシフトレジスタ回路5a1からゲート線へLレベルの出力信号gate1が出力される。この状態で、クロック信号VCLK1がLレベル(VVSS)になった場合にも、1段目のシフトレジスタ回路5a1からゲート線への出力信号gate1はLレベルに保持される。

#### [0078]

なお、ノードND12の電位がVVSSまで低下したときのノードND11の電位はVVSSよりも低くなっている。このため、正側電位VVDDに接続されたトランジスタPT13に印加されるバイアス電圧は、VVDDとVVSSとの電位差よりも大きくなる。また、クロック信号VCLK2がHレベル(VVDD)なった場合には、クロック信号線(VCLK2)に接続されたトランジスタPT14に印加されるバイアス電圧も、VVDDとVVSSとの電位差よりも大きくなる。

#### [0079]

次に、イネーブル信号 ENB が L レベル(VVSS)になるとともに、反転イネーブル信号 X E N B が H レベル(VVDD)になることによって、トランスファゲート T G 1 およびトランジスタ P T 1 7 はオン状態になる。トランジスタ P T 1 7 がオン状態になることによりノード N D 1 3 の電位は H レベルになる。これにより、ゲートがノード N D 1 3 に接続されたトランジスタ P T 1 5 はオフ状態になる。このため、トランスファゲート T G 1 がオン状態になるとともに、トランジスタ P T 1 5 がオフ状態になることによりノード N D 1 2 の電位は H レベルになる。これにより、1 段目のシフトレジスタ回路 5 a 1 からゲート線へ H レベルの出力信号 g a t e 1 が出力される。

## [0080]

また、1段目のシフトレジスタ回路5a1からのHレベルの出力信号gate1は、2段目のシフトレジスタ回路5a2の第1回路部5b21にも入力される。2段目以降のシフトレジスタ回路は、前段のシフトレジスタ回路からの出力信号、クロック信号VCLK1およびVCLK2、イネーブル信号ENBおよび反転イネーブル信号により、上記した1段目のシフトレジスタ回路5a1と同様の動作を行う。これにより、各段のゲート線が、順次、駆動(走査)される。この場合、イネーブル信号ENBがLレベルの間は、シフトレジスタ回路の出力が強制的にHレベルに保持されるので、図6に示したようなタイミングでイネーブル信号ENBをLレベルにすることによって、前段のシフトレジスタ回路のLレベルの出力信号が重なることが防止されている。

#### [0081]

第2実施形態では、上記のように、トランジスタPT3、PT4、PT13、PT14、PT17およびPT18を、互いに電気的に接続された2つのゲート電極を有するように構成することによって、上記第1実施形態と同様、トランジスタPT3、PT4、PT1

3、PT14、PT17およびPT18に印加されるバイアス電圧がVVSSとVVDDとの電位差よりも大きくなった場合にも、トランジスタPT3、PT4、PT13、PT14、PT13、PT14、PT13、PT14、PT13、PT3、PT4、PT13、PT4、PT13、PT4、PT13、PT14、PT13、PT14、PT17およびPT18の特性が劣化することが抑制される。その結果、トランジスタPT3、PT4、PT13、PT14、PT13、PT14、PT13、PT14、PT13、PT14、PT13、PT14、PT15を含む液晶表示装置のスキャン特性が低下することを抑制することができる。

[0082]

10

なお、第2実施形態のその他の効果は、上記第1実施形態と同様である。

[0083]

(第3実施形態)

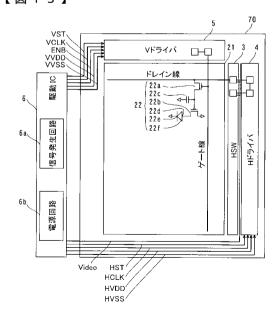

図7は、本発明の第3実施形態による液晶表示装置を示した平面図である。図8は、図7に示した第3実施形態による液晶表示装置のHドライバを構成するシフトレジスタ回路の回路図である。図9は、2つのゲート電極を有するnチャネルトランジスタの構造を説明するための模式図である。この第3実施形態では、ドレイン線を駆動(走査)するためのHドライバをnチャネルトランジスタで構成する例について説明する。

[0084]

20

まず、図7を参照して、この第3実施形態の液晶表示装置では、基板60上に、表示部11が設けられている。なお、図7の表示部11には、1画素分の構成を示している。また、表示部11にマトリクス状に配置された各画素12は、nチャネルトランジスタ12a、画素電極12b、画素電極12bに対向配置された各画素12に共通の対向電極12c、画素電極12bと対向電極12cとの間に挟持された液晶12d、および、補助容量12cに接続されているとともに、ドレインはドレイン線に接続されている。このnチャネルトランジスタ12aのソースは画接続されている。このnチャネルトランジスタ12aのゲートはゲート線に接続されている。また、表示部11の一辺に沿うように、基板60上に、表示部11のドレイン線を駆動(走査)するための水平スイッチ(HSW)13およびHドライバ14が設けられている。また、表示部11の他の辺に沿うように、基板60上に、表示部11のゲート線を駆動(た、表示部11の他の辺に沿うように、基板60上に、表示部11のゲート線を駆動(たまた、表示部11の他の辺に沿うように、基板60上に、表示部11のがテートに変するためのVドライバ15が設けられている。なお、水平スイッチ13には、図7ではスイッチを2つのみ図示しているが、画素の数に応じた数だけ配置されている。

30

[0085]

40

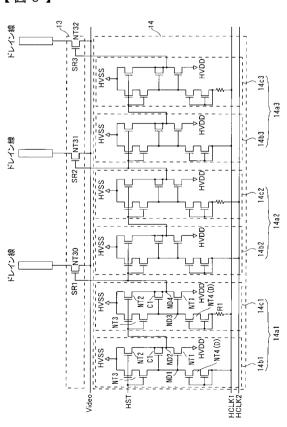

また、図8に示すように、Hドライバ14の内部には、複数段のシフトレジスタ回路14a1、14a2および14a3が設けられている。なお、図8では、図面の簡略化のため、3段のシフトレジスタ回路14a1、14a2および14a3のみ図示しているが、実際は画素の数に応じた段数が設けられている。また、1段目のシフトレジスタ回路14a1は、1つ目の第1回路部14b1および2つ目の第1回路部14c1によって構成されている。また、1つ目の第1回路部14b1は、nチャネルトランジスタNT1、NT2およびNT3と、ダイオード接続されたnチャネルトランジスタNT4と、nチャネルトランジスタのソース・ドレイン間を接続することにより形成された容量C1とを含んでいる。また、2つ目の第1回路部14c1は、上記した1つ目の第1回路部14b1と同様、nチャネルトランジスタNT1、NT2、NT3およびNT4と、容量C1とを含んでいる。また、2つ目の第1回路部14c1は、上記した1つ目の第1回路部14b1と異なり、高抵抗R1をさらに含んでいる。

[0086]

また、 2 段目のシフトレジスタ回路 1 4 a 2 は、 1 つ目の第 1 回路部 1 4 b 2 および 2 つ目の第 1 回路部 1 4 c 2 によって構成されており、 3 段目のシフトレジスタ回路 1 4 a 3

20

30

40

50

は、1つ目の第1回路部14b3および2つ目の第1回路部14c3によって構成されている。そして、2段目のシフトレジスタ回路14a2および3段目のシフトレジスタ回路14a1の回路構成と同様である。

## [0087]

ここで、第3実施形態では、1つ目の第1回路部14b1および2つ目の第1回路部14 c1に設けられたnチャネルトランジスタNT1~NT4と、容量C1を構成するnチャ ネルトランジスタとは、すべてn型のMOSトランジスタ(電界効果型トランジスタ)か らなるTFT(薄膜トランジスタ)によって構成されている。以下、nチャネルトランジ スタNT1~NT4は、それぞれ、トランジスタNT1~NT4と称する。

[0088]

また、第3実施形態では、トランジスタNT3およびNT4は、図9に示すように、それぞれ、互いに電気的に接続された2つのゲート電極96および97を有するように形成されている。具体的には、一方のゲート電極96および他方のゲート電極97は、それぞれ、一方のチャネル領域96cおよび他方のチャネル領域97c上にゲート絶縁膜95を介して形成されている。そして、一方のチャネル領域96cは、一方の低濃度不純物領域とを有するLDD(Light1y Doped Drain)構造のソース領域96aと、一方のLDD構造のドレイン領域96bとに挟まれるように形成されており、他方のチャネル領域97cは、他方のLDD構造のソース領域97aと、他方のLDD構造のドレイン領域97bとに挟まれるように形成されている。また、ドレイン領域96bとソース領域97aとは、共通の高濃度不純物領域を有している。

[0089]

また、図 8 に示すように、トランジスタN T 2 およびN T 3 のソースはそれぞれ、負側電位 H V S S に接続されているとともに、トランジスタN T 1 のドレインは正側電位 H V D D に接続されている。

[0090]

この第3実施形態によるシフトレジスタ回路14a1のこれら以外の部分の構成は、上記した第1実施形態によるシフトレジスタ回路4a1(図2参照)と同様である。

[0091]

また、水平スイッチ 1 3 は、複数のトランジスタNT 3 0、NT 3 1 およびNT 3 2 を含んでいる。トランジスタNT 3 0、NT 3 1 およびNT 3 2 のゲートは、それぞれ、 1 段目~ 3 段目のシフトレジスタ回路 1 4 a 1~ 1 4 a 3 の出力 S R 1、 S R 2 および S R 3 に接続されている。また、トランジスタNT 3 0~NT 3 2 のソースは、それぞれ、各段のドレイン線に接続されている。また、トランジスタNT 3 0~NT 3 2 のドレインは 1 本のビデオ信号線 V i d e o に接続されている。なお、ビデオ信号線の数は、たとえば、赤( R )、緑( G )および青( B )の 3 種類のビデオ信号 V i d e o が入力される場合は3本になる。

[0092]

図10は、図8に示した第3実施形態による液晶表示装置のHドライバのシフトレジスタ 回路のタイミングチャートである。図10を参照して、この第3実施形態によるシフトレジスタ回路では、図4に示した第1実施形態によるシフトレジスタ回路のタイミングチャートのクロック信号HCLK1およびHCLK2、および、スタート信号HSTのHレベルとLレベルとを反転させた波形の信号を、それぞれ、クロック信号HCLK1およびHCLK2、および、スタート信号HSTとして入力する。これにより、第3実施形態によるシフトレジスタ回路からの出力信号SR1~SR4のHレベルとLレベルとを反転させた波形を有する信号が出力される。この第3実施形態によるシフトレジスタ回路のこれ以外の動作は、上記した第1実施形態によるシフトレジスタ回路4a1と同様である。

[0093]

第3実施形態では、上記のように構成することによって、Hドライバ14を含む液晶表示

装置のスキャン特性の低下や消費電流の増加を抑制することができるなどの上記第 1 実施 形態と同様の効果を得ることができる。

#### [0094]

(第4実施形態)

図11は、本発明の第4実施形態による液晶表示装置のVドライバを構成するシフトレジスタ回路の回路図である。この第4実施形態では、ゲート線を駆動(走査)するためのVドライバをnチャネルトランジスタで構成する例について説明する。

## [0095]

図11を参照して、Vドライバ15の内部には、複数のシフトレジスタ回路15a1および15a2が設けられている。なお、図11では、図面の簡略化のため、2段のシフトレジスタ回路15a1および15a2のみ図示している。また、1段目のシフトレジスタ回路15a1は、1つ目の第1回路部15b11、2つ目の第1回路部15b12および3つ目の第1回路部15b13と、第2回路部15c1とによって構成されている。

### [0096]

1つ目の第1回路部15b11は、トランジスタNT1、NT2およびNT3と、ダイオード接続されたトランジスタNT4と、トランジスタのソース・ドレイン間を接続することにより形成された容量C1とを含んでいる。また、1段目のシフトレジスタ回路15a1の第2回路部15c1は、上記した1つ目の第1回路部15b11のトランジスタNT1、NT2、NT3およびNT4と、容量C1とにそれぞれ対応するトランジスタNT1、NT12、NT13およびNT14と、容量C11とを含んでいる。また、第2回路部15c1は、上記した第1回路部15b11と異なり、トランジスタNT15、NT16およびNT17と、ダイオード接続されたトランジスタNT18と、トランジスタのソース・ドレイン間を接続することにより形成された容量C12とをさらに含んでいる。

#### [0097]

また、1段目のシフトレジスタ回路15a1の2つ目の第1回路部15b12および3つ目の第1回路部15b13の回路構成は、1つ目の第1回路部15b11の回路構成と同様である。また、2段目のシフトレジスタ回路15a2は、1つ目の第1回路部15b21、2つ目の第1回路部15b22および3つ目の第1回路部15b23と、第2回路部15c2とによって構成されている。そして、2段目のシフトレジスタ回路15a2の回路構成は上記した1段目のシフトレジスタ15a1の回路構成と同様である。

#### [0098]

ここで、第4実施形態では、1つ目の第1回路部15 b 1 1 および第2回路部15 c 1 に設けられたトランジスタNT1~NT4およびNT11~NT18と、容量C 1、C 1 1 およびC 1 2 を構成するトランジスタとは、すべてn型のMOSトランジスタ(電界効果型トランジスタ)からなるTFT(薄膜トランジスタ)によって構成されている。

#### [0099]

また、第4実施形態では、トランジスタNT3、NT4、NT13、NT14、NT17 およびNT18は、それぞれ、図9に示した第3実施形態と同様、互いに電気的に接続された2つのゲート電極を有するように形成されている。

### [0100]

また、図11に示すように、トランジスタNT2、NT3、NT12、NT13、NT1 6およびNT17のソースは、それぞれ、負側電位VVSSに接続されているとともに、 トランジスタNT1およびNT15のドレインは、正側電位VVDDに接続されている。

## [0101]

この第4実施形態によるシフトレジスタ回路15 a 1 および15 a 2 の上記以外の部分の構成は、上記した第2実施形態によるシフトレジスタ回路5 a 1 (図5参照)と同様である。

### [0102]

図12は、図11に示した第4実施形態による液晶表示装置のVドライバのシフトレジスタ回路のタイミングチャートである。図12を参照して、この第4実施形態によるVドラ

10

20

30

40

イバのシフトレジスタ回路では、図6に示した第2実施形態によるシフトレジスタ回路の タイミングチャートのクロック信号VCLK1およびVCLK2、および、スタート信号 VSTのHレベルとLレベルとを反転させた波形の信号を、それぞれ、クロック信号VC LK1およびVCLK2、および、スタート信号VSTとして入力する。これにより、第 4 実施形態による液晶表示装置の V ドライバのシフトレジスタ回路からは、図 6 に示した 第2実施形態によるシフトレジスタ回路からの出力信号gate1~gate4のHレベ ルとLレベルとを反転させた波形を有する信号が出力される。この第4実施形態によるシ フトレジスタ回路のこれ以外の動作は上記した第2実施形態によるシフトレジスタ回路5 a 1と同様である。

### [0103]

第4実施形態では、上記のように構成することによって、Vドライバ15を含む液晶表示 装置のスキャン特性の低下や消費電流の増加を抑制することができるなどの上記第2実施 形態と同様の効果を得ることができる。

## [0104]

### (第5実施形態)

図13は、本発明の第5実施形態による有機EL表示装置を示した平面図である。図13 を参照して、この第5実施形態では、本発明を有機EL表示装置に適用する例について説 明する。

## [0105]

20

30

40

50

10

この第5実施形態の有機 EL表示装置では、図13に示すように、基板70上に、表示部 2.1が設けられている。なお、図1.3の表示部2.1には、1画素分の構成を示している。 また、表示部21にマトリクス状に配置された各画素22は、2つのpチャネルトランジ スタ22aおよび22b(以下、トランジスタ22aおよび22bという)と、補助容量 22cと、陽極22dと、陰極22eと、陽極22dと陰極22eとの間に挟持された有 機EL素子22fとによって構成されている。トランジスタ22aのゲートはゲート線に 接続されている。また、トランジスタ22aのソースはドレイン線に接続されている。ま た、トランジスタ22aのドレインには補助容量22cおよびトランジスタ22bのゲー トが接続されている。また、トランジスタ22bのドレインは陽極22dに接続されてい る。また、Hドライバ4内部の回路構成は、図2に示したpチャネルトランジスタを用い たシフトレジスタ回路によるHドライバ4の構成と同様である。また、Vドライバ5内部 の回路構成は、図5に示したpチャネルトランジスタを用いたシフトレジスタ回路による Vドライバ5の構成と同様である。第5実施形態による有機EL表示装置のこれら以外の 部分の構成は、図1に示した第1実施形態による液晶表示装置と同様である。

### [0106]

第5実施形態では、上記のように構成することによって、Hドライバ4およびVドライバ 5 を含む有機 E L 表示装置のスキャン特性の低下や消費電流の増加を抑制することができ るなどの上記第1および第2実施形態と同様の効果を得ることができる。

### [0107]

## (第6実施形態)

図14は、本発明の第6実施形態による有機EL表示装置を示した平面図である。図14 を参照して、この第6実施形態では、本発明を有機EL表示装置に適用する例について説 明する。

### [0108]

この第6実施形態の有機EL表示装置では、図14に示すように、基板80上に、表示部 3 1 が設けられている。なお、図14の表示部31には、1画素分の構成を示している。 また、表示部31にマトリクス状に配置された各画素32は、2つのnチャネルトランジ スタ32aおよび32b(以下、トランジスタ32aおよび32bという)と、補助容量 3 2 c と、陽極 3 2 d と、陰極 3 2 e と、陽極 3 2 d と陰極 3 2 e との間に挟持された有 機EL素子32fとによって構成されている。トランジスタ32aのゲートはゲート線に 接続されている。また、トランジスタ32aのドレインはドレイン線に接続されている。

また、トランジスタ32aのソースには補助容量32cおよびトランジスタ32bのゲートが接続されている。また、トランジスタ32bのソースは陽極32dに接続されている。また、Hドライバ14内部の回路構成は、図8に示したnチャネルトランジスタを用いたシフトレジスタ回路によるHドライバ14の構成と同様である。また、Vドライバ15内部の回路構成は、図11に示したnチャネルトランジスタを用いたシフトレジスタ回路によるVドライバ15の構成と同様である。第6実施形態による有機EL表示装置のこれら以外の部分の構成は、図7に示した第3実施形態による液晶表示装置と同様である。

## [0109]

第6実施形態では、上記のように構成することによって、Hドライバ14およびVドライバ15を含む有機 EL表示装置のスキャン特性の低下や消費電流の増加を抑制することができるなどの上記第3および第4実施形態と同様の効果を得ることができる。

10

#### [0110]

#### (第7実施形態)

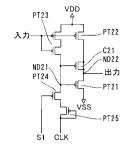

図15は、本発明の第7実施形態による液晶表示装置のHドライバおよびVドライバを構成するシフトレジスタ回路の第1回路部を示した回路図である。図15を参照して、この第7実施形態では、VDDとVSSとの電位差よりも大きいバイアス電圧が所定のトランジスタに印加されることに起因するスキャン特性の低下を抑制し、かつ、貫通電流をも抑制することが可能なシフトレジスタ回路について説明する。

[0111]

20

すなわち、この第7実施形態による液晶表示装置のHドライバおよびVドライバを構成するシフトレジスタ回路の第1回路部は、図15に示すように、トランジスタPT21、PT22、PT23およびPT24と、ダイオード接続されたトランジスタPT25と、トランジスタのソース・ドレイン間を接続することにより形成された容量C21とを含んでいる。なお、トランジスタPT21、PT22、PT23およびPT24は、それぞれ、本発明の「第1トランジスタ」、「第2トランジスタ」、「第3トランジスタ」および「第4トランジスタ」の一例である。

[ 0 1 1 2 ]

ここで、第7実施形態では、トランジスタPT21~PT25と、容量C21を構成するトランジスタとは、すべてp型のMOSトランジスタ(電界効果型トランジスタ)からなるTFT(薄膜トランジスタ)によって構成されている。

30

#### [0113]

また、第7実施形態では、トランジスタPT23は、図3に示した第1実施形態と同様、 互いに電気的に接続された2つのゲート電極を有するように形成されている。

[0114]

そして、図15に示すように、トランジスタPT21のソースはノードND22に接続されているとともに、ドレインは負側電位VSSに接続されている。このトランジスタPT21のゲートはノードND21に接続されているとともに、トランジスタPT21のゲートにはクロック信号CLKが供給される。トランジスタPT22のソースは正側電位VDDに接続されているとともに、ドレインはノードND22に接続されている。このトランジスタPT22のゲートには入力信号が供給される。

40

## [0115]

ここで、第7実施形態では、トランジスタPT23はトランジスタPT21のゲートと正側電位VDDとの間に接続されている。このトランジスタPT23のゲートには入力信号が供給される。そして、トランジスタPT23はトランジスタPT22がオン状態のときにトランジスタPT21をオフ状態にするために設けられている。これにより、トランジスタPT22とトランジスタPT21とが同時にオン状態になることが抑制される。また、容量C21はトランジスタPT21のゲートとソースとの間に接続されている。

#### [0116]

また、第7実施形態では、トランジスタPT24はトランジスタPT21のゲートとクロック信号線(CLK)との間に接続されている。このトランジスタPT24のゲートには

、トランジスタPT23のオン状態の期間と重ならないオン状態の期間が得られる信号S1が供給される。また、トランジスタPT25はトランジスタPT21のゲートとクロック信号線(CLK)との間に接続されている。

### [0117]

次に、第7実施形態による液晶表示装置のシフトレジスタ回路の動作としては、まず、入力信号がHレベルになることによって、トランジスタPT22およびPT23がオフ状態になる。また、クロック信号CLKがLレベルになることによって、トランジスタPT25がオン状態になる。このとき、トランジスタPT24のゲートには、トランジスタPT23のオン状態の期間と重ならないオン状態の期間が得られる信号S1(Lレベル)が供給される。これにより、トランジスタPT24がオン状態になるとともに、ノードND21の電位がLレベルに低下するので、トランジスタPT21がオン状態になる。このとき、ノードND22の電位はVSS側に低下する。

### [0118]

この場合、ノードND21の電位(トランジスタPT21のゲート電位)は、容量C21によってpチャネルトランジスタPT21のゲート・ソース間電圧が維持されるように、ノードND22の電位(トランジスタPT21のソース電位)の低下に伴って低下する。また、トランジスタPT23がオフ状態であるとともに、ダイオード接続されたトランジスタPT25には、クロック信号線(CLK)からのHレベルの信号がノードND21側に逆流することはないので、容量C21の保持電圧(トランジスタPT21のゲート・ソース間電圧)は維持される。これにより、ノードND22の電位が低下していくときにトランジスタPT21が常時オン状態に維持されるので、ノードND22の電位はVSSまで低下する。その結果、Lレベルの出力信号が出力される。

#### [0119]

なお、ノードND22の電位がVSSまで低下したときのノードND21の電位はVSSよりも低くなっている。このため、正側電位VDDに接続されたトランジスタPT23に 印加されるバイアス電圧は、VDDとVSSとの電位差よりも大きくなる。

#### [ 0 1 2 0 ]

この後、入力信号がLレベルになることによって、トランジスタPT22およびPT23がオン状態になる。このとき、第7実施形態では、トランジスタPT24がオフ状態になる。すなわち、トランジスタPT23とトランジスタPT24とが同時にオン状態になることはない。これにより、ノードND21の電位がHレベルに上昇するとともに、トランジスタPT21がオフ状態になる。その結果、ノードND22の電位がVDDに上昇するのでHレベルの出力信号が出力される。

#### [0121]

第7実施形態では、上記のように、トランジスタPT21のゲートとクロック信号線(CLK)との間に、トランジスタPT23のオン状態の期間と重ならないオン状態の期間が得られる信号S1に応答してオンするトランジスタPT24を接続することによって、トランジスタPT23とトランジスタPT24とが同時にオン状態になることがないので、トランジスタPT23およびPT24を介してVDDとクロック信号線(CLK)との間に貫通電流が流れることを防止することができる。

## [0122]

また、第7実施形態では、トランジスタPT23を、互いに電気的に接続された2つのゲート電極を有するように構成することによって、上記第1実施形態と同様、トランジスタPT23に印加されるバイアス電圧がVSSとVDDとの電位差よりも大きくなった場合にも、トランジスタPT23の各ゲート電極に対応するソース・ドレイン間にバイアス電圧が概ね半分程度ずつ(電圧の分配比率はトランジスタサイズなどによって変動)分配されるので、トランジスタPT23の特性が劣化することが抑制される。その結果、トランジスタPT23の特性が劣化することが抑制される。その結果、トランジスタPT23の特性が劣化することが抑制される。その結果、トランジスタPT23の特性が劣化することに起因するスキャン特性の低下を抑制しながら、消費電力が増加することを抑制することが可能な液晶表示装置を得ることができる。

## [0123]

50

10

20

30

#### (第8実施形態)

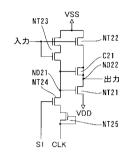

図16は、本発明の第8実施形態による液晶表示装置のHドライバおよびVドライバを構成するシフトレジスタ回路の第1回路部を示した回路図である。この第8実施形態では、上記第7実施形態の構成において、pチャネルトランジスタに変えて、nチャネルトランジスタを用いる場合について説明する。

#### [0124]

すなわち、この第8実施形態による液晶表示装置のHドライバおよびVドライバを構成するシフトレジスタ回路の第1回路部は、図16に示すように、トランジスタNT21、NT22、NT23およびNT24と、ダイオード接続されたトランジスタNT25と、トランジスタのソース・ドレイン間を接続することにより形成された容量C21とを含んでいる。

10

#### [0125]

ここで、第8実施形態では、トランジスタNT21~NT25と、容量C21を構成するトランジスタとは、すべてn型のMOSトランジスタ(電界効果型トランジスタ)からなるTFT(薄膜トランジスタ)によって構成されている。

#### [0126]

また、第8実施形態では、トランジスタNT23は、図9に示した第3実施形態と同様、 互いに電気的に接続された2つのゲート電極を有するように形成されている。

#### [0127]

また、図16に示すように、トランジスタNT22およびNT23のソースは、それぞれ、負側電位VSSに接続されているとともに、トランジスタNT21のドレインは正側電位VDDに接続されている。

20

### [0128]

この第8実施形態のこれら以外の構成は、上記第7実施形態と同様である。

#### [0129]

第8実施形態では、上記のように構成することによって、上記第7実施形態と同様、トランジスタNT23の特性が劣化することに起因するスキャン特性の低下を抑制しながら、消費電力が増加するのを抑制することが可能な液晶表示装置を得ることができる。

### [0130]

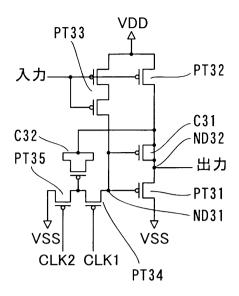

### (第9実施形態)

30

図17は、本発明の第9実施形態による液晶表示装置のHドライバおよびVドライバを構成するシフトレジスタ回路の第1回路部を示した回路図である。図17を参照して、この第9実施形態では、上記第7および第8実施形態と異なる方法を用いることにより、VDDとVSSとの電位差よりも大きいバイアス電圧が所定のトランジスタに印加されることに起因するスキャン特性の低下を抑制し、かつ、貫通電流をも抑制する場合について説明する。

## [0131]

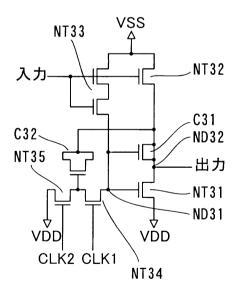

すなわち、この第9実施形態による液晶表示装置のHドライバおよびVドライバを構成するシフトレジスタ回路の第1回路部は、図17に示すように、トランジスタPT31、PT32、PT33、PT34およびPT35と、トランジスタのソース・ドレイン間を接続することにより形成された容量C31およびC32とを含んでいる。なお、トランジスタPT31、PT32、PT33、PT34およびPT35は、それぞれ、本発明の「第1トランジスタ」、「第2トランジスタ」、「第3トランジスタ」、「第4トランジスタ」および「第5トランジスタ」の一例である。

40

#### [0132]

ここで、第9実施形態では、トランジスタPT31~PT35と、容量C31およびC32を構成するトランジスタとは、すべてp型のMOSトランジスタ(電界効果型トランジスタ)からなるTFT(薄膜トランジスタ)によって構成されている。

### [0133]

また、第9実施形態では、トランジスタPT33は、図3に示した第1実施形態と同様、

互いに電気的に接続された2つのゲート電極を有するように形成されている。

## [0134]

そして、図17に示すように、トランジスタPT31のソースはノードND32に接続されているとともに、ドレインは負側電位VSSに接続されている。このトランジスタPT31のゲートはノードND31に接続されている。トランジスタPT32のソースは正側電位VDDに接続されているとともに、ドレインはノードND32に接続されている。このトランジスタPT32のゲートには入力信号が供給される。

### [0135]

ここで、第9実施形態では、トランジスタPT33は、トランジスタPT31のゲートと正側電位VDDとの間に接続されている。このトランジスタPT33のゲートには入力信号が供給される。そして、トランジスタPT33は、トランジスタPT32がオン状態のときにトランジスタPT31をオフ状態にするために設けられている。これにより、トランジスタPT32とトランジスタPT31とが同時にオン状態になることが抑制される。また、容量C31はトランジスタPT31のゲートとソースとの間に接続されている。

#### [0136]

また、第9実施形態では、トランジスタPT31のゲートにトランジスタPT34が接続されているとともに、トランジスタPT34と負側電位VSSとの間に、トランジスタPT31のが一トに接続されている。具体的には、トランジスタPT34のソースはトランジスタPT31のゲートに接続されているとともに、ドレインはトランジスタPT35のソースに接続されている。トランジスタPT35のドレインは負側電位VSSに接続されている。また、トランジスタPT34のゲートにはクロック信号CLK1が供給される。また、トランジスタPT35のゲートにはクロック信号CLK1が供給されるトランジスタPT34のオン状態の期間が得られるクロック信号CLK2が供給される。なお、クロック信号CLK1は、本発明の「第1の信号」の一例であり、クロック信号CLK2は、本発明の「第2の信号」の一例である。そして、容量C32は、トランジスタPT34とトランジスタPT35との間に接続されている。

#### [0137]

次に、第9実施形態による液晶表示装置のシフトレジスタ回路の動作としては、まず、クロック信号CLK1がHレベルになるとともに、クロック信号CLK2がLレベルになることによって、トランジスタPT35がオン状態となる。この際、容量C32に、トランジスタPT35を介して負側電位VSSからのLレベルの電位が蓄積される。

#### [0138]

この後、入力信号がHレベルになることによって、トランジスタPT32およびPT33がオフ状態になる。また、クロック信号CLK1がLレベルになるとともに、クロック信号CLK2がHレベルになることによって、トランジスタPT34がオン状態になるとともに、トランジスタPT35がオフ状態となる。このとき、トランジスタPT34を介して容量C32に蓄積されたLレベルの電位が供給される。これにより、ノードND31の電位がLレベルに低下するので、トランジスタPT31がオン状態になる。このとき、ノードND32の電位はVSS側に低下する。

## [0139]

この場合、ノードND31の電位(トランジスタPT31のゲート電位)は、容量C31によって、トランジスタPT31のゲート・ソース間電圧が維持されるように、ノードND32の電位(トランジスタPT31のソース電位)の低下に伴って低下する。また、トランジスタPT33およびPT35がオフ状態であるので、容量C31の保持電圧(トランジスタPT31のゲート・ソース間電圧)は維持される。これにより、ノードND32の電位が低下していくときに、トランジスタPT31が常時オン状態に維持されるので、ノードND32の電位はVSSまで低下する。その結果、Lレベルの出力信号が出力される。

## [0140]

10

20

30

20

30

40

50

なお、ノードND32の電位がVSSまで低下したときのノードND31の電位はVSSよりも低くなっている。このため、正側電位VDDに接続されたトランジスタPT33に印加されるバイアス電圧は、VDDとVSSとの電位差よりも大きくなる。

### [0141]

この後、入力信号がLレベルになることによって、トランジスタPT32およびPT33がオン状態になる。また、クロック信号CLK1がHレベルになるとともに、クロック信号CLK2がLレベルになることによって、トランジスタPT34がオフ状態になるとともに、トランジスタPT35がオン状態となる。このように、第9実施形態では、トランジスタPT33がオン状態のときには、トランジスタPT34およびPT35のいずれか一方がオフ状態になる。これにより、ノードND31の電位がHレベルに上昇するとともに、トランジスタPT31がオフ状態となる。その結果、ノードND32の電位がVDDに上昇するのでHレベルの出力信号が出力される。

#### [0142]

第9実施形態では、上記のように、トランジスタPT31のゲートに、クロック信号CLK1に応答してオンするトランジスタPT34を接続するとともに、トランジスタPT34と負側電位VSSとの間に、クロック信号CLK1が入力されるトランジスタPT34のオン状態の期間と重ならないオン状態の期間が得られるクロック信号CLK2に応答してオンするトランジスタPT35を接続することによって、トランジスタPT34およびPT35のどちらか一方は、常にオフ状態になるので、正側電位VDDに接続されたトランジスタPT33がオン状態である場合にも、トランジスタPT33、PT34およびPT35を介してVSSとVDDとの間に貫通電流が流れることを抑制することができる。

#### [0143]

また、第9実施形態では、トランジスタPT33を、互いに電気的に接続された2つのゲート電極を有するように構成することによって、上記第1実施形態と同様、トランジスタPT33に印加されるバイアス電圧がVSSとVDDとの電位差よりも大きくなった場合にも、トランジスタPT33の各ゲート電極に対応するソース・ドレイン間にバイアス電圧が概ね半分ずつ(電圧の分配比率はトランジスタサイズなどによって変動)分配されるので、トランジスタPT33の特性が劣化することが抑制される。その結果、トランジスタPT33の特性が劣化することが抑制される。その結果、トランジスタPT33の特性が劣化することが抑制される。その結果、トランジスタPT33の特性が劣化することに起因するスキャン特性の低下を抑制しながら、消費電力が増加することを抑制することが可能な液晶表示装置を得ることができる。

#### [0144]

## (第10実施形態)

図18は、本発明の第10実施形態による液晶表示装置のHドライバおよびVドライバを構成するシフトレジスタ回路の第1回路部を示した回路図である。この第10実施形態では、上記第9実施形態の構成において、pチャネルトランジスタに変えて、nチャネルトランジスタを用いる場合について説明する。

## [0145]

すなわち、この第10実施形態による液晶表示装置のHドライバおよびVドライバを構成するシフトレジスタ回路の第1回路部は、図18に示すように、トランジスタNT31、NT32、NT33、NT34およびNT35と、トランジスタのソース・ドレイン間を接続することにより形成された容量 C 31および C 32とを含んでいる。

#### **[** 0 1 4 6 ]

ここで、第10実施形態では、トランジスタNT31~NT35と、容量C31およびC32を構成するトランジスタとは、すべてn型のMOSトランジスタ(電界効果型トランジスタ)からなるTFT(薄膜トランジスタ)によって構成されている。

## [0147]

また、第10実施形態では、トランジスタNT33は、図9に示した第3実施形態と同様、互いに電気的に接続された2つのゲート電極を有するように形成されている。

#### [0148]

また、図18に示すように、トランジスタNT32およびNT33のソースは、それぞれ

、 負側電位 V S S に接続されているとともに、トランジスタNT31およびNT35のド レインは、それぞれ、正側電位 V D D に接続されている。

[0149]

この第10実施形態のこれら以外の構成は、上記第9実施形態と同様である。

[0150]

第10実施形態では、上記のように構成することによって、上記第9実施形態と同様、トランジスタNT33の特性が劣化することに起因するスキャン特性の低下を抑制しながら、消費電力が増加することを抑制することが可能な液晶表示装置を得ることができる。

[0151]

なお、今回開示された実施形態は、すべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は、上記した実施形態の説明ではなく特許請求の範囲によって示され、さらに特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれる。

[0152]

たとえば、上記実施形態では、本発明を液晶表示装置および有機 EL表示装置に適用する例を示したが、本発明はこれに限らず、液晶表示装置および有機 EL表示装置以外の表示装置にも適用可能である。

[ 0 1 5 3 ]

また、上記実施形態では、Hドライバのシフトレジスタ回路またはVドライバのシフトレジスタ回路のいずれか一方にのみ本発明を適用する例を説明したが、本発明はこれに限らず、Hドライバのシフトレジスタ回路およびVドライバのシフトレジスタ回路の両方に、本発明を適用するようにしてもよい。この場合、表示装置のスキャン特性の低下および消費電力の増大をより抑制することができる。

【図面の簡単な説明】

【図1】本発明の第1実施形態による液晶表示装置を示した平面図である。

【図2】図1に示した第1実施形態による液晶表示装置のHドライバを構成するシフトレジスタ回路の回路図である。

【図3】2つのゲート電極を有する p チャネルトランジスタの構造を説明するための模式 図である。

【図4】図2に示した第1実施形態による液晶表示装置のHドライバのシフトレジスタ回路のタイミングチャートである。

【図5】本発明の第2実施形態による液晶表示装置のVドライバを構成するシフトレジスタ回路の回路図である。

【図 6 】図 5 に示した第 2 実施形態による液晶表示装置の V ドライバのシフトレジスタ回路のタイミングチャートである。

【図7】本発明の第3実施形態による液晶表示装置を示した平面図である。

【図8】図7に示した第3実施形態による液晶表示装置のHドライバを構成するシフトレジスタ回路の回路図である。

【図9】2つのゲート電極を有する n チャネルトランジスタの構造を説明するための模式 図である。

【図10】図8に示した第3実施形態による液晶表示装置のHドライバのシフトレジスタ 回路のタイミングチャートである。

【図11】本発明の第4実施形態による液晶表示装置のVドライバを構成するシフトレジスタ回路の回路図である。

【図12】図11に示した第4実施形態による液晶表示装置の V ドライバのシフトレジスタ回路のタイミングチャートである。

【図13】本発明の第5実施形態による有機EL表示装置を示した平面図である。

【図14】本発明の第6実施形態による有機EL表示装置を示した平面図である。

【図15】本発明の第7実施形態による液晶表示装置のHドライバおよびVドライバを構成するシフトレジスタ回路の第1回路部を示した回路図である。

10

20

30

40

【図16】本発明の第8実施形態による液晶表示装置のHドライバおよびVドライバを構成するシフトレジスタ回路の第1回路部を示した回路図である。

【図17】本発明の第9実施形態による液晶表示装置のHドライバおよびVドライバを構成するシフトレジスタ回路の第1回路部を示した回路図である。

【図18】本発明の第10実施形態による液晶表示装置のHドライバおよびVドライバを 構成するシフトレジスタ回路の第1回路部を示した回路図である。

【図19】従来のブートストラップ型のインバータ回路を示した回路図である。

## 【符号の説明】

4 a 1、4 a 2、4 a 3、5 a 1、5 a 2、1 4 a 1、1 4 a 2、1 4 a 3、1 5 a 1、 1 5 a 2 シフトレジスタ回路

4 b 1、 4 c 1、 4 b 2、 4 c 2、 4 b 3、 4 c 3、 5 b 1 1、 5 b 1 2、 5 b 1 3、 5 b 2 1、 5 b 2 3、 1 4 b 1、 1 4 c 1、 1 4 b 2、 1 4 c 2、 1 4 b 3、 1 4 c 3、 1 5 b 1 1、 1 5 b 1 2、 1 5 b 1 3、 1 5 b 2 1、 1 5 b 2 2、 1 5 b 2 3 第 1 回路部

5 c 1、5 c 2、15 c 1、15 c 2 第 2 回路部

## 【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

## フロントページの続き

(51) Int.CI. F I

H 0 3 K

19/0175

(2006.01)

G 0 9 G

3/30

J

H 0 1 L

51/50

(2006.01)

G 1 1 C

19/00

J

H 0 3 K

19/00

1 0 1 F

H 0 5 B

33/14

A

(56)参考文献 特開2002-335153(JP,A)

特開2001-296843(JP,A)特開平10-179095(JP,A)特開平09-179095(JP,A)特開2003-273228(JP,A)特開2003-141893(JP,A)特開2002-197885(JP,A)

特開2001-051292(JP,A)

(58)調査した分野(Int.CI., DB名)

IPC G09G 3/00 - 3/38 G02F 1/133 505-580 G11C 19/00