(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7139552号**

**(P7139552)**

(45)発行日 令和4年9月21日(2022.9.21)

(24)登録日 令和4年9月12日(2022.9.12)

(51)国際特許分類

|        |                  |     |        |        |   |

|--------|------------------|-----|--------|--------|---|

| H 01 L | 21/82 (2006.01)  | F I | H 01 L | 21/82  | C |

| G 06 F | 30/30 (2020.01)  |     | G 06 F | 30/30  |   |

| G 06 F | 30/32 (2020.01)  |     | G 06 F | 30/32  |   |

| G 06 F | 30/39 (2020.01)  |     | G 06 F | 30/39  |   |

| G 06 F | 30/394 (2020.01) |     | G 06 F | 30/394 |   |

請求項の数 12 (全16頁)

|          |                             |

|----------|-----------------------------|

| (21)出願番号 | 特願2019-125804(P2019-125804) |

| (22)出願日  | 令和1年7月5日(2019.7.5)          |

| (65)公開番号 | 特開2021-12935(P2021-12935A)  |

| (43)公開日  | 令和3年2月4日(2021.2.4)          |

| 審査請求日    | 令和3年7月19日(2021.7.19)        |

|          |                                                 |

|----------|-------------------------------------------------|

| (73)特許権者 | 391016358<br>東芝情報システム株式会社<br>神奈川県川崎市川崎区日進町1番地53 |

| (74)代理人  | 100090169<br>弁理士 松浦 孝                           |

| (74)代理人  | 100074147<br>弁理士 本田 崇                           |

| (74)代理人  | 100124497<br>弁理士 小倉 洋樹                          |

| (72)発明者  | 長谷川 智洋<br>神奈川県川崎市川崎区日進町1番地53<br>東芝情報システム株式会社内   |

| 審査官      | 市川 武宜                                           |

最終頁に続く

(54)【発明の名称】 半導体集積回路の配線設計装置及び半導体集積回路の配線設計用プログラム

**(57)【特許請求の範囲】****【請求項1】**

セルの位置情報及び大きさ情報、前記セル内のピンの位置情報及び大きさ情報、幹線配線の位置情報を含む配線設計情報を基づき、複数の幹線配線中の所定数本の幹線配線を始点とし前記幹線配線に直交する幹線始点支線と、セル内のピンを始点とし前記幹線配線に直交するように延びるピン始点支線とを発生する始点支線発生手段と、

発生された前記幹線始点支線と発生された前記ピン始点支線とに関する発生支線情報及び前記配線設計情報を基づき、発生された前記幹線始点支線と発生された前記ピン始点支線が他の配線に重ならぬように最短距離で接続する最短距離接続手段と

を具備し、

前記最短距離接続手段は、複数本の幹線配線に最も近接するセルのピンと幹線配線との間にについては、発生された前記幹線始点支線と発生された前記ピン始点支線とを直接接続した直線支線により接続を行う

ことを特徴とする半導体集積回路の配線設計装置。

**【請求項2】**

前記最短距離接続手段は、前記幹線始点支線または前記ピン始点支線が他の配線と重なる場合には、前記幹線始点支線と前記ピン始点支線に直交する接続線を発生させて前記幹線始点支線と前記ピン始点支線とを接続することを特徴とする請求項1に記載の半導体集積回路の配線設計装置。

**【請求項3】**

同じ大きさのセルであって、セル内の同じ位置にピンが配置されているセルが縦横に複数並べられた半導体集積回路について配線設計を行うことを特徴とする請求項<sub>1</sub>または<sub>2</sub>に記載の半導体集積回路の配線設計装置。

**【請求項 4】**

前記始点支線発生手段は、

前記複数の幹線配線から数えて第1行目のセルにおけるピンと接続する幹線始点支線に隣接させて、複数の幹線配線から数えて第2行目のセルにおけるピンと接続する幹線始点支線を発生させ、

前記複数の幹線配線から数えて第2行目のセルにおけるピンと接続する幹線始点支線に隣接させて、複数の幹線配線から数えて第3行目のセルにおけるピンと接続する幹線始点支線を発生させ、

以下同様に、前行のセルにおけるピンと接続する幹線始点支線と次行のセルにおけるピンと接続する幹線始点支線とを隣接させて幹線始点支線を発生させることを特徴とする請求項<sub>3</sub>に記載の半導体集積回路の配線設計装置。

**【請求項 5】**

前記始点支線発生手段は、前記幹線始点支線または前記ピン始点支線が他の配線と重なる場合には、セルを横方向にシフトさせてシフトした位置のピンと複数の幹線配線との間で支線を発生させることを特徴とする請求項<sub>3</sub>または<sub>4</sub>に記載の半導体集積回路の配線設計装置。

**【請求項 6】**

前記始点支線発生手段は、セルの大きさに応じてシフト量を決定してシフトを行うことを特徴とする請求項<sub>5</sub>に記載の半導体集積回路の配線設計装置。

**【請求項 7】**

コンピュータを、

セルの位置情報及び大きさ情報、前記セル内のピンの位置情報及び大きさ情報、幹線配線の位置情報及び大きさ情報を含む配線設計情報に基づき、複数の幹線配線中の所定数本の幹線配線を始点とし前記幹線配線に直交する幹線始点支線と、セル内のピンを始点とし前記幹線配線に直交するように延びるピン始点支線とを発生する始点支線発生手段、

発生された前記幹線始点支線と発生された前記ピン始点支線とに関する発生支線情報及び前記配線設計情報に基づき、発生された前記幹線始点支線と発生された前記ピン始点支線が他の配線に重ならぬように最短距離で接続する最短距離接続手段

として機能させ、

前記コンピュータを前記最短距離接続手段として、

複数本の幹線配線に最も近接するセルのピンと幹線配線との間については、発生された前記幹線始点支線と発生された前記ピン始点支線とを直接接続した直線支線により接続を行うように機能させる

ことを特徴とする半導体集積回路の配線設計用プログラム。

**【請求項 8】**

前記コンピュータを前記最短距離接続手段として、

前記幹線始点支線または前記ピン始点支線が他の配線と重なる場合には、前記幹線始点支線と前記ピン始点支線に直交する接続線を発生させて前記幹線始点支線と前記ピン始点支線とを接続するように機能させることを特徴とする請求項<sub>7</sub>に記載の半導体集積回路の配線設計用プログラム。

**【請求項 9】**

同じ大きさのセルであって、セル内の同じ位置にピンが配置されているセルが縦横に複数並べられた半導体集積回路について配線設計を行うことを特徴とする請求項<sub>7</sub>または<sub>8</sub>に記載の半導体集積回路の配線設計用プログラム。

**【請求項 10】**

前記コンピュータを前記始点支線発生手段として、

前記複数の幹線配線から数えて第1行目のセルにおけるピンと接続する幹線始点支線に

10

20

30

40

50

隣接させて、複数の幹線配線から数えて第2行目のセルにおけるピンと接続する幹線始点支線を発生させ、

前記複数の幹線配線から数えて第2行目のセルにおけるピンと接続する幹線始点支線に隣接させて、複数の幹線配線から数えて第3行目のセルにおけるピンと接続する幹線始点支線を発生させ、

以下同様に、前行のセルにおけるピンと接続する幹線始点支線と次行のセルにおけるピンと接続する幹線始点支線とを隣接させて幹線始点支線を発生させるように機能させることを特徴とする請求項9に記載の半導体集積回路の配線設計用プログラム。

#### 【請求項11】

前記コンピュータを前記始点支線発生手段として、

10

前記幹線始点支線または前記ピン始点支線が他の配線と重なる場合には、セルを横方向にシフトさせてシフトした位置のピンと複数の幹線配線との間で支線を発生させるように機能させることを特徴とする請求項9または10に記載の半導体集積回路の配線設計用プログラム。

#### 【請求項12】

前記コンピュータを前記始点支線発生手段として、セルの大きさに応じてシフト量を決定してシフトを行うように機能させることを特徴とする請求項11に記載の半導体集積回路の配線設計用プログラム。

#### 【発明の詳細な説明】

##### 【技術分野】

20

##### 【0001】

この発明は、半導体集積回路の配線設計装置及び半導体集積回路の配線設計用プログラムに関するものである。

##### 【背景技術】

##### 【0002】

従来、半導体集積回路の設計の素子配置工程においては、できる限りサイズを小さくすることを優先し、デッドスペースを作らない配置プランを作ることが一般的である。例えば、特許文献1には、セル上フィードスルーの使用効率上昇を図り、配線の迂回を減少させて、チップ全体の面積を小さくする配線設計用CAD装置が開示されている。しかし、ほとんどのケースでは配置の段階で結線に要する配線トラックの利用効率まで考慮されておらず、配置効率を優先するが故に配線効率、品質の悪化を招来する可能性があった。

30

##### 【0003】

素子が格子状に配置されている場合、幹線から素子のピンまで最短距離で結線しようとすると、上下に配置されている素子と配線トラックが重なり合うことになり、配線ショートが発生することとなった。

##### 【0004】

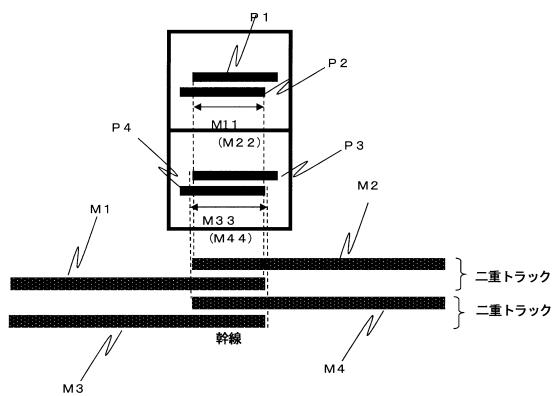

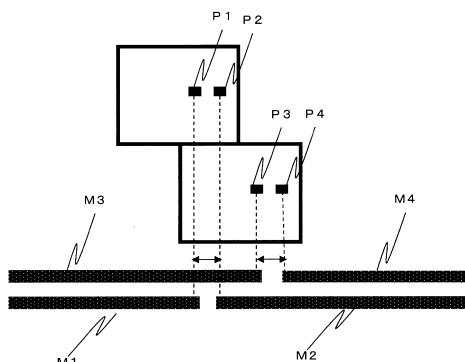

また、どの座標からでも支線と結線できるようにセルのピン形状を長くすることが考えられる(図1)。即ち、ピンP1は幹線配線M1の区間M11で直線的に接続されれば良く、また、P2は幹線配線M2の区間M22で直線的に接続されれば良い。しかし、区間M11と区間M22は同じ直線上に配置する訳にはいかず、図の上下方向にずれた位置に配置せざるを得ない。同様に、ピンP3は幹線配線M3の区間M33で直線的に接続されれば良く、また、P4は幹線配線M4の区間M44で直線的に接続されれば良い。しかし、区間M33と区間M44は同じ直線上に配置する訳にはいかず、図の上下方向にずれた位置に配置せざるを得ない。このように支線の迂回配線は回避できるが、幹線の配線時にピンの座標から終点を特定できなくなるため、二重配線トラックを作ってしまう問題もある。

40

##### 【0005】

特許文献2には、配線レイアウトの設計方法が開示されている。この設計手法は、側壁法と呼ばれる手法を用いる。側壁法を前提としたレイアウトの設計方法であって、第1の方向に延び、前記第1の方向と交差する第2の方向に第1の周期で配置された複数本の第

50

1のパターン、及び、前記第1の方向に延び、前記第1のパターン間の中央にそれぞれ配置された複数本の第2のパターンが設けられたベースパターンを用意する工程を備える。更に、1本の前記第2のパターンを挟んで隣り合う2本の前記第1のパターン間に、前記第2の方向に延び、前記2本の第1のパターン同士を接続すると共に、前記1本の第2のパターンを前記2本の第1のパターンと接しない2つのパターンに置き換える工程と、を備える。これにより高集積度を実現するものである。

#### 【0006】

特許文献3には、配線後の入力レイアウトデータの配線パターンの配線毎の配線幅を検出したり、配線領域毎の配線密度を検出したりする。そして、上記の検出結果に基づいて、プロセスによって決まる配線幅・配線密度条件を用いて、CMPの際に段差が発生しやすい太幅配線や配線密度の高い領域を特定する。その後、上記により特定された太幅配線や配線領域の周辺領域に存在し、円錐部の高いエアギャップが形成される配線間隔箇所を検出し、その検出結果に基づいてエアギャップ生成領域を生成又は削除する手法が開示されている。10

#### 【0007】

特許文献4には、チップサイズの増大を防止しつつ、厳格なデザインルールおよびチップの平坦性を考慮した、効率的な電源配線のレイアウト設計を実現する手法が開示されている。具体的には、電源配線補強実施部が電源配線の補強を行う際に、一般配線との関係も考慮してレイアウトを決定する。また、配線面積率制約判定部が測定した各配線層の配線面積率を参照し、面積率の最も低い配線層を優先的に用いて配線の補強を実施する。補強配線には、補強配線属性付与部が属性情報を付与し、一般配線の設計変更があったときは、その属性情報に基づき、補強配線削除部が補強配線を一括削除し、レイアウト設計のやり直しを可能とするものである。20

#### 【先行技術文献】

#### 【特許文献】

#### 【0008】

【文献】特開平5-304209号公報

特開2013-61575号公報

特開2008-205283号公報

特開2005-243886号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0009】

本実施形態では、事前に配線工程を考慮してセル配置することによって、必要な座標計算を単純化して自動配置配線する半導体集積回路の配線設計装置を提供する。

#### 【課題を解決するための手段】

#### 【0010】

実施形態に係る半導体集積回路の配線設計装置は、セルの位置情報及び大きさ情報、前記セル内のピンの位置情報及び大きさ情報、幹線配線の位置情報及び大きさ情報を含む配線設計情報に基づき、複数の幹線配線中の所定数本の幹線配線を始点とし前記幹線配線に直交する幹線始点支線と、セル内のピンを始点とし前記幹線配線に直交するように延びるピン始点支線とを発生する始点支線発生手段と、発生された前記幹線始点支線と発生された前記ピン始点支線とに関する発生支線情報及び前記配線設計情報に基づき、発生された前記幹線始点支線と発生された前記ピン始点支線が他の配線に重ならぬように最短距離で接続する最短距離接続手段とを具備することを特徴とする。40

#### 【図面の簡単な説明】

#### 【0011】

【図1】従来の配線手法を示す配線部分の平面図。

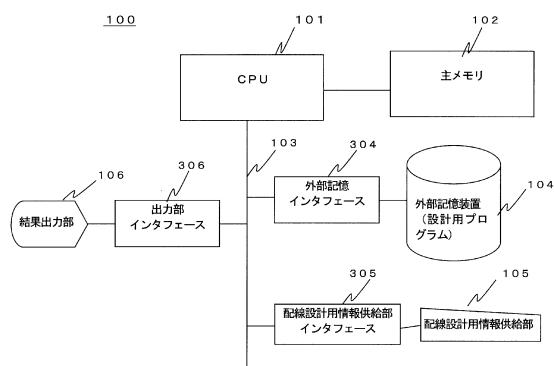

【図2】本発明に係る半導体集積回路の配線設計装置の実施形態の構成を示すブロック図。

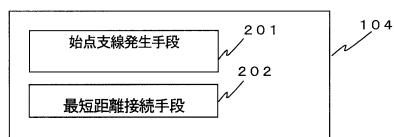

【図3】本発明に係る半導体集積回路の配線設計装置の実施形態の機能構成を示すブロック図50

ク図。

【図4】本発明に係る半導体集積回路の配線設計装置の実施形態により配線設計されるセルの構成を示す図。

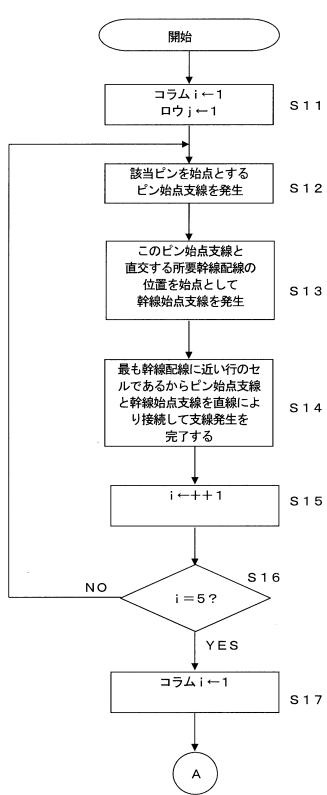

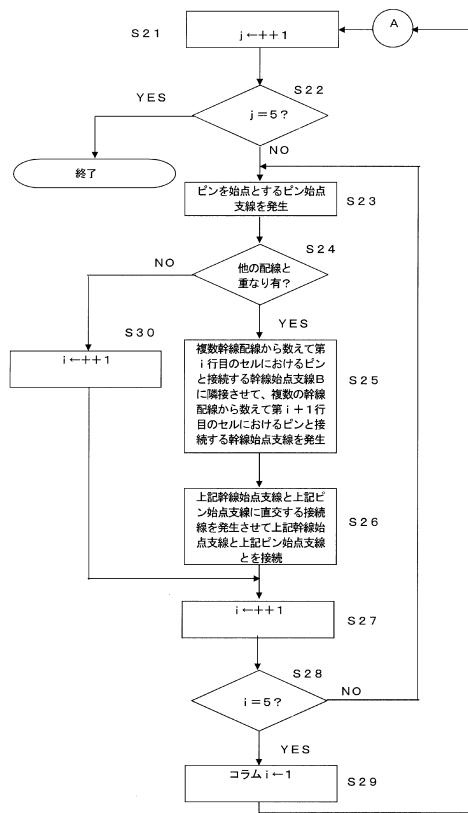

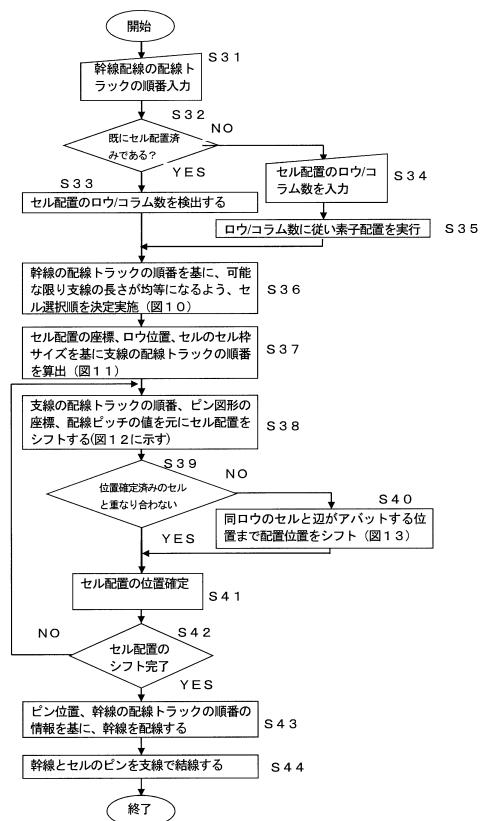

【図5】本発明に係る半導体集積回路の配線設計装置の第1の実施形態の動作を示すフローチャート(前半)。

【図6】本発明に係る半導体集積回路の配線設計装置の第1の実施形態の動作を示すフローチャート(後半)。

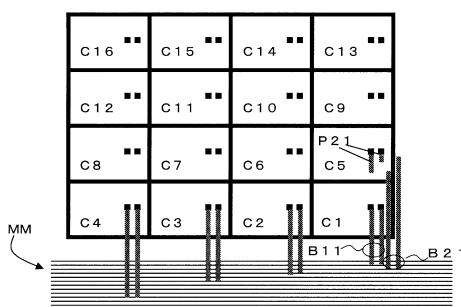

【図7】本発明に係る半導体集積回路の配線設計装置の第1の実施形態の配線動作手順を示す平面図(その1)。

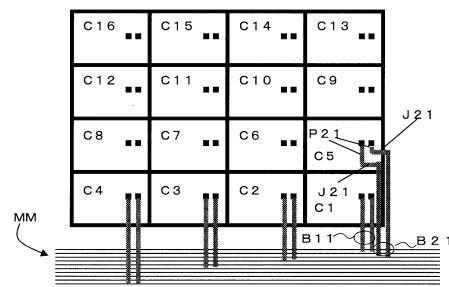

【図8】本発明に係る半導体集積回路の配線設計装置の第1の実施形態の配線動作手順を示す平面図(その2)。

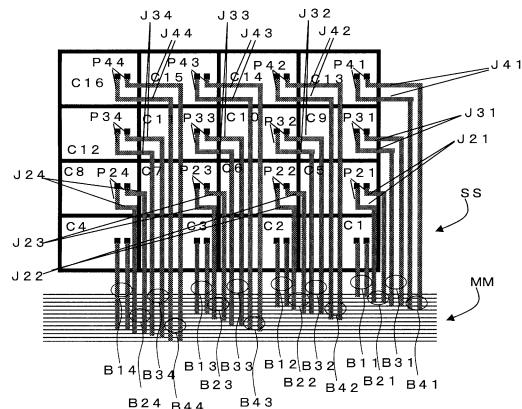

【図9】本発明に係る半導体集積回路の配線設計装置の第1の実施形態の配線動作手順により完成した配線の平面図。

【図10】本発明に係る半導体集積回路の配線設計装置の第2の実施形態の配線ルール(その1)を示す平面図。

【図11】本発明に係る半導体集積回路の配線設計装置の第2の実施形態の配線ルール(その2)を示す平面図。

【図12】本発明に係る半導体集積回路の配線設計装置の第2の実施形態の配線ルール(その3)を示す平面図。

【図13】本発明に係る半導体集積回路の配線設計装置の第2の実施形態の配線ルール(その4)を示す平面図。

【図14】本発明に係る半導体集積回路の配線設計装置の第2の実施形態の動作を示すフローチャート。

【図15】本発明に係る半導体集積回路の配線設計装置の第2の実施形態の配線動作手順により完成した配線の平面図。

【図16】本発明に係る半導体集積回路の配線設計装置の第2の実施形態の配線動作手順を詳細に説明する配線の要部平面図。

【図17】本発明に係る半導体集積回路の配線設計装置の第2の実施形態の配線動作手順により、1群の幹線配線の両方の側部に対してセル群が配置される半導体集積回路について第2の実施形態を適用した場合により完成した配線の平面図。

#### 【発明を実施するための形態】

##### 【0012】

以下添付図面を参照して、本発明に係る半導体集積回路の配線設計装置及び半導体集積回路の配線設計用プログラムの実施形態を説明する。各図において同一の構成要素には、同一の符号を付して重複する説明を省略する。図2に実施形態に係る半導体集積回路の配線設計装置100のブロック図を示す。半導体集積回路の配線設計装置100は、サーバコンピュータ、パーソナルコンピュータ、その他のコンピュータにより構成することができる。

##### 【0013】

半導体集積回路の配線設計装置100は、CPU101が主メモリ102のプログラムやデータに基づき演算を行うものである。CPU101には、バス103及び外部記憶インターフェース304を介して外部記憶装置104が接続されており、外部記憶装置104には、半導体集積回路の配線設計用プログラムが記憶されている。CPU101が外部記憶装置104から半導体集積回路の配線設計用プログラムを主メモリ102へ読み出してこのプログラムを実行することにより半導体集積回路の配線設計装置100として機能する。

##### 【0014】

バス103には、外部記憶装置104以外に配線設計用情報供給部インターフェース305を介して半導体集積回路の配線設計用情報供給部105が接続されている。配線設計用情報供給部105は、外部の入力装置などから配線設計用情報を入力して保持するものと

10

20

30

40

50

することができ、或いは、外部の何らかの装置等で既に作成された配線設計用情報を取り込み保持したものとすることができる。更に、クライアントから提供された配線設計用情報を記憶した媒体がセットされることにより、配線設計用情報を保持し供給可能となっている装置であっても良い。更に、上記の構成を全て備えたものであっても良い。いずれにしても、C P U 1 0 1 が半導体集積回路の配線設計用プログラムを実行して配線設計用情報に基づき配線設計を行う場合には配線設計用情報はこの配線設計用情報供給部 1 0 5 から供給される。

#### 【 0 0 1 5 】

配線設計用情報は、配線を行うために必要な情報であって、セルの位置情報及び大きさ情報、前記セル内のピンの位置情報及び大きさ情報、幹線配線の位置情報及び大きさ情報を含むものであり、接続すべきピンの識別情報と幹線配線の識別情報のペアが含まれる。なお、大きさ情報は、セル、ピン、幹線配線のいずれのものについても、例えば四角の枠により規定されるものとし、四角形における対角線により結ばれる 2 つの角の座標によって表すものとすることができます。また、半導体集積回路自体については、設計済みであっても未設計であっても良く、上記配線設計用情報が作成されれば良い。

10

#### 【 0 0 1 6 】

バス 1 0 3 には、出力部インターフェース 3 0 6 を介して結果出力部 1 0 6 が接続されている。結果出力部 1 0 6 は、表示装置やプリンタなど、半導体集積回路の設計装置 1 0 0 において処理した結果を出力する装置とすることができる。また、結果出力部 1 0 6 は、半導体集積回路の配線設計装置 1 0 0 において処理した結果を記憶する媒体でもよく、更に、回線などを介して処理の依頼者（クライアント）へ処理結果を送信などする装置であっても良い。

20

#### 【 0 0 1 7 】

本実施形態では、外部記憶装置 1 0 4 に記憶されている半導体集積回路の配線設計用プログラムが実行されることにより、図 3 に示される各手段が実現される。即ち、半導体集積回路の配線設計装置 1 0 0 は、図 3 に示されるように、始点支線発生手段 2 0 1 、最短距離接続手段 2 0 2 を具備している。

#### 【 0 0 1 8 】

始点支線発生手段 2 0 1 は、セルの位置情報及び大きさ情報、上記セル内のピンの位置情報及び大きさ情報、幹線配線の位置情報及び大きさ情報を含む配線設計情報に基づき、複数の幹線配線中の所定数本の幹線配線を始点とし上記幹線配線に直交する幹線始点支線と、セル内のピンを始点とし上記幹線配線に直交するように延びるピン始点支線とを発生するものである。

30

#### 【 0 0 1 9 】

最短距離接続手段 2 0 2 は、発生された上記幹線始点支線と発生された上記ピン始点支線とに関する発生支線情報及び上記配線設計情報に基づき、発生された上記幹線始点支線と発生された上記ピン始点支線が他の配線に重ならぬように最短距離で接続するものである。

#### 【 0 0 2 0 】

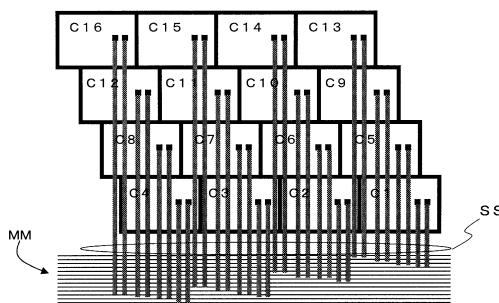

本実施形態では、半導体集積回路の配線設計装置 1 0 0 は、同じ大きさのセルであって、セル内の同じ位置にピンが配置されているセルが図 4 の如く縦横に複数並べられた半導体集積回路について配線設計を行う。図 4 は、4 行 4 列でセル C 1 ~ C 1 6 が並べられたものである。各セル C 1 ~ C 1 6 の領域内に示されている 2 つのドットは、ピン位置を示している。

40

#### 【 0 0 2 1 】

本実施形態では、前記最短距離接続手段 2 0 2 は、上記幹線始点支線または上記ピン始点支線が他の配線と重なる場合には、上記幹線始点支線と上記ピン始点支線に直交する接続線を発生させて上記幹線始点支線と上記ピン始点支線とを接続する。また、最短距離接続手段 2 0 2 は、複数本の幹線配線に最も近接するセルのピンと幹線配線との間については、発生された上記幹線始点支線と発生された上記ピン始点支線とを直接接続した直線支

50

線により接続を行う。

#### 【 0 0 2 2 】

本実施形態では、前記始点支線発生手段 201 は、上記複数の幹線配線から数えて第 1 行目のセルにおけるピンと接続する幹線始点支線に隣接させて、複数の幹線配線から数えて第 2 行目のセルにおけるピンと接続する幹線始点支線を発生させる。また、上記複数の幹線配線から数えて第 2 行目のセルにおけるピンと接続する幹線始点支線に隣接させて、複数の幹線配線から数えて第 3 行目のセルにおけるピンと接続する幹線始点支線を発生させる。以下同様に、前行のセルにおけるピンと接続する幹線始点支線と次行のセルにおけるピンと接続する幹線始点支線とを隣接させて幹線始点支線を発生させる。

#### 【 0 0 2 3 】

以上の構成を有する第 1 の実施形態は、図 5、図 6 に示されるフローチャートに対応するプログラムが実行されることにより実現される。本実施形態では、4 列 4 行のセルであり、コラム i を 1 とし、ロウ j を 1 とする (S11)。ピンを始点とするピン始点支線を発生し (S12)、このピン始点支線と直交する所要幹線配線の位置を始点として幹線始点支線を発生させる (S13)。ロウ j = 1 であり、最も幹線配線に近い行のセルであるからピン始点支線と幹線始点支線を直線により接続して (コラム i , ロウ j ) = (1, 1) の支線発生を完了する (S14)。

10

#### 【 0 0 2 4 】

次にコラム i を 1 歩進し (S15)、コラム i = 5 となっていないかを検出する (S16)。コラム i = 5 となっていない場合には、ステップ S12 へ戻って処理を続ける。ステップ S16 においてコラム i = 5 となっていることが検出された場合にはコラム i = 1 として (S17)、図 6 のフローチャートへ進み、ロウ j を 1 歩進し (S21)、ロウ j = 5 となっていないかを検出する (S22)。ロウ j = 5 となっていない場合には、ピンを始点とするピン始点支線 P21 を発生し (S23)、他の配線と重なりがないかを検出する (S24)。この例では、重なりが生じるので YES へ分岐し、上記複数の幹線配線 MM から数えて第 1 行目のセル C1 におけるピンと接続する幹線始点支線 B11 に隣接させて、複数の幹線配線 MM から数えて第 2 行目のセル C5 におけるピンと接続する幹線始点支線 B21 を発生させる (S25)。この様子を図 7 に示す。

20

#### 【 0 0 2 5 】

次に、上記は、幹線始点支線 B21 または上記ピン始点支線 P21 が他の配線と重なる場合に相当するので、上記幹線始点支線 B21 と上記ピン始点支線 P21 に直交する接続線 J21 を発生させて上記幹線始点支線 B21 と上記ピン始点支線 P21 とを接続する (S26)。この様子を図 8 に示す。

30

#### 【 0 0 2 6 】

ステップ S26 の次には、コラム i を 1 歩進し (S27)、コラム i = 5 となっていないかを検出する (S28)。コラム i = 5 となっていない場合には、ステップ S23 へ戻って処理を続ける。上記ステップ S28 においてコラム i = 5 となっていることが検出された場合には、コラム i = 1 として (S29)、次の行のセル内のピンからのピン始点支線の発生処理を行うためにステップ S21 へ戻る。このため、以下同様に、前行のセルにおけるピンと接続する幹線始点支線と次行のセルにおけるピンと接続する幹線始点支線とを隣接させて幹線始点支線を発生させる処理が行われる (S21 ~ S29)。

40

#### 【 0 0 2 7 】

本実施形態では、4 行分の処理が行われたときに、ステップ S22 において YES へ分岐することになり、処理は終了となる。このときに、図 9 に示すように全てのセル C1 ~ C16 のピンと複数の幹線配線 MM の対応する幹線配線との間に、ピン始点支線 (P × × (× × は、数字)) で示した線) と幹線始点支線 (B × × で示した線) と接続線 (J × × で示した線) とにより構成される支線 SS が設けられる。この支線 SS は、前行のセルにおけるピンと接続する幹線始点支線と次行のセルにおけるピンと接続する幹線始点支線とを隣接させて幹線始点支線を発生させる処理を行っているために、接続線 (J × × で示した線) を最短にでき、最短距離の配線を実現している。

50

**【 0 0 2 8 】**

次に第2の実施形態を説明する。この第2の実施形態では、上記第1の実施形態において発生させた接続線（J × ×で示した線）を用いない。本実施形態の始点支線発生手段201は、上記幹線始点支線または上記ピン始点支線が他の配線と重なる場合には、セルを横方向にシフトさせてシフトした位置のピンと複数の幹線配線との間で支線を発生させる。

**【 0 0 2 9 】**

シフトした位置のピンと複数の幹線配線との間で支線を発生させる場合において、ピンからは複数の幹線配線に直交する方向に延びるピン始点支線を発生させ、幹線配線の上記ピンに対応する位置から幹線配線に直交するようにピン方向へ延びる幹線始点支線を発生させる点は、第1の実施形態と同じである。発生させたピン始点支線と対応する幹線始点支線を直線的に接続する。

10

**【 0 0 3 0 】**

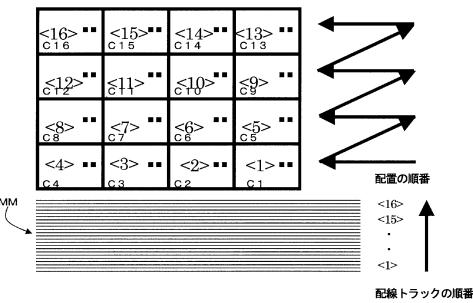

上記のようにすることから、図10に示すように上記複数の幹線配線MMに近いセルC1～C4のピンと上記複数の幹線配線MM中のセル側から遠い位置（図では下側）から幹線の選択を行って該当位置から幹線始点支線を発生する。即ち、幹線については配線トラックの順番<1>～<16>で選択し、セルのピンの選択は、「セルのピン選択順」の矢印に示される順で行う。この順は、セルの枠内に<1>～<16>で示されている。

**【 0 0 3 1 】**

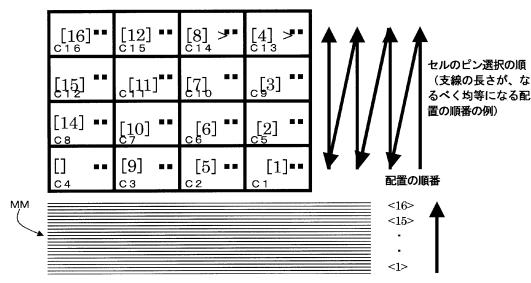

発生された幹線始点支線と発生されたピン始点支線とを接続する順は、図11に示されるようになる。即ち、幹線については配線トラックの順番<1>～<16>で選択したものに対し、ピン始点支線としては図11の右側に描かれている矢印の通りに進む。つまり、ピン始点支線としてはセル枠内に[1]～[16]の順に幹線始点支線と接続してゆく。しかしながら、上記の通りにピン始点支線を発生させ、幹線始点支線を発生させた場合には、ピン始点支線は同じ列にあるから、そのままでは支線に重なりが生じる。

20

**【 0 0 3 2 】**

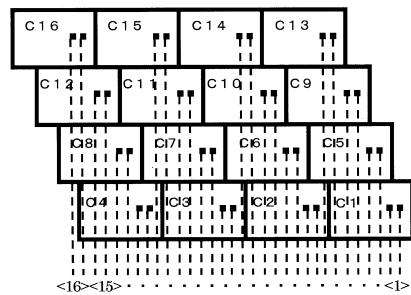

始点支線発生手段201は、上記幹線始点支線または上記ピン始点支線が他の配線と重なる場合には、セルを横方向にシフトさせてシフトした位置のピンと複数の幹線配線との間で支線を発生させる。例えば、図12に示すように、第1行目のセルC1～C4については、当初の位置へ配置したままとし、第2行目のセルC5～C8については、セルC5～C8のピンから引き出したピン始点支線が第1行目のセルC1～C4のピンから引き出したピン始点支線と重ならないようにシフトを行う（ここでは、左シフト）。また、第3行目のセルC9～C12については、セルC9～C12のピンから引き出したピン始点支線が第2行目のセルC5～C8のピンから引き出したピン始点支線と重ならないようにシフトを行う（ここでは、左シフト）。更に、第4行目のセルC13～C16については、セルC13～C16のピンから引き出したピン始点支線が第3行目のセルC9～C12のピンから引き出したピン始点支線と重ならないようにシフトを行う（ここでは、左シフト）。

30

**【 0 0 3 3 】**

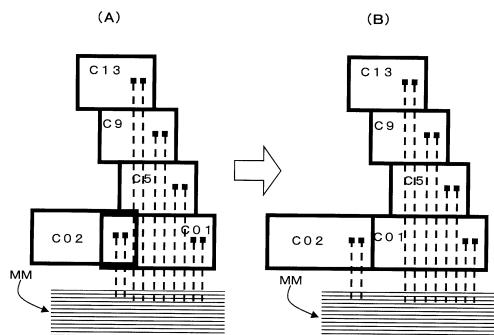

また、始点支線発生手段201は、セルの大きさに応じてシフト量を決定してシフトを行う。例えば、セルの一部について示す図13のように、1行目のセルC01、C02、…が2行目以降のセルC5、…、C9、…、C13の大きさと異なる場合について説明する。この例では、4行目のセルはシフトせず、3行目から1行目のセルをシフトするものとする。すると、3行目から1行目のセルを同じ距離シフトした場合には、図13（A）に示すように、1行目のセルC01、C02が重なってしまう。係る場合には、1行目のセルC01、C02についてシフト量の調整を行い、図13（B）に示されるように1行目のセルC01、C02が重ならぬようにする。

40

**【 0 0 3 4 】**

以上の構成を有する第2の実施形態は、図14に示されるフローチャートに対応するプログラムが実行されることにより実現される。本実施形態では、4列4行のセルである。まず、幹線配線の配線する順を入力する（S31）。ここでは、図10において説明した

50

ように、順番 <1> ~ <16> と入力がなされる。次に既にセル配置の設計が完了しているか検出する (S 3 2)。ステップ S 3 2においてNOへ分岐すると、セルが何行 (ロウ) × 何列 (コラム) に配置されているかの情報を入力し (S 3 4)、この情報に基づきセルの配置が行われる (S 3 5)。一方、セル配置の設計が完了している場合には、設計済の情報 (データ) からセルが何行 (ロウ) × 何列 (コラム) に配置されているかの情報を取り出す (S 3 3)。

#### 【0035】

ステップ S 3 3 またはステップ S 3 5 に続いて、図 1 0 において説明した通り、幹線の配線トラックの順番を元に、可能な限り支線の長さが均等になるよう、「セルのピン選択順」を決定する (S 3 6)。次に、図 1 1 において説明した通りに、セル配置の座標、ロウ位置、セルのセル枠サイズを基に支線の配線トラックの順番 (配線順) を算出する (S 3 7)。

10

#### 【0036】

ステップ S 3 7 に続いて図 1 2 において説明した通り、支線の配線トラックの順番、ピン図形の座標、配線ピッチの値を元にセル配置をシフトする (S 3 8)。次に、シフトによりセルの重なりが生じないかを検出し (S 3 9)、生じる場合には図 1 3 において説明した通りにシフト量を調整して適正な位置に配置する (S 4 0)。以上によりセルの配置位置が確定となる (S 4 1)。

#### 【0037】

上記でセルのシフトが完了したのかを検出し (S 4 2)、NOとなるとステップ S 3 8 へ戻って発生させるセルから伸びる支線が他の配線 (支線) と重ならないように処理を続ける。この結果、ステップ S 4 2 において YES へ分岐すると、ピン位置、幹線の配線トラックの順番の情報を基に、幹線を配線する (S 4 3)。更に、幹線とセルのピンを支線で結線する (S 4 4)。即ち、図 1 2、図 1 3 により説明した通りのシフト後のセルのピンから発生させたピン始点支線と、幹線始点支線とを直線で結んで支線として配線を完了する。この結果、図 1 5 に示されるように、セル C 1 ~ C 1 6 からは幹線 M M へ向けて直交するように伸びた直線である支線 S S によりピンと幹線 M M の間が最短距離で接続される。

20

#### 【0038】

また、図 1 6 に示す通り、ピン P 1 は幹線配線 M 1 の端部で直線的に接続されれば良く、また、P 1 は幹線配線 M 1 の端部で直線的に接続されれば良いので、無駄な配線を不要とでき、しかも最短距離で支線の配線を行うことができる。ピン P 2 と幹線配線 M 2 、ピン P 3 と幹線配線 M 3 、ピン P 4 と幹線配線 M 4 についてもピン P 1 と幹線配線 M 1 について述べた事項が成り立ち、図 1 に示した二重トラックを防ぐことができる。

30

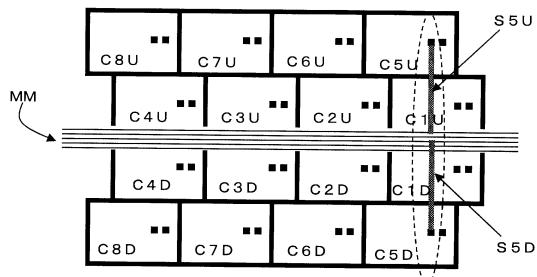

#### 【0039】

なお、以上の実施形態では、1群の幹線配線 M M の一方の側部に対してセル群が配置される半導体集積回路について述べてきたが、1群の幹線配線 M M の両方の側部に対してセル群が配置される半導体集積回路について第 1 の実施形態と第 2 の実施形態は適用可能である。例えば、図 1 7 に示されるように1群の幹線配線 M M に対し図の上側と図の下側にセル群が配置される場合を考える。

40

#### 【0040】

図 1 7 において、1群の幹線配線 M M に対し図の上側に配置されているセル群のセルを C 1 U ~ C 8 U とし、図の下側に配置されているセル群のセルを C 1 D ~ C 8 D とする。係る場合に、図の上側の半導体集積回路についても図の下側の半導体集積回路についても、第 1 の実施形態の手法で動作する始点支線発生手段 2 0 1 と最短距離接続手段 2 0 2 とにより装置を構成することにより、第 1 の実施形態の例と同じように処理がなされ同様の効果を得ることができる。また、図の上側の半導体集積回路についても図の下側の半導体集積回路についても、第 2 の実施形態の実施形態の手法で動作する始点支線発生手段 2 0 1 と最短距離接続手段 2 0 2 とにより装置を構成することにより、第 2 の実施形態の例と同じように処理がなされ同様の効果を得ることができる。

50

**【0041】**

そして、図の上側の半導体集積回路のセル内のピン構成及び位置が、図の下側の半導体集積回路のセル内のピン構成及び位置と対象的である場合には、図の上側において設計される支線と図の上側において設計される支線とは、1群の幹線配線MMを挟んで対称となる。図17においては、図の上側のセルC5Uの1つのピンへ延びる支線S5Uと図の下側のセルC5Dの1つのピンへ延びる支線S5Dとは、1群の幹線配線MMを挟んで対称となる。このことから、図の上側の半導体集積回路のセル内のピンへ延びる全ての支線と対称的な下側の半導体集積回路のセル内のピンへ延びる全ての支線とは、1群の幹線配線MMを挟んで一直線となることから、支線の配線トラック（半導体集積回路における配線領域）として一連の位置に形成することができる。つまり、支線の配線トラックは共有ないしは一本化することができる。

10

**【符号の説明】****【0042】**

- 100 配線設計装置

- 102 主メモリ

- 103 バス

- 104 外部記憶装置

- 105 配線設計用情報供給部

- 106 結果出力部

- 201 始点支線発生手段

- 202 最短距離接続手段

- 304 外部記憶インターフェース

- 305 配線設計用情報供給部インターフェース

- 306 出力部インターフェース

20

30

40

50

【図面】

【図 1】

【図 2】

10

【図 3】

【図 4】

|     |    |     |    |     |    |     |    |

|-----|----|-----|----|-----|----|-----|----|

| C16 | ■■ | C15 | ■■ | C14 | ■■ | C13 | ■■ |

| C12 | ■■ | C11 | ■■ | C10 | ■■ | C9  | ■■ |

| C8  | ■■ | C7  | ■■ | C6  | ■■ | C5  | ■■ |

| C4  | ■■ | C3  | ■■ | C2  | ■■ | C1  | ■■ |

20

30

40

50

【図 5】

【図 6】

10

20

30

【図 7】

【図 8】

40

50

【図 9】

【図 10】

10

【図 11】

【図 12】

20

30

40

50

【図 1 3】

【図 1 4】

10

20

30

40

50

【図 1 5】

【図 1 6】

【図 1 7】

10

20

30

40

50

---

フロントページの続き

- (56)参考文献

- 特開平02-278748 (JP, A)

特開2012-084862 (JP, A)

特開平07-130859 (JP, A)

特開平02-305472 (JP, A)

米国特許出願公開第2017/0053054 (US, A1)

- (58)調査した分野 (Int.Cl., DB名)

- H01L 21/82

G06F 30/30

G06F 30/32

G06F 30/39

G06F 30/394