(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7357165号**

**(P7357165)**

(45)発行日 令和5年10月5日(2023.10.5)

(24)登録日 令和5年9月27日(2023.9.27)

(51)国際特許分類

|         |                 |     |         |              |

|---------|-----------------|-----|---------|--------------|

| G 0 9 G | 3/3233(2016.01) | F I | G 0 9 G | 3/3233       |

| G 0 9 G | 3/20 (2006.01)  |     | G 0 9 G | 3/20 6 1 1 H |

| H 1 0 K | 59/123(2023.01) |     | G 0 9 G | 3/20 6 2 4 B |

| H 1 0 K | 59/131(2023.01) |     | G 0 9 G | 3/20 6 2 1 F |

G 0 9 G 3/20 6 1 1 E

請求項の数 17 (全33頁) 最終頁に続く

(21)出願番号 特願2022-538541(P2022-538541)

(86)(22)出願日 令和2年7月22日(2020.7.22)

(86)国際出願番号 PCT/JP2020/028372

(87)国際公開番号 WO2022/018842

(87)国際公開日 令和4年1月27日(2022.1.27)

審査請求日 令和4年12月27日(2022.12.27)

(73)特許権者 000005049

シャープ株式会社

大阪府堺市堺区匠町1番地

(74)代理人 100104695

弁理士 島田 明宏

(74)代理人 100148459

弁理士 河本 悟

(72)発明者 小林 史幸

大阪府堺市堺区匠町1番地 シャープ株

式会社内

審査官 橋本 直明

最終頁に続く

(54)【発明の名称】 表示装置

**(57)【特許請求の範囲】****【請求項1】**

電流によって駆動される表示素子を含む画素回路を備えた表示装置であつて、複数行×複数列の前記画素回路と、対応する列の前記画素回路にデータ信号を供給するための複数のデータ信号線と、対応する行の前記画素回路への前記データ信号の書き込みを制御するための複数の走査信号線と、対応する行の前記画素回路に含まれる前記表示素子に電流を供給するか否かを制御するための複数の発光制御線と、ハイレベル電源電圧を供給する第1電源線と、ローレベル電源電圧を供給する第2電源線と、基準電圧を供給する基準電源線とを含む表示部を備え、

前記画素回路は、

第1制御ノードと、

第2制御ノードと、

第1端子と、前記第2電源線に接続された第2端子とを有する前記表示素子と、

前記複数の走査信号線の1つに接続された制御端子と、前記第1電源線に接続された第1導通端子と、前記第1制御ノードに接続された第2導通端子とを有する第1初期化トランジスタと、

前記複数の走査信号線の1つに接続された制御端子と、前記第1制御ノードに接続された第1導通端子と、第2導通端子とを有する閾値電圧補償トランジスタと、

前記複数の走査信号線の1つに接続された制御端子と、前記複数のデータ信号線の1つに接続された第1導通端子と、前記第2制御ノードに接続された第2導通端子とを有す

10

20

る書き込み制御トランジスタと、

前記第1制御ノードに接続された制御端子と、前記閾値電圧補償トランジスタの第2導通端子に接続された第1導通端子と、前記表示素子の第1端子に接続された第2導通端子とを有する駆動トランジスタと、

前記複数の発光制御線の1つに接続された制御端子と、前記第1電源線に接続された第1導通端子と、前記駆動トランジスタの第1導通端子に接続された第2導通端子とを有する第1発光制御トランジスタと、

前記複数の走査信号線の1つに接続された制御端子と、前記第2制御ノードに接続された第1導通端子と、前記表示素子の第1端子に接続された第2導通端子とを有する第2発光制御トランジスタと、

制御端子と、前記表示素子の第1端子に接続された第1導通端子と、前記基準電源線に接続された第2導通端子とを有する第2初期化トランジスタと、

前記第1制御ノードに接続された第1電極と、前記第2制御ノードに接続された第2電極とを有する保持キャパシタと

を含み、

前記第1初期化トランジスタのチャネル層および前記閾値電圧補償トランジスタのチャネル層は、酸化物半導体によって形成されていることを特徴とする、表示装置。

#### 【請求項2】

前記酸化物半導体は、インジウム、ガリウム、亜鉛、および酸素によって構成されていることを特徴とする、請求項1に記載の表示装置。

#### 【請求項3】

前記第2初期化トランジスタの制御端子は、前記複数の走査信号線の1つに接続されていることを特徴とする、請求項1または2に記載の表示装置。

#### 【請求項4】

前記第1初期化トランジスタの制御端子と前記閾値電圧補償トランジスタの制御端子とは異なる走査信号線に接続され、

前記閾値電圧補償トランジスタの制御端子と前記書き込み制御トランジスタの制御端子と前記第2初期化トランジスタの制御端子とは同じ走査信号線に接続され、

各フレーム期間において、前記第1初期化トランジスタの制御端子に接続された走査信号線に印加される走査信号が所定期間オンレベルで維持された後、前記閾値電圧補償トランジスタの制御端子と前記書き込み制御トランジスタの制御端子と前記第2初期化トランジスタの制御端子とに接続された走査信号線に印加される走査信号が所定期間オンレベルで維持されることを特徴とする、請求項3に記載の表示装置。

#### 【請求項5】

前記表示部は、前記複数の発光制御線と1対1で対応し前記表示素子の第1端子の状態を初期化するための複数のリセット制御線を含み、

前記第2初期化トランジスタの制御端子は、前記複数のリセット制御線の1つに接続されていることを特徴とする、請求項1または2に記載の表示装置。

#### 【請求項6】

前記第1初期化トランジスタの制御端子と前記閾値電圧補償トランジスタの制御端子とは異なる走査信号線に接続され、

前記閾値電圧補償トランジスタの制御端子と前記書き込み制御トランジスタの制御端子とは同じ走査信号線に接続され、

各フレーム期間において、前記第1初期化トランジスタの制御端子に接続された走査信号線に印加される走査信号が所定期間オンレベルで維持された後、前記閾値電圧補償トランジスタの制御端子と前記書き込み制御トランジスタの制御端子とに接続された走査信号線に印加される走査信号が所定期間オンレベルで維持されることを特徴とする、請求項5に記載の表示装置。

#### 【請求項7】

各発光制御線に印加される発光制御信号がオンレベルで維持される期間には、それに対

10

20

30

40

50

応するリセット制御線に印加されるリセット制御信号はオフレベルで維持され、かつ、各発光制御線に印加される発光制御信号がオフレベルで維持される期間には、それに対応するリセット制御線に印加されるリセット制御信号はオンレベルで維持されることを特徴とする、請求項 5 または 6 に記載の表示装置。

**【請求項 8】**

前記駆動トランジスタのチャネル層は、低温ポリシリコンによって形成されていることを特徴とする、請求項 1 から 7 までのいずれか 1 項に記載の表示装置。

**【請求項 9】**

前記第 2 初期化トランジスタのチャネル層は、酸化物半導体によって形成され、

前記書き込み制御トランジスタ、前記第 1 発光制御トランジスタ、および前記第 2 発光

制御トランジスタのチャネル層は、低温ポリシリコンによって形成されていることを特徴

とする、請求項 8 に記載の表示装置。 10

**【請求項 10】**

前記第 1 初期化トランジスタ、前記閾値電圧補償トランジスタ、前記書き込み制御トランジスタ、前記駆動トランジスタ、前記第 1 発光制御トランジスタ、前記第 2 発光制御トランジスタ、および前記第 2 初期化トランジスタは、n チャネル型の薄膜トランジスタで

あることを特徴とする、請求項 9 に記載の表示装置。

**【請求項 11】**

前記画素回路で前記第 1 発光制御トランジスタと前記第 2 発光制御トランジスタとがオ

フ状態で維持されている期間中において、前記第 1 初期化トランジスタが所定期間オン状

態になった後、前記閾値電圧補償トランジスタと前記書き込み制御トランジスタと前記第

2 初期化トランジスタとが所定期間オン状態となることを特徴とする、請求項 1 から 10

までのいずれか 1 項に記載の表示装置。 20

**【請求項 12】**

電流によって駆動される表示素子を含む画素回路を備えた表示装置であって、

複数行 × 複数列の前記画素回路と、対応する列の前記画素回路にデータ信号を供給する

ための複数のデータ信号線と、対応する行の前記画素回路への前記データ信号の書き込み

を制御するための複数の走査信号線と、対応する行の前記画素回路に含まれる前記表示素

子に電流を供給するか否かを制御するための複数の発光制御線と、ハイレベル電源電圧を

供給する第 1 電源線と、ローレベル電源電圧を供給する第 2 電源線と、基準電圧を供給す

る基準電源線とを含む表示部を備え、 30

前記画素回路は、

第 1 制御ノードと、

第 2 制御ノードと、

第 1 端子と、前記第 2 電源線に接続された第 2 端子とを有する前記表示素子と、

前記複数の走査信号線の 1 つに接続された制御端子と、前記第 1 電源線に接続された

第 1 導通端子と、前記第 1 制御ノードに接続された第 2 導通端子とを有する第 1 初期化ト

ランジスタと、

前記複数の走査信号線の 1 つに接続された制御端子と、前記第 1 制御ノードに接続さ

れた第 1 導通端子と、第 2 導通端子とを有する閾値電圧補償トランジスタと、 40

前記複数の走査信号線の 1 つに接続された制御端子と、前記複数のデータ信号線の 1

つに接続された第 1 導通端子と、前記第 2 制御ノードに接続された第 2 導通端子とを有す

る書き込み制御トランジスタと、

前記第 1 制御ノードに接続された制御端子と、前記閾値電圧補償トランジスタの第 2

導通端子に接続された第 1 導通端子と、前記表示素子の第 1 端子に接続された第 2 導通端

子とを有する駆動トランジスタと、

前記複数の発光制御線の 1 つに接続された制御端子と、前記第 1 電源線に接続された

第 1 導通端子と、前記駆動トランジスタの第 1 導通端子に接続された第 2 導通端子とを有

する第 1 発光制御トランジスタと、

前記複数の走査信号線の 1 つに接続された制御端子と、前記第 2 制御ノードに接続さ

れた第 1 導通端子と、前記駆動トランジスタの第 1 導通端子に接続された第 2 導通端子とを有

する第 1 発光制御トランジスタと、 50

れた第1導通端子と、前記表示素子の第1端子に接続された第2導通端子とを有する第2発光制御トランジスタと、

制御端子と、前記表示素子の第1端子に接続された第1導通端子と、前記基準電源線に接続された第2導通端子とを有する第2初期化トランジスタと、

前記第1制御ノードに接続された第1電極と、前記第2制御ノードに接続された第2電極とを有する保持キャパシタと

を含むことを特徴とする、表示装置。

【請求項13】

電流によって駆動される表示素子を含む画素回路を備えた表示装置であって、

複数行×複数列の前記画素回路と、対応する列の前記画素回路にデータ信号を供給するための複数のデータ信号線と、対応する行の前記画素回路への前記データ信号の書き込みを制御するための複数の走査信号線と、対応する行の前記画素回路に含まれる前記表示素子に電流を供給するか否かを制御するための複数の発光制御線と、ハイレベル電源電圧を供給する第1電源線と、ローレベル電源電圧を供給する第2電源線と、初期化電圧を供給する初期化電源線と、基準電圧を供給する基準電源線とを含む表示部を備え、

前記画素回路は、

第1制御ノードと、

第2制御ノードと、

第1端子と、前記第2電源線に接続された第2端子とを有する前記表示素子と、

前記複数の走査信号線の1つに接続された制御端子と、前記基準電源線に接続された第1導通端子と、前記第2制御ノードに接続された第2導通端子とを有する第1初期化トランジスタと、

前記複数の走査信号線の1つに接続された制御端子と、前記第1制御ノードに接続された第1導通端子と、第2導通端子とを有する閾値電圧補償トランジスタと、

前記複数の走査信号線の1つに接続された制御端子と、前記複数のデータ信号線の1つに接続された第1導通端子と、前記第2制御ノードに接続された第2導通端子とを有する書き込み制御トランジスタと、

前記第1制御ノードに接続された制御端子と、前記第1電源線に接続された第1導通端子と、前記閾値電圧補償トランジスタの第2導通端子に接続された第2導通端子とを有する駆動トランジスタと、

前記複数の発光制御線の1つに接続された制御端子と、前記駆動トランジスタの第2導通端子に接続された第1導通端子と、前記表示素子の第1端子に接続された第2導通端子とを有する第1発光制御トランジスタと、

前記複数の発光制御線の1つに接続された制御端子と、前記表示素子の第1端子に接続された第2導通端子とを有する第2発光制御トランジスタと、

前記複数の走査信号線の1つに接続された制御端子と、前記第1制御ノードに接続された第1導通端子と、前記初期化電源線に接続された第2導通端子とを有する第2初期化トランジスタと、

前記第1制御ノードに接続された第1電極と、前記第2制御ノードに接続された第2電極とを有する保持キャパシタと

を含み、

前記閾値電圧補償トランジスタのチャネル層および前記第2初期化トランジスタのチャネル層は、酸化物半導体によって形成され、

前記第1初期化トランジスタの制御端子と前記第2初期化トランジスタの制御端子とは異なる走査信号線に接続され、

前記第1初期化トランジスタの制御端子と前記閾値電圧補償トランジスタの制御端子と前記書き込み制御トランジスタの制御端子とは同じ走査信号線に接続され、

各フレーム期間において、前記第2初期化トランジスタの制御端子に接続された走査信号線に印加される走査信号が所定期間ハイレベルで維持された後、前記第1初期化トラン

10

20

30

40

50

ジスタの制御端子と前記閾値電圧補償トランジスタの制御端子と前記書き込み制御トランジスタの制御端子とに接続された走査信号線に印加される走査信号が所定期間ハイレベルで維持されることを特徴とする、表示装置。

【請求項 1 4】

前記酸化物半導体は、インジウム、ガリウム、亜鉛、および酸素によって構成されていることを特徴とする、請求項 1 3 に記載の表示装置。

【請求項 1 5】

前記駆動トランジスタのチャネル層は、低温ポリシリコンによって形成されていることを特徴とする、請求項 1 3 または 1 4 に記載の表示装置。

【請求項 1 6】

前記閾値電圧補償トランジスタ、前記書き込み制御トランジスタ、前記第 2 発光制御トランジスタ、および前記第 2 初期化トランジスタは、n チャネル型の薄膜トランジスタであり、

前記第 1 初期化トランジスタ、前記駆動トランジスタ、および前記第 1 発光制御トランジスタは、p チャネル型の薄膜トランジスタであることを特徴とする、請求項 1 5 に記載の表示装置。

【請求項 1 7】

前記画素回路で前記第 1 発光制御トランジスタがオフ状態かつ前記第 2 発光制御トランジスタがオン状態で維持されている期間中において、前記第 2 初期化トランジスタが所定期間オン状態になった後、前記第 1 初期化トランジスタが所定期間オフ状態となるとともに前記閾値電圧補償トランジスタと前記書き込み制御トランジスタとが所定期間オン状態となることを特徴とする、請求項 1 3 から 1 6 までのいずれか 1 項に記載の表示装置。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

以下の開示は、表示装置に関し、より詳しくは、有機 E L 素子などの電流によって駆動される表示素子を含む画素回路を備える表示装置に関する。

【背景技術】

【0 0 0 2】

近年、有機 E L 素子を含む画素回路を備えた有機 E L 表示装置が実用化されている。有機 E L 素子は、O L E D (Organic Light-Emitting Diode)とも呼ばれており、それに流れる電流に応じた輝度で発光する自発光型の表示素子である。このように有機 E L 素子は自発光型の表示素子であるので、有機 E L 表示装置は、バックライトおよびカラーフィルタなどを要する液晶表示装置に比べて、容易に薄型化・低消費電力化・高輝度化などを図ることができる。

【0 0 0 3】

有機 E L 表示装置の画素回路に関し、有機 E L 素子への電流の供給を制御するための駆動トランジスタとして、典型的には薄膜トランジスタ (T F T) が採用される。しかしながら、薄膜トランジスタについては、その特性にばらつきが生じやすい。具体的には、閾値電圧にばらつきが生じやすい。表示部内に設けられている駆動トランジスタに閾値電圧のばらつきが生じると、輝度のばらつきが生じるので表示品位が低下する。そこで、従来より、閾値電圧のばらつきを補償する各種処理（補償処理）が提案されている。

【0 0 0 4】

補償処理の方式としては、駆動トランジスタの閾値電圧の情報を保持するためのキャパシタを画素回路内に設けることによって補償処理を行う内部補償方式と、例えば所定条件下で駆動トランジスタに流れる電流の大きさを画素回路の外部に設けられた回路で測定してその測定結果に基づいて映像信号を補正することによって補償処理を行う外部補償方式などが知られている。

【0 0 0 5】

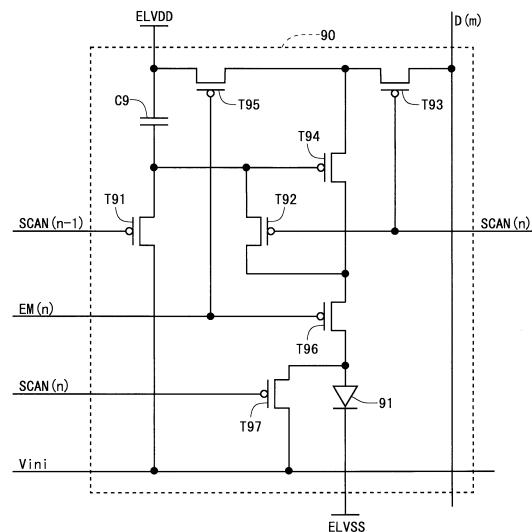

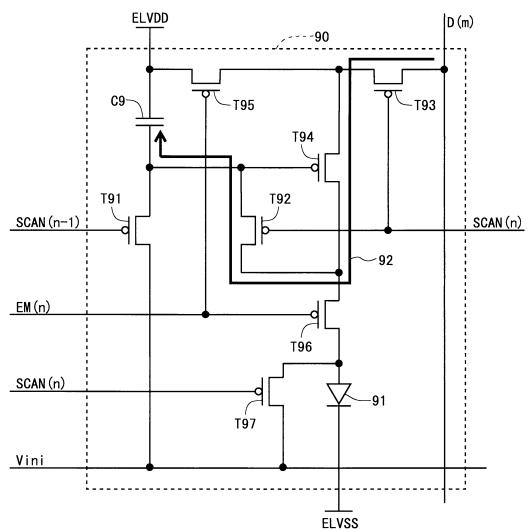

補償処理に内部補償方式を採用した有機 E L 表示装置の画素回路として、例えば図 2 8

10

20

30

40

50

に示すような、1個の有機EL素子91と7個のトランジスタT91～T97と1個の保持キャパシタC9とを含む画素回路90が知られている。画素回路90内のトランジスタT91～T97のチャネルのタイプは全てP型(pチャネル型)である。また、典型的には、画素回路90内のトランジスタT91～T97には、低温ポリシリコンによってチャネル層が形成されている薄膜トランジスタ(以下、「LTPS-TFT」という。)が採用されている。LTPS-TFTについては、移動度が高いので高速駆動が可能であるという利点やパネルの狭額縫化を実現しやすいという利点がある。

#### 【0006】

データ信号D(m)に基づき画素回路90内の保持キャパシタC9の充電を行う際には、まず、トランジスタT91をオン状態にすることによって駆動トランジスタ(トランジスタT94)のゲート電圧の初期化が行われる。その後、トランジスタT92, T93をオン状態にすることによって、保持キャパシタC9へのデータ信号D(m)の書き込みが行われる。その際、図29で符号92を付した矢印で示すように、電流が供給される。すなわち、駆動トランジスタ(トランジスタT94)を介して保持キャパシタC9の充電が行われる。一般に高い分解能が得られるよう駆動トランジスタの電流駆動能力は低くされているので、駆動トランジスタにLTPS-TFTが採用されていても、保持キャパシタC9の充電時間を短くすることは困難である。仮に駆動周波数を120Hzとするような高周波駆動(高速駆動)を採用した場合、充電不足に起因して表示品位が低下するおそれがある。

#### 【0007】

そこで、画素回路に関し、駆動トランジスタを介さずに保持キャパシタの充電が行われるよう、データ信号線に接続されたノードと駆動トランジスタの制御端子(ゲート端子)に接続されたノードとの間に保持キャパシタを設けた構成が提案されている(例えば、日本の特開2014-139696号公報を参照)。

#### 【0008】

また、近年、表示装置に関して、低消費電力化の要求が高まっている。そこで、表示画面に変化がないときなどに駆動周波数を例えば1Hzとする低周波駆動(低速駆動)を行う表示装置が開発されている。これに関し、LTPS-TFTについては比較的大きなりーク電流(オフリーケ)が生じるので、図28に示した構成の画素回路90が採用されると低周波駆動が行われた際にリーク電流によって保持キャパシタC9の充電電圧が変化するおそれがある。すなわち、低周波駆動が行われた際に表示品位が低下することが懸念される。

#### 【0009】

そこで、米国特許第10304378号明細書には、低周波駆動が行われた際のリーク電流の発生を防止するために、画素回路内的一部の薄膜トランジスタに酸化物半導体によってチャネル層が形成されている薄膜トランジスタ(以下、「酸化物TFT」という。)を用いることが記載されている。酸化物TFTは、リーク電流(オフリーケ)が極めて小さいという長所を有しており、近年、表示装置の画素回路や駆動回路を構成する薄膜トランジスタへの採用が増加しつつある。酸化物TFTのチャネル層を形成する酸化物半導体は、例えば、インジウム、ガリウム、亜鉛、および酸素によって構成されている。

#### 【先行技術文献】

#### 【特許文献】

#### 【0010】

#### 【文献】日本の特開2014-139696号公報

米国特許第10304378号明細書

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0011】

ところで、近年、例えば1～120Hzの間の様々な周波数で動作可能な画素回路(換言すれば、高周波駆動および低周波駆動の双方に対応可能な画素回路)を備えた表示装置

10

20

30

40

50

の開発が行われている。上述の米国特許第10304378号明細書に記載された構成によれば、表示品位の低下を引き起こすことなく低周波駆動を行うことは可能である。しかしながら、図28に示した構成と同様、保持キャパシタの充電は駆動トランジスタを介して行われる。それ故、高周波駆動を採用した場合に充電不足に起因して表示品位が低下するおそれがある。

#### 【0012】

そこで、以下の開示は、表示品位の低下を引き起こすことなく高周波駆動および低周波駆動の双方を可能ならしめる画素回路を備えた表示装置を実現することを目的とする。

#### 【課題を解決するための手段】

#### 【0013】

本開示のいくつかの実施形態に係る表示装置は、電流によって駆動される表示素子を含む画素回路を備えた表示装置であって、

複数行×複数列の前記画素回路と、対応する列の前記画素回路にデータ信号を供給するための複数のデータ信号線と、対応する行の前記画素回路への前記データ信号の書き込みを制御するための複数の走査信号線と、対応する行の前記画素回路に含まれる前記表示素子に電流を供給するか否かを制御するための複数の発光制御線と、ハイレベル電源電圧を供給する第1電源線と、ローレベル電源電圧を供給する第2電源線と、基準電圧を供給する基準電源線とを含む表示部を備え、

前記画素回路は、

第1制御ノードと、

第2制御ノードと、

第1端子と、前記第2電源線に接続された第2端子とを有する前記表示素子と、

前記複数の走査信号線の1つに接続された制御端子と、前記第1電源線に接続された第1導通端子と、前記第1制御ノードに接続された第2導通端子とを有する第1初期化トランジスタと、

前記複数の走査信号線の1つに接続された制御端子と、前記第1制御ノードに接続された第1導通端子と、第2導通端子とを有する閾値電圧補償トランジスタと、

前記複数の走査信号線の1つに接続された制御端子と、前記複数のデータ信号線の1つに接続された第1導通端子と、前記第2制御ノードに接続された第2導通端子とを有する書き込み制御トランジスタと、

前記第1制御ノードに接続された制御端子と、前記閾値電圧補償トランジスタの第2導通端子に接続された第1導通端子と、前記表示素子の第1端子に接続された第2導通端子とを有する駆動トランジスタと、

前記複数の発光制御線の1つに接続された制御端子と、前記第1電源線に接続された第1導通端子と、前記駆動トランジスタの第1導通端子に接続された第2導通端子とを有する第1発光制御トランジスタと、

前記複数の走査信号線の1つに接続された制御端子と、前記第2制御ノードに接続された第1導通端子と、前記表示素子の第1端子に接続された第2導通端子とを有する第2発光制御トランジスタと、

制御端子と、前記表示素子の第1端子に接続された第1導通端子と、前記基準電源線に接続された第2導通端子とを有する第2初期化トランジスタと、

前記第1制御ノードに接続された第1電極と、前記第2制御ノードに接続された第2電極とを有する保持キャパシタとを含み、

前記第1初期化トランジスタのチャネル層および前記閾値電圧補償トランジスタのチャネル層は、酸化物半導体によって形成されている。

#### 【0014】

本開示の他のいくつかの実施形態に係る表示装置は、電流によって駆動される表示素子を含む画素回路を備えた表示装置であって、

複数行×複数列の前記画素回路と、対応する列の前記画素回路にデータ信号を供給する

10

20

30

40

50

ための複数のデータ信号線と、対応する行の前記画素回路への前記データ信号の書き込みを制御するための複数の走査信号線と、対応する行の前記画素回路に含まれる前記表示素子に電流を供給するか否かを制御するための複数の発光制御線と、ハイレベル電源電圧を供給する第1電源線と、ローレベル電源電圧を供給する第2電源線と、基準電圧を供給する基準電源線とを含む表示部を備え、

前記画素回路は、

第1制御ノードと、

第2制御ノードと、

第1端子と、前記第2電源線に接続された第2端子とを有する前記表示素子と、

前記複数の走査信号線の1つに接続された制御端子と、前記第1電源線に接続された第1導通端子と、前記第1制御ノードに接続された第2導通端子とを有する第1初期化トランジスタと、

前記複数の走査信号線の1つに接続された制御端子と、前記第1制御ノードに接続された第1導通端子と、第2導通端子とを有する閾値電圧補償トランジスタと、

前記複数の走査信号線の1つに接続された制御端子と、前記複数のデータ信号線の1つに接続された第1導通端子と、前記第2制御ノードに接続された第2導通端子とを有する書き込み制御トランジスタと、

前記第1制御ノードに接続された制御端子と、前記閾値電圧補償トランジスタの第2導通端子に接続された第1導通端子と、前記表示素子の第1端子に接続された第2導通端子とを有する駆動トランジスタと、

前記複数の発光制御線の1つに接続された制御端子と、前記第1電源線に接続された第1導通端子と、前記駆動トランジスタの第1導通端子に接続された第2導通端子とを有する第1発光制御トランジスタと、

前記複数の走査信号線の1つに接続された制御端子と、前記第2制御ノードに接続された第1導通端子と、前記表示素子の第1端子に接続された第2導通端子とを有する第2発光制御トランジスタと、

制御端子と、前記表示素子の第1端子に接続された第1導通端子と、前記基準電源線に接続された第2導通端子とを有する第2初期化トランジスタと、

前記第1制御ノードに接続された第1電極と、前記第2制御ノードに接続された第2電極とを有する保持キャパシタと

を含む。

#### 【0015】

本開示のさらに他のいくつかの実施形態に係る表示装置は、電流によって駆動される表示素子を含む画素回路を備えた表示装置であって、

複数行×複数列の前記画素回路と、対応する列の前記画素回路にデータ信号を供給するための複数のデータ信号線と、対応する行の前記画素回路への前記データ信号の書き込みを制御するための複数の走査信号線と、対応する行の前記画素回路に含まれる前記表示素子に電流を供給するか否かを制御するための複数の発光制御線と、ハイレベル電源電圧を供給する第1電源線と、ローレベル電源電圧を供給する第2電源線と、初期化電圧を供給する初期化電源線と、基準電圧を供給する基準電源線とを含む表示部を備え、

前記画素回路は、

第1制御ノードと、

第2制御ノードと、

第1端子と、前記第2電源線に接続された第2端子とを有する前記表示素子と、

前記複数の走査信号線の1つに接続された制御端子と、前記基準電源線に接続された第1導通端子と、前記第2制御ノードに接続された第2導通端子とを有する第1初期化トランジスタと、

前記複数の走査信号線の1つに接続された制御端子と、前記第1制御ノードに接続された第1導通端子と、第2導通端子とを有する閾値電圧補償トランジスタと、

前記複数の走査信号線の1つに接続された制御端子と、前記複数のデータ信号線の1

10

20

30

40

50

つに接続された第1導通端子と、前記第2制御ノードに接続された第2導通端子とを有する書き込み制御トランジスタと、

前記第1制御ノードに接続された制御端子と、前記第1電源線に接続された第1導通端子と、前記閾値電圧補償トランジスタの第2導通端子に接続された第2導通端子とを有する駆動トランジスタと、

前記複数の発光制御線の1つに接続された制御端子と、前記駆動トランジスタの第2導通端子に接続された第1導通端子と、前記表示素子の第1端子に接続された第2導通端子とを有する第1発光制御トランジスタと、

前記複数の発光制御線の1つに接続された制御端子と、前記表示素子の第1端子に接続された第1導通端子と、前記初期化電源線に接続された第2導通端子とを有する第2発光制御トランジスタと、

前記複数の走査信号線の1つに接続された制御端子と、前記第1制御ノードに接続された第1導通端子と、前記初期化電源線に接続された第2導通端子とを有する第2初期化トランジスタと、

前記第1制御ノードに接続された第1電極と、前記第2制御ノードに接続された第2電極とを有する保持キャパシタとを含み、

前記閾値電圧補償トランジスタのチャネル層および前記第2初期化トランジスタのチャネル層は、酸化物半導体によって形成され、

前記第1初期化トランジスタの制御端子と前記第2初期化トランジスタの制御端子とは異なる走査信号線に接続され、

前記第1初期化トランジスタの制御端子と前記閾値電圧補償トランジスタの制御端子と前記書き込み制御トランジスタの制御端子とは同じ走査信号線に接続され、

各フレーム期間において、前記第2初期化トランジスタの制御端子に接続された走査信号線に印加される走査信号が所定期間ハイレベルで維持された後、前記第1初期化トランジスタの制御端子と前記閾値電圧補償トランジスタの制御端子と前記書き込み制御トランジスタの制御端子とに接続された走査信号線に印加される走査信号が所定期間ハイレベルで維持される。

#### 【発明の効果】

#### 【0016】

本開示のいくつかの実施形態によれば、画素回路の構成に関し、書き込み制御トランジスタを介してデータ信号線に接続された第2制御ノードと駆動トランジスタの制御端子に接続された第1制御ノードとの間に保持キャパシタが設けられる。このような構成により、保持キャパシタの充電は駆動トランジスタを介さずに行われる。すなわち、保持キャパシタの充電は速やかに行われる。また、データ信号の電圧は閾値電圧補償トランジスタがオン状態からオフ状態に変化する時点までに確定していれば良いので、データ信号の波形変化に大きな遅延が生じない限り表示品位は低下しない。以上より、例えば駆動周波数を120Hzとするような高周波駆動（高速駆動）が行われても、良好な表示品位が維持される。また、第1制御ノードに導通端子が接続されたトランジスタ（第1制御ノードに第2導通端子が接続された第1初期化トランジスタおよび第1制御ノードに第1導通端子が接続された閾値電圧補償トランジスタ）については、チャネル層が酸化物半導体によって形成されている。それ故、それらのトランジスタでのリーク電流の発生が防止される。従って、例えば駆動周波数を1Hzとするような低周波駆動（低速駆動）が行われても、リーク電流に起因して表示品位が低下することはない。すなわち、良好な表示品位が維持される。以上より、表示品位の低下を引き起こすことなく高周波駆動および低周波駆動の双方を可能ならしめる画素回路を備えた表示装置が実現される。

#### 【図面の簡単な説明】

#### 【0017】

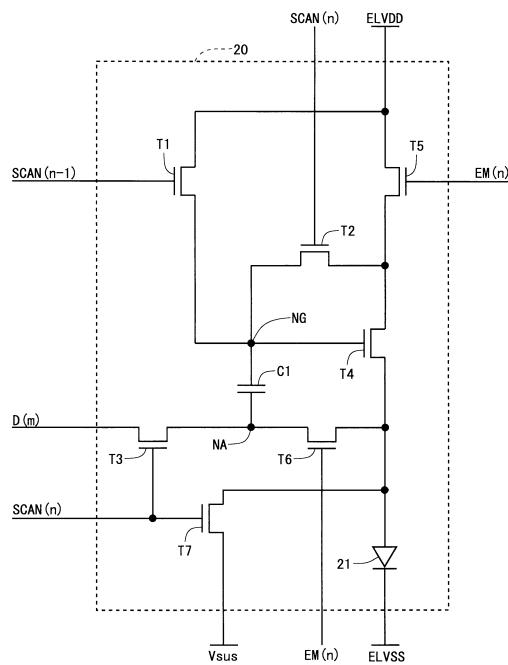

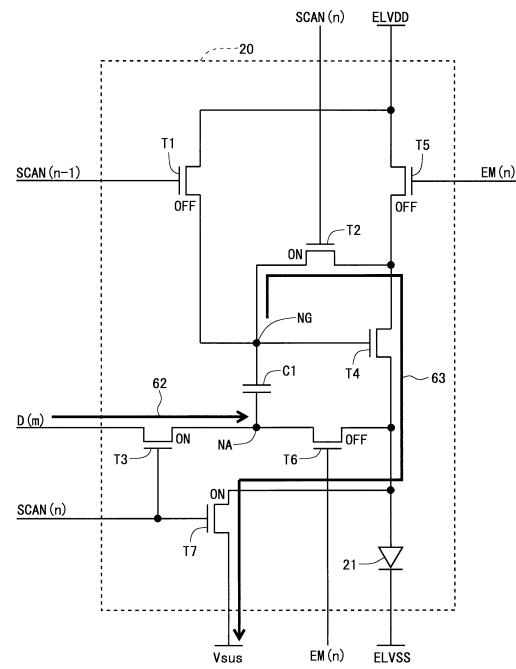

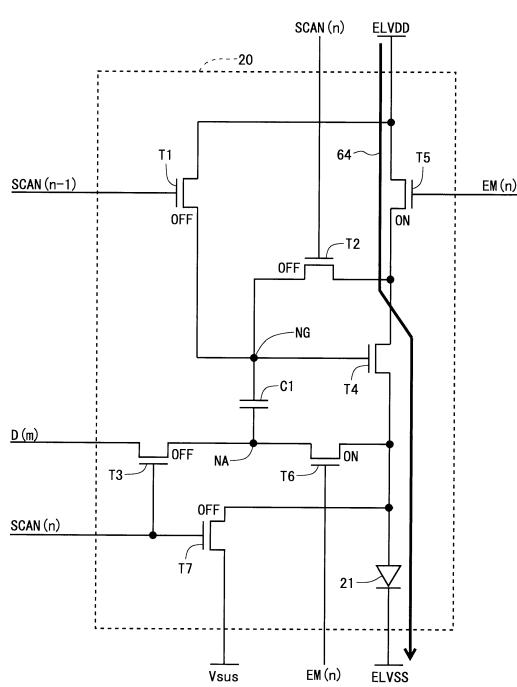

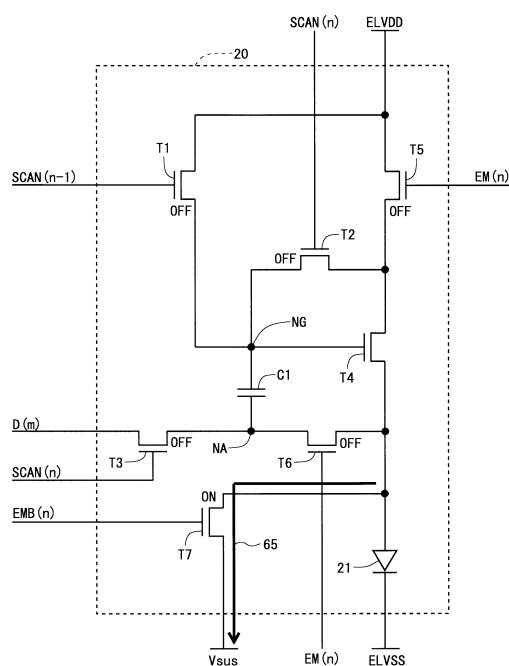

【図1】第1の実施形態において、第n行第m列の画素回路の構成を示す回路図である。

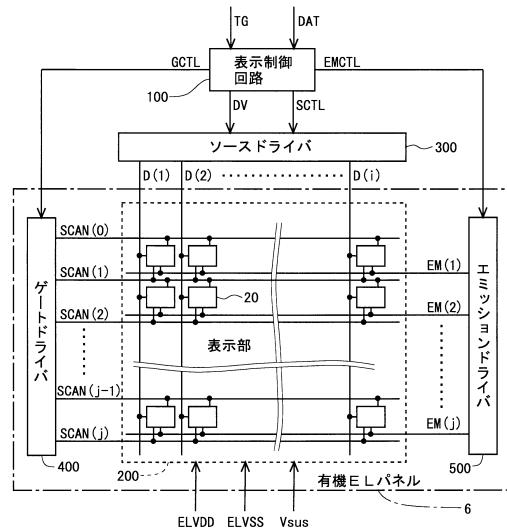

【図2】上記第1の実施形態に係る有機EL表示装置の全体構成を示すブロック図である。

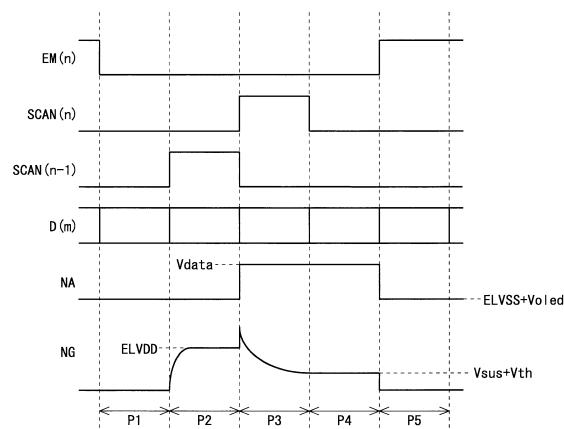

【図 3】上記第 1 の実施形態において、画素回路の動作について説明するための波形図である。

【図 4】上記第 1 の実施形態において、画素回路内の各トランジスタの状態の推移を示す図である。

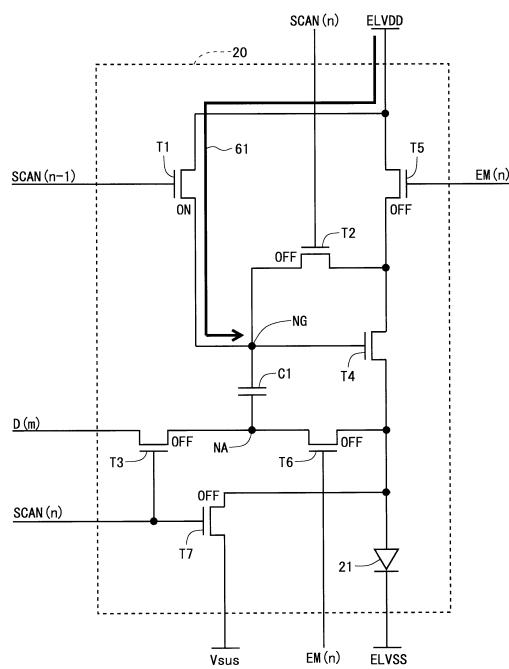

【図 5】上記第 1 の実施形態において、画素回路の動作について説明するための図である。

【図 6】上記第 1 の実施形態において、画素回路の動作について説明するための図である。

【図 7】上記第 1 の実施形態において、画素回路の動作について説明するための図である。

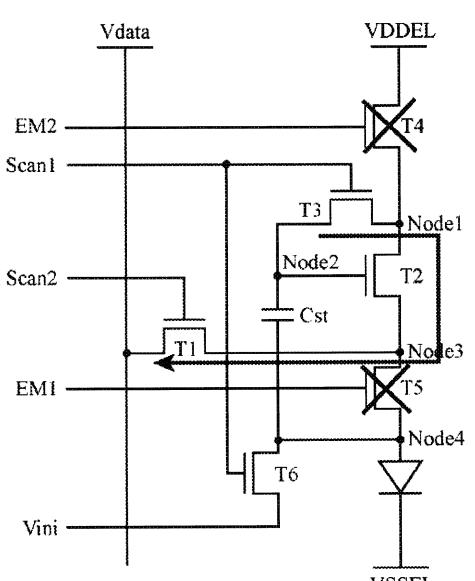

【図 8】米国特許第 1 0 3 0 4 3 7 8 号の図 6 C である。

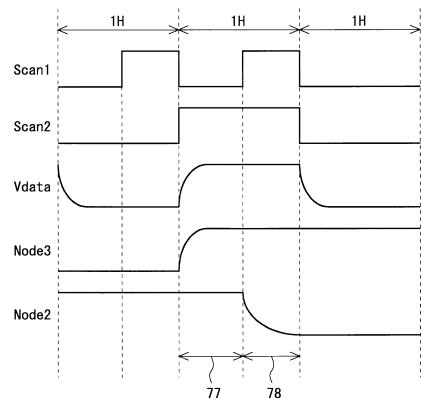

【図 9】米国特許第 1 0 3 0 4 3 7 8 号明細書に記載された画素回路の動作について説明するための波形図である。

10

【図 10】本実施形態の効果について説明するための波形図である。

【図 11】上記第 1 の実施形態の変形例に係る有機 E L 表示装置の全体構成を示すブロック図である。

【図 12】上記第 1 の実施形態の変形例において、第 n 行第 m 列の画素回路の構成を示す回路図である。

【図 13】上記第 1 の実施形態の変形例において、画素回路の動作について説明するための波形図である。

【図 14】上記第 1 の実施形態の変形例において、画素回路内の各トランジスタの状態の推移を示す図である。

【図 15】上記第 1 の実施形態の変形例において、画素回路の動作について説明するための図である。

20

【図 16】上記第 1 の実施形態の変形例において、画素回路の動作について説明するための図である。

【図 17】上記第 1 の実施形態の変形例において、画素回路の動作について説明するための図である。

【図 18】上記第 1 の実施形態の変形例の効果について説明するための波形図である。

【図 19】上記第 1 の実施形態の変形例の効果について説明するための波形図である。

【図 20】第 2 の実施形態に係る有機 E L 表示装置の全体構成を示すブロック図である。

【図 21】上記第 2 の実施形態において、第 n 行第 m 列の画素回路の構成を示す回路図である。

30

【図 22】上記第 2 の実施形態において、画素回路の動作について説明するための波形図である。

【図 23】上記第 2 の実施形態において、画素回路内の各トランジスタの状態の推移を示す図である。

【図 24】上記第 2 の実施形態において、画素回路の動作について説明するための図である。

【図 25】上記第 2 の実施形態において、画素回路の動作について説明するための図である。

【図 26】上記第 2 の実施形態において、画素回路の動作について説明するための図である。

40

【図 27】上記第 2 の実施形態において、画素回路の動作について説明するための図である。

【図 28】従来例における画素回路の構成を示す回路図である。

【図 29】従来例における画素回路の動作について説明するための図である。

【発明を実施するための形態】

【0 0 1 8】

以下、添付図面を参照しつつ、実施形態について説明する。なお、以下においては、 i および j は 2 以上の整数であると仮定し、 m は 1 以上 i 以下の整数であると仮定し、 n は 1 以上 j 以下の整数であると仮定する。また、各ノード等の電圧は、 0 V を基準電位とした場合の当該基準電位からの電位差を表している。

50

**【0019】**

<1. 第1の実施形態>

<1.1 全体構成>

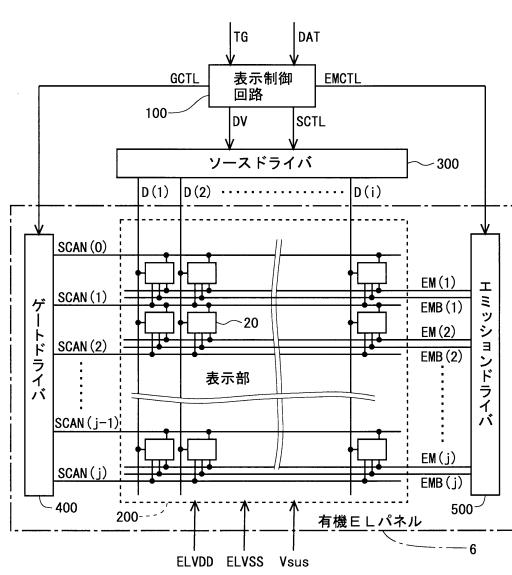

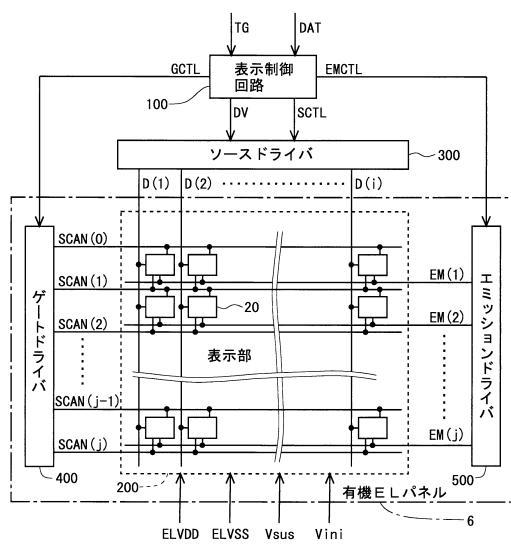

図2は、第1の実施形態に係る有機EL表示装置の全体構成を示すブロック図である。図2に示すように、この有機EL表示装置は、表示制御回路100と表示部200とソースドライバ(データ信号線駆動回路)300とゲートドライバ(走査信号線駆動回路)400とエミッションドライバ(発光制御線駆動回路)500とを備えている。なお、本実施形態においては、表示部200を含む有機ELパネル6内にゲートドライバ400およびエミッションドライバ500が形成されている。すなわち、ゲートドライバ400およびエミッションドライバ500はモノリシック化されている。但し、ゲートドライバ400およびエミッションドライバ500がモノリシック化されていない構成を採用することもできる。

10

**【0020】**

表示部200には、 $i$ 本のデータ信号線D(1)～D( $i$ )およびこれらに直交する( $j+1$ )本の走査信号線SCAN(0)～SCAN( $j$ )が配設されている。また、表示部200には、走査信号線SCAN(0)を除く $j$ 本の走査信号線SCAN(1)～SCAN( $j$ )と1対1で対応するように、 $j$ 本の発光制御線EM(1)～EM( $j$ )が配設されている。走査信号線SCAN(0)～SCAN( $j$ )と発光制御線EM(1)～EM( $j$ )とは互いに平行になっている。さらに、表示部200には、 $i$ 本のデータ信号線D(1)～D( $i$ )と $j$ 本の走査信号線SCAN(1)～SCAN( $j$ )との交差点に対応するように、 $i \times j$ 個の画素回路20が設けられている。このように $i \times j$ 個の画素回路20が設けられることによって、 $i$ 列× $j$ 行の画素マトリクスが表示部200に形成されている。なお、以下においては、( $j+1$ )本の走査信号線SCAN(0)～SCAN( $j$ )にそれぞれ与えられる走査信号にも符号SCAN(0)～SCAN( $j$ )を付す場合があり、 $j$ 本の発光制御線EM(1)～EM( $j$ )にそれぞれ与えられる発光制御信号にも符号EM(1)～EM( $j$ )を付す場合があり、 $i$ 本のデータ信号線D(1)～D( $i$ )にそれぞれ与えられるデータ信号にも符号D(1)～D( $i$ )を付す場合がある。

20

**【0021】**

表示部200には、また、全ての画素回路20に共通の図示しない電源線が配設されている。より詳細には、有機EL素子を駆動するためのハイレベル電源電圧ELVDDを供給する電源線(以下、「ハイレベル電源線」という。)、有機EL素子を駆動するためのローレベル電源電圧ELVSSを供給する電源線(以下、「ローレベル電源線」という。)、および基準電圧Vsusを供給する電源線(以下、「基準電源線」という。)が配設されている。ハイレベル電源電圧ELVDD、ローレベル電源電圧ELVSS、および基準電圧Vsusは、図示しない電源回路から供給される。本実施形態においては、ハイレベル電源線によって第1電源線が実現され、ローレベル電源線によって第2電源線が実現されている。

30

**【0022】**

以下、図2に示す各構成要素の動作について説明する。表示制御回路100は、外部から送られる画像データDATとタイミング信号群(水平同期信号、垂直同期信号など)TGとを受け取り、デジタル映像信号DVと、ソースドライバ300の動作を制御するソース制御信号SCTLと、ゲートドライバ400の動作を制御するゲート制御信号GCTLと、エミッションドライバ500の動作を制御するエミッションドライバ制御信号EMCTLとを出力する。ソース制御信号SCTLには、ソーススタートパルス信号、ソースクロック信号、ラッチストローブ信号などが含まれている。ゲート制御信号GCTLには、ゲートスタートパルス信号、ゲートクロック信号などが含まれている。エミッションドライバ制御信号EMCTLには、エミッションスタートパルス信号、エミッションクロック信号などが含まれている。

40

**【0023】**

ソースドライバ300は、 $i$ 本のデータ信号線D(1)～D( $i$ )に接続されている。

50

ソースドライバ300は、表示制御回路100から出力されたデジタル映像信号DVおよびソース制御信号SCTLを受け取り、i本のデータ信号線D(1)～D(i)にデータ信号を印加する。ソースドライバ300は、図示しないiビットのシフトレジスタ、サンプリング回路、ラッチ回路、およびi個のD/Aコンバータなどを含んでいる。シフトレジスタは、縦続接続されたi個のレジスタを有している。シフトレジスタは、ソースクロック信号に基づき、初段のレジスタに供給されるソーススタートパルス信号のパルスを入力端から出力端へと順次に転送する。このパルスの転送に応じて、シフトレジスタの各段からサンプリングパルスが出力される。そのサンプリングパルスに基づいて、サンプリング回路はデジタル映像信号DVを記憶する。ラッチ回路は、サンプリング回路に記憶された1行分のデジタル映像信号DVをラッチストローブ信号に従って取り込んで保持する。D/Aコンバータは、各データ信号線D(1)～D(i)に対応するように設けられている。D/Aコンバータは、ラッチ回路に保持されたデジタル映像信号DVをアナログ電圧に変換する。その変換されたアナログ電圧は、データ信号として全てのデータ信号線D(1)～D(i)に一斉に印加される。

#### 【0024】

ゲートドライバ400は、(j+1)本の走査信号線SCAN(0)～SCAN(j)に接続されている。ゲートドライバ400は、シフトレジスタおよび論理回路などによって構成されている。ゲートドライバ400は、表示制御回路100から出力されたゲート制御信号GCTLに基づいて、(j+1)本の走査信号線SCAN(0)～SCAN(j)を駆動する。

#### 【0025】

エミッションドライバ500は、j本の発光制御線EM(1)～EM(j)に接続されている。エミッションドライバ500は、シフトレジスタおよび論理回路などによって構成されている。エミッションドライバ500は、表示制御回路100から出力されたエミッションドライバ制御信号EMCTLに基づいて、j本の発光制御線EM(1)～EM(j)を駆動する。

#### 【0026】

以上のようにして、i本のデータ信号線D(1)～D(i)、(j+1)本の走査信号線SCAN(0)～SCAN(j)、およびj本の発光制御線EM(1)～EM(j)が駆動されることによって、画像データDATに基づく画像が表示部200に表示される。

#### 【0027】

##### <1.2 画素回路の構成>

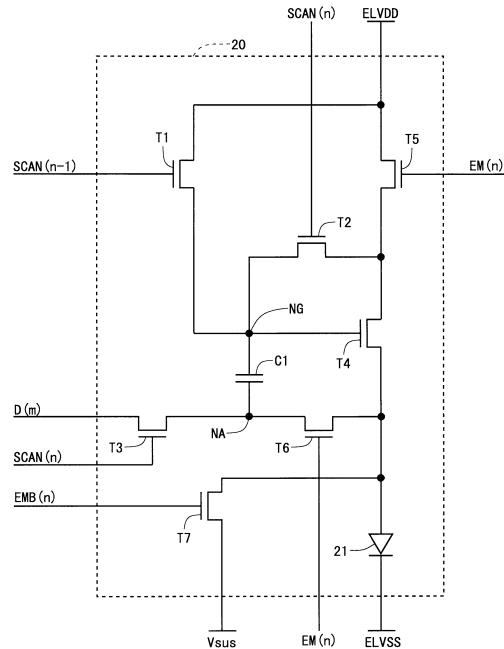

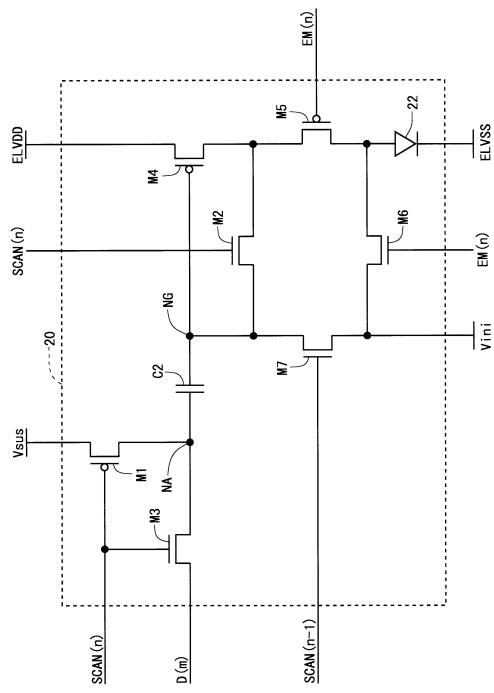

次に、表示部200内の画素回路20の構成について説明する。図1は、第n行第m列の画素回路20の構成を示す回路図である。この画素回路20は、表示素子（電流によって駆動される表示素子）としての1個の有機EL素子（有機発光ダイオード）T1と、7個のトランジスタ（典型的には薄膜トランジスタ）T1～T7（第1初期化トランジスタT1、閾値電圧補償トランジスタT2、書き込み制御トランジスタT3、駆動トランジスタT4、第1発光制御トランジスタT5、第2発光制御トランジスタT6、第2初期化トランジスタT7）と、1個の保持キャパシタC1とを含んでいる。保持キャパシタC1は、2つの電極（第1電極および第2電極）からなる容量素子である。トランジスタT1～T7は、nチャネル型のトランジスタである。

#### 【0028】

図1に示した構成に関し、第1初期化トランジスタT1の第2導通端子、閾値電圧補償トランジスタT2の第1導通端子、駆動トランジスタT4の制御端子、および保持キャパシタC1の第1電極に接続されたノードを「第1制御ノード」という。第1制御ノードには符号NGを付す。また、書き込み制御トランジスタT3の第2導通端子、第2発光制御トランジスタT6の第1導通端子、および保持キャパシタC1の第2電極に接続されたノードを「第2制御ノード」という。第2制御ノードには符号NAを付す。

#### 【0029】

第1初期化トランジスタT1については、制御端子は(n-1)行目の走査信号線SC

10

20

30

40

50

A N ( n - 1 ) に接続され、第 1 導通端子はハイレベル電源線と第 1 発光制御トランジスタ T 5 の第 1 導通端子とに接続され、第 2 導通端子は第 1 制御ノード N G に接続されている。閾値電圧補償トランジスタ T 2 については、制御端子は n 行目の走査信号線 S C A N ( n ) に接続され、第 1 導通端子は第 1 制御ノード N G に接続され、第 2 導通端子は駆動トランジスタ T 4 の第 1 導通端子と第 1 発光制御トランジスタ T 5 の第 2 導通端子に接続されている。書き込み制御トランジスタ T 3 については、制御端子は n 行目の走査信号線 S C A N ( n ) に接続され、第 1 導通端子は m 列目のデータ信号線 D ( m ) に接続され、第 2 導通端子は第 2 制御ノード N A に接続されている。駆動トランジスタ T 4 については、制御端子は第 1 制御ノード N G に接続され、第 1 導通端子は閾値電圧補償トランジスタ T 2 の第 2 導通端子と第 1 発光制御トランジスタ T 5 の第 2 導通端子とに接続され、第 2 導通端子は第 2 発光制御トランジスタ T 6 の第 2 導通端子と第 2 初期化トランジスタ T 7 の第 1 導通端子と有機 E L 素子 2 1 のアノード端子（第 1 端子）とに接続されている。

10

#### 【 0 0 3 0 】

第 1 発光制御トランジスタ T 5 については、制御端子は n 行目の発光制御線 E M ( n ) に接続され、第 1 導通端子はハイレベル電源線と第 1 初期化トランジスタ T 1 の第 1 導通端子とに接続され、第 2 導通端子は閾値電圧補償トランジスタ T 2 の第 2 導通端子と駆動トランジスタ T 4 の第 1 導通端子とに接続されている。第 2 発光制御トランジスタ T 6 については、制御端子は n 行目の発光制御線 E M ( n ) に接続され、第 1 導通端子は第 2 制御ノード N A に接続され、第 2 導通端子は駆動トランジスタ T 4 の第 2 導通端子と第 2 初期化トランジスタ T 7 の第 1 導通端子と有機 E L 素子 2 1 のアノード端子とに接続されている。第 2 初期化トランジスタ T 7 については、制御端子は n 行目の走査信号線 S C A N ( n ) に接続され、第 1 導通端子は駆動トランジスタ T 4 の第 2 導通端子と第 2 発光制御トランジスタ T 6 の第 2 導通端子と有機 E L 素子 2 1 のアノード端子とに接続され、第 2 導通端子は基準電源線に接続されている。保持キャパシタ C 1 については、第 1 電極は第 1 制御ノード N G に接続され、第 2 電極は第 2 制御ノード N A に接続されている。有機 E L 素子 2 1 については、アノード端子は駆動トランジスタ T 4 の第 2 導通端子と第 2 発光制御トランジスタ T 6 の第 2 導通端子と第 2 初期化トランジスタ T 7 の第 1 導通端子とに接続され、カソード端子（第 2 端子）はローレベル電源線に接続されている。

20

#### 【 0 0 3 1 】

本実施形態においては、第 1 初期化トランジスタ T 1 、閾値電圧補償トランジスタ T 2 、および第 2 初期化トランジスタ T 7 には酸化物 T F T が採用され、書き込み制御トランジスタ T 3 、駆動トランジスタ T 4 、第 1 発光制御トランジスタ T 5 、および第 2 発光制御トランジスタ T 6 には L T P S - T F T が採用されている。

30

#### 【 0 0 3 2 】

なお、酸化物 T F T のチャネル層を形成する酸化物半導体は、本実施形態においては、インジウム、ガリウム、亜鉛、および酸素によって構成されている。但し、これには限定されない。

#### 【 0 0 3 3 】

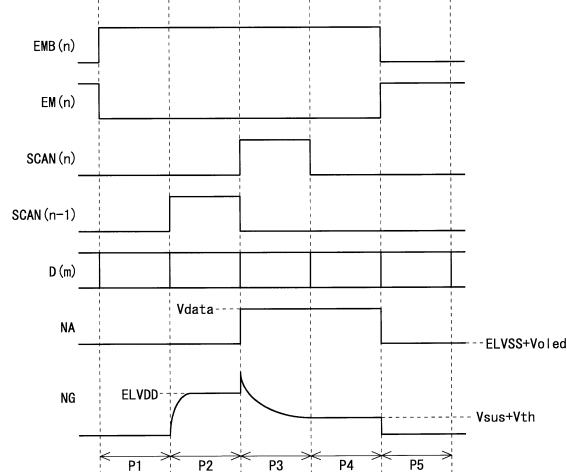

##### < 1 . 3 駆動方法（画素回路の動作）>

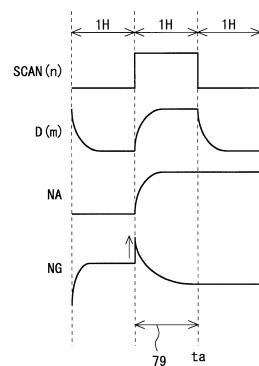

次に、図 3 を参照しつつ、図 1 に示した画素回路 2 0 の動作について説明する。期間 P 1 よりも前の期間および期間 P 5 以降の期間が、この画素回路 2 0 内の有機 E L 素子 2 1 についての発光期間である。発光制御信号 E M および走査信号 S C A N に関し、ハイレベルがオンレベルに相当し、ローレベルがオフレベルに相当する。なお、第 2 制御ノード N A および第 1 制御ノード N G の電圧の変化はデータ信号 D ( m ) に依存するので、図 3 に示す第 2 制御ノード N A および第 1 制御ノード N G の電圧波形は一例である。また、図 3 の期間 P 1 ~ P 5 における各トランジスタ（但し、駆動トランジスタ T 4 を除く）の状態（オン / オフ状態）の推移を図 4 に示している。

40

#### 【 0 0 3 4 】

期間 P 1 よりも前の期間には、発光制御信号 E M ( n ) はハイレベルとなっていて、走査信号 S C A N ( n ) , S C A N ( n - 1 ) はローレベルとなっている。このとき、第 1

50

発光制御トランジスタ T 5 および第 2 発光制御トランジスタ T 6 はオン状態となっている。第 2 発光制御トランジスタ T 6 がオン状態となっているので、駆動トランジスタ T 4 の制御端子 - 第 2 導通端子間の電圧は保持キャパシタ C 1 の充電電圧に等しくなっている。また、第 1 発光制御トランジスタ T 5 がオン状態となっているので、保持キャパシタ C 1 の充電電圧の大きさに応じて駆動電流が有機 EL 素子 2 1 に供給されている。これにより、有機 EL 素子 2 1 は駆動電流の大きさに応じて発光している。

#### 【 0 0 3 5 】

期間 P 1 になると、発光制御信号 E M ( n ) がハイレベルからローレベルに変化する。これにより、第 1 発光制御トランジスタ T 5 および第 2 発光制御トランジスタ T 6 がオフ状態となる。その結果、有機 EL 素子 2 1 への駆動電流の供給が遮断され、有機 EL 素子 2 1 は消灯状態となる。

10

#### 【 0 0 3 6 】

期間 P 2 になると、走査信号 S C A N ( n - 1 ) がローレベルからハイレベルに変化する。これにより、第 1 初期化トランジスタ T 1 がオン状態となり、図 5 で符号 6 1 を付した矢印で示すように第 1 制御ノード N G に電流が供給される。その結果、保持キャパシタ C 1 が充電され、第 1 制御ノード N G の電圧が上昇する。これにより、第 1 制御ノード N G の電圧はハイレベル電源電圧 E L V D D に等しくなる。以上のように、期間 P 2 には、第 1 制御ノード N G の電圧（すなわち、駆動トランジスタ T 4 のゲート電圧）が初期化される。

20

#### 【 0 0 3 7 】

期間 P 3 になると、走査信号 S C A N ( n - 1 ) がハイレベルからローレベルに変化する。これにより、第 1 初期化トランジスタ T 1 がオフ状態となり、第 1 制御ノード N G の電圧の初期化は終了する。また、期間 P 3 になると、走査信号 S C A N ( n ) がローレベルからハイレベルに変化する。これにより、閾値電圧補償トランジスタ T 2 、書き込み制御トランジスタ T 3 、および第 2 初期化トランジスタ T 7 がオン状態となる。書き込み制御トランジスタ T 3 がオン状態となることによって、図 6 で符号 6 2 を付した矢印で示すように、データ信号 D ( m ) が書き込み制御トランジスタ T 3 を介して第 2 制御ノード N A に与えられる。これにより、データ信号 D ( m ) に応じて、第 2 制御ノード N A の電圧が変化する。このとき、第 2 制御ノード N A の電圧は、上昇する場合もあるし、低下する場合もあるし、維持される場合もある。ところで、第 2 制御ノード N A - 第 1 制御ノード N G 間には保持キャパシタ C 1 が設けられている。従って、第 2 制御ノード N A の電圧の変化に応じて第 1 制御ノード N G の電圧も変化する。また、閾値電圧補償トランジスタ T 2 および第 2 初期化トランジスタ T 7 がオン状態となることによって、図 6 で符号 6 3 を付した矢印で示すように、第 1 制御ノード N G から基準電源線へと電流が流れれる。これにより、第 1 制御ノード N G の電圧は徐々に低下する。そして、駆動トランジスタ T 4 の制御端子 - 第 2 導通端子間の電圧が当該駆動トランジスタ T 4 の閾値電圧に等しくなると、駆動トランジスタ T 4 の第 1 導通端子 - 第 2 導通端子間に電流が流れなくなり、第 1 制御ノード N G の電圧の低下が止まる。具体的には、第 1 制御ノード N G の電圧は、基準電圧 V s u s と駆動トランジスタ T 4 の閾値電圧 V t h との和に等しくなるまで低下する。このとき、有機 EL 素子 2 1 のアノード電圧は基準電圧 V s u s に等しくなっている。すなわち、期間 P 3 には、有機 EL 素子 2 1 のアノード電圧が基準電圧 V s u s に基づいて初期化される。

30

#### 【 0 0 3 8 】

期間 P 4 になると、走査信号 S C A N ( n ) がハイレベルからローレベルに変化する。これにより、閾値電圧補償トランジスタ T 2 、書き込み制御トランジスタ T 3 、および第 2 初期化トランジスタ T 7 がオフ状態となる。期間 P 4 には、第 1 制御ノード N G および第 2 制御ノード N A の電圧は、期間 P 3 の終了時点における電圧が維持される。

40

#### 【 0 0 3 9 】

期間 P 5 になると、発光制御信号 E M ( n ) がローレベルからハイレベルに変化する。これにより、第 2 発光制御トランジスタ T 6 がオン状態となり、駆動トランジスタ T 4 の

50

第2導通端子と第2制御ノードN Aとの間が電気的に接続された状態となる。すなわち、駆動トランジスタT 4の第2導通端子の電圧と第2制御ノードN Aの電圧とが等しくなる。また、期間P 5には、第1発光制御トランジスタT 5がオン状態となる。以上より、駆動トランジスタT 4の制御端子 - 第2導通端子間の電圧（保持キャパシタC 1の充電電圧）の大きさに応じて、図7で符号6 4を付した矢印で示すように駆動電流が有機EL素子2 1に供給される。その結果、その駆動電流の大きさに応じて有機EL素子2 1が発光する。なお、有機EL素子2 1のアノード電圧は駆動電流の大きさに応じて変化し、第2制御ノードN Aの電圧は有機EL素子2 1のアノード電圧に等しくなるように変化する。そして、第2制御ノードN Aの電圧の変化に応じて第1制御ノードN Gの電圧も変化する。

#### 【0040】

その後、発光制御信号EM(n)がハイレベルからローレベルに変化するまでの期間を通じて、駆動電流の大きさに応じて有機EL素子2 1が発光する状態が継続される。

#### 【0041】

ここで、電圧の設定や電圧の変化の具体例について説明する。例えば、ハイレベル電源電圧ELVDDは11.5Vに設定され、ローレベル電源電圧ELVSSおよび基準電圧V<sub>sus</sub>は2.5Vに設定され、走査信号SCANおよび発光制御信号EMのハイレベル側の電圧は14.5Vに設定され、走査信号SCANおよび発光制御信号EMのローレベル側の電圧は-3.5Vに設定される。また、データ信号Dの電圧は1V～6Vの範囲内で設定される。これに関し、白色に対応する電圧が1Vであり、黒色に対応する電圧が6Vである。なお、駆動トランジスタT 4の閾値電圧は4Vになっていると仮定する。また、データ信号Dの電圧が白色に対応する電圧(1V)である時には発光期間中の有機EL素子2 1のアノード・カソード間電圧V<sub>ole</sub>dが4Vになると仮定し、データ信号Dの電圧が黒色に対応する電圧(6V)である時には発光期間中の有機EL素子2 1のアノード・カソード間電圧V<sub>ole</sub>dが0Vになると仮定する。

#### 【0042】

まず、データ信号Dの電圧が白色に対応する電圧(1V)であるケースについて説明する。期間P 2の終了時点には、データ信号Dの電圧に関わらず第1制御ノードN Gの電圧が11.5Vとなる。

#### 【0043】

期間P 3には、第2制御ノードN Aの電圧が1Vとなる。また、上述したように、第1制御ノードN Gの電圧は、基準電圧V<sub>sus</sub>と駆動トランジスタT 4の閾値電圧V<sub>th</sub>との和に等しくなるまで低下する。従って、期間P 3の終了時点には、第1制御ノードN Gの電圧は6.5Vとなる。上述したように、期間P 4には、第1制御ノードN Gおよび第2制御ノードN Aの電圧は、期間P 3の終了時点における電圧が維持される。以上より、期間P 4の終了時点においては、第2制御ノードN Aの電圧は1Vであり、第1制御ノードN Gの電圧は6.5Vである。

#### 【0044】

期間P 5には、第2制御ノードN Aの電圧は、ローレベル電源電圧ELVSSと有機EL素子2 1のアノード・カソード間電圧V<sub>ole</sub>dとの和に等しくなる。すなわち、期間P 5における第2制御ノードN Aの電圧V<sub>NA</sub>は下記の式(1)で表される。

$$V_{NA} = ELVSS + V_{ole}d \quad \dots (1)$$

従って、期間P 5には、第2制御ノードN Aの電圧V<sub>NA</sub>は6.5Vとなる。

#### 【0045】

また、データ信号Dの電圧をV<sub>data</sub>で表すと、期間P 4から期間P 5にかけての第2制御ノードN Aの電圧の変化V<sub>NA</sub>は下記の式(2)で表される。

$$V_{NA} = ELVSS + V_{ole}d - V_{data} \quad \dots (2)$$

この例では、第2制御ノードN Aの電圧の変化V<sub>NA</sub>は5.5Vとなる。

#### 【0046】

上述したように、期間P 5には、第2制御ノードN Aの電圧の変化に応じて第1制御ノードN Gの電圧も変化する。期間P 4の終了時点における第1制御ノードN Gの電圧は基

10

20

30

40

50

準電圧  $V_{sus}$  と駆動トランジスタ T 4 の閾値電圧  $V_{th}$  との和に等しいので、期間 P 5 における第 1 制御ノード N G の電圧  $V_{NG}$  は下記の式(3)で表される。なお、k は第 2 制御ノード N A によって形成される容量全体の容量値に対する保持キャパシタ C 1 の容量値の割合であって、ここでは「 $k = 1$ 」が成立すると仮定する。

$$V_{NG} = V_{sus} + V_{th} + k \cdot V_{NA} \quad \dots (3)$$

以上より、期間 P 5 には、第 1 制御ノード N G の電圧  $V_{NG}$  は 12 V となる。

#### 【0047】

期間 P 5 における駆動トランジスタ T 4 の第 1 導通端子 - 第 2 導通端子間の電圧  $V_{gs}$  は下記の式(4)で表される。

$$\begin{aligned} V_{gs} &= V_{NG} - V_{NA} \\ &= V_{sus} + V_{th} + k \cdot V_{NA} - (ELVSS + V_{oled}) \\ &= V_{sus} + V_{th} + ELVSS + V_{oled} - V_{data} - (ELVSS + V_{oled}) \\ &= V_{sus} + V_{th} - V_{data} \quad \dots (4) \end{aligned}$$

この例では、駆動トランジスタ T 4 の第 1 導通端子 - 第 2 導通端子間の電圧  $V_{gs}$  は 5.5 V となる。

#### 【0048】

期間 P 5 以降の期間に有機 E L 素子 2 1 に流れる電流  $I_{oled}$  は、「 $V_{gs} = V_{th}$ 」が成立する時には下記の式(5)で表され、「 $V_{gs} < V_{th}$ 」が成立する時には下記の式(6)で表される。

#### 【数 1】

$$\begin{aligned} I_{oled} &= \frac{\beta}{2} (V_{gs} - V_{th})^2 \\ &= \frac{\beta}{2} (V_{sus} + V_{th} - V_{data} - V_{th})^2 \\ &= \frac{\beta}{2} (V_{sus} - V_{data})^2 \quad \dots (5) \end{aligned}$$

$$\text{但し、 } \beta = \frac{W}{L} \times \mu \times Cox$$

$$\left. \begin{array}{l} W : \text{駆動トランジスタのチャネル幅} \\ L : \text{駆動トランジスタのチャネル長} \\ \mu : \text{駆動トランジスタの移動度} \\ Cox : \text{駆動トランジスタのゲート絶縁膜容量} \end{array} \right\}$$

#### 【数 2】

10

20

30

40

50

$$I_{oled} = \frac{qAD_nn_i e^{\frac{q\psi_B}{kT}}}{L} (1 - e^{-qV_D/kT}) e^{q\psi_S/kT} \dots (6)$$

A : 駆動トランジスタのチャネルの断面積

D<sub>n</sub> : 拡散係数

n<sub>i</sub> : 真性キャリア密度

q : 素電荷

k : ボルツマン定数

T : 温度

V<sub>D</sub> : 駆動トランジスタの第1端子の電圧

L : 駆動トランジスタのチャネル長

ψ<sub>B</sub> : 基板のフェルミ準位と真性フェルミ準位の差

ψ<sub>S</sub> : 表面ポテンシャル

10

20

なお、 “  $V_{gS} < V_{th}$  ” が成立する時に關し、表面ポテンシャルは “  $V_{NG} - V_{th}$  ” で近似することができるので、  $I_{oled}$  は  $\exp(q(V_{NG} - V_{th})/kT)$  に比例する。すなわち、 “  $V_{gS} < V_{th}$  ” が成立する時、  $V_{NG}$  が小さくなるにつれて  $I_{oled}$  は指數関数的に減少する。

## 【0049】

次に、データ信号Dの電圧が黒色に対応する電圧(6V)であるケースについて説明する。なお、上述したように、期間P2の終了時点には、データ信号Dの電圧に関わらず第1制御ノードNGの電圧が11.5Vとなる。

## 【0050】

30

期間P3には、第2制御ノードNAの電圧が6Vとなる。また、上述したように、期間P3の終了時点には、第1制御ノードNGの電圧は6.5Vとなり、期間P4には、第1制御ノードNGおよび第2制御ノードNAの電圧は、期間P3の終了時点における電圧が維持される。以上より、期間P4の終了時点においては、第2制御ノードNAの電圧は6Vであり、第1制御ノードNGの電圧は6.5Vである。

## 【0051】

期間P5には、上式(1)より、第2制御ノードNAの電圧VNAは2.5Vとなる。期間P4から期間P5にかけての第2制御ノードNAの電圧の変化VNAは、上式(2)より、-3.5Vとなる。また、期間P5には、上式(3)より、第1制御ノードNGの電圧VNGは3Vとなる。期間P5における駆動トランジスタT4の第1導通端子-第2導通端子間の電圧Vgsは、上式(4)より、0.5Vとなる。

40

## 【0052】

期間P5以降の期間に有機EL素子21に流れる電流I<sub>oled</sub>については、データ信号Dの電圧が白色に対応する電圧(1V)であるケースと同様の式で表される(上式(5)および上式(6)を参照)。

## 【0053】

<1.4 従来例との対比>

上述した米国特許第10304378号明細書に記載された構成(図8参照)によれば、例えば、図9で符号78を付した矢印で表される期間に、保持キャパシタCstへのデータ信号Vdataに応じた電圧の充電(書き込み)と、駆動トランジスタの閾値電圧の

50

ばらつきを補償するための補償処理とが行われる。但し、補償処理の開始時点には Node 3 の電圧がデータ信号 V data の電圧に設定されている必要がある。従って、信号 Scan 1 をローレベルかつ信号 Scan 2 をハイレベルとすることによって Node 3 の電圧をデータ信号 V data の電圧に設定するための期間（図 9 で符号 77 を付した矢印で表される期間）が必要である。以上より、データ信号 V data の電圧の変化開始時点から補償処理の終了時点（Node 2 の電圧が駆動トランジスタの閾値電圧に応じた大きさとなる時点）までの期間は比較的長くなる。これに対して、本実施形態によれば、図 6 から把握されるようにデータ信号 D の書き込みのための電流経路と補償処理のための電流経路とが全く別の経路となっているため、データ信号 D の電圧の変化開始時点に補償処理の動作を開始することができる。すなわち、図 10 で符号 79 を付した矢印で表される期間のように、データ信号 D の電圧の変化開始時点から補償処理の終了時点（第 1 制御ノード NG の電圧が駆動トランジスタの閾値電圧に応じた大きさとなる時点）までの期間は比較的短くなる。以上のように、米国特許第 10304378 号明細書に記載された構成によれば、本実施形態に係る構成と比較して、1 水平期間（1H）の長さは少なくとも図 9 で符号 77 を付した矢印で表される期間だけ長くなる。換言すれば、本実施形態によれば、1 水平期間（1H）の長さを短くすることができるので、従来よりも高速駆動が可能となる。

#### 【0054】

##### < 1.5 効果 >

本実施形態によれば、画素回路 20 の構成に関し、書き込み制御トランジスタ T3 を介してデータ信号線 D に接続された第 2 制御ノード NA と駆動トランジスタ T4 の制御端子に接続された第 1 制御ノード NG との間に保持キャパシタ C1 が設けられている。このような構成により、保持キャパシタ C1 の充電は駆動トランジスタ T4 を介さずに行われる。すなわち、保持キャパシタ C1 の充電は速やかに行われる。また、データ信号 D の電圧は閾値電圧補償トランジスタ T2 がオン状態からオフ状態に変化する時点（図 10 の時点 ta）までに確定していれば良いので、データ信号 D の波形変化に大きな遅延が生じない限り表示品位は低下しない。さらに、駆動トランジスタ T4 には LTPS-TFT が採用されているので、駆動トランジスタ T4 の閾値電圧を補償するための補償処理が行われる期間 P3（図 3 参照）に第 1 制御ノード NG の充電が速やかに行われる。以上より、例えば駆動周波数を 120Hz とするような高周波駆動（高速駆動）が行われても、良好な表示品位が維持される。また、第 1 制御ノード NG に導通端子が接続されたトランジスタ（詳しくは、第 1 制御ノード NG に第 2 導通端子が接続された第 1 初期化トランジスタ T1 および第 1 制御ノード NG に第 1 導通端子が接続された閾値電圧補償トランジスタ T2）には、酸化物 TFT が採用されている。それ故、それらのトランジスタでのリーク電流の発生が防止される。従って、例えば駆動周波数を 1Hz とするような低周波駆動（低速駆動）が行われても、リーク電流に起因して表示品位が低下することはない。すなわち、良好な表示品位が維持される。以上より、本実施形態によれば、表示品位の低下を引き起こすことなく高周波駆動および低周波駆動の双方を可能ならしめる画素回路 20 を備えた有機 EL 表示装置が実現される。

#### 【0055】

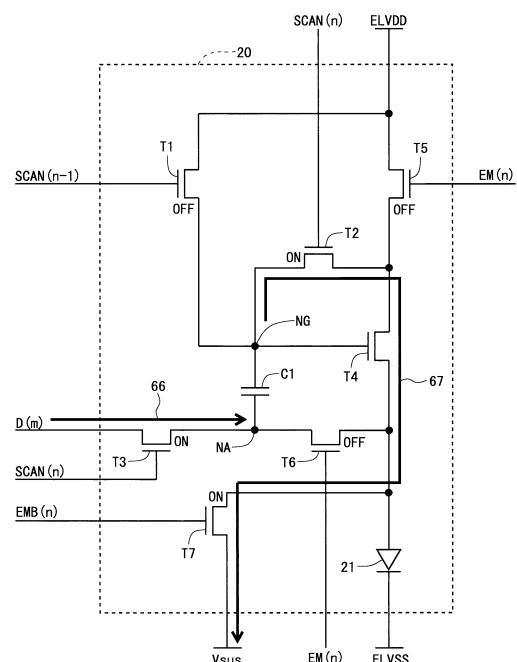

##### < 1.6 変形例 >

第 1 の実施形態の変形例について説明する。但し、第 1 の実施形態と異なる点を中心に説明する。

#### 【0056】

図 11 は、第 1 の実施形態の変形例に係る有機 EL 表示装置の全体構成を示すブロック図である。本変形例においては、発光制御信号 EM の論理反転信号を伝達する信号配線（以下、「リセット制御線」という。）が表示部 200 に配設されている。詳しくは、j 本の発光制御線 EM(1) ~ EM(j) と 1 対 1 で対応するように、j 本のリセット制御線 EMB(1) ~ EMB(j) が表示部 200 に配設されている。このように、本変形例においては、表示部 200 には、i 本のデータ信号線 D(1) ~ D(i)、(j+1) 本の

走査信号線 S C A N ( 0 ) ~ S C A N ( j ) 、および j 本の発光制御線 E M ( 1 ) ~ E M ( j ) に加えて、 j 本のリセット制御線 E M B ( 1 ) ~ E M B ( j ) が配設されている。なお、以下においては、 j 本のリセット制御線 E M B ( 1 ) ~ E M B ( j ) によって伝達されるリセット制御信号（発光制御信号 E M の論理反転信号）にも符号 E M B ( 1 ) ~ E M B ( j ) を付す場合がある。

#### 【 0 0 5 7 】

図 1 2 は、第 n 行第 m 列の画素回路 2 0 の構成を示す回路図である。第 1 の実施形態（図 1 参照）と同様、この画素回路 2 0 は、1 個の有機 E L 素子 2 1 と、7 個のトランジスタ（典型的には薄膜トランジスタ）T 1 ~ T 7（第 1 初期化トランジスタ T 1、閾値電圧補償トランジスタ T 2、書き込み制御トランジスタ T 3、駆動トランジスタ T 4、第 1 発光制御トランジスタ T 5、第 2 発光制御トランジスタ T 6、第 2 初期化トランジスタ T 7）と、1 個の保持キャパシタ C 1 を含んでいる。本変形例においては、第 2 初期化トランジスタ T 7 の制御端子が n 行目のリセット制御線 E M B ( n ) に接続されている。それ以外の点については、第 1 の実施形態と同様である。

#### 【 0 0 5 8 】

第 2 初期化トランジスタ T 7 がオン状態になると、有機 E L 素子 2 1 のアノード端子と基準電源線とが電気的に接続された状態となり、基準電圧 V s u s に基づいて有機 E L 素子 2 1 のアノード電圧が初期化される。このように、リセット制御線 E M B は、有機 E L 素子 2 1 のアノード端子の状態を初期化するための信号配線である。

#### 【 0 0 5 9 】

なお、本変形例においても、第 1 初期化トランジスタ T 1、閾値電圧補償トランジスタ T 2、および第 2 初期化トランジスタ T 7 には酸化物 T F T が採用され、書き込み制御トランジスタ T 3、駆動トランジスタ T 4、第 1 発光制御トランジスタ T 5、および第 2 発光制御トランジスタ T 6 には L T P S - T F T が採用されている。

#### 【 0 0 6 0 】

図 1 3 を参照しつつ、図 1 2 に示した画素回路 2 0 の動作について説明する。なお、図 1 3 の期間 P 1 ~ P 5 における各トランジスタ（但し、駆動トランジスタ T 4 を除く）の状態（オン / オフ状態）の推移を図 1 4 に示している。

#### 【 0 0 6 1 】

期間 P 1 よりも前の期間については、第 1 の実施形態と同様である。なお、リセット制御信号 E M B ( n ) はローレベルとなっている。期間 P 1 には、第 1 の実施形態と同様、有機 E L 素子 2 1 は消灯状態となる。また、期間 P 1 には、リセット制御信号 E M B ( n ) がローレベルからハイレベルに変化する。これにより、第 2 初期化トランジスタ T 7 がオン状態となり、図 1 5 で符号 6 5 を付した矢印で示すように電流が生じ、有機 E L 素子 2 1 のアノード電圧が基準電圧 V s u s に基づいて初期化される。

#### 【 0 0 6 2 】

期間 P 2 には、第 1 の実施形態と同様、第 1 初期化トランジスタ T 1 がオン状態となることによって第 1 制御ノード N G の電圧（すなわち、駆動トランジスタ T 4 のゲート電圧）が初期化される。

#### 【 0 0 6 3 】

期間 P 3 には、リセット制御信号 E M B ( n ) はハイレベルで維持され、走査信号 S C A N ( n ) がローレベルからハイレベルに変化する。これにより、第 2 初期化トランジスタ T 7 はオン状態で維持され、閾値電圧補償トランジスタ T 2 および書き込み制御トランジスタ T 3 がオン状態となる。以上より、第 1 の実施形態と同様、図 1 6 で符号 6 6 を付した矢印で示すようにデータ信号 D ( m ) が書き込み制御トランジスタ T 3 を介して第 2 制御ノード N A に与えられ、また、図 1 6 で符号 6 7 を付した矢印で示すように第 1 制御ノード N G から基準電源線へと電流が流れる。これにより、データ信号 D ( m ) に応じて第 2 制御ノード N A の電圧が変化し、また、第 1 制御ノード N G の電圧は基準電圧 V s u s と駆動トランジスタ T 4 の閾値電圧 V t h との和に等しくなる。

#### 【 0 0 6 4 】

10

20

30

40

50

期間 P 4 には、第 1 の実施形態と同様、第 1 制御ノード NG および第 2 制御ノード NA の電圧は、期間 P 3 の終了時点における電圧が維持される。

#### 【 0 0 6 5 】

期間 P 5 になると、リセット制御信号 E M B ( n ) がハイレベルからローレベルに変化する。これにより、第 2 初期化トランジスタ T 7 がオフ状態となる。また、期間 P 5 には、発光制御信号 E M ( n ) がローレベルからハイレベルに変化する。これにより、第 1 発光制御トランジスタ T 5 および第 2 発光制御トランジスタ T 6 がオン状態となり、第 1 の実施形態と同様、駆動トランジスタ T 4 の制御端子 - 第 2 導通端子間の電圧（保持キャパシタ C 1 の充電電圧）の大きさに応じて、図 1 7 で符号 6 8 を付した矢印で示すように駆動電流が有機 E L 素子 2 1 に供給される。その結果、その駆動電流の大きさに応じて有機 E L 素子 2 1 が発光する。10

#### 【 0 0 6 6 】

その後、発光制御信号 E M ( n ) がハイレベルからローレベルに変化するまでの期間を通じて、駆動電流の大きさに応じて有機 E L 素子 2 1 が発光する状態が継続される。

#### 【 0 0 6 7 】

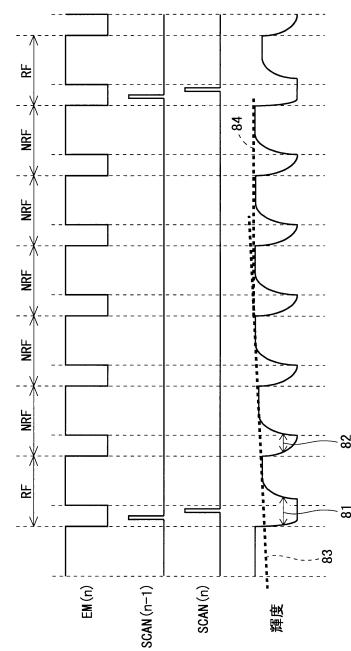

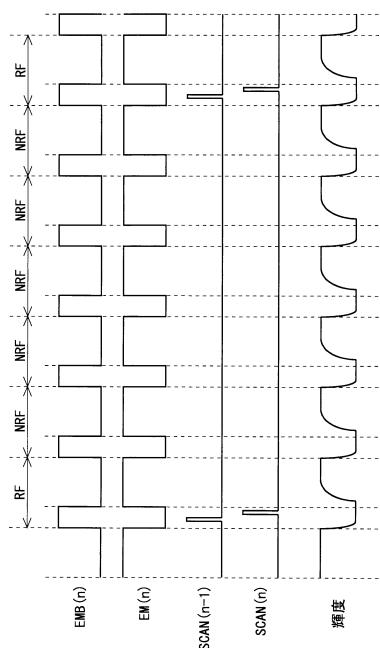

本変形例によれば、第 1 の実施形態と比較して低周波駆動が行われている際のフリッカの発生が抑制されるという効果が得られる。これについて、図 1 8 および図 1 9 を参照しつつ、以下に説明する。図 1 8 は、第 1 の実施形態における低周波駆動時の動作について説明するための波形図であり、図 1 9 は、本変形例における低周波駆動時の動作について説明するための波形図である。ここでは、n 行目の画素回路 2 0 に着目し、白色表示が行われていると仮定する。図 1 8 および図 1 9 では、表示画面の更新（画素回路 2 0 内へのデータ信号 D の書き込み）が行われるフレーム期間であるリフレッシュフレームを符号 R F で表し、表示画面の更新が行われないフレーム期間であるノンリフレッシュフレームを符号 N R F で表している。なお、発光制御信号 E M ( n ) がハイレベルとなっている期間が発光期間であり、発光制御信号 E M ( n ) がローレベルとなっている期間が非発光期間である。20

#### 【 0 0 6 8 】

まず、第 1 の実施形態に着目する（図 1 8 参照）。リフレッシュフレーム R F の非発光期間には、走査信号 S C A N ( n ) がハイレベルとなる期間があるので、第 2 初期化トランジスタ T 7 がオン状態となることによって有機 E L 素子 2 1 のアノード電圧が速やかに低下する。従って、輝度は速やかに低下する。また、このように有機 E L 素子 2 1 のアノード電圧が初期化されていることから、リフレッシュフレーム R F において非発光期間から発光期間に遷移した際に輝度は緩やかに上昇する。ノンリフレッシュフレーム N R F の非発光期間には、第 2 初期化トランジスタ T 7 はオフ状態で維持されるので、有機 E L 素子 2 1 のアノード電圧はそのまま維持される。そして、第 1 発光制御トランジスタ T 5 がオフ状態となることのみによって輝度が低下する。従って、輝度は緩やかに低下する。また、有機 E L 素子 2 1 のアノード電圧がそのまま維持されていることから、ノンリフレッシュフレーム N R F において非発光期間から発光期間に遷移した際には輝度は速やかに上昇する。以上より、リフレッシュフレーム R F とノンリフレッシュフレーム N R F とでは、輝度が所定レベル以下となっている期間の長さが異なる。より詳しくは、輝度が所定レベル以下となっている期間は、リフレッシュフレーム R F においては図 1 8 で符号 8 1 を付した矢印で示されるように比較的長いのに対して、ノンリフレッシュフレーム N R F においては図 1 8 で符号 8 2 を付した矢印で示されるように比較的短い。また、これに起因して、リフレッシュフレーム R F の終了後に安定した輝度が得られるまでに数フレームを要する（図 1 8 で符号 8 3 , 8 4 を付した太点線を参照）。以上のことから、第 1 の実施形態においては低周波のフリッカの発生が懸念される。30

#### 【 0 0 6 9 】

次に、本変形例に着目する（図 1 9 参照）。リフレッシュフレーム R F においてもノンリフレッシュフレーム N R F においても、非発光期間にはリセット制御信号 E M B ( n ) がハイレベルとなることによって第 2 初期化トランジスタ T 7 がオン状態になる。このた40

め、リフレッシュフレーム R Fにおいてもノンリフレッシュフレーム N R Fにおいても、発光期間から非発光期間に遷移する際には輝度は速やかに低下し、非発光期間から発光期間に遷移する際には輝度は緩やかに上昇する。すなわち、リフレッシュフレーム R Fとノンリフレッシュフレーム N R Fとで輝度は同じように変化する。従って、第 1 の実施形態とは異なり、輝度が所定レベル以下となっている期間の長さはリフレッシュフレーム R Fとノンリフレッシュフレーム N R Fとで等しくなる。また、第 1 の実施形態とは異なり、1 フレーム期間毎に駆動トランジスタ T 4 にオンバイアストレスが掛かるので、駆動トランジスタ T 4 のヒステリシスの影響を除去することが可能となる。以上より、本変形例によれば、低周波のフリッカの発生が抑制される。

## 【0070】

10

&lt; 2 . 第 2 の実施形態 &gt;

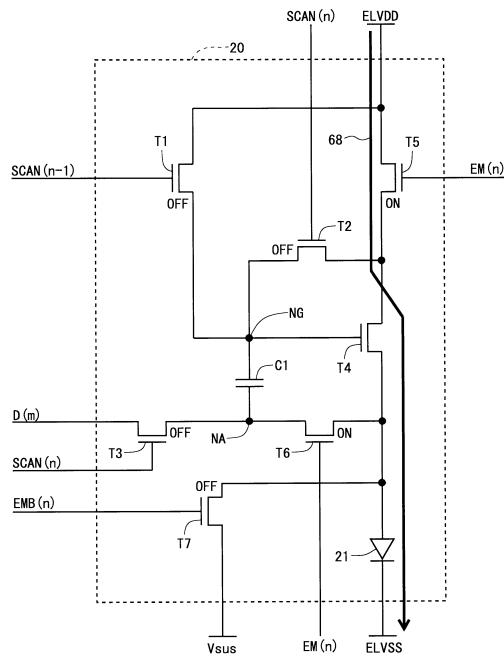

&lt; 2 . 1 全体構成 &gt;

図 2 0 は、第 2 の実施形態に係る有機 E L 表示装置の全体構成を示すブロック図である。本実施形態における全体構成は、第 1 の実施形態における全体構成（図 2 参照）とほぼ同様である。但し、本実施形態においては、初期化電圧 V i n i を供給する電源線（以下、「初期化電源線」という。）が表示部 2 0 0 に配設されている。初期化電圧 V i n i は、図示しない電源回路から供給される。

## 【0071】

20

&lt; 2 . 2 画素回路の構成 &gt;

図 2 1 は、第 n 行第 m 列の画素回路 2 0 の構成を示す回路図である。この画素回路 2 0 は、表示素子（電流によって駆動される表示素子）としての 1 個の有機 E L 素子（有機発光ダイオード）2 2 と、7 個のトランジスタ（典型的には薄膜トランジスタ）M 1 ~ M 7（第 1 初期化トランジスタ M 1、閾値電圧補償トランジスタ M 2、書き込み制御トランジスタ M 3、駆動トランジスタ M 4、第 1 発光制御トランジスタ M 5、第 2 発光制御トランジスタ M 6、第 2 初期化トランジスタ M 7）と、1 個の保持キャパシタ C 2 を含んでいる。保持キャパシタ C 2 は、2 つの電極（第 1 電極および第 2 電極）からなる容量素子である。閾値電圧補償トランジスタ M 2、書き込み制御トランジスタ M 3、第 2 発光制御トランジスタ M 6、および第 2 初期化トランジスタ M 7 は、n チャネル型のトランジスタである。第 1 初期化トランジスタ M 1、駆動トランジスタ M 4、および第 1 発光制御トランジスタ M 5 は、p チャネル型のトランジスタである。

30

## 【0072】

図 2 1 に示した構成に関し、閾値電圧補償トランジスタ M 2 の第 1 導通端子、駆動トランジスタ M 4 の制御端子、第 2 初期化トランジスタ M 7 の第 1 導通端子、および保持キャパシタ C 2 の第 1 電極に接続されたノードを「第 1 制御ノード」という。また、第 1 初期化トランジスタ M 1 の第 2 導通端子、書き込み制御トランジスタ M 3 の第 2 導通端子、および保持キャパシタ C 2 の第 2 電極に接続されたノードを「第 2 制御ノード」という。第 1 の実施形態と同様、第 1 制御ノードには符号 N G を付し、第 2 制御ノードには符号 N A を付す。

## 【0073】

40

第 1 初期化トランジスタ M 1 については、制御端子は n 行目の走査信号線 S C A N ( n ) に接続され、第 1 導通端子は基準電源線に接続され、第 2 導通端子は第 2 制御ノード N A に接続されている。閾値電圧補償トランジスタ M 2 については、制御端子は n 行目の走査信号線 S C A N ( n ) に接続され、第 1 導通端子は第 1 制御ノード N G に接続され、第 2 導通端子は駆動トランジスタ M 4 の第 2 導通端子と第 1 発光制御トランジスタ M 5 の第 1 導通端子に接続されている。書き込み制御トランジスタ M 3 については、制御端子は n 行目の走査信号線 S C A N ( n ) に接続され、第 1 導通端子は m 列目のデータ信号線 D ( m ) に接続され、第 2 導通端子は第 2 制御ノード N A に接続されている。駆動トランジスタ M 4 については、制御端子は第 1 制御ノード N G に接続され、第 1 導通端子はハイレベル電源線に接続され、第 2 導通端子は閾値電圧補償トランジスタ M 2 の第 2 導通端子と第 1 発光制御トランジスタ M 5 の第 1 導通端子とに接続されている。

50

### 【 0 0 7 4 】

第1発光制御トランジスタM5については、制御端子はn行目の発光制御線EM(n)に接続され、第1導通端子は閾値電圧補償トランジスタM2の第2導通端子と駆動トランジスタM4の第2導通端子とに接続され、第2導通端子は第2発光制御トランジスタM6の第1導通端子と有機EL素子21のアノード端子(第1端子)とに接続されている。第2発光制御トランジスタM6については、制御端子はn行目の発光制御線EM(n)に接続され、第1導通端子は第1発光制御トランジスタM5の第2導通端子と有機EL素子21のアノード端子とに接続され、第2導通端子は第2初期化トランジスタM7の第2導通端子と初期化電源線とに接続されている。第2初期化トランジスタM7については、制御端子は(n-1)行目の走査信号線SCAN(n-1)に接続され、第1導通端子は第1制御ノードNGに接続され、第2導通端子は第2発光制御トランジスタM6の第2導通端子と初期化電源線とに接続されている。保持キャパシタC2については、第1電極は第1制御ノードNGに接続され、第2電極は第2制御ノードNAに接続されている。有機EL素子21については、アノード端子は第1発光制御トランジスタM5の第2導通端子と第2発光制御トランジスタM6の第1導通端子とに接続され、カソード端子(第2端子)はローレベル電源線に接続されている。

10

### 【 0 0 7 5 】

本実施形態においては、閾値電圧補償トランジスタM2、書き込み制御トランジスタM3、第2発光制御トランジスタM6、および第2初期化トランジスタM7には酸化物TFTが採用され、第1初期化トランジスタM1、駆動トランジスタM4、および第1発光制御トランジスタM5にはLTPS-TFTが採用されている。

20

### 【 0 0 7 6 】

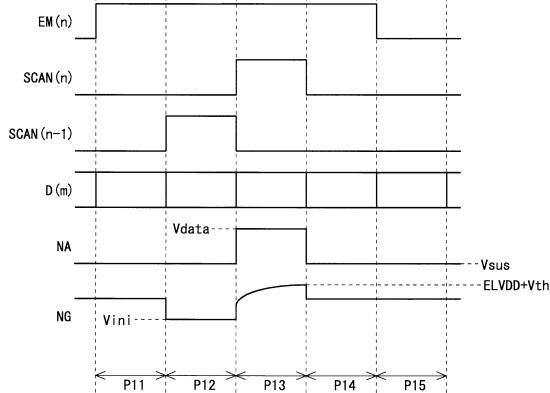

#### < 2 . 3 駆動方法(画素回路の動作) >

次に、図22を参照しつつ、図21に示した画素回路20の動作について説明する。図22の期間P11～P15における各トランジスタ(但し、駆動トランジスタM4を除く)の状態(オン/オフ状態)の推移を図23に示している。

### 【 0 0 7 7 】

期間P11よりも前の期間には、発光制御信号EM(n)、走査信号SCAN(n)、および走査信号SCAN(n-1)はローレベルとなっている。このとき、閾値電圧補償トランジスタM2、第2発光制御トランジスタM6、および第2初期化トランジスタM7はオフ状態となっていて、第1発光制御トランジスタM5はオン状態となっている。従って、駆動トランジスタM4の制御端子-第2導通端子間の電圧の大きさに応じて駆動電流が有機EL素子22に供給されている。これにより、有機EL素子22は駆動電流の大きさに応じて発光している。なお、書き込み制御トランジスタM3はオフ状態かつ第1初期化トランジスタM1はオン状態となっているので、第2制御ノードNAの電圧は基準電圧V<sub>sus</sub>に等しくなっている。

30

### 【 0 0 7 8 】

期間P11になると、発光制御信号EM(n)がローレベルからハイレベルに変化する。これにより、第1発光制御トランジスタM5がオフ状態となり、第2発光制御トランジスタM6がオン状態となる。第1発光制御トランジスタM5がオフ状態となることによって、有機EL素子22への駆動電流の供給が遮断され、有機EL素子22は消灯状態となる。また、第2発光制御トランジスタM6がオン状態となることによって、有機EL素子22のアノード電圧が初期化電圧V<sub>ini</sub>に基づいて初期化される。

40

### 【 0 0 7 9 】

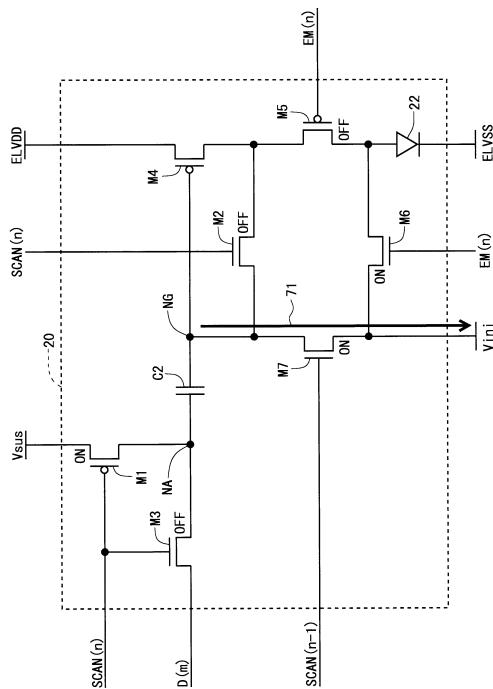

期間P12になると、走査信号SCAN(n-1)がローレベルからハイレベルに変化する。これにより、第2初期化トランジスタM7がオン状態となり、図24で符号71を付した矢印で示すように、第1制御ノードNGから初期化電源線へと電流が流れる。その結果、第1制御ノードNGの電圧は初期化電圧V<sub>ini</sub>に等しくなる。以上のように、期間P12には、第1制御ノードNGの電圧(すなわち、駆動トランジスタM4のゲート電圧)が初期化される。

50

### 【 0 0 8 0 】

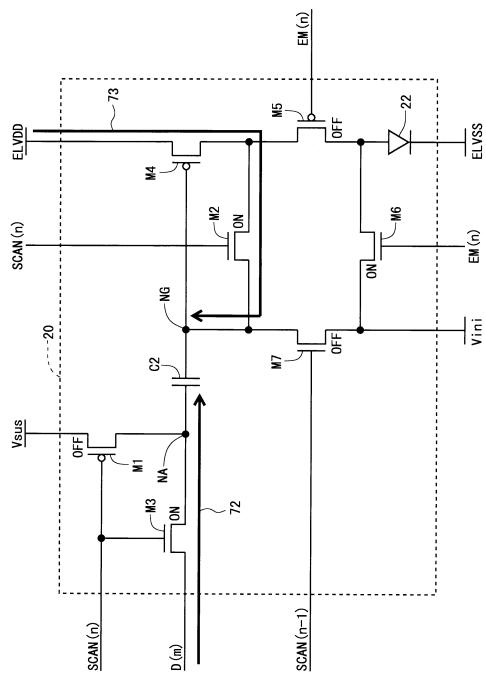

期間 P 1 3 になると、走査信号 S C A N ( n - 1 ) がハイレベルからローレベルに変化する。これにより、第 2 初期化トランジスタ M 7 がオフ状態となり、第 1 制御ノード N G の電圧の初期化は終了する。また、期間 P 1 3 になると、走査信号 S C A N ( n ) がローレベルからハイレベルに変化する。これにより、第 1 初期化トランジスタ M 1 がオフ状態となり、閾値電圧補償トランジスタ M 2 および書き込み制御トランジスタ M 3 がオン状態となる。第 1 初期化トランジスタ M 1 がオフ状態かつ書き込み制御トランジスタ M 3 がオン状態となることによって、図 2 5 で符号 7 2 を付した矢印で示すように、データ信号 D ( m ) が書き込み制御トランジスタ M 3 を介して第 2 制御ノード N A に与えられる。これにより、データ信号 D ( m ) に応じて、第 2 制御ノード N A の電圧が上昇する。ところで、第 2 制御ノード N A - 第 1 制御ノード N G 間には保持キャパシタ C 2 が設けられている。従って、第 2 制御ノード N A の電圧の上昇に応じて第 1 制御ノード N G の電圧も上昇する。また、閾値電圧補償トランジスタ M 2 がオン状態となることによって、図 2 5 で符号 7 3 を付した矢印で示すように、ハイレベル電源線から第 1 制御ノード N G へと電流が流れれる。これにより、第 1 制御ノード N G の電圧は徐々に上昇する。そして、駆動トランジスタ M 4 の制御端子 - 第 2 導通端子間の電圧が当該駆動トランジスタ M 4 の閾値電圧に等しくなると、駆動トランジスタ M 4 の第 1 導通端子 - 第 2 導通端子間に電流が流れなくなり、第 1 制御ノード N G の電圧の上昇が止まる。具体的には、第 1 制御ノード N G の電圧は、ハイレベル電源電圧 E L V D D と駆動トランジスタ M 4 の閾値電圧 V t hとの和に等しくなるまで上昇する。以上のようにして、期間 P 1 3 には、データ信号 D ( m ) に応じて保持キャパシタ C 2 が充電される。

### 【 0 0 8 1 】

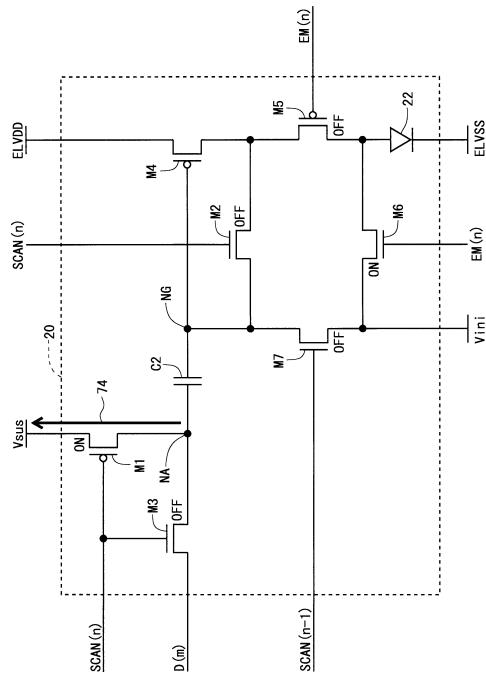

期間 P 1 4 になると、走査信号 S C A N ( n ) がハイレベルからローレベルに変化する。これにより、閾値電圧補償トランジスタ M 2 および書き込み制御トランジスタ M 3 がオフ状態となり、第 1 初期化トランジスタ M 1 がオン状態となる。書き込み制御トランジスタ M 3 がオフ状態かつ第 1 初期化トランジスタ M 1 がオン状態となることによって、図 2 6 で符号 7 4 を付した矢印で示すように、第 2 制御ノード N A から基準電源線へと電流が流れれる。これにより、第 2 制御ノード N A の電圧は、基準電圧 V s u s に等しくなるまで低下する。このとき、保持キャパシタ C 2 の存在に起因して、第 1 制御ノード N G の電圧も低下する。

### 【 0 0 8 2 】

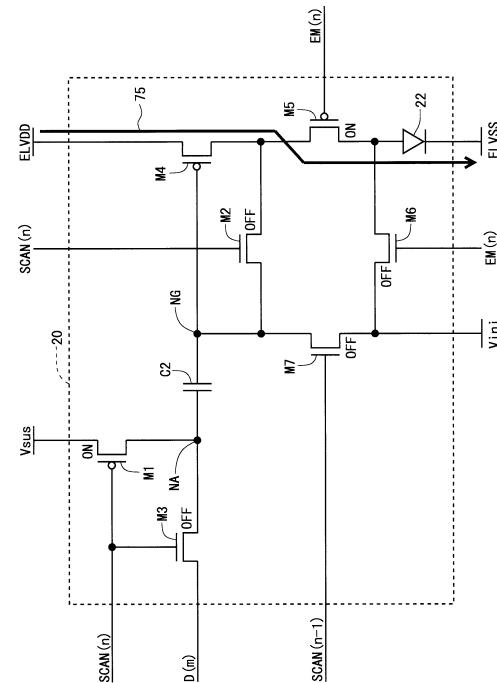

期間 P 1 5 になると、発光制御信号 E M ( n ) がハイレベルからローレベルに変化する。これにより、第 2 発光制御トランジスタ M 6 がオフ状態となり、第 1 発光制御トランジスタ M 5 がオン状態となる。その結果、駆動トランジスタ M 4 の制御端子 - 第 2 導通端子間の電圧の大きさに応じて、図 2 7 で符号 7 5 を付した矢印で示すように駆動電流が有機 E L 素子 2 2 に供給される。これにより、有機 E L 素子 2 2 は駆動電流の大きさに応じて発光する。

### 【 0 0 8 3 】

その後、発光制御信号 E M ( n ) がハイレベルからローレベルに変化するまでの期間を通じて、駆動電流の大きさに応じて有機 E L 素子 2 2 が発光する状態が継続される。

### 【 0 0 8 4 】

#### < 2 . 4 効果 >

本実施形態によれば、画素回路 2 0 の構成に関し、書き込み制御トランジスタ M 3 を介してデータ信号線 D に接続された第 2 制御ノード N A と駆動トランジスタ M 4 の制御端子に接続された第 1 制御ノード N G との間に保持キャパシタ C 2 が設けられている。このような構成により、保持キャパシタ C 2 の充電は駆動トランジスタ M 4 を介さずに行われる。すなわち、保持キャパシタ C 2 の充電は速やかに行われる。また、データ信号 D の電圧は閾値電圧補償トランジスタ M 2 がオン状態からオフ状態に変化する時点までに確定していれば良いので、データ信号 D の波形変化に大きな遅延が生じない限り表示品位は低下しない。さらに、駆動トランジスタ M 4 には L T P S - T F T が採用されているので、駆動

トランジスタM 4 の閾値電圧を補償するための補償処理が行われる期間P 1 3 ( 図 2 2 参照 ) に第1制御ノードN G の充電が速やかに行われる。以上より、例えば駆動周波数を1 2 0 H z とするような高周波駆動 ( 高速駆動 ) が行われても、良好な表示品位が維持される。また、第1制御ノードN G に導通端子が接続されたトランジスタ ( 詳しくは、第1制御ノードN G に第1導通端子が接続された閾値電圧補償トランジスタM 2 および第1制御ノードN G に第1導通端子が接続された第2初期化トランジスタM 7 ) には、酸化物T F T が採用されている。それ故、それらのトランジスタでのリーク電流の発生が防止される。従って、例えば駆動周波数を1 H z とするような低周波駆動 ( 低速駆動 ) が行われても、リーク電流に起因して表示品位が低下することはない。すなわち、良好な表示品位が維持される。以上より、本実施形態によれば、第1の実施形態と同様、表示品位の低下を引き起こすことなく高周波駆動および低周波駆動の双方を可能ならしめる画素回路2 0 を備えた有機E L 表示装置が実現される。

#### 【 0 0 8 5 】

また、第1初期化トランジスタM 1 にpチャネル型のトランジスタを採用し、かつ、閾値電圧補償トランジスタM 2 および書き込み制御トランジスタM 3 にnチャネル型のトランジスタを採用することによって、それらトランジスタM 1 ~ M 3 の動作を1本の制御線 ( 走査信号線S C A N ) で制御することが可能となっている。それ故、高精細化が可能となる。

#### 【 0 0 8 6 】

< 3 . その他 >

上記においては有機E L 表示装置を例に挙げて説明したが、これには限定されず、無機E L 表示装置、Q L E D 表示装置などにも本発明を適用することができる。

#### 【 符号の説明 】

#### 【 0 0 8 7 】

6 ... 有機E L パネル

2 0 ... 画素回路

2 1 , 2 2 ... 有機E L 素子

2 0 0 ... 表示部

3 0 0 ... ソースドライバ ( データ信号線駆動回路 )

4 0 0 ... ゲートドライバ ( 走査信号線駆動回路 )

5 0 0 ... エミッションドライバ ( 発光制御線駆動回路 )

D ( 1 ) ~ D ( i ) ... データ信号線、データ信号

E M ( 1 ) ~ E M ( j ) ... 発光制御線、発光制御信号

E M B ( 1 ) ~ E M B ( j ) ... リセット制御線、リセット制御信号

S C A N ( 0 ) ~ S C A N ( j ) ... 走査信号線、走査信号

N G ... 第1制御ノード

N A ... 第2制御ノード

C 1 , C 2 ... 保持キャパシタ

T 1 , M 1 ... 第1初期化トランジスタ

T 2 , M 2 ... 閾値電圧補償トランジスタ

T 3 , M 3 ... 書き込み制御トランジスタ

T 4 , M 4 ... 駆動トランジスタ

T 5 , M 5 ... 第1発光制御トランジスタ

T 6 , M 6 ... 第2発光制御トランジスタ

T 7 , M 7 ... 第2初期化トランジスタ

10

20

30

40

50

【図面】

【図 1】

【図 2】

10

20

【図 3】

【図 4】

|    | P1  | P2  | P3  | P4  | P5  |

|----|-----|-----|-----|-----|-----|

| T1 | OFF | ON  | OFF | OFF | OFF |

| T2 | OFF | OFF | ON  | OFF | OFF |

| T3 | OFF | OFF | ON  | OFF | OFF |

| T5 | OFF | OFF | OFF | OFF | ON  |

| T6 | OFF | OFF | OFF | OFF | ON  |

| T7 | OFF | OFF | ON  | OFF | OFF |

30

40

50

【図 5】

【図 6】

10

20

【図 7】

【図 8】

30

40

50

【図 9】

【図 10】

10

20

【図 11】

【図 12】

30

40

50

【図 1 3】

【図 1 4】

|    | P1  | P2  | P3  | P4  | P5  |

|----|-----|-----|-----|-----|-----|

| T1 | OFF | ON  | OFF | OFF | OFF |

| T2 | OFF | OFF | ON  | OFF | OFF |

| T3 | OFF | OFF | ON  | OFF | OFF |

| T5 | OFF | OFF | OFF | OFF | ON  |

| T6 | OFF | OFF | OFF | OFF | ON  |

| T7 | ON  | ON  | ON  | ON  | OFF |

10

【図 1 5】

【図 1 6】

20

30

40

50

【図 17】

【図 18】

10

20

【図 19】

【図 20】

30

40

50

【図 2 1】

【図 2 2】

10

20

【図 2 3】

|    | P11 | P12 | P13 | P14 | P15 |

|----|-----|-----|-----|-----|-----|

| M1 | ON  | ON  | OFF | ON  | ON  |

| M2 | OFF | OFF | ON  | OFF | OFF |

| M3 | OFF | OFF | ON  | OFF | OFF |

| M5 | OFF | OFF | OFF | OFF | ON  |

| M6 | ON  | ON  | ON  | ON  | OFF |

| M7 | OFF | ON  | OFF | OFF | OFF |

【図 2 4】

30

40

50

【図 2 5】

【図 2 6】

10

20

【図 2 7】

【図 2 8】

30

40

50

【図 2 9】

10

20

30

40

50

---

フロントページの続き

## (51)国際特許分類

| F I                            |

|--------------------------------|

| G 0 9 G      3/20      6 1 1 F |

| G 0 9 G      3/20      6 2 1 M |

| G 0 9 G      3/20      6 8 0 G |

| G 0 9 G      3/20      6 2 1 A |

| G 0 9 G      3/20      6 2 2 D |

| H 1 0 K      59/123            |

| H 1 0 K      59/131            |

## (56)参考文献

中国特許出願公開第 1 0 7 6 8 0 5 3 3 ( C N , A )

特表 2 0 2 0 - 5 0 9 4 1 9 ( J P , A )

特表 2 0 1 6 - 5 3 4 3 9 0 ( J P , A )

米国特許出願公開第 2 0 1 9 / 0 0 4 3 4 2 6 ( U S , A 1 )

特開 2 0 0 5 - 1 6 4 8 9 1 ( J P , A )

特開 2 0 1 6 - 1 6 7 0 4 5 ( J P , A )

特開 2 0 1 9 - 0 6 6 8 4 7 ( J P , A )

特開 2 0 1 2 - 1 3 3 2 0 7 ( J P , A )

特開 2 0 1 4 - 2 2 8 7 4 4 ( J P , A )

## (58)調査した分野

(Int.Cl. , DB名)

G 0 9 G      3 / 3 2 3 3

G 0 9 G      3 / 2 0

H 1 0 K      5 9 / 1 2 3

H 1 0 K      5 9 / 1 3 1