# (12) UK Patent Application (19) GB (11) 2 251 773(13)A

(43) Date of A publication 15.07.1992

- (21) Application No 9100361.6

- (22) Date of filing 09.01.1991

- (71) Applicant

Du Pont Pixel Systems Limited

(Incorporated in the United Kingdom)

Wedgewood Way, Stevenage, Hertfordshire, SG1 4QN, United Kingdom

- (72) Inventor John Walter Neave

- (74) Agent and/or Address for Service D Young & Co 10 Staple Inn, London, WC1V 7RD, United Kingdom

- (51) INT CL<sup>5</sup> G06F 15/72

- (52) UK CL (Edition K) **H4T TBBX**

- (56) Documents cited US 4873515 A

- (58) Field of search UK CL (Edition K) H4T TBBA TBBD TBBG TBBN **TBBX** INT CL<sup>5</sup> G06F On-line databases: WPI, INSPEC.

#### (54) Graphics accelerator using parallel processed pixel patch to render line

(57) A graphics accelerator system which provides improved image rendering speed. In computers using sophisticated image systems, the processor must be able to refer to graphical objects (such as lines, polygons, etc.) in the image space. At some point, these graphical objects must be translated into a specification which can be used by a display driver (i.e. a set of pixel values). This necessary translation step is called "rendering," and presents a key performance bottleneck in sophisticated graphics systems.

One key bottleneck in rendering is the memory bandwidth from the pixel processor into the display memory. To improve this bandwidth, the pixel processor will access multiple contiguous pixels at a time, and process them in parallel. Such a group of pixels is referred to as a "patch". By providing a pixel processor with parallel patch access to the memory subsystem, higher rendering rates can be obtained. The disclosed innovations provide improved techniques for rendering lines into a patch accessed memory subsystem.

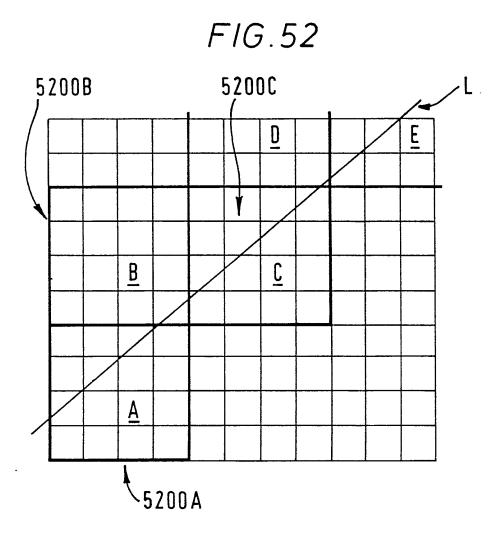

A method somewhat like Bresenham's algorithm is used to access the appropriate patches for manipulation. Within each accessed patch, the appropriate linear equation is solved to select the appropriate pixels. Thus, a line is first mapped onto an appropriate patch of pixels, and then mapped onto the appropriate pixel.

The patches used are defined, within the overall geometry of the image, to have aligned corners. That is, within the geometry of the image space, the patches make up an aligned rectangular grid, so that any two adjacent patches are aligned horizontally or aligned vertically. Each stage of patch-to-patch stepping consists of one vertical step or one horizontal step: diagonal movement is forbidden. With page mode memory access, this reduces access times.

#CA.

Ĉ.

FIG. 10A

FIG. 10 B

FIG.11B V RAM MEMORY SPACE PAGE 12,12 12 PAGE D 6,10 PAGE B 4,8 8 8 12 4

FIG.11C

## PAGE SELECTION

|                                                                                        | IF 4px+mx<125<br>& 4py+my<125 | IF 4px+mx>124<br>& 4py+my<125 | IF 4px+mx<125<br>& 4py+my>124 | IF 4px+mx>124<br>& 4py+my>124 |

|----------------------------------------------------------------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|

| IF bx≥mx<br>& by≥my                                                                    | Α                             | А                             | A                             | А                             |

| IF bx <mx<br>&amp; by≥my</mx<br>                                                       | А                             | В                             | A                             | В                             |

| IF bx≥mx<br>& by <my< td=""><td>А</td><td>A</td><td>С</td><td>С</td></my<>             | А                             | A                             | С                             | С                             |

| IF bx <mx<br>&amp; by<my< td=""><td>A</td><td>В</td><td>С</td><td>D</td></my<></mx<br> | A                             | В                             | С                             | D                             |

FIG. 12

## PATCH ADDRESS INCREMENT SELECTION

## X ADDRESS

| CONDITION                                     | PATCH X ADDRESS |  |  |  |

|-----------------------------------------------|-----------------|--|--|--|

| bx≥mx                                         | px              |  |  |  |

| bx <mx< td=""><td colspan="3">px+1</td></mx<> | px+1            |  |  |  |

## Y ADDRESS

| CONDITION                         | PATCH Y ADDRESS |  |  |  |  |

|-----------------------------------|-----------------|--|--|--|--|

| by≥my                             | ру              |  |  |  |  |

| by <my< td=""><td>py+1</td></my<> | py+1            |  |  |  |  |

FIG. 13

FIG. 14

FIG. 16

| D"(12) | D"(13) | D"(14) | D"(15) |

|--------|--------|--------|--------|

| D"(8)  | D"(9)  | D"(10) | D"(11) |

| D"(4)  | D"(5)  | D"(6)  | D"(7)  |

| D"(0)  | D"(1)  | D"(2)  | D"(3)  |

| D"(14) | D"(15) | D"(12) | D"(13) |

|--------|--------|--------|--------|

| D"(10) | D"(11) | D"(8)  | D"(9)  |

| D"(6)  | D"(7)  | D"(4)  | D"(5)  |

| D"(2)  | D"(3)  | D"(0)  | D"(1)  |

| D(12) | D(13) | D(14) | D(15) |

|-------|-------|-------|-------|

| D(8)  | D(9)  | D(10) | D(11) |

| D(4)  | D(5)  | D(6)  | D(7)  |

| D(0)  | D(1)  | D(2)  | D(3)  |

| equal | to |

|-------|----|

| _     |    |

FIG. 19

| D"(2)  | D"(3)  | D"(0)  | D"(1)  |  |  |  |  |  |  |

|--------|--------|--------|--------|--|--|--|--|--|--|

| D"(14) | D"(15) | D"(12) | D"(13) |  |  |  |  |  |  |

| D"(10) | D"(11) | D"(8)  | D"(9)  |  |  |  |  |  |  |

| D"(6)  | (7)"ם  | D"(4)  | D"(5)  |  |  |  |  |  |  |

FIG. 20

|                         | ,              | 660ر      | و        | 662 | گے         | 664      | گے       | 666      | (        | 68        | اس (     | 670      | أسر      | 672       | 9          | 574      |

|-------------------------|----------------|-----------|----------|-----|------------|----------|----------|----------|----------|-----------|----------|----------|----------|-----------|------------|----------|

| i                       | xi<br>hex      | yi<br>hex | In<br>US |     | q=<br>US   | =0<br>XW | q:<br>US | =2<br>XW | q=<br>US | :10<br>XW | q:<br>US | =3<br>XW | q=<br>US | :11<br>XW | q:<br>US   | =8<br>XW |

| 0                       | 1234           | 1234      | 1        | 0   | 0          | 0        | 0        | 0        | 0        | 0         | 0        | 0        | 0        | 0         | 0          | 0        |

|                         | 1234           | 1234      | 1        | 0   | 0          | 0        | 0        | 0        | 0        | 0         | 0        | 0        | 0        | 0         | 0          | 0        |

| 2                       | 1235           | 1234      | 1        | 0   | 1          | 1        | 0        | 0        | 0        | 0         | 0        | 0        | 0        | 0         | 0          | 0        |

| 3                       | 1235           | 1235      | 1        | 0   | 1          | 0        | 1        | 0        | 1        | 0         | 0        | 0        | 0        | 0         | 0          | 0        |

| 4                       | -              | -         | 0        | 0   | 0          | 0        | 0        | 0        | 0        | 0         | 0        | 0        | 0        | 0         | 0          | 0        |

| 5                       | -              | -         | 0        | 0   | 0          | 0        | 0        | 0        | 0        | 0         | 0        | 0        | 0        | 0         | 0          | 0        |

| 6                       | -              | -         | 0        | 0   | 0          | 0        | 0        | 0        | 0        | 0         | 0        | 0        | 0        | 0         | 0          | 0        |

| 7                       | _              | -         | 0        | 0   | 0          | 0        | 0        | 0        | 0        | 0         | 0        | 0        | 0        | 0         | 0          | 0        |

| 8                       | 1234           | 1236      | 1        | 0   | 1          | 0        | 1        | 0        | 1        | 0         | 1        | 0        | 1        | 0         | 0          | 0        |

| 9                       | 1234           | 1236      | 1        | 0   | 1          | 0        | 1        | 0        | 1        | 0         | 1        | 0        | 1        | 0         | 0          | 0        |

| 10                      | 1236           | 1234      | 1        | 0   | 1          | 1        | 1        | 1        | 0        | 0         | 0        | 0        | 0        | 0         | 0          | 0        |

| $\overline{\mathbf{u}}$ | 1236           | 1235      | 1        | 0   | 1          | 0        | 1        | 0        | 1        | 0         | 1        | 1        | 0        | 0         | 0          | 0        |

| 12                      | _              | -         | 0        | 0   | 0          | 0        | 0        | 0        | 0        | 0         | 0        | 0        | 0        | 0         | 0          | 0        |

| 13                      | -              | -         | 0        | 0   | 0          | 0        | 0        | 0        | 0        | 0         | 0        | 0        | 0        | 0         | 0          | 0        |

| 14                      | _              | -         | 0        | 0   | 0          | 0        | 0        | 0        | 0        | 0         | 0        | 0        | 0        | 0         | 0          | 0        |

| © 一                     | -              |           | 0        | 0   | 0          | 0        | 0        | 0        | 0        | 0         | 0        | 0        | 0        | 0         | 0          | 0        |

| ADD                     | ADDRESSES READ |           | AD.      |     | x0,<br>x1, | - 1      | x2,      | y2       | x10,     | y10       | х3,      | у3       | x11,     | y11       | x8,<br>x9, | - 1      |

FIG. 24

ć

FIG. 27

| 32-bit                                                                                                            | 16-bit                                                                               | 8-bit                                        | PATCH     |

|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------|-----------|

| L ignored                                                                                                         | L=0 or 1                                                                             | 0≤L≤3                                        | X ADDRESS |

| bx≥mx                                                                                                             | L=0 OR                                                                               | L<>3 OR                                      | xq        |

|                                                                                                                   | bx≥mx                                                                                | bx≥mx                                        |           |

| bx <mx< td=""><td>L=1 AND<br/>bx<mx< td=""><td>L=3 AND<br/>bx<mx< td=""><td>px+1</td></mx<></td></mx<></td></mx<> | L=1 AND<br>bx <mx< td=""><td>L=3 AND<br/>bx<mx< td=""><td>px+1</td></mx<></td></mx<> | L=3 AND<br>bx <mx< td=""><td>px+1</td></mx<> | px+1      |

<u>FIG. 30C</u>

## VIRTUAL ADDRESS BITS

| MODE   | 8      | 7      | 6      | 5     | 4     | 3   | 2     |

|--------|--------|--------|--------|-------|-------|-----|-------|

| 32-bit | PAGE   | PX (2) |        | patch | рх    | (5) |       |

| 16-bit | PX (1) |        |        |       | L (1) |     |       |

| 8-bit  |        |        | px (5) |       |       |     | L (2) |

FIG. 31

FIG. 32

GENERAL ZSFT TABLE

|           |        |        | MODE   | 16-bit |        | 32-bit |        |

|-----------|--------|--------|--------|--------|--------|--------|--------|

|           | IF L=0 | IF L=1 | IF L=2 | 1F L=3 | IF L=0 | IF L=1 | }      |

| IF mx+x<4 | 0      | 1      | 2      | 3      | 0      | 2      | ALWAYS |

| IF mx+x>3 | 1      | 2      | 3      | 0      | 2      | 0      | 0      |

FIG. 35A

ZSFT TABLE 818b (x=1)

ZSFT (1), (5), (9), (13)

| L  | 8-bit MODE |   |   | 16-bit MODE |   | 32-bit |        |

|----|------------|---|---|-------------|---|--------|--------|

| mx | 0          | 1 | 2 | 3           | 0 | 1      |        |

| 0  | 0          | 1 | 2 | 3           | 0 | 2      |        |

| 1  | 0          | 1 | 2 | 3           | 0 | 2      | ALWAYS |

| 2  | 0          | 1 | 2 | 3           | 0 | 2      | 0      |

| 3  | 1          | 2 | 3 | 0           | 2 | 0      | 1      |

FIG. 35B

| 32-bit<br>L=0   | 16-bit<br>L=0 or 1 | 8-bit<br>0≤L≤3 |        |

|-----------------|--------------------|----------------|--------|

| 4px+(4L)+mx<125 | 8px+4L+mx<253      | 16px+4L+mx<509 | NPEx=0 |

| 4px+(4L)+mx>124 | 8px+4L+mx>252      | 16px+4L+mx>508 | NPEx=1 |

| 4py+my<125      | 4py+my<125         | 4py+my<125     | NPEy=0 |

| 4py+my>124      | 4py+my>124         | 4py+my>124     | NPEy=1 |

FIG. 36 B

FIG. 37

GENERAL PWE TABLE

|                                                                                                                | IF L=0 |      | MODE<br>IF L=2 | IF L=3 | 16-bit<br>IF L=0 | MODE<br>IF L=1 | 32-bit |

|----------------------------------------------------------------------------------------------------------------|--------|------|----------------|--------|------------------|----------------|--------|

| IF bx≥mx                                                                                                       |        | 0010 | 0100           | 1000   | 0011             | 1100           | ALWAYS |

| IF bx <mx< td=""><td></td><td>0100</td><td>1000</td><td>0001</td><td>1100</td><td>0011</td><td>1111</td></mx<> |        | 0100 | 1000           | 0001   | 1100             | 0011           | 1111   |

FIG. 38

PWE TABLE (bx=2)

| L  | 8-bit MODE |      |      | 16-bit | 32-bit |      |           |

|----|------------|------|------|--------|--------|------|-----------|

| mx | 0          | 1    | 2    | 3      | 0      | 1    |           |

| 0  | 0001       | 0010 | 0100 | 1000   | 0011   | 1100 |           |

| 1  | 0001       | 0010 | 0100 | 1000   | 0011   | 1100 | ALWAYS    |

| 2  | 0001       | 0010 | 0100 | 1000   | 0011   | 1100 | 1111      |

| 3  | 0010       | 0100 | 1000 | 0001   | 1100   | 0011 | ` ' ' ' ' |

FIG. 39

FIG. 40

FIG. 42

FIG. 43

|                                              | AFTER<br>COPY<br>FROM<br>PAGING<br>MEMORY                                                   | 1ST<br>COPY<br>TO<br>MON | AFTER<br>1ST<br>COPY<br>TO<br>MON | 1ST<br>REND        | AFTER<br>FIRST<br>RENDER                                                                    | 2ND<br>COPY<br>TO<br>MON | AFTER 2ND COPY TO MON           |

|----------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------|-----------------------------------|--------------------|---------------------------------------------------------------------------------------------|--------------------------|---------------------------------|

| 2047<br>: '<br>403 (S)<br>402 (R)<br>401 (Q) | :<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>: | :<br>:<br>Y<br>Y         | :<br>:<br>00000000<br>00000000    | :<br>:<br>N<br>N   | :<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>: | N                        | :<br>:<br>00000000<br>0000000   |

| 400 (P)<br>:<br>0                            | 00001100<br>00001100                                                                        | Y<br>::                  | 00000000<br>00000000<br>:         | Y<br>N<br>/:<br>/: | 10001000<br>000000000<br>:                                                                  | Y<br>N<br>:              | 10000000<br>000000000<br>:<br>: |

| dsB — dro                                    |                                                                                             | drD<br>drC<br>drB<br>drA | -Y=Yes<br>N=No/<br>)<br>904       | /                  | 906                                                                                         |                          | 908                             |

|         | 2ND<br>REND | AFTER<br>SECOND<br>RENDER | 3RD<br>COPY<br>TO<br>MON | AFTER<br>3RD<br>COPY<br>TO<br>MON | 3RD<br>REND | AFTER<br>THIRD<br>RENDER | 4TH<br>COPY<br>TO<br>MON | AFTER 4TH COPY TO MON | COPY<br>BACK<br>TO<br>PAGING<br>MEMORY | AFTER<br>COPY<br>BACK                            |

|---------|-------------|---------------------------|--------------------------|-----------------------------------|-------------|--------------------------|--------------------------|-----------------------|----------------------------------------|--------------------------------------------------|

| 2047    | :           | . :                       | :                        | :                                 |             | •                        |                          |                       |                                        |                                                  |

| :       | :           | :                         | :                        |                                   |             |                          |                          |                       |                                        | :                                                |

| 403 (S) | N           | 00000000                  | N                        | 00000000                          | Y           | 10001000                 | Y                        | 10000000              | Ÿ                                      | 00000000                                         |

| 402 (R) | N           | 00000000                  | N                        | 00000000                          | N           | 00000000                 | N                        | 00000000              | N                                      | 00000000                                         |

| 401 (Q) | М¬          | 10000000                  | Y                        | 10000000                          | Y           | 10001000                 | Υ                        | 10000000              | Y                                      | 00000000                                         |

| 400 (P) | Y           | 11001100                  | Y                        | 11000000                          | N           | 11000000                 | N                        | 11000000              | Y                                      | 00000000                                         |

| :       |             | :                         | :                        | :                                 | :           | :                        | :                        | :                     |                                        |                                                  |

| 0       | :           | :                         |                          | :                                 | :           | :                        | :                        | :                     | :                                      |                                                  |

|         |             | 7                         |                          | 7                                 |             | 7                        |                          | <del></del>           |                                        | <del>-                                    </del> |

|         | M=          | 910                       |                          | 912                               |             | 914                      |                          | 916                   |                                        | 918                                              |

|         | His-        |                           |                          |                                   |             |                          |                          |                       |                                        |                                                  |

|         | ali-        |                           |                          |                                   |             |                          |                          |                       |                                        |                                                  |

|         | all-        |                           |                          |                                   |             |                          |                          |                       |                                        |                                                  |

FIG. 44

FIG. 45A

PAGE A AT (PX,PY)

PAGE B AT (PX+1,PY); PAGE B' AT (PX-1,PY)

PAGE C AT (PX,PY+1); PAGE C' AT (PX,PY-1)

PAGE D AT (PX+1,PY+1); PAGE D' AT (PX-1,PY-1)

PAGE E AT (PX+1,PY-1); PAGE E' AT (PX-1,PY+1)

| PAGE | PAGE | PAGE |  |

|------|------|------|--|

| E'   | C    | D    |  |

| PAGE | PAGE | PAGE |  |

| B'   | A    | B    |  |

| PAGE | PAGE | PAGE |  |

| D'   | C'   | E    |  |

FIG. 45D

FIG. 45B

FIG. 45C

FIG. 46

FIG. 48

FIG.50A

FIG. 50B

FIG.50C

FIG.50D

Graphics Accelerator System with Line Drawing and Tracking Operations

Parallelized by Aligned Patches of Pixels

### Cross References to Other Applications

10

15

Reference is made to the following earlier International patent applications, which share some text and drawings in common with the present application, and each of which is incorporated herein by reference as if printed in full below:

Application No. PCT/GB90/01209, filed 3 August 1990, entitled "Data-Array Parallel Processing System";

Application No. PCT/GB90/01210, filed 3 August 1990, entitled "Data-Array Parallel Processing Systems";

Application No. PCT/GB90/01211, filed 3 August 1990, entitled "Data-Array Parallel-Access Memory Systems";

25

Application No. PCT/GB90/01212, filed 3 August 1990, entitled "Data-Array Processing and Memory Systems";

Application No. PCT/GB90/01213, filed 3 August 1990, entitled 30 "Virtual Memory System";

Application No. PCT/GB90/01214, filed 3 August 1990, entitled "Parallel Processing Systems";

Application No. PCT/GB90/01215, filed 3 August 1990, entitled "Data Processing and Memory Systems"; and

Application No. PCT/GB90/01216, filed 3 August 1990, entitled "Data-Array Processing System". Reference is also made to the following concurrent United Kingdom patent applications, which share some text and drawings in common with 5 the present application, and each of which is incorporated herein by reference as if printed in full below: Application No. GB \_\_\_\_\_\_, Agents' reference N568-5, entitled "Graphics Accelerator System with Polygon Traversal Operation 10 Parallelized by Aligned Patches of Pixels" (DPS-107); Application No. GB \_\_\_\_\_\_, Agents' reference N568-6, entitled "Graphics Accelerator System with Highly Parallel Fill Area Set 15 Operations" (DPS-108); Application No. GB ., Agents' reference N568-7, entitled "Graphics Accelerator System with Rapid Computation of Outlines" (DPS-109); 20 Application No. GB \_\_\_\_\_\_, Agents' reference N568-8, entitled "Programmable Computer Graphics System with Parallelized Clipper Operations" (DPS-110); Application No. GB \_\_\_\_\_, Agents' reference N568-9, entitled 25 "Computer Graphics System with Synchronization to a Band of Lines in the Display Scan" (DPS-111); and

Application No. GB \_\_\_\_\_\_, Agents' reference N568-10, entitled

"Graphics Accelerator System with Line Drawing and Tracking Operations

Parallelized by Adaptively Shifted Pixel Patches (DPS-112)".

30

10

15

20

25

30

### **BACKGROUND AND SUMMARY OF THE INVENTION**

The present invention relates to computer systems with highperformance graphics capabilities, and to subassemblies and methods for use in such systems.

Modern computer systems tend to manipulate graphical objects as high-level entities. For example, a circle may be described simply as having a certain radius and a certain center point, or a straight line segment may be described by listing its two endpoints. Such high-level descriptions are a necessary basis for high-level geometric manipulations, and also have the advantage of providing a compact format which does not consume memory space unnecessarily.

By contrast, when an image containing graphical objects is to be displayed, a very low-level description is needed. For example, in a conventional CRT display, a "flying spot" is moved across the screen (one line at a time), and the electron beams are switched on or off (or to a desired level in between) as the flying spot passes each pixel. For example, suppose that an image is to be displayed on a NEC 5D<sup>TM</sup> monitor. This particular monitor has a specified resolution of 1280×1024 pixels. (That is, the screen has 1024 scan lines; and, across the width of the screen, there are 1280 locations which can all have different displayed colors.) Thus, there are a total of about 1.3 million pixels in this display. If this monitor is to be used for a display of 16 colors, then four bits of information are needed, for each pixel, each time the pixel is addressed. Thus, more than 5 million bits of data are needed to describe one screen on the display.

Other display technologies have similar pixel-by-pixel addressing requirements. Thus, the data format actually used by the display is a pixel-by-pixel description of the pixel attributes (color and/or gray level). At some point, it is necessary to translate the high-level descriptions of graphic objects into a low-level pixel-by-pixel description which can be used by a display driver.

This process is called "rendering" or "drawing" the graphical objects, and imposes a significant computational burden. For example, consider the

10

25

30

simple case of drawing a straight line segment. The high-level description of this object may be merely the locations of the two endpoints  $(x_1, y_1)$  and  $(x_2, y_2)$ . A straightforward way to compute a pixel-by-pixel representation of this line would be:

1) solve for the line's equation y = mx + b;

- 2) and repeatedly, for a series of  $x_i$  starting with  $x_i$ :

- a) calculate  $y_i = mx_i + b$ ,

- b) calculate which available pixel row  $\bar{y}_i$  is vertically closest to  $y_i$ ,

- c) turn on pixel  $(x_i, \tilde{y}_i)$ , and

- d) increment  $x_i$  and repeat, until  $x_2$  is reached.

This simple method is computationally intensive, and requires the use of real-number arithmetic for each pixel. This makes it impracticable for many applications.

The normal method for line-drawing is referred to as "Bresenham's algorithm." See Bresenham, "Algorithm for computer control of digital plotter," 4 *IBM Systems Journal* 25 (1965), which is hereby incorporated by reference. This method uses integer arithmetic to rapidly calculate the individual pixels to be turned on. By carrying an error term, the average slope of the line is followed exactly, without having to perform multiplies at each pixel.

The rendering operation is often performed separately from the main computations, by a separate processor. However, rendering operations can still impose a large computational burden.

The disclosed hardware architecture provides a parallel-processing graphics architecture, with a pixel processing unit which includes multiple subprocessors operating in parallel. These subprocessors are configured for parallel memory access to aligned patches of pixels (*i.e.* to groups of pixels which are aligned in the image space). However, there are substantial difficulties in exploiting such an architecture for rendering. Since the

<sup>&</sup>lt;sup>1</sup>In the presently preferred embodiment, the patches are squares of 4×4 pixels, but of course other patch sizes could be used.

<u>DPS-106</u>

10

15

20

25

computations for each pixel depend on those for an adjacent pixel, it is obviously impossible to perform such computations simultaneously.

5

The data rates required for control of a high-resolution display can be substantial. For example, the NEC 5D<sup>TM</sup> monitor, as sold in the US in 1990, has a refresh rate of 60 Hz. Thus, each of the electron guns (one for each primary color) illuminates each of the 1.3 million pixels 60 times per second. If the color information is only 4 bits per pixel, the net data rate is hundreds of millions of bits per second. For high-resolution displays, this data rate is supplied from a dual-port frame memory, which can be accessed independently by the processor and by the display driver. The processor can access any randomly selected location in the frame memory (to change the pixel-attribute values), and the display driver reads out the pixel data, serially, at high speed, continually as needed.

Thus, if the display is unchanging, no demand is placed on the rendering operations. However, some common operations (such as zooming or rotation) will require every object in the image space to be rerendered. Slow rendering will make the rotation or zoom appear jerky.

The present application discloses a new method for rendering lines in a parallelized graphics-processing architecture. A sequential method, which is somewhat analogous to Bresenham's algorithm, is used to incrementally identify the patches of pixels to be accessed for manipulation, together with a starting and ending error term for each patch. The identified patches are then retrieved, and the pixels of each patch are processed in parallel, using an interpolation calculation to identify the correct pixels to be turned on. This interpolation calculation is more time-consuming than Bresenham's algorithm; but since this calculation is performed by multiple processors in parallel, it does not add unacceptable delay.

# BRIEF DESCRIPTION OF THE DRAWING

6

The present invention will be described with reference to the accompanying drawings, which show important sample embodiments of the invention and which are incorporated in the specification hereof by reference, wherein:

<u>DPS-106</u>

5

10

15

20

25

30

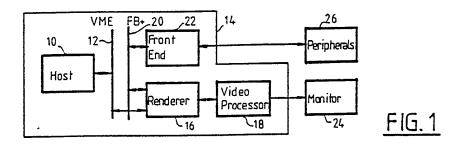

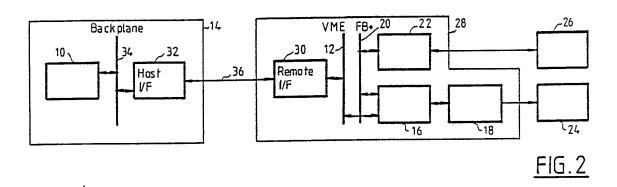

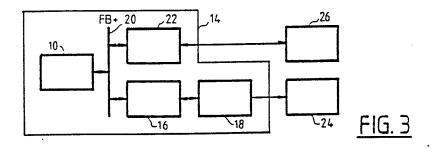

Figure 1 is a high-level schematic illustration of an innovative computer system used in the presently preferred embodiment. Figures 2 and 3 are illustrations of modified forms of the system of Figure 1.

7

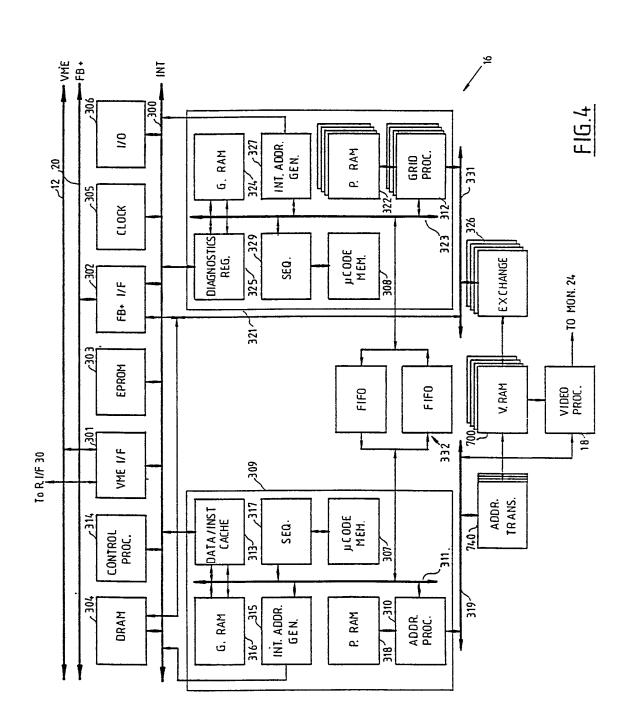

Figure 4 is an illustration in greater detail of a renderer module preferably employed in the systems of Figures 1 to 3.

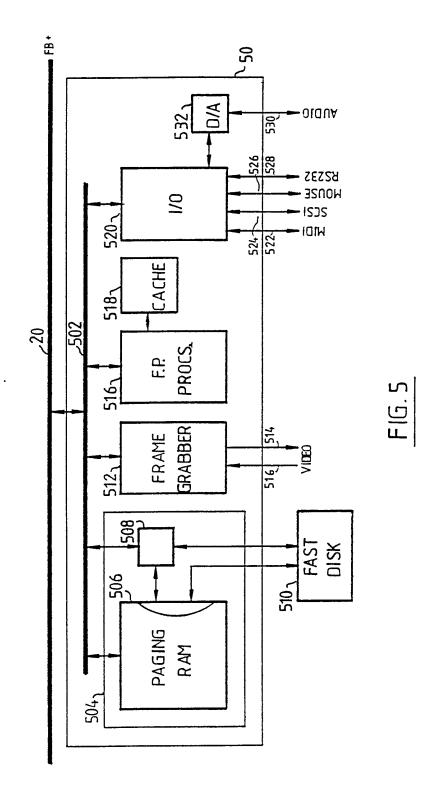

Figure 5 is an illustration, in greater detail, of a front-end processor board preferably employed in the systems of Figures 1 to 3.

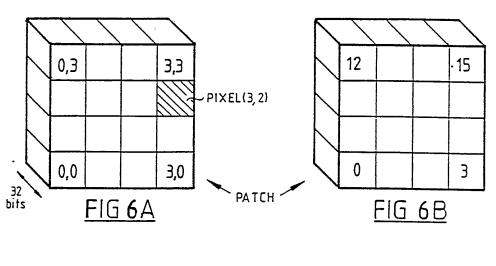

Figure 6A and 6B show how patches of pixel data are made up.

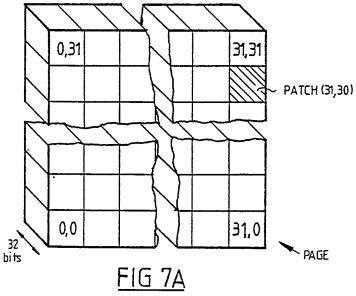

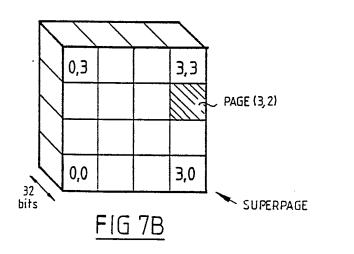

Figures 7A and 7B show how pages of patch data, and groups or "superpages" of page data are made up.

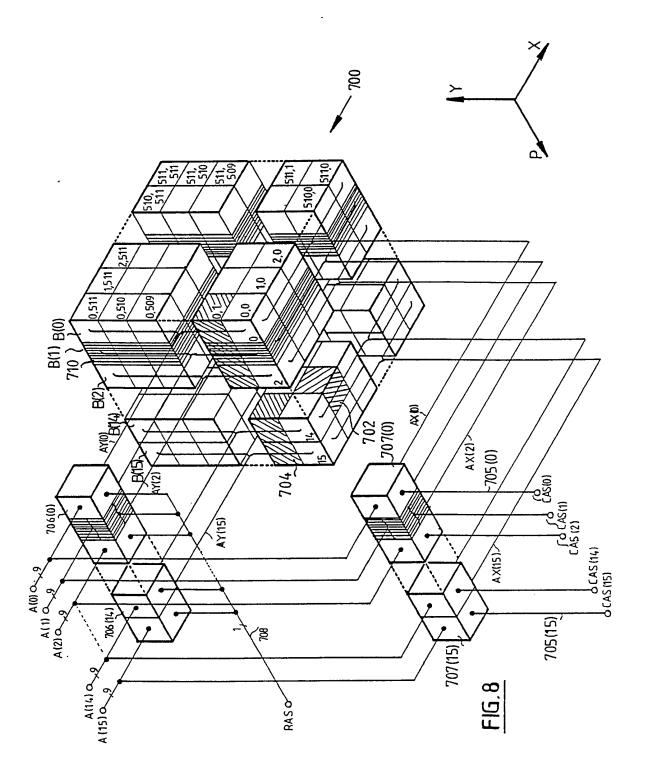

Figure 8 is a schematic illustration of a physical image memory and the address lines therefor, as preferably used in the renderer of Figure 4.

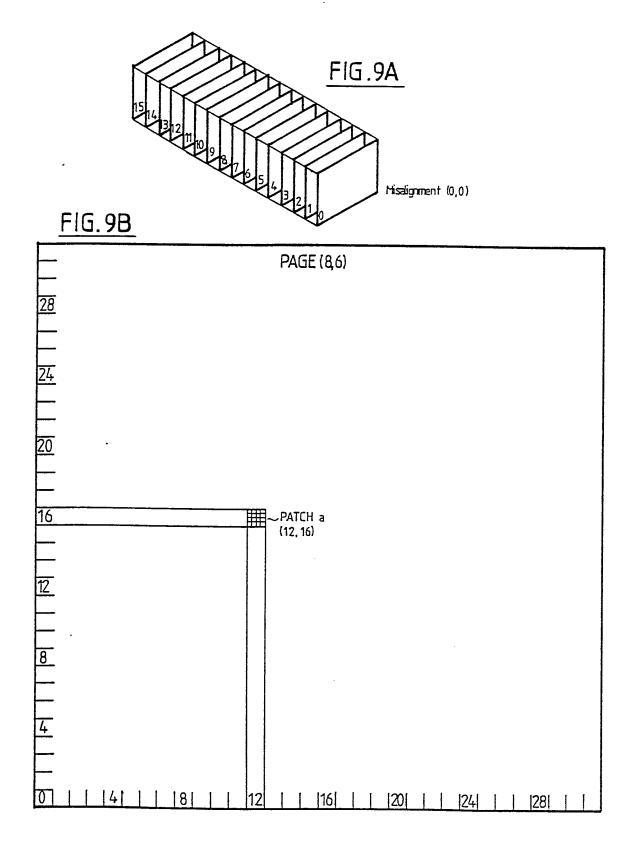

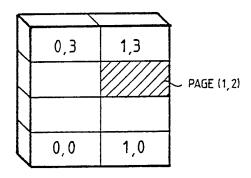

Figure 9A is a 3-D representation of an aligned patch of data within a single page in the image memory, and Figure 9B is a 2-D representation of a page, showing the patch of Figure 9A.

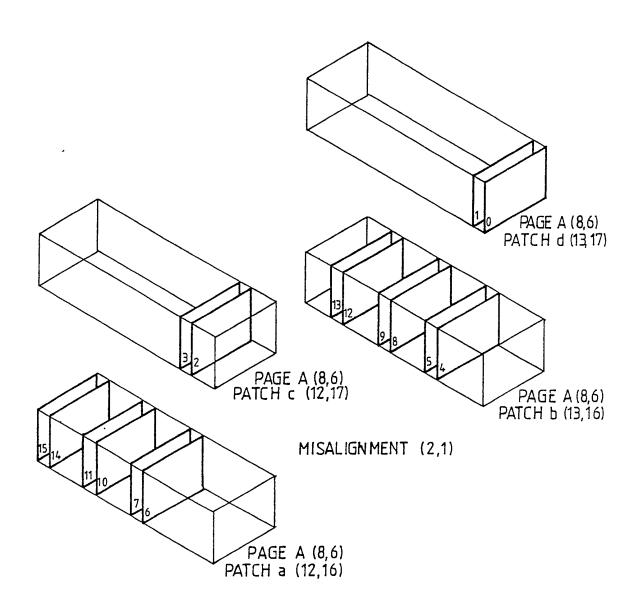

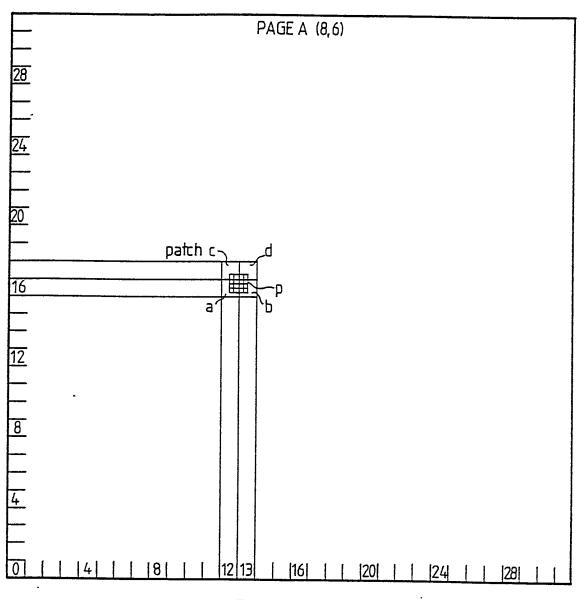

Figure 10A is a 3-D representation of a non-aligned patch of data within a single page in the image memory, and Figure 10B is a 2-D representation of a page, showing the patch of Figure 10A.

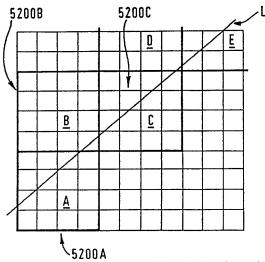

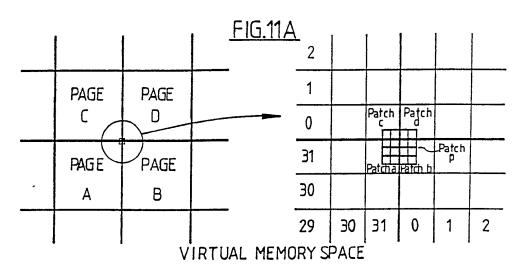

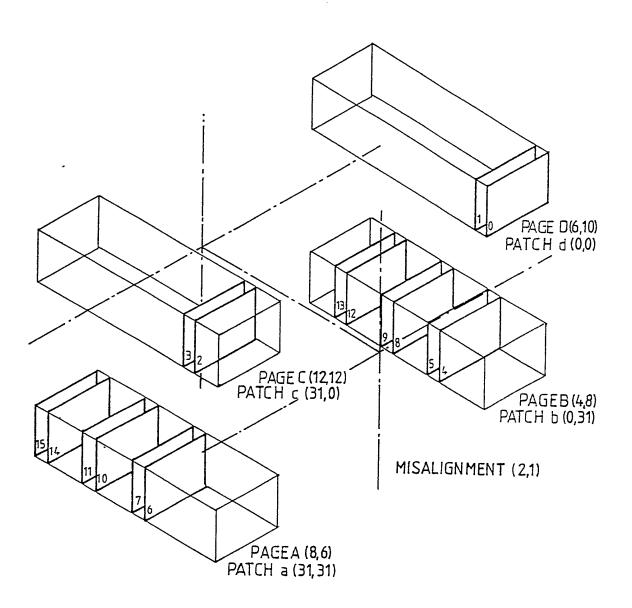

Figure 11A is a 2-D representation of four pages in a virtual memory, showing a non-aligned patch which crosses the page boundaries, and including an enlargement of the circled part of the page boundary intersection. Figure 11B is a 2-D representation of the physical memory, illustrating locations of the four pages shown in Figure 11A. Figure 11C is a 3-D representation of the non-aligned patch of Figure 11A. Figure 12 is a truth table showing how page selection is made for patches which cross page boundaries. Figure 13 shows two truth tables for selecting, respectively, X and Y patch address incrementation.

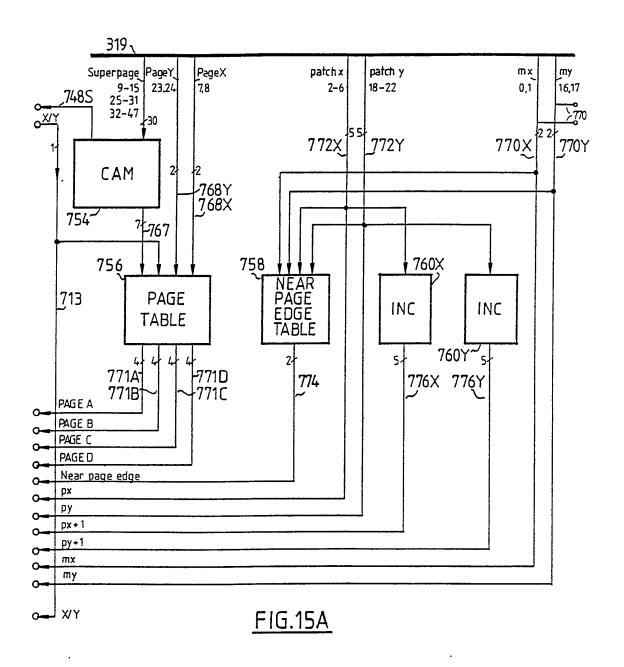

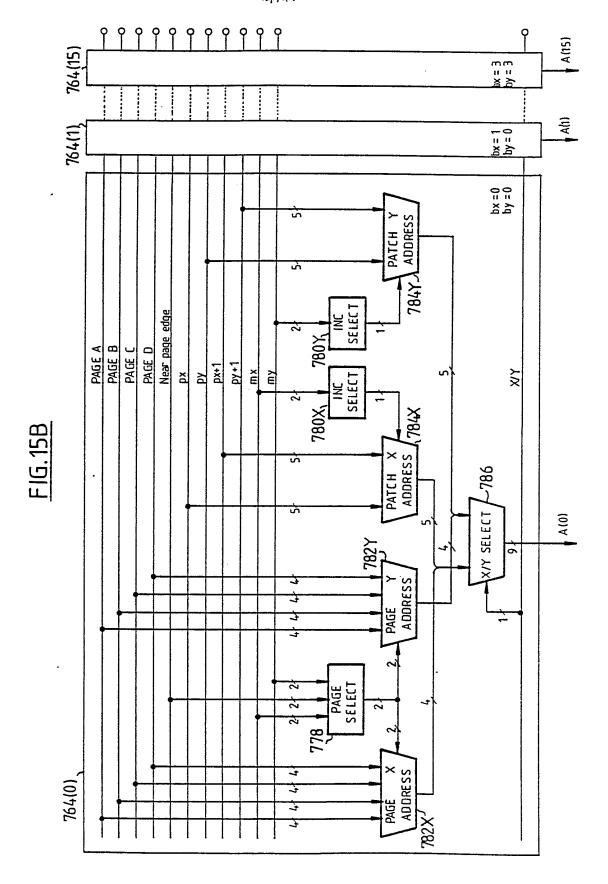

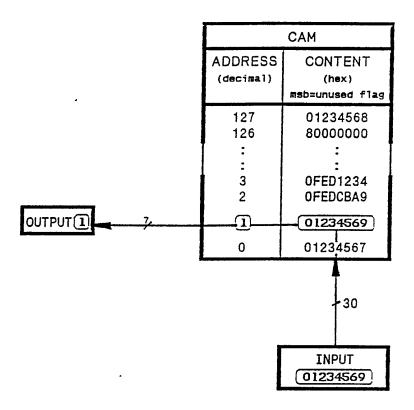

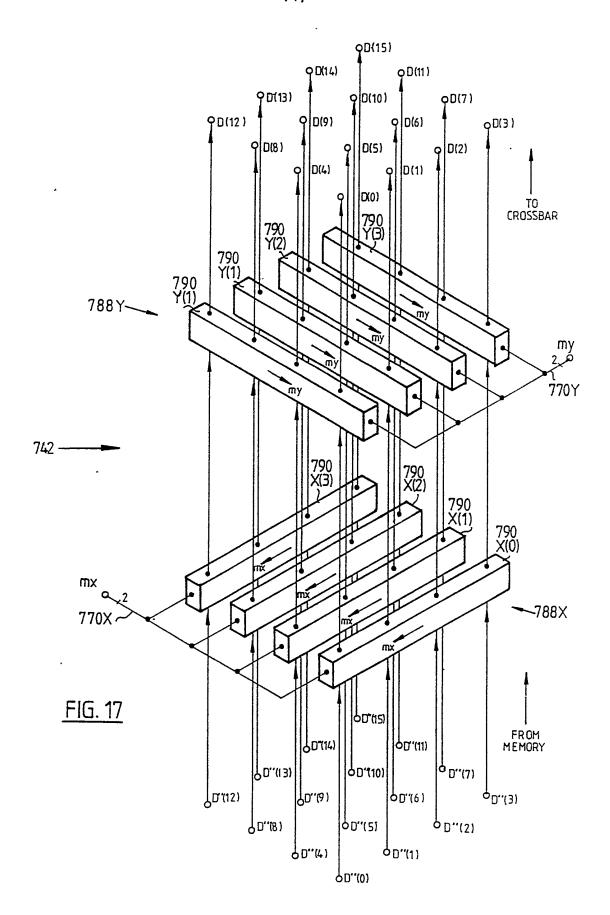

Figure 14 is a schematic illustration in greater detail of part of the renderer of Figure 4, and Figure 15 is a schematic illustration in greater detail of an address translator of Figure 14. Figure 16 is an illustration of the operation of a content-addressable memory used in the address translator of Figure 15. Figure 17 is a schematic illustration in greater detail of a read surface shifter used in the apparatus of Figure 14. Figure

10

15

20

25

30

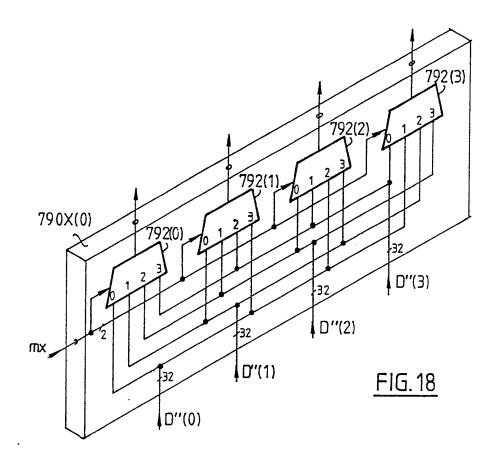

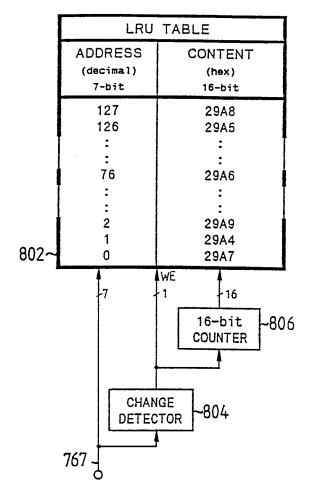

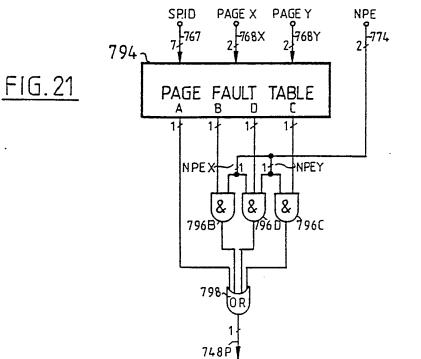

18 shows in greater detail an array of multiplexers forming part of the surface shifter of Figure 17. Figure 19 illustrates the translation made by the surface shifter of Figure 17. Figure 20 is an illustration of the operation a least-recently-used superpage table which may be used with the address translator of Figure 15. Figure 21 is a schematic diagram showing a page fault table which may be used with the address translator of Figure 15.

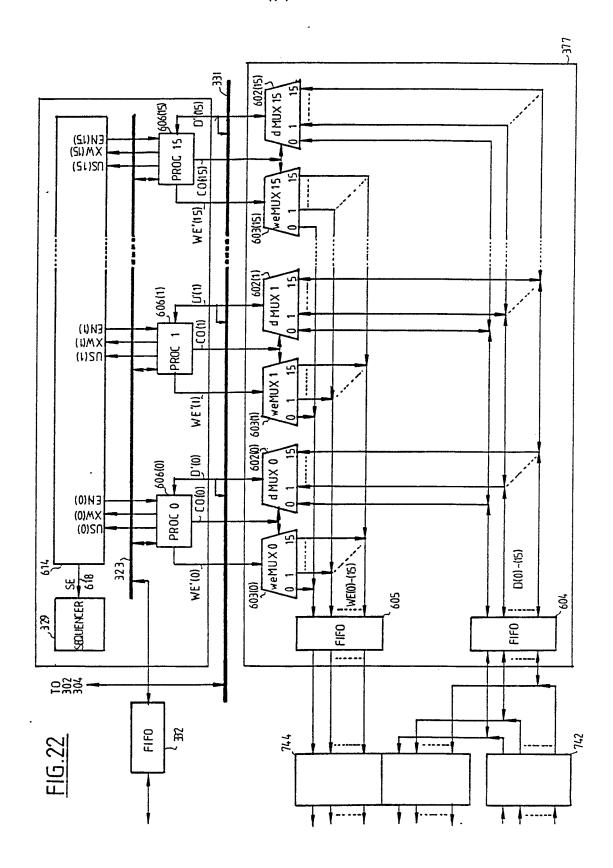

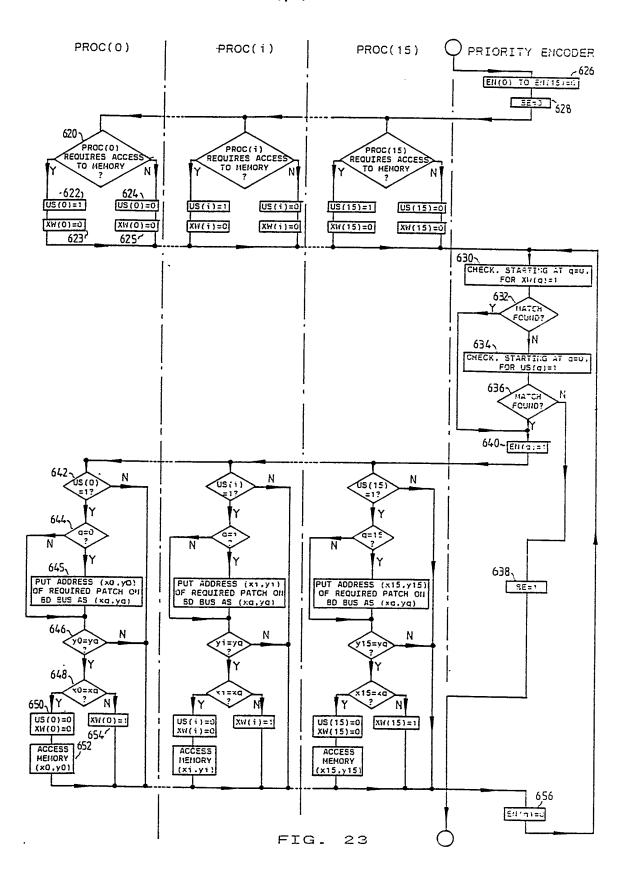

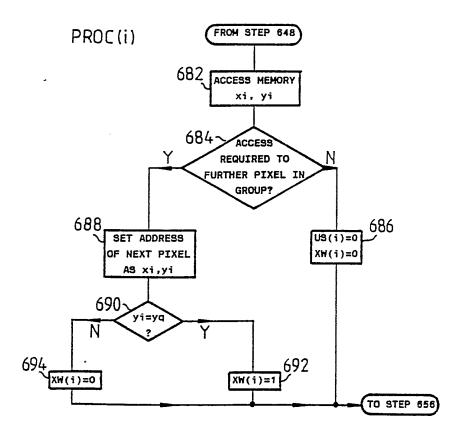

Figure 22 is a schematic diagram of an exchange and grid processor which, in the presently preferred embodiment, is part of the renderer of Figure 4. Figure 23 is a flow diagram illustrating the operation of the processors and a priority encoder of the grid processor of Figure 22. Figure 24 is a table giving an example of the operation of the priority encoder of Figure 22.

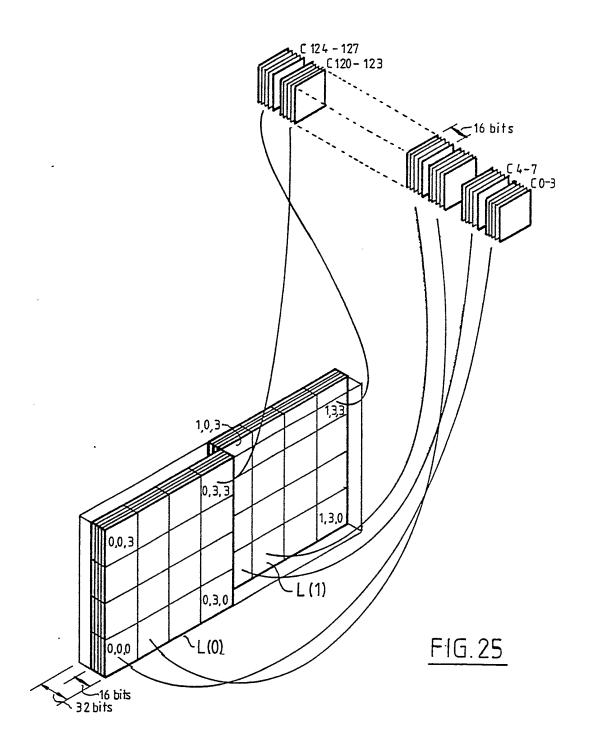

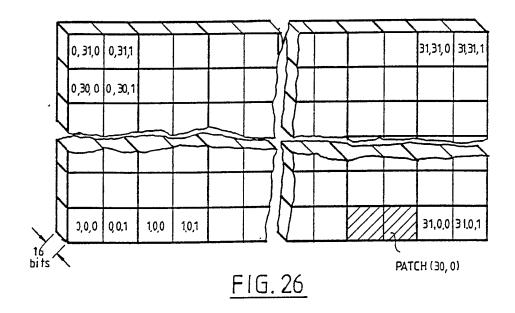

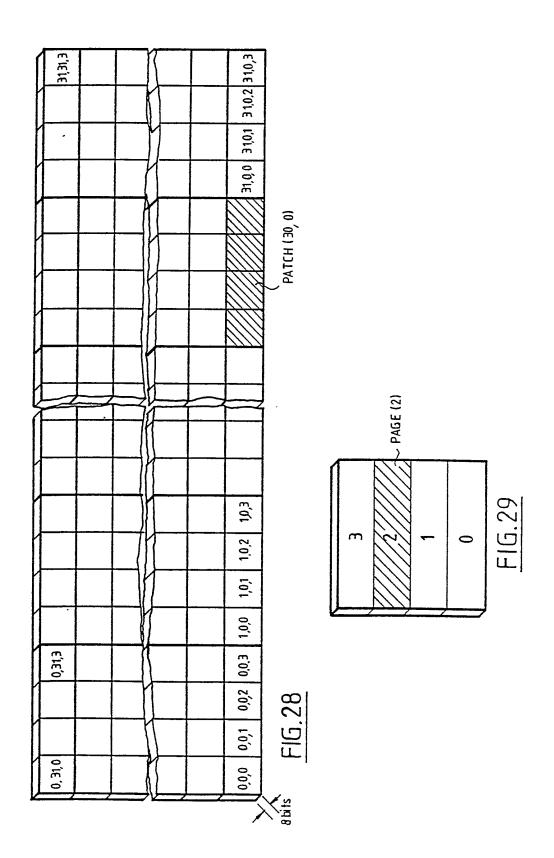

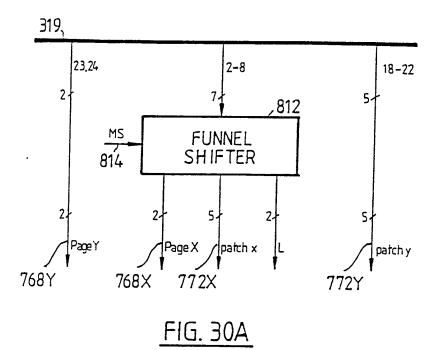

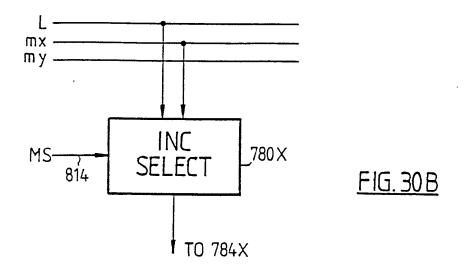

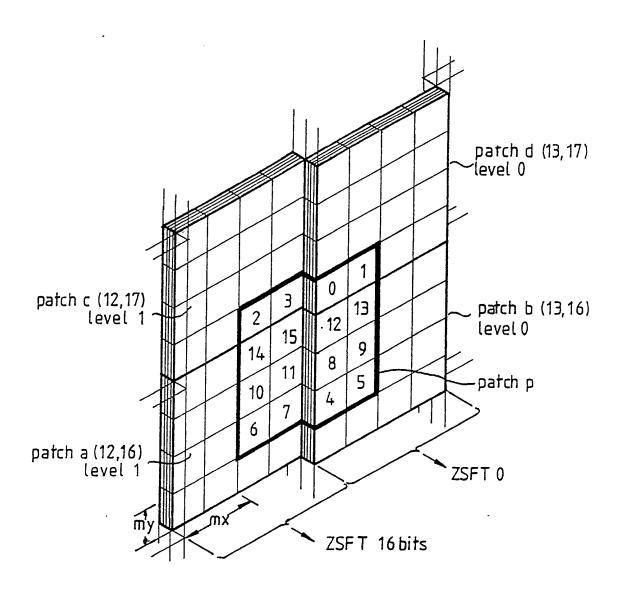

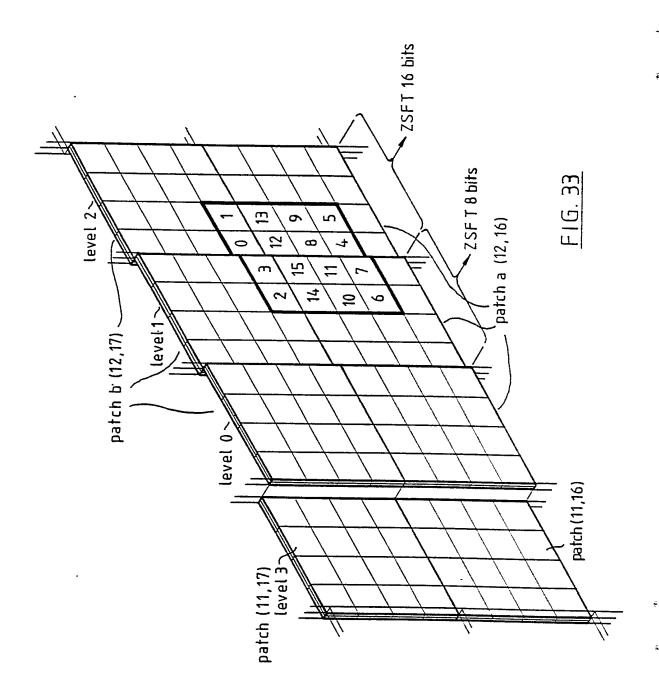

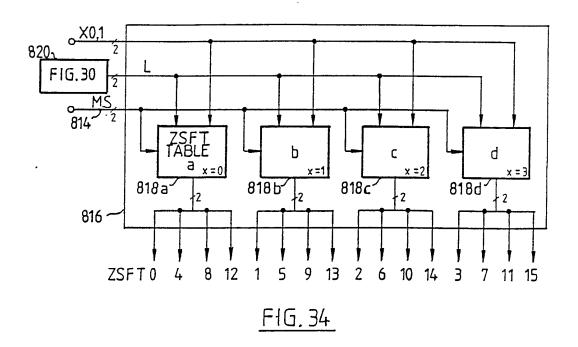

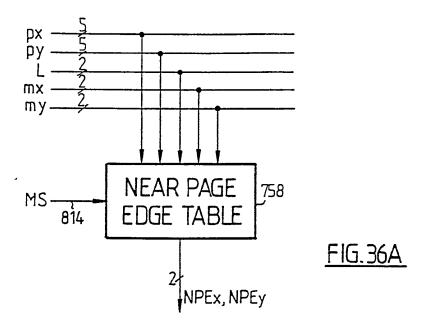

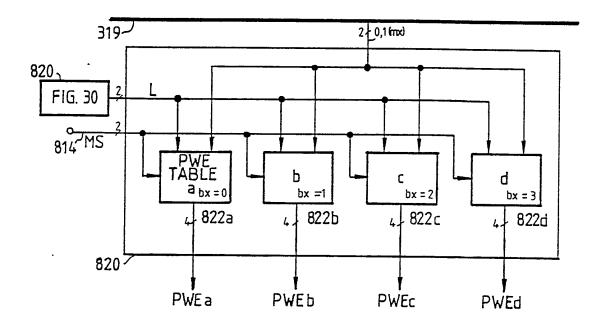

Figure 25 illustrates the correlation between aligned memory cells and two levels of a patch in a 16-bit split patch system. Figures 26 and 27 show how pages of patch data, and superpages of page data are made up in a 16-bit split patch system. Figures 28 and 29 correspond to Figures 26 and 27 respectively in an 8-bit split patch system. Figures 30A to 30C show modifications of the address translator of Figure 15 used in the split patch system. Figure 31 is a table to explain the operation of a funnel shifter used in the circuit of Figure 30A. Figures 32 and 33 illustrate non-aligned split patches in a 16-bit and an 8-bit patch system, respectively. Figure 34 shows a further modification of part of the address translator of Figure 15 used in the split patch system. Figures 35A and 35B illustrate the operation of lookup tables in the circuit of Figure 34. Figures 36A and 36B shows modifications of a near-page-edge table of Figure 15A used in the split patch system. Figure 37 illustrates, in part, a modification to the exchange and grid processor of Figure 22 used in the split patch system.

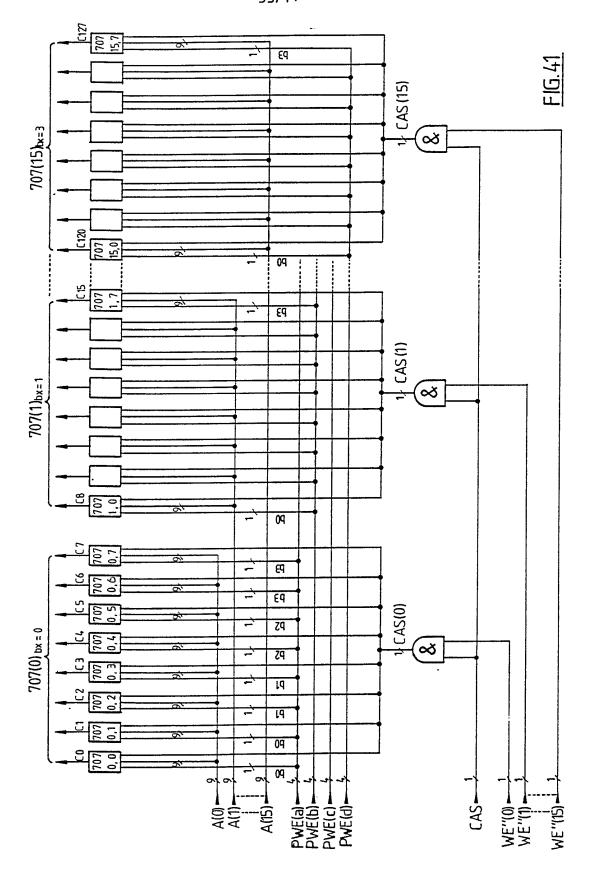

Figures 38 and 39 are tables which illustrate the operation of further tables in a further modification of part of the address translator of Figure 15. Figure 40 shows the further modification to Figure 15. Figure 41 shows a modification to Figure 8 which is made in addition to the modification shown in Figure 40.

15

20

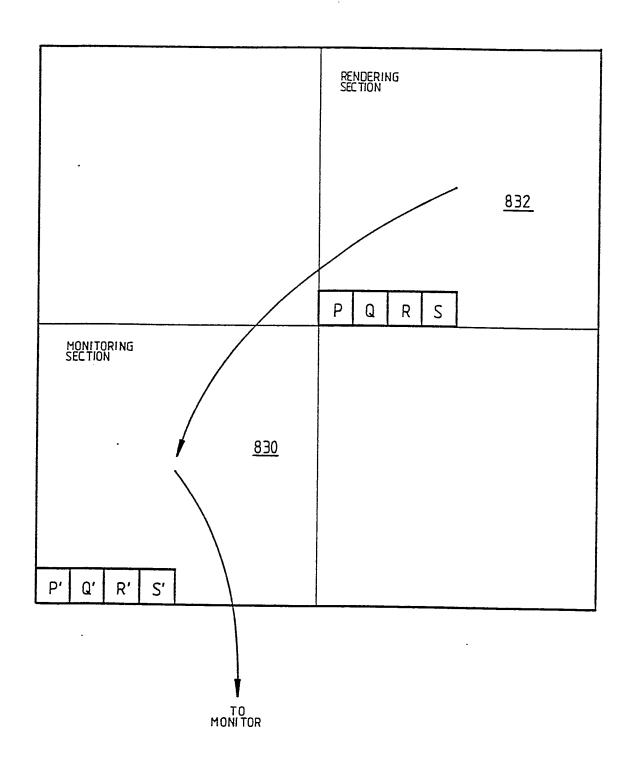

Figure 42 is a representation of the VRAM memory space, showing how pages of data are rendered in one section of the memory and then copied to another monitoring section of the memory.

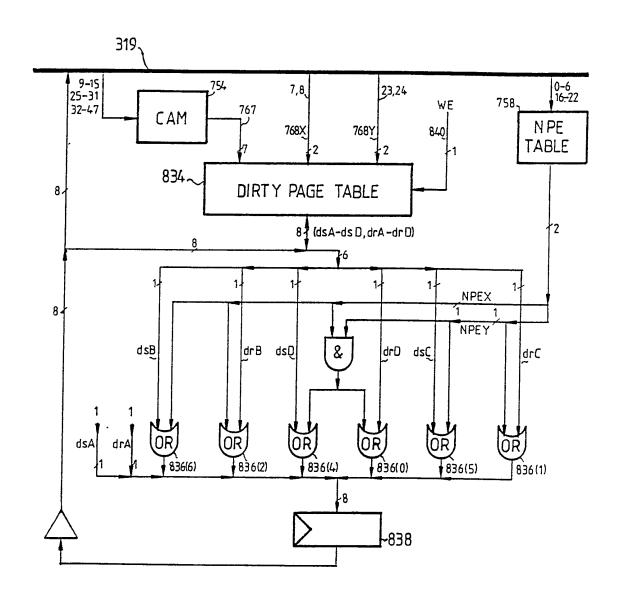

Figure 43 shows a circuit for determining which pages need not be copied from the rendering section to the monitoring section and to the virtual memory. Figure 44 illustrates the setting and resetting of flags in a table of the circuit of Figure 43.

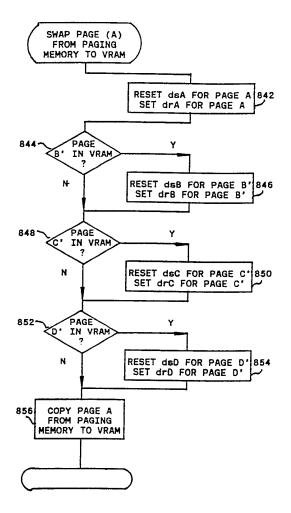

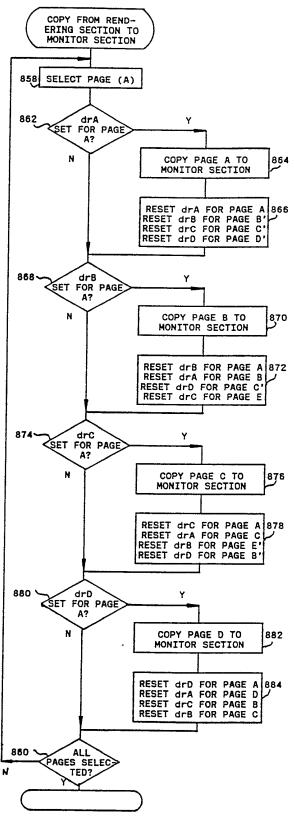

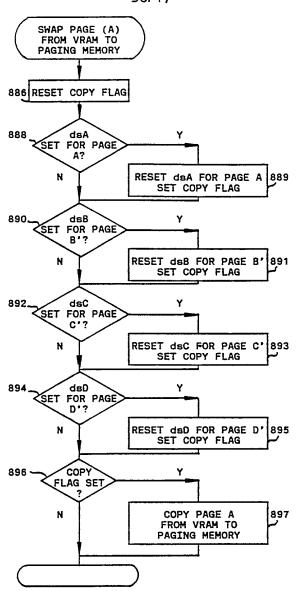

Figure 45A to 45C are flow diagrams illustrating the copying operations and Figure 45D shows the notation used in Figures 45A to 45C.

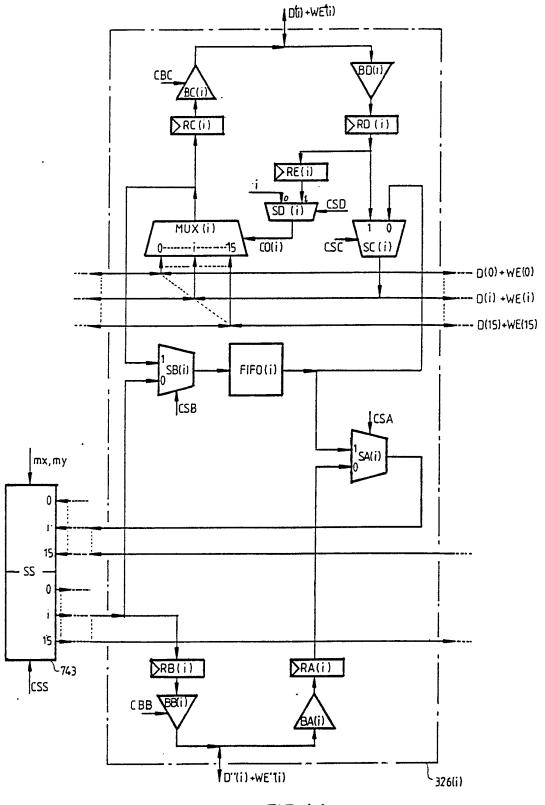

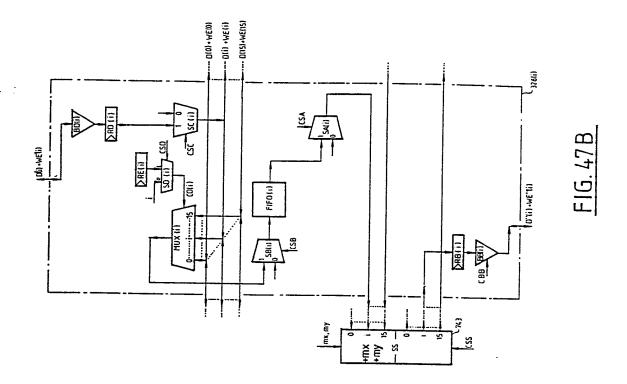

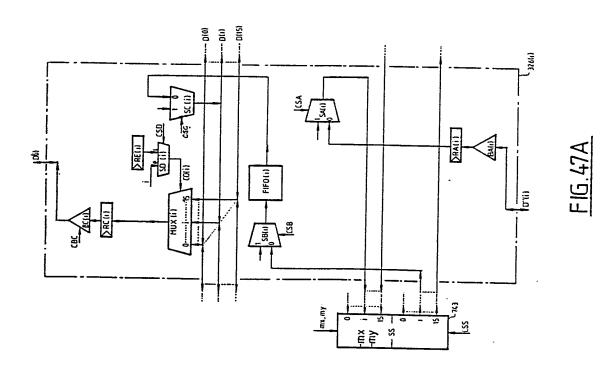

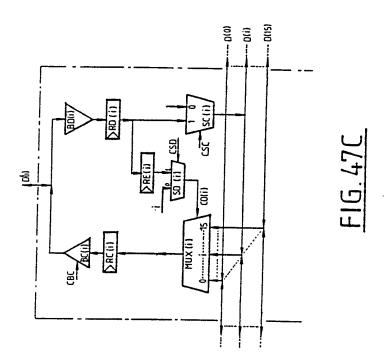

Figure 46 is a circuit diagram of a modification to the exchange of Figure 22. Figure 47A to 47C are simplified forms of the circuit of Figure 46 when operating in three different modes.

Figure 48 shows a modification of the flow diagram at Figure 23.

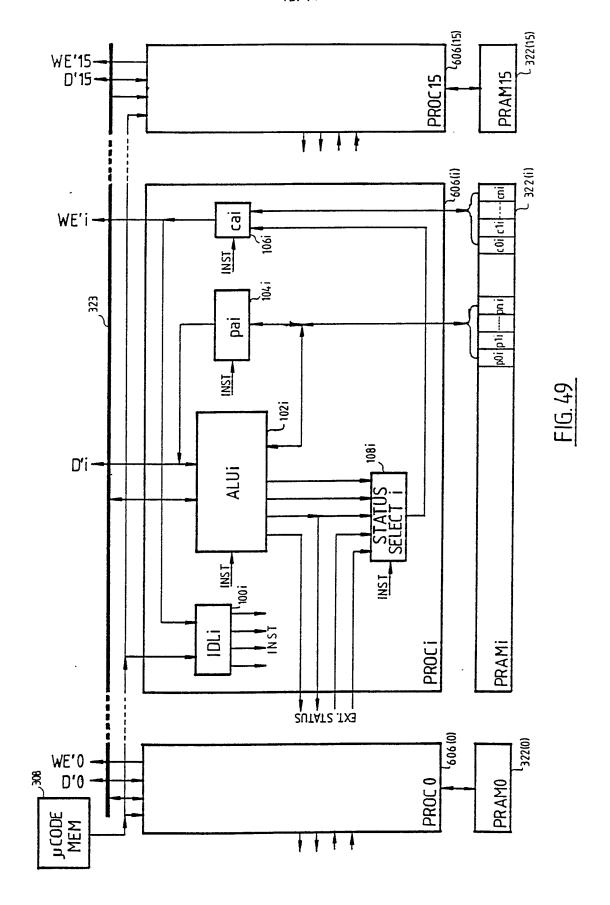

Figure 49 is a schematic diagram of the processors and a microcode memory, with one of the processors shown in detail.

Figures 50A to 50D illustrate three images (Figs 50A to 50C) which are processed to form a fourth image (Fig. 50D).

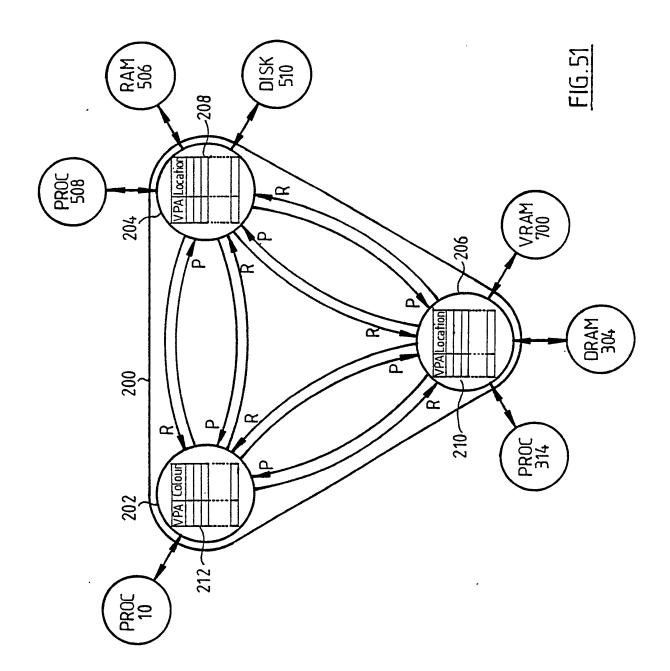

Figure 51 is a system diagram showing a page filing system.

Figure 52 shows how a line is mapped onto a sequence of patches of pixels accessed by the renderer.

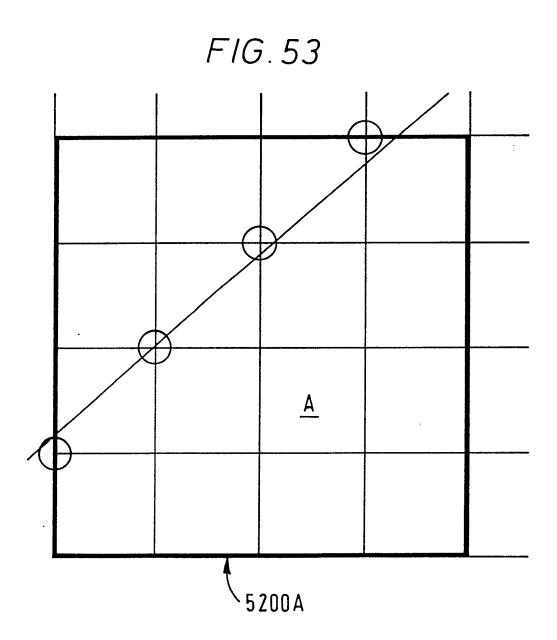

Figure 53 shows how, within each accessed patch, the correct pixels are rendered.

# **DESCRIPTION OF THE PREFERRED EMBODIMENTS**

The hardware context of the claimed inventions will first be described in detail, and then the innovative features will be described in further detail.

#### HARDWARE OVERVIEW

Figures 1 to 3 show three different hardware configurations of computer systems embodying the invention. Referring firstly to Figure 1, a host computer 10 has its own backplane in the form of a VME bus 12 which provides general purpose communications between various circuit boards of the computer, such as processor, memory and disk controller boards. To this known configuation, and within a standard housing 14 for the computer 10, there is added a board on which is provided a renderer 16 and a video processor 18, a Futurebus+ 20, and a front-end board 22. The renderer 16 is connected to the VME bus 12 and the Futurebus+ 20, and also communicates with the video processor 18, which in turn drives an external colour monitor 24 having a high-resolution of, for example, 1280 imes 1024 pixels. The front-end board 22 is also connected to the Futurebus+ 20 and can communicate with a selection of peripherals, which are illustrated collectively by the block 26. The configuration of Figure  $\boldsymbol{1}$ is of use when the host computer 10 has a VME backplane 12 and there is sufficient room in the computer housing 14 for the renderer 16, video processor 18, Futurebus+ 20 and front-end board 22, and may be used, for example, with a 'Sun Workstation'.

In the case where the computer housing 14 is physically too small, or where the host computer 10 does not have a VME or Futurebush backplane, the configuration of Figure 2 may be employed. In Figure 2, a separate housing 28 is used for the renderer 16, video processor 18, frontend board 22 and Futurebus+ 20, as described above, together with a VME bus 12 and a remote interface 30. In the host computer housing 14, a host interface 32 is connected to the backplane 34 of the host computer 10, which may be of VME, Qbus, Sbus, Multibus II, MCA, PC/AT, etc. format. The host interface 32 and remote interface 30 are connected by an asynchronous differential bus 36 which provides reliable communication despite the physical separation of the host and remote interfaces. The configuration of Figure 2 is appropriate when the host computer 10 is, for example, an 'Apple Mackintosh', 'Sun Sparkstation', 'IBM-PC', or Du Pont Pixel Systems bRISC'.

In the event that a host computer becomes available which has a Futurebus+ backplane and sufficient space in its housing for the additional components, then the configuration of Figure 3 may be employed. In Figure 3, the renderer 16 and the front-end board 22 are directly connected to the Futurebus+ backplane 20.

The general functions of the elements shown in Figures 1 to 3 will now be described in more detail. The host computer 10 supplies data in the form of control information, high level commands and parameters therefor to the renderer 16 via the VME backplane (Figure 1), via the backplane 34, host and remote interfaces 32, 30 and the VME bus 12 (Figure 2), or via the Futurebus+ backplane 20 (Figure 3). Some of this data may be forwarded to the front-end board via the Futurebus+ 20 (Figures 1 and 2), or sent direct via the Futurebus+ backplane 20 (Figure 3) to the front-end board 22.

The Futurebus+ 20 serves to communicate between the renderer 16 and the front-end processor 22 and is used, in preference to a VME bus or the like, in view of its high bit width of 128 bits and its high bandwidth of about 500 to 800 Mbytes/s.

As will be decribed in greater detail below, the renderer 16 includes an image memory, part of which is mapped to the monitor 24 by the video processor 18, and the renderer serves to perform image calculations and rendering, that is the drawing of polygons in the memory, in accordance with the commands and parameter supplied by the host computer 10 or the front-end board 22.

The front-end board 22 serves a number of functions. It includes a large paging RAM, which also interfaces with external disk storage, to provide a massive paging memory, and pages of image data can be swapped between the paging RAM and the image memory of the renderer 16 via the Futurebus+ 20. The front-end board also has a powerful floating-point processing section which can be used for graphics transformation and shading operations. Furthermore, the front-end board

may provide interfacing with peripherals such as a video camera or recorder, monitor, MIDI audio, microphone, SCSI disk and RS 232.

Overall, therefore, the renderer 16, video processor 18 and frontend board 22 can accelerate pixel handling aspects of an application, and also accelerate other computation intensive aspects of an application.

The renderer 16 and video processor 18 will now be described in greater detail with reference to Figure 4, which shows the main elements of the renderer 16 and the main data and address pathways.

The renderer 16 includes a 32-bit internal bus 300, a VME interface 301 which interfaces between the VME bus 12 (Figure 1) or the remote interface 30 (Figure 2) and the internal bus 300, and a Futurebus+ interface 302 which interfaces between the Futurebus+ 20 and the internal bus 300. Also connecting to the internal bus 300 are a control processor 314 implemented by an Intel 80960i, an EPROM 303, 4 or 16 Mbyte of DRAM 304, a real time clock and an I/O block 306 including a SCSI ports. The functions of the control processor 314 and the associated DRAM 304 and EPROM 303 are (a) to boot-up and configure the system; (b) to provide resource allocation for local PRAM 318, 322 of address and grid processors 310, 312 (described in detail below) to ensure that there is no memory space collision; (c) to control the loading of microcode into microcode memories 307, 308 (described below); (d) to run application specific remote procedure calls (RPCs); and (e) to communicate via the I/O block 306 with a diagnostics port of the host computer 10 to enable diagnostics information to be displayed on the monitor 24. The DRAM 304 can also be used as a secondary image page store for the VRAM 700 described below.

The renderer 16 also includes an address processing section 309 comprising an address broadcast bus 311 to which are connected 64 kbyte of global GRAM 316, a data/instruction cache 313 which also connects to the internal bus 300, an internal bus address generator 315 which also connects to the internal bus 300, an address processor 310 with 16 kbyte

of local PRAM 318, and a sequencer 317 for the address processor 310 which receives microcode from a microcode memory 307. The address processor 310 also connects to a virtual address bus 319. The main purpose of the address processing section 309 is to generate virtual addresses which are placed on the virtual address bus under control of microcode from the microcode memory 307.

Also included in the renderer 16 is an address translator 740 (described in further detail below) which receives the virtual addresses on the virtual address bus 319 and translates them into physical addresses of data in the video RAM 700, if the required data is present, or interrupts the address processor 310 to cause the required data to be swapped in from the paging RAM 304 or other page stores on the external buses, if the required data is not present in the VRAM 700.

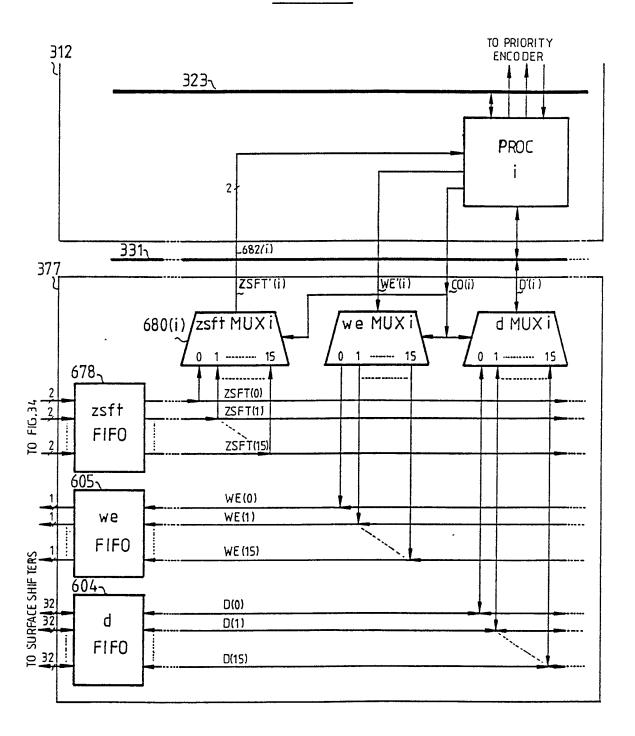

The renderer 16 furthermore includes a data processing section 321 which is somewhat similar to the address processing section 309 and comprises a data broadcast bus 323, to which are connected 64 kbyte of global GRAM 324, a diagnostics register 325 which also connects to the internal bus 300 and which may be used instead of the I/O block 306 to send diagnostics information to the host computer 10, an internal bus address generator 327 which also connects to the internal bus 300, a grid processor 312 having sixteen processors each with 8 kbyte of local PRAM 322, and a sequencer 329 for the grid processor 312 which receives microcode from a microcode memory 308. The processors of the grid processor 312 also connect to a data bus 331. The main purpose of the data processing section 321 is to receive data on the data bus 331, process the data under control of microcode from the microcode memory 308, and to put the processed data back onto the data bus 331.

The physical VRAM 700 connects with the data bus 331 via an exchange 326 which is described in detail below, but which has the main purposes of shuffling the order of the sixteen pixels read from or written to the VRAM 700 at one time, as desired, to enable any of the sixteen processors in the grid processor 312 to read from or write to any of the

sixteen addressed locations in the VRAM 700 and to enable any of the sixteen processors to transfer pixel data to any other of the sixteen processors.

The last main element of the renderer 16 is a bidirectional FIFO 332 connecting between the broadcast buses 311, 323 of the address and data processing sections 309, 321, which enables virtual addresses to be transferred directly between these two sections.

The front-end board 22 will now be described in greater detail with reference to Figure 5.

The front-end board 22 has an internal bus 502 which communicates with the Futurebus+ 20. A paging memory section 504 is connected to the internal bus 502 and comprises a large paging RAM 506 of, for example, 4 to 256 Mbytes capacity which can be used in conjunction with the DRAM 304 of the renderer, a paging memory control processor 508, and connections to, for example, two external high speed IPI-2 disk drives 510 (one of which is shown) each of which may have a capacity of, for example, 4 Gbytes, and a data communication speed of 50 Mbytes/s, or two external SCSI drives. The paging RAM 506 enables an extremely large amount of pixel data to be stored and to be available to be paged into the renderer 32 as required, and the fast disk 510 enables even more pixel data to be available ready to be transferred into the paging RAM 506.

Floating point processing is provided by 1 to 4 Intel 80860 processors 516, each rated at 80 MFlops peak. The general purpose processing power can be used on dedicated tasks such as geometric pipeline processing, or to accelerate any part of an application which is compute-intensive, such as floating point fast Fourier transforms. Each of the floating point processors 516 has a 128KByte secondary cache memory 518 in addition to its own internal primary cache memory.

The front-end board 22 may also, if desired, include a broadcast

standard 24-bit frame grabber connected to the internal bus 502 and having a video input 514 and output 516 for connection to video camera or television-type monitor.

The front-end board 22 may also, if desired, include an input/output processor 520 which provides interfacing with MIDI on line 522, SCSI disk on line 524, at least one mouse on line 526, RS232 on line 528, and audio signals on line 530 via a bi-directional digital/analogue convertor 532.

#### VIDEO RAM AND ADDRESSING THEREOF

Now that an overview of the hardware of the whole system has been set out, the image memory configuration will be described in more detail.

As mentioned above, the VRAM has a of 16 Mbyte capacity. The system is capable of operating with 32-bit pixels, and therefore the image memory has a capacity of  $16M \times 8/32 = 4 \text{ Mpixels.}$  As illustrated in Figures 6A and 6B, pixels are arranged in 4 x 4 groups referred to as 'patches'. Figures 6A and 6B show, respectively, two-and one-dimensional notations for designating a pixel in a patch, as will be used in the following description. In turn, as illustrated in Figure 7A, the patches are arranged in 32 x 32 groups referred to as 'pages'. Furthermore, as illustrated in Figure 7B, the pages are arranged in 4 x 4 groups referred to as 'superpages'. The VRAM therefore has a capacity of 4 Mpixels, or 256k patches, or 256 complete pages, or 16 complete superpages. However, not all pages of a particular superpage need be stored in the memory at any one time, and support is provided for pages from parts of up to 128 different superpages to be stored in the physical memory at the same time.

The VRAM 700 and addressing lines therefor are shown schematically in Figure 8. Each small cube 702 in Figure 8 represents a 32-bit pixel. The pixels are arranged in 512 pixel x 512 pixel banks B(0) -

B(15) lying in the XY plane, and these pixel banks are 16 pixels deep (in the P direction). A line of 16 pixels in the P direction provides an aligned patch 704. The pixels in each bank are addressable as to X address by a respective one of 16 9-bit X address lines AX(0) to AX(15) and are addressable as to Y address by a respective one of 16 9-bit Y address lines AY(0) to AY(15). The Y and X addresses are sequentially supplied on a common set of 16 9-bit address lines A(0) to A(15), with the Y addresses being supplied first and latched in a set of 16 9-bit Y latch groups 706-0 to 706-15 each receiving a row address strobe (RAS) signal on 1-bit line 708, and the X addresses then being supplied and latched in a set of 16 9-bit X latch groups, 707-0 to 707-15 each receiving a respective column address strobe signal CAS(0) to CAS(15) on lines 709(0) to 709(15), respectively.

The memory for each XY bank of pixels (512 pixels x 512 pixels x 1 pixel) is implemented using eight video-RAM (VRAM) chips 710, each 256 K (4-bit) nibbles. Each chip provides a one-eighth thick slice of each pixel bank, whereby  $8 \times 16 = 128$  chips are required. Each Y latch group and X latch group comprises eight latches (shown in detail for Y latch group 706(1) and X latch group 707(1) and a respective one of the X and Y latches is provided on each VRAM chip 710.

In this specification, the banks of memory will sometimes be referred to by the bank number B(0) to B(15) and at other times by a 2-dimensional bank address (bx,by) with the correlation between the two being as follows:

| Bank Number | (bx,by) | Bank Number | <u>(bx,by)</u> |

|-------------|---------|-------------|----------------|

| B(0)        | (0,0)   | B(8)        | (0,2)          |

| B(1)        | (1,0)   | B(9)        | (1,2)          |

| B(2)        | (2,0)   | B(10)       | (2,2)          |

| B(3)        | (3,0)   | B(11)       | (3,2)          |

| B(4)        | (0,1)   | B(12)       | (0,3)          |

| B(5)        | (1,1)   | B(13)       | (1,3)          |

| B(6)        | (2,1)   | B(14)       | (2,3)          |

| B(7)        | (3,1)   | B(15)       | (3,3)          |

|             |         |             |                |

When a location in the memory 700 is to be accessed, a patch of 16 pixels is made available for reading or writing at one time. If the Y address and X address for all of the VRAMs 710 is the same, then an "aligned" patch of pixels (such as patch 704) will be accessed. However, it is desirable that access can be made to patches of sixteen pixels which are not aligned, but where various pixels in the patch to be accessed are derived from two or four adjacent aligned patches.

÷

3

It will be appreciated that access to an aligned patch in memory is more straightforward than access to a non-aligned patch, because for an aligned patch the (x,y) address of each pixel in the different XY planes of memory as shown in Figure 8 is the same. Furthermore, the (x,y) address of each pixel in the patch is equal to the bank address (bx,by) of the memory cell from which that pixel is derived. Referring to Figures 9A and 9B, an aligned patch "a" having a patch address (12, 16) in a page "A" having a page address (8, 6) is shown, as an example. The pixels in the aligned patch all have the same address in the sixteen XY banks of the memory, as represented in Figure 9A, and when displayed would produce a 4 X 4 patch of pixels offset from the page boundaries by an integral number of patches, as represented in Figure 9B. In the particular example the absolute address of the aligned patch in the memory would be  $(8 \times 32 + 12, 6 \times 32 + 16) = (268, 208)$ .

If, however, a patch "p" is non-aligned, and has a misalignment (mx,my) = (2,1), for example, from the previously considered aligned patch "a" at patch address (12, 16) in page A at page address (8, 6), then some of the pixels of patch "p" will need to be derived from three other aligned patches "b", "c" and "d" having patch addresses (12 + 1, 16), (12, 16 + 1) and (12 + 1, 16 + 1), or (13, 16), (12, 17) and (13, 17) in page A at page address (8, 6). This situation is represented in Figures 10A and 10B. The absolute address of these patches "b", "c" and "d" in the VRAM 700 are (269, 208), (268, 209) and (269, 209); respectively.

A further problem which arises in accessing a non-aligned patch "p" is that the (x,y) address of each pixel in the patch "p" does not correspond to

the bank address (bx,by) in the memory from which that pixel is derived. In the particular example, the following pixel derivations and translations are required.

| Address (x,y) of     | Aligned patch | Bank address | Translation            |

|----------------------|---------------|--------------|------------------------|

| pixel in non-aligned | (px,py) from  | (bx,by) from | required from          |

| patch "p"            | which pixel   | which pixel  | bank address           |

|                      | is derived    | is derived   | (bx,by) to             |

|                      |               |              | pixel address          |

|                      |               |              | (x <b>,</b> y) in      |

|                      |               |              | patch "p"              |

|                      |               |              |                        |

| (0,0)                | a (12,16)     | (2,1)        | (-2,-1)                |

| (1,0)                | a (12,16)     | (3,1)        | (-2,-1)                |

| (2,0)                | b (13,16)     | (0,1) .      | (-2,-1) mod 4          |

| (3,0)                | b (13,16)     | (1,1)        | (-2 <b>,</b> -1) mod 4 |

| (0,1)                | a (12,16)     | (2,2)        | (-2,-1)                |

| (1,1)                | a (12,16)     | (3,2)        | (-2,-1)                |

| (2,1)                | b (13,16)     | (0,2)        | (-2,-1) mod 4          |

| (3,1)                | b (13,16)     | (1,2)        | (-2 <b>,</b> -1) mod 4 |

| (0,2)                | a (12,16)     | (2,3)        | (-2,-1)                |

| (1,2)                | a (12,16)     | (3,3)        | (-2,-1)                |

| (2,2)                | b (13,16)     | (0,3)        | (-2,-1) mod 4          |

| (3,2)                | b (13,16)     | (1,3)        | (-2,-1) mod 4          |

| (0,3)                | c (12,17)     | (2,0)        | (-2,-1) mod 4          |

| (1,3)                | c (12,17)     | (3,0)        | (-2 <b>,-</b> 1) mod 4 |

| (2,3)                | d (13,17)     | (0,0)        | (-2,-1) mod 4          |

| (3,3)                | d (13,17)     | (1,0)        | (-2,-1) mod 4          |

From the right hand column above, it will be noted that the translation from the bank address (bx,by) to the corresponding address in the non-aligned patch is constant for a particular non-aligned patch and in particular is equal to the negative of the misalignment (mx,my) of the non-aligned patch "p" from the base aligned patch "a", all translations being in modulus arithmetic with the modulus equal to the patch dimension.

Yet another further complication arises with non-aligned patches, and that is that the patch may extend across the boundary between two or four pages. To provide flexibility, not all pages which make up an image and which are contiguous in the virtual address space need to be stored in the VRAM at one time, and pages are swapped between the paging memory and the VRAM as required. This results in those pages making up an image which are in the VRAM not necessarily being stored adjacent each other in the VRAM, but possibly being scattered in non-contiguous areas of the VRAM.

For example, Figure 11A represents four contiguous pages A, B, C, D in the virtual address space. When these pages are swapped into the physical memory 700, they may be scattered at, for example, page addresses (8,6), (4,8), (12, 12) and (6,10) in the VRAM, as represented in Figure 11B. Now, if it is desired to access a non-aligned patch "p" who base aligned patch "a" in page A has an x or y patch address of 31, then the non-aligned patch "p" may extend into page B, page C or pages B, C and D, depending on the direction of the misalignment. In the example shown specifically in Figure 11, the patch "p" to be accessed has a misalignment (mx,my) = (2,1)relative to base aligned patch "a" having patch address (px,py) = (31,31) in page A having page address (8,6) in the VRAM. It will be appreciated that, in addition to translating accessed pixels between their bank addresses (bx,by) and the addresses (x,y) in the non-aligned patch as described above with reference to Figure 10, it is also necessary to determine the various pages B, C, D which are to be accessed in addition to the basic page A and furthermore to determine the addresses in these other pages B, C, D of the aligned patches to be accessed, it being noted in the example that although the aligned patch "a" in page A has a patch address of (31,31), different patch addresses need to be used in other the pages B, C, D, that is (0,31), (31,0) and (0,0), respectively. The following table sets out, for each of the pixels in the patch "p" to be accessed: the page and patch address of the aligned patch from which that pixel is derived; the translation necessary from the patch address of the basic patch "a" in page A to the patch address of the patch from which the pixel is derived; the bank address from which the pixel is derived; and the translation necessary from this latter address to

the address of the pixel in the patch "p".

| Address (x,y) of pixel in non-aligned patch "p" | aligned patch<br>from which<br>pixel is<br>derived | Translation necessary from address of patch "a" to address (px,py) | Bank address (bx,by) of pixel | Translation necessary from bank address (bx,by) to |

|-------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------|-------------------------------|----------------------------------------------------|

|                                                 | <u>P/(px,py)</u>                                   | of patch from which pixel is                                       |                               | pixel<br>address                                   |

|                                                 |                                                    | derived                                                            |                               | (x,y) in                                           |

|                                                 |                                                    |                                                                    |                               | patch "p"                                          |

|                                                 |                                                    |                                                                    |                               |                                                    |

| (0 <b>,</b> 0)                                  | A/(31,31)a                                         | (0,0)                                                              | (2,1)                         | (-2,-1)                                            |

| (1,0)                                           | A/(31,31)a                                         | (0,0)                                                              | (3,1)                         | (-2,-1)                                            |

| (2,0)                                           | B/(0,31)b                                          | (1,0) mod 32                                                       | (0,1)                         | (-2,-1) mod 4                                      |

| (3,0)                                           | B/(0,31)b                                          | (1 <b>,</b> 0) mod 32                                              | (1,1)                         | (-2,-1) mod 4                                      |

| (0,1)                                           | A/(31,31)a                                         | (0,0)                                                              | (2,2)                         | (-2,-1)                                            |

| (1,1)                                           | A/(31,31)a                                         | (0,0)                                                              | (3,2)                         | (-2,-1)                                            |

| (2,1)                                           | B/(0,31)b                                          | (1 <b>,</b> 0) mod 32                                              | (0,2)                         | (-2,-1) mod 4                                      |

| (3,1)                                           | B/(0,31)b                                          | (1,0) mod 32                                                       | (1,2)                         | (-2,-1) mod 4                                      |

| (0,2)                                           | A/(31 <b>,</b> 31)a                                | (0,0)                                                              | (2,3)                         | (-2,-1)                                            |

| (1,2)                                           | A/(31,31)a                                         | (0,0)                                                              | (3,3)                         | (-2,-1)                                            |

| (2,2)                                           | B/(0,31)b                                          | (1 <b>,</b> 0) mod 32                                              | (0,3)                         | (-2,-1) mod 4                                      |

| (3,2)                                           | B/(0,31)b                                          | (1,0) mod 32                                                       | (1,3)                         | (-2,-1) mod 4                                      |

| (0,3)                                           | C/(31,0)c                                          | (0,1) mod 32                                                       | (2,0)                         | (-2,-1) mod 4                                      |

| (1,3)                                           | C/(31,0)c                                          | (0,1) mod 32                                                       | (3,0)                         | (-2,-1) mod 4                                      |

| (2,3)                                           | D/(0 <b>,</b> 0)d                                  | (1,1) mod 32                                                       | (0,0)                         | (-2,-1) mod 4                                      |

| (3,3)                                           | D/(0 <b>,</b> 0)d                                  | (1,1) mod 32                                                       | (1,0)                         | (-2,-1) mod 4                                      |

A representation of the locations of the pixels in the four aligned patches is shown in Figure 11C.

In the example, the basic patch "a" has a patch address (px,py) of (31,31) and the non-aligned patch "p" to be accessed has a misalignment (mx,

my) of (2,1) relative to the basic patch "a". In the general case of a base patch address (px, py), where  $0\le px$ , py $\le 31$ , and a misalignment (mx, my), where  $0\le mx$ , my $\le 3$ , the table of Figure 12 sets out which page A, B, C or D should be used when accessing a pixel at bank address (bx,by), where  $0\le bx$ ,by $\le 3$ , in dependence up bx, by, mx, my, px and py, and the table of Figure 13 sets out the X patch address px, or px + 1 mod 4, and the Y patch address py, or py + 1 mod 4, which should be used in order to obtain the address of the aligned patch a, b, c or d to be accessed, in dependence upon bx, by, mx and my. The increment is calculated using modular arithmetic of base 32. It is also to be noted that for all pixels where (mx, my)  $\le 0.0$ , a translation of (-mx, -my) is required between the bank address (bx,by) from which the pixel is derived and the address (x,y) of the pixel in the non-aligned patch "p".

Having described various addressing functions which it is required to be performed, there now follows a description in greater detail of the apparatus for performing these functions.

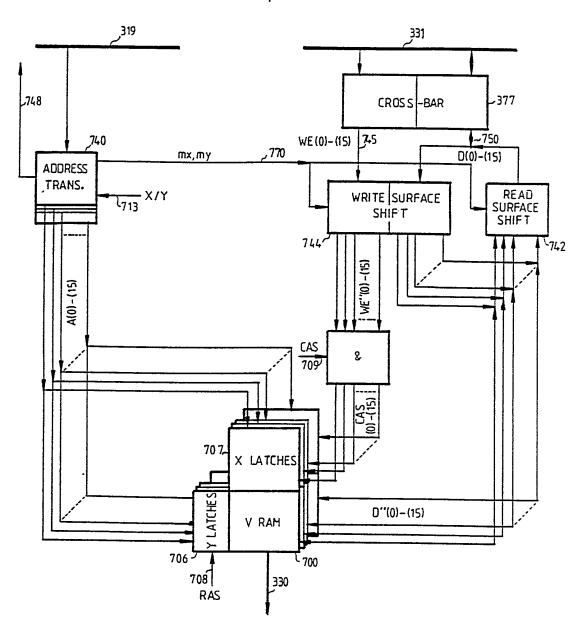

As described above with reference to Figure 4, the VRAM 700 is addressed by the address processor 310 <u>via</u> the address translator 740, communicates data with the grid processor 312 <u>via</u> the exchange 326 and provides data to the video processor 34. A greater degree of detail of the address translator, VRAM and exchange is shown in Figure 14.

The address translator 740 receives a 48-bit virtual address on bus 319 of a patch origin address. The translator determines whether the required page(s) to access the addressed patch are resident in the VRAM physical memory 700. If not, a page or superpage fault is flagged on line 748, as will be described in detail below. However, if so, the address translator determines the addresses in the sixteen XY banks of the physical memory of the sixteen pixels making up the patch, and addresses the memory 700 firstly with the Y addresses on the sixteen sets of 9-bit lines A(0) to A(15) and then with the X addresses on these lines. The X and Y addresses are generated under control of the X/Y select signal on line 713.

The exchange 326 includes a read surface shifter 742 and a write surface shifter 744. Pixel data is transferred, during a read operation, from the memory 700 to the read surface shifter 742 by a set of sixteen 32-bit data lines D"(0) to D"(15), and, during a write operation, from the write surface shifter 744 to the memory 700 by the same data lines D"(0) to D."(15). The read and write surface shifters 742, 744 receive 4-bit address data from the address translator on line 770, consisting of the least significant two bits of the X and Y address data. This data represents the misalignment (mx, my) of the accessed patch "p" from the basic aligned patch "a". The purpose of the surface shifters is re-order the pixel data in non-aligned patches, that is to apply the translation (-mx, -my) when reading and an opposite translation (mx, my) when writing. Pixel data to be written is supplied by a crossbar 327 forming part of the exchange 326 to the write surface shifter 744, and pixel data which has been read is supplied by the read surface shifter 742 to the crossbar 327, on the 512-bit line 750 made up of a set of 16 32-bit lines. The write surface shifter also receives on line 745 16-bit write enable signals WE(0) - WE(15) from the crossbar 327 one for each pixel, and the write surface shifter 744 re-organises these signals in accordance with the misalignment (mx, my) of the patch "p" to be accessed to provide the sixteen column write enable signals WE"(0) to WE"(15). Each of these signals is then ANDed with a common CAS signal on line 709 to form sixteen CAS signals CAS(0) to CAS(15), one for each of the sixteen banks of memory. This enables masking of pixels within a patch during writing, taking into account any misalignment of the patch.

The address translator 740 will now be described in more detail primarily with reference to Figure 15. The translator 740 includes as shown, a contents addressable memory (CAM) 754, a page address table 756, a near-page-edge table 758, and X and Y incrementers 760X, 760Y. The translator 740 also includes sixteen sections 764(0) to 764(15), one for each output address line A(0) to A(15), and thus for each memory bank B(0) to B(15).

The translator 740 receives a 48-bit virtual address of the origin (0,0) pixel of a patch on the bus 319. It will therefore be appreciated that up to 248 (i.e. 281, 474, 976, 710, 656) different pixels can be addressed. Many

formats of the 48-bit address can be employed, but the following example will be considered in detail.

|     | BITS  | IDENTITY                                                                            |

|-----|-------|-------------------------------------------------------------------------------------|

| LSB | 0,1   | X misalignment (mx) of patch (p) to be accessed relative to basic aligned patch (a) |

|     | 2-6   | X address (px) of aligned patch (a) in page A                                       |

|     | 7,8   | X address of page A                                                                 |

|     | 9-15  | X portion of superpage address                                                      |

|     |       |                                                                                     |

|     | 16,17 | Y misalignment (my) of patch (p) to be accessed                                     |

|     |       | relative to basic aligned patch (a)                                                 |

|     | 18-22 | Y address (py) of aligned patch (a) in page A                                       |

|     | 23,24 | Y address of page A                                                                 |

|     | 25-31 | Y portion of superpage address                                                      |

| MSB | 32-47 | Image ID portion of superpage address                                               |

The bits identifying the superpage (i.e. bits 9 to 15, 25 to 31 and 32 to 47) are supplied to the CAM 754. The CAM 754 is an associative memory device which compares the incoming 30-bit word with all of the words held in its memory array, and if a match occurs it outputs the location or address in the memory of the matching value on line 767. The CAM 754 has a capacity of 128 32-bit words. Thirty of these bits are used to store the virtual address of a superpage which is registered in the CAM 754. Thus up to 128 superpages can be registered in the CAM. One of the other bits is used to flag any location in the CAM which is unused. The remaining bit is spare. Figure 16 illustrates how the CAM 754 operates. Upon input of a 30bit superpage address, e.g. 01234569 (hex), this input value is compared with each of the contents of the CAM. If a match is found and provided the unused flag is not set, the address in the CAM of the match is output, e.g. 1 in the illustration. If no match is found with the contents at any of the 128 addresses of the CAM, then a superpage fault is flagged on line 748S, and the required superpage is then set up in the CAM in the manner described in

detail later.

Referring back to Figure 15, the 7-bit superpage identification output from the CAM 754 on line 767 is used as part of an address for the page address table 756, implemented by a 4k word x 16-bit SRAM. The remaining 5 bits of the address for the page table 756 are made up by: bits 7, 8, 23 and 24 of the virtual address which identify the page within a superpage; and an  $\times/Y$  select signal on line 713. The page table 756 has registered therein the X and Y page addresses in the VRAM 700 of: a) the basic page A in which the pixel to be accessed is located; b) the page B which is to the right of the page A in the virtual address space; c) the page C which is above the page A in the virtual address space; and d) the page D which is to the right of page C and above page B in the virtual address space, and these addresses are output on lines 771A to 771D, respectively. If these pages A to D are required, but are not stored in the VRAM 700 and thus are not registered in the page table 756, then a page fault is flagged on a line 748p (as described below with reference to Figure 21) and the required page of data is then swapped into the VRAM 700 in the manner described in detail below. However, if all of the pages A to D which may possibly need to be accessed are stored, their addresses are made available on the lines 771A to 771D to all of the sections 764(0) to 764(15), the Y or X addresses being output depending on the state of the X/Y select signal on line 713.

Bits 2 to 6 and 18 to 22 of the virtual address are also supplied to each of the sections 764(0) to 764(15) on lines 772X and 772Y. These denote the patch address (px, py). The X and Y patch addresses together with bits 0,1, 16 and 17 of the virtual address (which indicate the misalignment mx, my of the patch p to be accessed) are also supplied to the near-page-edge table 758, implemented using combinatorial logic, which provides a 2-bit output to the sections 764(0) to 764(15) on line 774, with one bit being high only if the patch X address px is 31 and the X misalignment mx is greater than zero and the other bit being high only if the patch Y address py is 31 and the Y misalignment my is greater than zero.

Furthermore, the X and Y patch addresses (px, py) are also supplied

to the X and Y incrementers 760X, 760Y, and these incrementers supply the incremented values px + 1, mod 32 and py + 1, mod 32, to each of the sections 764(0) to 764(15) on lines 776X, 776Y.

The four bits 0,1, 16 and 17 giving the misalignment mx and my are also supplied to the sections 764(0) to 764(15) on lines 770X, 770Y and are also supplied to the surface shifters 742, 744 on line 770.

Each section 764(0) to 764(15) comprises: a page selection logic circuit 778; X and Y increment select logic circuits 780X 780Y; X and Y 4:1 4-bit page address multiplexers 782X, 782Y; X and Y 2:1 5-bit patch address multiplexers 784X, 784Y; and a 2:1 9-bit address selection multiplexer 786.

The page selection logic circuit 778 implemented using combinatorial logic, provides a 2-bit signal to the page address multiplexers 782X,Y to control which page address A, B, C or D to use. The page selection logic circuit 778 performs this selection by being configured to act as a truth table which corresponds to the table of Figure 12. The circuit 778 receives the 2-bit signal on line 774 from the near-page-edge table 758 and this determines which of the four columns of the table of Figure 12 to use. The circuit 778 also receives the misalignment (mx, my) on lines 770X, 770Y, and this data in combination with which section 764(0) to 764(15) (and thus which bx and by applies) determines which of the four rows in Figure 12 to use. The X and Y page address multiplexers 782X, 782Y therefore supply appropriate page address as four bits to complementary inputs of the X/Y address selection multiplexer 786.

The increment selection logic circuits 780X, 780Y, which are implemented using combinatorial logic, receive the respective X and Y misalignments mx, my and provide respective 1-bit signals to control the patch address multiplexers 784X, 784Y. The increment selection circuits perform this selection by being configured to act as truth tables which correspond to the upper and lower parts, respectively, of the table of Figure 13. It will be noted that selection depends upon the misalignment mx or my in combination with the bx or by position of the memory bank (and thus

which of the sections 764(0) to 764(15) is being considered). The X and Y patch address multiplexers 784X, 784Y therefore output the appropriate 5-bit patch addresses px or px + 1 (mod. 32) and py or py + 1 (mod. 32) which are combined with the X and Y page addresses at the inputs to the X/Y selection multiplexers 786. This latter multiplexer receives as its control signal the X/Y selection signal on line 713 and therefore outputs the 9-bit X or Y address appropriate to the particular section 764(0) to 764(15).

The address translator 740 therefore deals with the problems described above of addressing pixels from different aligned patches a, b, c, d in the memory 700 when a patch "p" to be accessed is misaligned, and of addressing pixels from different pages A, B, C, D in the memory 700 when a patch "p" to be accessed extends across the boundary of the basic page A.

It is still necessary also to perform a translation of the pixel positions in the accessed patch of (-mx,-my) if reading, or (mx,my) if writing. This is performed by the surface shifter 742 for reading and the surface shifter 744 for writing. The read surface shifter 742 will now be described with reference to Figures 17 and 18.

The read surface shifter 742 comprises a pair of 4 x 4 32-bit barrel shifters, 788X, 788Y. The X barrel shifter 788X has four banks  $790\times(0)$  to  $790\times(3)$  of multiplexers arranged in one direction, and the outputs of the X barrel shifter 788X are connected to the inputs of the Y barrel shifter 788Y, which has four banks  $790\times(0)$  to  $790\times(3)$  of multiplexers arranged in the orthogonal direction. As control signals, the X and Y barrel shifters  $788\times$ , Y receive the X and Y misalignments mx, my, respectively.