(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5193045号

(P5193045)

(45) 発行日 平成25年5月8日(2013.5.8)

(24) 登録日 平成25年2月8日(2013.2.8)

(51) Int.Cl.

F 1

|              |           |              |         |

|--------------|-----------|--------------|---------|

| G 11 C 16/06 | (2006.01) | G 11 C 17/00 | 6 3 6 Z |

| G 11 C 16/02 | (2006.01) | G 11 C 17/00 | 6 1 1 G |

| G 11 C 16/04 | (2006.01) | G 11 C 17/00 | 6 1 3   |

|              |           | G 11 C 17/00 | 6 2 2 E |

請求項の数 32 (全 41 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2008-532552 (P2008-532552)  |

| (86) (22) 出願日 | 平成18年9月29日 (2006.9.29)        |

| (65) 公表番号     | 特表2009-510657 (P2009-510657A) |

| (43) 公表日      | 平成21年3月12日 (2009.3.12)        |

| (86) 國際出願番号   | PCT/CA2006/001609             |

| (87) 國際公開番号   | W02007/036050                 |

| (87) 國際公開日    | 平成19年4月5日 (2007.4.5)          |

| 審査請求日         | 平成21年4月16日 (2009.4.16)        |

| (31) 優先権主張番号  | 60/722,368                    |

| (32) 優先日      | 平成17年9月30日 (2005.9.30)        |

| (33) 優先権主張国   | 米国(US)                        |

| (31) 優先権主張番号  | 11/324,023                    |

| (32) 優先日      | 平成17年12月30日 (2005.12.30)      |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                      |

|-----------|------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 508034325<br>モサイド・テクノロジーズ・インコーポレーテッド<br>カナダ・オンタリオ・K 2 K · 2 X 1 · オタワ・ハインズ・ロード・1 1 · スイート<br>· 2 0 3 |

| (74) 代理人  | 100064908<br>弁理士 志賀 正武                                                                               |

| (74) 代理人  | 100089037<br>弁理士 渡邊 隆                                                                                |

| (74) 代理人  | 100108453<br>弁理士 村山 靖彦                                                                               |

| (74) 代理人  | 100140534<br>弁理士 木内 敏二                                                                               |

最終頁に続く

(54) 【発明の名称】出力制御部を備えたメモリ

## (57) 【特許請求の範囲】

## 【請求項 1】

メモリと、

入力データをデータ入力ポートで受信するように、およびデータをデータ出力ポートに転送するように構成されたデータリンクインターフェースと、

前記メモリデバイスが前記データを前記データ出力ポートに転送できるようにするために使用される、第1の出力イネーブル信号を受信するための第1の制御入力ポートと、

前記メモリデバイスが前記入力データを受信できるようにするために使用される、第1の入力イネーブル信号を受信するための第2の制御入力ポートと、

第2の出力イネーブル信号を出力するための第1の制御出力ポートと、

第2の入力イネーブル信号を出力するための第2の制御出力ポートと、

前記データ出力ポート上でデータ転送を制御する前記第1の出力イネーブル信号に応答する制御回路と

を備える、半導体メモリデバイス。

## 【請求項 2】

前記第2の出力イネーブル信号が、遅延した前記第1の出力イネーブル信号である、請求項1に記載の半導体メモリデバイス。

## 【請求項 3】

前記データリンクインターフェースがシリアルデータリンクインターフェースであり、前記入力データがシリアル入力データであり、さらに前記データリンクインターフェース

10

20

が、シリアル入力データをパラレルデータに変換するように、および前記データを前記メモリに転送するように構成された、請求項1に記載の半導体メモリデバイス。

**【請求項4】**

前記メモリ、前記データリンクインターフェース、および前記制御回路が、片面パッドアーキテクチャを有する単一パッケージ内に配置される、請求項1から3のいずれか一項に記載の半導体メモリデバイス。

**【請求項5】**

さらに前記制御回路が、前記出力ポート上の前記データ転送が完了するまで出力イネーブル信号が引き続きアクティブであることを要求するように構成される、請求項1から3のいずれか一項に記載の半導体メモリデバイス。 10

**【請求項6】**

クロック信号を受信するためのクロック入力ポートをさらに備える、

請求項1から3のいずれか一項に記載の半導体メモリデバイス。

**【請求項7】**

前記第1の制御入力ポート、前記第2の制御入力ポート、前記制御出力ポート、前記データ入力ポート、および前記データ出力ポートが、前記クロック信号と同期するように構成される、請求項6に記載の半導体メモリデバイス。

**【請求項8】**

前記制御回路が、ターゲットデバイスアドレスおよびコマンド命令が受信されるまで、

入力イネーブル信号が引き続きアクティブであることを要求するように構成される、請求

項1から3のいずれか一項に記載の半導体メモリデバイス。 20

**【請求項9】**

さらに前記制御回路が、選択された一つ以上の行アドレスおよび列アドレスが受信されるまで、入力イネーブル信号が引き続きアクティブであることを要求するように構成される、請求項8に記載の半導体メモリデバイス。

**【請求項10】**

命令をデータ入力ポートで受信するステップと、

前記メモリデバイスが前記命令を受信できるようにするために使用される、第1の入力イネーブル信号を第1の制御入力ポートで受信するステップと、

制御出力ポートから第2の入力イネーブル信号を出力するステップと、

出力イネーブル信号を第2の制御入力ポートで受信するステップと、

前記出力イネーブル信号に基づいて、出力データの出力を実行可能にするステップと、

データリンクインターフェースから出力データストリームを送信するステップと

を含む、半導体メモリデバイスにおいてデータリンクインターフェースからのデータ転送を制御する方法。 30

**【請求項11】**

前記データリンクインターフェースがシリアルデータリンクインターフェースであり、

前記出力データストリームがシリアル出力データストリームであり、前記方法が、

前記メモリデバイスのメモリと前記シリアルデータリンクインターフェースとの間でパラレルデータを転送するステップと、 40

前記シリアル出力データストリームを前記シリアルデータリンクインターフェースから送信するステップに先立って、前記パラレルデータをシリアル出力データに変換するステップと

をさらに含む、請求項10に記載の方法。

**【請求項12】**

i) 入力データを受信するためのデータ入力ポートと、ii) 出力データを出力するためのデータ出力ポートと、iii) 外部ソースデバイスから第1の出力イネーブル信号を受信するための第1の制御入力ポートと、iv) 前記メモリデバイスが前記入力データを受信できるようにするために使用される第1の入力イネーブル信号を受信するための第2の制御入力ポートと、v) 第2の出力イネーブル信号を出力するための第1の制御出力ポートと 50

、vi) 第2の出力イネーブル信号を出力するための第2の制御出力ポートと、を有する第1のフラッシュメモリデバイスと、

前記第1のフラッシュメモリデバイスに直列に接続されるとともに、データ入力ポートを有し、前記出力データを前記第1のフラッシュメモリデバイスから受信するように構成されている第2のフラッシュメモリデバイスと

を備え、

前記第1のフラッシュメモリデバイスが、出力データを前記第1の出力イネーブル信号に基づいて出力するように構成されている、フラッシュメモリシステム。

**【請求項13】**

前記第2のフラッシュメモリデバイスが、出力データを出力するように構成されたデータ出力ポートと、前記第1のフラッシュメモリデバイスの前記第1の制御出力ポートから前記第2の出力イネーブル信号を受信するように構成された制御入力ポートとをさらに含む、請求項12に記載のフラッシュメモリシステム。10

**【請求項14】**

前記データリンクインターフェースがシリアルデータリンクインターフェースであり、前記データ入力ポートがシリアルデータ入力ポートであり、前記データ出力ポートがシリアルデータ出力ポートである、請求項1または2に記載の半導体メモリデバイス。10

**【請求項15】**

前記入力データとの同期をとるためのクロック信号を受信するためのクロック入力ポートと、20

その他との同期をとるための出力クロック信号を出力するためのクロック入力ポートとをさらに備える、請求項1から3のいずれか一項に記載の半導体メモリデバイス。

**【請求項16】**

前記入力クロック信号と前記出力クロック信号との間のいかなる位相差にも同期するロッカルループをさらに備える、請求項15に記載の半導体メモリデバイス。20

**【請求項17】**

前記入力クロック信号と前記出力クロック信号との間のいかなる位相差にも同期する位相ロッカルループをさらに備える、請求項15に記載の半導体メモリデバイス。20

**【請求項18】**

前記メモリはフラッシュメモリである、請求項1から3のいずれか一項に記載の半導体メモリデバイス。30

**【請求項19】**

前記第2の出力イネーブル信号は、前記第1の出力イネーブル信号から得られる、請求項1または3に記載の半導体メモリデバイス。30

**【請求項20】**

前記受信された命令との同期をとるための入力クロック信号を受信するステップと、

その他との同期をとるための出力クロック信号を出力するステップと

をさらに含む、請求項10または11に記載の方法。

**【請求項21】**

前記半導体メモリデバイスは、ダブルデータレート動作で前記入力クロック信号を使用する、請求項20に記載の方法。40

**【請求項22】**

前記外部ソースデバイスは、メモリコントローラである、請求項12または13に記載のフラッシュメモリシステム。

**【請求項23】**

前記第2の出力イネーブル信号は、前記第1の出力イネーブル信号から得られる、請求項12または13に記載のフラッシュメモリシステム。40

**【請求項24】**

フラッシュメモリと、

クロック信号を受信するように構成されたクロック入力と、50

入力データおよびコマンドデータを異なる時間で受信するように構成されたコモン・コマンドおよびデータ入力と、

2つのイネーブル信号における第1信号を受信するように構成された第1の制御入力と、

前記2つのイネーブル信号における第2信号を受信するように構成された第2の制御入力と、

前記コマンドデータに対応してフラッシュメモリ上で動作を実行するように構成されたコア回路と、

ラッチ回路と

を備え、

10

前記ラッチ回路は、

前記2つのイネーブル信号における前記第1信号が少なくとも所定時間だけアクティブ論理レベルで保持されている間、前記コマンドデータをラッチするとともに、前記コマンドデータが前記コモン・コマンドおよびデータ入力で受信され、前記クロック信号の立ち上がりおよび立ち下がりエッジに同期して前記入力データをラッチするように構成されている、メモリデバイス。

#### 【請求項25】

前記2つのイネーブル信号における前記第1信号が少なくとも所定時間だけアクティブ論理レベルで保持されているときのみ、前記コマンドデータが前記コモン・コマンドおよびデータ入力で受信される、請求項24に記載のメモリデバイス。

20

#### 【請求項26】

前記2つのイネーブル信号における前記第1信号は、入力ポートイネーブル信号である、請求項24に記載のメモリデバイス。

#### 【請求項27】

前記2つのイネーブル信号における前記第2信号は、出力ポートイネーブル信号である、請求項24に記載のメモリデバイス。

#### 【請求項28】

前記動作は、消去動作である、請求項24に記載のメモリデバイス。

#### 【請求項29】

前記動作は、プログラム動作である、請求項24に記載のメモリデバイス。

30

#### 【請求項30】

前記コモン・コマンドおよびデータ入力は、シリアル入力である、請求項24に記載のメモリデバイス。

#### 【請求項31】

非アクティブ状態からアクティブ状態への前記2つのイネーブル信号における前記第1信号の遷移は、前記コマンドデータが前記コモン・コマンドおよびデータ入力で受信されることの開始を示す、請求項24に記載のメモリデバイス。

#### 【請求項32】

コントローラと、

請求項24に記載のメモリデバイスと

40

を備え、

前記メモリデバイスは、前記コントローラと通信可能に結合されている、システム。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、半導体メモリデバイスに関する。より詳細に言えば、本発明は、半導体フラッシュメモリデバイスの速度および/または容量を向上させるためのメモリアーキテクチャに関する。

##### 【背景技術】

##### 【0002】

50

デジタルカメラ、携帯情報端末、ポータブルオーディオ/ビデオプレーヤ、および携帯端末などの、移動体電子デバイスは、容量および速度機能が上昇の一途をたどる大容量記憶メモリ、好ましくは不揮発性メモリを、引き続き必要としている。たとえば、現在利用可能なオーディオプレーヤは、オーディオ/ビデオデータを格納するために、256Mバイトから40ギガバイトまでのメモリを有することができる。データは電源が入っていない時にも保持されるため、フラッシュメモリおよびハードディスクドライブなどの不揮発性メモリが好ましく、したがって、バッテリの寿命が延びる。

#### 【0003】

現在、ハードディスクドライブは、20から40ギガバイトのデータを格納できる高密度を有するが、比較的かさばる。しかしながら、ソリッドステートドライブとも呼ばれるフラッシュメモリは、ハードディスクドライブと比べた、その高密度、不揮発性、および小型サイズにより、人気が高い。フラッシュメモリ技術は、EPROMおよびEEPROM技術に基づくものである。「フラッシュ」という用語は、各バイトが個々に消去されるEEPROMと区別した場合、多数のメモリセルが一度に消去できることから選択された。マルチレベルセル(MLC)の出現により、シングルレベルセルに比べて、フラッシュメモリ密度がさらに増加している。当業者であれば、フラッシュメモリがNORフラッシュまたはNANDフラッシュとして構成可能であり、所与あたりの密度がより高いNANDフラッシュは、そのよりコンパクトなメモリアレイ構造によるものであることを理解されよう。以下の考察のために、フラッシュメモリへの言及は、NORまたはNAND、あるいは他のタイプのフラッシュメモリのいずれかであるものとして理解されたい。

#### 【0004】

既存のフラッシュメモリモジュールは、多くの現行の大衆消費電子デバイスにとっては十分な速度で動作するが、こうしたメモリモジュールは、高いデータレートが望ましい今後のデバイスでの使用には不適当となる可能性がある。たとえば、高精細度の動画を記録する携帯マルチメディアデバイスは、少なくともプログラミングスループットが10MB/秒のメモリモジュールを必要とする可能性があり、これは、典型的なプログラミングデータレートが7MB/秒の現在のフラッシュメモリ技術では得ることができない。マルチレベルセルフラッシュは、セルをプログラミングするために必要なマルチステッププログラミングシーケンスにより、これよりもかなり低レートの1.5MB/秒である。

#### 【0005】

フラッシュメモリのプログラミングおよび読み取りスループットは、フラッシュメモリの動作周波数を上げることによって、直接上げることができる。たとえば約20~30MHzのこの動作周波数を、約200MHzまで1桁上げることができる。この解決策は簡単であるように見えるが、こうした高周波数では信号品質にかなりの問題があり、フラッシュメモリの動作周波数に実際的な制限を設定する。特に、フラッシュメモリは、所望の構成に応じて8または16個の並列入力/出力(I/O)ピンのセットを使用して、コマンド命令を受け取り、入力データを受け取り、出力データを提供する、他の構成要素と通信する。これは一般に、パラレルインターフェースと呼ばれる。高速動作は、たとえば信号品質を劣化させる、クロストーク、信号スキュー、および信号減衰などの、よく知られた通信劣化効果の原因となる。

#### 【0006】

こうしたパラレルインターフェースは、多数のピンを使用してデータの読み取りおよび書き込みを行う。入力ピンおよびワイヤの数が増加するほど、望ましくない効果の数も増加する。これらの効果には、符号間干渉、信号スキュー、およびクロストークが含まれる。符号間干渉は、ワイヤに沿って移動する信号の減衰、および複数の要素がワイヤに接続される場合に発生する反射の結果として生じる。信号スキューは、信号が、異なる長さおよび/または特徴を有するワイヤに沿って移動し、異なる時点でエンドポイントに到達する場合に生じる。クロストークは、ごく接近しているワイヤ上の信号の望ましくない結合を言い表す。クロストークは、メモリデバイスの動作速度が上昇するに連れて、より大きな問題となる。

10

20

30

40

50

**【発明の開示】****【発明が解決しようとする課題】****【0007】**

したがって、当技術分野では、携帯電子デバイスで使用するためのメモリモジュールと、メモリモジュールへのアクセスに必要な入力ピンおよびワイヤの数を最小限にしながら、メモリ容量および/または動作速度を増加した、ソリッドステートドライブの適用例が求められている。

**【課題を解決するための手段】****【0008】**

次に、本発明の様々な態様について基本的に理解するために、本発明のいくつかの実施形態についての簡単な概要を示す。この概要是、本発明の広範囲に及ぶ概略ではない。本発明の主要なまたは不可欠な要素を識別すること、あるいは本発明の範囲を線引きすることを意図するものではない。その唯一の目的は、本発明のいくつかの実施形態を、以下に示されるより詳細な説明の前置きとして簡略化された形で示すことである。10

**【0009】**

本発明の実施形態によれば、半導体メモリデバイスは、メモリ、シリアル入力データをメモリに転送するシリアルデータリンク、および入力制御信号を含む。制御回路は、シリアルデータリンクインターフェースとメモリとの間のデータ転送を制御する。本発明の原理に従って、メモリは、単一のメモリバンクまたは複数のメモリバンクとすることができます。シリアルデータリンクインターフェースは、シリアル入力データを、メモリバンクに転送されることになるパラレルデータに変換することができます。加えて、シリアルリンクインターフェースは、メモリバンクからシリアル出力データへと、パラレルデータを変換することができます。本明細書全体を通じて、本発明の様々な他の態様も開示される。20

**【0010】**

本発明の諸原理によれば、フラッシュメモリシステムは、複数の直列に接続されたフラッシュメモリデバイスを有することができる。システム内のフラッシュメモリデバイスは、シリアル入力データポート、シリアルデータ出力ポート、複数の制御入力ポート、および複数の制御出力ポートを含む。フラッシュメモリデバイスは、シリアル入力データおよび制御信号を外部ソースから受け取るように、ならびにデータおよび制御信号を外部デバイスに提供するように、構成される。外部ソースおよび外部デバイスは、システム内の他のフラッシュメモリデバイスとすることができます。本発明の一部の実施形態では、フラッシュメモリデバイスは、それぞれ固有のデバイス識別子を含むことができる。デバイスは、ターゲットデバイス情報をデバイスの固有デバイス識別番号と相關させて、デバイスがターゲットデバイスであるかどうかを判別するために、シリアル入力データ内のターゲットデバイス情報フィールドを解析するように構成することができる。デバイスは、いずれかの追加の入力データを受け取るのに先立って、ターゲットデバイス情報フィールドを解析することができる。メモリデバイスがターゲットデバイスでない場合、シリアル入力データを無視するため、追加の処理時間およびリソースを節約することになる。30

**【0011】**

本発明の諸実施形態によれば、メモリデバイスおよび方法は、シリアル入力および出力ピン、SIP(シリアル入力ポート)およびSOP(シリアル出力ポート)の單一セットを、ならびに、それぞれ入力/出力ポートのイネーブル/ディスエーブルのための2つの制御信号、IPE(入力ポートイネーブル)およびOPE(出力ポートイネーブル)と共に、完全に直列化する。これにより、メモリコントローラにデータ通信の最大の柔軟性を与える。本発明のメモリデバイスは、IPEが「高」論理状態にある場合にのみ、そのSIPポートを介して情報信号ストリームを受信し、さらにデバイスは、OPEが「高」論理状態にある場合にのみ、そのSOPポートを介して出力データ信号ストリームを送信する。IPEが「高」になり、自走シリアルクロック信号(SCLK)の立ち上がりで参照されると、SIPポートは、各動作ケースについて所定数のクロックサイクルで、デバイスアドレスバイト、コマンドバイト、列アドレス40

バイト、行アドレスバイト、および/または入力データバイトである、連続するシリアル入力ストリームバイトの受信を開始する。IPEが「低」状態になると、SIPポートは入力信号ストリーミングバイトの受信を停止する。OPE信号が「高」状態になると、SOPポートは、自走シリアルクロック信号(SCLK)の立ち上がりで参照されたデータの出力を開始する。OPEが「低」状態になると、SOPはデータの出力を停止する。したがってメモリコントローラは、メモリデバイスとコントローラ自身との間の通信を制御する上でより柔軟性を持つことができる。

【 0 0 1 2 】

加えてデバイスは、システム内で直列にカスケードされる場合、受信したIPEおよびOPE信号を外部デバイスに「エコー出力」する出力制御ポートをさらに備えることができる。これによりシステムは、デイジーチェーンカスケーディング方式(対ブロードキャスティング/マルチドロップカスケーディング方式)を形成するために、2地点間接続された信号ポート(たとえば、SIP/SOP、IPE/IPEQ、OPE/OPEQ、SCLK1/SCLK0)を有することができる。これらのシステムは、制限されたハードウェア物理デバイス選択ピンを使用するのではなく、固有のデバイス識別およびターゲットデバイス選択アドレス方式を使用することが可能であるため、システムの全体性能を犠牲にすることなく、メモリ密度に関してシステム全体を容易に可能な限り拡張することができる。

【 0 0 1 3 】

本発明は、同じ参照番号が同様の要素を示す添付の図面において、限定的ではなく、単なる例として示される。

## 【発明を実施するための最良の形態】

【 0 0 1 4 】

半導体メモリ用のシリアルデータインターフェースが開示される。シリアルデータインターフェースは、中央集中制御論理と通信する、1つまたは複数のシリアルデータリンクを含むことが可能であり、各シリアルデータリンクはコマンドおよびデータを逐次受信することが可能であり、出力データを逐次提供することが可能である。各シリアルデータリンクは、データのプログラミングおよび読み取りのために、メモリ内の任意のメモリバンクにアクセスすることができる。シリアルインターフェースの少なくとも1つの利点は、密度間で同じ標準ピン配列を備えた低ピンカウントデバイスであり、その結果、ボードを設計変更せずに、将来、より高い密度への適合アップグレードが可能になる。

【 0 0 1 5 】

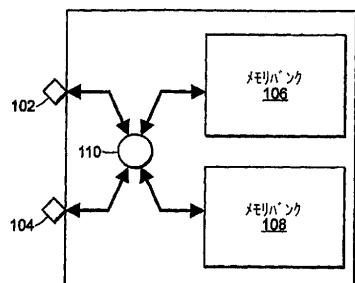

図1Aおよび1Bは、本発明の様々な態様に従った、同時動作をサポートする例示的なメモリデバイスを示す高水準図である。図1Aは、複数のシリアルデータリンクインターフェース102および104ならびに複数のメモリバンク106および108を有する、メモリデバイスを示す。現在示されている配置構成は、本明細書ではデュアルポート構成と呼ばれる。各シリアルデータリンクインターフェースは、関連する入力/出力ピンと、データ入力およびデータ出力回路とを有し、これについては図2Aに関してさらに詳細に説明する。シリアルデータリンクインターフェースを介して転送されるデータは、シリアル様式で(たとえば、データの単一ビット幅ストリームとして)通過する。メモリデバイス内のデータリンクインターフェース102および104はそれぞれ独立しており、メモリバンク106および108のいずれかと、データ転送をやりとりすることができる。たとえば、シリアルデータリンク102は、メモリバンク106またはメモリバンク108とデータ転送をやりとりすることができる。同様に、シリアルデータリンク104は、メモリバンク106およびメモリバンク108とデータ転送をやりとりすることができる。図示されたこの2つのシリアルデータリンクインターフェースは独立しているため、別々のメモリバンクとのデータ転送を同時にやりとりすることができる。本明細書で使用されるリンクとは、1つまたは複数のメモリバンクとのデータのやりとりのためのパスを提供し、これらとのデータ転送のやりとりを制御する、回路を言い表すものである。制御モジュール110は、各シリアルデータリンクインターフェース102および104と各メモリバンク106および108との間でのデータの交換を制御するためのコマンドで構成可能である。たとえば制御モジュール110は、シリアルデータリンク1

ンターフェース104がメモリバンク108にデータを書き込んでいるのと同時に、シリアルデータリンクインターフェース102がメモリバンク106からデータを読み取ることができるよう構成することができる。この機能により、システム設計の柔軟性が向上し、デバイスの使用率(たとえばバス使用率およびコア使用率)が向上する。後で示すように、制御モジュール110は、制御回路、レジスタ、および交換回路を含むことができる。

#### 【0016】

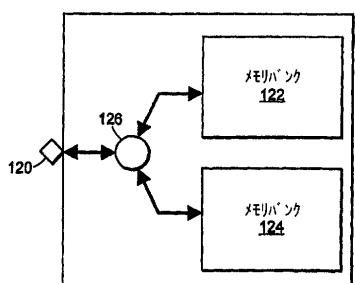

図1Bは、単一のシリアルデータリンクインターフェース120が制御モジュール126を介して複数のメモリバンク122および124にリンクされる、実施形態を示す。ここで示された配置構成は、本明細書では单一ポート構成と呼ばれ、図1Aで示されたデュアルポート構成よりは少ないメモリデバイス入力/出力ピンを利用する。制御モジュール126は、2つの動作プロセスまたはスレッドを実施または実行するように構成されるため、シリアルデータリンクインターフェース120は、メモリバンク122および124とパイプライン様式でデータを交換することができる。たとえば、データがメモリバンク122に書き込まれている間に、データリンクインターフェース120はメモリバンク124からデータを読み取ることができる。本発明の様々な態様によれば、また以下でより詳細に説明されるように、メモリデバイスは、図1Bに示された單一リンク構成を使用して複数のリンク動作をエミュレートする。この單一リンクを、本明細書では仮想多重リンクとも呼ばれる複数バンク構成と共に使用して、他のバンクがビジー状態の可能性がある間に、任意の使用可能なバンクにアクセスすることができる。結果として、メモリデバイスは、リンクアービトレーション回路を介して他の使用可能バンクにアクセスすることにより、單一リンク構成の使用率向上を達成することができる。

#### 【0017】

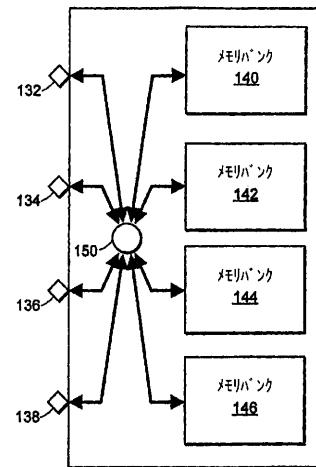

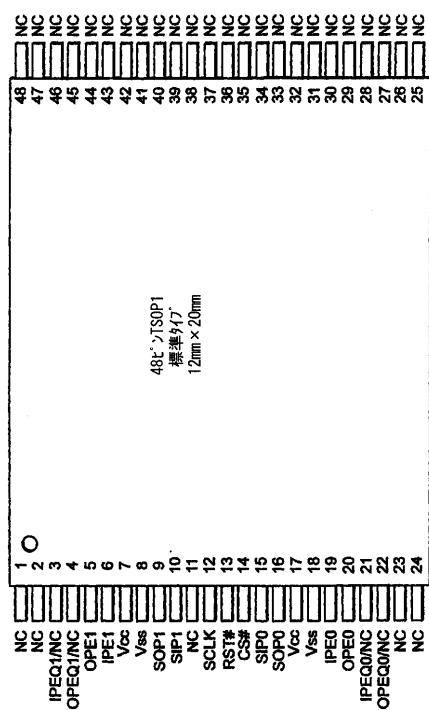

図1Aおよび1Bに示されたメモリデバイスは、単なる例示の目的で、2つのメモリバンクを含む。当業者であれば、本明細書に開示された本発明のいくつかの態様がスケーラブルであり、複数のメモリバンクおよび複数のシリアルデータリンクインターフェースの使用が可能であることを理解されよう。單一メモリデバイスは、たとえば2、4、またはそれ以上のメモリバンクを含むことができる。図1Cは、4つの独立したシリアルデータリンク132、134、136、および138が、制御モジュール150の制御の下で4つのメモリバンク140、142、144、および146とデータを交換するように構成された、実施形態を示す。仮想多重リンク構成を使用した場合、1つのリンクのみが必要であるため、残りのリンク(たとえば、図1Aのデュアルリンクまたは図1Cのクワッドリンクピン配列構成)は使用されず、NC(すなわち接続なし)とみなすことができる。従来のパラレルインターフェース構造と比較したシリアルデータリンクインターフェースの少なくとも1つの利点は、リンクの柔軟性および高密度が維持されながら、メモリデバイス上のピンの数が削減されることである。たとえば、従来のフラッシュメモリデバイスは、パッケージの複数の面全体にわたる48のピンが必要な可能性があるが、本発明の諸態様に従ったメモリデバイスは、図11に示されるように、標準パッケージ1100の單一面のより少ないピン(たとえば11ピン)を使用することができる。別の方法として、代わりに、必要な内部接着パッドが少ないと、異なる、より小さいタイプのパッケージを使用することができる。

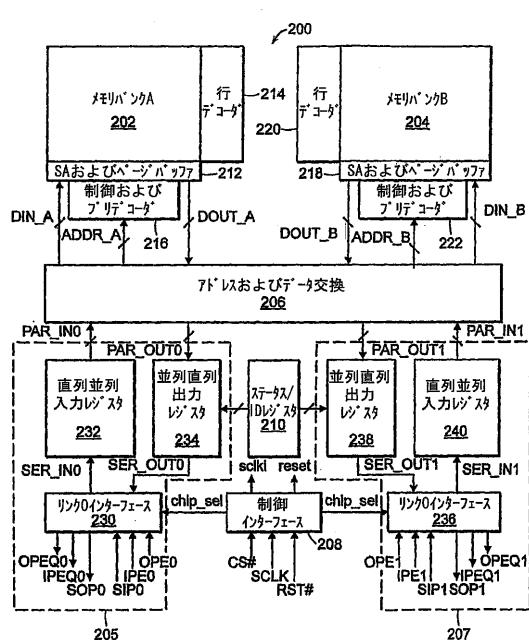

#### 【0018】

図2Aは、本発明の一実施形態に従った、図1Aに示されたメモリデバイスのより詳細な概略図を示す。メモリデバイス200内の各メモリバンクのアーキテクチャは、NANDフラッシュメモリコアアーキテクチャと同一または同様とすることができます。図2Aは本発明に関連する回路を示し、図2Aを簡略化するためにある特定の回路ブロックを意図的に省略している。たとえば、フラッシュメモリコアアーキテクチャと共に実施されたメモリデバイス200は、メモリセルのプログラミングおよび消去に必要な高電圧発生器回路を含むことになる。本明細書で使用されるコアアーキテクチャ(またはコア回路)は、メモリセルアレイ、ならびにデコードおよびデータ転送回路などの関連するアクセス回路を含む、回路のことを言い表す。標準的なメモリアーキテクチャはよく知られているため、選択されたアーキテクチャに関連付けられた固有の動作も同様であり、当業者であれば誰でも理解している

10

20

30

40

50

はずである。さらに当業者であれば、任意の知られた不揮発性または揮発性メモリーアーキテクチャが本発明の代替実施形態で使用可能であることも理解されよう。

#### 【0019】

メモリデバイス200は、メモリバンクA 202およびメモリバンクB 204などの、それそれぞれのデータ、制御、およびアドレス指定の回路を備えた多数の同一のメモリバンク、メモリバンク202および204の両方に接続されたアドレスおよびデータバス交換回路206、ならびに、交換回路206にデータを提供するため、およびこれからデータを受信するために、それぞれのメモリバンクに関連付けられた、同一のインターフェース回路205および207を含む。メモリバンク202および204は、好ましくは、たとえばフラッシュメモリなどの不揮発性メモリである。論理的には、メモリバンク202によって受信および提供される信号は文字「A」で指定され、メモリバンク204によって受信および提供される信号は文字「B」で指定される。同様に、インターフェース回路205によって受信および提供される信号は数字「0」で指定され、インターフェース回路207によって受信および提供される信号は数字「1」で指定される。各インターフェース回路205/207は、シリアルデータストリーム内のアクセスデータを受信し、アクセスデータは、たとえばプログラミング動作に関する、コマンド、アドレス情報、および入力データを含むことができる。読み取り動作では、インターフェース回路は、読み取りコマンドおよびアドレスデータに応答して、シリアルデータストリームとして出力データを提供することになる。メモリデバイス200は、メモリバンク202および204の両方の回路ならびにそれぞれのインターフェース回路205および207に、クロック信号sclk<sub>i</sub>およびresetなどのグローバル信号を提供する、制御インターフェース208およびステータス/IDレジスタ回路210などの、グローバル回路をさらに含む。

次に、前述の回路について詳細に論じる。

#### 【0020】

メモリバンク202は、出力データDOUT\_Aを提供するため、および入力プログラムデータDIN\_Aを受信するための、センス増幅器およびページバッファ回路ブロック212、ならびに行デコーダブロック214などの、よく知られたメモリ周辺回路を含む。当業者であれば、ブロック212が列デコーダ回路も含むことになることを理解されよう。制御およびプリデコーダ回路ブロック216は、信号回線ADDR\_Aを介してアドレス信号および制御信号を受信し、プリデコード済みアドレス信号を、行デコーダ214ならびにセンス増幅器およびページバッファ回路ブロック212に提供する。

#### 【0021】

メモリバンク204に関する周辺回路は、メモリバンク202に関して前述したものと同一である。メモリバンクBの回路は、出力データDOUT\_Bを提供するため、および入力プログラムデータDIN\_Bを受信するための、センス増幅器およびページバッファ回路ブロック218、行デコーダブロック220、ならびに制御およびプリデコーダ回路ブロック222を含む。制御およびプリデコーダ回路ブロック222は、信号回線ADDR\_Bを介してアドレス信号および制御信号を受信し、プリデコード済みアドレス信号を、行デコーダ2220ならびにセンス増幅器およびページバッファ回路ブロック222に提供する。各メモリバンクおよびその対応する周辺回路は、よく知られたアーキテクチャで構成可能である。

#### 【0022】

一般的な動作では、各メモリバンクは、特定のコマンドおよびアドレス、ならびに必要であれば入力データに応答する。たとえばメモリバンク202は、読み取りコマンドおよび読み取りアドレスに応答して出力データDOUT\_Aを提供することになり、プログラムコマンドおよびプログラムアドレスに応答して入力データをプログラミングすることができる。各メモリバンクは、たとえば消去コマンドなどの他のコマンドにも応答可能である。

#### 【0023】

現在示されている実施形態では、バス交換206は、メモリバンク202および204とインターフェース回路205および207との間で信号を渡すために、2つのモードのうちの1つで動作可能な、デュアルポート回路である。第1のモードは、メモリバンク202およびインターフェース回路205の信号が互いに渡される、直接転送モードである。同時に、メモリバンク2

10

20

30

40

50

04およびインターフェース回路207の信号が、直接転送モードで互いに渡される。第2のモードは、メモリバンク202およびインターフェース回路207の信号が互いに渡される、クロス転送モードである。同時に、メモリバンク204およびインターフェース回路205の信号が、互いに渡される。パス交換206の単一ポート構成については、後述する。

#### 【 0 0 2 4 】

前述のように、インターフェース回路205および207は、シリアルデータストリームとしてデータを送受信する。これは、チップのピン配列要件を減少させるため、ならびに高動作周波数での全体信号スループットを増加させるためである。メモリバンク202および204の回路は、通常、パラレルアドレスおよびデータ用に構成されるため、変換回路が必要である。

10

#### 【 0 0 2 5 】

インターフェース回路205は、シリアルデータリンク230、直列並列入力レジスタプロック232、および並列直列出力レジスタプロック234を含む。シリアルデータリンク230は、シリアル入力データSIP0、入力イネーブル信号IPE0、および出力イネーブル信号OPE0を受け取り、シリアル出力データSOP0、入力イネーブルエコー信号IPEQ0、および出力イネーブルエコー信号OPEQ0を提供する。信号SIP0および(SIP1)は、それぞれ、アドレス、コマンド、および入力データを含むことが可能な、シリアルデータストリームである。シリアルデータリンク230は、SIP0に対応するバッファリング済みシリアル入力データSER\_IN0を提供し、並列直列出力レジスタプロック234からシリアル出力データSER\_OUT0を受け取る。直列並列入力レジスタプロック232は、SER\_IN0を受け取り、これを信号PAR\_IN0の並列セットに変換する。並列直列出力レジスタプロック234は、出力データPAR\_OUT0の並列セットを受け取り、これを直列出力データSER\_OUT0に変換し、その後これは、データストリームSOP0として提供される。並列直列出力レジスタプロック234は、PAR\_OUT0データの代わりに、ステータス/IDレジスタ回路210の内部に格納されたデータを出力するために、ステータス/IDレジスタ回路210からデータを受信することも可能である。この特定の機能についての詳細は、後述する。さらに、シリアルデータリンク230は、制御信号およびデータ信号と他のメモリデバイス200とのデイジーチェーンカスケーディングに対処するようにも構成される。

20

#### 【 0 0 2 6 】

シリアルインターフェース回路207は、インターフェース回路205と同一に構成され、シリアルデータリンク236、直列並列入力レジスタプロック240、および並列直列出力レジスタプロック238を含む。シリアルデータリンク236は、シリアル入力データSIP1、入力イネーブル信号IPE1、および出力イネーブル信号OPE1を受け取り、シリアル出力データSOP1、入力イネーブルエコー信号IPEQ1、および出力イネーブルエコー信号OPEQ1を提供する。シリアルデータリンク236は、SIP1に対応するバッファリング済みシリアル入力データSER\_IN1を提供し、並列直列出力レジスタプロック238からシリアル出力データSER\_OUT1を受け取る。直列並列入力レジスタプロック240はSER\_IN1を受け取り、これを信号PAR\_IN1の並列セットに変換する。並列直列出力レジスタプロック238は、出力データPAR\_OUT1の並列セットを受け取り、これを直列出力データSER\_OUT1に変換し、その後これは、データストリームSOP1として提供される。並列直列出力レジスタプロック238は、PAR\_OUT1データの代わりに、ステータス/IDレジスタ回路210の内部に格納されたデータを出力するために、ステータス/IDレジスタ回路210からデータを受信することも可能である。シリアルデータリンク230の場合と同様に、シリアルデータリンク236は、制御信号およびデータ信号と他のメモリデバイス200とのデイジーチェーンカスケーディングに対処するように構成される。

30

#### 【 0 0 2 7 】

制御インターフェース208は、標準入力バッファ回路を含み、それぞれCS#、SCLK、およびRST#に対応する、内部チップ選択信号chip\_sel、内部クロック信号sclk\_i、および内部リセット信号resetを生成する。信号chip\_selは、主にシリアルデータリンク230および236によって使用されるが、resetおよびsclk\_iはメモリデバイス200全体にわたる多くの回路

40

50

によって使用される。

【0028】

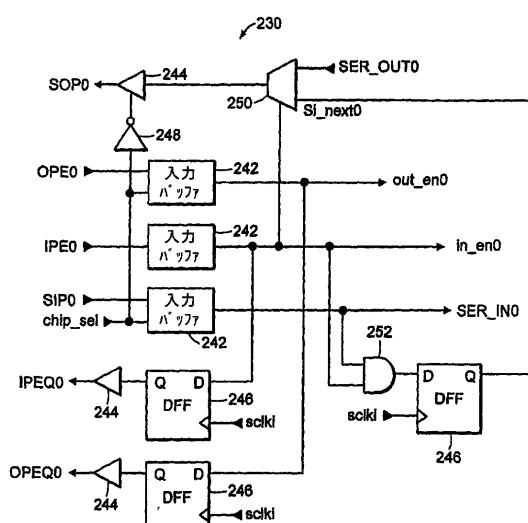

図2Bは、本発明の実施形態に従ったシリアルデータリンク230を示す概略図である。シリアルデータリンク230は、入力信号OPE0、IPE0、およびSIP0を受け取るための入力バッファ242、信号SOP0、IPEQ0、およびOPEQ0を駆動するための出力ドライバ244、信号out\_en0およびin\_en0をクロックアウトするためのフリップフロップ回路246、インバータ248、ならびにマルチプレクサ(MUX)250を含む。信号OPE0およびSIP0用の入力バッファは、chip\_selに応答して実行可能となり、信号SOP0用の出力ドライバは、インバータ248を介して反転済みchip\_selに応答して実行可能となる。信号out\_en0は、図2Eで示される、出力バッファを実行可能とし、信号SER\_OUT0を提供する。信号in\_en0はSER\_IN0データをラッチするように直列並列入力レジスタブロック232を実行可能とする。信号in\_en0、out\_en0、およびSER\_IN0。10

【0029】

シリアルデータリンク230は、メモリデバイス200と他のメモリデバイスとのデイジーチェーンカスケーディングを実行可能にするための回路を含む。より具体的に言えば、シリアル入力データストリームSIP0、ならびにイネーブル信号OPE0およびIPE0は、シリアルデータリンク230を介して他のメモリデバイスの対応するピンへと渡すことができる。SER\_IN0は、AND論理ゲート252によって受信され、in\_en0がアクティブな高論理レベルにある場合、その対応するフリップフロップ246へと渡される。同時に、アクティブな高論理レベルにあるin\_en0は、Si\_next0を出力ドライバ244に渡すように、MUX 250を制御することになる。同様に、IPE0およびOPE0は、それぞれのフリップフロップ246を介して、IPEQ0およびOPEQ0にクロックアウトすることができる。シリアルデータリンク230について論じてきたが、シリアルデータリンク236が同じ構成要素を含み、これらが図2Bのシリアルデータリンク230と同じ方法で相互に接続されることを理解されよう。20

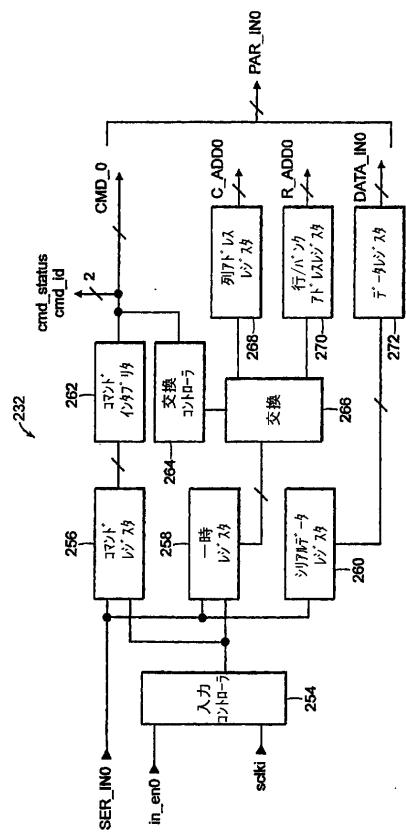

【0030】

図2Cは、直列並列入力レジスタブロック232を示す概略図である。このブロックは、クロック信号sclk\_i、イネーブル信号in\_en0、および入力データストリームSER\_IN0を受け取り、SER\_IN0をデータの並列グループに変換する。特に、SER\_IN0は、コマンドCMD\_0、列アドレスC\_ADD0、行アドレスR\_ADD0、および入力データDATA\_IN0を提供するように変換することができる。現在開示されている本発明の実施形態は、好ましくは、たとえば200MHzなどの高周波数で動作する。この速度では、シリアル入力データストリームは、受信されたコマンドをデコードできるよりも速い速度で受信することができる。これは、シリアル入力データストリームが、初期にレジスタセットにバッファリングされるためである。現在示されている概略図が直列並列入力レジスタブロック240にも適用され、唯一の相違点は信号名の指定子であることを理解されたい。30

【0031】

直列並列入力レジスタブロック232は、in\_en0およびsclk\_iを受け取るための入力コントローラ254、コマンドレジスタ256、一時レジスタ258、ならびにシリアルデータレジスタ260を含む。シリアル入力データストリームのデータ構造は事前に決定されるため、特定ビット数の入力データストリームを前述のレジスタに配布することができる。たとえば、コマンドに対応するビットをコマンドレジスタ256に格納することが可能であり、行および列アドレスに対応するビットを一時レジスタ258に格納することが可能であり、入力データに対応するビットをシリアルデータレジスタ260に格納することができる。シリアル入力データストリームのビットの配布は、各所定数のビットが受信された後に制御信号を実行可能にする適切なレジスタを生成するためのカウンタを含むことができる、入力コントローラ254によって制御可能である。言い換えれば、3つのレジスタそれぞれを、シリアル入力データストリームの所定のデータ構造に従って、シリアル入力データストリームのデータビットを受信および格納するように、順番に実行可能にすることができる。40

【0032】

コマンドインタプリタ262は、コマンドレジスタ256から並列にコマンド信号を受信し、50

デコード済みコマンドCMD\_0を生成する。コマンドインタプリタ262は、受信したコマンドをデコードするための、相互接続された論理ゲートまたはファームウェアによって実施される標準回路である。図2Cに示されるように、CMD\_0は信号cmd\_statusおよびcmd\_idを含むことができる。交換コントローラ264は、単純な交換回路266を制御するために、CMD\_0から1つまたは複数の信号を受け取る。交換回路266は、一時レジスタ258に格納されたすべてのデータを並列に受信し、デコード済みコマンドCMD\_0に従って、列アドレスレジスタ268および行/バンクレジスタ270のうちの1つまたは両方にデータをロードする。このデータコーディングは、好ましくは、一時レジスタが常に列および行/バンクの両方のアドレスデータを含むとは限らないために、実行される。たとえば、ブロック消去コマンドを有するシリアル入力データストリームは、行アドレスのみを使うことになり、この場合、一時レジスタ258に格納された関連ビットのみが行/バンクレジスタ270にロードされる。プログラミング動作のために、列アドレスレジスタ268はパラレル信号C\_ADD0を提供し、行/バンクアドレスレジスタ270はパラレル信号R\_ADD0を提供し、データレジスタ272はパラレル信号DATA\_IN0を提供する。CMD\_0、C\_ADD0、R\_ADD0、およびDATA\_IN0(オプション)はまとめてパラレル信号PAR\_IN0を形成する。各パラレル信号の所望のビット幅は、カスタマイズ可能であるか、または特定の標準を遵守するように調整可能な、設計パラメータであるため、この幅は指定されていない。

#### 【 0 0 3 3 】

フラッシュコアアーキテクチャ実施に関するメモリデバイス200のいくつかの動作の例が、以下の表1に示される。表1は、CMD\_0に関する可能なOP(動作)コード、ならびに、列アドレス(C\_ADD0)、行/バンクアドレス(R\_ADD0)、および入力データ(DATA\_IN0)の対応する状態を列挙する。

#### 【 0 0 3 4 】

10

20

【表1】

| 動作                | OPコード<br>(1バイト) | 列アドレス<br>(2バイト) | 行/バンク<br>アドレス<br>(3バイト) | 入力データ<br>(1バイトから<br>2112バイト) |

|-------------------|-----------------|-----------------|-------------------------|------------------------------|

| ページ読み取り           | 00h             | 有効              | 有効                      | -                            |

| ランダムデータ読み取り       | 05h             | 有効              | -                       | -                            |

| コピー用のページ読み取り      | 35h             | -               | 有効                      | -                            |

| コピー用のターゲットアドレス入力  | 8Fh             | -               | 有効                      | -                            |

| シリアルデータ入力         | 80h             | 有効              | 有効                      | 有効                           |

| ランダムデータ入力         | 85h             | 有効              | -                       | 有効                           |

| ページプログラミング        | 10h             | -               | -                       | -                            |

| ロック消去             | 60h             | -               | 有効                      | -                            |

| ステータス読み取り         | 70h             | -               | -                       | -                            |

| ID読み取り            | 90h             | -               | -                       | -                            |

| 構成レジスタ書き込み        | A0h             | -               | -                       | 有効(1バイト)                     |

| DN(デバイス名)エントリ書き込み | B0h             | -               | -                       | -                            |

| リセット              | FFh             | -               | -                       | -                            |

| バンク選択             | 20h             | -               | 有効(バンク)                 | -                            |

10

20

30

表1: コマンドセット

## 【0035】

さらに、表2は、入力データストリーム内の好ましい入力シーケンスを示す。コマンド、アドレス、およびデータは、最上位ビットから始まり、逐次、メモリデバイス200へシフトインおよびメモリデバイス200からシフトアウトされる。コマンドシーケンスは1バイトコマンドコード(表2の「cmd」)から始まる。コマンドにより、1バイトコマンドコードの後には、列アドレスバイト(表2の「ca」)、行アドレスバイト(表2の「ra」)、バンクアドレスバイト(表2の「ba」)、データバイト(表2の「data」)、ならびに/あるいは、組み合わせまたは無しが続く場合がある。

## 【0036】

【表2】

| 動作               | 第1バイト | 第2バイト | 第3バイト | 第4バイト | 第5バイト | 第6バイト | 第7バイト | ... | 第2115バイト | ... | 第2118バイト |

|------------------|-------|-------|-------|-------|-------|-------|-------|-----|----------|-----|----------|

| ページ読み取り          | cmd   | ca    | Ca    | ba/ra | ra    | ra    | -     | -   | -        | -   | -        |

| ランダムデータ読み取り      | cmd   | ca    | Ca    | -     | -     | -     | -     | -   | -        | -   | -        |

| コピー用のページ読み取り     | cmd   | ba/ra | Ra    | ra    | -     | -     | -     | -   | -        | -   | -        |

| コピー用のターゲットアドレス入力 | cmd   | ba/ra | Ra    | ra    | -     | -     | -     | -   | -        | -   | -        |

| シリアルデータ入力        | cmd   | ca    | Ca    | ba/ra | ra    | ra    | data  | ... | data     | ... | data     |

| ランダムデータ入力        | cmd   | ca    | Ca    | data  | data  | data  | data  | ... | data     | -   | -        |

| ページプログラミング       | cmd   | -     | -     | -     | -     | -     | -     | -   | -        | -   | -        |

| ブロック消去           | cmd   | ba/ra | Ra    | ra    | -     | -     | -     | -   | -        | -   | -        |

| ステータス読み取り        | cmd   | -     | -     | -     | -     | -     | -     | -   | -        | -   | -        |

| ID読み取り           | cmd   | -     | -     | -     | -     | -     | -     | -   | -        | -   | -        |

| 構成レジスタ書き込み       | cmd   | data  | -     | -     | -     | -     | -     | -   | -        | -   | -        |

| DNエントリ書き込み       | cmd   | -     | -     | -     | -     | -     | -     | -   | -        | -   | -        |

| リセット             | cmd   | -     | -     | -     | -     | -     | -     | -   | -        | -   | -        |

| バンク選択            | cmd   | ba    | -     | -     | -     | -     | -     | -   | -        | -   | -        |

表2: バイトモードでの入力シーケンス

## 【0037】

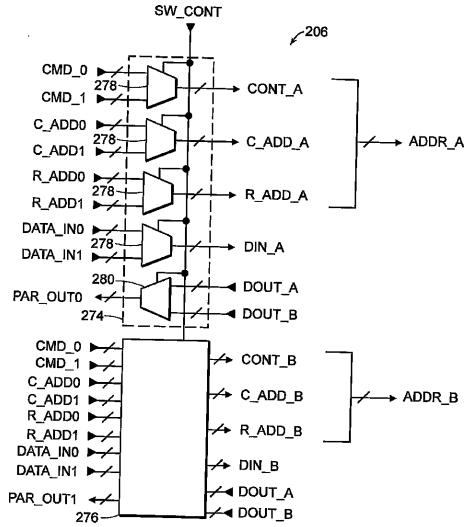

図2Dは、図2Aに示されたバス交換206を示す概略図である。交換206は、論理的には同一に構成された2つの交換サブ回路274および276に分割される。交換サブ回路274は、インターフェース回路205またはインターフェース回路207のいずれかのコマンド、アドレス、および入力データを、メモリバンク202の回路に選択的に渡す、4つの入力マルチプレクサ278を含む。これらの信号については、図2Cで、例によってPAR\_IN0としてすでにグループ化されている。交換サブ回路274は、メモリバンク202またはメモリバンク204のいずれかからの出力データを、インターフェース回路205に選択的に渡すための、1つの出力マルチプレクサ280を含む。交換サブ回路276は、インターフェース回路205またはインターフェース回路207のいずれかのコマンド、アドレス、および入力データを、メモリバンク204の回路に選択的に渡す、4つの入力マルチプレクサ(図示せず)を含む。交換サブ回路276は、メモリバンク202またはメモリバンク204のいずれかからの出力データを、インターフェース回路207に選択的に渡すための、1つの出力マルチプレクサ(図示せず)を含む。

## 【0038】

交換サブ回路274および276はどちらも、交換制御信号SW\_CONTの状態に応じて、直接転送モードまたはクロス転送モードで同時に動作可能である。バス交換回路206は、現在デ

10

20

30

40

50

ユアルポート構成で示されており、これは、インターフェース回路205および207のいずれかを介してメモリバンク202および204の両方に同時にアクセス可能なことを意味する。

#### 【0039】

本発明の他の実施形態によれば、以前に図1Bで示したように、パス交換206は、インターフェース回路205および207のうちの1つのみがアクティブな単一ポートモードで動作可能である。さらにこの構成は、未使用的インターフェース回路に関連付けられた入力/出力パッドがもはや不要であるため、メモリデバイス200のピン配列領域要件を削減することができる。単一ポート構成では、交換サブ回路274および276が直接転送モードでのみ動作するように設定されるが、依然としてSW\_CONT選択信号に応答可能なそれぞれの出力マルチプレクサ280は例外である。

10

#### 【0040】

インターフェース回路205のみがアクティブな単一ポート実施形態では、交換266およびシリアルデータレジスタ260の出力からのデータを、対応する直列並列入力レジスタブロック232または240のいずれかの列、行/バンク、およびデータのレジスタに選択的に渡すために、補助バス交換(図示せず)が、並列直列入力レジスタブロック232(またはブロック234)に含まれる。事実上、補助バス交換は交換206と同様とすることができる。したがって、直列並列入力レジスタブロック232および240の両方の、列、行/バンク、およびデータレジスタに、代替メモリバンクアクセスまたはほぼ同時アクセスのためのデータを、ロードすることができる。

#### 【0041】

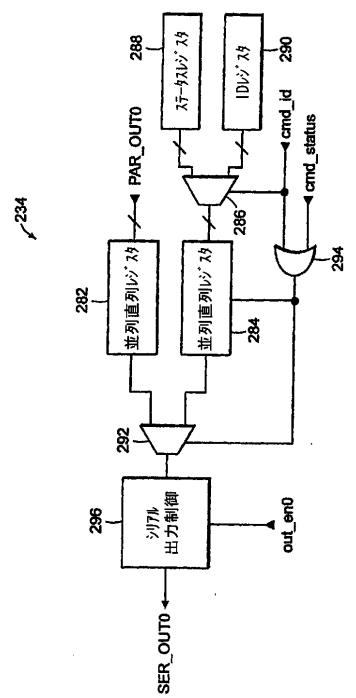

図2Eは、並列直列出力レジスタブロック234を示す概略図である。並列直列出力レジスタブロック238が同一に構成されることに留意されたい。並列直列出力レジスタブロック234は、メモリバンクからアクセスされたデータ、またはあらかじめレジスタに格納されたステータスデータの、いずれかを提供する。より具体的に言えば、ユーザまたはシステムは、シリアルデータリンク230または236のいずれかのステータスを要求することができる。出力されたステータスデータ内の指定ビット位置(たとえばビット4)の値「1」は、特定のシリアルデータリンクインターフェースがビジーであることを示すことができる。固定データは、ステータスデータと共に、メモリデバイス200の電源投入時にデフォルト状態でどちらもプリロード可能な、チップ識別データをさらに含むことができる。ステータスデータは、システムによって認識可能な任意の事前に選択されたビットパターンを有するように構成可能である。図示されていないが、図2Eは、レジスタ284内に格納された1つまたは複数のビットを、1つまたは複数の所定の条件に基づいて更新するための、追加の制御回路を含むことができる。たとえば、1つまたは複数のステータスピットを、経過したクロックサイクルのカウントに基づいて、あるいはメモリデバイス200の様々な回路ブロックから受け取った1つまたは複数のフラグ信号の組み合わせに基づいて、変更することができる。

20

#### 【0042】

並列直列出力レジスタブロック234は、パス交換206から出力データPAR\_OUT0を受け取るための第1の並列直列レジスタ282、マルチプレクサ286から固定データを受け取るための第2の並列直列レジスタ284を含む。マルチプレクサ286は、信号cmd\_idに応答して、ステータスレジスタ288に格納されたステータスデータ、またはIDレジスタ290に格納されたチップ識別データのうちの1つを、選択的に渡す。出力マルチプレクサ292は、ORゲート294を介したアクティブなcmd\_idまたはcmd\_statusのいずれかに応答して、第1の並列直列レジスタ282または第2の並列直列レジスタ284のいずれかからのデータを渡す。最終的に、out\_en0によって実行可能となったシリアル出力制御回路296が、SER\_OUT0を提供する。

30

#### 【0043】

当業者であれば、本発明の様々な態様に従って、ステータスインジケータのサイズおよび場所が変更可能であることを理解されよう。たとえば、シリアルデータリンクインターフェースのステータスインジケータは、他のタイプのステータスインジケータ(たとえばメモリバンクステータスインジケータ)と結合すること、および/または、レジスタブロッ

40

50

クの外部(たとえば、リンクアービトレーションモジュール内または制御モジュール238内)に物理的に配置することが可能である。他の例では、シリアルデータリンクインターフェースのステータスインジケータは、1ビットレジスタである。

#### 【 0 0 4 4 】

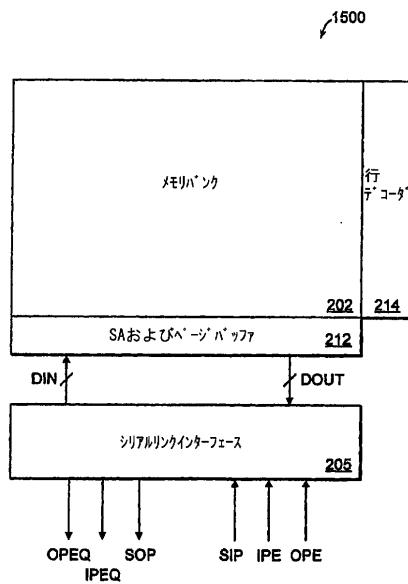

図15Aは、本発明の態様に従った例示的メモリデバイスを示す高水準ブロック図である。メモリデバイス1500内のメモリバンク202のアーキテクチャは、NANDフラッシュメモリコアアーキテクチャと同一または同様とすることができます。図15Aを簡略化するために、特定の回路ブロックが省略される。たとえば、フラッシュメモリコアアーキテクチャで実施されるメモリデバイス1500は、メモリセルをプログラミングおよび消去するために必要な、高電圧発生器回路を含むことになる。本明細書で使用されるコアアーキテクチャ(またはコア回路)は、メモリセルアレイ、ならびにデコーディングおよびデータ転送回路などの関連するアクセス回路を含む、回路を言い表す。標準的なメモリアーキテクチャはよく知られているため、選択されたアーキテクチャに関連付けられた固有の動作も同様であり、当業者であれば誰でも理解しているはずである。さらに当業者であれば、任意の知られた不揮発性または揮発性メモリアーキテクチャが本発明の代替実施形態で使用可能であることも理解されよう。10

#### 【 0 0 4 5 】

メモリデバイス1500は、メモリバンク202、シリアル入力データをメモリバンクに転送するシリアルデータリンクインターフェース205を含む。メモリバンク202は、出力データDOUTを提供するためおよび入力プログラムデータDINを受け取るためのセンス増幅器およびページバッファ回路ブロック212、ならびに行デコーダブロック214などの、よく知られたメモリ周辺回路を含む。当業者であれば、ブロック212が列デコーダ回路も含むことを理解されよう。図15Aに示されるように、シリアルリンクインターフェース205は、シリアル入力ポート(SIP)、シリアル出力ポート(SOP)、入力イネーブル制御ポート(IPE)、出力イネーブル制御ポート(OPE)、入力イネーブルエコー制御ポート(IPEQ)、および出力イネーブルエコー制御ポート(OPEQ)を含む。当業者であれば、シリアルリンクインターフェース205が、チップ選択(CS#)ピン、クロック信号入力(SCLK)、またはリセット選択(RST#)ピンなどの、他のデバイスポートをさらに含むことができるることを理解されよう。20

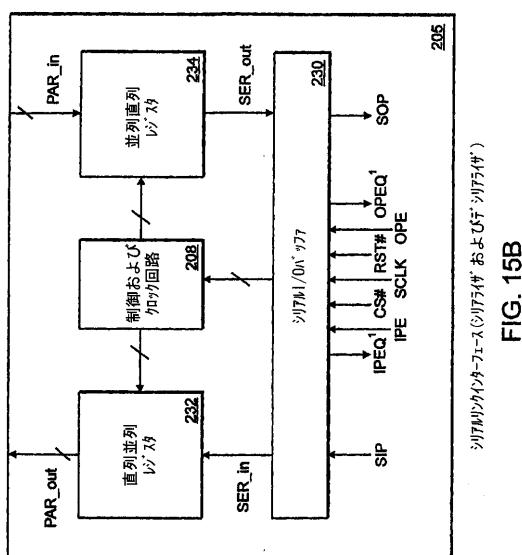

#### 【 0 0 4 6 】

図15Bは、図15Aに示されたメモリデバイスで使用可能なシリアルリンクインターフェースをより詳細に示すブロック図である。図2Aのメモリデバイス200と同様に、インターフェース回路205は、シリアルデータリンク230、直列並列入力レジスタブロック232、および並列直列出力レジスタブロック234を含む。シリアルデータリンクインターフェース230は、シリアル入力データSIP、入力イネーブル信号IPE、および出力イネーブル信号OPEを受け取り、シリアル出力データSOP、入力イネーブルエコー信号IPEQ、および出力イネーブルエコー信号OPEQを提供する。信号SIPは、それぞれがアドレス、コマンド、および入力データを含むことが可能なシリアルデータストリームである。シリアルデータリンク230は、SIPに対応するバッファリング済みシリアル入力データSER\_inを提供し、並列直列レジスタブロック234の出力から、シリアル出力データSER\_outを受け取る。直列並列入力レジスタブロック232はSER\_inを受け取り、これを信号PAR\_inの並列セットに変換する。並列直列出力レジスタブロック234は、出力データPAR\_inの並列セットを受け取り、これをシリアル出力データSER\_outに変換し、次にこれがデータストリームSOPとして提供される。さらに、入力イネーブル信号IPE、出力イネーブル信号OPE、入力イネーブルエコー信号IPEQおよび出力イネーブルエコー信号OPEQを使用して、制御信号およびデータ信号と他のメモリデバイス1500とのデイジーチェーンカスケーディングに対処するように、シリアルデータリンク230が構成される。制御モジュール208は、シリアルデータリンクインターフェースとメモリバンクとの間のデータ転送を制御する。3040

#### 【 0 0 4 7 】

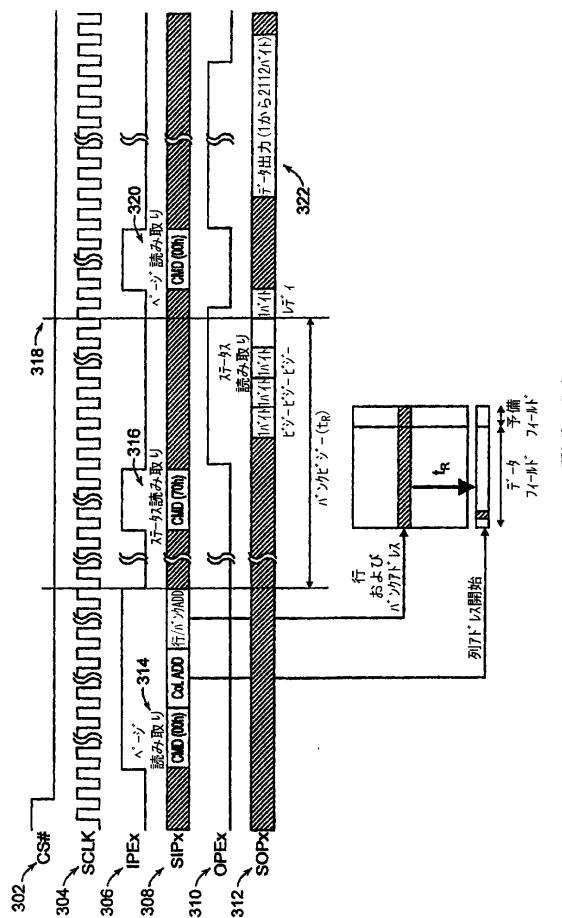

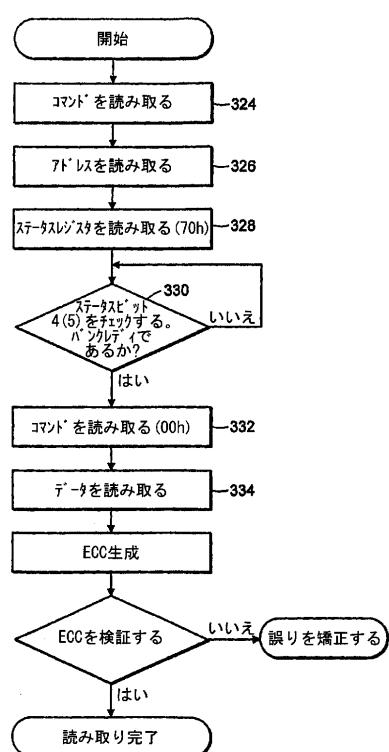

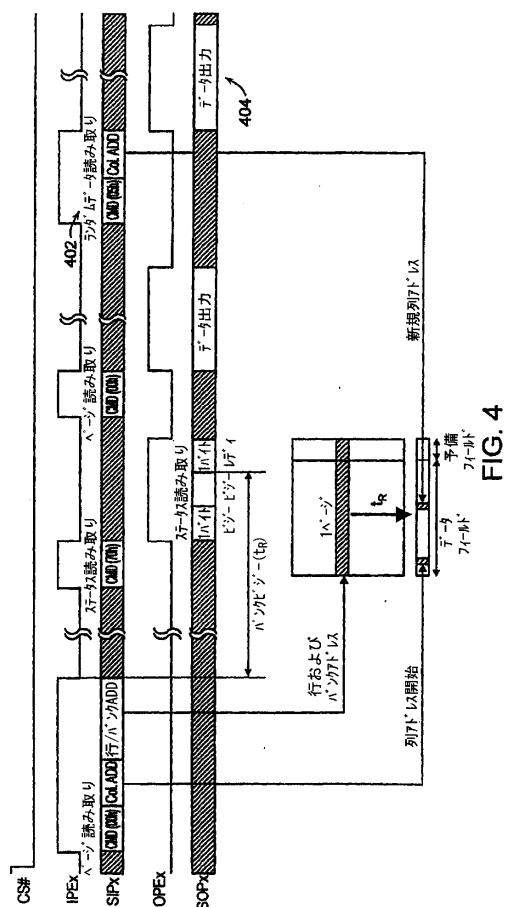

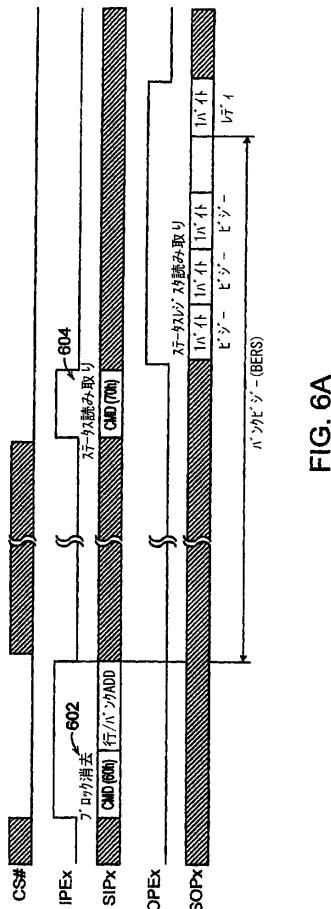

図3A、4、5A、6A、および7は、本発明の様々な態様に従った、メモリデバイス200によって実行される何らかのメモリ動作に関する例示的タイミング図を示す。メモリデバイス50

200によって実行されるメモリコマンドの一部には、ページ読み取り、ランダムデータ読み取り、コピー用のページ読み取り、コピー用のターゲットアドレス入力、シリアルデータ入力、ランダムデータ入力、ページプログラミング、ロック消去、ステータス読み取り、ID読み取り、構成レジスタ書き込み、デバイス名エントリ書き込み、リセット、および/または、バンク選択が含まれるが、これらに限定されることはない。タイミング図に関する以下の考察は、前述で説明されたメモリデバイス200の前述の諸実施形態ならびに表1および2を参照しながら行われる。

#### 【0048】

図3Aのタイミング図に示された例では、本発明に従ったメモリデバイス200のシリアルデータリンク230で、「ページ読み取り」メモリコマンド314が受信される。さらに、図3B 10は、図3Aのタイミング図における「ページ読み取り」メモリコマンド314の動作に対応する簡略流れ図を示す。実際には、図3Bに示されたステップについて、図3Aのタイミング図と共に考察する。たとえばステップ324では、メモリデバイス200のシリアルデータリンク230で、「ページ読み取り」メモリコマンド314が読み取られる。

#### 【0049】

この例の着信データストリームは、コマンドデータ(第1バイト内)、列アドレスデータ(第2および第3バイト内)、ならびに行およびバンクアドレスデータ(第4、第5、および第6バイト内)を含む、6バイトのシリアルデータストリーム(すなわちシリアル入力データ)である。後で論じるように、ターゲットデバイスのアドレス指定に関して、シリアルデータストリームは、ターゲットデバイスアドレス('tda')を識別し、ビットストリーム内のコマンドデータに先行する、追加バイトを含むことができる。バンクアドレスを使用して、パッチ交換206を介してバンク202または204のいずれにアクセスするかを決定することができる。当業者であれば、様々なメモリコマンドが異なるデータストリームを有することが可能であることを理解されよう。たとえば、「ランダムデータ読み取り」コマンドは、コマンドデータ(第1バイト内)および列アドレスデータ(第2および第3バイト内)の、3バイトのみの所定のデータストリームを有する。後者の例では、シリアル入力データのアドレスフィールドは、列アドレスデータのみを含み、2バイト長さであった。一方で、前者の例では、アドレスフィールドは5バイト長さであった。当業者であれば、本明細書に開示された全文を再検討した後に、本発明の様々な態様に従った、多数のメモリコマンドおよび所定のデータストリームが明らかになることを理解されよう。 20 30

#### 【0050】

引き続き、図3Aに示された「ページ読み取り」コマンドを含む例を見ると、チップ選択(CS#)信号302が低に設定されている間、入力ポートイネーブル(IPEx)信号306が高に設定されるのに応答して、シリアルクロック(SCLK)信号304の第1の立ち上がりで、シリアル入力(SIPx)ポート308がサンプリングされる(ここで「x」は、たとえばリンク0インターフェース232またはリンク1インターフェース234などのリンクインターフェース番号を表す、プレースホルダとして働く)。読み取られる(ステップ328で)データは、「ページ読み取り」メモリコマンド314に対応するデータストリームである。CS#信号302は、メモリデバイス200への入力であり、とりわけ、メモリデバイス200がアクティブであるかどうか(たとえばCS#が低の場合)を示すために使用することができる。IPEx信号306は、着信データストリームが特定のリンクインターフェースで受け取られることになるかどうか(たとえばIPExが高の場合)、または、特定のリンクインターフェースが着信データストリームを無視することになるかどうか(たとえばIPExが低の場合)を示す。着信データストリームは、リンクインターフェースのSIPx 308時に、メモリデバイスで受信される。最終的に、システムクロック(SCLK)信号304はメモリデバイス200への入力であり、メモリデバイス200の多数の回路によって実行される様々な動作を同期化するために使用される。当業者であれば、本発明の様々な態様に従ったメモリデバイスは、こうしたクロック信号と同期化可能である(たとえば、動作およびデータ転送は、クロック信号の立ち上がりおよび/または立ち下りに発生する)か、または非同期(すなわち同期的でない)とすることが可能であることを、理解されよう。別の方法として、ダブルデータレート(DDR)の実施では、SCLKクロック 40 50

ク信号の立ち上がりおよび立ち下がりの両方を使用して、情報をラッチすることができる。しかしながら図3Aの例では、入力データはSCLKの立ち下がり時にラッチされ、出力データ322は、SCLKの立ち上がり後にシリアル出力ピン312SOPx上に現れる。

### 【0051】

「ページ読み取り」のステータスは、図3Aに示されるようにSOPxピン312上でチェック可能であり、これによって「バンクビジー」の結果は、「レディ」指示が現れることになる時間318までにSOPx上で提供されることになり、出力データは、間もなく時間322の間に現れることになる。図3Aは、後続の「ステータス読み取り」を伴う「ページ読み取り」を示すが、本発明の態様に従って、「ステータス読み取り」なしの「ページ読み取り」も企図されることに留意されたい。その実施形態では、出力データがレディになるまでSOPxピン上には何のデータも提供されない。10

### 【0052】

SIPxによってサンプリングされたコマンドデータは、図2Cの適切なレジスタ(たとえばコマンドレジスタ256)に書き込まれる。第1バイトがコマンドデータであるように着信データストリームを設計するオプションの少なくとも1つの利点は、追加の処理なしにデータをコマンドレジスタに転送できることである。データストリーム内の後続バイトは、メモリコマンドのタイプに従って、アドレスデータおよび/または入力データとすることができる。当業者であれば、本発明の様々な態様に従って、メモリデバイスによって認識されるメモリコマンドのセットは、ワードベース(すなわち16ビット)または任意のI/O幅で定義可能であることを理解されよう。図3Aでは、コマンドデータ(すなわち、「ページ読み取り」314に対応する00h)の後に、5バイトのアドレスデータ、すなわち2バイトの列アドレスデータおよび3バイトの行/バンクアドレスデータが続く。アドレスデータは、図2Cのアドレスレジスタ258に書き込まれる。アドレスデータは、読み取られることになるメモリバンク202内に格納されたデータの位置を特定するために使用される。このプロセスでは、読み取られることになるデータを選択するために、プリデコーダ回路216、回路212内の列デコーダ、および行デコーダ214が使用される。たとえば、プリデコーダモジュール214を使用して、アドレス情報がプリデコードされる。その後、回路212内の列デコーダおよび行デコーダ214を使用して、アドレスデータに対応するビットラインおよびワードラインが活動化される。「ページ読み取り」コマンドの場合、ワードラインに対応する複数のビットラインが活動化される。その後、メモリバンク202に格納されたデータが、センス增幅器によって感知された後に、回路212内のページレジスタに転送される。ページレジスタ内のデータは、図3A内の時間318まで使用可能でない、すなわち、出力ピンSOPxが「ビジー」を示す場合がある。経過した時間量は、転送時間( $t_R$ )と呼ばれる。転送期間は時間318(図3A内)で終了し、( $t_R$ )の間、続行する。2030

### 【0053】

転送時間間隔が経過する前に、メモリバンクステータスインジケータは、特定のメモリバンク(たとえばメモリバンク202)が「ビジー」であることを示すように設定される。図3Aの例示的なメモリバンクステータスインジケータは、ビットのうちの1つ(たとえばビット4)が、メモリバンク202(すなわちバンク0)が「ビジー」または「レディ」であるかどうかを示す、1バイトフィールドである。メモリバンクステータスインジケータは、図2Eのステータスレジスタ288に格納される。メモリバンクステータスインジケータは、着信データストリームからメモリバンクが識別された後に、更新される(たとえば、ビット4が「0」に設定される)。メモリ動作が完了すると、メモリバンクがもはや「ビジー」ではない(すなわち「レディ」である)ことを示すように、バンクステータスインジケータが更新される(たとえばビット4が「1」に設定される)。以下でより詳細に説明するように、バンクステータスインジケータならびにSOPx出力ピンの両方が、「ビジー」ステータスを示すことになることに留意されたい。当業者であれば、メモリバンクステータスインジケータは、図3Aでは1バイトフィールドとして示されるが、そのサイズは必ずしもこれに限定されないことを理解されよう。より大きなステータスインジケータの少なくとも1つの利点は、より大量のメモリバンクのステータスを監視できることである。加えて、このステータ4050

スインジケータを使用して、他のタイプのステータス(たとえば、「ページプログラミング」などのメモリ動作が実行された後に、メモリバンクが「合格」または「不合格」のどちらのステータスにあるか)を監視することもできる。加えて、当業者であれば、各ビットが異なるメモリバンクのステータスを指定するように実施されているこの例のステータスインジケータは、単なる例であることが明らかであろう。たとえば、ビットの組み合わせの値を使用して、メモリバンクのステータスを(たとえば、論理ゲートおよび他の回路を使用することによって)示すことができる。メモリバンクステータスインジケータに対応する「ステータス読み取り」コマンドの動作については、図7に関して以下で考察する。

#### 【0054】

図3Aの例におけるメモリバンクステータスインジケータは、「ステータス読み取り」メモリコマンド316(ステップ328)を使用して読み取られる。転送期間中の何らかの時点で、「ステータス読み取り」コマンド316がレジスタブロック224内のコマンドレジスタに送信される。「ステータス読み取り」コマンドは、メモリバンク202からページレジスタ216へのデータの転送が完了した時点を特定するために、メモリバンク202のステータスを監視するよう、メモリデバイス200に命令する。「ステータス読み取り」コマンドは、制御モジュール238からデータバス制御モジュール230を介して、またはデータバス制御モジュール230によって直接、送信される。「ステータス読み取り」コマンドが発行される(たとえば、コマンドインタプリタ228および/または制御モジュール238に送信される)と、出力ポートイネーブル(OPEx)信号310が高にされ、メモリバンクステータスインジケータのコンテンツが、シリアル出力(SOPx)ポート312を介して出力される。IPEx信号306と同様に、OPEx信号310は、高に送られた場合にシリアル出力ポートバッファ(たとえばデータ出力レジスタ)を実行可能にする。図3Aの時間318で、SOPx内のステータスインジケータデータは、メモリバンク202が「ビジー」ステータスから「レディ」ステータスに変更されたことを示す。ステータスインジケータのコンテンツがもはや不要であるため、OPEx信号310は低に戻される。

#### 【0055】

次に図3Aでは、IPEx信号が高に設定され、データレジスタから出力ピンSOPxへとデータを提供するために、「ページ読み取り」コマンド320が、後続のアドレスデータなしで、レジスタブロック224内のコマンドレジスタに再発行される(ステップ332)。その後、OPEx信号は高に設定され(およびIPExは低に戻され)、ページレジスタ216のコンテンツはSOPx 312に転送される。出力データは、メモリデバイス200からリンクインターフェース230を介して提供される(ステップ334)。誤り訂正回路(図示せず)は、出力データを検出し、誤りが検出された場合に読み取り誤りを示すことができる。当業者であれば、ステータスの監視およびページ読み取りコマンドの再アサートが、システムによって自動的に実行可能であることを理解されよう。図3Aは、本発明の諸態様に従ったメモリデバイス動作の單なる一例であり、本発明はこれに限定されるものではない。たとえば、本発明の様々な態様に従って、他のメモリコマンドおよびタイミング図が想起される。

#### 【0056】

たとえば図4では、「ページ読み取り」コマンドに続く「ランダムデータ読み取り」コマンドに関する簡略化されたタイミング図が示される。「ランダムデータ読み取り」コマンドは、「ページ読み取り」コマンドまたは「ランダムデータ読み取り」コマンドに続く单一または複数の列アドレスで、追加データの読み取りを実行可能にする。「ランダムデータ読み取り」コマンド402に関するデータストリームは、コマンドデータ(第1バイト内)および列アドレスデータ(第2および第3バイト内)の、3バイトからなる。データは、「ページ読み取り」コマンドで選択された同じ行から読み取られることになるため、行アドレスデータは不要である。通常の「ページ読み取り」コマンド完了後に発行された「ランダムデータ読み取り」コマンドは、結果として現在のページ(すなわち、初期のコマンド中のページ読み取り)から何らかのデータ404を出力されることになる。「ランダムデータ読み取り」コマンドの少なくとも1つの利点は、データが、メモリバンク202に対応する回路

10

20

30

40

50

212のページレジスタ内にすでに存在するため、事前に選択されたページからのデータが

出力できる効率が向上することである。

#### 【0057】

図5Aに関して、「ページプログラミング」コマンドに関するタイミング図が示される。

図2Aに示された実施形態はシリアルデータ入力および出力リンク構造を使用するため、ペ

ージのプログラミング開始に先立って、第1にプログラムデータをバンクページレジスタ

にロードしなければならない。これは、「シリアルデータ入力コマンド」で実施される。

「シリアルデータ入力」コマンド502は、データのあるページまで(たとえば2、2112バ

イト)が回路212内のページバッファにロードされる、シリアルデータローディング期間から

なる。データレジスタのローディングプロセスが完了した後、バンクレジスタから適切な

メモリバンクへとデータを転送するために、「ページ開始」コマンド504が発行される。

コマンド504が発行されると、内部書き込み状態マシンが適切なアルゴリズムを実行し、

動作のプログラミングおよび検証のタイミングを制御する。したがって、本発明の実施形

態に従い、「ページ開始」コマンドは、シリアルデータ入力および検証の2つのステップ

に分けられる。「ページプログラミング」コマンドが正常に完了すると、メモリバンクス

テータスインジケータは、動作の成功を示すために「合格」(「不合格」に対して)結果を

提供することになる。他の点では、図5Aの例に関係するタイミング図およびステップは、

上記でより詳細に説明した図3Aのそれらと同様である。

10

#### 【0058】

さらに、図5Bは、図5Aのタイミング図における「ページプログラミング」の動作に対応

する簡略流れ図を示す。ステップ506では、「シリアルデータ入力」コマンド502がシリアル

入力ポート(SIP)ラインに入力される。この例でのSIPラインへのデータストリーム入力

は、コマンドデータ(第1バイト内)で始まるマルチバイトシリアルデータストリーム(すな

わちシリアル入力データ)である。次に、列アドレスデータ(シリアルデータストリームの

第2および第3バイト内)および行アドレス/バンクデータ(シリアルデータストリームの第4

、第5、および第6バイト内)が、SIPラインに入力される(ステップ508)。入力データは、

シリアルデータストリームの後続バイトでSIPラインに入力される(ステップ510)。ステップ

512では、「プログラム開始」コマンド504が発行される。次に、動作のステータスを監

視するために、「ステータス読み取り」コマンドがSIPラインに書き込まれる(ステップ51

4)。この結果、メモリデバイスがメモリバンクステータスレジスタのステータスピットを

監視する。ステータスピットが、メモリバンクがレディであること(ステップ516)および

メモリバンクが「合格」を示すこと(ステップ518)を示す場合、「ページプログラミング」

メモリコマンドは適切に実行されている。

20

30

#### 【0059】

加えて、「コピー用のページ読み取り」および「コピー用のターゲットアドレス入力」

メモリコマンドは、本発明の諸態様に従い、メモリデバイスによって実行される他の動作

である。「コピー用のページ読み取り」コマンドがシリアルリンクインターフェースのコ

マンドレジスタに書き込まれた場合、メモリ位置の内部ソースアドレス(3バイト)が書き

込まれる。ソースアドレスが入力されると、メモリデバイスは、指定されたソースアドレ

スにあるメモリバンクのコンテンツをデータレジスタ内に転送する。その後、「コピー用

のターゲットアドレス入力」メモリコマンド(3バイトのバンク/行アドレスシーケンスを

備える)を使用して、ページコピー動作用のターゲットメモリアドレスが指定される。そ

の後、「ページプログラミング」コマンドを使用して、内部制御論理に、ページデータを

ターゲットアドレスに自動的に書き込ませる。次に、「ステータス読み取り」コマンドを

使用して、コマンドの正常な実行を確認することができる。当業者であれば、本明細書の

開示全体を再検討した後に、他のメモリ動作が明らかとなろう。

40

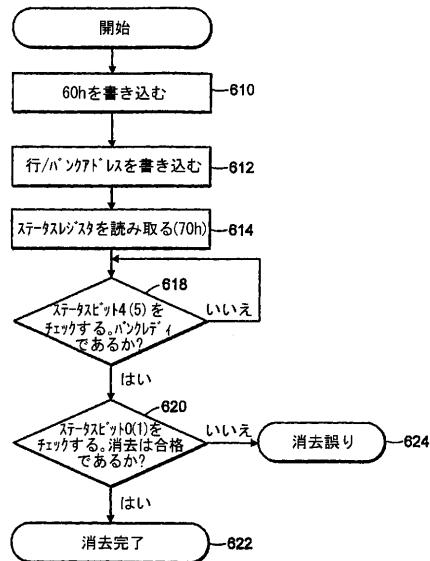

#### 【0060】

図6Aに関して、「消去」(または「ロック消去」)コマンドに関するタイミング図が示

される。加えて、図6Bは、図6Aのタイミング図における「消去」コマンドの動作に対応す

る簡略流れ図を示す。当業者であれば、消去は、通常、ロックレベルで発生することが

50

わかる。たとえば、フラッシュメモリデバイス200は、各バンクで、ブロックあたり64の2,112バイト(2,048+64)ページとして編成された2,048の消去可能ブロックを有することができる。各ブロックは132Kバイト(128K+4Kバイト)である。「消去」コマンドは一度に1ブロック上で動作する。ブロック消去は、ステップ610で、「消去」コマンドに対応するコマンドデータ602(すなわち、「60h」のコマンドデータ)を、ステップ612での行およびバンクアドレスに関する3バイトと共に、SIPxを介してコマンドレジスタに書き込むことによって開始される。コマンドおよびアドレス入力が完了した後、内部消去状態マシンが自動的にプロパティアルゴリズムを実行し、動作を消去および検証するために必要なすべてのタイミングを制御する。「消去」動作は、論理値「1」を、メモリブロック内のあらゆるメモリ位置に書き込むかまたはプログラミングすることによって、実行可能であることに留意されたい。 $t_{BERS}$ (すなわち、ブロック消去時間)が完了した時点を決定するための消去ステータスを監視するために、ステップ614で「ステータス読み取り」コマンド604(たとえば70hに対応するコマンドデータ)を発行することができる。「ステータス読み取り」コマンド後、すべての読み取りサイクルは、メモリバンクステータスレジスタから新しいコマンドが与えられるまでとなる。この例では、メモリバンクステータスレジスタの適切なビット(たとえばビット4)が、対応するメモリバンクの状態(たとえばビジーまたはレディ)を反映する。ステップ618でバンクがレディになった場合、ステップ620で、メモリバンクステータスレジスタの適切なビット(たとえばビット0)がチェックされ、ステップ622で消去動作が合格である(すなわち適切に実行された)か、またはステップ624で不合格であるかを判別する。いくつかの点で、図6Aの例に関するタイミング図およびステップは、以前により詳細に説明した図3Aのそれらと同様である。

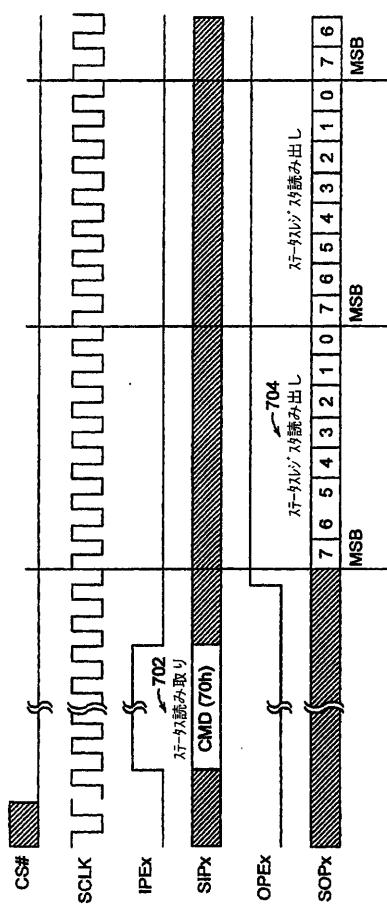

#### 【0061】

図7に関して、「ステータス読み取り」メモリコマンドを使用して、メモリバンクステータスインジケータが読み取られる。「ステータス読み取り」コマンド(すなわち「70h」)が、702で図2C内のコマンドレジスタ256に送信された場合、メモリデバイス200は、とりわけ、メモリバンク202から回路212内のページバッファへのデータの転送が正常に完了した時点を決定するために、メモリバンク202のステータスを監視するように命令される。「ステータス読み取り」コマンドが発行される(たとえば、コマンドインタプリタ262に送信される)と、出力ポートイネーブル(OPEx)信号は高になり、704でシリアル出力(SOPx)ポートを介してメモリバンクステータスインジケータのコンテンツが出力される。OPEx信号は、高に設定された場合、シリアル出力ポートバッファ(たとえば、データ出力レジスタ)を実行可能にする。図7の例では、メモリバンクステータスインジケータは、とりわけ、各ビットがメモリバンク(たとえばメモリバンク202)が「ビジー」であるか「レディ」であるか、および/またはメモリバンク上で実行される動作(たとえば「消去」コマンド)が「合格」であるか「不合格」であるかを示す、1バイト(すなわち8ビット)フィールドである。当業者であれば、図7ではメモリバンクステータスインジケータが1バイトフィールドとして示されているが、そのサイズは必ずしもこれに限定されないことを理解されよう。より大きなステータスインジケータの少なくとも1つの利点は、より大量のメモリバンクのステータスを監視できることである。加えて、当業者であれば、この例のステータスインジケータは、各ビットが異なるメモリバンクのステータスを指定するように実施されたが、本発明はそのように限定されないことを理解されよう。たとえば、ビットの組み合わせの値を使用して、メモリバンクのステータスを(たとえば、論理ゲートおよび他の回路を使用することによって)示すことができる。

#### 【0062】

図8A、8B、および8Cは、2つの独立したシリアルデータリンク230および236を使用して、同時動作を実行するために使用される、本発明の諸態様に従ったメモリデバイスに関するタイミング図を示す。本発明の諸態様に従ったメモリデバイスによって実行されるいくつかの同時動作は、同時読み取り、同時プログラミング、同時消去、プログラミング時読み取り、消去時読み取り、および消去時プログラミングを含むが、これらに限定されることはない。図8Aは、バンクA(バンク202)およびバンクB(バンク204)上で実行されている同

10

20

30

40

50

時「ページ読み取り」動作を示す。図8Aでは、バンクAは「バンク0」として表され、バンクBは「バンク1」として表される。図8B。当業者であれば、本明細書の開示全体を再検討することで他の同時動作が明らかとなろう。

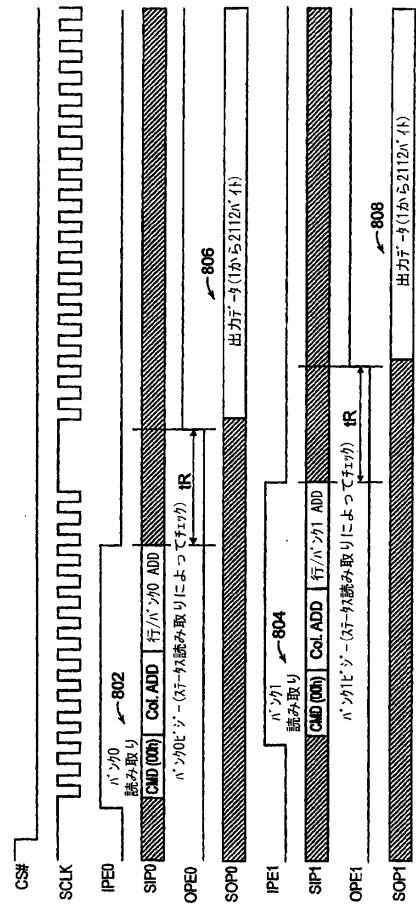

#### 【0063】

図8Aを参照すると、メモリデバイス200内の異なるメモリバンクで指示される同時「ページ読み取り」動作802、804が実行される。2つのデータリンクインターフェース230、236を備えるメモリデバイス200では、「ページ読み取り」コマンド804はデータリンクインターフェース236(すなわちリンク1)を介して発行され、「ページ読み取り」802はデータリンクインターフェース230(すなわちリンク0)を介してペンドィングされる。図8Aは、バンク1上の「ページ読み取り」以前に開始しているバンク0上の「ページ読み取り」を示すが、この2つの「ページ読み取り」動作はほぼ同時に開始可能であり、同時に動作可能である。それぞれの「ページ読み取り」コマンドから出力されたデータ806、808は、それらそれぞれのデータリンクインターフェースを介して同時に送信される。したがって、メモリデバイス200内の各データリンクインターフェースは、任意のメモリバンクにアクセスし、独立して動作することができる。この機能の少なくとも1つの利点は、システム設計におけるより高い柔軟性およびデバイス使用率(たとえばバス使用率およびコア使用率)の向上である。10

#### 【0064】

図8Aにおいてメモリバンクからデータリンクインターフェースへ出力されるデータのバスは、前述の図3Aのそれと同様である。たとえば、メモリバンク204から出力されるデータは、S/Aおよびページバッファ218から、たとえばバンクアドレスによって制御されるバス交換206を介して、並列直列出力レジスタブロック240へ、およびシリアルデータリンクインターフェース236(すなわちリンク1)へと流れる。メモリバンク202および204とシリアルデータリンクインターフェース230、236との間での同時データ転送は、それぞれ、互いに独立して実行されることになる。バンクアドレスはバス交換206を制御することが可能なため、シリアルデータリンクインターフェース236は代わりにバンク202にアクセス可能である。メモリデバイス200内のデータリンクインターフェースの数は、メモリデバイス200上のポートまたはピンの数に限定されない。また、メモリデバイス200内のリンクインターフェースの数も、メモリデバイス内のメモリバンクの数によって限定されない。たとえば、各データリンクインターフェースは、単一の入力ストリームおよび/または単一の出力ストリームを処理することができる。2030

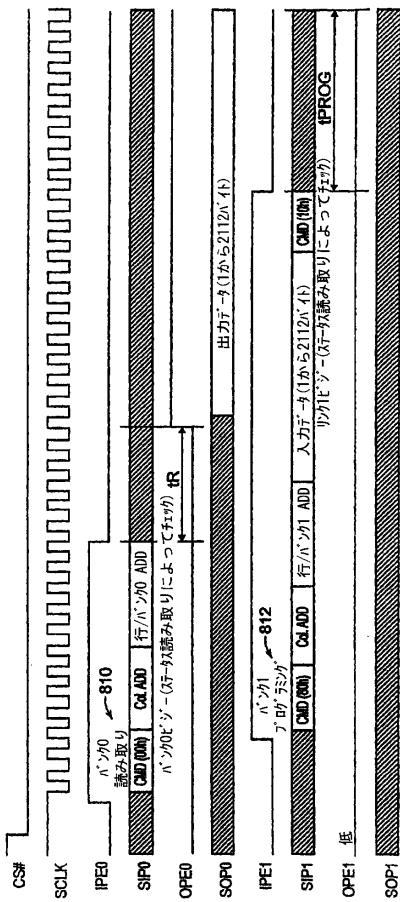

#### 【0065】

さらに、本発明の様々な態様に従って、図8Bは、同時に実行されているメモリデバイス200内の異なるメモリバンクで指示される「ページ読み取り」コマンド810および「ページプログラミング」コマンド812のタイミング図を示す。この例では、シリアルデータリンクインターフェース230を介して、複数のメモリバンクのうちの一方(たとえばメモリバンク202)で、読み取り動作(「ページ読み取り」810)が実行されている。その一方で、同時に、複数のメモリバンクのうちの他方(たとえばメモリバンク204)で、書き込み動作(「ページプログラミング」812)が実行されている。本発明の様々な態様によれば、メモリデバイス200内の各リンクは、任意のメモリバンクにアクセスし、独立して動作することができる。40

#### 【0066】

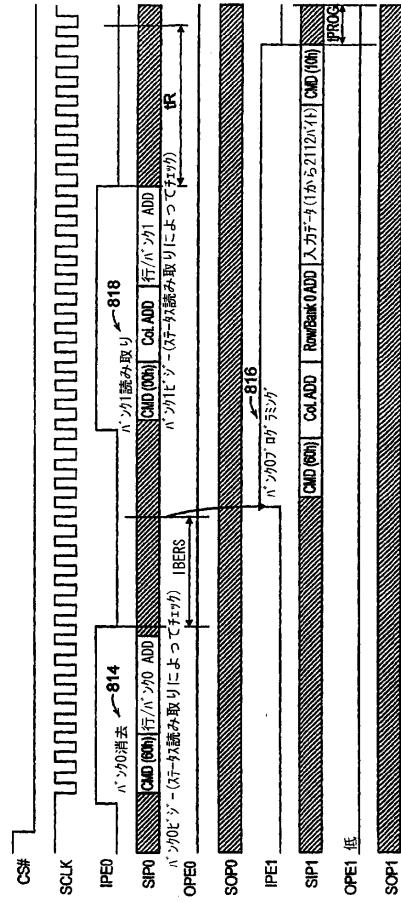

図8Cは、同時にメモリ動作を実行する2つのシリアルデータリンクインターフェースおよび2つのメモリバンクを備える、メモリデバイス200の例示的タイミング図である。第1に、メモリバンク0(バンク202)で指示される「消去」コマンド814が、シリアルデータリンク0(シリアルデータリンク230)から発行される。リンク0(シリアルデータリンク230)およびメモリバンク0(バンク202)は「消去」コマンド814でビジーであるが、「ページプログラミング」コマンドがメモリデバイスで受信され、リンク1(シリアルデータリンク236)を使用するように指示される。したがって、シリアルデータリンクインターフェース1(シリアルデータリンク236)からメモリバンク0(バンク202)上で「ページプログラミング」コマンド816が発行される。50

ング」コマンド816が実行される。その一方で、同時に、シリアルデータインターフェース0(シリアルデータリンク230)によって、読み取りコマンド818がメモリバンク1(バンク204)上で実行される。データは、メモリコマンド814時にはシリアルデータリンクインターフェース0(シリアルデータリンク230)とバンク0(バンク202)との間で、メモリコマンド818時には同じリンクインターフェース0(シリアルデータリンク230)とバンク1(バンク204)との間で、転送される。したがって、本発明の諸態様によれば、メモリデバイス200内の各リンクは、メモリバンク(すなわち、ビジーでないメモリバンク)のいずれかに独立してアクセスする。

#### 【0067】

当業者であれば、本明細書に開示された全文を再検討した後、図8A、8B、および8Cが、

10 本発明に従って想起された同時メモリ動作のいくつかの例を単に示すものであることが明らかとなろう。同時動作の他の例は、同時消去、プログラミング時読み取り、消去時読み取り、消去時プログラミング、プログラミング時消去、および/または同時プログラミングを含むが、これらに限定されることはない。当業者であれば、流れ図内に示されたステップの順序は、ステップをその特定の順序にのみ限定するように解釈されるべきではないことを理解されよう。たとえば、読み取りおよびプログラミングコマンドは、ステータス読み取りコマンドと共に、またはこのコマンドなしで、発行することができる。

#### 【0068】

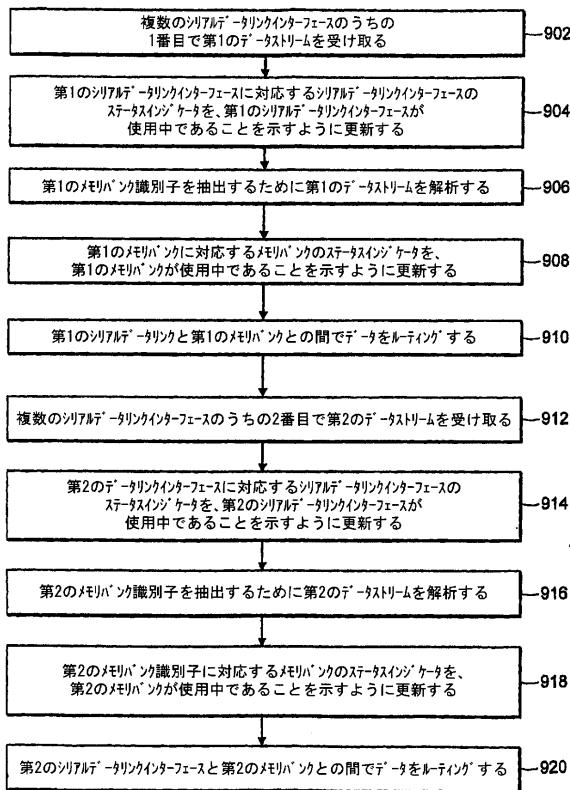

図9は、本発明の諸態様に従った、複数のシリアルリンクインターフェースと複数のメモリバンクとの間での2つの同時書き込み動作の、より概説的な説明を示す。図9は、本発明の実施形態に従って、シリアルデータリンクインターフェースを介してメモリバンクにデータを書き込む方法を示す。最初に、ステップ902では、シリアルデータリンクインターフェースでデータストリームが受け取られる。データストリームは、レジスタに格納されることになるコマンド、アドレス、およびデータを含む。次にステップ904で、第1のシリアルデータリンクインターフェースに対応するシリアルデータリンクインターフェースのステータスインジケータが、第1のシリアルデータリンクインターフェースが使用中であることを示すように更新される。ステップ904は、ステータスレジスタ内のビット値の変更を含む。ステップ904での更新は、特定のインターフェースが使用中であることを示す。ステップ906で、第1のメモリバンク識別子を抽出するためにデータストリームが解析される。メモリバンク識別子は、メモリデバイス内のメモリバンクを固有に識別する。

20 メモリバンク識別子は、データストリームのアドレスフィールドまたは他のフィールド内に含めることができる。次に、メモリバンク識別子抽出のためのデータストリームの解析後、ステップ908で、対応するメモリバンクステータスインジケータが更新される。ステップ904および908で実行される更新は、たとえば、ステータス/IDレジスタ210内の制御回路によって生成された制御信号によって実行することができる。これらの制御信号は、話をわかりやすくするために、含められたタイミング図から省略されている。最後にステップ910で、データは、第1のシリアルデータリンクと第1のメモリバンクとの間をルーティングされる。データは第1にメモリバンクページレジスタに書き込まれ、続いてメモリバンクにプログラミングされるため、この概説的説明ではステップ910が簡略化されていることに留意されたい。

30

#### 【0069】

その一方で、示された動作902と同時に、他のデータ書き込み動作が異なるメモリバンク上で異なるシリアルデータリンクインターフェースを介して実行される。言い換えれば、第2のシリアルデータリンクインターフェースと第2のメモリバンクとの間でルーティングされる第2のデータストリームを使用して、第2のメモリ動作が同時に実行される。最初に、ステップ912では、第2のデータストリームが複数のシリアルデータリンクインターフェースのうちの2番目で受け取られる。ステップ912および902で言及されるシリアルデータリンクインターフェースは、同じメモリデバイスのすべての部分である。ステップ914で、第2のデータリンクインターフェースに対応するシリアルデータリンクインターフェースのステータスインジケータが、第2のシリアルデータリンクインターフェースが使用

40

10

20

30

40

50

中であることを示すように更新される。次に、ステップ916で、第2のメモリバンク識別子を抽出するために第2のデータストリームが解析される。ステップ918で、第2のメモリバンク識別子に対応するメモリバンクステータスインジケータは、第2のメモリバンクが使用中であることを示すように更新され、ステップ920で、データは、「ページプログラミング」コマンドに関して前述したように、第2のシリアルデータリンクインターフェースと第2のメモリバンクとの間で、第2のメモリバンクの関連するページレジスタを介してルーティングされる。図9では、データの転送が実行されると、すなわち、シリアルデータリンクインターフェースが指定されたメモリバンクに書き込まれることになるすべてのデータを受け取ると、各シリアルデータリンクインターフェースに対応するシリアルデータリンクインターフェースインジケータは、関連するリンクが現在使用可能であることを示すようにリセットされ、メモリバンクインジケータは、すべての関連するデータがプログラミングされるまでビジーのままとなり、その後、メモリバンクインジケータは関連するバンクが使用可能になったことを示すようになる。10

#### 【0070】

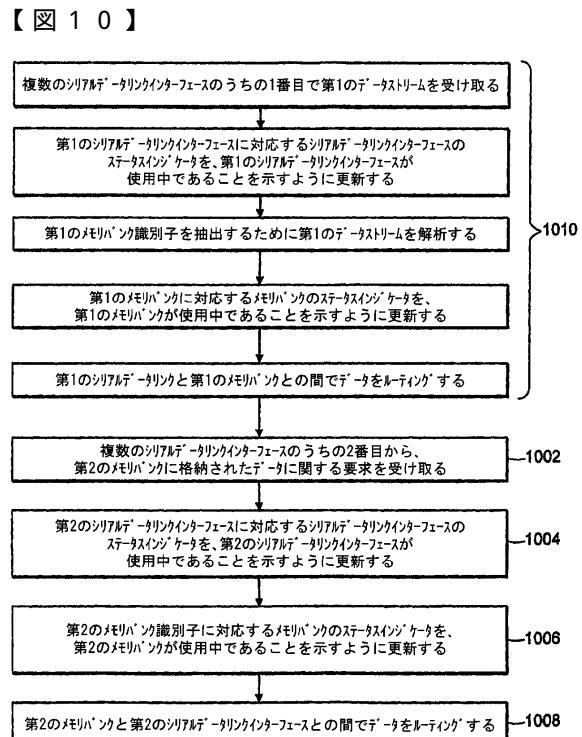

図10は、図9のステップ902から910に示されたデータの書き込みと同時に、メモリバンクからデータが読み取られた場合に実行可能な、例示的ステップを含む(ステップ1010と指定される)。図10は、図7で図示された同時メモリ動作の完了で実行可能なステップのうちのいくつかの例を示す。最初にステップ1002で、第2のメモリバンクに格納されたデータに関する読み取り要求が、複数のシリアルデータリンクインターフェースのうちの2番目から受け取られる。ステップ1004で、第2のデータリンクインターフェースに対応するシリアルデータリンクインターフェースのデータステータスインジケータが、第2のシリアルデータリンクインターフェースが使用中であることを示すように更新される。第2のメモリバンク識別子に対応するメモリバンクステータスインジケータは、ステップ1006で、第2のメモリバンクが使用中であることを示すように更新される。最後にステップ1008で、データは第2のメモリバンクと第2のシリアルデータリンクインターフェースとの間でルーティングされる。図10に示されたステップのうちの1つまたは複数を、同時に実行することができる。20

#### 【0071】

図1Bに戻ると、図示されたメモリデバイスは、仮想多重リンクを使用する単一のデータリンクインターフェース120構成を含む。図1Bは、前述された直列並列入力レジスタ232の構成で実施可能である。より一般的には、図1Bの実施形態は、メモリデバイス200で実施可能であるが、2つのシリアルデータリンクのうちの1つのみが使用中の状態である。従来のフラッシュメモリでは、I/Oピンは動作が完了するまで占有される。したがって、デバイススピジーステータス時には、何の動作もアサートすることができず、それによってデバイスの可用性が減少し、全体性能が低下する。図1Bに示された例では、2つのメモリバンクのうちの1つで動作が開始された後、「データ読み取り」動作によってチェックされたいかなる使用可能メモリバンクにもアクセス可能である。その後、メモリデバイスは、シリアルデータリンクを使用して、補助交換回路を介して使用可能メモリバンクにアクセスすることができる。したがって本発明の本態様により、単一リンクを使用して、複数のメモリバンクにアクセスすることができる。この仮想多重リンク構成は、単一リンクを使用して複数のリンク動作をエミュレートする。3040

#### 【0072】

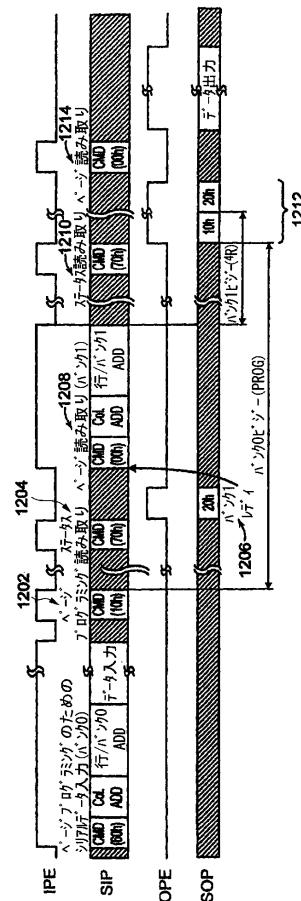

図12は、バンク0での「ページプログラミング」およびバンク1での「ページ読み取り」が実行されることになる仮想多重リンク構成を使用して、メモリ動作を実行する、2つのメモリバンクを備えたメモリデバイスのタイミング図を示す。最初に、メモリバンク0で指示される「ページプログラミング」コマンド1202が発行される。「ページプログラミング」コマンドについてすでに前述したが、要約すると、第1に、そのデータがバンク0にプログラミングされることになるバンク0ページレジスタにロードするために「シリアルデータ入力」コマンドが実行される。続いて、「ページプログラミング」コマンドが発行され、ページレジスタからバンク0にデータが書き込まれる。「データ読み取り」コ50

マンド1204がデバイスに発行された場合、デバイスは、バンク1が「レディ」であること(およびバンク0が「ビジー」であること)を示す1206を示す。したがって、本発明に従った仮想多重リンク構成に基づき、メモリバンク0がビジーの間に、メモリバンク1で指示される「ページ読み取り」コマンド1208が発行可能であり、発行される。「ページ読み取り」コマンドについては前述されている。「ステータス読み取り」コマンド1210は、メモリバンクのステータスを決定するために発行可能である(および図12では発行されるように示される)。「ステータス読み取り」コマンドの結果は、間隔1212の間に、メモリバンク0およびメモリバンク1の両方がレディであることを示す。最後に、「ページ読み取り」コマンド1214(バンク1用)が発行され、結果として、シリアル出力ピン(SOP)上で出力されることになるバンク1「ページ読み取り」コマンドに対応するメモリアドレスのコンテンツが生じる。バンク0での「ページプログラミング」動作が実施されている間、バンク1を「レディ」として識別する「ステータス読み取り」コマンドを受け取るために、シリアルデータインターフェースリンクピンSIPが使用可能であることに留意されたい。同様に、バンク1上の「ページ読み取り」コマンドが初期化されると、SIPピンは「ステータス読み取り」コマンドに再度使用することが可能であり、現在バンク0および1の両方がレディであることを示す。結果として、単一シリアルデータインターフェースリンクを使用して、両方のバンクのステー

タスにアクセスし、これをチェックすることができる。図12で実施される仮想多重リンク機能の諸態様は、たとえ初期のメモリ動作がペンドィング中であっても、リンクが使用可能であることを示す。この機能からの少なくとも1つの利点は、仮想多重リンク構成から結果として生じるピンカウントが削減されることである。他の利点は、メモリデバイスの性能が向上することである。

#### 【0073】

加えて、仮想多重リンク機能の諸態様が、デュアルリンクまたはクワッドリンク構成のメモリデバイスで実施された場合、1つを除くすべてのリンクが非アクティブであるとみなすことが望ましい場合がある。たとえば、クワッドリンク構成(図1C)において4つのリンクのうちの3つが使用できず、NC(接続なし)と指定される場合がある。こうした実施の少なくとも1つの利点は、リンクの柔軟性および可用性を維持しながら、メモリデバイス上のピンの数が削減されることである。

#### 【0074】

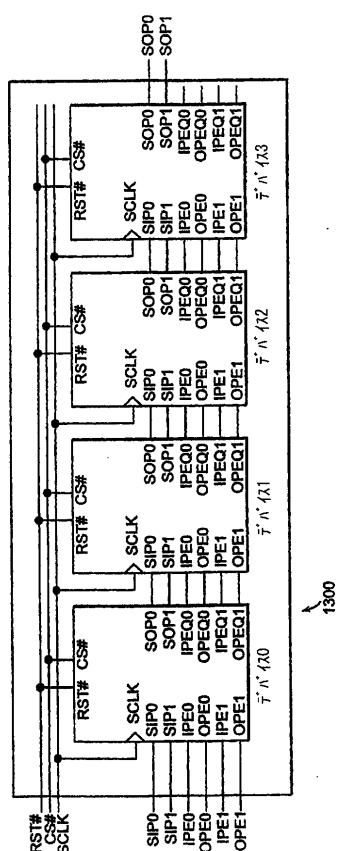

本発明の様々な態様によれば、図13Aは、複数のメモリデバイス200を直列に接続するための、デイジーチェーンカスケード構成1300を示す。特に、デバイス0は、複数のデータ入力ポート(SIP0、SIP1)、複数のデータ出力ポート(SOP0、SOP1)、複数の制御入力ポート(IPE0、IPE1)、および複数の制御出力ポート(OPE0、OPE1)からなる。これらのデータおよび制御信号は、外部ソース(たとえばメモリコントローラ(図示せず))からメモリデバイス1300に送信される。さらに、本発明によれば、第2のフラッシュメモリデバイス(デバイス1)は、デバイス0と同じタイプのポートからなるものとすることができます。デバイス1は、デバイス0と直列に接続することができる。たとえばデバイス1は、データおよび制御信号をデバイス0から受け取ることができる。1つまたは複数の追加のデバイスを、同様に、デバイス0およびデバイス1と並んで直列に接続することもできる。カスケード構成における最終デバイス(たとえばデバイス3)は、データおよび制御信号を所定の待ち時間後にメモリコントローラに戻す。各メモリデバイス200(たとえばデバイス0、1、2、3)はIPE0、IPE1、OPE0、およびOPE1(すなわち制御出力ポート)のエコー(IPEQ0、IPEQ1、OPEQ0、OPEQ1)を後続のデバイスに出力する。図2Bで前述した回路は、1つのデバイスから後続のデイジーチェーンデバイスへどのように信号を渡すことができるかを示す。加えて、单一クロック信号が、直列に接続された複数のメモリデバイスのそれぞれに送られる。

#### 【0075】

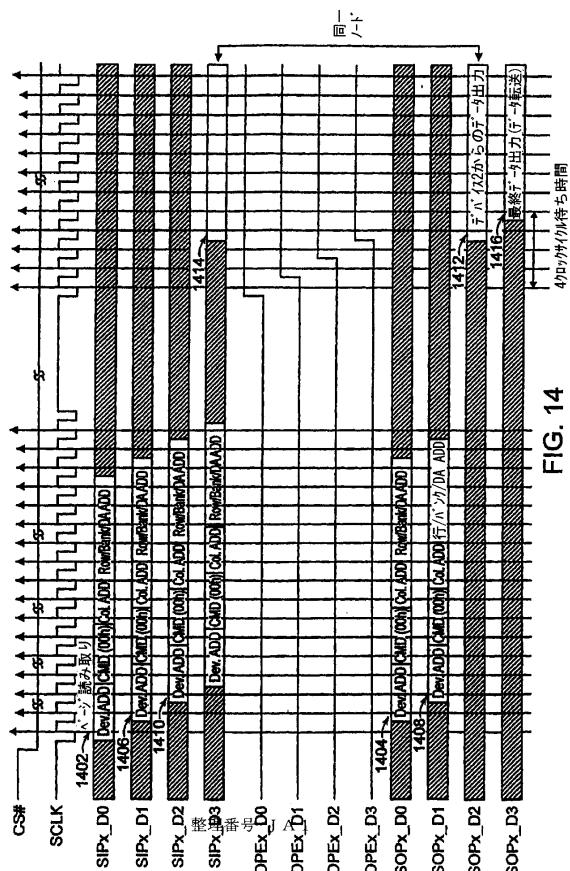

前述のカスケード構成では、カスケード化メモリデバイス1300のデバイス動作は、非カスケード化メモリデバイス200の動作と同じである。当業者であれば、カスケード構成ではメモリデバイス1300の全体待ち時間が増加する可能性があることを理解されよう。たと

えば図14は、メモリデバイス1300で受信され、メモリデバイス1300内のデバイス2のメモリバンクで指示される、「ページ読み取り」メモリコマンド1402に関する、かなり簡略化されたタイミング図を示す。メモリコマンドはメモリデバイス1300で受信され、デバイス0およびデバイス1を介してデバイス2に送信される。たとえば、「ページ読み取り」コマンド1402に対応するデータストリームは、メモリデバイス1300内のデバイス0のSIP0ラインから、デバイス0の回路を介して転送され、デバイス0のSOP0ラインで出力されることになる。デバイス0の出力は、図14の簡略化タイミング図で1404のSOPx\_D0出力ライン上に反映される。「SOPx\_D0」は、デバイス0上のシリアル出力ポート0に対応する。同様に、その後データストリームは、デバイス1のSIPx\_D1で受信され(1406)、SOPx\_D1ライン上の1408でデバイス1によって出力されるためにデバイス1を介して送信される。次に、データストリームは、デバイス2のSIPx\_D2上の1410で受信される。この例では、「ページ読み取り」コマンドは、メモリデバイス200内の回路に関して説明した方法と同様に、デバイス2のメモリバンクに向けて送られるため、デバイス2内の回路は「ページ読み取り」コマンドを受信し、デバイス2内のメモリバンクからデバイス2上の1412でのSOPx\_D2出力ラインへの、要求されたデータの転送を制御する。デバイス2によって出力されたデータは、1414でデバイス3によって受信され、メモリデバイス1300から出力される。当業者であれば、図14の簡略化タイミング図から、4クロックサイクルの所定の待ち時間がカスケーディング構成によって生じたことを理解されよう。

#### 【0076】

その一方で、カスケード構成は、デバイスのスループットを犠牲にすることなく、事実上無限数のデバイスを接続することができる。本発明の諸態様は、複数チップパッケージソリューションおよびソリッドステート大容量ストレージアプリケーションの実施において有利な場合がある。カスケード化デバイス1300における着信データストリームは、非カスケード化メモリデバイス200のそれと同様であるが、データストリームの第1バイトは1バイトのデバイス識別子によって先行される可能性がある。たとえば、第1バイトの値「0000」はデバイス0を示し、値「0001」はデバイス1を示すことができる。当業者であれば、デバイス識別子は必ずしも1バイトに限定される必要がなく、所望に応じて増減できることを理解されよう。また、デバイス識別子は必ずしもデータストリーム内の第1バイトとして位置決めされる必要はない。たとえば、識別子のサイズは、カスケード化構成においてより多くのデバイスを収容するように増加すること、およびデータストリームのアドレスフィールドで位置決めすることが可能である。

#### 【0077】

本発明に従った一実施形態では、メモリデバイス200は単一のモノリシック4Gbチップを使用する。他の実施形態では、メモリデバイスは8Gb用の1対のスタックリップを使用する。さらに他の実施形態では、メモリデバイス1300は16Gbを構成するために4チップのスタックリップを使用する。本発明の様々な態様に従ったフラッシュメモリデバイスは、ソリッドステートファイルストレージなどの大規模不揮発性ストレージアプリケーション、および不揮発性が望ましい他のポータブルアプリケーション向けの、改良型ソリューションとすることが可能である。メモリデバイス1300は、システムのより高い拡張可能性および柔軟性との統合に対処するために、事実上無限数のリンクデバイスのための新規なフラッシュデバイスカスケード方式から恩恵を受けることができる。シリアルインターフェースは、より速いクロックレート、より良好な信号整合性、およびより少ない電力消費量によって、追加の性能向上を提供することになる。シリアルインターフェースは、パッケージ構成を変更することなく、無制限の拡張可能I/O幅も提供する。さらに、I/Oの数が少ない本発明に従ったメモリデバイスの片面パッドアーキテクチャは、チップパッケージサイズを大幅に縮小する。

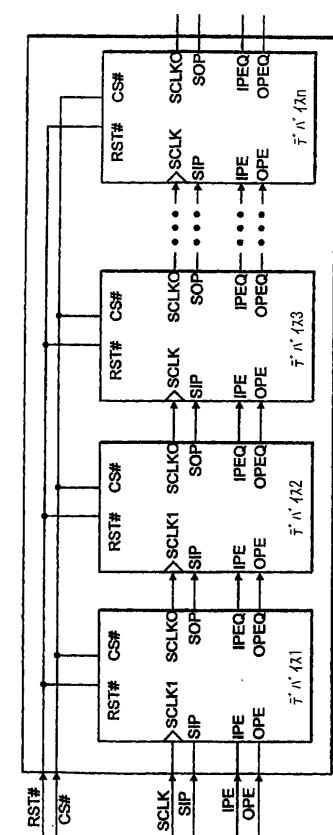

#### 【0078】

図13Bは、図15Aに示された複数のメモリデバイス1500を使用する、デイジーチェーンカスケード構成におけるデバイス接続の他のシステム実施例を示す。図15Aおよび15Bについて前述したように、メモリデバイスは、單一シリアル入力ポート(SIP)、單一シリアル出

力ポート(SOP)、入力イネーブル(IPE)ポートおよび出力イネーブル(OPE)ポートのペア、ならびに、対応する入力イネーブルエコー(IPEQ)ポートおよび出力イネーブルエコー(OPEQ)ポートのペアを含む。このカスケード構成では、あらゆるデバイスにシリアルクロック出力ポート(SCLK0)が追加される。さらにシリアルクロック入力ポート名は、シリアルクロック出力ポート(SCLK0)と区別するために、SCLK1に変更される。SCLK1信号とSCLK0信号との間のいかなる位相差も一致(または同期化)させるために、位相ロックループ(PLL)またはデジタル位相ロックループ(DLL)回路などの追加の回路を、あらゆるデバイスで使用することもできる。

## 【0079】

10 フラッシュコアアーキテクチャ実施に関するカスケード化メモリデバイスのいくつかの動作の例が、以下の表3に示される。表3は、ターゲットデバイスアドレス(TDA)、可能なOP(動作)コード、ならびに、対応する列アドレス、行/バンクアドレス、および入力データの状態を列挙する。

## 【0080】

【表3】

| 動作                | ターゲットデバイスアドレス(1バイト) | OPコード(1バイト) | 列アドレス(2バイト) | 行/バンクアドレス(3バイト) | 入力データ(1バイトから2112バイト) |

|-------------------|---------------------|-------------|-------------|-----------------|----------------------|

| ページ読み取り           | tda                 | 00h         | 有効          | 有効              | -                    |

| ランダムデータ読み取り       | tda                 | 05h         | 有効          | -               | -                    |

| コピー用のページ読み取り      | tda                 | 35h         | -           | 有効              | -                    |

| コピー用のターゲットアドレス入力  | tda                 | 8Fh         | -           | 有効              | -                    |

| シリアルデータ入力         | tda                 | 80h         | 有効          | 有効              | 有効                   |

| ランダムデータ入力         | tda                 | 85h         | 有効          | -               | 有効                   |

| ページプログラミング        | tda                 | 10h         | -           | -               | -                    |

| ロック消去             | tda                 | 60h         | -           | 有効              | -                    |

| ステータス読み取り         | tda                 | 70h         | -           | -               | -                    |

| ID読み取り            | tda                 | 90h         | -           | -               | -                    |

| 構成レジスタ書き込み        | tda                 | A0h         | -           | -               | 有効(1バイト)             |

| DN(デバイス名)エントリ書き込み | 00h                 | B0h         | -           | -               | -                    |

| リセット              | tda                 | FFh         | -           | -               | -                    |

| バンク選択             | tda                 | 20h         | -           | 有効(バンク)         | -                    |

10

20

30

40

表3: コマンドセット

## 【0081】

本発明のいくつかの実施形態では、図13Aのシステム1300または図13Bのシステム1310における各デバイスが、シリアル入力データ内のターゲットデバイスアドレス(tda)として使用可能な固有デバイス識別子を有することができる。シリアル入力データを受信した場合、フラッシュメモリデバイスは、シリアル入力データ内のターゲットデバイスアドレスフィールドを解析すること、および、デバイスがターゲットデバイスであるかどうかをターゲットデバイスアドレスとデバイスの固有デバイス識別番号とを相關させることによって判別することが可能である。

50

**【 0 0 8 2 】**

表4は、図13Aおよび13Bに関して説明されたシステムを含む、本発明の諸実施形態に従った入力データストリームの好ましい入力シーケンスを示す。コマンド、アドレス、およびデータは、最上位ビットから始まり、逐次、メモリデバイス1500へシフトイン、およびメモリデバイス1500からシフトアウトされる。シリアル入力信号(SIP)は、入力ポートイネーブル(IPE)が高の間に、シリアルクロック(SCLK)の立ち上がり時にサンプリングされる。コマンドシーケンスは1バイトのターゲットデバイスアドレス(「tda」)および1バイトの動作コードで始まり、代わりにコマンドコード(表3の「cmd」)と呼ぶこともできる。シリアル入力信号を最高位ビットの1バイトのターゲットデバイスアドレスで開始することにより、デバイスは、受信された任意の追加入力データの処理に先立って、ターゲットデバイスアドレスフィールドを解析することができる。メモリデバイスは、ターゲットデバイスでない場合、シリアル入力データを処理に先立って他のデバイスに転送し、追加の処理時間およびリソースを節約することができる。10

**【 0 0 8 3 】**

【表4】

| 動作               | 第1<br>バイ<br>ト | 第2<br>バイ<br>ト | 第3<br>バイ<br>ト | 第4<br>バイ<br>ト | 第5<br>バイ<br>ト | 第6<br>バイ<br>ト | 第7<br>バイ<br>ト | 第8<br>バイ<br>ト | .. | 第2116<br>バイ<br>ト | .. | 第2119<br>バイ<br>ト |

|------------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|----|------------------|----|------------------|

| ページ読み取り          | tda           | cmd           | ca            | ca            | ra            | ra            | ra            | -             | -  | -                | -  | -                |

| ランダムデータ読み取り      | tda           | cmd           | ca            | ca            | -             | -             | -             | -             | -  | -                | -  | -                |

| コピー用のページ読み取り     | tda           | cmd           | ra            | ra            | ra            | -             | -             | -             | -  | -                | -  | -                |

| コピー用のターゲットアドレス入力 | tda           | cmd           | ra            | ra            | ra            | -             | -             | -             | -  | -                | -  | -                |

| シリアルデータ入力        | tda           | cmd           | ca            | ca            | ra            | ra-           | ra            | data          | .. | data             | .. | data             |

| ランダムデータ入力        | tda           | cmd           | ca            | ca            | data          | data          | data          | data          | .. | data             | -  | -                |

| ページログラミング        | tda           | cmd           | -             | -             | -             | -             | -             | -             | -  | --               | -  | -                |

| ロック消去            | tda           | cmd           | ra            | ra            | ra            | -             | -             | -             | -  | -                | -  | -                |

| ステータス読み取り        | tda           | cmd           | -             | -             | -             | -             | -             | -             | -  | -                | -  | -                |

| ID読み取り           | tda           | cmd           | -             | -             | -             | -             | -             | -             | -  | -                | -  | -                |

| 構成レジスタ書き込み       | tda           | cmd           | data          | -             | -             | -             | -             | -             | -  | -                | -  | -                |

| DNエントリ書き込み       | tda           | cmd           | -             | -             | -             | -             | -             | -             | -  | -                | -  | -                |

| リセット             | tda           | cmd           | -             | -             | -             | -             | -             | -             | -  | --               | -  | -                |

表4: バイトモードでの入力シーケンス

## 【0084】

1バイトのTDAがデバイスにシフトされ、その後に1バイトのcmbコードが続く。最上位ビット(MSB)はSIP上で開始され、各ビットはシリアルクロック(SCLK)の立ち上がりでラッチされる。コマンドに応じて、1バイトのコマンドコードの後に、列アドレスバイト、行アドレスバイト、バンクアドレスバイト、データバイト、ならびに/あるいは、組み合わせまたは無しを続けることができる。

## 【0085】

本発明の諸実施形態では、フラッシュデバイス上の信号バスが完全に多重化される。コマンド、アドレス、およびデータ入力/出力は、同じピンを共用することができる。一例として、コマンドシーケンスは、通常、1バイトのターゲットデバイスアドレスラッチャイクル、1バイトのコマンドラッチャイクル、アドレスラッチャイクル(たとえば列アドレス用に2バイト、行アドレス用に3バイト)、および、必要であれば1バイトまたはそれ以上

10

20

30

40

50

(最高2112バイト)のデータ入力ラッチサイクルからなる。IPEが高から低への移行を実行した後、コマンド命令のあらゆるセットの後には2つの特別クロックサイクルが続く。デイジーチェーンカスケード化構成の場合、低へのIPE移行後のクロックサイクル遅延は、構成内のカスケード化されたデバイスの数に依存する可能性がある。本発明の諸実施形態では、シリアル入力シーケンスは「バイトベース」であり、これは8クロックサイクル単位に対してIPEおよびSIPが有効であるものとすることを意味する。全バイトの完了(すなわち8クロックサイクル)前に、IPEが高から低への移行を実行する場合、対応するコマンドおよび/またはアドレスシーケンスは、デバイスによって無視されることになる。データ入力シーケンスの場合、入力データの最後の未完了バイトは無視されることになるが、入力データの先行完了バイトは有効となる。

10

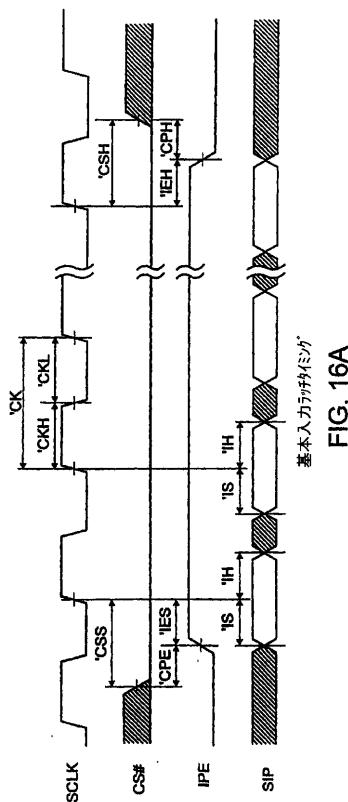

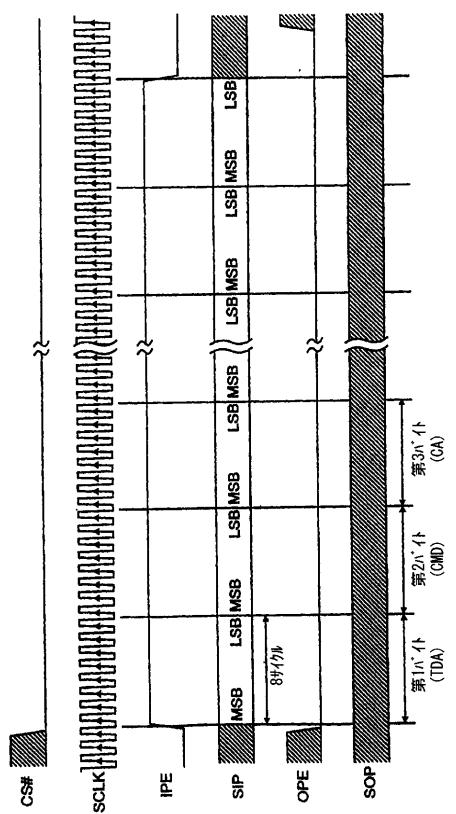

#### 【0086】

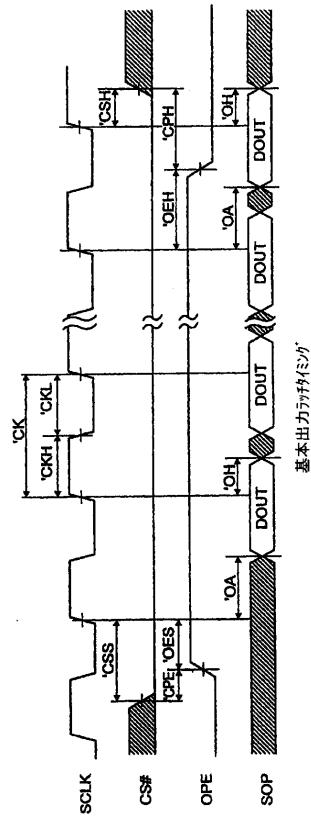

図16A、16B、17A、および17Bは、本発明のメモリデバイスでのシリアルデータの入力および出力ラッチタイミングに関する例示的タイミング図を示す。

#### 【0087】

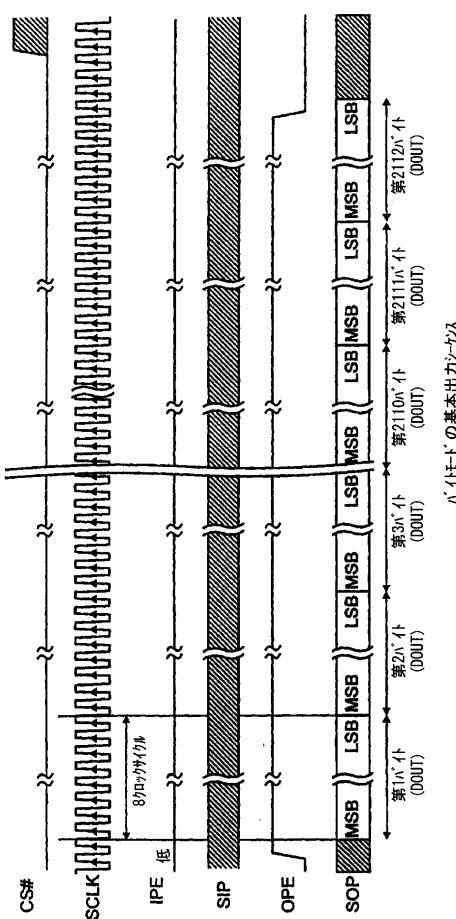

図16Aは、本発明の諸原理に従った基本入力ラッチタイミングを示す。シリアル入力ポート(SIP)でデータを受信した場合、TDA/コマンド/アドレス/データ入力が、SIPポートを介してアサートされ、CS#が低およびIPEが高の際に、SCLKの立ち上がりでキャプチャされる。図16Bは、バイトモードの入力シーケンスを詳細に示すクロック図である。入力データは、SIP上の最初の最上位ビット(MSB)でデバイスにシフトされなければならず、各ビットはSCLKの立ち上がりでラッチされる。

20

#### 【0088】

図17Aは、本発明の諸原理に従った基本出力ラッチタイミングを示す。デバイスからシリアル出力ポート(SOP)を介してデータを送信する場合、データは、CS#が低およびOPEが高の際に、SCLKの立ち上がりでSOPポートを介してアサートされる。SOP上のシリアルデータ出力は、SCLKの立ち上がりで同期的にシフトアウトされる。図17Bは、バイトモードの出力シーケンスを詳細に示すクロック図である。出力データは、SOP上の最初の最上位ビット(MSB)でデバイスからシフトされ、各ビットはSCLKの立ち上がりで同期化される。

#### 【0089】

前述のように、メモリデバイスはデュアルバンクメモリとすることが可能であり、各バンクは任意のシリアルリンクによってアクセス可能である。別の方法として、本発明の他の実施形態では、メモリデバイスは單一メモリバンクおよび单シリアルインターフェースを含むことが可能である。メモリデバイスのシリアルインターフェースは、機能豊富な動作をサポートしながら、従来のパラレルインターフェース方式よりもデータスループットをかなり向上させる。たとえば、プログラム動作は、(2K+64)バイトページ上で200 μsで実行可能であり、消去動作は(128K+4K)バイトブロック上で1.5msで実行可能である。オンクリップ書き込みコントローラを使用して、すべてのプログラムを自動化すること、ならびに、使用される場合はパルス反復、ならびにデータの内部検証およびマージニング(margining)を含む、機能を消去することができる。集中書き込みシステムでは、実時間マップアウトアルゴリズムを伴うECC(誤り訂正コード)を使用して、メモリデバイス内の100Kプログラム/消去サイクルの拡張信頼性を強化することができる。

30

#### 【0090】

当業者であれば、本発明の様々な態様の有用性が明らかとなろう。本明細書の任意およびすべての例示または例示的言い回し(たとえば「などの」)の使用は、単に本発明をより良く解明することを意図しており、特に主張のない限り、本発明の範囲に制限を課すものではない。本明細書のいかなる言い回しも、いずれかの非請求要素を本発明の実施に不可欠であるとして示すものと解釈されるべきではない。

#### 【0091】

以上、本発明について、時折、その好ましい例示的実施形態に関して説明してきた。当業者であれば、本開示を再検討することにより、添付の特許請求の範囲の範囲および精神における、多数の他の実施形態、修正、および変形が想起されることになろう。

40

50

**【図面の簡単な説明】****【0092】**

【図1A】本発明の様々な態様に従った、同時動作を可能にする例示的なメモリデバイスを示す高水準図である。

【図1B】本発明の様々な態様に従った、同時動作を可能にする例示的なメモリデバイスを示す高水準図である。

【図1C】本発明の様々な態様に従った、同時動作を可能にする例示的なメモリデバイスを示す高水準図である。

【図2A】本発明の諸態様に従った、例示的なメモリデバイスを示す高水準ブロック図である。10

【図2B】本発明の実施形態に従った、図2Aに示されたシリアルデータリンクを示す概略図である。

【図2C】本発明の実施形態に従った、図2Aに示された直列並列入力レジスタブロックを示す概略図である。

【図2D】本発明の実施形態に従った、図2Aに示されたバス交換回路を示す概略図である。。

【図2E】本発明の実施形態に従った、図2Aに示された並列直列出力レジスタブロックを示す概略図である。

【図3A】本発明の様々な態様に従った、メモリデバイスによって実行されるメモリ動作を示すタイミング図である。20

【図3B】本発明の様々な態様に従ったデバイスにおける、図3Aのメモリ動作を示す流れ図である。

【図4】本発明の様々な態様に従った、メモリデバイスによって実行されるメモリ動作を示すタイミング図である。

【図5A】本発明の様々な態様に従った、メモリデバイスによって実行されるメモリ動作を示すタイミング図である。

【図5B】本発明の様々な態様に従ったデバイスにおける、図5Aのメモリ動作を示す流れ図である。

【図6A】本発明の様々な態様に従った、メモリデバイスによって実行されるメモリ動作を示すタイミング図である。30

【図6B】本発明の様々な態様に従ったデバイスにおける、図6Aのメモリ動作を示す流れ図である。

【図7】本発明の様々な態様に従った、メモリデバイスによって実行されるメモリ動作を示すタイミング図である。

【図8A】本発明の様々な態様に従ったメモリデバイスにおいて実行される同時メモリ動作を示すタイミング図である。

【図8B】本発明の様々な態様に従ったメモリデバイスにおいて実行される同時メモリ動作を示すタイミング図である。

【図8C】本発明の様々な態様に従ったメモリデバイスにおいて実行される同時メモリ動作を示すタイミング図である。40

【図9】本発明の様々な態様に従った、複数のシリアルデータリンクインターフェースと複数のメモリバンクとの間でのデータ転送を制御する方法を示す流れ図である。

【図10】本発明の様々な態様に従った、複数のシリアルデータリンクインターフェースと複数のメモリバンクとの間でのデータ転送を制御する方法を示す流れ図である。

【図11】本発明の様々な態様に従ったデバイス内の、メモリデバイスのピン配置構成を示すブロック図である。

【図12】本発明に従った、仮想多重リンク機能の様々な態様が備えられたメモリデバイスで実行されるメモリ動作を示すタイミング図である。

【図13A】本発明の様々な態様に従った、多数のメモリデバイスのカスケード化構成を示す高水準ブロック図である。50

【図13B】本発明の様々な態様に従った、多数のメモリデバイスの代替カスケード化構成を示す高水準ブロック図である。

【図14】本発明の諸態様に従った、カスケード化構成におけるメモリデバイス上で実行されるメモリ動作を示す簡略化タイミング図である。

【図15A】本発明の諸態様に従った例示的メモリデバイスを示す高水準ブロック図である。

【図15B】図15Aに示されたメモリデバイスで使用可能なシリアルリンクインターフェースをより詳細に示すブロック図である。

【図16A】入力ラッチタイミングを示すタイミング図である。

【図16B】バイトモードの入力シーケンスタイミングを示すタイミング図である。 10

【図17A】出力ラッチタイミングを示すタイミング図である。

【図17B】バイトモードの出力シーケンスタイミングを示すタイミング図である。

【符号の説明】

【0093】

|     |                    |    |

|-----|--------------------|----|

| 202 | メモリバンクA            |    |

| 204 | メモリバンクB            |    |

| 205 | インターフェース回路         |    |

| 206 | アドレスおよびデータパス交換回路   |    |

| 207 | インターフェース回路         |    |

| 208 | 制御インターフェース         | 20 |

| 210 | ステータス/IDレジスタ回路     |    |

| 212 | SAおよびページバッファ回路ブロック |    |

| 214 | 行デコーダ              |    |

| 216 | 制御およびプリデコーダ        |    |

| 218 | SAおよびページバッファ       |    |

| 220 | 行デコーダ              |    |

| 222 | 制御およびプリデコーダ        |    |

| 230 | シリアルデータリンク         |    |

| 232 | 直列並列入力レジスタブロック     |    |

| 234 | 並列直列出力レジスタブロック     | 30 |

| 236 | シリアルデータリンク         |    |

| 238 | 並列直列出力レジスタブロック     |    |

| 240 | 直列並列入力レジスタブロック     |    |

【図 1 A】

FIG. 1A

【図 1 B】

FIG. 1B

【図 1 C】

FIG. 1C

【図 2 A】

FIG. 2A

【図 2 B】

FIG. 2B

【図 2 C】

FIG. 2C

【図 2 D】

FIG. 2D

【図 2 E】

FIG. 2E

【図 3 A】

FIG. 3A

【図3B】

FIG. 3B

【図4】

【図 6 A】

FIG. 6A

【図 6 B】

FIG. 6B

【図 7】

FIG. 7

【図 8 A】

FIG. 8A

【図 8 B】

FIG. 8B

【図 8 C】

FIG. 8C

【図 9】

FIG. 9

FIG. 10

【 义 1 1 】

1100 / FIG. 11

【図13A】

FIG. 13A

〔 図 12 〕

FIG. 12

【図13B】

1310

【図 14】

【図 15 A】

FIG. 15A

【図 15 B】

FIG. 15B

【図 16 A】

FIG. 16A

【図16B】

FIG. 16B

【図17A】

EIG 17A

【図17B】

FIG. 17B

---

フロントページの続き

(31)優先権主張番号 60/847,790

(32)優先日 平成18年9月27日(2006.9.27)

(33)優先権主張国 米国(US)

(72)発明者 ハクジュン・オ

カナダ・オンタリオ・K2T・1J3・カナタ・カンビオー・クレッセント・21

(72)発明者 ホン・ボム・ピヨン

カナダ・オンタリオ・K2M・2E1・カナタ・リバーグリーン・クレセント・16

(72)発明者 ジン・キ・キム

カナダ・オンタリオ・K2K・3H6・カナタ・アイロンサイド・コート・46

審査官 園田 康弘

(56)参考文献 特開2000-315185(JP,A)

特開平05-210981(JP,A)

特開2000-207889(JP,A)

特開2005-190648(JP,A)

特開2000-163969(JP,A)

特開昭63-081691(JP,A)

特開平09-022393(JP,A)

特開2000-030499(JP,A)

特開2003-043116(JP,A)

特開2003-317490(JP,A)

特開2003-308698(JP,A)

(58)調査した分野(Int.Cl., DB名)

G11C 16/06

G01R 31/28

G06F 12/06

G06F 13/37

G11C 16/02

G11C 16/04