(19) 日本国特許庁(JP)

## (12) 特許公報(B1)

(11) 特許番号

特許第5866491号

(P5866491)

(45) 発行日 平成28年2月17日(2016.2.17)

(24) 登録日 平成28年1月8日(2016.1.8)

(51) Int.Cl.

G 11 C 15/04 (2006.01)

F 1

G 11 C 15/04 631 E

G 11 C 15/04 631 F

請求項の数 11 (全 19 頁)

(21) 出願番号 特願2015-550689 (P2015-550689)

(86) (22) 出願日 平成25年12月20日 (2013.12.20)

(86) 国際出願番号 PCT/US2013/076848

(87) 国際公開番号 WO2014/105683

(87) 国際公開日 平成26年7月3日 (2014.7.3)

審査請求日 平成27年9月7日 (2015.9.7)

(31) 優先権主張番号 13/730,524

(32) 優先日 平成24年12月28日 (2012.12.28)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 595020643

クアアルコム・インコーポレイテッド

QUALCOMM INCORPORATED

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100158805

弁理士 井関 守三

(74) 代理人 100194814

弁理士 奥村 元宏

最終頁に続く

(54) 【発明の名称】 3値連想メモリ(TCAM)のための静的NANDセル

## (57) 【特許請求の範囲】

## 【請求項1】

静的3値連想メモリ(TCAM)であって、

第1のプルダウントランジスタと第1のプルアップトランジスタとに結合されたキーセルと、

第2のプルダウントランジスタと第2のプルアップトランジスタとに結合されたマスクセルと、前記第1のプルダウントランジスタと前記第2のプルダウントランジスタとは、並列に接続され、前記第1のプルアップトランジスタと前記第2のプルアップトランジスタとは、直列に接続される、

前記第1のプルダウントランジスタと前記第2のプルダウントランジスタとに結合され、前記第1のプルアップトランジスタと前記第2のプルアップトランジスタとにさらに結合された一致ライン出力と

を備える、TCAM。

## 【請求項2】

前記マスクセルは、スタティックランダムアクセスメモリ(SRAM)ビットセルである、

請求項1に記載のTCAM。

## 【請求項3】

前記キーセルは、スタティックランダムアクセスメモリ(SRAM)セルとXNOR論理とを含む、

10

20

請求項 1 に記載の T C A M。

**【請求項 4】**

前記第 1 のプルダウントランジスタと前記第 1 のプルアップトランジスタとに結合された前記 X N O R 論理の出力をさらに備える、

請求項 3 に記載の T C A M。

**【請求項 5】**

前記キーセルへの探索ライン入力をさらに備える、

請求項 1 に記載の T C A M。

**【請求項 6】**

前記第 1 のプルダウントランジスタと前記第 2 のプルダウントランジスタとに結合された中間一致ラインをさらに備える、

請求項 1 に記載の T C A M。

**【請求項 7】**

静的 3 値連想メモリ (T C A M) 内の方法であって、

第 1 のプルダウントランジスタと第 1 のプルアップトランジスタにおいてキーセルの出力を受信することと、

第 2 のプルダウントランジスタと第 2 のプルアップトランジスタにおいてマスクセルの出力を受信することと、前記第 1 のプルダウントランジスタと前記第 2 のプルダウントランジスタとは、並列に接続され、前記第 1 のプルアップトランジスタと前記第 2 のプルアップトランジスタとは、直列に接続される、

前記キーセルの前記出力と前記マスクセルの前記出力とに少なくとも部分的に基づいて一致ライン出力を設定することとを備える方法。

**【請求項 8】**

前記一致ライン出力を設定することは、

前記キーセルの前記出力が一致を示すとき、前記第 1 のプルダウントランジスタを介して、低値に前記一致ライン出力を設定することと、

前記マスクセルの前記出力が前記一致を示すとき、前記第 2 のプルダウントランジスタを介して、前記低値に前記一致ライン出力を設定することと、

前記マスクセルの前記出力と前記キーセルの前記出力とが不一致を示すとき、前記第 1 のプルアップトランジスタと前記第 2 のプルアップトランジスタとを介して、高値に前記一致ライン出力を設定することとを備える、請求項 7 に記載の方法。

**【請求項 9】**

前の探索値比較が一致であったことを中間一致ラインが示すとき、前記キーセルの値と前記マスクセルの値とを比較することをさらに備える、

請求項 7 に記載の方法。

**【請求項 10】**

前記マスクセルは、スタティックランダムアクセスメモリ (S R A M) ビットセルである、

請求項 7 に記載の方法。

**【請求項 11】**

前記キーセルは、

スタティックランダムアクセスメモリ (S R A M) セルと X N O R 論理とを含む、請求項 7 に記載の方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

[0001] 本開示は、一般に、3 値連想メモリ (T C A M) に関する。より詳細には、本開示は、T C A M のための静的 N A N D アーキテクチャに関する。

10

20

30

40

50

**【背景技術】****【0002】**

[0002] T C A M は、一般に、インターネットプロトコル( I P )アドレス転送のためにルータおよびイーサネット( 登録商標 )スイッチ中で使用される。記憶要素は、一般に、動的N O R / N A N D タイプセルを使用するように設計される。

**【0003】**

[0003] 連想メモリ( C A M )は、読み取り動作、書き込み動作、および比較動作をサポートする。C A M 中のエントリとしての同じ幅の(たとえば、ビット/ワード)の比較バスは、クロックエッジにおける入力である。比較バスのデータは、C A M 中のあらゆるエントリと同時に比較される。すなわち、比較は平行して行われ、したがって、バスは、1つのクロックサイクル中にC A M 中のあらゆるエントリと比較され得る。エントリ中のあらゆるビットが比較バス中の対応するビットに一致するとき、エントリは一致となる。代替的に、エントリ中のいずれかのビットが比較バス中の対応するビットに一致しないとき、エントリは不一致となる。C A M 中のエントリのビットは0または1である。10

**【0004】**

[0004] T C A M は、セルに記憶され得るマスク値を伴ったC A M と同様のものである。マスク値は、ローカルマスクと呼ばれることがある。マスク値は比較ビットと比較されず、したがって、比較結果は常に一致になる。

**【0005】**

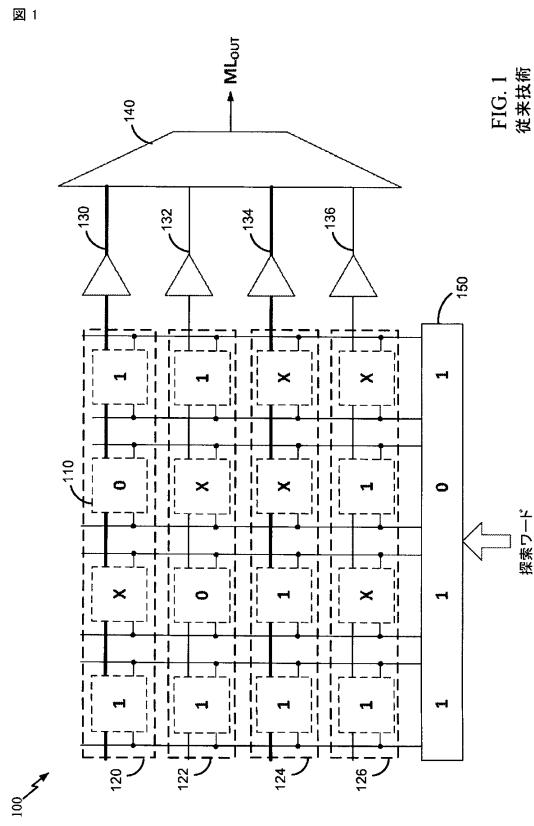

[0005] 図1に、従来のT C A M 1 0 0 のアーキテクチャを示す。図1に示すように、「1 1 0 1」などの探索ワードは、T C A M 1 0 0 のレジスタ1 5 0への入力である。探索ワードは、T C A M セル1 1 0 に記憶された値と比較される。T C A M は、一般に、ステージごとに1 6 個のT C A M セルを有する。探索は、T C A M セル1 1 0 にわたって同時に行われる。T C A M セル1 1 0 のコンテンツは、高ビット(1)、低ビット(0)、またはマスク値( X )であり得る。探索の前に、T C A M セルの各セット1 2 0 ~ 1 2 6 の一致ライン1 3 0 ~ 1 3 6 が高に設定される。一致ライン1 3 0 ~ 1 3 6 は、優先度エンコーダ1 4 0への入力である。T C A M 1 0 0 は、探索ワードラインに一致するT C A M セルのセットのアドレスを出力する( M L o u t )。探索が並列探索であるので、探索は、1クロックサイクルで完了し得る。マスク値は0または1であり得、依然として、本開示では、マスク値がXと呼ばれることがあることに留意されたい。2030

**【0006】**

[0006] 一例として、図1に示すように、T C A M セルの第1のセット1 2 0 は、「1 X 0 1」に設定され、T C A M セルの第2のセット1 2 2 は、「1 0 X 1」に設定され、T C A M セルの第3のセット1 2 4 は、「1 1 X X 」に設定され、T C A M セルの第4のセット1 2 6 は、「1 X 1 X 」に設定される。探索ビットとT C A M セルのコンテンツを比較するときに、T C A M セルのコンテンツがマスク値Xであるとき、比較は一致をもたらすことになる。したがって、図1に示す例によれば、T C A M セルの第1のセット1 2 0 とT C A M セルの第3のセット1 2 4 とは、レジスタ1 5 0 中の探索ワードに一致する。したがって、T C A M セルの第1のセット1 2 0 およびT C A M セルの第3のセット1 2 4 の一致ライン1 3 0 および1 3 4 は一致を示し、優先度エンコーダ1 4 0 は、T C A M セルの第1のセット1 2 0 およびT C A M セルの第3のセット1 2 4 のアドレスを出力する。40

**【0007】**

[0007] 従来のT C A M アーキテクチャは、動的回路であり、高い動的消費電力を有する。場合によっては、T C A M は、動的N A N D アーキテクチャを有し得る。他の場合には、T C A M は、動的N O R アーキテクチャを有し得る。

**【0008】**

[0008] 動的N O R T C A M アーキテクチャでは、一致ラインは、高にプリチャージされ、不一致を示すために低を評価する。比較の大部分は不一致をもたらし、したがって、動的N O R は、不一致を示すための高から低への切替えの結果として電力消費量が増加す50

る。さらに、プリチャージ信号が各クロックサイクル中で各一致ラインによって使用されるので、動的NORは、複雑なタイミング制御を有する。

#### 【0009】

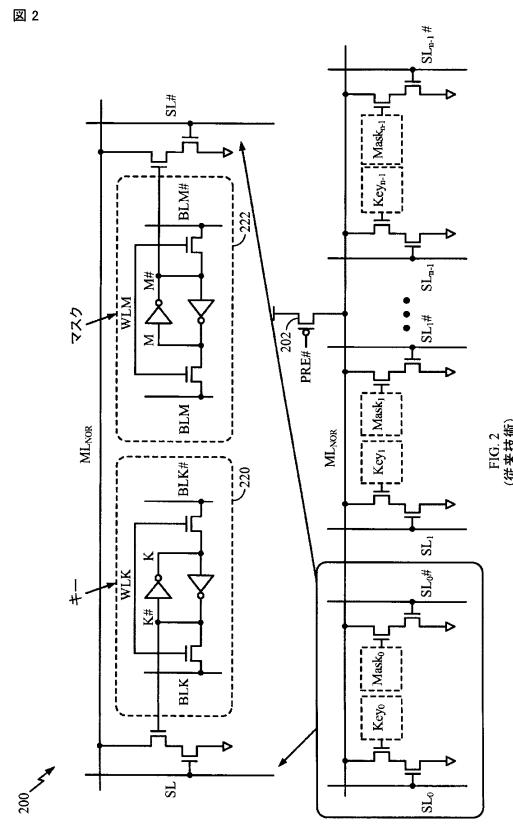

[0009]図2に、従来の動的NOR TCAM200を示す。図2に示すように、動的NOR TCAM200は、キーセルKey<sub>0</sub>~Key<sub>n-1</sub>とマスクセルMask<sub>0</sub>~Mask<sub>n-1</sub>とを含む。一般に、図2のNOR TCAM200などのNOR TCAMは、16個のキーセルとマスクセルとを有し得る。データは、探索ライン(SL<sub>0</sub>~SL<sub>n-1</sub>およびSL<sub>0</sub>#~SL<sub>n-1</sub>#)を介して入力される。データは、キーセルKey<sub>0</sub>~Key<sub>n-1</sub>とマスクセルMask<sub>0</sub>~Mask<sub>n-1</sub>とに記憶された値と比較される。一致ラインML<sub>NOR</sub>は、プルアップトランジスタ202からのプリチャージラインPRE#を介して高にプリチャージされる。探索ライン(SL<sub>0</sub>~SL<sub>n-1</sub>およびSL<sub>0</sub>#~SL<sub>n-1</sub>#)のうちの1つを介して入力されたデータと、セルKey<sub>0</sub>~Key<sub>n-1</sub>、Mask<sub>0</sub>~Mask<sub>n-1</sub>のうちの1つに記憶されたデータとの間に不一致があるとき、一致ラインML<sub>NOR</sub>は低を評価することになる。セルKey<sub>0</sub>~Key<sub>n-1</sub>、Mask<sub>0</sub>~Mask<sub>n-1</sub>のすべての値が入力データに一致すると、一致ラインは高にとどまる。

10

#### 【0010】

[0010]キーセルKey<sub>0</sub>~Key<sub>n-1</sub>の構造は、拡大されたキーセル220に示されており、マスクセルMask<sub>0</sub>~Mask<sub>n-1</sub>の構造は、拡大されたマスクセル222に示されている。拡大されたキーセル220に示すように、キーセルKey<sub>0</sub>~Key<sub>n-1</sub>は、SRAMセルを介して実装される。比較動作中に、キーバーK#は、探索ラインSLとの論理積がとられる。キーセルKey<sub>0</sub>~Key<sub>n-1</sub>は、ビットラインB<sub>L</sub>Kと、ビットラインB<sub>L</sub>K#と、ワードラインW<sub>L</sub>Kとを含む。

20

#### 【0011】

[0011]拡大されたマスクセル222に示すように、マスクセルMask<sub>0</sub>~Mask<sub>n-1</sub>は、SRAMセルを介して実装される。比較動作中に、マスクバーM#は、探索ラインB<sub>L</sub>S<sub>L</sub>#との論理積がとられる。マスクセルMask<sub>0</sub>~Mask<sub>n-1</sub>は、ビットラインB<sub>L</sub>Mと、ビットラインバーB<sub>L</sub>M#と、ワードラインW<sub>L</sub>Mとを含む。

#### 【0012】

[0012]表1は、動的NAND TCAMのための真理値表を示す。表1に、マスクセル(M)、キーセル(K)、および探索ライン(SLおよびSL#)の値に基づいた一致ラインの値を示す。状態が、記憶要素(キーセルおよびマスクセル)の状態を指すことに留意されたい。キービットが0の値を有するとき、状態は0であり、キービットが1の値を有するとき、状態は1であり、マスクビットとキービットとの両方が1であるとき、状態はXである。Xの状態は、一致も不一致もない、むしろ、探索ラインの値とマスクセルおよびキーセルの値との間の比較がないマスク状態を指す。したがって、一致ラインは、常に一致を示す。

30

## 【表1】

| 表1 |                   |              |                    |                        |                        |

|----|-------------------|--------------|--------------------|------------------------|------------------------|

| 状態 | マスク<br>ビット<br>(M) | キービット<br>(K) | 探索<br>ライン<br>(S L) | 探索<br>ラインバー<br>(S L #) | 一致<br>ライン<br>(M L NOR) |

| 0  | 1                 | 0            | 0                  | 1                      | 1                      |

| 0  | 1                 | 0            | 1                  | 0                      | 0                      |

| 1  | 0                 | 1            | 0                  | 1                      | 0                      |

| 1  | 0                 | 1            | 1                  | 0                      | 1                      |

| X  | 1                 | 1            | X                  | X                      | 1                      |

| -  | 0                 | 0            | -                  | -                      | 不可                     |

10

20

## 【0013】

[0013]表1に示すように、キービットと探索ラインとが異なる値を有するとき、一致ラインは、0（低）になり、不一致を示すことになる。同様に、マスクビットと探索ラインバーの両方が異なる値を有するとき、一致ラインは、0になり、不一致を示すことになる。すなわち、キービットが0であり（たとえば、キービットバー（K #）が1であり）、探索ラインが1であるとき、またはマスクビットが0であり（たとえば、マスクビットバー（M #）が1であり）、探索ラインバーが1であるとき、フルダウントランジスタは、一致ラインを低に引き下げるためにアクティブ化されることになる。さらに、キービットと探索ラインとが同じ値を有するとき、一致ラインは、1（高）になり、一致を示すことになる。同様に、マスクビットと探索ラインバーの両方が同じ値を有するとき、一致ラインは、1になり、一致を示すことになる。さらに、マスクビットとキービットの両方が1であるとき、状態はXである。すなわち、一致ラインは、探索ラインの値にかかわらず、高にとどまり、一致を示すことになる。

30

## 【0014】

[0014]上記で説明したように、動的NOR TCAMでは、一致ラインと探索ラインとは、あらゆるサイクルの始めに高にプリチャージされ、一致ラインは、不一致を示すために低を評価する。TCAMでのセルの比較の大部分は不一致をもたらす。したがって、不一致を示すときの高から低への切替えの結果として、動的NOR TCAMの電力消費量は増加する。場合によっては、一致ラインは、電力消費量を低減するために、低にプリディスチャージされ得る。依然として、その結果、一致ラインがプリディスチャージされたときでも、プリチャージ動作は、あらゆるサイクルの始めに一致ラインをチャージする。したがって、一致ラインのプリチャージは、電力消費量の増加さらには制御回路の増加につながる。

40

## 【0015】

[0015]動的NAND TCAMアーキテクチャでは、一致ラインは、高にプリチャージされ、一致を示すために低を評価する。すなわち、プリチャージ信号は、一致ラインを高に設定するために、あらゆるサイクル中に各マッチラインのために使用される。マスクセルまたはキーセルの状況に応じて、一致ラインは、低に引き下げられるか、または高にとどまり得る。各中間一致ラインは、マスクセルとキーセルとに関連付けられる。さらに、各キーセルは、XNOR論理をさらに含む。動的NAND TCAMは、直列動作を使用

50

する。したがって、前の中間一致ライン( $n - 2$ )が一致を示すために低に引き下げられたとき、中間一致ライン( $n - 1$ )はディスチャージし得る(たとえば、探索ラインの値と比較し得る)。すなわち、動作は、一致があるとき、1つの中間一致ライン( $n - 2$ )から後続の中間一致ライン( $n - 1$ )に継続し、不一致があるとき、中間一致ラインを進行するのを停止する。

#### 【0016】

[0016]一致ライン評価中の従来の動的NAND TCAMの電力消費量は、直列動作のために従来の動的NOR TCAMの電力消費量よりも小さくなり得る。依然として、従来の動的NAND TCAMは、電荷共有から生じる誤りのために望ましくないことがある。

10

#### 【0017】

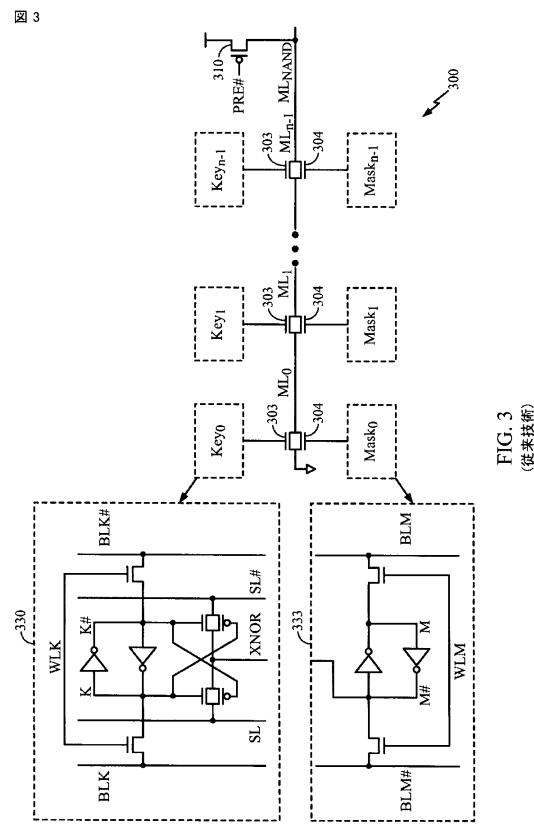

[0017]図3に、従来の動的NAND TCAM 300を示す。図3に示すように、動的NANDアーキテクチャ300は、プルアップトランジスタ310からプリチャージラインPRE#によってチャージされる一致ライン出力ML<sub>NAND</sub>を含む。一致ライン出力ML<sub>NAND</sub>は、一連の中間一致ラインML<sub>0</sub>～ML<sub>n-1</sub>に接続される。中間一致ラインML<sub>0</sub>～ML<sub>n-1</sub>の各々は、並列に接続されたトランジスタ(たとえば、トランスミッショングート)を介してマスクセルMask<sub>0</sub>～Mask<sub>n-1</sub>およびキーセルKey<sub>0</sub>～Key<sub>n-1</sub>に結合される。並列に接続されたトランジスタは、キーセルKey<sub>0</sub>～Key<sub>n-1</sub>に結合されたキーN MOSトランジスタ303と、マスクセルMask<sub>0</sub>～Mask<sub>n-1</sub>に結合されたマスクN MOSトランジスタ304とを含む。

20

#### 【0018】

[0018]マスクセルMask<sub>0</sub>～Mask<sub>n-1</sub>のコンテンツは、拡大されたマスクセル333に示されている。拡大されたマスクセル333に示すように、マスクセルMask<sub>0</sub>～Mask<sub>n-1</sub>は、マスク値Mと、マスク値バーM#と、マスクワードラインWLMと、マスクビットラインBLMと、マスクビットラインバーBLM#とを含むSRAMセルである。キーセルKey<sub>0</sub>～Key<sub>n-1</sub>のコンテンツは、拡大されたキーセル330に示されている。拡大されたキーセル330に示すように、キーセルKey<sub>0</sub>～Key<sub>n-1</sub>は、X NOR論理を用いるSRAMセルである。キーセルKey<sub>0</sub>～Key<sub>n-1</sub>は、探索ラインSLと、探索ラインバーSL#と、キービットラインBLKと、キービットラインバーBLK#と、キー値Kと、キーバー値K#と、キー書き込みラインWLKと、出力ラインXNORとをさらに含む。

30

## 【表2】

| 表2 |                   |              |                    |      |                                       |              |

|----|-------------------|--------------|--------------------|------|---------------------------------------|--------------|

| 状態 | マスク<br>ビット<br>(M) | キービット<br>(K) | 探索<br>ライン<br>(S L) | XNOR | $M L_i \rightarrow M L_{i+1}$<br>への伝搬 | $M L_{NAND}$ |

| 0  | 1                 | 0            | 0                  | 1    | オン                                    | 0/1          |

| 0  | 1                 | 0            | 1                  | 0    | オフ                                    | 浮動           |

| 1  | 1                 | 1            | 0                  | 0    | オフ                                    | 浮動           |

| 1  | 1                 | 1            | 1                  | 1    | オン                                    | 0/1          |

| X  | 0                 | X            | X                  | X    | オン                                    | 0/1          |

10

20

## 【0019】

[0019] 動的NAND TCAMアーキテクチャでは、 $M L_{NAND}$ は、高にプリチャージされ、一致を示すために低を評価する。マスクセルまたはキーセルの状況に応じて、 $M L_{NAND}$ は、低に引き下げられるか、または高にとどまり得る。各中間一致ライン( $M L_0 \sim M L_{N-1}$ )は、マスクセルとキーセルとに関連付けられる。動的NAND TCAMは、直列動作を使用し、したがって、前の中間一致ライン $M L_{i-1}$ が一致を示す場合、中間一致ライン $M L_i$ は、(キーセルとマスクセルとの値に応じて)低に引き下げられ得る。すなわち、一致があるとき、0(低中間一致ライン)は、1つの中間一致ライン $M L_i$ から後続の中間一致ライン $M L_{i+1}$ に伝搬する。さらに、不一致があるとき、0は、中間一致ラインを進行するのを停止する。したがって、現在の中間一致ライン $M L_i$ から後続の中間一致ライン $M L_{i+1}$ への0の伝搬はまた、前の一致ラインのすべてが一致を示したこと 30 を指定する。

## 【0020】

[0020] 中間一致ラインが直列に接続されるので、すべての中間一致ラインが評価されるまで、または不一致が決定されるまで、一致ライン出力 $M L_{NAND}$ の状態は知られない。したがって、表2に示すように、不一致がまだ決定されていないとき、一致ライン出力 $M L_{NAND}$ は0/1のいずれかになる。

## 【0021】

[0021] 現在の中間一致ライン $M L_i$ が一致を示すために低を評価するとき、動的NAND TCAMは、現在の中間一致ライン $M L_i$ から後続の中間一致ライン $M L_{i+1}$ にこの低値を伝搬する。現在の中間一致ライン $M L_i$ から後続の中間一致ライン $M L_{i+1}$ への伝搬は、表2にオンスイッチとして示されている。さらに、不一致がまだ決定されていないので、一致ライン出力 $M L_{NAND}$ は0/1のいずれかである。 40

## 【0022】

[0022] 現在の中間一致ライン $M L_i$ が不一致を示すために高にとどまるとき、動的NAND TCAMは、現在の中間一致ライン $M L_i$ から後続の中間一致ライン $M L_{i+1}$ に伝搬しない。したがって、表2は、現在の中間一致ライン $M L_i$ が不一致を示すとき、伝搬をオフとして示す。より詳細には、現在の中間一致ラインが不一致を示すとき、後続の中間一致ラインの動作は停止する。

## 【0023】

30

40

50

[0023]表2において、X N O Rの値は、キーセルからの出力の値を表す。X N O Rが0であるとき、不一致が示される。M L<sub>i</sub>などの現在の中間一致ラインは、不一致のために高にとどまる。X N O Rが1であるとき、一致が示され、一致があるとき（現在の中間一致ラインの左側の中間一致ラインも低に引き下げられた場合）、M L<sub>i</sub>などの現在の中間一致ラインが低に引き下げられる。最後に、表2において、状態は、記憶要素（キーセルおよびマスクセル）の状態を指す。キーセルが0の値を有するとき、状態は0であり、キーセルが1の値を有するとき、状態は1であり、マスクセルが0であるとき、状態はXである。すなわち、Xの状態の場合、マスクセルが0であるとき、マスクN M O Sトランジスタ304は、X N O R値にかかわらず、有効化される。より詳細には、Xの状態は、一致も不一致もない、むしろ、探索ラインの値とキーセルの値との間の比較がないマスク状態を指す。

#### 【0024】

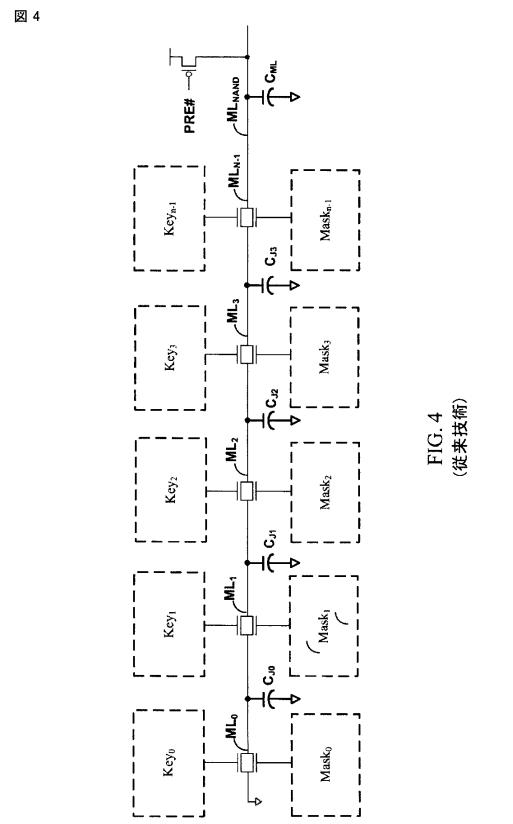

[0024]場合によっては、ディープN M O Sスタックをもつ従来の動的N A N D T C A Mは、電荷共有により機能しないことがある。図4に、ディープN M O Sスタックをもつ動的N A N Dの例を示す。プリチャージサイクル中に、すべての中間一致ライン接合キャパシタンスC<sub>J0</sub>～C<sub>J3</sub>が低にディスチャージされ得る。評価サイクル中に、M L<sub>NAND</sub>は、高にプリチャージされ、動的ノードキャパシタンスC<sub>ML</sub>が、中間一致ライン接合キャパシタンスC<sub>J</sub>のうちの1つまたは複数に露出され、1つまたは複数の中間一致ライン接合キャパシタンスC<sub>J</sub>と電荷を共有する。電荷共有の結果として、一致ライン出力M L<sub>NAND</sub>の電圧レベルは、次のインバータのしきい値電圧を下回り、誤動作をトリガし得る。

#### 【0025】

[0025]T C A Mの速度は、N M O Sスタックの深度の増加とともに増加し得る。依然として、動的N A N Dの速度は、上述の電荷共有障害により制限される。したがって、動的N O R T C A Mは、動的N A N D T C A Mの速度よりも速い速度で実行し得る。場合によっては、電荷共有から生じる障害を緩和するために、中間接合キャパシタンスC<sub>J</sub>は、V<sub>DD</sub>-V<sub>t</sub>の電圧レベルにプリチャージされ得、ここで、V<sub>DD</sub>が供給レベルであり、V<sub>t</sub>がしきい値電圧である。依然として、中間接合キャパシタンスをプリチャージすることは、エリアの増加と追加のタイミング複雑さにより望ましくないことがある。他の場合には、電荷共有から生じる障害を緩和するために、探索ラインは、動的であり、N M O Sスタックを通してV<sub>DD</sub>-V<sub>t</sub>の電圧レベルを伝搬するためにあらゆるサイクルで高にプリチャージされ得る。それにもかかわらず、探索ラインをプリチャージすることは、それが動的電力ソリューションであり、遅延を増加するので望ましくないことがある。

#### 【発明の概要】

#### 【0026】

[0026]本開示の一態様によれば、静的3値連想メモリ（T C A M）が提示される。静的T C A Mは、第1のプルダウントランジスタと第1のプルアップトランジスタとに結合されたキーセルを含む。静的T C A Mはまた、第2のプルダウントランジスタと第2のプルアップトランジスタとに結合されたマスクセルを含む。第1のプルダウントランジスタと第2のプルダウントランジスタとは、並列に接続され、第1のプルアップトランジスタと第2のプルアップトランジスタとは、直列に接続される。静的T C A Mは、第1のプルダウントランジスタと第2のプルダウントランジスタとに結合され、第1のプルアップトランジスタと第2のプルアップトランジスタとにさらに結合された一致ライン出力とをさらに含む。

#### 【0027】

[0027]本開示の別の態様によれば、静的T C A M内の方法が提示される。本方法は、第1のプルダウントランジスタと第1のプルアップトランジスタとにおいてキーセルの出力を受信することを含む。本方法はまた、第2のプルダウントランジスタと第2のプルアップトランジスタとにおいてマスクセルの出力を受信することを含む。第1のプルダウントランジスタと第2のプルダウントランジスタとは、並列に接続され、第1のプルアップトランジスタと第2のプルアップトランジスタとは、直列に接続される。本方法は、キーセ

10

20

30

40

50

ルの出力とマスクセルの出力とに少なくとも部分的に基づいて一致ライン出力を設定することをさらに含む。

#### 【0028】

[0028]さらに別の態様によれば、静的T C A Mが提示される。静的T C A Mは、第1のプルダウントランジスタと第1のプルアップトランジスタとに結合された探索値を比較するための第1の手段を含む。静的T C A Mはまた、第2のプルダウントランジスタと第2のプルアップトランジスタとに結合された探索値を比較するための第2の手段を含む。第1のプルダウントランジスタと第2のプルダウントランジスタとは、並列に接続され、第1のプルアップトランジスタと第2のプルアップトランジスタとは、直列に接続される。静的T C A Mは、第1のプルダウントランジスタと第2のプルダウントランジスタとに結合され、第1のプルアップトランジスタと第2のプルアップトランジスタとにさらに結合された一致ライン出力をさらに含む。10

#### 【0029】

[0029]ここでは、以下の発明を実施するための形態がより良く理解され得るように、本開示の特徴および技術的利点についてやや広く概説した。以下で、本開示の追加の特徴および利点について説明する。本開示は、本開示の同じ目的を実行するための他の構造を変更または設計するための基礎として容易に利用され得ることを、当業者は了解されたい。また、そのような等価な構成は、添付の特許請求の範囲に記載の本開示の教示から逸脱しないことを、当業者は諒解されたい。さらなる目的および利点とともに、本開示の編成と動作の方法の両方に関して、本開示を特徴づけると考えられる新規の特徴は、添付の図に関連して以下の説明を検討するとより良く理解されよう。ただし、図の各々は、例示および説明のみの目的で与えたものであり、本開示の限界を定めるものではないことを明確に理解されたい。20

#### 【図面の簡単な説明】

#### 【0030】

[0030]本開示の特徴、性質、および利点は、図面とともに、以下に記載する詳細な説明を読めばより明らかになろう。

【図1】[0031] T C A Mメモリシステムを示す図。

【図2】[0032]従来技術の動的N O Rアーキテクチャを示す図。

【図3】[0033]従来技術の動的N A N Dアーキテクチャを示す図。30

【図4】従来技術の動的N A N Dアーキテクチャを示す図。

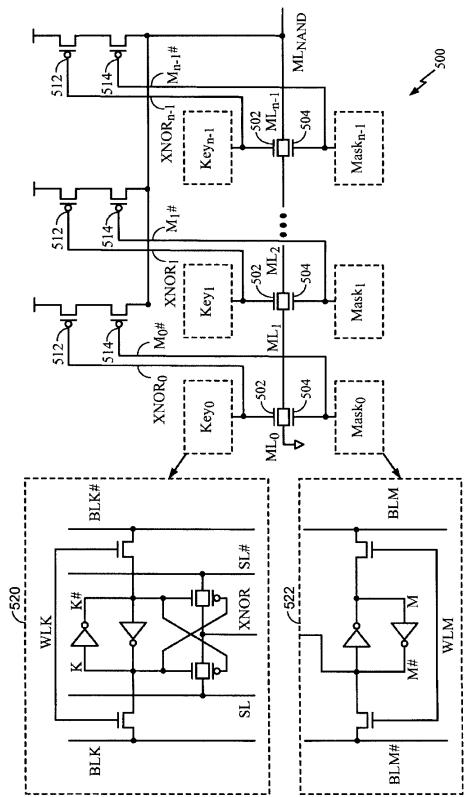

【図5】[0034]本開示の一態様による、静的N A N Dアーキテクチャを示す図。

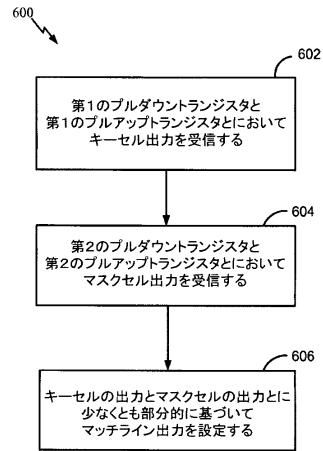

【図6】[0035]本開示の一態様による、方法のブロック図。

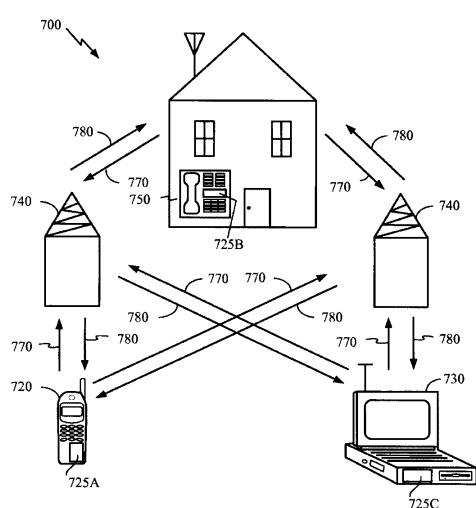

【図7】[0036]本開示の構成が有利に採用され得る例示的なワイヤレス通信システムを示す図。

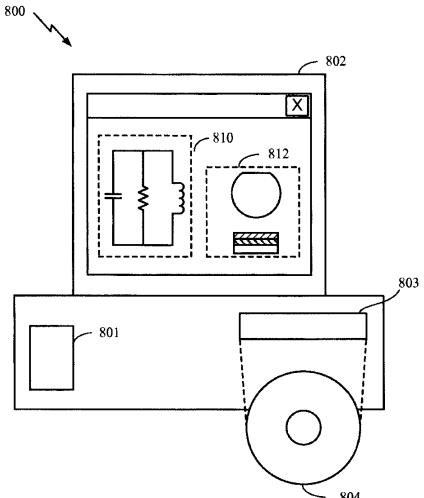

【図8】[0037]本開示の一態様による、半導体構成要素の回路、レイアウト、および論理設計のために使用される設計ワークステーションを示すブロック図。

#### 【発明を実施するための形態】

#### 【0031】

[0038]添付の図面に関して以下に記載する発明を実施するための形態は、様々な構成を説明するものであり、本明細書で説明する概念が実施され得る構成のみを表すものではない。発明を実施するための形態は、様々な概念の完全な理解を与えるための具体的な詳細を含む。ただし、これらの概念はこれらの具体的な詳細なしに実施され得ることが当業者には明らかであろう。いくつかの例では、そのような概念を不明瞭にしないように、よく知られている構造および構成要素をブロック図の形式で示す。40

#### 【0032】

[0039]本開示の態様は、一致ラインをプリチャージせず、タイミング制御回路の複雑さを低減する静的N A N D T C A Mを提供する。本開示によれば、一致ライン(M L)は各サイクルの前にプリチャージされないので、静的N A N D T C A Mは、一致ラインプリチャージのために複雑なタイミング制御回路を使用しない。一致ラインは、中間一致ラ50

イン  $M_L_0 \sim M_L_{n-1}$  と一致ライン出力  $M_L_{NAND}$  を含む。さらに、静的実装形態は、電荷共有問題の可能性を低減する。

#### 【0033】

[0040] 図 5 に、本開示の一態様による、静的 NAND TCAM 500 のアーキテクチャを示す。図 5 に示すように、一致ライン出力  $M_L_{NAND}$  は、一連の中間一致ライン  $M_L_0 \sim M_L_{n-1}$  に接続される。中間一致ライン  $M_L_0 \sim M_L_{n-1}$  の各々は、マスク NMOS トランジスタ 504 などの第 1 のプルダウントランジスタを介してマスクセル  $Mask_0 \sim Mask_{n-1}$  に結合され、キ - NMOS トランジスタ 502 などの第 2 のプルダウントランジスタを介してキーセル  $Key_0 \sim Key_{n-1}$  に結合される。プルダウントランジスタは、並列に接続される。マスクセル  $Mask_0 \sim Mask_{n-1}$  のコンテンツは、拡大されたマスクセル 522 に示されている。拡大されたマスクセル 522 に示すように、マスクセル  $Mask_0 \sim Mask_{n-1}$  は、マスクビット  $M$  と、マスクビットバー  $M\#$  と、マスクワードライン  $WLM$  と、マスクビットライン  $BLM$  と、マスクビットラインバー  $BLM\#$  を含む SRAM セルである。キーセル  $Key_0 \sim Key_{n-1}$  のコンテンツは、拡大されたキービットセル 520 に示されている。拡大されたキービットセル 520 に示すように、キーセル  $Key_0 \sim Key_{n-1}$  は、XNOR 論理を用いる SRAM セルである。キーセル  $Key_0 \sim Key_{n-1}$  は、探索ライン  $SL$  と、探索ラインバー  $SL\#$  と、キービットライン  $BLK$  と、キービットラインバー  $BLK\#$  と、キービット  $K$  と、キービットバー  $K\#$  と、キー書き込みライン  $WLK$  と、出力ライン XNOR とをさらに含む。

10

#### 【0034】

[0041] さらに、キーセル  $Key_0 \sim Key_{n-1}$  の各々は、第 1 の PMOS トランジスタ 512 に結合され、マスクセル  $Mask_0 \sim Mask_{n-1}$  の各々は、第 2 の PMOS トランジスタ 514 に結合される。各第 1 の PMOS トランジスタ 512 は、XNOR ライン ( $XNOR_0 \sim XNOR_{n-1}$ ) を介してそれぞれのキーセル  $Key_0 \sim Key_{n-1}$  に結合され、各第 2 の PMOS トランジスタ 514 は、マスクビットラインバー ( $M_0\# \sim M_{n-1}\#$ ) を介してそれぞれのマスクセル  $Mask_0 \sim Mask_{n-1}$  に結合される。第 1 の PMOS トランジスタ 512 と第 2 の PMOS トランジスタ 514 とはまた、一致ライン出力 ( $M_L_{NAND}$ ) に結合される。第 1 の PMOS トランジスタ 512 と第 2 の PMOS トランジスタ 514 とは、直列に接続され、直列 PMOS トランジスタと呼ばれることがある。したがって、本開示の一態様によれば、各セルペア（たとえば、1 つのマスクセルおよび 1 つのキーセル）は、並列 NMOS トランジスタ（たとえば、キ - NMOS トランジスタ 502 およびマスク NMOS トランジスタ 504）と直列 PMOS トランジスタ（たとえば、第 1 の PMOS トランジスタ 512 および第 2 の PMOS トランジスタ 514）とに結合される。

20

#### 【0035】

[0042] 第 1 の PMOS トランジスタ 512 と第 2 の PMOS トランジスタ 514 とが各セルペアに結合されるので、一致ラインは、各クロックサイクルの前にプリチャージされない。したがって、静的 NAND TCAM 500 は、複雑なタイミング制御方式を使用せず、動的 NAND TCAM（図 3）と比較して、より多くの電力を節約する。さらに、中間一致ラインは  $V_{DD} \sim V_t$  の電圧レベルにプリチャージされず、それによって、探索ラインのためのエリアの減少と電力消費量の減少とをもたらす。

30

#### 【0036】

[0043] 表 3 に、本開示の一態様による、静的 NAND のための真理値表を示す。

## 【表3】

| 表3 |           |          |           |      |                                  |             |

|----|-----------|----------|-----------|------|----------------------------------|-------------|

| 状態 | マスクビット(M) | キービット(K) | 探索ライン(SL) | XNOR | $ML_i \rightarrow ML_{i+1}$ への伝搬 | $ML_{NAND}$ |

| 0  | 1         | 0        | 0         | 1    | オン                               | 0/1         |

| 0  | 1         | 0        | 1         | 0    | オフ                               | 1           |

| 1  | 1         | 1        | 0         | 0    | オフ                               | 1           |

| 1  | 1         | 1        | 1         | 1    | オン                               | 0/1         |

| X  | 0         | X        | X         | X    | オン                               | 0/1         |

10

20

## 【0037】

[0044] 前に説明したように、現在の中間一致ラインの左側の中間一致ラインのすべてが一致を示すために低を評価するときにのみ、 $ML_i$ などの現在の中間一致ラインが低に引き下げられるので、静的NAND TCAMは直列動作である。同様に、現在の中間一致ライン $ML_i$ が低を評価する場合にのみ、後続の中間一致ライン $ML_{i+1}$ は低に引き下げられ得る。すなわち、1つの中間一致ラインが不一致を示す場合、後続の一致ライン（その1つの中間一致ラインの右側の中間一致ライン）は低に引き下げられない。より詳細には、前の中間一致ラインのすべてが一致を示すために低を評価するときにのみ、 $ML_{i+1}$ などの後続の中間一致ラインが低に引き下げられ得る。

## 【0038】

30

[0045] さらに、静的NAND TCAMでは、動的NAND TCAMとは対照的に、一致ライン出力 $ML_{NAND}$ が直列PMOSトランジスタ（たとえば、第1のPMOSトランジスタ512および第2のPMOSトランジスタ514）に接続されるので、不一致があるとき、 $ML_{NAND}$ 値は浮動小数点値でなく、むしろ、直列PMOSトランジスタは、不一致を示すために一致ライン出力 $ML_{NAND}$ を高に引き上げる。さらに、中間一致ラインは、直列に接続され、すべての一一致ラインが評価されるまで、または不一致が決定されるまで、一致ライン出力 $ML_{NAND}$ の状態は知られない。したがって、表3に示すように、出力がまだ知られていない場合、不一致がまだ決定されていないとき、一致ライン出力 $ML_{NAND}$ は0/1のいずれかになる。

## 【0039】

40

[0046] さらに、表3に示すように、XNORが1であるか、またはマスクビット(M)が0であるかのいずれかのとき、現在の中間一致ライン $ML_i$ から後続の中間一致ライン $ML_{i+1}$ への伝搬( $ML_i \rightarrow ML_{i+1}$ への伝搬)はアクティブ化し得る(オン)。すなわち、XNORが1であるとき、キーノ MOSトランジスタ502が、アクティブ化され、一致を示すために現在の中間一致ライン $ML_i$ を低に引き下げる。代替的に、マスクビット(M)が0であるとき、マスクセルのマスクビットバー(M#)は、1になり、マスクN MOSトランジスタ504は、アクティブ化され、一致を示すために現在の中間一致ライン $ML_i$ を低に引き下げる。表3に示すように、マスクビットが0であるとき、状態、キービット、および探索ラインなどの他の値にかかわらず、現在の中間が一致を示すために低に引き下げるところになるので、他の変数の状態はXである。より詳細には、Xの状態は

50

「無関心」状態であり、一致も不一致もない、むしろ、探索ラインの値とキーセルの値との間の比較がないマスク状態を指す。

#### 【0040】

[0047]さらに、XNORが0であり、マスクビット(M)が1であるとき、不一致が示される。表3には示されていないが、マスクビットが1であるとき、マスクビットバー(M#)は0であり、その逆も同様である。すなわち、XNORが0であるとき、XNORライン(XNOR<sub>0</sub>~XNOR<sub>n-1</sub>)も0である。さらに、マスクビットバーが0である(たとえば、マスクビットが1である)とき、マスクビットバーライン(M<sub>0</sub>#~M<sub>n-1</sub>#)は0である。したがって、XNORラインとマスクビットバーラインの両方が0であるとき、第1のPMOSトランジスタ512と第2のPMOSトランジスタ514とが有効化され、一致ライン出力(ML<sub>NAND</sub>)が高に設定される。前に説明したように、一致ラインが高であるとき、不一致が示される。10

#### 【0041】

[0048]最後に、表3において、状態は、記憶要素(キーセルおよびマスクセル)の状態を指す。キーセルが0の値を有するとき、状態は0であり、キーセルが1の値を有するとき、状態は1であり、マスクセルが0であるとき、状態はXである。すなわち、Xの状態の場合、マスクセルが0であるとき、マスクNMOSトランジスタ504は、XNOR値にかかわらず、有効化され、中間一致ラインを低に引き下げる。

#### 【0042】

[0049]図6に、TCAM内の方法600のブロック図を示す。図6に示すように、ブロック602において、キーセル出力は、第1のプルダウントランジスタと第1のプルアップトランジスタとにおいて受信される。ブロック604において、マスクセル出力は、第2のプルダウントランジスタと第2のプルアップトランジスタとにおいて受信される。さらに、ブロック606において、マッチライン出力は、キーセルの出力および/またはマスクセルの出力に基づいて設定される。20

#### 【0043】

[0050]図7に、有利には本開示の一実施形態が採用され得る例示的なワイヤレス通信システム700を示す。説明のために、図7に、3つのリモートユニット720、730、および750と、2つの基地局740とを示す。ワイヤレス通信システムはより多くのリモートユニットおよび基地局を有し得ることを認識されよう。リモートユニット720、730、および750は、静的NAND TCAM725A、725B、および725Cを用いるマルチコアプロセッサを含む。図7に、基地局740およびリモートユニット720、730、および750からの順方向リンク信号770と、リモートユニット720、730、および750から基地局740への逆方向リンク信号780とを示す。30

#### 【0044】

[0051]図7では、リモートユニット720は携帯電話として示され、リモートユニット730はポータブルコンピュータとして示され、リモートユニット750はワイヤレスローカルループシステム中の固定ロケーションリモートユニットとして示されている。たとえば、リモートユニットは、セルフォン、ハンドヘルドパーソナル通信システム(PCN)ユニット、セットトップボックス、音楽プレーヤー、ビデオプレーヤー、エンターテインメントユニット、ナビゲーションデバイス、個人情報端末などのポータブルデータユニット、またはメーター読み取り機器などの固定ロケーションデータユニットであり得る。図7は、本開示の教示による、静的NAND TCAM725A、725B、および725Cを用いるマルチコアプロセッサを採用し得るリモートユニットを示すが、本開示は、これらの例示的な図示されたユニットに限定されない。たとえば、本開示の態様による静的NAND TCAMを用いるマルチコアプロセッサは、任意のデバイスにおいて適切に採用され得る。40

#### 【0045】

[0052]図8は、上記で開示した静的NAND TCAMを用いるマルチコアプロセッサなど、半導体構成要素の回路、レイアウト、および論理設計のために使用される設計ワー50

クステーションを示すブロック図である。設計ワークステーション 800 は、オペレーティングシステムソフトウェア、サポートファイル、および Cadence または OrCAD などの設計ソフトウェアを含んでいる、ハードディスク 801 を含む。設計ワークステーション 800 はまた、回路 810、または静的 NAND TCAM などの半導体構成要素 812 の設計を容易にするためのディスプレイ 802 を含む。回路設計 810 または半導体構成要素 812 を有形に記憶するための記憶媒体 804 が提供される。回路設計 810 または半導体構成要素 812 は、GDSII または GERBER など、ファイル形式で記憶媒体 804 に記憶され得る。記憶媒体 804 は、CD-ROM、DVD、ハードディスク、フラッシュメモリ、または他の適切なデバイスであり得る。さらに、設計ワークステーション 800 は、記憶媒体 804 から入力を受け付けるか、または記憶媒体 804 に出力を書き込むためのドライブ装置 803 を含む。

#### 【0046】

[0053] 記憶媒体 804 に記録されたデータは、論理回路構成、フォトリソグラフィマスクのためのパターンデータ、または電子ビームリソグラフィなどのシリアル書込みツールのためのマスクパターンデータを指定し得る。データは、論理シミュレーションに関するタイミング図またはネット回路など、論理検証データをさらに含み得る。記憶媒体 804 にデータを与えることにより、半導体ウエハを設計するためのプロセスの数が減少するので、回路設計 810 または半導体構成要素 812 の設計が容易になる。

#### 【0047】

[0054] 一構成では、TCAM は、受信手段と設定手段とを含む。受信手段および設定手段は、記憶手段によって具陳される機能を実行するように構成されたキーセル、ビットセル、中間一致ライン、一致ライン出力、並列プルアップトランジスタ、および / または直列プルダウントランジスタであり得る。

#### 【0048】

[0055] 特定の回路について説明したが、開示する実施形態を実施するために、開示する回路のすべてが必要とされるとは限らないことを、当業者は諒解されよう。さらに、本開示への集中を維持するために、いくつかのよく知られている回路については説明していない。

#### 【0049】

[0056] 本明細書で説明する方法は、適用例に応じて様々な手段によって実装され得る。たとえば、これらの方法は、ハードウェア、ファームウェア、ソフトウェア、またはそれらの任意の組合せで実装され得る。ハードウェア実装の場合、処理ユニットは、1つまたは複数の特定用途向け集積回路 (ASIC)、デジタル信号プロセッサ (DSP)、デジタル信号処理デバイス (DSPD)、プログラマブル論理デバイス (PLD)、フィールドプログラマブルゲートアレイ (FPGA)、プロセッサ、コントローラ、マイクロコントローラ、マイクロプロセッサ、電子デバイス、本明細書で説明した機能を実行するように設計された他の電子ユニット、またはそれらの組合せの中で実装され得る。

#### 【0050】

[0057] ファームウェアおよび / またはソフトウェア実装の場合、本方法は、本明細書で説明した機能を実行するモジュール（たとえば、プロシージャ、関数など）を用いて実装され得る。命令を有形に実施するいかなる機械またはコンピュータ可読媒体も、本明細書で説明した方法を実装する際に使用され得る。たとえば、ソフトウェアコードは、メモリに記憶され、プロセッサによって実行され得る。実行ソフトウェアコードは、プロセッサによって実行されたときに、本明細書で提示した教示の異なる態様の様々な方法および機能を実装する動作環境を生成する。メモリは、プロセッサの内部またはプロセッサの外部に実装され得る。本明細書で使用する「メモリ」という用語は、長期メモリ、短期メモリ、揮発性メモリ、不揮発性メモリ、または他のメモリのいずれかのタイプを指し、メモリの特定のタイプまたはメモリの数、あるいはメモリが記憶される媒体のタイプに限定されるべきではない。

#### 【0051】

10

20

30

40

50

[0058]本明細書で説明した方法および機能を定義するソフトウェアコードを記憶する機械またはコンピュータ可読媒体は、物理コンピュータ記憶媒体を含む。記憶媒体は、コンピュータによってアクセスされ得る任意の利用可能な媒体であり得る。限定ではなく、例として、そのようなコンピュータ可読媒体は、RAM、ROM、EEPROM(登録商標)、CD-ROMまたは他の光ディスクストレージ、磁気ディスクストレージまたは他の磁気ストレージデバイス、あるいは命令またはデータ構造の形態の所望のプログラムコードを記憶するために使用され得、コンピュータによってアクセスされ得る、任意の他の媒体を備えることができる。本明細書で使用するディスク(disk)および/またはディスク(disc)は、コンパクトディスク(disc)(CD)、レーザディスク(登録商標)(disc)、光ディスク(disc)、デジタル多用途ディスク(disc)(DVD)、フロッピー(登録商標)ディスク(disk)およびブルーレイ(登録商標)ディスク(disc)を含み、ディスク(disk)は、通常、データを磁気的に再生し、ディスク(disc)は、データをレーザで光学的に再生する。上記の組合せもコンピュータ可読媒体の範囲内に含めるべきである。

## 【0052】

[0059]コンピュータ可読媒体上の記憶に加えて、命令および/またはデータは、通信装置中に含まれる伝送媒体上の信号として与えられ得る。たとえば、通信装置は、命令とデータとを示す信号を有するトランシーバを含み得る。命令およびデータは、1つまたは複数のプロセッサに、特許請求の範囲で概説する機能を実装させるように構成される。

## 【0053】

[0060]本教示およびそれらの利点について詳細に説明したが、添付の特許請求の範囲によって規定される本教示の技術から逸脱することなく様々な変更、置換および改変を本明細書で行うことができることを理解されたい。さらに、本出願の範囲は、本明細書で説明するプロセス、機械、製造、組成物、手段、方法およびステップの特定の態様に限定されるものではない。当業者なら本開示から容易に諒解するように、本明細書で説明する対応する態様と実質的に同じ機能を実行するか、または実質的に同じ結果を達成する、現存するかまたは後で開発される、プロセス、機械、製造、組成物、手段、方法、またはステップは本教示に従って利用され得る。したがって、添付の特許請求の範囲は、それらの範囲内にそのようなプロセス、機械、製造、組成物、手段、方法、またはステップを含むものとする。

以下に、本願出願の当初の特許請求の範囲に記載された発明を付記する。

## [C1]

静的3値連想メモリ(TCAM)であって、

第1のプルダウントランジスタと第1のプルアップトランジスタとに結合されたキーセルと、

第2のプルダウントランジスタと第2のプルアップトランジスタとに結合されたマスクセルと、前記第1のプルダウントランジスタと前記第2のプルダウントランジスタとは、並列に接続され、前記第1のプルアップトランジスタと前記第2のプルアップトランジスタとは、直列に接続される、

前記第1のプルダウントランジスタと前記第2のプルダウントランジスタとに結合され、前記第1のプルアップトランジスタと前記第2のプルアップトランジスタとにさらに結合された一致ライン出力と

を備える、TCAM。

## [C2]

前記マスクセルは、スタティックランダムアクセスメモリ(SRAM)ビットセルである、

[C1]に記載のTCAM。

## [C3]

前記キーセルは、スタティックランダムアクセスメモリ(SRAM)セルとXNOR論理とを含む、

10

20

30

40

50

[ C 1 ] に記載の T C A M。

[ C 4 ]

前記第 1 のプルダウントランジスタと前記第 1 のプルアップトランジスタとに結合された前記 X N O R 論理の出力をさらに備える、

[ C 3 ] に記載の T C A M。

[ C 5 ]

前記キーセルへの探索ライン入力をさらに備える、

[ C 1 ] に記載の T C A M。

[ C 6 ]

前記第 1 のプルダウントランジスタと前記第 2 のプルダウントランジスタとに結合された中間一致ラインをさらに備える、

[ C 1 ] に記載の T C A M。

[ C 7 ]

静的 3 値連想メモリ ( T C A M ) 内の方法であって、

第 1 のプルダウントランジスタと第 1 のプルアップトランジスタにおいてキーセルの出力を受信することと、

第 2 のプルダウントランジスタと第 2 のプルアップトランジスタにおいてマスクセルの出力を受信することと、前記第 1 のプルダウントランジスタと前記第 2 のプルダウントランジスタとは、並列に接続され、前記第 1 のプルアップトランジスタと前記第 2 のプルアップトランジスタとは、直列に接続される、

前記キーセルの前記出力と前記マスクセルの前記出力とに少なくとも部分的に基づいて一致ライン出力を設定することとを備える方法。

[ C 8 ]

前記一致ライン出力を設定することは、

前記キーセルの前記出力が一致を示すとき、前記第 1 のプルダウントランジスタを介して、低値に前記一致ライン出力を設定することと、

前記マスクセルの前記出力が前記一致を示すとき、前記第 2 のプルダウントランジスタを介して、前記低値に前記一致ライン出力を設定することと、

前記マスクセルの前記出力と前記キーセルの前記出力とが不一致を示すとき、前記第 1 のプルアップトランジスタと前記第 2 のプルアップトランジスタとを介して、高値に前記一致ライン出力を設定することとを備える、[ C 7 ] に記載の方法。

[ C 9 ]

前の探索値比較が一致であったことを中間一致ラインが示すとき、前記キーセルの値と前記マスクセルの値とを比較することをさらに備える、

[ C 7 ] に記載の方法。

[ C 10 ]

前記マスクセルは、スタティックランダムアクセスメモリ ( S R A M ) ビットセルである、

[ C 7 ] に記載の方法。

[ C 11 ]

前記キーセルは、

スタティックランダムアクセスメモリ ( S R A M ) セルと X N O R 論理とを含む、

[ C 7 ] に記載の方法。

[ C 12 ]

静的 3 値連想メモリ ( T C A M ) であって、

第 1 のプルダウントランジスタと第 1 のプルアップトランジスタとに結合された探索値を比較するための第 1 の手段と、

第 2 のプルダウントランジスタと第 2 のプルアップトランジスタとに結合された前記探

10

20

30

40

50

索値を比較するための第2の手段と、前記第1のプルダウントランジスタと前記第2のプルダウントランジスタとは、並列に接続され、前記第1のプルアップトランジスタと前記第2のプルアップトランジスタとは、直列に接続される。

前記第1のプルダウントランジスタと前記第2のプルダウントランジスタとに結合され、前記第1のプルアップトランジスタと前記第2のプルアップトランジスタとにさらに結合された一致ライン出力と

を備える、T C A M。

[ C 1 3 ]

前記第1の手段は、スタティックランダムアクセスメモリ ( S R A M ) ビットセルである、

10

[ C 1 2 ] に記載の T C A M。

[ C 1 4 ]

前記第2の手段は、スタティックランダムアクセスメモリ ( S R A M ) セルと X N O R 論理とを含む、

[ C 1 2 ] に記載の T C A M。

[ C 1 5 ]

前記第1のプルダウントランジスタと前記第1のプルアップトランジスタとに結合された前記 X N O R 論理の出力をさらに備える、

[ C 1 4 ] に記載の T C A M。

[ C 1 6 ]

前記第2の手段への探索ライン入力をさらに備える、

[ C 1 2 ] に記載の T C A M。

[ C 1 7 ]

前記第1のプルダウントランジスタと前記第2のプルダウントランジスタとに結合された中間一致ラインをさらに備える、

[ C 1 2 ] に記載の T C A M。

### 【要約】

静的3値連想メモリ ( T C A M ) は、中間一致ラインに結合されたキーセルとマスクセルとを含む。キーセルは、第1のプルダウントランジスタと第1のプルアップトランジスタとに結合される。マスクセルは、第2のプルダウントランジスタと第2のプルアップトランジスタとに結合される。第1のプルダウントランジスタと第2のプルダウントランジスタとは、並列に接続され、第1のプルアップトランジスタと第2のプルアップトランジスタとは、直列に接続される。一致ライン出力はまた、第1のプルダウントランジスタと第2のプルダウントランジスタとに結合され、第1のプルアップトランジスタと第2のプルアップトランジスタとにさらに結合される。

【選択図】図 5

30

【図1】

【図2】

FIG. 2

(従来技術)

【図3】

FIG. 3

(従来技術)

【図4】

FIG. 4

(従来技術)

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

---

フロントページの続き

(72)発明者 タージオグル、イージン

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

(72)発明者 デサイ、ニシス

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

(72)発明者 バッティコンダ、ラケッシュ

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

(72)発明者 ジュン、チャンホ

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

(72)発明者 ユン、セイ・スン

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

審査官 滝谷 亮一

(56)参考文献 米国特許出願公開第2009/0310395(US,A1)

(58)調査した分野(Int.Cl., DB名)

G11C 15/04