(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6325526号

(P6325526)

(45) 発行日 平成30年5月16日(2018.5.16)

(24) 登録日 平成30年4月20日(2018.4.20)

(51) Int.Cl.

HO3F 3/217 (2006.01)

F 1

HO3F 3/217

請求項の数 26 (全 34 頁)

(21) 出願番号 特願2015-509373 (P2015-509373)

(86) (22) 出願日 平成25年4月24日 (2013.4.24)

(65) 公表番号 特表2015-515841 (P2015-515841A)

(43) 公表日 平成27年5月28日 (2015.5.28)

(86) 國際出願番号 PCT/EP2013/058450

(87) 國際公開番号 WO2013/164229

(87) 國際公開日 平成25年11月7日 (2013.11.7)

審査請求日 平成28年3月28日 (2016.3.28)

(31) 優先権主張番号 61/640,565

(32) 優先日 平成24年4月30日 (2012.4.30)

(33) 優先権主張国 米国(US)

(73) 特許権者 513104424

メルス オーディオ アンパーティゼルスカ

ブ

デンマーク国, デーコーー 2730 ヘア

レウ, ヘルケル 24

(74) 代理人 100099759

弁理士 青木 篤

(74) 代理人 100092624

弁理士 鶴田 準一

(74) 代理人 100141162

弁理士 森 啓

(74) 代理人 100141254

弁理士 榎原 正巳

最終頁に続く

(54) 【発明の名称】調整可能ループ・フィルター特性を有するクラスDオーディオ・アンプ

(57) 【特許請求の範囲】

【請求項 1】

ラウドスピーカ負荷に接続可能な、第1出力ノードを備える第1出力ドライバであって

該第1出力ドライバは、負荷信号を該ラウドスピーカ負荷に供給し、

前記第1出力ドライバは、第1供給電圧と第1出力ノードの間で接続する1つ以上の半導体スイッチを備えるアッパー・レッグと、第1出力ノードと第2供給電圧の間で接続する1つ以上の半導体スイッチを備えるローワー・レッグと、備え、

前記半導体スイッチの各々は、オン状態またはオフ状態に選択的に半導体スイッチを設定するために、半導体スイッチの状態を制御するのに適しているスイッチ制御端子を備える、

第1出力ドライバと、

フィルタ処理したオーディオ信号の受信、および、前記第1出力ドライバのそれぞれのスイッチ制御端子に対する調整可能変調周波数におけるパルス幅変調制御信号の第1セットの生成のためのパルス幅変調器と、

調整可能ループ・フィルターならびにオーディオ信号および前記負荷信号から導出されたフィードバック信号に接続する加算ノードを備えるフィードバック・ループであって、該フィードバック・ループは、該フィードバック信号を、前記加算ノードに接続させるように構成される、フィードバック・ループと、

パルス幅変調制御信号の前記第1セットの調整可能変調周波数の周波数設定に基づいて

10

20

、調整可能ループ・フィルターの周波数特性を制御するように構成されたコントローラと

、

を備えるクラスDオーディオ・アンプ。

**【請求項2】**

前記コントローラは、前記調整可能変調周波数のセッティングに基づいて、前記調整可能ループ・フィルターの次数をえるように構成される、請求項1に記載のクラスDオーディオ・アンプ。

**【請求項3】**

前記フィードバック・ループは、前記調整可能変調周波数の前記周波数設定の0.01と1.0倍との間、好適には、0.1と0.5倍との間のオープン・ループ帯域幅を持つ

、請求項1又は2に記載のクラスDオーディオ・アンプ。 10

**【請求項4】**

前記コントローラは、調整可能変調周波数の最小周波数設定においてよりも、調整可能変調周波数の最大周波数設定における、前記調整可能ループ・フィルターのより高次数を選択するように構成される、請求項2又は3に記載のクラスDオーディオ・アンプ。

**【請求項5】**

前記調整可能ループ・フィルターは、それぞれの積分器時定数および、それぞれの積分器利得係数を備える複数のカスケード接続積分器と、を備える、請求項1ないし4のいずれか1項に記載のクラスDオーディオ・アンプ。 20

**【請求項6】**

前記コントローラは、調整可能ループ・フィルターの周波数応答特性ファクタをコントロールするために、0.25と4の間のスケーリング・ファクタのような共通のスケーリング・ファクタで前記複数の積分器の前記それぞれの積分器時定数を調整するように構成される、請求項5に記載のクラスDオーディオ・アンプ。

**【請求項7】**

前記コントローラは、調整可能ループ・フィルターの周波数応答特性ファクタをコントロールするために、複数のスケーリング・ファクタで前記複数の積分器の前記それぞれの積分器利得係数を測定するように構成される請求項5に記載のクラスDオーディオ・アンプ。 30

**【請求項8】**

前記調整可能ループ・フィルターは、2つないし8つのカスケード接続積分器を備える

、請求項5ないし7のいずれか1項に記載のクラスDオーディオ・アンプ。

**【請求項9】**

前記カスケード接続積分器の1つ以上が、最大出力電圧レベルまたは最大電流レベルの

ような、前記カスケード接続積分器の最大出力レベルを制限するために出力レベル・クラ

ンプを備える、請求項5ないし7のいずれか1項に記載のクラスDオーディオ・アンプ。

**【請求項10】**

前記ラウドスピーカ負荷にわたる第1の3レベル負荷信号を提供するために、中点電圧

のよう、第1出力ノードにおいて、第3供給電圧をセットするように構成されるDC電

圧源をさらに備える請求項1ないし9のいずれか1項に記載のクラスDオーディオ・アン

プ。 40

**【請求項11】**

前記第1出力ドライバの前記アッパー・レッグは、カスケードで接続する第1カスケー

ド半導体スイッチおよび第2カスケード半導体スイッチを備え、前記第1出力ドライバの

前記ローワー・レッグは、カスケードで接続する第3カスケード半導体スイッチおよび第

4カスケード半導体スイッチを備え、

前記DC電圧源は、前記第3供給電圧にチャージされ、前記第1カスケード半導体スイ

ッチおよび前記第2カスケード半導体スイッチの間に位置する第1ノードと、前記第3カ

スケード半導体スイッチおよび前記第4カスケード半導体スイッチの間に位置する第2ノ

ードとの間で接続されたキャパシタを備え、 50

パルス幅変調制御信号の前記第1セットは、

第1状態において、前記キャパシタの第1端子を、前記第1カスケード半導体スイッチおよび前記第3カスケード半導体スイッチを通して、第1出力ノードに接続し、

第2状態において、前記キャパシタの第2端子を、前記第4カスケード半導体スイッチおよび前記第2カスケード半導体スイッチを通して、第1出力ノードに接続する、よう

に構成される、請求項10に記載のクラスDオーディオ・アンプ。

#### 【請求項12】

バランス負荷信号をそれに供給するために、前記ラウドスピーカ負荷に接続可能な第2出力ノードを備える第2出力ドライバをさらに備え、

前記第2出力ドライバは、前記第1供給電圧と前記第2出力ノードとの間で接続する1つ以上の半導体スイッチを備えるアッパー・レッグと、前記第2出力ノードと前記第2供給電圧との間で接続する1つ以上の半導体スイッチを備えるローワー・レッグとを備え、

前記第2出力ドライバの前記半導体スイッチの各々が、オン状態またはオフ状態に選択的に半導体スイッチを設定するために、半導体スイッチの状態を制御するのに適しているスイッチ制御端子を備え、

前記コントローラは、前記第2出力ドライバのそれぞれのスイッチ制御端子に対する調整可能変調周波数において、パルス幅変調制御信号の第2セットを生成するようにさらに適している、請求項1ないし11のいずれか1項に記載のクラスDオーディオ・アンプ。

#### 【請求項13】

前記コントローラは、第1動作モードにおいて、前記ラウドスピーカ負荷にわたる第1複数レベル・バランス負荷信号を生成するために、変調制御信号の前記第1セットおよび第2セットの間での第1所定の位相関係をセットし、

第2動作モードにおいて、前記ラウドスピーカ負荷にわたる第2複数レベル・バランス負荷信号を生成するために、変調制御信号の前記第1セットおよび前記第2セットの間での第2所定の位相関係をセットするように構成される請求項12に記載のクラスDオーディオ・アンプ。

#### 【請求項14】

前記コントローラは、前記第1動作モードにおいて、3レベル・バランス負荷信号を生成するために変調制御信号の第1セットの対応する制御信号に対して逆位相を有する変調制御信号の第2セットの各々の制御信号を提供し、

前記第2動作モードにおいて、5レベル・バランス負荷信号を生成するために変調制御信号の第1セットの対応する制御信号に対して逆位相、および、追加的+/-90度位相シフトを有する変調制御信号の第2セットの各々の制御信号を提供するように構成される請求項13に記載のクラスDオーディオ・アンプ。

#### 【請求項15】

前記コントローラはオーディオ信号レベル検出器備え、

前記コントローラは、前記オーディオ信号の検出されたレベルに依存して、変調制御信号の前記第1セットおよび/または第2セットの前記調整可能変調周波数を制御するのに適している、請求項1ないし14のいずれか1項に記載のクラスDオーディオ・アンプ。

#### 【請求項16】

前記コントローラは、前記オーディオ信号の検出されたレベルに依存して、前記第1動作モードと前記第2動作モードとの間でスイッチするのに適している、請求項13または14に記載のクラスDオーディオ・アンプ。

#### 【請求項17】

前記コントローラは、前記オーディオ信号の前記検出されたレベルを、所定のレベル閾値と比較し、

検出オーディオ信号レベルが所定のレベル閾値より小さいとき、変調制御信号の前記第1セットおよび/または第2セットの第1変調周波数をセットし、

検出オーディオ信号レベルが所定のレベル閾値より大きいとき、変調制御信号の前記第1セットおよび/または第2セットの第2変調周波数をセットするのにさらに適しており

10

20

30

40

50

、

第1変調周波数は、第2変調周波数より低い、請求項16に記載のクラスDオーディオ・アンプ。

【請求項18】

前記コントローラは、

前記検出オーディオ信号レベルが前記所定のレベル閾値を上回るときに、前記第1動作モードを選択し、

検出オーディオ信号レベルが所定のレベル閾値より小さいときに、前記第2動作モードを選択するのにさらに適している、請求項17に記載のクラスDオーディオ・アンプ。

【請求項19】

前記コントローラは、

前記フィルタ処理したオーディオ信号に接続し、デジタル・パルス幅変調器にデジタル・フィルタ処理したオーディオ信号を生成するために、デジタル・クロック信号に従つて、動作するサンプリング・デバイスを更に含み、

前記デジタル・パルス幅変調器は、一様にサンプルされたパルス幅変調オーディオ信号を生成するように構成され、

前記コントローラは、一様にサンプルされたパルス幅変調オーディオ信号に基づいて、パルス幅変調制御信号の前記第1セットおよび／または第2セットを生成する、請求項1ないし18のいずれか1項に記載のクラスDオーディオ・アンプ。

【請求項20】

前記DC電圧源は、チャージされたキャパシタ、フローティング浮動DC電源レール、バッテリーのグループのうちの少なくとも1つのコンポーネントを備える、請求項10または11に記載のクラスDオーディオ・アンプ。

【請求項21】

前記半導体スイッチの各々のオン抵抗は、0.01と10との間にある、請求項1ないし20のいずれか1項に記載のクラスDオーディオ・アンプ。

【請求項22】

前記半導体スイッチの各々は、フィールド効果トランジスタ(FET)、バイポーラ・トランジスタ(BJT)、絶縁ゲート・バイポーラ・トランジスタ(IGBT)のグループから選択したトランジスタ・スイッチを備えている、請求項1ないし21のいずれか1項に記載のクラスDオーディオ・アンプ。

【請求項23】

前記第1および第2供給電圧は、5Vと120Vとの間のDC電圧差を提供するように構成される、請求項1ないし22のいずれか1項に記載のクラスDオーディオ・アンプ。

【請求項24】

パルス幅変調制御信号の前記第1セットの最大変調周波数は、150kHzと5MHzとの間、好適には、500kHzと1MHzとの間に存在する、請求項1ないし23のいずれか1項に記載のクラスDオーディオ・アンプ。

【請求項25】

請求項12ないし14のいずれか1項に記載のクラスDオーディオ・アンプと、

動作的に、第1出力ドライバの第1出力ノードおよび、第1DC供給電圧および第2DC供給電圧のうちの1つに接続するラウドスピーカ負荷、または、動作的に、前記第1出力ドライバおよび前記第2出力ドライバの、それぞれの、前記第1出力ノードおよび前記第2出力ノードの中間に接続するラウドスピーカ負荷と、

を備えるサウンド再生アセンブリ・コンポーネント。

【請求項26】

前記第1出力ドライバの前記第1出力ノードと前記ラウドスピーカ負荷の間で接続する負荷インダクタと、

前記ラウドスピーカ負荷と前記第1DC供給電圧および前記第2DC供給電圧のうちの1つとの間で接続された負荷キャパシタとをさらに備える請求項25に記載のサウンド再

10

20

30

40

50

生アセンブリ・コンポーネント。

【発明の詳細な説明】

【技術分野】

【0001】

本願発明は、パルス幅変調器、調整可能ループ・フィルター、および、フィードバック・ループを備えるクラスDオーディオ・アンプに関するものである。パルス幅変調器は、第1の出力ドライバのスイッチ制御端末のそれぞれに対する調整可能変調周波数におけるパルス幅変調制御信号の最初のセットを生成する。クラスDオーディオ・アンプのコントローラは、調整可能変調周波数の周波数設定に基づいて、調整可能ループ・フィルターの周波数特性を制御するように構成される。

10

【背景技術】

【0002】

クラスDオーディオ・アンプは、一般に、ラウドスピーカ負荷にわたりパルス幅変調(PWM)またはパルス密度変調(PDM)信号を切り替えることによって、ラウドスピーカ負荷のエネルギー効率の良いオーディオ・ドライブを提供すると認められる、良く知られたタイプのオーディオ・パワー増幅器である。典型的には、クラスDオーディオ・アンプは、ラウドスピーカ全体に反対位相のパルス幅変調またはパルス密度変調オーディオ信号を印加するために、ラウドスピーカ負荷のそれぞれの側または端子に接続する出力端子のペアを有するH-ブリッジ・ドライバを備える。パルス幅変調オーディオ信号のためのいくつかの変調スキームが、先行技術のPWMベースのクラスDアンプにおいて利用されてきた。いわゆるAD変調において、パルス幅変調オーディオ信号は、H-ブリッジの各々の出力端子またはノードにおいて、逆位相の2つの異なるレベルの間で、切り替えられる、または、トグルする。この2つの異なるレベルは、典型的には、それぞれ、例えば、クラスDアンプの正と負のDC電源レールのような、上位、下位の電源レールに対応する。いわゆるBD変調において、前記ラウドスピーカ負荷にわたるパルス幅変調信号は、3レベル間で交互に切り替えられる。そのうちの2つのレベルは、上記の上位、下位の電源レールに対応し、第3のレベルは、ラウドスピーカ負荷の両方の端子を、DC電源レールのうちの1つに同時に引っぱることによって得られる0レベルである。複数レベルPWM変調において、本願出願人の同時係属の特許出願PCT/EP2011/068873に記載されているように、第3の供給電圧レベルは、しばしば、正と負とのDC電源レールの中間レベルにセットされ、たとえば、3レベルまたは5レベル・パルス幅変調信号を、適切に構成された出力ドライバによってラウドスピーカ負荷にわたり印加することができる出力ドライバの出力ノードに印加される。

20

【0003】

本願発明の発明者は、オーディオ入力信号の特定の特性にしたがって、パルス幅変調器の変調周波数を調整することによって、クラスDアンプにおける顕著な性能改善を得た。変調周波数調整は、例えば、EMI放出を減少させる、出力スイッチ・デバイスにおける電力損失を減少させるなど、いくつかの理由によって、有益である。しかしながら、クラスDオーディオ・アンプのループ・フィルターの周波数応答特性は、通常、フィードバック・ループが、完全な出力パワー、および、変調周波数の最大のセッティングにおける、コンポーネント拡大と生産拡大のための要求された安全性の限界の範囲内でちょうど安定なままであるように、設計されるか、選択される。このループ・フィルター設計は、フィードバック・ループの中のクラスDアンプの回路とコンポーネントの非理想的ふるまいによって導入される歪み・雑音生成メカニズムを抑制するために有利である。しかしながら、調整可能変調の最大のセッティングにおけるループ・フィルターのちょうど安定した設計は、最大の周波数設定より低い変調周波数が選ばれるならば、フィードバック・ループが不安定になる傾向があることを意味する。そのような低い変調周波数は、さもなければ、先に述べたように、たとえば、電力を節約するために有利である。これゆえに、調整可能ループ・フィルターの周波数応答特性を、パルス幅変調器の変調周波数の特定のセッティングに対するループ安定度制約の中でオーディオ帯域幅(20Hz ~ 20kHz)を通し

30

40

50

てフィードバック・ループの最も高い可能なループ利得を得るために、変調周波数の現在の設定、そして、選択的に、負荷電力レベルに対して、調整あるいは適応させることは有利である。

#### 【0004】

したがって、E M I 雑音のレベルを減少したクラスDオーディオ・アンプは、非常に望ましいものである。同様に、特に、低いか小さなオーディオ入力信号レベルにおいて電力効率を改善したクラスDアンプは、また、非常に有利なものである。最後に、さらにコンパクトで、電力効率が良く、信頼性があり、そして、よりコストが低いカスタマに対するクラスDアンプ・ソリューション、および、他のタイプのオーディオ製品を提供するために、外部負荷インダクタおよび負荷キャパシタのサイズを減少することは、望ましい。

10

#### 【発明の概要】

#### 【0005】

本願発明の第1の態様は、- 負荷信号をそれに供給するラウドスピーカ負荷に接続可能な、第1の出力ノードを備える第1の出力ドライバを備えているクラスDオーディオ・アンプに関するものである。この第1のドライバは、第1の供給電圧と第1の出力ノードとの間で接続する1つ以上の半導体スイッチを備えるアッパー・レッグと、第1の出力ノードと第2の供給電圧の間で接続する1つ以上の半導体スイッチを備えるローワー・レッグとを備え、ここで、半導体スイッチの各々は、オン状態またはオフ状態に選択的に半導体スイッチを設定するために、半導体スイッチの状態を制御するのに適しているスイッチ制御端末を備えている。このクラスDオーディオ・アンプAは、更に、フィルタ処理したオーディオ信号の受信、および、前記第1の出力ドライバのそれぞれのスイッチ制御端末に対する調整可能変調周波数におけるパルス幅変調制御信号の第1のセットの生成のためのパルス幅変調器と、- 調整可能ループ・フィルターと、音声入力信号および負荷信号から導出されたフィードバック信号に接続する加算ノードとを備えるフィードバック・ループとを備える。このフィードバック・ループは、加算ノードに信号をこのフィードバックを接続させるように構成されている。コントローラは、パルス幅変調制御信号の前記第1セットの調整可能変調周波数の周波数設定に基づいて、調整可能ループ・フィルターの周波数特性を制御するように構成されている。

20

#### 【0006】

コントローラは、たとえばソフトウェア・プログラム可能DSP、または物理的に配線されたカスタマイズDSP、たとえば、ASICに集積されたデジタル・ステート・マシンを備えるデジタル・シグナル・プロセッサ(DSP)を備えることができる。他の実施形態において、コントローラは、適切に構成されたフィールドPLA(FPGA)を備えることができる。コントローラがソフトウェア・プログラム可能DSPを備えるならば、EEPROMまたはフラッシュ・メモリ・デバイスの中に位置する不揮発性メモリ空間は、複数の半導体スイッチならびに他の機能に対して、それぞれのパルス幅変調制御信号を生成する適切なプログラム命令またはルーチンを備えることができる。半導体スイッチに対するパルス幅変調制御信号の第1のセットの個々の制御信号は、適切なDSPプログラムまたはアルゴリズムによって生成され、個々の半導体スイッチに直接印加することができる。他の実施形態において、パルス幅変調制御信号の第1のセットは、複数の半導体スイッチに対して、制御信号の振幅レベルを適切なレベルへ上げるために、ゲートまたはブレ・ドライバ回路を通して接続することができる。多くのアプリケーションにおいて、ゲート・ドライバは、150kHzと5MHzの間の変調周波数を有するパルス幅変調信号を含むことができる。この実施形態において、第1のドライバ出力は、クラスDオーディオ・アンプからのPWM変調負荷信号を、ラウドスピーカ負荷に印加するのに適していることができる。一般に、パルス幅変調制御信号の第1セットの変調周波数は、望ましくは、150kHzと5MHzの間にあり、さらに望ましくは500kHzと1MHzの間にある。

40

#### 【0007】

当業者であれば、調整可能変調周波数の各々の周波数設定は、本願のクラスDオーディオ

50

・アンプの特定の実施形態において適用されたパルス幅変調のタイプに依存する特定の効果的なスイッチ周波数に対応することを理解するであろう。効果的スイッチ周波数は、クラス A D 变調のための調整可能变調周波数と等しい。効果的スイッチ周波数は、クラス B D 变調のための調整可能变調周波数の 2 倍と等しい。同様に、負荷信号の 3 レベルの变調に対して、变调周波数は、調整可能变调周波数の 2 倍と等しく、5 レベルの变調に対して、調整可能变调周波数の 4 倍と等しい、等である。一般に、効果的スイッチ周波数は、パルス幅变調の選択されたタイプの P W M 位相の数に調整可能变调周波数を掛けたものに等しい。

#### 【 0 0 0 8 】

第 1 および第 2 の供給電圧は、クラス D オーディオ・アンプの第 1 および第 2 の D C 供給電圧または電力レール電圧を含むことができる。第 2 の供給電圧は、クラス D アンプのグラウンド電圧、G N D、または、たとえば、大きさにおいて第 1 の供給電圧に実質的に等しい負電源電圧であることができる。第 1 の出力ドライバは、特定のアプリケーションの必要条件に依存して、所定の供給電圧の広範囲にわたって動作するのに適応することができる。有用なアプリケーションの範囲において、クラス D オーディオ・アンプの効率的 D C 供給である第 1 および第 2 の D C 供給電圧の差異は、5 ボルトと 1 2 0 ボルトとの間の値にセットすることができる。この D C 供給電圧差は、たとえば、+ 5 ボルトと G N D、あるいは、グラウンド・レファレンス、G N、に対して + / - 2 . 5 ボルトなど、ユニポーラまたはバイポーラの直流電圧として提供することができる。

#### 【 0 0 0 9 】

本願発明の 1 つの実施形態において、コントローラは、マスター・クロック・ジェネレータにより生成されるマスター・クロック信号にしたがって、動作する。マスター・クロック信号は、パルス幅变調制御信号の選択された变調周波数設定よりも、例えば、1 0 倍から 1 0 0 倍のように、著しく高くなることができる。それぞれの半導体スイッチに対する变調制御信号の第 1 セットまたは、制御信号は、マスター・クロック信号に同期して動作することができる。そのような実施形態において、クラス D オーディオ・アンプは、例えば、デジタル・パルス幅变調器へのアプリケーションのために、対応するデジタル・オーディオ信号への調整可能ループ・フィルターの出力において発生されたフィルタ処理したオーディオ信号を变换するように構成された A / D 变換器のようなサンプリング・デバイスを備える。デジタル・パルス幅变調器は、フィルタ処理したデジタル・オーディオ信号を、直接受け入れるのに適切であり得る。あるいは、デジタル・パルス幅变調器は、デジタル・パルス幅变調器の解像度に対するデジタル・オーディオ信号の解像度にマッチするデジタル・オーディオ信号の時間領域量子化を実行することができる。しかしながら、フィードバック・ループのエラー伝達関数を表す図 6 に関連してもっと詳細に下で説明されるように、フィードバック・ループのノイズ整形動作は、オーディオ帯域幅の中でこのプロセスにより発生するいかなる量子化雑音でも抑制する。

#### 【 0 0 1 0 】

コントローラは、本願発明に従う、調整可能变调周波数の周波数設定に基づいて、調整可能ループ・フィルターの周波数特性を制御するように構成される。以下のセクションにまとめられるように、これは種々の理由により有利である。ループ・フィルターの周波数応答特性は、典型的には、クラス D アンプのフィードバック・ループが、調整可能变调周波数の最大セッティングにおいて、コンポーネント拡大と生産拡大のための要求された安全性の限界の範囲内でちょうど安定なままであるように、設計されるか、選択される。このループ・フィルター設計は、フィードバック・ループの中のクラス D アンプの回路とコンポーネントの非理想ふるまいによって導入される歪み・雑音生成メカニズムを抑制するために有利である。これらの歪み・雑音生成メカニズムは複雑で、例えば、出力ドライバのパワー・トランジスタのタイミング誤差、フィードバック・バスの非理想的な周波数応答、と再量子化誤差などによるエイリアシング誤差のような種々の誤差源に起因していることがあり得る。一般に、出力ドライバ・タイミング誤差および、エイリアシング誤差は、クラス D アンプの上の負荷の増加とともに、あるいは、クラス D アンプの出力電力レベ

10

20

30

40

50

ルの増加とともに増加する傾向がある。時間量子化誤差によって誘発される誤差電力は、スイッチング周波数、あるいは、所与のデジタル・サンプリング周波数に対する変調周波数に比例している。したがって、誤差と雑音のこれらのタイプの抑制の必要は、最高の負荷電力レベル、およびより高い変調周波数において、例えば、調整可能変調周波数の最大セッティングにおいて、または、その近くにおいて、最も顕著である。より小さな負荷電力レベルで、より低い変調周波数において、さほどアグレッシブでない誤差と雑音の抑圧が実行されるように、調整可能ループ・フィルターの周波数応答特性をセットすることは、しばしば完全に許容される。すなわち、オーディオ帯域幅の中のフィードバック・ループの誤差伝達関数の小さい大きさとして表されるものである。しかしながら、調整可能変調周波数の最大セッティングにおいて、ループ・フィルターのちょうど安定した設計は、高い負荷電力レベルと共に、コントローラが、変調周波数の最大セッティングよりも低い周波数設定を選択するとき、フィードバック・ループは、本質的に不安定になる傾向があることを意味する。この現象は、フィードバック・ループの安定した帯域幅に起因し、これは、変調周波数の特定の分数（デュアル・エッジ・ナチュラル・サンプル PWM に対して  $1/2$ ）に限られている。これゆえに、調整可能ループ・フィルターの周波数応答特性を、変調周波数の実際の、あるいは、現在のセッティング、および、選択的に負荷電力レベルに対して、ループ安定度制約または境界の内のオーディオ帯域幅の中でフィードバック・ループの最も高い可能なループ利得に到達するために、調整することは有利である。ループ・フィルターの周波数応答特性のこの動的または適応調整は、調整可能変調周波数の最大、最小周波数セッティングの両方において、クラスDオーディオ・アンプ中での上記の誤差と雑音メカニズムの優れた抑制へと導く。加えて、調整可能変調周波数のいかなる中間周波数セッティングでも、ループ・フィルターの周波数応答特性の特別に調整されたセッティングと結びつくことができる。10

#### 【0011】

したがって、有利な実施形態にしたがって、コントローラは、調整可能変調周波数の最小周波数セッティングに対してよりも、調整可能変調周波数の最大周波数セッティングに対して、調整可能ループ・フィルターのより高次数を選択するように構成される。調整可能変調周波数の最大周波数セッティングは、前述のように、好適には、5 MHz、ないし、それ以下に存在する。調整可能変調周波数の対応する最小周波数セッティングは、選択された最大周波数の  $1/2$  と  $1/4$  の間に存在することができ、好適には、150 kHz より上である。20

#### 【0012】

現在の負荷電力レベルは、コントローラにより種々の方法で、また、応答において選択される調整可能変調周波数の適切な周波数セッティングで検出することができる。そのような実施形態において、コントローラは、オーディオ信号レベル検出器を備える。コントローラは、変調制御信号の第1セット、および、選択的に、第2の出力ドライバに対する変調制御信号の第2セットの調整可能変調周波数を制御するのに適応している。これは、オーディオ入力信号の検出されたレベルに依存して、出力ドライバのH-ブリッジ・タイプに関連して下に記載される。オーディオ入力信号のレベルは、直接的な方法で、または、間接的に検出することができる。オーディオ入力信号のレベルは、変調デューティ・サイクル、または、パルス幅変調制御信号の変調インデックス、または、負荷信号の変調インデックスを検出または分析することによって間接的に検出することができる。当業者であれば、オーディオ入力信号のレベルは、多数の方法で、例えば、そのピークの電圧、平均的電圧、RMS電圧その他によって表現することができることを理解するであろう。30

#### 【0013】

調整可能ループ・フィルターは、連続時間周波数選択フィルタ、または、スイッチ・キャパシター・タイプ（時間離散）周波数選択フィルタを備えることができる。好適な実施形態にしたがって、調整可能ループ・フィルターは、フィードバック・ループの順方向信号パスに、たとえば、通常、エラー信号と呼ばれる加算ノードの出力信号と、パルス幅変調器の入力との間に挿入された低域フィルタを備える。これは、ループ・フィルターが、パ4050

ルス幅変調器のためにフィルタ処理したオーディオ信号を生成するようにするためである。別の実施形態において、調整可能ループ・フィルターは、負荷信号から加算ノードへ走るフィードバック・ループの逆信号バスに挿入された高域フィルタを備える。当業者であれば、加算ノードは、エラー信号を生成するそれらのそれぞれの位相に依存して、フィードバック信号とオーディオ入力信号とを加算したり、減算したりするように構成することができますことを理解するであろう。低域フィルタは、それぞれの積分器時定数とそれぞれの積分器利得係数を備える複数のカスケード接続積分器を含むことができる。カットオフ振動数と低域フィルタの次数は、カスケード接続積分器の数と、関連する積分器時定数との適切な選択によってセットすることができる。低域フィルタの好適な実施形態において、1つ以上のカスケード接続積分器は、最大出力電圧レベルまたは最大出力電流レベルのような積分器の最大出力レベルを制限するために出力レベル・クランプを備える。出力レベル・クランプは、好適には、カスケード接続積分器のチェーンにおいて、1つ以上のフロントエンド積分器に適用される。なぜなら、これらの積分器の出力信号の縮小は、飽和した状態からのループ・フィルターの回復時間を減らすために、そして、それゆえに、クラスDオーディオ・アンプの通常動作を回復させるために最も効果的であるからである。

#### 【0014】

出力レベル・クランプは、クランプされない積分器の最大の出力ピーク・ピーク信号電圧またはピーク・ピーク信号出力電流に相対して、クランプされた積分器の最大の出力ピーク・ピーク信号電圧またはピーク・ピーク信号電流を減少させる。1つの実施形態において、クランプされた積分器の最大出力ピーク・ピーク信号電圧は、クランプされない積分器の1/2より小さく、好適には、1/3より小さい。コントローラは、多数の方法で調整可能ループ・フィルターの周波数応答特性を調整するのに適していることがあり得る。1つの好適な実施形態においては、コントローラは、調整可能変調周波数のセッティングに基づいて、調整可能ループ・フィルターの次数を変えるように構成される。ループ・フィルターの次数は、2ないし8の第1のプリ・セット次数、たとえば第4次数から、第2のプリ・セット次数、第1のプリ・セット次数より1または2次数小さい次数に変更、または、切り替えることができる。別の実施形態において、コントローラは、調整可能ループ・フィルターの周波数応答特性ファクタをコントロールするために、0.25と4の間のスケーリング・ファクタのような共通のスケーリング・ファクタで複数の積分器の前記それぞれの積分器時定数を調整するように構成される。後者の実施形態において、ループ・フィルターの次数と傾斜特性は、一定のままであるが、しかし、フィードバック・ループのオープン・ループ帯域幅は変更される。さらに別の実施形態においては、調整可能ループ・フィルターの周波数応答特性は、コントローラにより、複数の積分器のそれぞれの利得係数を、調整可能ループ・フィルターの周波数応答特性ファクタをコントロールするための複数のスケーリング係数でスケーリングすることによって調整される。スケーリング係数は、例えば、スケーリング・ファクタは、0.5にセットすることができ、一連のスケーリング係数、第4次数ループ・フィルターに対して、0.0625、0.125、0.25、および、0.5の結果になるように、スケーリング・ファクタルールに従って異なることができる。スケーリング係数(N) = (スケーリング・ファクタ)<sup>N</sup>、ここでNは、ループ・フィルターの入力において、1から始まる積分インデックスである。

#### 【0015】

フィードバック・ループのオープン・ループ帯域幅は、効率的スイッチング周波数の、好適には、0.01倍と1.0倍との間、好適には0.1倍と0.5倍との間の値にセットされる。本願のコンテキストにおいては、オープン・ループ帯域幅は、オープン・ループ振幅特性の0dB利得の周波数として定義される。

#### 【0016】

本願クラスDオーディオ・アンプのいくつかの有利な実施形態によって、第1の出力ドライバは、ラウドスピーカ負荷への複数レベル負荷信号を生成するように構成される。これらの実施形態の各々は、第1の出力ノードで、ラウドスピーカ負荷にわたる第1の3レベル負荷信号を提供するために、例えば、中点値電圧のような第3の供給電圧をセットする

10

20

30

40

50

ように構成されるDC電圧源を備えている。1つのそのような実施形態において、DC電圧源は、第3の供給電圧にチャージされる、いわゆるフライング・キャパシタを備える。本願のクラスDオーディオ・アンプの後者の実施形態において、第1のドライバのアップ・レッグは、カスケードで接続する第1および第2の半導体スイッチを備え、第1のドライバのローワー・レッグは、カスケードで接続する第3および第4の半導体スイッチを備える。DC電圧源は、第3の供給電圧にチャージされ、前記第1および前記第2のカスケード半導体スイッチの間に位置する第1のノードと、第3および第4のカスケード半導体スイッチの間に位置する第2のノードとの間で接続されるキャパシタ（上述のフライング・キャパシタ）を備える。パルス幅変調制御信号の第1のセットは、- 第1の状態において、前記キャパシタの第1の端子を、前記第1および前記第3の半導体スイッチを通して、第1の出力ノードに接続し、- 第2の状態において、前記キャパシタの第2の端子を、第4および第2の半導体スイッチを通して、第1の出力ノードに接続する、ように構成される。第1および第2の供給電圧の間のDC電圧差は、アップ・レッグまたはローワー・レッグの少なくとも2つのカスケードまたは直列接続した連結半導体スイッチの間で分配されることとは、後者の実施形態の顯著に有利な点である。このカスケード半導体スイッチは、個々の半導体スイッチの絶縁破壊電圧条件を減らす。

#### 【0017】

本願クラスDオーディオ・アンプの他の複数レベル実施形態にしたがって、第1の出力ノードにおける3の供給電圧セッティングは、第1の供給電圧と第2の供給電圧との間で接続される、レジスタまたはキャパシタ・ネットワークの中間ポイントまたはタッピング・ポイントにおけるDC電圧から導出される。古典的なAD、BDパルス幅変調に対するクラスDオーディオ・アンプの複数レベル実施形態の顯著に有利な点は、ラウドスピーカ負荷と出力フィルタ・コンポーネント全体でのコモンモード・リップル電圧の抑制または減衰である。このコモンモード・リップル電圧は、パルス幅変調キャリアの、スイッチングまたは変調周波数の不必要的残りである。別の利点は、オーディオ入力信号の小さいレベルに対応する小さな変調デューティ・サイクルでの、より低い、出力フィルタ・インダクタ・リップル電流および出力フィルタ・キャパシタ・リップル電圧である。

#### 【0018】

DC電圧源は、{チャージされたキャパシタ、フローティングDC電源レール、バッテリー}のグループから選択した少なくとも1つのコンポーネントを備えることができる。フライング・キャパシタに基づいた好適な実施形態において、各々のフライング・キャパシタは、 $100\text{nF}$ と $10\mu\text{F}$ との間のキャパシタンスを持つことができる。DC電圧源は、クラスDオーディオ・アンプの動作の間、少ないエネルギー量を届けることを要求されるだけであり、リニア性の要求は緩和されているので、限られたキャパシタンスと物理的サイズのキャパシタをフライング・キャパシタとして使用することができる。

#### 【0019】

いくつかの有利な実施形態は、好適には、トポロジーにおいて、第1の出力ドライバと大部分は同一の第2の出力ドライバを備えるH-ブリッジ・出力ドライバに基づいている。ラウドスピーカ負荷は、前記ラウドスピーカ負荷に差動またはバランス負荷信号が適用されるように、第2の出力ドライバの第1の出力ノードと第2の出力ノードとの間に接続する。したがって、負荷信号をそれに供給するラウドスピーカ負荷に接続可能な第2の出力ノードを備える第2の出力ドライバを更に備えるクラスDオーディオ・アンプが提供される。この第2の出力ドライバは、第1の供給電圧と第2の出力ノードとの間で接続する1つ以上の半導体スイッチを備えるアップ・レッグと、第2の出力ノードと第2の供給電圧との間で接続する1つ以上の半導体スイッチを備えるローワー・レッグと備え、ここで、第2の出力ドライバの半導体スイッチの各々が、オン状態またはオフ状態に選択的に半導体スイッチを設定するために、半導体スイッチの状態を制御するのに適しているスイッチ制御端末を備え、このコントローラは、前記第2のドライバのそれぞれのスイッチ制御端末に対する調整可能変調周波数において、パルス幅変調制御信号の第2のセットを生成するようにさらに適合している。

10

20

30

40

50

## 【0020】

第2の出力ドライバは、第1の出力ドライバの上述の実施形態に関連して記載された、個々の特徴、あるいは、いかなる個々の特徴の組合せも、もちろん含むことができる。

## 【0021】

本願のクラスDオーディオ・アンプがH-ブリッジ出力ドライバを備える場合、2つ以上の異なった動作モードが、複数レベル・バランス負荷信号の異なる数のレベルを利用するように、それは、第1の出力ドライバの対応するパルス幅変調制御信号と第2の出力ドライバとの間の位相関係に依存する出力レベルの異なる数を提供するのに適していることがあり得る。これらの実施形態において、好適には、コントローラは、

- 第1の動作モードにおいて、3レベル・バランス負荷信号を生成するために変調制御信号の第1セットの対応する制御信号に対して逆位相を有する変調制御信号の第2セットの各々の制御信号を提供し、

- 第2の動作モードにおいて、5レベル・バランス負荷信号を生成するために変調制御信号の第1セットの対応する制御信号に対して逆位相、および、追加的+/-90度位相シフトを有する変調制御信号の第2セットの各々の制御信号を提供するように構成される。有利な実施形態にしたがい、コントローラは、前述のオーディオ信号レベル検出器を備える。これは、コントローラを、5-レベル、3-レベル・バランス負荷信号間のスイッチングが、オーディオ入力信号のレベルに基づいてコントロールされるように、オーディオ入力信号の検出されたレベルに依存して、第1の動作モードと第2の動作モードとの間をスイッチするように構成することができるようとするためである。コントローラは、オーディオ入力信号のレベルに基づくのと同様に、変調制御信号の第1セットおよび/または第2セットの変調周波数をコントロールするように、さらに構成されることができる。これは、好適な実施形態にしたがい、コントローラを、所定のレベル閾値によるオーディオ入力信号の検出レベルを比較するのに適応させることによって、達成される。コントローラは、検出オーディオ信号レベルが所定のレベル閾値より小さいとき、変調制御信号の第1セットや第2セットの第1の変調周波数をセットするのに、また、検出オーディオ信号レベルが所定のレベル閾値より大きいとき、変調制御信号の第1セットや第2セットの第2の変調周波数をセットするのに適応している。第1の変調周波数は、第2の変調周波数より低い。

## 【0022】

オーディオ入力信号とフィードバック信号とは、好適には、アナログ信号と加算ノードである。これらの信号を、ループ・フィルターにアナログ・フォーマットで誤差または差異信号を提供するために、アナログ・ドメインにおいて、減算、または、加算するように構成される。しかしながら、パルス幅変調器は、一般に、アナログまたはデジタル・パルス幅変調器としてインプリメントすることができる。デジタル・パルス幅変調器は、クロック信号、および、デジタル・フォーマットで提供されるフィルタ処理したオーディオ信号を要求する。これゆえに、フィードバック・ループは、例えば、A/D変換器、フィルタ処理したオーディオ信号を受信し、対応するデジタルまたはサンプル・フィルタ処理したオーディオ信号に変換するための好適には、5-10ビットの解像度を有するフラッシュA/D変換器のようなサンプリング・デバイスを備えることができる。サンプリング・デバイスは、デジタル・フィルタ処理したオーディオ信号を、デジタル・パルス幅変調器に対して生成するために、サンプリング・クロック信号に従って、動作している。サンプリング・クロック信号は、同期フォーマットにおけるコントローラのクロック信号から導出することができる。デジタル・パルス幅変調器は、サンプリング・クロック信号にしたがって、一様にサンプルされたパルス幅変調オーディオ信号を生成する、ように構成される。最後に、この実施形態では、コントローラは、好適には、一様にサンプルされたパルス幅変調オーディオ信号に基づいて、パルス幅変調制御信号の第1セットおよび/または第2セットを生成するのに適応している。サンプリング・デバイスで生成された量子化雑音は、この動作、すなわち、フィードバック・ループのエラー伝達関数(ETF)の大きさによって抑制される。サンプリング・デバイスは、代替的に、ループ・フィルターの前に

10

20

30

40

50

、加算ノードの出力において配置することができる。ここで、ループ・フィルターは、加算ノードからデジタル化された出力信号を直接に受信するデジタル・ローパス・フィルタとしてインプリメントすることができる。

#### 【0023】

第1および第2の出力ドライバは、任意の特定のアプリケーションの要求に依存して、たとえば、低電圧または高電圧アプリケーションに依存して、多数の種類の半導体スイッチを利用することができます。出力ドライバの半導体スイッチの各々は、好適には、1つまたはいくつかの並列に接続した、{フィールド効果トランジスタ(FET)、バイポーラ・トランジスタ(BJT)、絶縁ゲート・バイポーラ・トランジスタ(IGBT)}のグループから選択されたトランジスタを備える。第1の出力ドライバの1つ以上の半導体スイッチ、および、第2の出力ドライバの1つ以上の半導体スイッチは、好適には、それぞれ、例えば、NMOSトランジスタのようなCMOSトランジスタ・スイッチを備える。全体のクラスDオーディオ・アンプは、好適には、テレビ・セット、携帯電話、MP3プレーヤーなど、量の多い消費者向け音声アプリケーションのために、特に適切な、強固で低コスト・シングルチップ・ソリューションを提供するために、CMOSまたはBCD半導体ダイまたは基板の上に集積される。ここで、コストは、重要なパラメータである。オン状態または「ON」において、半導体スイッチは、MOSトランジスタのドレイン端子およびソース端子のような、制御されたスイッチ端子のペアの間で、好適には、例えば、10より小さい、あるいは、より好適には、1より小さい低い抵抗値を示す。オフ状態または「OFF」において、半導体スイッチは、制御された端末のペアの間で、好適には、例えば、1M、数Mを超えるような、大きい抵抗値を示す。半導体デバイスのオン抵抗は、一般に、その製造プロセスとその幾何形状により決定される。半導体スイッチは、CMOSトランジスタとしてインプリメントされるので、関連した幾何学的なパラメータは、CMOSトランジスタの長さと幅と(W/L)の比率である。CMOS半導体プロセスのPMOSトランジスタは、一般に、同様の大きさを有し、同一の半導体プロセスで製造されたNMOSトランジスタのオン抵抗より2-3倍大きいオン抵抗を示す。一般に、半導体スイッチの各々のオン抵抗は、好適には、0.01と10との間にある。

#### 【0024】

例えば、パルス幅変調制御信号の第1および第2のセットの各々の制御信号のような、変調制御信号のそれぞれの振幅またはレベルは、好適には、選択的に、オン状態/閉状態またはオフ状態/開状態において、問題の半導体スイッチを置くのに十分に大きい。いくつか実施形態において、第1および第2の出力ドライバは、第1のレベルから、この第1のレベルより高い、あるいは、より大きい第2のレベルに変調制御信号のそれぞれの振幅を上げるように構築された1つ以上のコンバータを備えることができる。第2のレベルは、好適には、半導体スイッチの各々を、必要であるときに、そのオン状態へ駆動するのに十分に高い。第1および第2の出力ドライバは、特定のアプリケーションの必要条件に依存して、前記供給電圧の広範囲、すなわち、第1および第2の供給電圧のDC供給電圧差異の範囲にわたって動作するのに適していることがあり得る。第1の供給電圧は、正のDC供給電圧であることができ、第2の供給電圧は、負のDC供給電圧またはグラウンド基準であることができる。有用なアプリケーションの範囲において、供給電圧差は、5ボルトと120ボルトとの間の直流電圧にセットすることができる。

#### 【0025】

本願発明の第2の態様は、上述の態様とその実施形態のいずれかにしたがう、クラスDオーディオ・アンプ、および、第1のドライバの出力ノード、および、第1および第2の供給電圧のうちの1つに動作的に接続したラウドスピーカ負荷を備えるサウンド再生アセンブリに関するものである。第2の供給電圧は、GNDであることができる。代替的に、サウンド再生アセンブリは、上で概説された第1および第2の出力ドライバを有するクラスDオーディオ・アンプに基づくH-ブリッジを備えることができる。ここで、ラウドスピーカ負荷は、第1および第2の出力ドライバのそれぞれの出力ノードの中間に、動作的に接続している。ラウドスピーカ負荷は、可動コイル(ダイナミック)の任意のタイプ、可

10

20

30

40

50

動アーマチュア、圧電、静電型の音声スピーカーを備えることができる。サウンド再生アセンブリは、好適には、例えば、テレビ・セット、コンピュータ、H i - F i 装置その他の据え付け型または携帯型のエンターテイメント製品での集積化のために形状、サイズの設定をされる。

**【 0 0 2 6 】**

サウンド再生アセンブリは、第 1 のドライバの出力ノードとラウドスピーカ負荷の間で接続する負荷インダクタと、ラウドスピーカ負荷と第 1 および第 2 の D C 供給電圧のうちの 1 つとの間に接続した負荷キャパシタと、を更に備えることができる。負荷インダクタとキャパシタは、組合せで、出力ノードまたは出力ノードにおけるパルス幅またはパルス密度変調出力信号のスイッチング周波数を結びついた高周波成分を抑制するローパス・フィルターを形成する。このローパス・フィルターのカットオフ振動数は、負荷インダクタとキャパシタとのコンポーネント値の適切な選択により、例えば、2 0 k H z と 1 0 0 k H z との間のような、上記のオーディオ・バンドであることができる。10

**【 図面の簡単な説明 】**

**【 0 0 2 7 】**

本願発明の好適な実施形態は、添付の図面に関連して更に詳細に記述される。

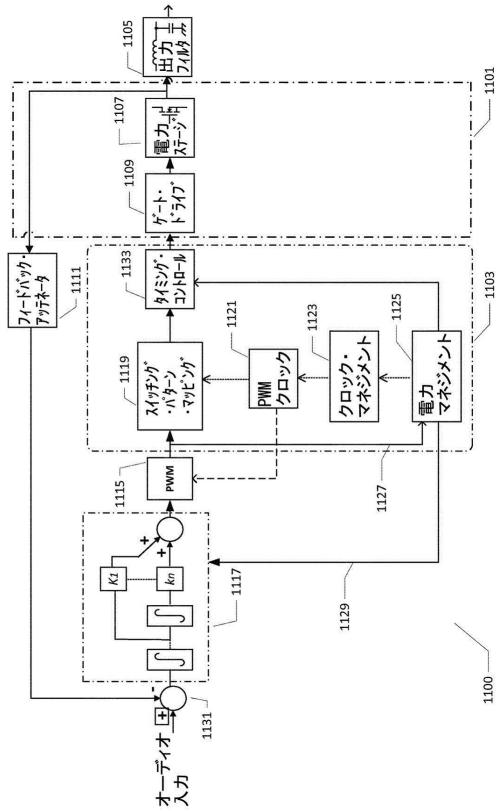

**【 図 1 】** 図 1 は、本願発明の好適な実施形態に従って、調整可能な周波数応答特性を有するループ・フィルターを備えるフィードバック・ループを有するクラス D オーディオ・アンプを図式的に示す。

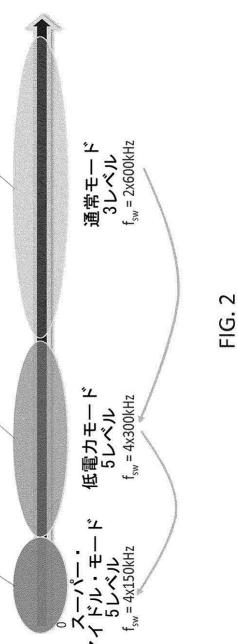

**【 図 2 】** 図 2 は、本願発明のクラス D オーディオ・アンプを、本願発明の好適な実施形態に従って、オーディオ入力信号の検出されたレベルに依存する異なる動作モードで動作させるためのモード・スイッチング・スキームを図示する。20

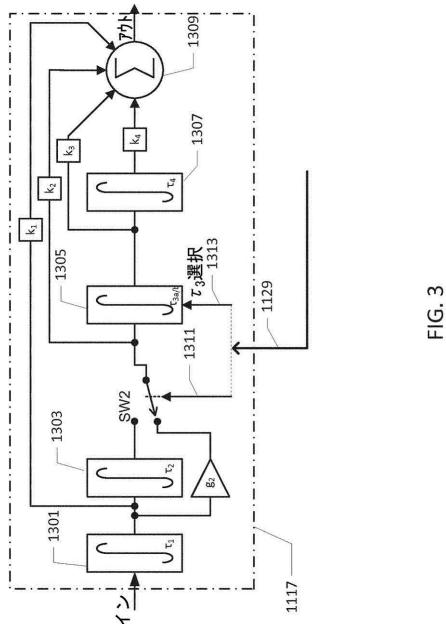

**【 図 3 】** 図 3 は、図 1 に描かれたクラス D オーディオ・アンプのフィードバック・ループで使用される調整可能あるいは適応可能ループ・フィルターの簡略図である。

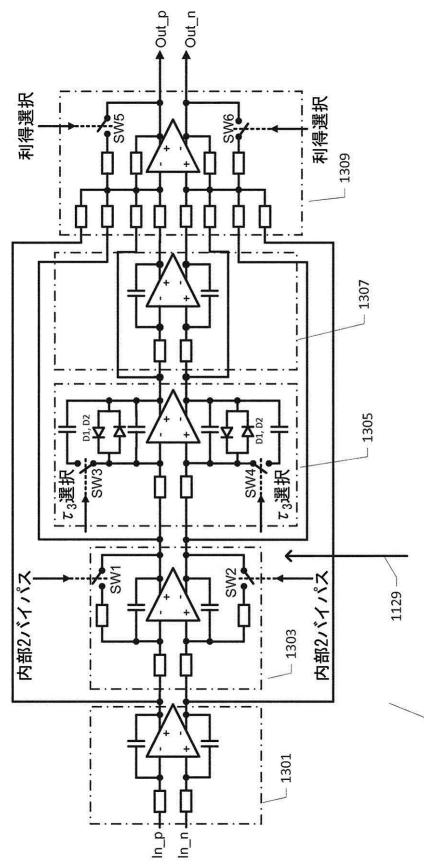

**【 図 4 】** 図 4 は、図 3 に描かれた調整可能あるいは適応可能ループ・フィルターの詳細な回路ダイアグラムである。

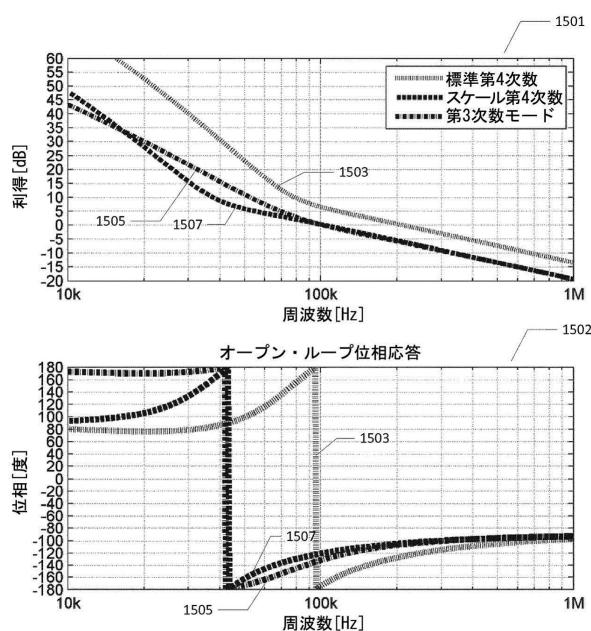

**【 図 5 】** 図 5 は、ループ・フィルターの周波数応答特性の 3 つの異なるセッティングに対する、本願発明のクラス D オーディオ・アンプのフィードバック・ループのオープン・ループの大きさと位相特性のプロットである。

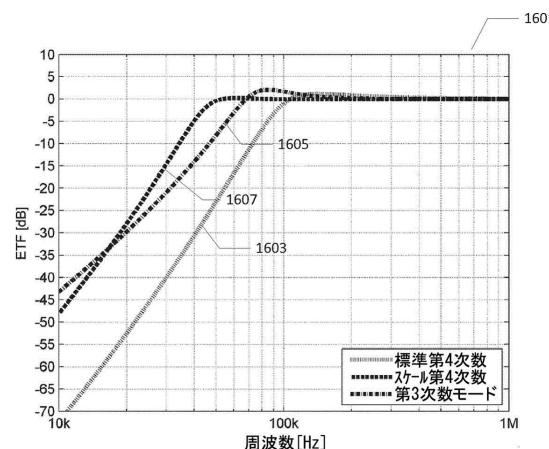

**【 図 6 】** 図 6 は、図 5 に描かれたループ・フィルターの 3 つの異なる周波数応答セッティングに対する、本願発明のクラス D オーディオ・アンプのフィードバック・ループの誤差伝達関数 ( E T F ) の大きさのプロットである。30

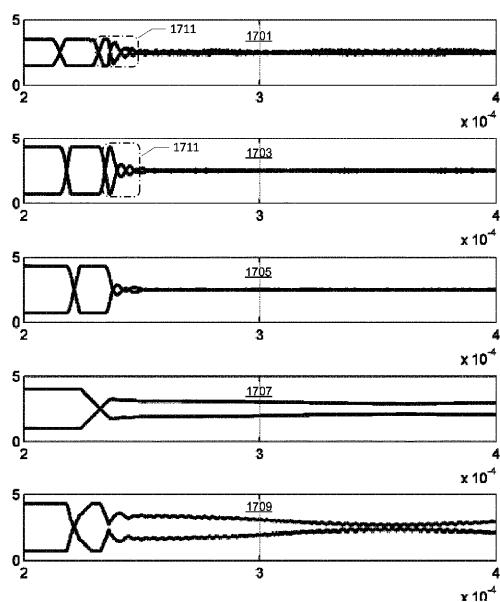

**【 図 7 】** 図 7 は、クラス D オーディオ・アンプのスタートアップにおけるクランプされない積分器に対する、時間にわたるループ・フィルターの個々の積分器出力信号のシリーズを示す。

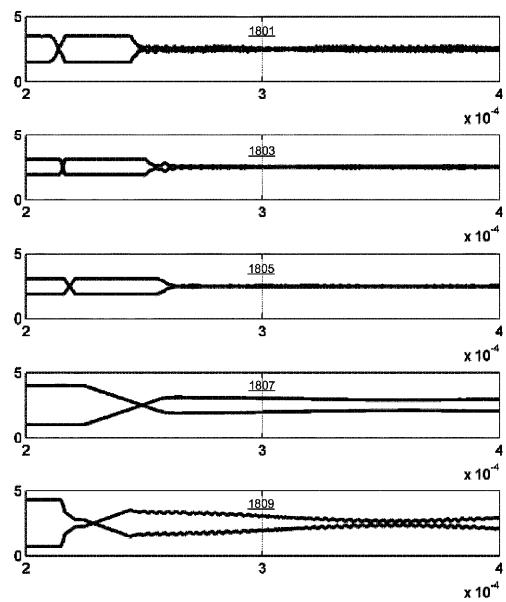

**【 図 8 】** 図 8 は、クラス D オーディオ・アンプのスタートアップにおけるクランプされた積分器に対する、時間にわたるループ・フィルターの個々の積分器出力信号のシリーズを示す。

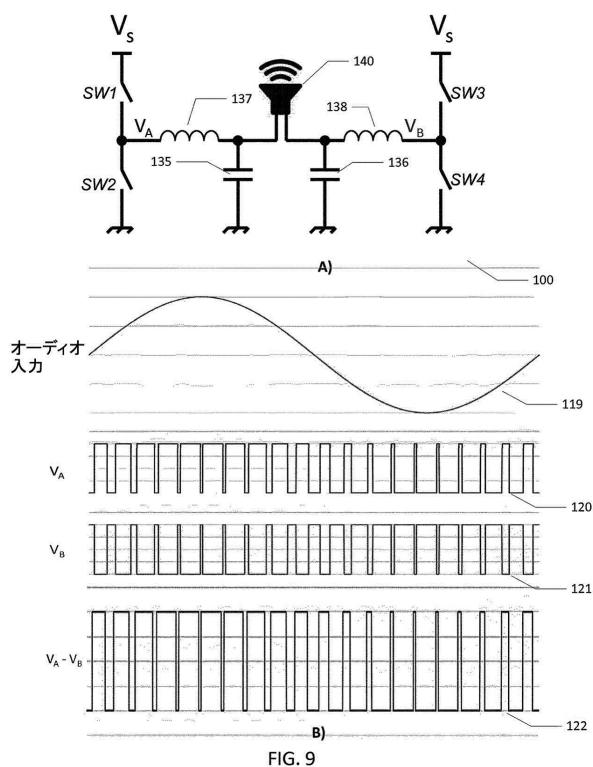

**【 図 9 】** 図 9 A と図 9 B とは、出力ドライバの第 1 の実施形態に従って、ラウドスピーカ負荷に接続する H - ブリッジ・ドライバ、および、A D 変調を利用する H - ブリッジ・ドライバのパルス幅変調出力信号波形を図示する。40

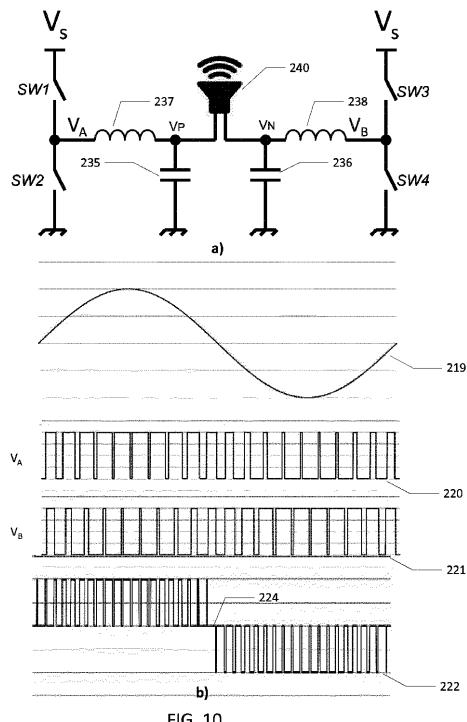

**【 図 1 0 】** 図 1 0 A と図 1 0 B とは、出力ドライバの第 2 の実施形態に従って、ラウドスピーカ負荷に接続する H - ブリッジ・ドライバ、および、B D 変調を利用する H - ブリッジ・ドライバのパルス幅変調出力信号波形を図示する。

**【 図 1 1 】** 図 1 1 は、図 9 および図 1 0 に描かれた H - ブリッジ・ドライバに対する負荷インダクタ・リップル電流波形と負荷キャパシタ・リップル電圧波形を示す。

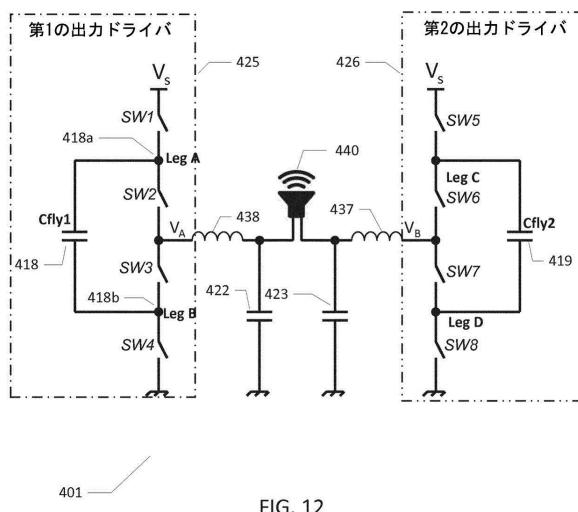

**【 図 1 2 】** 図 1 2 は、出力ドライバの第 3 の実施形態に従って、切り替え可能な複数レベル変調スキームを利用するラウドスピーカ負荷に接続する H - ブリッジ出力ドライバの概要図を示す。

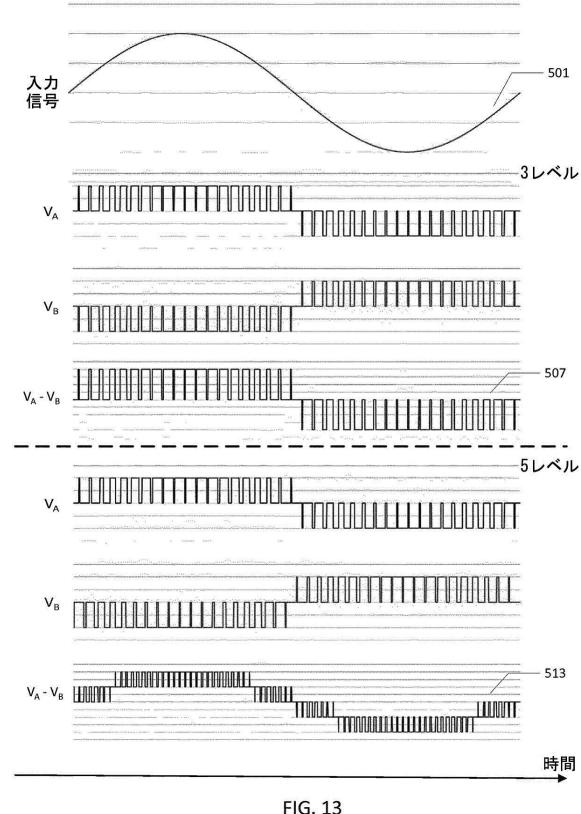

**【 図 1 3 】** 図 1 3 は、図 1 2 と図 1 4 に描かれた H - ブリッジ出力ドライバによって生成

50

された3 - レベルおよび5 - レベル・パルス幅変調出力信号波形を図示する。

【図14】図14は、出力ドライバの第4の実施形態に従って、ラウドスピーカ負荷に接続するH - ブリッジ出力ドライバの系統図である。

【図15】図15Aと図15Bとは、3レベル動作モードと5 - レベル動作モードとのそれぞれにおいて図12に描かれたH - ブリッジの出力ドライバの各々の半導体スイッチに対するパルス幅変調制御信号の生成を図示する。

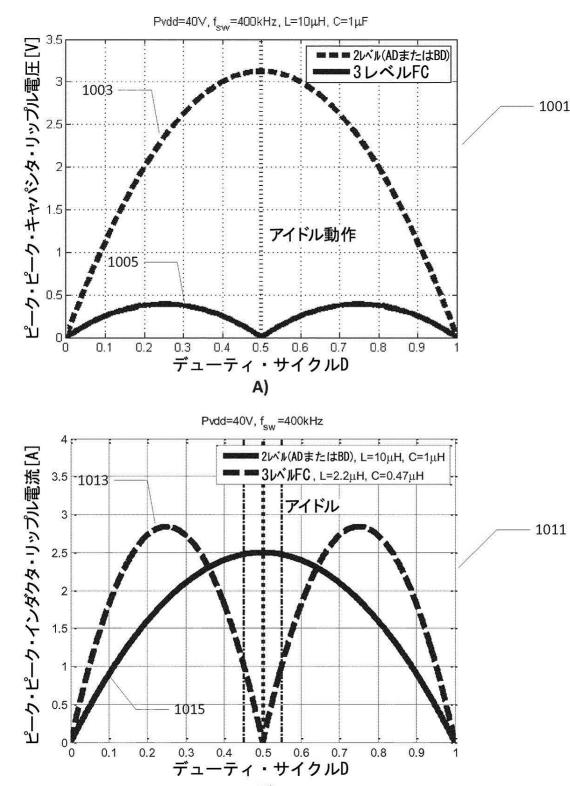

【図16】図16Aと図16Bとは、図9および図10の上で図示されるH - ブリッジ・ドライバのための変調デューティ・サイクル(クラスAD変調およびクラスBD変調)に対して、図12に描かれた3 - レベル変調において動作するH - ブリッジ・ドライバと比較して、負荷キャパシタ・リップル電圧と負荷インダクタ・リップル電流を、それぞれ示す。

10

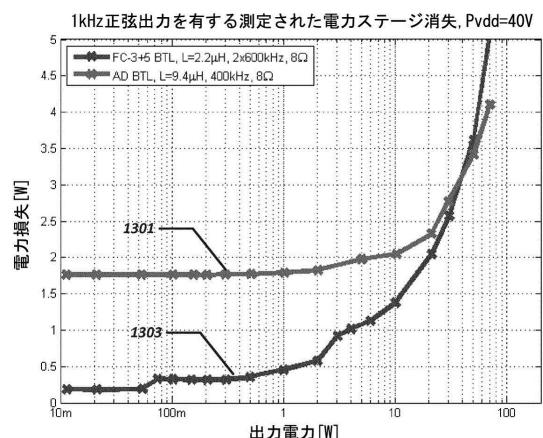

【図17】図17は、図9に描かれたクラスAD・H - ブリッジ・ドライバおよび図12に描かれた複数レベルH - ブリッジの出力ドライバに対する実験的に記録されたパワー損失データを図示する。

#### 【発明を実施するための形態】

##### 【0028】

図1は、たとえば図12に描かれた複数レベルH - ブリッジ出力ドライバ401と同様の、本願発明の好適な実施形態に従って、コントローラ1103に接続するバランス/作動またはH - ブリッジ・ドライバ1101を備えるPWBベース・クラスDオーディオ・アンプを図式的に示す。以下に詳細に説明されるように、本願のクラスDオーディオ・アンプ1100は、クラスDアンプ1100のフィードバック・ループまたはバスの調整可能ループ・フィルター1117の異なる周波数応答特性の間でのスイッチングに依存する高度な変調周波数を利用する。図式的に示されたH - ブリッジ・ドライバ1101は、バランス出力ドライバ1107の8つの半導体スイッチに対して、それぞれのパルス幅変調制御信号の信号振幅を、個々の半導体スイッチをON状態とオフ状態に適切に置くことを可能とするレベルに、増加するゲート・ドライブ回路1109を備える。ゲート・ドライブ回路1109は、種々のレベル変換器を備えることができる。パルス幅変調スイッチ制御信号の各々の振幅は、コントローラ1103を備える通常のCMOS集積回路から供給されるとき、およそ1.8ボルト、3.3ボルト、または5ボルトができる。H - ブリッジ・ドライバのDC供給電圧が、たとえば、およそ40のボルトにセットされるならば、同様にゲート・ドライブ回路1109により、パルス幅変調制御信号の振幅は、およそ40のボルトまで、あるいはもっと、上げられる。H - ブリッジ出力ドライバ1101は、前述したように図12に描かれたH - ブリッジ出力ドライバ401と、好適には、同一である。しかしながら、コントローラが、パルス幅変調制御信号を、問題の出力ドライバタイプの個々の半導体スイッチに適切に供給するように再構成される場合には、異なるタイプのシングルエンドまたはバランス(H - ブリッジ)出力ドライバを、逐一的に使用することができ、良い結果を提供する。出力フィルタ回路1105の電気特性は、好適には、H - ブリッジ出力ドライバ401に接続する出力フィルタとも同様である。出力フィルタ回路1105は、したがって、H - ブリッジ出力ドライバ1101の第1および第2の出力ノードの各々に接続する、負荷インダクタと負荷キャパシタを備える。

30

40

##### 【0029】

コントローラ1103は、ソフトウェア・プログラム可能な構成について、あるいは、たとえば、デジタル・ステート・マシンを備える専用ハードウェアとして、実行可能なプログラム命令のセット、または物理的に配線された状態に従って、下記の機能または動作を提供するように構成されるデジタル・シグナル・プロセッサ(DSP)を備えることができる。クラスDオーディオ・アンプ1100は、オーディオ・イン・ノードにおいてアナログ・オーディオ入力信号を受信するために調整可能ループ・フィルター1117の前に配置されたアナログ加算ノード1131を更に含む。H - ブリッジ出力ドライバの第1のおよび/または第2の出力ノードから導出されたフィードバック信号は、出力フィルタ回路1105の前において、フィードバック・アッテネータ1111を介して、加算ノード1

50

131に接続する。負荷フィードバック信号は、加算ノード1131により、調整可能ループ・フィルター1117の入力に印加される誤差信号または差異信号を形成するために、アナログ・オーディオ入力信号から減算される。この誤差信号は、したがって、本願発明の実施形態のアナログ回路としてインプリメントすることができる調整可能ループ・フィルター1117の入力に印加される。調整可能ループ・フィルター1117は、本願発明のこの実施形態において、図3および図4に関連して、以下に詳細に記載されているように、4つのカスケード接続積分器を備える。当業者であれば、このループ・フィルターの代替的な実施形態は、より少ない、あるいは、もっと多いカスケード接続積分器、または、他のタイプの低域フィルタを使うことができることを理解するであろう。この積分器は、図1に、積分器シンボルとそれぞれの利得係数 $k_1 - k_n$ によって図式的に示される。これらは、アナログ・パルス幅変調器回路1115またはPWM回路への伝達の前に、結果として生じるオーディオ入力信号をローパス・フィルターにかけるように動作する。当業者であれば、調整可能ループ・フィルター1117の出力信号が、たとえば、フラッシュまたはシグマ-デルタA/D変換器によって、デジタル化される場合には、PWM回路1115は、デジタルPWM回路と置き換えることができることを認識するであろう。

### 【0030】

PWM回路1115の変調または搬送周波数は、コントローラ1103の内に配置され、PWM回路1115への同期パルスを生成するPWMクロック回路1121により、制御される。PWM回路1115は、変調周波数セットで、または、PWMクロック回路1121により制御されたナチュラル・サンプル・パルス幅変調オーディオ信号(natural sampled pulse width modulated audio signal)を生成する、このナチュラル・サンプル・パルス幅変調オーディオ信号は、スイッチング・パターン・マッピング回路1119に伝えられる。スイッチング・パターン・マッピング回路1119は、図15A)、図15B)に関連して下で説明されるように、各々の電力ステージ1107の8つの半導体スイッチに対して適切な位相とタイミングでパルス幅変調制御信号を生成するように構成される。本願発明のこの実施形態において、H-ブリッジ出力ドライバ1101の第1および第2の出力ドライバの各々は、4つのスタック半導体スイッチを備える場合、スイッチング・パターン・マッピング回路1119の出力は、オプショナル・タイミング・コントローラ1133に伝えられる8つのパルス幅変調制御信号を備える。タイミング・コントローラ1133は、8つのパルス幅変調制御信号の1つ以上の特定のタイムベース調整、たとえば、同じ制御信号のオーバーラップがないことを確実にするために、制御信号の特定のペアの間での無駄時間制御を実行するのに適していることができる。変調制御信号の8つのタイムベースを調整したパルス幅は、先に述べたように、その後ゲート・ドライブ1109に送られる。本願の実施形態においては、スイッチング・パターン・マッピング回路1119は、電力ステージ1107のそれぞれの8つの半導体スイッチに対して、パルス幅変調制御信号の各々が、ナチュラル・サンプル・パルス幅変調オーディオ信号であるように、完全に、アナログ・ドメインで動作する。スイッチング・パターン・マッピング回路1119は、適切なタイミングと極性で、図12、図15a、図15bに関連して、下記に記載されるように、H-ブリッジ出力ドライバ1101の8つの個々の半導体スイッチ(SW1-SW8)へのパルス幅変調スイッチ制御信号を生成するように構成される。パルス幅変調制御信号の各々の変調または搬送周波数が、上述のように、クラスDアンプに、調整可能なPWM変調周波数が提供されるように、クロック管理回路1123によりセットされたクロック周波数制御信号に従って、動作しているPWMクロック・ジェネレータ1121により、セットされる。パワー・マネジメント回路1125は、パワー・マネジメント回路1125がスイッチング・パターン・マッピング回路1119の入力に供給されるパルス幅変調オーディオ信号の変調デューティ・サイクルを検出することを可能とする変調感知入力ポート1127を備える。検出されたデューティ・サイクルが、結果となるオーディオ入力信号の瞬間レベルを示すので、パワーマネジメント・モジュールは、パルス幅変調制御信号の調整可能変調周波数の周波数セッティング・ファクタ、あるいは、H-ブリッジ出力ドライ

10

20

30

40

50

バ 1 1 0 1 に印加されるスイッチ制御信号をコントロールするために、このオーディオ・レベルの情報を利用する。本願の実施形態においては、調整可能変調周波数は、オーディオ入力信号の予めセットされた3つのセッティング、高レベル、中間レベルおよび、低レベルのそれぞれに対する、150 kHz、300 kHz、および、600 kHzの間で切り替えられる。当業者であれば、コントローラ1103は、本願発明の他の実施形態において、更なる予めセットされた変調周波数セッティングを使うように構成することができることを理解するであろう。さらにまた、調整可能変調周波数の特定の周波数設定は、特定のアプリケーションに依存して、広く変化することができる。調整可能変調周波数の最大セッティングは、いくつかの有用な実施形態において、300 kHzと5 MHzの間に存在することができる。本願の実施形態においては、コントローラ1103は、調整可能変調周波数の周波数セッティングに基づいて、調整可能ループ・フィルター1117の周波数応答特性を制御するように構成される。この制御器のパワー・マネジメント回路1125は、調整可能変調周波数の選択されたセッティングに依存して、適応的態様で、フィルタ制御ラインまたはバス1129を介して、ループ・フィルター1117の周波数応答特性を変更する。1つの実施形態にしたがい、ループ・フィルターの次数は、たとえば、第4次数低域フィルタと、第3次または第2次低域フィルタとの間で、変更、あるいは、切り替えられる。別の実施形態において、1つ以上の積分器のそれぞれの積分器時定数(図4の項目310、1303、1305、1307)は、ループ・フィルターの次数は、不变のままであるが、しかし、カットオフ振動数は、例えば、0.25と4との間のファクタで、上げる、または、下げられるように、変更、あるいは、切り替えられる。これは、以下で、図3の詳細なループ・フィルター系統図の記載に関連して更に詳細に説明される。ループ・フィルター1117の調整可能な周波数応答特性は、以下に記載されているように、必然的にいくつかの利点を伴う。

10

20

#### 【0031】

ループ・フィルター1117の周波数応答特性は、典型的には、フィードバック・ループが、調整可能変調周波数の最大セッティングにおいて、コンポーネント拡大と生産拡大のための要求された安全性の限界の範囲内でちょうど安定であるように、設計される。これは、フィードバック・ループの中のクラスDアンプの回路とコンポーネントの非理想的ふるまいによって導入される歪み・雑音生成メカニズムを抑制するために有利である。これらの歪み・雑音生成メカニズムは、一般に、複雑であり、例えば、出力ドライバのパワー・トランジスタのタイミング誤差、フィードバック・バスの非理想的な周波数応答、と再量子化誤差など、によるエイリアシング誤差のような種々のソースを含むことがあり得る。さらにまた、タイムベース量子化誤差が、本願発明のいくつかの実施形態において、導入され得る。ここで、アナログPWMが、H-ブリッジ出力ドライバ1107、または、他のタイプの出力ドライバのスイッチング・パターン・マッピングを実行するために、同期(クロック)デジタル・ステート・マシンと併せてパルス幅変調制御信号を生成するために利用される。一般に、出力ドライバ・タイミング誤差、および、エイリアシング誤差は、負荷または、出力パワー・レベルの増加とともに、増加する傾向がある。時間量子化誤差によって誘発された誤差電力は、スイッチング周波数、あるいは、所与のデジタル・サンプリング周波数に対する変調周波数に比例している。したがって、誤差と雑音のこれらのタイプの抑制の必要は、最高の負荷電力レベルにおいて、およびより高い変調周波数において最も顕著である。より低い負荷電力レベル、および、より低い変調周波数で、さほどアグレッシブでない誤差と雑音の抑圧に対して、調整可能ループ・フィルター1117の周波数応答特性を選択することは、充分に許容できることが多い。

30

40

#### 【0032】

変調周波数の最大セッティング、および高負荷電力レベルにおけるループ・フィルター1103のちょうど安定した設計は、コントローラ1103が変調周波数の最大セッティングより低いセッティングを選択するときに、フィードバック・ループは、本質的に不安定になる傾向があることを意味する。これは、フィードバック・ループの安定的帯域幅が、変調周波数の特定の分数(デュアル・エッジ・ナチュラル・サンプルPWMに対して1/

50

)に限られているために起こる。これゆえに、ループ・フィルター1117の周波数応答特性を、変調周波数の実際の、あるいは、現在のセッティング、および、選択的に負荷電力レベルに対して、オーディオ帯域幅の中で最も高い可能なループ利得に、関連するループ安定度制約または境界に対して、到達するように、調整することは有利である。変調周波数のセッティングに基づいた、ループ・フィルター1103の周波数応答特性のこの動的な、または適応的な調整は、クラスDアンプにおいて、調整可能変調周波数の最大、最小周波数セッティングの両方において、上記の誤差と雑音メカニズムの優れた抑制へと導く。加えて、調整可能変調周波数のいかなる中間周波数セッティングでも、ループ・フィルター1103の周波数応答特性の特別に調整されたセッティングを有することができる。

10

### 【0033】

1つの実施形態において、ループ・フィルターの次数は、調整可能変調周波数が減らされるときには、コントローラにより、ループ・フィルター1103の周波数応答特性の調整を実行するために、減らされる。これは、フィードバック・ループの安定度を、低い変調周波数において、ループ利得の大きさをそれほど犠牲にすることなく、また、すべての積分器時定数を調整することなく維持する。通常、安定した第3次数設計に減らすべき第4次数ループ・フィルターに対して、(図3の中で図示されるように)、それゆえに、それは、3つのパラメータを変えるのに必要なだけである。他方、積分器時定数を調整することによって、第4の次数ループ・フィルターの周波数応答を測定するためには、合計4つのパラメータの変更を要求する。

20

### 【0034】

この実施形態において、パワー・マネジメント回路またはモジュール1125は、H-ブリッジ出力ドライバ1107の出力ノードにおいて、バランス負荷信号に対して3レベル変調モードと5レベル変調モードとの間で選択するために、オーディオ・レベル情報を利用するのにさらに適している。当業者であれば、この特徴は、まったくオプションであり、調整可能変調周波数の選択されたセッティングに依存するループ・フィルター1117の周波数応答特性の上述の動的または適応的調整は、3レベルと5レベル・バランス負荷信号の間でのそのようなスイッチングなしで機能することを理解するであろう。特に、当業者であれば、ループ・フィルター1117の周波数応答特性の上述の動的な調整は、例えば、下の図9-11に関連して記述された古典的なクラスADまたはBD変調のために構成された通常のH-ブリッジなどの、複数レベル能力のない出力ドライバと等しくよく機能することを認識するであろう。パワー・マネジメント回路1125は、検出された変調デューティ・サイクルに依存して、3つの異なった動作モードの間で切り替えるよう構成される。低いほうと、高いほうの変調閾値は、変調周波数の適切なセッティングと、動作モードの適切なセッティング(本願実施形態の3レベル・モードまたは5レベル・モード)との両方を、検出された変調デューティ・サイクルが低いほうの変調閾値より下にあるとき、第1の、または、スーパー・アイドルのモードに入るように、決定する。この第1の変調閾値は、たとえば、およそ0.02のような0.01と0.05との間の変調インデックスにセットすることができる。スーパー・アイドル・モードにおいて、変調周波数セッティング $f_{sw}$ は、600kHzの効率的スイッチング周波数を提供するために、およそ150のkHzであり得、スイッチ制御信号は、好適には、スイッチング・パターン・マッピング回路1119によって、5レベル変調を提供するように構成される。この動作モードは、図2に、スーパー・アイドル・モード1203として、視覚的に表される。ここで、水平の矢印は、オーディオ入力信号のレベルの増加の方向、したがって、変調デューティ・サイクルの増加を示す。

30

### 【0035】

パワー・マネジメント回路1125は、一旦、検出された変調デューティ・サイクルが低いほうの変調閾値を上回り、しかし、まだ、高い方の変調閾値の下にあるならば、第2または低出力モード1205に切り替える(図2を参照)ように構成される。この第2の変調閾値は、たとえば、およそ0.1のような0.05と0.2との間の変調インデックス

40

50

にセットすることができる。低電力モードにおいて、変調周波数セッティング  $f_{s_w}$  は、好適には、スーパー・アイドル・モードと比較して増加される。電力ステージ 1107 の H - ブリッジ出力ドライバにおける非線形性の抑制を改善するように、フィードバック・バスのより高いループ帯域幅を許容するからである。低電力モードの変調周波数セッティングは、スーパー・アイドル・モードの後者の変調周波数セッティングのおよそ 2 倍はであることができる。好適には、コントローラは、ナチュラル・サンプル・パルス幅変調オーディオ信号の変調周波数  $f_{s_w}$  の所与のセッティングに対して、フィードバック・バスのループ帯域幅を最大にする 5 レベル変調の存在を維持するために、スイッチ制御信号を生成するように構成される。最後に、パワー・マネジメント回路 1125 は、一旦、検出された変調デューティ・サイクルが高いほうの変調閾値を上回るならば、第 3 または標準モード 1207 に切り替える（図 2 を参照）ように構成される。標準モードにおいて、変調周波数  $f_{s_w}$  は、好適には、例えば、通常モードにおける動作モードの変化のために、低電力モードの変調周波数と比較して、1.5 と 4 との間のファクタだけのような、所定の量だけ、増加される。変調周波数が一定のままであるならば、この変化は、ループ帯域幅を減らす傾向がある。しかしながら、ラウドスピーカ負荷にわたる出力信号の 3 - レベル変調は、大きなオーディオ信号レベルにおいて EMI パフォーマンスを向上させる有利な態様で、負荷キャパシタ・リップル電圧のコモンモード・コンポーネントを抑制する。

### 【0036】

図 3 は、調整可能あるいは適応可能ループ・フィルター 1117 の簡略図ダイアグラムである。調整可能あるいは適応可能ループ・フィルター 1117 は、4 つのカスケード接続した積分器、1301、1303、1307 および、1307 を備える。第 1 の積分器 1301 は、オーディオ入力信号からのフィードバック信号の減算の後に、加算ノードまたはジャンクション 1131 の出力において供給される誤差信号または差異信号である入力信号を受けるために接続される。調整可能ループ・フィルター 1117 の応答特性周波数は、上述のように、制御ラインまたはバス 1129 を介して、制御可能である。4 つの積分器、1301、1303、1307 および、1307 の各々は、関連する利得係数  $k_1 - k_4$  と、関連する積分器時定数、 $\tau_1 - \tau_4$  を有する。それは、各々の積分器の周波数応答を一緒にセットしたものである。4 つの積分器の出力信号、1301、1303、1305 および 1307 は、端子「Out」において、最終的なループ・フィルター出力信号を提供するために、積算ジャンクション 1309 において、積算されるか、結合される。調整可能ループ・フィルター 1117 は、ループ・フィルターの次数が、制御ラインまたはバス 1129 により制御された第 4 次数低域フィルタと第 3 次数ローパス・フィルターとの間で変更されるのを許容するように第 2 の積分器 1303 にわたって接続したバイパス・スイッチを更に備える。加えて、制御ラインまたはバス 1129 は、第 3 の積分器の積分器時定数  $\tau_3$  に動作的に接続し、後者がコントローラ 1103 のコントロール下で調整されるのを可能にする。調整可能ループ・フィルター 1117 の第 3 の積分器 1307 は、以下のさらなる詳細説明に記載されているように、この積分器の最大の出力電圧を制限するクランプ回路（図示せず）をさらに備える。

### 【0037】

図 4 は、図 3 の上で図式的に表される調整可能ループ・フィルター 1117 の詳細な回路ダイアグラムである。調整可能ループ・フィルター 1117 は、電源装置ノイズ除去を改善し、ループ・フィルター 1117 のリニア性と信号スイング能力を強化するために、バランスであるか差動回路に基づいている。第 1 の積分器 1301 の入力において、結果として生じるオーディオ信号は、差動信号として、第 1 の演算増幅器のそれぞれの差動入力に供給される。第 1 の積分器 1301 の積分器時定数は、第 1 の演算増幅器に接続した、フィードバック・コンデンサと、入力レジスタとの組合せによって決定される。第 2 の積分器 1303 は、第 1 の積分器と同様の方法で、フィードバック・コンデンサと、入力レジスタとの組合せによって決定された積分器時定数を有する。また、第 3 および第 4 積分器 1307、1309 と、それぞれ、同様である。しかしながら、第 2 の積分器は、バイパス・スイッチのペアの閉状態において後のコンポーネントを短絡させるためにフィード

バック・キャパシタのそれぞれのものに接続したバイパス・スイッチ SW1、SW2 のペアを備えるこのように、第2の積分器 1303 の積分器機能は、選択的に除くことができる、例えば、バス 1129 を通して供給される制御信号にしたがって、信号利得または減衰機能に変えることができる。バイパス・スイッチ SW1、SW2 のペアは、実際に、多数の方法で、たとえば、適切に構成されるゲート制御信号によって制御されるそれらの MOS トランジスタ回路としてインプリメントすることができる。第3の積分器 1307 は、各々が半導体ダイオード D1、D2 を備える同一の出力電圧クランプ回路のペアを備える。半導体ダイオード D1、D2 は、アンチパラレル構成で第3の積分器 1307 のフル差動演算増幅器の2つの側のそれぞれの出力と入力との間に接続する。半導体ダイオード D1、D2 の各ペアは、演算増幅器の出力において最大出力電圧または信号振幅を、その演算増幅器の固有の出力電圧能力の下にある出力電圧に制限している。前に述べた、積分器時定数<sub>3</sub>の第3の積分器の調整は、それらの半導体スイッチ SW3、SW4 によって、積分器キャパシタと並列に接続することができる追加的な積分器キャパシタのペアによってインプリメントされる。これゆえに、半導体スイッチ SW3、SW4 が閉じている、あるいは、「ON」であるとき、トータル積分器キャパシタンスは、積分器時定数<sub>3</sub>を増加し、第3の積分器 1307 のカットオフ振動数を低くするために、増加される。4つの積分器の出力信号、1301、1303、1307 および 1307 は、アナログ加算回路 1309 において積算されるか、結合される。バランス信号として最終的なループ・フィルター出力信号 Out\_p および Out\_n を生成するフル・バランス演算増幅器の周辺に設計される。アナログ加算回路 1309 は、最終的に、一対の半導体スイッチのペア SW5、SW6 によってコントロールされるオプション・ゲイン調整またはセッティング機能を備える。10

20

#### 【0038】

図5は、ループ・フィルター 1117(図3と図4)の周波数応答特性の3つの異なるセッティングに対する、クラスDオーディオ・アンプ 1100 のフィードバック・ループのオープン・ループ利得の大きさ・位相レスポンスのプロットを含む。振幅プロット 1501 の第1の振幅特性曲線 1503 は、変調周波数の最大セッティングにおいて適用されるループ・フィルターの第4次数低域フィルタ・セッティングに対して計算される。第2の振幅特性曲線 1505 は、上で示したように、第2の積分器(図4の 1203)のバイパスにより生じるループ・フィルターのローパス・セッティングの第3次数セッティングに対して計算される。第3の振幅特性曲線 1507 が、ループ・フィルター 117 の低域フィルタの第4次数セッティングに対して計算される。ここで、すべての積分器時定数は、カットオフ周波数が、振幅特性曲線 1503 と比較して半分にされるが、しかし、レスポンス形状本質的に維持されるように、2の共通ファクタでスケールされる。下のプロット 1502 は、振幅特性の上記の3つの異なるセッティングに対して、対応する位相特性曲線 1503、105 および 1507 を示す。30

#### 【0039】

図6は、図5のプロットの上で表されるループ・フィルターの周波数応答特性の3つのセッティングに対する、本願発明のクラスDオーディオ・アンプのフィードバック・ループの誤差伝達関数(ETF)の大きさのプロット 1601 である。20kHzにおける雑音と歪みとの抑制は、ループ・フィルターの標準第4次数セッティングに対して、およそ 52dB、ループ・フィルターのスケールされた第4次数と、第3次数セッティングに対して、それぞれおよそ 28dB、30dB になる。誤差伝達関数(ETF)の大きさは、このループ・フィルターのローパス積分器振幅特性から期待されるような高域通過特性を備えている。前述のように、出力ドライバ・タイミング誤差とエイリアシング誤差は、クラスDアンプの負荷または、出力パワー・レベルの増加とともに、増加する傾向がある。調整可能ループ・フィルターは、たとえば、これが前述した、ループ・フィルターの3つの異なる周波数応答特性の間でのスイッチングに依存するオーディオ・レベルを通して要求されたときに、ETFは、そのような誤差と雑音メカニズムの最も高い抑制を有することを確実にする。40

50

## 【0040】

図7は、図4に表されるループ・フィルター1117の4つのカスケード接続積分器1301、1303、1305、1307、および、加算アンプ1309、それぞれの個々の積分器出力信号を表すプロット1701、1703、1705、1707、1709のシリーズを示す。X軸スケールは、およそ $200\mu\text{s}$ の時間スパンにわたる時間を示す。積分器出力信号のプロットは、クランプされない積分器出力の状態に対するものである。ループ・フィルターは、すべてのカスケード接続積分器が、ループ・フィルターを通して（すなわち、いずれもバイパスされない）信号バスに配置されるように、標準的第4次モードで動作する。 $225 - 230\mu\text{s}$ のあたりの時間間隔の間（ウィンドウ1711の内部）プロット1701の積分器No.1と、プロット1703の積分器No.2との出力信号の振動する挙動は、クラスDオーディオ・アンプのスタートアップまたはオーバーロードにおいてフィードバック・ループは、不安定に近いことを示す。

## 【0041】

図8は、図4に表されるループ・フィルター1117の4つのカスケード接続積分器1301、1303、1305、1307、そして、加算アンプ1309、のそれぞれの個々の積分器出力信号を表すプロット1801、1803、1805、1707、1809の第2のシリーズを表す。X軸スケールは、およそ $200\mu\text{s}$ の時間スパンにわたる時間を示す。積分器出力信号のプロットは、積分器No.2（図4の項目1303）と積分器No.3（図4の項目1305）とに対するクランプされた積分器出力の状態に対するものである。残りの積分器は、クランプされないままにされるが、しかし、当業者であれば、本願発明の他の実施形態において、より少ない、または、追加的な積分器出力が、クランプされ得ることを理解するであろう。好適には、積分器カスケードの少なくとも積分器No.2およびNo.3は、両方ともクランプされる。図7のプロット1701の積分器No.1と、プロット1703の積分器No.2との出力信号のはっきりした振動挙動は、図7の同じプロットと比較して、プロット1801と1803の積分器出力の検査から明らかであるように効果的に抑制された。これゆえに、フィードバック・ループの安定性と回復時間とは、積分器出力電圧クランプにより、著しく改善された。

## 【0042】

図9は、ラウドスピーカ負荷140に接続するH-ブリッジ出力ドライバ100の、図式的に示す。H-ブリッジ出力ドライバ100の一方の側は、図1の図式的に示された第1の出力ドライバ1101の第1の出力ドライバとして用いることができる。スイッチSW3（SW4）を備えるH-ブリッジ出力ドライバ100の第2の側は、第2の出力ドライバとして使うことができる。ここで、スイッチSW3、SW4は、コントローラで生成される適切な位相のパルス幅変調制御信号の第2のセットにより駆動される。H-ブリッジ出力ドライバ100は、差動またはバランス負荷信号を提供するために、ラウドスピーカ負荷140のそれぞれの側に接続された出力ノード $V_A$ 、 $V_B$ を備える。図9bに表された変調出力信号波形120、121が、H-ブリッジの出力ドライバのそれぞれの出力ノード $V_A$ 、 $V_B$ において、提供される。クラスDオーディオ・アンプは、半導体スイッチSW1、SW2、SW3とSW4のコントロール端子に印加される（図示せず）それぞれのパルス幅スイッチ制御信号に従って、ラウドスピーカ負荷140が、正DC供給電圧 $V_s$ と、GNDなどの負DC供給電圧の間で、および、その逆で、交互に接続されるよう、バランス負荷信号のAD変調のために構成される。 $V_s$ とGNDとの間でのラウドスピーカ負荷の交互スイッチングが、出力信号波形122により図示されるように、第1の位相セッティングにおいて、SW1およびSW4がそれぞれのONになること、あるいは、導電状態およびSW2とSW3が、のそれぞれのOFF状態またはオフ状態になることによって、得られる。第2の位相において、SW1、SW4は、それぞれOFF、または不伝導性状態にセットされ、そして、SW2とSW3とは、それぞれのオン状態にセットされる。パルス幅変調出力信号波形に対応するオーディオ入力信号波形が、波形119によって図示される。負荷インダクタ138、137は、H-ブリッジ出力ドライバ100のそれぞれの出力ノード $V_A$ と $V_B$ との間で、かつ、ラウドスピーカ負荷140の両側で接

10

20

30

40

50

続する。同様に、負荷キャパシタ 136、135 は、ラウドスピーカ負荷の各々の端子または側から GND に接続する負荷キャパシタと負荷インダクタとの組み合わせ動作は、ラウドスピーカ負荷にわたり出力信号波形において変調または搬送周波数コンポーネントを抑制するために出力ノード  $V_A$ 、 $V_B$  をわたるパルス幅変調出力波形 120、121 の、ローパス・フィルタリングを提供するためである。

#### 【0043】

図 10 は、図 1 で図示される H - ブリッジ・ドライバと同様のトポロジーを有し、ラウドスピーカ負荷 240 に接続した別の H - ブリッジの出力ドライバを図示する。しかしながら、本願のクラス D オーディオ・アンプは、出力ノード  $V_A$ 、 $V_B$  にわたるバランス出力信号のいわゆる BD 变調のために構成される。クラス BD 变調において、特定の時間間隔の間に出力ノード  $V_A$ 、 $V_B$  を同じ状態にセッティングすること、または、同時に電圧、すなわち、 $V_S$  または GND を供給することを含む、「0」の状態が存在する。「0」の状態において、ラウドスピーカ負荷 240 の両端または端子は、ラウドスピーカ負荷 240 にわたる駆動電圧をゼロにセットするように、同時に、 $V_S$  か GND のいずれかに接続する。したがって、オーディオ入力信号のレベルがゼロに近いとき、それぞれの出力ノード  $V_A$ 、 $V_B$  におけるパルス幅変調出力波形 220、221 のスイッチングは、放棄される。これは、オーディオ入力信号 219 の振幅がゼロを横切るところの参照番号 224 によってマークされた時刻におけるパルス幅変調出力波形 222 において、図示される。しかしながら、ラウドスピーカ負荷 240 にわたるゼロ差動電圧を有する状態の存在にもかかわらず、2つの異なる状態、または電圧レベル、すなわち、 $V_S$  または GND だけが、出力ドライバの出力ノード  $V_A$ 、 $V_B$  の各々で存在することに注意することは重要である。

#### 【0044】

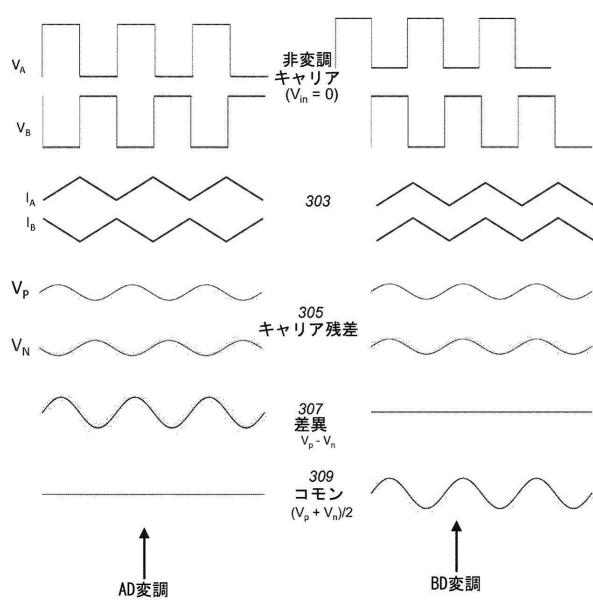

図 11 は、とりわけ、図 1 および図 2 で表されるクラス D アンプに対する負荷インダクタ・リップル電流波形および負荷キャパシタ・リップル電圧波形を図示する。オーディオ入力信号の「ゼロ」レベルの状況または振幅に対応する波形は、第 1 および第 2 の出力ノード  $V_A$ 、 $V_B$  でのパルス幅変調出力波形の変調は、ゼロであるように、図 11 に図示される。図面の左側の波形は、図 9 に関連して上で概説されたように、AD 变調に対応する。一方、右側の波形は、図 10 に関連して上で概説されたように、クラス BD 变調に対する同じ電圧または電流の変数を表す。波形プロット 303 の上で、それぞれの負荷インダクタ・リップル電流波形は、矩形キャリア波形の上で負荷インダクタ 237、238 と 137、138 の積分機能を反映する。ラウドスピーカ負荷のそれぞれの入力端子で測定された波形プロット 305 の上のおよその正弦形の負荷キャパシタ・リップル電圧波形  $V_P$  および  $V_N$  は、矩形キャリア波形の上で負荷キャパシタ 235、236、および、135、136 のローパス・フィルター効果を反映している。負荷キャパシタ・リップル電圧波形  $V_P$  および  $V_N$  は、クラス AD と BD 变調クラスに対して実質的に同一の振幅であるのに対して、差動リップル電圧、すなわち、 $V_P$  マイナス  $V_N$ 、は、波形 307 によって図示されるように、図示されるラウドスピーカ負荷にわたって、異なることに注意すると興味深い。クラス AD 变調に対して、差動リップル電圧は、個々のキャパシタ・リップル電圧の 2 倍であり、一方、差動リップル電圧は、クラス BD 变調に対しておよそ 0 である。クラス BD 变調に対するリップル電圧値の低いレベルは、パルス幅変調キャリア波形のラウドスピーカ負荷への適用に関連して低いパワー損失を示す。しかしながら、クラス BD 变調に対するラウドスピーカ負荷にわたりおよそ 0 差動リップル電圧にもかかわらず、コモンモード波形プロット 309 の上で図示されるように、顕著なコモンモード差動電圧が依然として存在する。そして、このタイプの変調に対してパワー損失となる。これは、実際のクラス D アンプでパワー損失を引き起こす負荷インダクタを通して前後に循環する負荷電流によって引き起こされる。これは、実際のインダクタが、固有の抵抗およびヒステリシス損失を有するからである。

#### 【0045】

図 12 は、複数レベル・バランス負荷信号を利用する本願発明の好適な実施形態に従って

10

20

30

40

50

、ラウドスピーカ負荷440に接続するH-ブリッジ出力ドライバ401を図式的に示す。本願の実施形態においては、第1のDC電圧源は、第3の供給電圧を、好適には、第1の出力ドライバ425の第1の出力ノード $V_A$ において $V_S$ の半分にセットするように構成される。第2のDC電圧源は、第3の供給電圧を、好適には、第2の出力ドライバ426の第2の出力ノード $V_B$ において $V_S$ の半分にセットするように構成される。第1および第2のDC電圧源は各々が、以下で説明されるように、チャージされたフライング・キャパシタを備える。

#### 【0046】

H-ブリッジ出力ドライバ401の動作は、ラウドスピーカ負荷は、動作的に、出力ノード $V_A$ と $V_B$ のペアの間で相互接続する場合、以下に詳細に説明される。一方、パルス幅変調出力信号波形が、差動フォーマットで、第1および第2の出力ノード $V_A$ と $V_B$ とにおいて、図13において、図示される。図2に描かれた変調モード・スイッチング・スキームに関連して説明されるように、本願のクラスDオーディオ・アンプは、好適には、検出された変調デューティ・サイクルが、高い方の変調閾値を上回る場合、高出力パワー・レベルのためにバランス負荷信号の3レベル変調を使用して標準モードで動作するように構成される。低出力パワー・レベルに対して、本願のクラスDオーディオ・アンプは、好適には、バランス負荷信号の5レベル変調を使用して低パワーまたはアイドル・モードで動作するように構成される。

#### 【0047】

H-ブリッジ出力ドライバ401は、出力ノード $V_A$ と $V_B$ とを通して、ラウドスピーカ負荷440に動作的に接続する。H-ブリッジの出力ドライバ401は、第1および第2の実質的に同一の出力ドライバ425、426を備える。出力ドライバの各々は、4つのカスケード接続CMOSトランジスタ・スイッチ、たとえば、上位のDC供給電圧またはレール $V_S$ と、下位のDC供給電圧または、グラウンドまたはGNDレールの形のレールとの間で連結したNMOSトランジスタを備える。さらにまた、各々の出力ドライバ425、426は、第3の出力レベル、または、出力ノード $V_A$ と $V_B$ とにおいて、 $V_S$ とGNDとの間でのおよそ中間に存在する中点電圧の生成を可能にするチャージされたいわゆるフライング・キャパシタ $C_{f1y1}$ 、 $C_{f1y2}$ 、 $418$ 、 $419$ を備える。これらは、もっと詳細に下で説明されるように、複数レベル・バランス負荷信号の生成を可能とする。本願の実施形態においては、H-ブリッジ・ドライバ401の第1の出力ドライバ425のアッパー・レッグAは、CMOSトランジスタ、好適には、NMOSトランジスタなどの直列またはカスケード接続半導体スイッチのペアを備える。直列接続された半導体スイッチSW1、SW2は、第1の端部において $V_S$ に接続し、反対の端部において、出力ノード $V_A$ に接続する。第1の出力ドライバ425のローワー・レッグB425は、出力ノード $V_A$ からGNDへ接続する直列またはカスケード接続CMOS半導体スイッチSW3とSW4の別のペアを備える。H-ブリッジ・ドライバ401の第2の出力ドライバ426のアッパー・レッグCは、電気特性において好適にはレッグAのCMOS半導体スイッチSW1とSW2のそれぞれのものと同一である直列またはカスケード接続CMOS半導体スイッチSW5とSW6のペアを備える。ローワー・レッグDは、さらに、電気特性において好適にはレッグBのCMOS半導体スイッチSW3とSW4のそれぞれのものと同一であるカスケード接続CMOS半導体スイッチSW7とSW8の別のペアを備える。上述のCMOS半導体スイッチは、図4に、それぞれのゲートまたは制御端子によって、コントロールされる理想的なスイッチ素子として図式的に示される。半導体スイッチの各々は、図式的に示されるように、単一の半導体スイッチから成ることができる、あるいは、他の実施形態では、共有の制御端子を有する複数の並列に連結した個々の半導体スイッチを備えることができる。

#### 【0048】

図1に表されるクラスDオーディオ・アンプにおいて、このコントローラは、適切な振幅のパルス幅変調制御信号の第1のセットをCMOS半導体スイッチSW1、SW2、SW3とSW4の、それぞれ、第1、第2、第3および第4ゲート端子(図示せず)のそれぞ

10

20

30

40

50

れのものに適用するように構成される H - ブリッジ・ドライバ 401 の動作の間、それにより、これらの CMOS 半導体スイッチのそれぞれの状態をコントロールする。それによつて、CMOS 半導体スイッチの各々状態は、問題のパルス幅変調制御信号の遷移に従つて、オン状態または「ON」と、オフ状態または導通無し、との間で、トグルする、あるいは、切り替わることができる。同じことを、ゲート端子のそれぞれにおいて、パルス幅変調制御信号の第 2 セットを供給される第 2 の出力ドライバ 426 の CMOS 半導体スイッチ SW5、SW6、SW7 および SW8 に適用する。オン状態または伝導状態または閉状態における CMOS 半導体スイッチ SW1、SW2 の各々のオン抵抗は、特定のアプリケーションの要求、特に、ラウドスピーカ負荷 440 のオーディオ周波数インピーダンスにしたがつて、かなり変化することがあり得る。半導体スイッチのオン抵抗は、スイッチの大きさ、制御端子における駆動電圧、すなわち、本願実施形態のゲート端子、および、半導体プロセス結果に依存して、変化する。半導体スイッチ SW1、SW2 は、好適には、出力ノード  $V_A$ 、 $V_B$  を通して供給されるパワーが、ラウドスピーカ負荷 440 で主に消散され、より小さな程度に、半導体スイッチの個々のオン抵抗では、スイッチ・パワー損失として消費されるように、ラウドスピーカ負荷 440 のオーム抵抗より非常に小さいオン抵抗を有するように構成されるか、設計される。CMOS 半導体スイッチ SW1、SW2、SW3、SW4、SW5、SW6、SW7 および SW8 の各々のオン抵抗は、本願発明のこの実施形態において、好適には、0.05 と 5 との間、例えば、0.1 と 0.5 オームとの間のような値にセットされる。

## 【0049】

可動コイル、可動アーマチュア、または、他のいかなるタイプのオーディオ・スピーカを備えることができるラウドスピーカ負荷 440 は、H - ブリッジ・ドライバ 400 の第 1 および第 2 の出力ノード  $V_A$  と  $V_B$  との中間で動作的に接続する。ラウドスピーカ負荷 440 は、典型的には、かなりのインダクティブ・コンポーネントと直列に、抵抗コンポーネントを含む。第 1 の負荷インダクタ 438 および第 1 の負荷キャパシタ 422 は、ローパス・フィルターを形成するように、ラウドスピーカ負荷 440 の、第 1 の出力ノード  $V_A$  と第 1 の端子との間で接続する。第 1 の負荷インダクタ 438 と第 1 の負荷キャパシタ 422 とは、H - ブリッジ・ドライバの第 1 および第 2 の出力ドライバ 425、426 の集積回路インプリメンテーションに外部コンポーネントとして提供することができる。ローパス・フィルタリングは、ラウドスピーカ負荷 440 にわたって印加される負荷信号において、出力ノード  $V_A$ 、 $V_B$  において存在する出力波形の変調またはスイッチング周波数コンポーネントを抑制する。本願の実施形態においては、第 1 の負荷キャパシタ 422 は、100nF と 500nF との間の、例えば、およそ 220nF のようなキャパシタンスを持つことができる第 1 の負荷インダクタ 414 は、1μH と 5μH との間の、例えば、およそ 2.20μH のようなインダクタンスを持つことができる。第 2 の出力ノード  $V_B$  の接続した第 2 の負荷インダクタ 437 と、第 2 の負荷キャパシタ 423 とのそれぞれの値は、好適には、同一である。

## 【0050】

第 1 のフライング・キャパシタ 418 は、SW1、SW2 と、フライング・キャパシタ端子との間で電気的接続を提供するために、第 1 の出力ドライバ 425 のアッパー・レッグ A のカスケード接続 CMOS 半導体スイッチ SW1、SW2 のペアの間で第 1 の接続ノード 418a に接続する 1 つの端子を有する。第 1 のフライング・キャパシタ 418 の反対の端子は、第 1 の出力ドライバ 425 のローワー・レッグ B のカスケード接続 CMOS 半導体スイッチのペア SW3、SW4 の間にある第 2 の接続ノード 418b に接続される。第 1 のフライング・キャパシタ 418 は、本願発明の H - ブリッジ・ドライバ 400 の動作が始まる前に、 $V_S$  と GND との間の DC 電圧差のおよそ 2 分の 1 に等しい、すなわち、下位の DC 供給電圧の GND 接続のために、単に  $V_S$  の半分の所定の直流電圧にプリチャージされる。したがつて、第 1 のフライング・キャパシタ 418 は、第 1 および第 2 の接続ノード 418a、418b の間で、 $1/2 V_S$  の DC 電圧差を維持するか、セットする DC 電圧源として動作する。コントローラ（図 1 の項目 1103 として図示される）は

、C M O S 半導体スイッチ S W 1、S W 4 が、決して同時にオン状態でない、あるいは、パルス幅変調制御信号のゼロ変調で導通する、すなわち、オーディオ信号入力は、ゼロであるように、逆位相でオーバーラップがなく、S W 1、S W 4 に印加されるパルス幅変調制御信号提供するように構成される。同様に、S W 2 および S W 3 に印加されるパルス幅変調制御信号は、好適には、C M O S 半導体スイッチ S W 2 と S W 3 とが、決してONでない、あるいは、同時にゼロ変調において導通しないように、パルス幅変調制御信号のゼロ変調において、逆位相を有し、オーバーラッピングしていない。これは、第1の出力ドライバ4 2 5 の第1の状態の第1のフライング・キャパシタ4 1 8 は、S W 1、S W 3 が、同時にONであり、一方、S W 4 と S W 2 は、両方のOFFであり、V<sub>s</sub>マイナス、V<sub>s</sub>の1/2の出力レベル、すなわち、V<sub>s</sub>の1/2のV<sub>A</sub>における出力レベルに至るときに、V<sub>s</sub>と出力ノードV<sub>A</sub>との間で接続することを意味する。<sup>10</sup> 第2の第1の出力ドライバ4 2 5 の状態において、第1のフライング・キャパシタ4 1 8 は、S W 2 と S W 4 とが同時にONであって、一方、S W 1 および S W 3 は、両方ともOFFで、GNDプラスDC供給電圧の1/2の出力レベル、すなわち、第1の状態の場合のように1/2V<sub>s</sub>に至るとき、GNDと、S W 2 と S W 4 とを通した出力ノードV<sub>A</sub>との間で接続する。したがって、第1のキャパシタが、本願の実施形態において、DC供給電圧V<sub>s</sub>の出力の1/2に等しくなっているノードV<sub>A</sub>において、第3の供給電圧レベルを生成するように動作する。この第3の供給電圧レベルは、第1のフライング・キャパシタ4 1 8 の、1/2V<sub>s</sub>へのDC電圧の選ばれた適合性のため、上で概説されるように、第1と第2の出力ドライバ状態において生成される。したがって、第1のドライバ4 2 5 の出力ノードV<sub>A</sub>での出力レベルは、したがって、3つの別々のレベル、V<sub>s</sub>、1/2V<sub>s</sub>、および、GNDの間でトグルする。当然に、GND電圧は、他の実施形態において、負または正のDC供給電圧、たとえば、実質的に大きさにおいて第1のDC供給電圧に等しい負DC電圧を含むことができる。<sup>20</sup>

#### 【0051】

図示されたH-ブリッジの出力ドライバ4 0 1 は、第2の出力ノードV<sub>B</sub>を通して、ラウドスピーカ負荷4 4 4 0 の別の側または端子に接続する第2の出力ドライバ4 2 6 を備える。例えばC M O S 半導体スイッチ S W 5、S W 6、S W 7、S W 8などの個々のコンポーネント、および、第2の出力ドライバ4 2 6 のフライング・キャパシタ4 1 9 の回路トポロジー効果と電気特性は、好適には、実質的に、第1の出力ドライバ4 2 5 の対応するコンポーネントのものと同一である。同様に、外部の第2の負荷インダクタ4 3 7 および、外部の第2の負荷キャパシタ4 2 3 は、好適には、第1の出力ドライバ4 2 5 と関連する対応する外部コンポーネントと同一である。<sup>30</sup>

#### 【0052】

標準モードにおいて、パルス幅変調制御信号は、S W 1、S W 5 に対する信号は、ゼロ変調において逆位相であるように、構成される。S W 4 と S W 8 に、S W 3 と S W 7 に、S W 2 と S W 6 に印加されるパルス幅変調制御信号のそれぞれのペアに対しても同じことである。パルス幅変調制御信号のこの構成は、フライング・キャパシタC<sub>f1y1</sub>、C<sub>f1y2</sub>(4 1 8、4 1 9)の所定のDC電圧のそれぞれの第1のDC供給電圧V<sub>s</sub>の約1/2へのセッティングと接続して、第1および第2の出力ノードV<sub>A</sub>とV<sub>B</sub>との間で上述した3レベル・パルス幅変調バランス出力信号が生成されることを確実とする。この3レベル・パルス幅変調出力信号は、図13において、波形5 0 7として図示される。図示されるように、本願の3レベル・パルス幅変調バランス出力信号は、第1および第2の出力ノードV<sub>A</sub>とV<sub>B</sub>の状態スイッチング率が、オーディオ信号入力が0に近づくときに減少することにおいて、前に概説された先行技術のクラスB D変調と有利な特性を共有する。クラスDオーディオ・アンプの動作の低電力モードまたはアイドル・モードにおいて、種々のパルス幅変調制御信号は、S W 1 および S W 5 に対する信号が、逆にされ、そして、追加的に、ゼロ変調におけるその他の各々に対して+/-90度位相シフトされるように、構成される。S W 4 と S W 8 に、S W 3 と S W 7 に、S W 2 と S W 6 に印加されるパルス幅変調制御信号のそれぞれのペアに対しても同じことである。パルス幅変調制御信号のこ<sup>40</sup><sup>50</sup>

の適合は、フライング・キャパシタ  $C_{f1y1}$ 、 $C_{f1y2}$  (418、419) の所定の DC 電圧の第 1 の DC 供給電圧  $V_s$  の約 1/2 へのセッティングと接続して、ラウドスピーカ負荷のための望ましい 5 レベル・パルス幅変調バランス出力信号が、第 1 および第 2 の出力ノード  $V_A$  と  $V_B$  との間で生成されることを確実とする。この 5 - レベル・パルス幅変調バランス出力信号は、図 13 に、出力波形 513 として図示される。出力信号波形 513 は、2 つの別々のレベル・パルス幅変調波形、ゼロを上回るもの、ゼロ・レベル、および、ゼロより下のパルス幅変調波形の 2 つの別々のレベルを示す。図示されるように、本願の 5 レベル・パルス幅変調出力信号は、第 1 および第 2 の出力ノード  $V_A$  と  $V_B$  の状態スイッチング率が、オーディオ信号入力が 0 に近づくときに減少することにおいて、前に概説されたクラス BD 变調および 3 レベル变調と有利な特性を共有する。

10

#### 【0053】

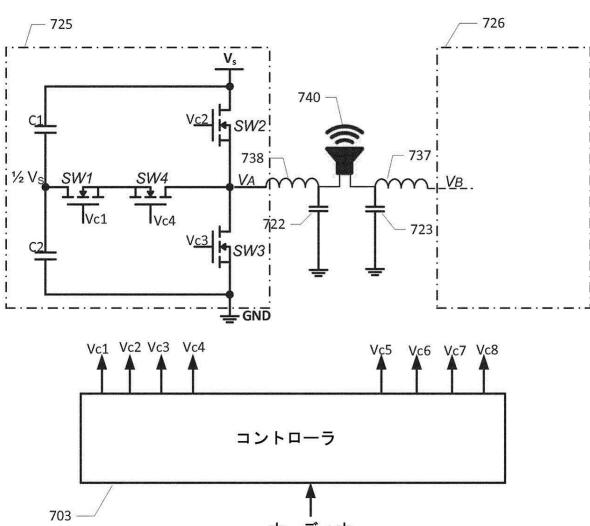

図 14 は、クラス D オーディオ・アンプの第 4 の実施形態に従って、ラウドスピーカ負荷 740 に接続する第 1 および第 2 の出力ドライバ 725、726 をそれぞれ備える H - ブリッジ出力ドライバを有するクラス D オーディオ・アンプの系統図である。図示されたクラス D オーディオ・アンプは、また、複数レベル・バランス負荷信号を利用する。本願の実施形態においては、第 1 の DC 電圧源は、第 3 の供給電圧を、好適には、第 1 の出力ドライバ 725 の第 1 の出力ノード  $V_A$  において  $V_s$  の半分にセットするように構成される。第 2 の DC 電圧源は、第 3 の供給電圧を、好適には、第 2 の出力ドライバ 726 の第 2 の出力ノード  $V_B$  において  $V_s$  の半分にセットするように構成される。第 1 および第 2 の DC 電圧源は、以下でもっと詳細に説明されるように、 $V_s$  電圧レベルの 1/2 分を生成するために、キャパシタ電圧分配器と半導体スイッチのそれぞれのペアを備える。

20

#### 【0054】

出力ドライバ 725、726 の各々のトポロジーは、しばしば、「中性点クランプ」3 レベル・ハーフブリッジとして言及される。第 1 の負荷インダクタ 738 と第 1 の負荷キャパシタ 722 は、第 1 のドライバ 725 の出力ノード  $V_A$  と、ローパス・フィルターを形成するラウドスピーカ負荷 740 の第 1 の端子との間で接続する。別のローパス・フィルターが、第 2 のドライバ 726 の第 2 の出力ノード  $V_B$  と、ラウドスピーカ負荷 740 の第 2 の端子との間で接続した第 2 の負荷インダクタ 737 と第 2 の負荷キャパシタ 723 によって形成される。これらのローパス・フィルターの各々の目的と特性は、出力ドライバ 401 の第 1 の実施形態に関連して前に述べたものと同じである。第 1 の出力ドライバ 725 は、第 1 の供給電圧  $V_s$  と第 1 の出力ドライバの第 1 の出力ノード  $V_A$  との間で直列に接続する第 1 の半導体スイッチ SW2 を有するアッパー・レッグを備える。第 2 のレッグは、GND、すなわち、第 2 の供給電圧と、 $V_A$  との間で直列に接続する第 2 の半導体スイッチ SW3 を備える。第 3 および第 4 の半導体スイッチ SW1、SW4 は、それぞれ、第 3 の供給電圧、すなわち、中点電圧 1/2  $V_s$  および  $V_A$  の間で、直列に接続する。中点電圧 1/2  $V_s$  は、第 3 の供給電圧源により、第 1 の、選択的に第 2 の、出力ドライバ 725、726 のための第 3 の供給電圧として生成される。第 3 の電圧源は、中点電圧を提供するために、第 1 の供給電圧  $V_s$  と GND 電圧の間で直列に接続する供給キャパシタ、C1 と C2 のペアを備える。供給キャパシタ、C1、C2 は、中点電圧は、第 1 の供給電圧  $V_s$  のおよそ 1/2 にセットされるように、好適には、実質的に等しいキャパシタンスを有する。半導体スイッチの各々、SW1、SW2、SW3 および SW4 は、問題の半導体スイッチの状態をコントロールするために、ゲート端子、Vc1、Vc2、Vc3 および Vc4 を備える。半導体スイッチ、SW1、SW2、SW3 および SW4 は、N MOS トランジスタのような CMOS トランジスタを、それぞれ、備えることができる。

30

#### 【0055】

第 2 の出力ドライバ 726 は、反対側に接続した第 2 の出力ノード  $V_B$ 、または、ラウドスピーカ負荷 740 の端子を備える。第 2 の出力ドライバ 726 は、第 1 の出力ドライバ 725 と同様に、回路トポロジーにおいて接続する半導体スイッチ SW5、SW6、SW7 および SW8 を備える。第 2 の出力ドライバ 726 は、中点電圧を生成するために、別々の第 3 の供給電圧源、好適には、第 1 の出力ドライバの第 3 の供給電圧源と同様である

40

50

ものを備えることができる。代替的に、第1の出力ドライバ725に対して生成された中点電圧を、同様に、第2の出力ドライバによって利用することができる。第2の出力ドライバ726の回路トポロジー、および、その個々のコンポーネントの電気特性は、好適には、第1の出力ドライバ725のそれらと実質的に同一である。

#### 【0056】

コントローラ703は、オーディオ入力信号、オーディオを受信し、そこからパルス幅変調制御信号の第1のセット、および、パルス幅変調制御信号の第2セットを導出するように構成される。パルス幅変調制御信号の第1のセットは、CMOS半導体スイッチSW1、SW2、SW3およびSW4のそれぞれのゲート端子に印加されるVc1、Vc2、Vc3およびVc4によって図示される。パルス幅変調制御信号の第2のセットは、第2の出力ドライバ726の内部に配置されたCMOS半導体スイッチSW5、SW6、SW7とW8のそれぞれに印加されるVc5、Vc6、Vc7およびVc8によって図示される。

10

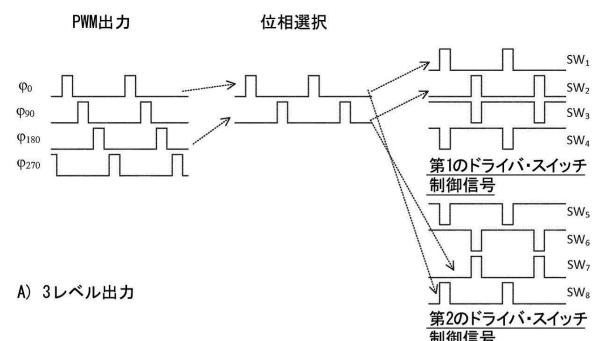

。コントローラ703は、標準動作モードにおいて、ラウドスピーカ負荷740にわたる3レベル負荷信号が生成され、上述した低パワー・モードおよびアイドル・モードにおいて、ラウドスピーカ負荷740にわたる5レベル負荷信号が生成されるように、パルス幅変調制御信号の第1セットとパルス幅変調制御信号の第2セットの間の所定の位相関係をコントロールするように構成される。パルス幅変調制御信号の第1および第2のセットの生成のプロセスの例示的な実例が、図15に関連して、以下の追加的な詳細において説明される。図15a、図15bは、図12に表されるH-ブリッジ出力ドライバ401の各々の半導体スイッチに対するパルス幅変調制御信号の生成を図示する。パルス幅変調制御信号SW1-SW8は、コントローラ1103(図11の上で)のスイッチング・パターン・マッピング回路(図1の1119)によって、オーディオ入力信号から導出される。

20

。図15a、図15bのパルス幅変調制御信号SW1-SW8の図示された波形の形状は、オーディオ入力信号の所定の非ゼロの瞬間的なレベルに対してマップされる。すなわち、変調である。図15aは、図1のクラスDオーディオ・アンプ1100の3レベル動作モードにおけるパルス幅変調制御信号の生成を図示する。一方、図15bは、5レベル動作モードにおけるパルス幅変調制御信号の生成を図示する。両方の動作モードにおいて、図1の上で表されるアナログPWM1115は、4つのパルス幅変調信号<sub>0</sub>、<sub>90</sub>、<sub>180</sub>および<sub>270</sub>を導出するように構成される。これらは、互いから、連続して90度位相シフトされたものであり、これらをスイッチング・パターン・マッピング回路119に伝達する。

30

#### 【0057】

図15aの上で表される3レベル動作モードにおいて、スイッチング・パターン・マッピング回路は、第1の出力ドライバ(図12の項目425)の半導体スイッチSW1、SW2に対するパルス幅変調制御信号SW1、SW2として、パルス幅変調信号<sub>0</sub>および<sub>180</sub>を選択することにより、位相選択を実行する。スイッチング・パターン・マッピング回路は、さらに、第1の出力ドライバの半導体スイッチSW3、SW4に対するパルス幅変調制御信号として、SW2とSW1に対して、それぞれ逆位相であるか、逆にされた、パルス幅変調制御信号SW3とSW4のペアを生成する。選択されたパルス幅変調信号から<sub>0</sub>および<sub>180</sub>から、スイッチング・パターン・マッピング回路は、さらに、第2の出力ドライバ(図12の項目426)の半導体スイッチSW8、SW7に対するパルス幅変調制御信号SW8とSW7を生成する。スイッチング・パターン・マッピング回路は、さらに、第2の出力ドライバの半導体スイッチSW8とSW7に対するパルス幅変調制御信号として、SW8およびSW7に、それぞれ、逆位相であるパルス幅変調制御信号SW5とSW6のペアを生成する。したがって、3レベル動作モードにおいて、スイッチング・パターン・マッピング回路は、第2の出力ドライバに対するパルス幅変調制御信号のSW5、SW6、SW7およびSW8第2セットの対応するパルス幅変調制御信号に対して逆位相であるか、逆にされた、第1の出力ドライバに対して、パルス幅変調制御信号SW1、SW2、SW3およびSW4の形式の変調制御信号の第1のセットを生成するように構成される。このように、第1の出力ドライバに対するパルス幅変調制御信号SW1

40

50

は、第1の出力ドライバに対するSW2は、第2の出力ドライバに対する対応するパルス幅変調制御信号SW6に対して逆位相にされる。等である。

#### 【0058】

図15bで表される5レベル動作モードにおいて、スイッチング・パターン・マッピング回路は、図示されたように、第1の出力ドライバに対するパルス幅変調制御信号SW1、SW2、SW3およびSW4の形式の変調制御信号の第1セットを生成する前に、パルス幅変調信号<sub>0</sub>、<sub>90</sub>、<sub>180</sub>および<sub>270</sub>すべてを選択して、再編成することにより位相選択を実行する。図15aと比べると、第1の出力ドライバのパルス幅変調制御信号SW1、SW2、SW3およびSW4のそれぞれの波形は、3レベルと5レベル動作モードとで同一であることは明白である。しかしながら、第2の出力ドライバのパルス幅変調制御信号SW5、SW6、SW7およびSW8の形式の制御信号の第2セットの波形は、図示されるように、3レベルと5レベル・動作モードとの間で異なる。スイッチング・パターン・マッピング回路は、逆にされ、追加的に、マイナス90度、第1の出力ドライバに対するパルス幅変調制御信号SW1、SW2、SW3およびSW4／の前記第1セットの対応するパルス幅変調制御信号に対して位相シフトされた第2の出力ドライバに対するパルス幅変調制御信号SW5、SW6、SW7およびSW8の第2セットにおけるパルス幅変調制御信号生成するように構成される。このように、第2の出力ドライバに対するパルス幅変調制御信号SW5は、第1の出力ドライバに対する対応するパルス幅変調制御信号SW1に対して、逆にされ、追加的にマイナス90度位相シフトされる。第2の出力ドライバに対するSW6は、第1の出力ドライバに対する対応するパルス幅変調制御信号SW2に対して、逆にされ、追加的にマイナス90度位相シフトされる、等である。

10

#### 【0059】

当業者であれば、Nレベル負荷信号は、 $360 / (N - 1)$ 度の位相差を持つ( $N - 1$ )の異なる制御信号位相の変調制御信号のセットから生成することができることを理解するであろう。3レベル負荷信号が、 $N = 3 \Rightarrow N - 1 = 2$ の異なる制御信号位相を、 $= > 360 / (3 - 1) = 180$ 度位相シフトにセットすることにより提供される。同様に、5レベル負荷信号は、 $N = 5 \Rightarrow N - 1 = 4$ の異なる制御信号位相を、 $= > 360 / (5 - 1) = 90$ 度位相シフトにセットすることにより提供されるさらにまた、7レベル負荷信号は、 $N = 7 \Rightarrow N - 1 = 6$ の異なる制御信号位相を、 $= > 360 / (7 - 1) = 60$ 度位相シフトにセットすることにより提供される。Nは、正整数であり、好適には、奇数である。

20

#### 【0060】

図16A、図16Bは、それぞれ、負荷キャパシタ・リップル電圧と、負荷インダクタ・リップル電流のグラフであり、それぞれ、パルス幅変調スイッチ制御信号の変調デューティ・サイクルに対してプロットされる。0.5の変調デューティ・サイクルは、「アイドル動作」をマークすることによって、グラフ1001の上で示されるように、オーディオ入力信号のゼロ・レベルに、順次対応するパルス幅変調オーディオ信号のゼロ変調に対応する。表されたグラフは、 $10 \mu H$ の負荷インダクタ値(図12項目438参照)と、 $1 \mu F$ の負荷キャパシタ値(図12項目422参照)とに対して、プロットされた。第1または上位のDC供給電圧 $V_S$ または、H-ブリッジ出力ドライバ401のPVDDは、40ボルトにセットされた。変調周波数は、前に説明されたルールにしたがって、3レベルFCケースに対する効果的なスイッチング周波数が $800 \text{ kHz}$ であるように、両方のタイプの変調に対して $400 \text{ kHz}$ にセットされた。

30

#### 【0061】

図16Aのグラフ1001は、クラスDオーディオ・アンプの2つの異なるタイプに対して負荷キャパシタ(図12の項目422)でボルト・ピーク・ピークで測定された負荷キャパシタ・リップル電圧を示す。曲線1003は、図1、図2、図3に示した、2レベル・クラスADまたはBD変調を利用する先行技術の出力ドライバに対するキャパシタ・リップル電圧を示す。曲線1005は、図12のH-ブリッジ出力ドライバ401の3レベル動作モードに対するキャパシタ・リップル電圧を示す。特にゼロ変調のまわりでの、ピ

40

ーク・ピーク・キャパシタ・リップル電圧の大規模な縮小が、明白である。キャパシタ・リップル電圧のこの減少は、複数レベルH-ブリッジ出力ドライバ401に基づいた、または、図9と図10に関連して記述されるもののようによりトラディショナルなH-ブリッジ出力ドライバ・トポロジーは、同様に使用可能であるのではあるが、クラスDアンプからのEMI放出の非常に有利な抑制または減弱となる。

#### 【0062】

図16Bのグラフ1011は、クラスDオーディオ・アンプの2つの異なるタイプに対して、アンペア・ピーク・ピークで測定した負荷インダクタ（図12の項目438）における負荷インダクタ・リップル電流を示す。曲線1013は、 $10\mu H$ の負荷インダクタ値と、 $1\mu F$ の負荷キャパシタ値とで測定した、図9、図10に示される、伝統的な2レベル・クラスADまたはBD変調出力ドライバの負荷インダクタ・リップル電流を示す。曲線1015は、図12のH-ブリッジ出力ドライバ401の3レベル動作モードに対する負荷インダクタ・リップル電流を示す。しかしながら、後者のケースにおいて、負荷インダクタ値は、（伝統的な2レベル・クラスADまたはBD変調出力ドライバに対する $10\mu H$ と比較して）わずか $2.2\mu H$ であり、負荷キャパシタ値は、 $0.47\mu F$ である。インダクタ・リップル電流の振幅の非常に大規模な縮小が、ゼロ変調のまわりで達成された。すなわち、本願のH-ブリッジの出力ドライバに対する負荷インダクタンスと負荷キャパシタンスのかなり小さい値にもかかわらず日常的に聞いている状況を支配する傾向がある小さなオーディオ入力信号に対して、達成された。

#### 【0063】

図17は、図2に関連して上で開示されたモード・スイッチング・スキームに依存する変調デューティ・サイクルを適用して、図12に描かれた複数レベルH-ブリッジ出力ドライバ401への比較において、前に言及されたモード・スイッチング・スキームのないAD変調を用いて、図9に描かれた伝統的なH-ブリッジ出力ドライバ100に対して実験的に記録されたパワー消散データを図示する。オーディオ入力信号は、 $1\text{kHz}$ の正弦波であり、ラウドスピーカ負荷は、両方の図のケースにおいて、8である。先行技術のH-ブリッジ・ドライバは、 $9.4\mu H$ の負荷インダクタ値、および、 $400\text{kHz}$ の変調周波数を使用する。本願発明にしたがうH-ブリッジの出力ドライバは、 $2.2\mu H$ の負荷インダクタ値、・・・を使用する。および、 $600\text{kHz}$ の変調周波数第2の出力ドライバに対する対応するパルス幅変調制御信号SW5に対して逆位相にされる。曲線1301は、伝統的なH-ブリッジ出力ドライバ100の供給負荷パワーまたは出力パワーに対してワットで測定したパワー損失を表す。一方、曲線1303は、複数レベルH-ブリッジ出力ドライバ401のメリットの同じ図を表す。図示されるように、パワー損失のかなりの縮小が、複数レベルH-ブリッジの出力ドライバ401によって、H-ブリッジ出力ドライバの大部分のリニア動作範囲を通して提供される。例えば、出力パワー・レベル $1\text{W}$ 未満のような伝達出力パワーの小さい値に対してパワー損失の著しい縮小は、特に目立つものである。パワー・レベルのこの範囲が、典型的には、日常的なリスニング状況で使用されるからである。測定されたパワー消散の節約は、出力または負荷パワーの小さい値に対して、およそ、9のファクタとなる。この著しく改善されたエネルギー効率は、本願H-ブリッジ・ドライバ-のより大きな負荷インダクタまたは負荷キャパシタの値を使用することなく得られることも、注目に値する。反対に、図16に表される実験的に記録されたパワー損失データに対する条件の下で、負荷インダクタは、かなりより小さいものである。

10

20

30

40

【図1】

【図2】

FIG. 2

【図3】

【図4】

FIG. 4

【図5】

FIG. 5

【図6】

FIG. 6

【図7】

FIG. 7

【図8】

FIG. 8

【図9】

FIG. 9

【図10】

FIG. 10

【図11】

FIG. 11

【図12】

FIG. 12

【図13】

FIG. 13

【図14】

FIG. 14

【図15】

A) 3レベル出力

B) 5レベル出力

【図16】

FIG. 16

【図 17】

FIG. 17

---

フロントページの続き

(72)発明者 ミケル ホイエルビュ

デンマーク国, デーコー - 2450 コペンハーゲン エスペー, ハンメルストルプバイ 26,

1. テベ

審査官 白井 亮

(56)参考文献 特開2008-066995(JP, A)

米国特許出願公開第2005/017799(US, A1)

特開2010-193455(JP, A)

特開2009-177951(JP, A)

特開2005-051303(JP, A)

特開平06-303049(JP, A)

米国特許出願公開第2008/297244(US, A1)

(58)調査した分野(Int.Cl., DB名)

H03F 3/217