(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-38368

(P2009-38368A)

(43) 公開日 平成21年2月19日(2009.2.19)

(51) Int.Cl.

**H01L 27/00** (2006.01)

**H01L 27/08** (2006.01)

**H01L 21/8238** (2006.01)

**H01L 27/092** (2006.01)

**H01L 29/786** (2006.01)

F 1

H01L 27/00

H01L 27/08

H01L 27/08

H01L 27/08

H01L 29/786

301D

301B

331E

321G

613A

テーマコード(参考)

5F048

5F110

審査請求 未請求 請求項の数 10 O L (全 33 頁) 最終頁に続く

(21) 出願番号

特願2008-179747 (P2008-179747)

(22) 出願日

平成20年7月10日 (2008.7.10)

(31) 優先権主張番号

特願2007-181762 (P2007-181762)

(32) 優先日

平成19年7月11日 (2007.7.11)

(33) 優先権主張国

日本国 (JP)

(71) 出願人

000153878 株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者

磯部 敦生 神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

F ターム(参考) 5F048 AA09 AB04 AB10 AC03 BA01

BB01 BB06 BB09 BF19 BG07

CB03 CB04 CB10

最終頁に続く

(54) 【発明の名称】 半導体装置、電子機器、半導体装置の作製方法

## (57) 【要約】

【課題】半導体装置の高集積化及び微細化に関する問題点を解決することを課題とする。また、上記の問題点を、低コストにて解決することを課題とする。

【解決手段】絶縁表面を有する基板上に第1の単結晶半導体層を形成し、第1の単結晶半導体層上に第2の絶縁層を形成し、第2の絶縁層上の第1の単結晶半導体層の一部と重なる領域に導電層を形成し、第2の絶縁層及び導電層を覆うように第3の絶縁層を形成し、第3の絶縁層の上面を平坦化し、第3の絶縁層上に第4の絶縁層を形成し、第2の損傷領域を有する第2の単結晶半導体基板の表面と、第4の絶縁層とを貼り合わせ、第2の単結晶半導体基板を、第2の損傷領域において分離して、絶縁表面を有する基板上に第2の単結晶半導体層を形成する。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

絶縁表面上の第1の単結晶半導体層と、

前記第1の単結晶半導体層上の第1の絶縁層と、

前記第1の絶縁層上の導電層と、

前記導電層上の第2の絶縁層と、

前記第2の絶縁層上の第2の単結晶半導体層を有することを特徴とする半導体装置。

**【請求項 2】**

絶縁表面上の第1の単結晶半導体層と、

前記第1の単結晶半導体層上の第1の絶縁層と、

前記第1の絶縁層上の導電層と、

前記導電層上の第2の絶縁層と、

前記第2の絶縁層上の第2の単結晶半導体層と、を有し、

前記導電層は、前記第1の絶縁層及び前記第2の絶縁層を介して、前記第1の単結晶半導体層及び前記第2の単結晶半導体層に電界を加えるためのものであることを特徴とする半導体装置。

**【請求項 3】**

請求項1又は2において、

前記第1の単結晶半導体層、前記第1の絶縁層、及び前記導電層により、トップゲート型の第1のトランジスタが形成され、

前記導電層、前記第2の絶縁層、及び前記第2の単結晶半導体層により、ボトムゲート型の第2のトランジスタが形成されたことを特徴とする半導体装置。

**【請求項 4】**

請求項3において、

前記第1のトランジスタのソース領域又はドレイン領域と、前記第2のトランジスタのソース領域又はドレイン領域には、それぞれ異なる導電性を付与する不純物元素が添加されていることを特徴とする半導体装置。

**【請求項 5】**

請求項4において、

前記半導体装置は相補型半導体装置であることを特徴とする半導体装置。

**【請求項 6】**

請求項1乃至5のいずれか一に記載の半導体装置を用いた電子機器。

**【請求項 7】**

第1の損傷領域を有する第1の単結晶半導体基板の表面と、絶縁表面を有する基板の表面に形成された第1の絶縁層とを貼り合わせ、

前記第1の単結晶半導体基板を、前記第1の損傷領域において分離して、前記絶縁表面を有する基板上に第1の単結晶半導体層を形成し、

前記第1の単結晶半導体層上に第2の絶縁層を形成し、

前記第2の絶縁層上の前記第1の単結晶半導体層の一部と重なる領域に導電層を形成し、

前記第2の絶縁層及び前記導電層を覆うように第3の絶縁層を形成し、

前記第3の絶縁層の上面を平坦化し、

前記第3の絶縁層上に第4の絶縁層を形成し、

第2の損傷領域を有する第2の単結晶半導体基板の表面と、前記第4の絶縁層とを貼り合わせ、

前記第2の単結晶半導体基板を、前記第2の損傷領域において分離して、前記絶縁表面を有する基板上に第2の単結晶半導体層を形成することを特徴とする半導体装置の作製方法。

**【請求項 8】**

第1の損傷領域を有する第1の単結晶半導体基板の表面に形成された第1の絶縁層と、

10

20

30

40

50

絶縁表面を有する基板の表面とを貼り合わせ、

前記第1の単結晶半導体基板を、前記第1の損傷領域において分離して、前記絶縁表面を有する基板上に第1の単結晶半導体層を形成し、

前記第1の単結晶半導体層上に第2の絶縁層を形成し、

前記第2の絶縁層上の前記第1の単結晶半導体層の一部と重なる領域に導電層を形成し、

前記第2の絶縁層及び前記導電層を覆うように第3の絶縁層を形成し、

前記第3の絶縁層の上面を平坦化し、

前記第3の絶縁層上に第4の絶縁層を形成し、

第2の損傷領域を有する第2の単結晶半導体基板の表面と、前記第4の絶縁層とを貼り合わせ、

前記第2の単結晶半導体基板を、前記第2の損傷領域において分離して、前記絶縁表面を有する基板上に第2の単結晶半導体層を形成することを特徴とする半導体装置の作製方法。

#### 【請求項9】

請求項7又は8において、

前記第1の単結晶半導体層、前記第2の絶縁層、及び前記導電層により、トップゲート型の第1のトランジスタを形成し、

前記導電層、前記第4の絶縁層、及び前記第2の単結晶半導体層により、ボトムゲート型の第2のトランジスタを形成することを特徴とする半導体装置の作製方法。

#### 【請求項10】

請求項9において、

前記第1のトランジスタのソース領域又はドレイン領域と、前記第2のトランジスタのソース領域又はドレイン領域には、それぞれ異なる導電性を付与する不純物元素を添加することを特徴とする半導体装置の作製方法。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、半導体装置、及びその作製方法、電子機器に関する。

#### 【背景技術】

#### 【0002】

現在、半導体集積回路の性能向上は、主にプロセスルールの微細化により進められている（ここで、プロセスルールとは、半導体装置内部の最小線幅をいう）。近年では65nmや45nmといったプロセスルールが採用されはじめており、半導体素子の微細化には一層の拍車がかかっている（例えば、特許文献1、特許文献2参照）。

#### 【特許文献1】特開2005-107195

#### 【特許文献2】特開2006-147897

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0003】

しかしながら、上述の如くプロセスルールの微細化により高集積化（いわば、2次元的な高集積化）を進めていった場合には、遠からず物理的な限界に達してしまう。例えば、回路パターンを形成するための露光機の解像度の限界を超えて微細化を進めることは困難である。また、仮に原子スケールの線幅（例えば、数nm程度以下）が実現できたとしても、リーク電流の増大や、宇宙線由来の中性子によるエラーの増大などにより、従来と同様の動作を実現することは困難である。

#### 【0004】

また、ガラス基板等の安価な基板を用いた半導体装置の場合には、基板自体に数十μm程度のうねりが存在する。このため、露光の際の焦点深度を十分に確保しなくてはならないが、焦点深度を確保すると解像度が低下してしまう。このため、いわゆるLSIの場合

10

20

30

40

50

と比較して、ガラス基板等の安価な基板を用いた半導体装置の集積度は低くなってしまうことになる。つまり、ガラス基板等の安価な基板を用いた半導体装置においては、LSI以上に集積化が困難であるといえる。

#### 【0005】

上述の如き問題点に鑑み、本発明では、高集積化及び微細化に関する上記の問題点を解決した半導体装置を提供することを課題とする。また、工程数の増加を抑え、上記の問題点を低コストにて解決することを課題とする。

#### 【課題を解決するための手段】

#### 【0006】

本発明では、2次元的な高集積化に代えて、3次元的な高集積化を実現する。これにより、プロセスルールの微細化によらず、半導体装置の高集積化を実現することができる。具体的には、2層以上に積層された単結晶半導体層を用いて半導体装置を作製する。また、単結晶半導体層に電界を加えるための導電層を共通化する。これにより、低コストに高集積化を実現することができる。ここで、単結晶半導体層を積層する方法としてはイオン注入剥離法を用いる。

#### 【0007】

本発明の半導体装置の一は、絶縁表面上の第1の単結晶半導体層と、第1の単結晶半導体層上の第1の絶縁層と、第1の絶縁層上の導電層と、導電層上の第2の絶縁層と、第2の絶縁層上の第2の単結晶半導体層を有することを特徴としている。

#### 【0008】

また、本発明の半導体装置の他の一は、絶縁表面上の第1の単結晶半導体層と、第1の単結晶半導体層上の第1の絶縁層と、第1の絶縁層上の導電層と、導電層上の第2の絶縁層と、第2の絶縁層上の第2の単結晶半導体層と、を有し、導電層は、第1の絶縁層及び第2の絶縁層を介して、第1の単結晶半導体層及び第2の単結晶半導体層に電界を加えるためのものであることを特徴としている。

#### 【0009】

上記において、第1の単結晶半導体層、第1の絶縁層、及び導電層により、トップゲート型の第1のトランジスタが形成され、導電層、第2の絶縁層、及び第2の単結晶半導体層により、ボトムゲート型の第2のトランジスタが形成されている。

#### 【0010】

また、上記において、第1のトランジスタのソース領域又はドレイン領域と、第2のトランジスタのソース領域又はドレイン領域には、同じ導電性を付与する不純物元素が添加されていても良いし、第1のトランジスタのソース領域又はドレイン領域と、第2のトランジスタのソース領域又はドレイン領域には、それぞれ異なる導電性を付与する不純物元素が添加されていても良い。

#### 【0011】

上記の如く、異なる導電性を付与する不純物元素を添加した場合には、第1のトランジスタ及び第2のトランジスタにより相補型半導体装置を形成することができる。また、上記の半導体装置を用いて様々な電子機器を提供することができる。

#### 【0012】

本発明の半導体装置の作製方法の一は、第1の損傷領域を有する第1の単結晶半導体基板の表面と、絶縁表面を有する基板の表面に形成された第1の絶縁層とを貼り合わせ、第1の単結晶半導体基板を、第1の損傷領域において分離して、絶縁表面を有する基板上に第1の単結晶半導体層を形成し、第1の単結晶半導体層上に第2の絶縁層を形成し、第2の絶縁層上の第1の単結晶半導体層の一部と重なる領域に導電層を形成し、第2の絶縁層及び導電層を覆うように第3の絶縁層を形成し、第3の絶縁層の上面を平坦化し、第3の絶縁層上に第4の絶縁層を形成し、第2の損傷領域を有する第2の単結晶半導体基板の表面と、第4の絶縁層とを貼り合わせ、第2の単結晶半導体基板を、第2の損傷領域において分離して、絶縁表面を有する基板上に第2の単結晶半導体層を形成することを特徴としている。

10

20

30

40

50

**【0013】**

また、本発明の半導体装置の作製方法の他の一は、第1の損傷領域を有する第1の単結晶半導体基板の表面に形成された第1の絶縁層と、絶縁表面を有する基板の表面とを貼り合わせ、第1の単結晶半導体基板を、第1の損傷領域において分離して、絶縁表面を有する基板上に第1の単結晶半導体層を形成し、第1の単結晶半導体層上に第2の絶縁層を形成し、第2の絶縁層上の第1の単結晶半導体層の一部と重なる領域に導電層を形成し、第2の絶縁層及び導電層を覆うように第3の絶縁層を形成し、第3の絶縁層の上面を平坦化し、第3の絶縁層上に第4の絶縁層を形成し、第2の損傷領域を有する第2の単結晶半導体基板の表面と、第4の絶縁層とを貼り合わせ、第2の単結晶半導体基板を、第2の損傷領域において分離して、絶縁表面を有する基板上に第2の単結晶半導体層を形成することを特徴としている。10

**【0014】**

上記において、第1の単結晶半導体層、第2の絶縁層、及び導電層により、トップゲート型の第1のトランジスタを形成し、導電層、第4の絶縁層、及び第2の単結晶半導体層により、ボトムゲート型の第2のトランジスタを形成することができる。

**【0015】**

また、上記において、第1のトランジスタのソース領域又はドレイン領域と、第2のトランジスタのソース領域又はドレイン領域には、同じ導電性を付与する不純物元素を添加しても良いし、第1のトランジスタのソース領域又はドレイン領域と、第2のトランジスタのソース領域又はドレイン領域には、それぞれ異なる導電性を付与する不純物元素を添加しても良い。20

**【0016】**

なお、本発明において、半導体装置とは、液晶表示装置やエレクトロルミネッセンス表示装置をはじめとする表示装置、RFID(Radio Frequency Identification)タグ、RFタグ、RFチップ、無線プロセッサ、無線メモリ、IC(Integrated Circuit)タグ、ICラベル、電子タグ、電子チップ等と呼ばれる無線タグ、中央処理装置(Central Processing Unit(CPU))をはじめとするマイクロプロセッサ、集積回路、その他、絶縁表面上に形成された単結晶半導体層を用いる装置全般を言うものとする。

**【発明の効果】****【0017】**

本発明により、工程数の増加を抑えつつ高度に集積化した半導体装置を提供することができる。つまり、より小型の半導体装置を提供することができる。また、高性能な半導体装置を提供することができる。すなわち、高性能な半導体装置を低コストにて提供することができる。

**【発明を実施するための最良の形態】****【0018】**

本発明の実施の形態について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々なに変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いることとする。40

**【0019】****(実施の形態1)**

本実施の形態では、本発明の半導体装置の製造方法の一例について、図1乃至7を参照して説明する。

**【0020】**

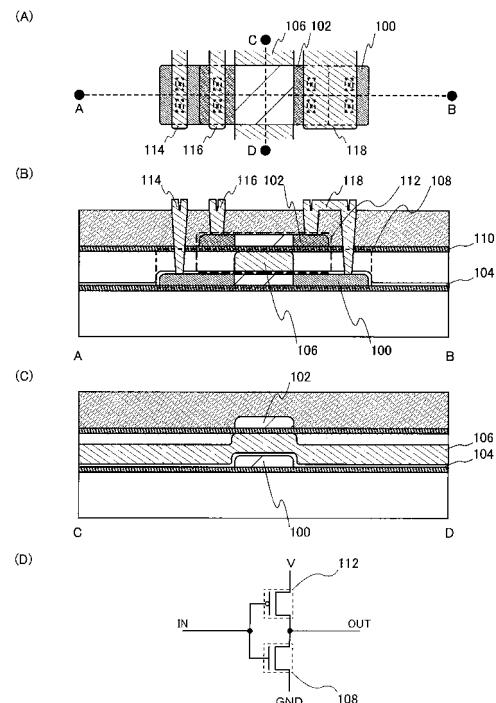

図1に、本発明の半導体装置の構成の一例を示す。図1(A)は本発明の半導体装置の平面図であり、図1(B)は図1(A)のA-Bにおける断面図であり、図1(C)は図1(A)のC-Dにおける断面図である。なお、図1の構成はあくまでも一例であり、本50

発明は該構成に限定されるものではない。

**【0021】**

図1に示す半導体装置は、2層の単結晶半導体層(単結晶半導体層100及び単結晶半導体層102)を有している。単結晶半導体層100は、絶縁層104、及び導電層106と共に第1のトランジスタ108を構成している。単結晶半導体層102は、導電層106及び絶縁層110と共に第2のトランジスタ112を構成している。ここで、第1のトランジスタ108はn型トランジスタであり、第2のトランジスタ112はp型トランジスタである。また、第1のトランジスタ108のソース領域又はドレイン領域の一部には、ソース電極又はドレイン電極114(以下、ソース配線又はドレイン配線とも言う)が電気的に接続されており、第2のトランジスタ112のソース領域又はドレイン領域の一部には、ソース電極又はドレイン電極116が電気的に接続されており、第1のトランジスタ及び第2のトランジスタのソース領域又はドレイン領域を電気的に接続するように、ソース電極又はドレイン電極118が設けられている。10

**【0022】**

図1(D)は、上記半導体装置の回路図である。図1(D)からも分かるように、第1のトランジスタ108及び第2のトランジスタ112により、相補型回路(より詳細には、CMOSインバータ回路)が形成されている。導電層106は第1のトランジスタ108及び第2のトランジスタ112のゲート電極として機能し、CMOS回路の入力端子に当たる。また、ソース電極又はドレイン電極118は、CMOS回路の出力端子に当たる。20

**【0023】**

図1に示すように、単結晶半導体層を積層して半導体素子(例えば、トランジスタ)を形成することにより、高度に集積化した半導体装置を作製することができる。また、本発明では、全ての半導体素子を、単結晶半導体を用いて形成するから、アモルファス半導体や多結晶半導体を用いる場合と比較して、優れた特性の半導体装置を提供することができる。さらに、本発明においては、単結晶半導体層に電界を加えるための導電層(ゲート電極)を共通化することにより、トランジスタごとの導電層が不要となる。つまり、複数の導電層を積層して形成する必要がないため、低コストに半導体装置を作製することができる。図1の如き相補型回路(CMOS回路、相補型半導体装置とも言う)を形成する場合には、そのメリットは顕著である。30

**【0024】**

次に、本発明の半導体装置の製造方法の一例について図2乃至7を参照して以下に説明する。

**【0025】**

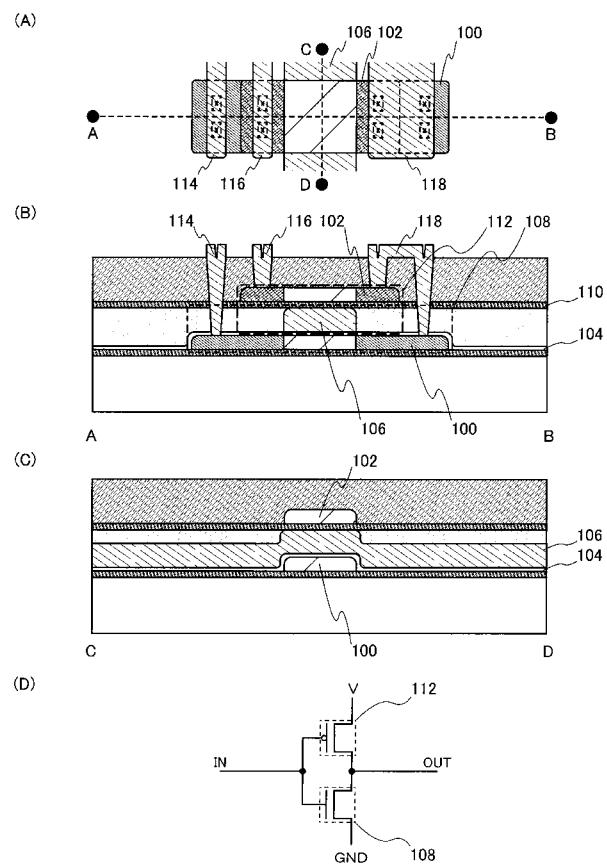

はじめに、単結晶半導体基板200を用意する。そして、単結晶半導体基板200の表面にイオンを照射し、単結晶半導体基板200中に損傷領域202及び単結晶半導体層204を形成する(図2(A)参照)。損傷領域202の形成方法としては、半導体層への不純物元素の添加に用いられる方法(イオンドーピング法)や、イオン化したガスを質量分離して選択的に半導体層に注入する方法(イオン注入法)等が挙げられる。イオンの照射は、形成される単結晶半導体層204の厚さを考慮して行えば良い。該単結晶半導体層204の厚さは5nm乃至500nm程度とすればよく、10nm乃至200nmの厚さとするとより好ましい。イオンを照射する際の加速電圧は上記の厚さを考慮して決定することができる。40

**【0026】**

単結晶半導体基板200は、単結晶半導体からなる基板であれば特に限られないが、本実施の形態においては一例として、単結晶シリコン基板を用いることとする。その他、ゲルマニウム基板や、ガリウムヒ素、インジウムリンなどの化合物半導体による基板を適用することもできる。

**【0027】**

照射するイオンとしては、フッ素に代表されるハロゲンや、水素、ヘリウム等のイオン

が挙げられる。ハロゲンのイオンとしてフッ素イオンを照射する場合には、原料ガスとしてBF<sub>3</sub>を用いれば良い。たとえば、単結晶半導体基板200として単結晶シリコン基板を用いて、該単結晶シリコン基板にフッ素イオンのようなハロゲンイオンを照射した場合には、損傷領域202には微小な空洞が形成される。これは、打ち込まれたハロゲンイオンがシリコン結晶格子内のシリコン原子を追い出すためと考えられる。このようにして形成された微小な空洞の体積を変化させることにより、単結晶シリコン基板を分離することができる。具体的には、低温の熱処理によって微小な空洞の体積変化を誘起する。なお、フッ素イオンを照射した後に、水素イオンを照射して空洞内に水素を含ませるようにしても良い。

## 【0028】

10

また、同一の原子から成り、質量の異なる複数のイオンを照射してもよい。例えば、水素を用いる場合には、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>イオンを含ませると共に、H<sub>3</sub><sup>+</sup>イオンの割合を高めておくと良い。H<sub>3</sub><sup>+</sup>イオンの割合を高めることで照射効率を高めることができるために、照射時間を短縮することができる。

## 【0029】

なお、損傷領域202の形成前に、単結晶半導体基板200の表面に保護層を形成する構成としても良い。保護層を形成することにより、イオンの照射に伴う単結晶半導体基板の表面の荒れを低減することができる。保護層としては、酸化シリコン、窒化シリコン、窒化酸化シリコン、酸化窒化シリコン等を用いることができる。

## 【0030】

20

なお、酸化窒化シリコンとは、その組成において、窒素よりも酸素の含有量が多いものを示し、例えば、酸素が50原子%以上70原子%以下、窒素が0.5原子%以上15原子%以下、珪素が25原子%以上35原子%以下、水素が0.1原子%以上10原子%以下の範囲で含まれるものという。また、窒化酸化シリコンとは、その組成において、酸素よりも窒素の含有量が多いものを示し、例えば、酸素が5原子%以上30原子%以下、窒素が20原子%以上55原子%以下、珪素が25原子%以上35原子%以下、水素が10原子%以上25原子%以下の範囲で含まれるものという。但し、上記範囲は、ラザフォード後方散乱法(RBS: Rutherford Backscattering Spectrometry)や、水素前方散乱法(HFS: Hydrogen Forward Scattering)を用いて測定した場合のものである。また、構成元素の含有比率は、その合計が100原子%を超えない値をとる。

30

## 【0031】

次に、絶縁表面を有する基板206上に、接合層208を形成する(図2(B)参照)。接合層208は、酸化シリコン膜を、有機シランガスを用いた化学気相成長法(CVD法)により形成すると良い。その他に、シランガスを用いて化学気相成長法により作製される酸化シリコン膜を適用することもできる。なお、接合層208は絶縁性材料より形成されるため、絶縁層と呼ぶことができる。

## 【0032】

40

なお、絶縁表面を有する基板206としては、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスのような電子工業用に使われる各種ガラス基板、石英基板、セラミック基板、サファイア基板等を用いることができる。好ましくはガラス基板を用いるのがよく、例えば第6世代(1500mm×1850mm)、第7世代(1870mm×2200mm)、第8世代(2200mm×2400mm)と呼ばれる大面積のマザーガラス基板を用いることもできる。大面積のマザーガラス基板を、絶縁表面を有する基板206として用いることで、半導体基板の大面積化が実現できる。なお、絶縁表面を有する基板206は上記の基板に限定されるものではない。例えば、耐熱温度が許せば樹脂材料からなる基板を用いることも可能である。もちろん、シリコンウエハのような単結晶半導体基板を用いても良い。この場合、単結晶半導体基板上に絶縁層を形成したものを用いれば良い。また、あらかじめ素子を形成した単結晶半導体基板上に絶縁層を形成したものを用いても良い。これにより、一層の集積化を図ることができる。

50

## 【0033】

接合層208は平滑に形成され、親水性表面を有する。この接合層208としては酸化シリコン膜が適している。特に有機シランガスを用いて化学気相成長法により作製される酸化シリコン膜が好ましい。有機シランガスとしては、珪酸エチル(TEOS:Si(O<sub>2</sub>H<sub>5</sub>)<sub>4</sub>)、トリメチルシラン((CH<sub>3</sub>)<sub>3</sub>SiH)、テトラメチルシラン((CH<sub>3</sub>)<sub>4</sub>Si)、テトラメチルシクロテトラシロキサン(TMCTS)、オクタメチルシクロテトラシロキサン(OMCTS)、ヘキサメチルジシラザン(HMDS)、トリエトキシシラン(SiH(OCH<sub>2</sub>H<sub>5</sub>)<sub>3</sub>)、トリスジメチルアミノシラン(SiH(N(CH<sub>3</sub>)<sub>2</sub>)<sub>3</sub>)等のシリコン含有化合物を用いることができる。

## 【0034】

上記接合層208は、5nm乃至500nm程度の厚さで設けられる。これにより、被成膜表面を平滑化すると共に当該膜の成長表面の平滑性を確保することが可能である。また、接合する基板との歪みを緩和することができる。なお、後の単結晶半導体基板200にも同様の接合層を設けておくことができる。このように、接合を形成する面の一方若しくは双方を、有機シランを原材料として成膜した酸化シリコン膜とすることで、接合を非常に強固なものとすることができる。

## 【0035】

なお、絶縁表面を有する基板206と接合層208との間に、バリア層を設ける構成としてもよい。バリア層は窒化シリコン、窒化酸化シリコン又は酸化窒化シリコンから選ばれた一又は複数の材料を用いて形成すると良い。なお、バリア層は単層構造でも良いし積層構造でも良い。バリア層は、絶縁表面を有する基板206中の可動イオンや水分等の不純物が、接合層208、又は、接合層208より上に形成される層に侵入することを防ぐために設けられる。なお、不純物の侵入を防ぐことができるのであれば、上記材料以外を用いたバリア層を形成しても良い。また、不純物の侵入が大きな問題とならない場合には、バリア層を設けない構成としても良い。

## 【0036】

本実施の形態においては、単結晶半導体基板200に損傷領域202を形成した後に、絶縁表面を有する基板206上に接合層208を形成する場合について説明したが、本発明はこれに限られない。本発明では、絶縁表面を有する基板206に単結晶半導体層204を形成することができればよいから、損傷領域202と接合層208の形成の順序は特に問われない。例えば、絶縁表面を有する基板206上に接合層208を形成した後に単結晶半導体基板200に損傷領域202を形成しても良い。接合層208の形成と損傷領域202の形成の順序は特に問われず、各々を独立したタイミングにて形成することができる。

## 【0037】

次に、接合層208と、単結晶半導体層204とを密接させる(図2(C)参照)。接合層208と単結晶半導体層204とを密接させて圧力をかけることで、水素結合や共有結合による強固な接合を形成することが可能である。なお、接合層208を介して絶縁表面を有する基板206と単結晶半導体基板200とを貼り合わせた後には、加熱処理を行うことが好ましい。加熱処理を行うことで接合強度をより向上させることができる。なお、接合層208と単結晶半導体層204との間に下地層を形成する構成としても良い。下地層を形成することにより、単結晶半導体層204への可動イオン等の侵入を防ぐことができる。下地層は、上記バリア層と同様の材料を用いて作製することができるがこれに限られるものではない。例えば、単結晶半導体層204側から酸化窒化シリコン膜、窒化酸化シリコン膜を積層して下地層とすることができます。

## 【0038】

良好な接合を形成するために、接合が形成される表面を活性化しておいても良い。例えば、接合を形成する面に原子ビーム又はイオンビームを照射する。原子ビーム又はイオンビームを利用する場合には、アルゴン等の不活性ガス原子ビーム又は不活性ガスイオンビームを用いることができる。その他に、プラズマ処理又はラジカル処理を行う。このよう

な表面処理により、200乃至400程度の低温で異種材料間の接合を形成することができる。

#### 【0039】

次に、加熱処理を行い、損傷領域202の一部を分離面として単結晶半導体層204を単結晶半導体基板200から分離する(図2(D)参照)。例えば、400乃至600の熱処理を行うことにより、損傷領域202に形成された微小な空洞の体積変化を誘起して分離させることができる。接合層208は絶縁表面を有する基板206と接合しているので、絶縁表面を有する基板206上には単結晶半導体層204が残存することとなる。なお、図2においては、損傷領域202と単結晶半導体層204との界面にて分離した様子を図示したが、本発明はこれに限られない。例えば、損傷領域202と単結晶半導体基板200との界面にて分離しても良いし、損傷領域202の一部にて分離しても良い。分離が生じる領域は、損傷領域202を形成する際の条件により異なるものと考えられる。

10

#### 【0040】

なお、絶縁表面を有する基板206としてガラス基板を用いる場合には、ガラス基板の歪み点近傍、具体的には歪み点±50で加熱を行えば良い。より具体的には、580以上680以下で行えばよい(ガラス基板の歪み点温度が630程度の場合)。なお、ガラス基板は加熱によって収縮するという性質を有する。このため、あらかじめガラス基板を歪み点近傍、具体的には歪み点±50程度(若しくはそれ以上)で加熱しておくと、その後の加熱処理における収縮を抑制することができる。これにより、熱膨張率の異なる単結晶半導体層を接合したガラス基板に加熱処理を行う場合であっても、ガラス基板からの単結晶半導体層の剥離を防ぐことができる。また、ガラス基板及び単結晶半導体層の反りなどの変形を防止することもできる。

20

#### 【0041】

なお、ガラス基板を用いる場合には、加熱終了時の急速な冷却を避けることが好ましい。具体的には2/分以下、好ましくは0.5/分以下、より好ましくは0.3/分以下の速度で、歪み点以下の温度まで冷却するとよい。降温速度を小さくすることにより、ガラス基板が縮む際に生じる局所的な応力を緩和することができる。該加熱処理は大気圧下で行っても良いし、減圧下で行っても良い。雰囲気も窒素雰囲気、酸素雰囲気など、適宜設定することができる。なお、該加熱処理は、加熱後に収縮する性質を有する基板を用いる場合であればガラス基板に限らず適用することができる。

30

#### 【0042】

なお、接合の工程に係る加熱処理と、分離の工程に係る加熱処理とを同時にを行うことができる。この場合、1度の加熱処理で二つの工程を行うことができるため、低コストに半導体基板を作製することができる。

#### 【0043】

上記の工程によって得られた単結晶半導体層204については、化学的機械的研磨(Chemical Mechanical Polishing: CMP)、レーザー光の照射、ドライエッティング等により表面を平坦化することが好ましい。単結晶半導体層204の平坦性を向上することにより、後に形成する半導体素子のばらつきを抑えることができる。なお、所望の特性が得られるようであれば、CMPやレーザー光照射、ドライエッティング等は省略してもかまわない。レーザー光の照射を行う場合には、イオン照射に起因する欠陥を低減することもできる。

40

#### 【0044】

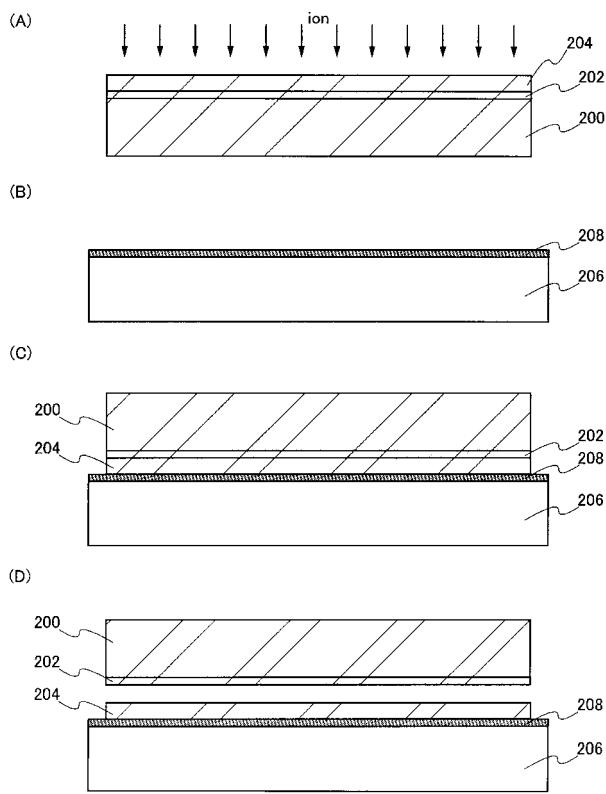

次に、単結晶半導体層204を所望の形状にパターニングして、島状の単結晶半導体層210を形成する(図3(A)参照)。パターニングの際のエッティング加工としては、プラズマエッティング(ドライエッティング)、ウエットエッティングのどちらを採用しても良いが、大面積基板を処理するにはプラズマエッティングが適している。エッティングガスとしては、 $\text{CF}_4$ 、 $\text{NF}_3$ 、 $\text{Cl}_2$ 、 $\text{BCl}_3$ 、などのフッ素系又は塩素系のガスを用い、 $\text{He}$ や $\text{Ar}$ などの不活性ガスを適宜加えて良い。また、大気圧放電のエッティング加工を適用

50

すれば、局所的な放電加工も可能であり、基板の全面にマスク層を形成する必要はない。

#### 【0045】

単結晶半導体層204をパターニングして、島状の単結晶半導体層210を形成した後には、しきい値電圧を制御するために、硼素、アルミニウム、ガリウムなどのp型不純物を添加すると良い。例えば、p型不純物として、硼素を $1 \times 10^{16} \text{ cm}^{-3}$ 以上 $1 \times 10^{18} \text{ cm}^{-3}$ 以下の濃度で添加することができる。なお、適切な不純物濃度の単結晶半導体基板を用いることにより、しきい値電圧制御のためのドーピング工程は省略することができる。

#### 【0046】

次に、島状の単結晶半導体層210を覆う絶縁層212を形成する（図3（B）参照）。絶縁層212はゲート絶縁層として機能する。絶縁層212はスパッタリング法、CVD法などを用い、厚さを2nm以上150nm以下程度として珪素を含む絶縁膜で形成する。具体的には、窒化珪素、酸化珪素、酸化窒化珪素、窒化酸化珪素に代表される珪素の酸化物材料又は窒化物材料等の材料で形成すればよい。なお、絶縁層212は単層構造であっても良いし、積層構造としても良い。さらに、島状の単結晶半導体層210と絶縁層212との間に、膜厚1nm以上100nm以下、好ましくは1nm以上10nm以下、より好ましくは2nm以上5nm以下の薄い酸化珪素膜を形成してもよい。なお、低い温度でリーク電流の少ないゲート絶縁層を形成するために、アルゴンなどの希ガス元素を反応ガスに含ませても良い。

#### 【0047】

次に、絶縁層212上に導電層を形成し、該導電層をパターニングすることで導電層214を形成する（図3（C）参照）。導電層214はゲート電極として機能する。ここでは、単層構造にて導電層214を形成したが、本発明はこれに限られない。2層以上の積層構造としても良い。導電層214の厚さとしては、20nm以上500nm以下程度が好適である。なお、導電層214は、スパッタリング法、蒸着法、CVD法等の手法により形成することができる。用いることができる材料としては、タンタル（Ta）、タングステン（W）、チタン（Ti）、モリブデン（Mo）、アルミニウム（Al）、銅（Cu）、クロム（Cr）、ネオジム（Nd）から選ばれた元素、又は前記の元素を主成分とする合金材料もしくは化合物材料等が挙げられる。リン等の不純物元素をドーピングした多結晶シリコンに代表される半導体材料や、AgPdCu合金などを用いてもよい。

#### 【0048】

次に、導電層214をマスクとして、n型を付与する不純物元素を添加し、不純物領域216及びチャネル形成領域218を形成する（図3（D）参照）。本実施の形態では、不純物元素を含むドーピングガスとしてホスフィン（PH<sub>3</sub>）を用いてドーピングを行う。ここでは、不純物領域216に、n型を付与する不純物元素であるリン（P）が $1 \times 10^{19} / \text{cm}^3$ 以上 $1 \times 10^{21} / \text{cm}^3$ 以下程度の濃度で含まれるようにする。

#### 【0049】

なお、本実施の形態においては、島状の単結晶半導体層210にn型を付与する不純物元素を添加する構成としたが、本発明はこれに限られない。p型を付与する不純物元素を添加する構成としても良い。p型を付与する不純物元素を添加する場合には、不純物元素（例えば、ボロン（B））の濃度が $1 \times 10^{20} / \text{cm}^3$ 以上 $5 \times 10^{21} / \text{cm}^3$ 以下程度となるようにする。また、不純物領域216とチャネル形成領域218との間にLD領域を形成する構成としても良い。LDD領域における不純物元素の濃度は $1 \times 10^{17} / \text{cm}^3$ 以上 $1 \times 10^{19} / \text{cm}^3$ 以下程度とするのが好適である。

#### 【0050】

以上の工程により、第1のトランジスタを構成する島状の単結晶半導体層210、絶縁層212、導電層214が形成されたことになる。なお、不純物領域216の活性化のために加熱処理等を施しても良い。

#### 【0051】

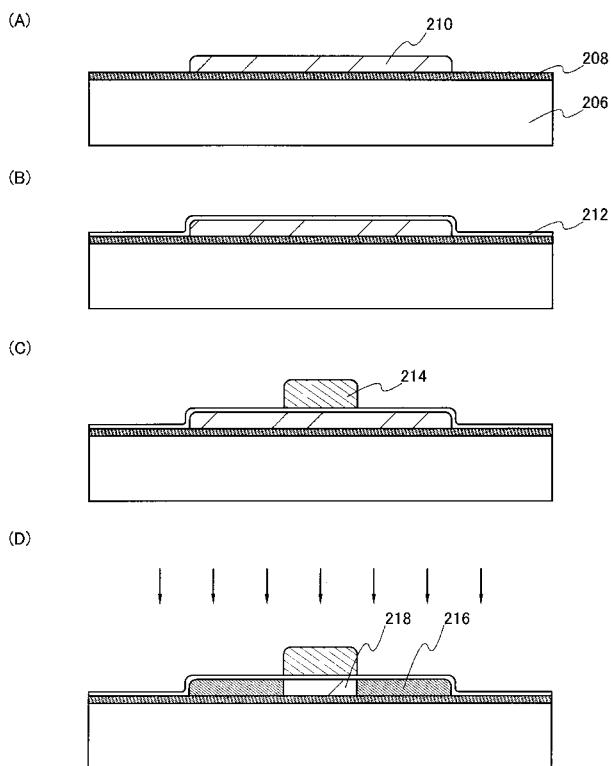

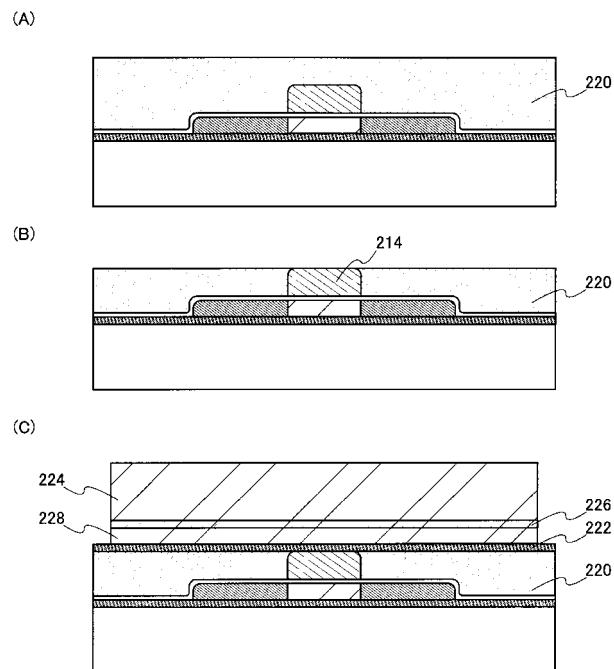

次に、絶縁層212及び導電層214を覆うように絶縁層220を形成する（図4（A）

10

20

30

40

50

) 参照)。絶縁層 212 はスパッタリング法、蒸着法、CVD 法、塗布法などを用いて形成することができる。絶縁層 212 に用いることができる材料としては、窒化珪素、酸化珪素、酸化窒化珪素、窒化酸化珪素に代表される珪素の酸化物材料又は窒化物材料等が挙げられる。また、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒素含有量が酸素含有量よりも多い窒化酸化アルミニウム、ダイアモンドライクカーボン (DLC) 、窒素含有炭素その他の無機絶縁性材料を含む物質から選ばれた材料を用いても良い。また、シロキサン樹脂を用いてもよい。なお、シロキサン樹脂とは、Si-O-Si 結合を含む樹脂をいう。シロキサンは、シリコン (Si) と酸素 (O) との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基 (例えばアルキル基、アリール基) が用いられる。有機基はフルオロ基を含んでいても良い。また、ポリイミド、アクリルポリマー、ポリアミド、ポリイミドアミド、ベンゾシクロブテン系材料、ポリシラザン等の有機絶縁性材料を用いることもできる。

10

#### 【0052】

絶縁層 220 の目的は、後に単結晶半導体層を接合する領域の平坦性を確保することにあるから、島状の単結晶半導体層 210 や絶縁層 212 、導電層 214 による凹凸が十分に小さい場合には、絶縁層 220 を形成しない構成としても構わない。しかしながら、凹凸がわずかに存在する場合であっても、接合の不良が生じる場合があるから、絶縁層 220 を設ける構成とすることが好ましい。

#### 【0053】

次に、絶縁層 220 の上面を、化学的機械的研磨 (Chemical Mechanical Polishing : CMP) 、レーザー光の照射、ドライエッティング等により平坦化する (図 4 (B) 参照)。より具体的には、導電層 214 の表面が露出する程度に平坦化すると良い。これにより、後に単結晶半導体層を接合する際の不良を大きく低減することができる。ここで、絶縁層 220 の上面が十分に平坦である場合には、該平坦化の工程は省略しても構わない。なお、導電層 214 の表面が露出する程度に平坦化 (研磨等) を行うことにより、後に形成される接合層のみをゲート絶縁層として用いることになる。接合層は非常に緻密な膜であり、十分に薄く形成することができるから、該接合層はゲート絶縁層として好適であり、該接合層を用いて形成したトランジスタは、その特性が非常に優れたものとなる。

#### 【0054】

次に、絶縁層 220 上に接合層 222 を形成する。また、単結晶半導体基板 224 の表面から所定の深さにイオンを打ち込むことにより、損傷領域 226 及び単結晶半導体層 228 を形成する。そして、接合層 222 と単結晶半導体層 228 を密接させる (図 4 (C) 参照)。接合層 222 と単結晶半導体層 228 とを密接させて圧力をかけることで、水素結合や共有結合による強固な接合を形成することができる。なお、接合層 222 と単結晶半導体層 228 を密接させた後には、加熱処理を行うことが好ましい。加熱処理を行うことで接合強度をより向上させることができる。なお、接合層 222 と単結晶半導体層 228 との間に下地層を形成する構成としても良いが、接合層 222 のみをゲート絶縁層として用いたい場合には、下地層は形成しない。下地層を形成する場合には、窒化シリコン、窒化酸化シリコン又は酸化窒化シリコンから選ばれた一又は複数の材料を用いて形成すると良い。ここで、接合層 222 は絶縁性材料より形成されるため、絶縁層と呼ぶことができる。

#### 【0055】

なお、絶縁層 220 上に接合層 222 を形成する工程と、単結晶半導体基板 224 に損傷領域 226 を形成する工程は、どちらを先に行っても良い。接合層 222 の形成と損傷領域 226 の形成の順序は特に問われず、各々を独立したタイミングにて形成することができる。接合に関する詳細については、上記の単結晶半導体層 204 と接合層 208 とを接合させる場合を参照できるため、ここでは省略する。

#### 【0056】

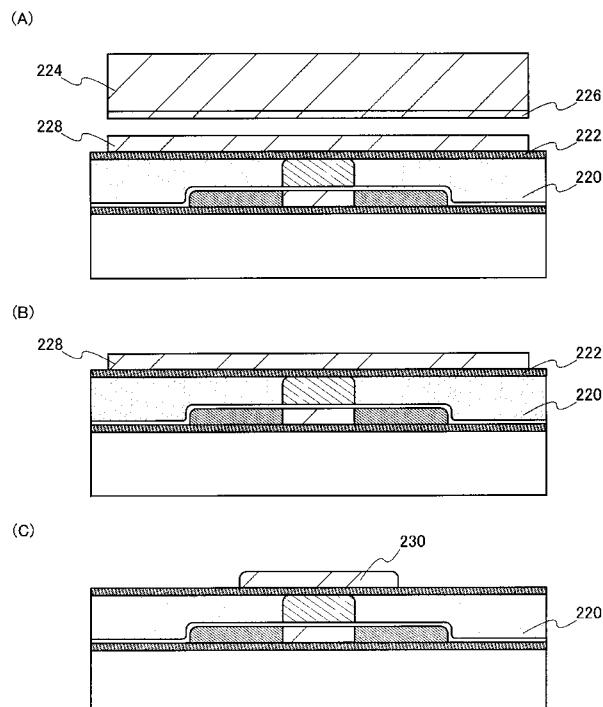

次に、加熱処理を行い、損傷領域 226 の一部を分離面として単結晶半導体層 228 を

10

20

30

40

50

単結晶半導体基板 224 から分離する（図 5（A）参照）。例えば、400 乃至 600 の熱処理を行うことにより、損傷領域 226 に形成された微小な空洞の体積変化を誘起して分離させることができる。これにより、絶縁層 220 上には単結晶半導体層 228 が残存することとなる。なお、図 5においては、損傷領域 226 と単結晶半導体層 228 との界面にて分離した様子を図示したが、本発明はこれに限られない。例えば、損傷領域 226 と単結晶半導体基板 224 との界面にて分離しても良いし、損傷領域 226 の一部にて分離しても良い。分離が生じる領域は、損傷領域 226 を形成する際の条件により異なるものと考えられる。

#### 【0057】

なお、分離の際の加熱条件の詳細については、上記の単結晶半導体層 204 を形成する場合を参照できるため、ここでは省略する。以上の工程により、絶縁層 220 上に単結晶半導体層 228 を形成することができる（図 5（B）参照）。

#### 【0058】

上記の工程によって得られた単結晶半導体層 228 については、化学的機械的研磨（Chemical Mechanical Polishing : CMP）、レーザー光の照射、ドライエッティング等により表面を平坦化することが好ましい。単結晶半導体層 228 の平坦性を向上することにより、後に形成する半導体素子のばらつきを抑えることができる。なお、所望の特性が得られるようであれば、CMP やレーザー光照射、ドライエッティング等は省略してもかまわない。レーザー光の照射を行う場合には、イオン注入に起因する欠陥を低減することもできる。

#### 【0059】

次に、単結晶半導体層 228 を所望の形状にパターニングして、島状の単結晶半導体層 230 を形成する（図 5（C）参照）。パターニングの際のエッティング加工としては、プラズマエッティング（ドライエッティング）、ウエットエッティングのどちらを採用しても良いが、大面積基板を処理するにはプラズマエッティングが適している。エッティングガスとしては、 $\text{CF}_4$ 、 $\text{NF}_3$ 、 $\text{Cl}_2$ 、 $\text{BCl}_3$ 、などのフッ素系又は塩素系のガスを用い、He や Ar などの不活性ガスを適宜加えても良い。また、大気圧放電のエッティング加工を適用すれば、局所的な放電加工も可能であり、基板の全面にマスク層を形成する必要はない。

#### 【0060】

本実施の形態においては、島状の単結晶半導体層 230 が、島状の単結晶半導体層 210 より小さくなるようにパターニングする。これは、後に配線（又は電極）を形成する際に、島状の単結晶半導体層 210 と配線とのコンタクトを良好に形成するためである。ただし、島状の単結晶半導体層 210 と配線とのコンタクトが適切に形成できるのであれば、これに限られない。

#### 【0061】

単結晶半導体層 228 をパターニングして、島状の単結晶半導体層 230 を形成した後には、しきい値電圧を制御するために、硼素、アルミニウム、ガリウムなどの p 型不純物を添加すると良い。例えば、p 型不純物として、硼素を  $1 \times 10^{16} \text{ cm}^{-3}$  以上  $1 \times 10^{18} \text{ cm}^{-3}$  以下の濃度で添加することができる。なお、適切な不純物濃度の単結晶半導体基板を用いることにより、しきい値電圧制御のためのドーピング工程は省略することができる。

#### 【0062】

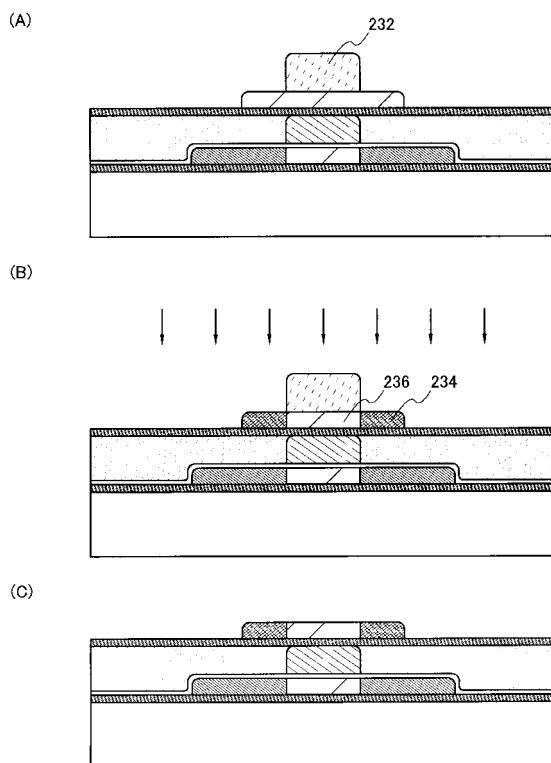

次に、フォトリソグラフィ法を用いて、島状の単結晶半導体層 230 上にレジスト材料からなるマスク 232 を形成する（図 6（A）参照）。なお、マスク 232 は導電層 214 をマスクとして用いた裏面露光により自己整合的に形成しても良いし、メタルマスクを用いた上面からの露光により形成しても良い。裏面露光により自己整合的にマスク 232 を形成する場合には、単結晶半導体層や絶縁層を十分に透過する波長の光を用いることが好ましい。例えば、高圧水銀ランプの g 線（波長：436 nm）等を用いることができる。

#### 【0063】

10

20

30

40

50

その後、マスク 232 を用いて p 型を付与する不純物元素を添加し、不純物領域 234 及びチャネル形成領域 236 を形成する（図 6（B）参照）。本実施の形態では、不純物元素を含むドーピングガスとしてジボラン（ $B_2H_6$ ）を用いてドーピングを行う。ここでは、不純物領域 234 にボロン（B）が  $1 \times 10^{20} / cm^3$  以上  $5 \times 10^{21} / cm^3$  以下程度の濃度で含まれるようにする。

#### 【0064】

なお、本実施の形態においては、島状の単結晶半導体層 230 に p 型を付与する不純物元素を添加する構成としたが、本発明はこれに限られない。n 型を付与する不純物元素を添加する構成としても良い。また、不純物領域 234 とチャネル形成領域 236 との間に LDD 領域を形成する構成としても良い。

10

#### 【0065】

その後、マスク 232 を除去する（図 6（C）参照）。マスク 232 の除去後には、不純物領域 234 の活性化のための加熱処理等を施しても良い。以上により、第 2 のトランジスタを構成する島状の単結晶半導体層 230、接合層 222（絶縁層）、導電層 214 が形成されたことになる。

20

#### 【0066】

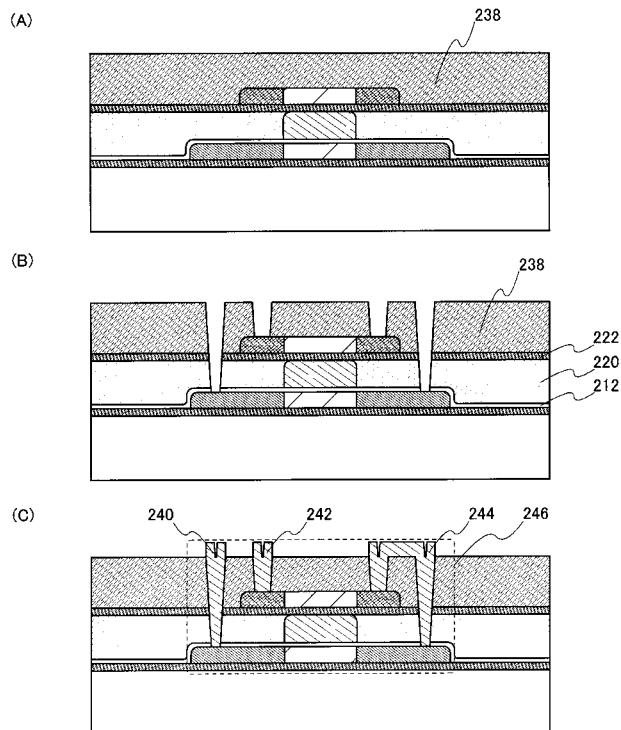

次に、島状の単結晶半導体層 230 及び接合層 222 を覆うように絶縁層 238 を形成する（図 7（A）参照）。絶縁層 238 はスパッタリング法、蒸着法、CVD 法、塗布法などを用いて形成することができる。絶縁層 238 に用いることができる材料としては、窒化珪素、酸化珪素、酸化窒化珪素、窒化酸化珪素に代表される珪素の酸化物材料又は窒化物材料等が挙げられる。また、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒素含有量が酸素含有量よりも多い窒化酸化アルミニウム、ダイアモンドライカーボン（DLC）、窒素含有炭素その他の無機絶縁性材料を含む物質から選ばれた材料を用いても良い。また、シロキサン樹脂を用いてもよい。なお、シロキサン樹脂とは、Si-O-Si 結合を含む樹脂をいう。シロキサンは、シリコン（Si）と酸素（O）との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基（例えばアルキル基、アリール基）が用いられる。有機基はフルオロ基を含んでいても良い。また、ポリイミド、アクリルポリマー、ポリアミド、ポリイミドアミド、ベンゾシクロブテン系材料、ポリシラザン等の有機絶縁性材料を用いることもできる。

30

#### 【0067】

次に、レジスト材料からなるマスクを用いて絶縁層 212、絶縁層 220、接合層 222、絶縁層 238 にコンタクトホール（開口部）を形成する（図 7（B）参照）。エッチングは、用いる材料の選択比によって、一回で行う構成としても良いし、複数回にて行う構成としても良い。

#### 【0068】

その後、開口部を覆うように導電層を形成し、該導電層をエッチングする。これにより、ソース領域又はドレイン領域の一部とそれぞれ電気的に接続するソース電極又はドレイン電極 240（ソース配線又はドレイン配線とも言う）、ソース電極又はドレイン電極 242、ソース電極又はドレイン電極 244 を形成する（図 7（C）参照）。ソース電極又はドレイン電極には、アルミニウム（Al）、タンタル（Ta）、チタン（Ti）、モリブデン（Mo）、タンゲステン（W）、ネオジム（Nd）、クロム（Cr）、ニッケル（Ni）、白金（Pt）、金（Au）、銀（Ag）、銅（Cu）、マグネシウム（Mg）、スカンジウム（Sc）、コバルト（Co）、ニッケル（Ni）、亜鉛（Zn）、ニオブ（Nb）、シリコン（Si）、リン（P）、ボロン（B）、ヒ素（As）、ガリウム（Ga）、インジウム（In）、錫（Sn）から選択された一若しくは複数の元素、又は前記元素を成分として含有する化合物や合金材料（例えば、インジウム錫酸化物（ITO）、インジウム亜鉛酸化物（IZO）、酸化珪素を添加したインジウム錫酸化物（ITSO）、酸化亜鉛（ZnO）、アルミニネオジム（Al-Nd）、マグネシウム銀（Mg-Ag）など）、若しくはこれらの化合物を組み合わせた物質等が用いられる。その他にも、シリサイド（例えば、アルミシリコン、モリブデンシリコン、ニッケルシリサイド）や、窒素を

40

50

含有する化合物（例えば、窒化チタン、窒化タンタル、窒化モリブデン）、リン（P）等の不純物元素をドーピングしたシリコン（Si）等を用いることもできる。

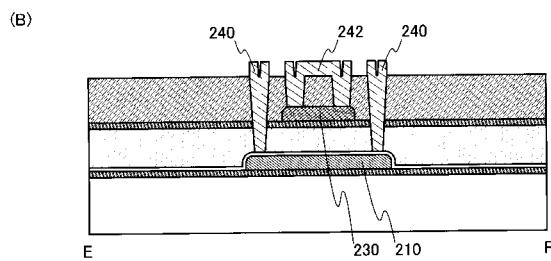

#### 【0069】

以上の工程で、第1のトランジスタ及び第2のトランジスタからなる相補型回路246（CMOS回路）が形成された（図7（C）参照）。なお、本実施の形態においては、第1のトランジスタをn型とし、第2のトランジスタをp型としたが本発明はこれに限られない。第1のトランジスタをp型とし、第2のトランジスタをn型としても良い。また、異なる極性の二つのトランジスタを用いて相補型回路246を形成することに限られない。同じ極性のトランジスタを積層して形成しても良い。第1のトランジスタ及び第2のトランジスタを同じ極性とする場合には、ゲート電極として機能する導電層を独立して設けても良いし、共通化しても良い。例えば、第1のトランジスタと第2のトランジスタのチャネル形成領域への不純物元素の注入量を異ならせることで、ゲート電極を共通化した場合でも二つのトランジスタを独立させて動作させることが可能である。

10

#### 【0070】

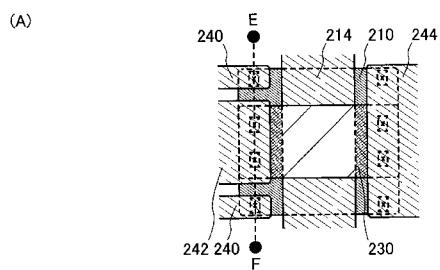

なお、本実施の形態においては、チャネル長方向に対して第1のトランジスタを形成する島状の単結晶半導体層210と、第2のトランジスタを形成する島状の単結晶半導体層230との大きさを異ならせる構成としたが、例えば、図19に示す構成のように、島状の単結晶半導体層210と島状の単結晶半導体層230とのチャネル幅方向の大きさを異ならせることも可能である。ここで、図19（A）は平面図であり、図19（B）は、図19（A）のE-Fにおける断面図である。図19において、ソース電極又はドレイン電極240（ソース配線又はドレイン配線とも言う）、ソース電極又はドレイン電極242、ソース電極又はドレイン電極244の対応関係は図7と同様であり、ソース電極又はドレイン電極244によって、二つのトランジスタが電気的に接続されている。また、図7と同様にゲート電極として機能する導電層214が設けられている。なお、ゲート電極として機能する導電層214はCMOS回路の入力端子に当たり、ソース電極又はドレイン電極244はCMOS回路の出力端子に当たる。図19から分かるように、第1の（下層の）トランジスタのチャネル幅（W<sub>1</sub>）は第2の（上層の）トランジスタのチャネル幅（W<sub>2</sub>）より大きくなっている。

20

#### 【0071】

上記のように相補型回路を形成する場合には、第1のトランジスタをp型とし、第2のトランジスタをn型とすることで、二つのトランジスタの移動度の差を補完することができる。つまり、移動度の低いp型トランジスタのチャネル幅を、移動度の高いn型トランジスタのチャネル幅より大きくすることで、相対的にp型トランジスタを流れる電流を増加させることができる。すなわち、レイアウトの効率化と共に、相補型回路の動作の高速化を実現することができる。もちろん、上記構成に限らず、要求される電流等に応じて、第1のトランジスタと、第2のトランジスタのチャネル幅を適宜変更しても良い。

30

#### 【0072】

本発明の如く、単結晶半導体層を積層して半導体素子（例えば、トランジスタ）を形成することにより、プロセスルールの微細化に頼らずに、高度に集積化した半導体装置を作製することができる。つまり、小型かつ高性能な半導体装置を提供することができる。また、プロセスルールの微細化に起因する様々な問題点を解消することができる。また、すべての半導体素子を単結晶半導体を用いて形成するため、アモルファス半導体や多結晶半導体を用いる場合と比較して、優れた特性の半導体装置を提供することができる。

40

#### 【0073】

また、本発明においては、単結晶半導体層に電界を加える導電層（いわゆるゲート電極）を共通化する。これにより、複数の導電層を形成する必要がないため、低コストに半導体装置を作製することができる。特に、相補型回路（CMOS回路、相補型半導体装置とも言う）を形成する場合には、そのメリットは顕著である。例えば2層の単結晶半導体層にて形成されるすべての回路を相補型回路とした場合には、従来の如く1層の半導体層により相補型回路を形成する場合と比較して、実に2倍の集積度を実現することができる。

50

しかも、ゲート電極はその大部分が共通化されるため、非常に低コストである。さらに、配線が共通化されるため、回路全体の配線長を短縮することができる。すなわち、配線容量に起因する消費電力を低減することができ、低消費電力化に大きく貢献する。

#### 【0074】

もちろん、3層以上の多層構造とすることにより、さらなる集積化を容易に実現することができる。この場合にも、本実施の形態にて説明した作製方法を参照して多層半導体構造を実現することができる。

#### 【0075】

##### (実施の形態2)

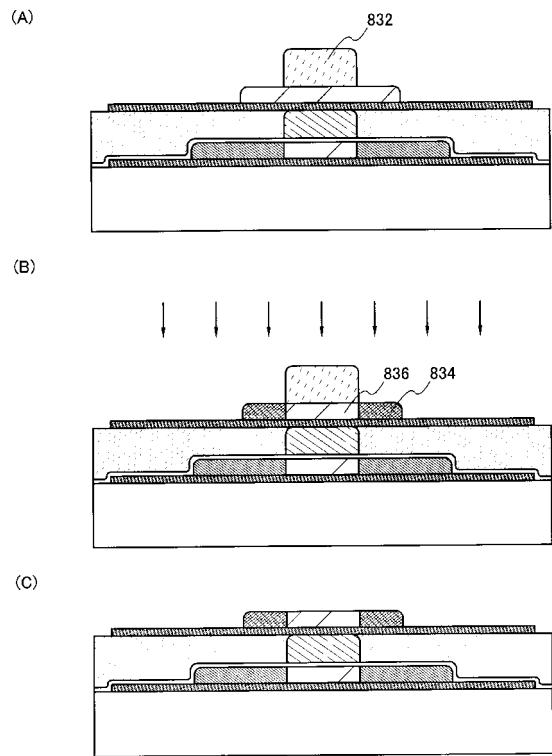

本実施の形態では、本発明の半導体装置の製造方法の別の一例について、図8乃至13を参照して説明する。なお、本実施の形態において、実施の形態1を参照できる部分については詳細な説明を省略することとする。

10

#### 【0076】

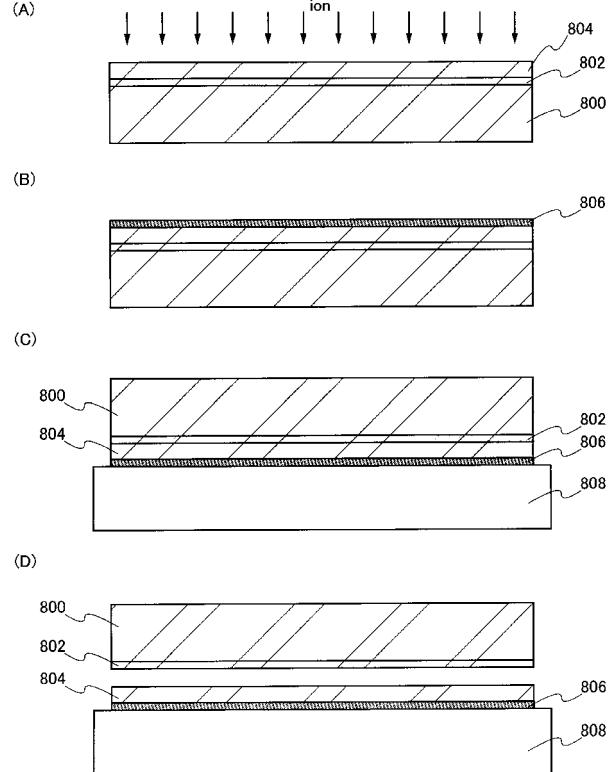

はじめに、単結晶半導体基板800を用意する。そして、単結晶半導体基板800の表面から所定の深さにイオンを打ち込み、損傷領域802及び単結晶半導体層804を形成する(図8(A)参照)。損傷領域802及び単結晶半導体層804の形成方法の詳細については、実施の形態1を参照できるため、ここでは省略する。

#### 【0077】

単結晶半導体基板800は、単結晶半導体材料からなる基板であれば特に限られないが、本実施の形態においては一例として、単結晶シリコン基板を用いることとする。その他、ゲルマニウム基板や、ガリウムヒ素、インジウムリンなどの化合物半導体による基板を適用することもできる。

20

#### 【0078】

なお、損傷領域802の形成前に、単結晶半導体基板800の表面に保護層を形成する構成としても良い。保護層を形成することにより、イオンの照射に伴う単結晶半導体基板の表面の荒れを低減することができる。保護層としては、酸化シリコン、窒化シリコン、窒化酸化シリコン、酸化窒化シリコン等を用いることができる。

20

#### 【0079】

次に、単結晶半導体層804上に、接合層806を形成する(図8(B)参照)。接合層806は、酸化シリコン膜を、有機シランガスを用いた化学気相成長法(CVD法)により形成すると良い。その他に、シランガスを用いて化学気相成長法により作製される酸化シリコン膜を適用することもできる。なお、接合層806は絶縁性材料より形成されるため、絶縁層と呼ぶことができる。接合層806の詳細については、実施の形態1を参照できるため、ここでは省略する。

30

#### 【0080】

なお、単結晶半導体層804と接合層806との間に、下地層を設ける構成としてもよい。下地層は窒化シリコン、窒化酸化シリコン若しくは酸化窒化シリコンから選ばれた一又は複数の材料を用いて形成すると良い。なお、下地層は単層構造でも良いし積層構造でも良い。下地層は、可動イオンや水分等の不純物が、単結晶半導体層804に侵入することを防ぐために設けられる。なお、不純物の侵入を防ぐことができるのであれば、上記材料以外を用いた下地層を形成しても良い。また、不純物の侵入が大きな問題とならない場合には、下地層を設けない構成としても良い。上記にて保護層を形成した場合には、該保護層を下地層として用いても良い。

40

#### 【0081】

次に、絶縁表面を有する基板808と、接合層806とを密接させる(図8(C)参照)。絶縁表面を有する基板808と接合層806とを密接させて圧力をかけることで、水素結合や共有結合による強固な接合を形成することができる。なお、接合層806を介して絶縁表面を有する基板808と単結晶半導体基板800とを貼り合わせた後には、加熱処理を行うことが好ましい。加熱処理を行うことで接合強度をより向上させることができる。また、接合層806と絶縁表面を有する基板808との間にバリア層を形成する

50

構成としても良い。バリア層を形成することにより、単結晶半導体層 804への可動イオン等の侵入を防ぐことができる。バリア層は、上記下地層と同様の材料を用いて作製することができるがこれに限られるものではない。

#### 【0082】

なお、絶縁表面を有する基板 808としては、アルミニノシリケートガラス、アルミニノホウケイ酸ガラス、バリウムホウケイ酸ガラスのような電子工業用に使われる各種ガラス基板、石英基板、セラミック基板、サファイア基板等を用いることができる。好ましくはガラス基板を用いるのがよく、例えば第6世代 ( $1500\text{mm} \times 1850\text{mm}$ )、第7世代 ( $1870\text{mm} \times 2200\text{mm}$ )、第8世代 ( $2200\text{mm} \times 2400\text{mm}$ )と呼ばれる大面積のマザーガラス基板を用いることもできる。大面積のマザーガラス基板を、絶縁表面を有する基板 808として用いることで、半導体基板の大面積化が実現できる。なお、絶縁表面を有する基板 808は上記の基板に限定されるものではない。例えば、耐熱温度が許せば樹脂材料からなる基板を用いることも可能である。

10

#### 【0083】

良好な接合を形成するために、接合が形成される表面を活性化しておいても良い。例えば、接合を形成する面に原子ビーム若しくはイオンビームを照射する。原子ビーム又はイオンビームを利用する場合には、アルゴン等の不活性ガス原子ビーム又は不活性ガスイオンビームを用いることができる。その他に、プラズマ処理又はラジカル処理を行う。このような表面処理により、200乃至400程度の低温で異種材料間の接合を形成することができる。

20

#### 【0084】

次に、加熱処理を行い、損傷領域 802の一部を分離面として単結晶半導体層 804を単結晶半導体基板 800から分離する(図8(D)参照)。例えば、400乃至600の熱処理を行うことにより、損傷領域 802に形成された微小な空洞の体積変化を誘起して分離させることができる。接合層 806は絶縁表面を有する基板 808と接合しているので、絶縁表面を有する基板 808上には単結晶半導体層 804が残存することとなる。なお、図8においては、損傷領域 802と単結晶半導体層 804との界面にて分離した様子を図示したが、本発明はこれに限られない。例えば、損傷領域 802と単結晶半導体基板 800との界面にて分離しても良いし、損傷領域 802の一部にて分離しても良い。分離が生じる領域は、損傷領域 802を形成する際の条件により異なるものと考えられる。

30

#### 【0085】

その他の条件に関しては、実施の形態1を参照できるため、ここでは省略するものとする。

#### 【0086】

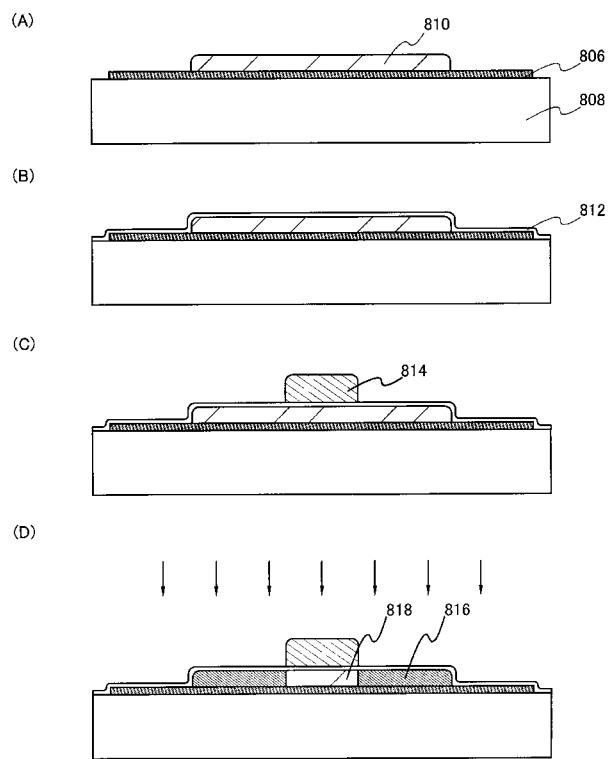

次に、単結晶半導体層 804を所望の形状にパターニングして、島状の単結晶半導体層 810を形成する(図9(A)参照)。パターニングの際のエッティング加工としては、プラズマエッティング(ドライエッティング)、ウェットエッティングのどちらを採用しても良いが、大面積基板を処理するにはプラズマエッティングが適している。エッティングガスとしては、 $\text{CF}_4$ 、 $\text{NF}_3$ 、 $\text{Cl}_2$ 、 $\text{BCl}_3$ 、などのフッ素系又は塩素系のガスを用い、 $\text{He}$ や $\text{Ar}$ などの不活性ガスを適宜加えても良い。また、大気圧放電のエッティング加工を適用すれば、局所的な放電加工も可能であり、基板の全面にマスク層を形成する必要はない。

40

#### 【0087】

単結晶半導体層 804をパターニングして、島状の単結晶半導体層 810を形成した後には、しきい値電圧を制御するために、硼素、アルミニウム、ガリウムなどのp型不純物を添加すると良い。例えば、p型不純物として、硼素を $1 \times 10^{16}\text{cm}^{-3}$ 以上 $1 \times 10^{18}\text{cm}^{-3}$ 以下の濃度で添加することができる。なお、適切な不純物濃度の単結晶半導体基板を用いることにより、しきい値電圧制御のためのドーピング工程は省略することができる。

#### 【0088】

50

次に、島状の単結晶半導体層810を覆う絶縁層812を形成する(図9(B)参照)。絶縁層812はゲート絶縁層として機能する。絶縁層812はスパッタリング法、CVD法などを用い、厚さを2nm以上150nm以下程度として珪素を含む絶縁膜で形成する。詳細については、実施の形態1を参照することができる。

#### 【0089】

次に、絶縁層812上に導電層を形成し、該導電層をパターニングすることで導電層814を形成する(図9(C)参照)。導電層814はゲート電極として機能する。詳細については、実施の形態1を参照することができる。

#### 【0090】

次に、導電層814をマスクとして、n型を付与する不純物元素を添加し、不純物領域816及びチャネル形成領域818を形成する(図9(D)参照)。本実施の形態では、不純物元素を含むドーピングガスとしてホスフィン(PH<sub>3</sub>)を用いてドーピングを行う。ここでは、不純物領域816に、n型を付与する不純物元素であるリン(P)が $1 \times 10^{19} / \text{cm}^3$ 以上 $1 \times 10^{21} / \text{cm}^3$ 以下程度の濃度で含まれるようにする。

10

#### 【0091】

なお、本実施の形態においては、島状の単結晶半導体層810にn型を付与する不純物元素を添加する構成としたが、本発明はこれに限られない。p型を付与する不純物元素を添加する構成としても良い。p型を付与する不純物元素を添加する場合には、不純物元素(例えば、ボロン(B))の濃度が $1 \times 10^{20} / \text{cm}^3$ 以上 $5 \times 10^{21} / \text{cm}^3$ 以下程度となるようにする。また、不純物領域816とチャネル形成領域818との間にLDD領域を形成する構成としても良い。LDD領域における不純物元素の濃度は $1 \times 10^{17} / \text{cm}^3$ 以上 $1 \times 10^{19} / \text{cm}^3$ 以下程度とするのが好適である。

20

#### 【0092】

以上の工程により、第1のトランジスタを構成する島状の単結晶半導体層810、絶縁層812、導電層814が形成されたことになる。なお、不純物領域816の活性化のために加熱処理等を施しても良い。

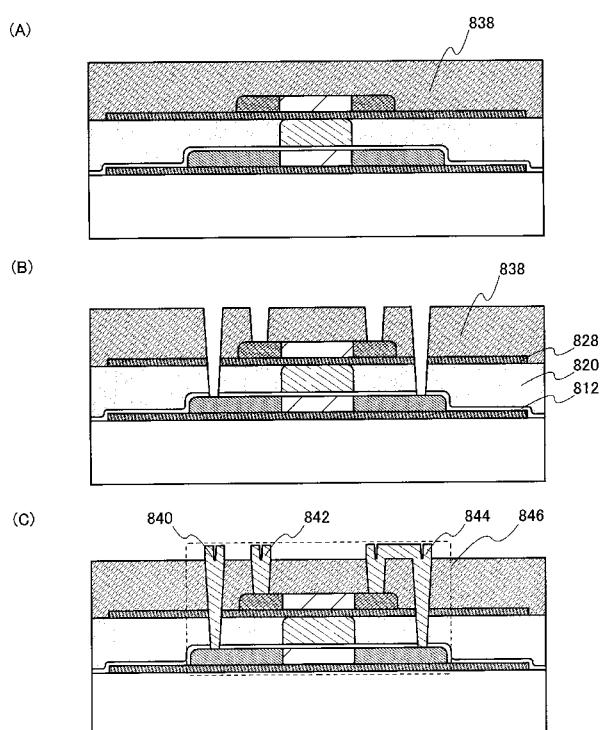

#### 【0093】

次に、絶縁層812及び導電層814を覆うように絶縁層820を形成する(図10(A)参照)。絶縁層812はスパッタリング法、蒸着法、CVD法、塗布法などを用いて形成することができる。詳細については、実施の形態1を参照すればよい。

30

#### 【0094】

絶縁層820の目的は、後に単結晶半導体層を接合する領域の平坦性を確保することにあるから、島状の単結晶半導体層810や絶縁層812、導電層814による凹凸が十分に小さい場合には、絶縁層820を形成しない構成としても構わない。しかしながら、凹凸がわずかに存在する場合であっても、接合の不良が生じる場合があるから、絶縁層820を設ける構成とすることが好ましい。

#### 【0095】

次に、絶縁層820の上面を、化学的機械的研磨(Chemical Mechanical Polishing: CMP)、レーザー光の照射、ドライエッチング等により平坦化する(図10(B)参照)。より具体的には、導電層814の表面が露出する程度に平坦化すると良い。これにより、後に単結晶半導体層を接合する際の不良を大きく低減することができる。ここで、絶縁層820の上面が十分に平坦である場合には、該平坦化の工程は省略しても構わない。なお、導電層814の表面が露出する程度に平坦化(研磨等)を行うことにより、後に形成される接合層のみをゲート絶縁層として用いることができるようになる。接合層は非常に緻密な膜であり、十分に薄く形成することができるから、該接合層はゲート絶縁層として好適であり、該接合層を用いて形成したトランジスタは、その特性が非常に優れたものとなる。

40

#### 【0096】

次に、単結晶半導体基板822の表面から所定の深さにイオンを打ち込むことにより、損傷領域824及び単結晶半導体層826を形成し、単結晶半導体層826上に接合層8

50

28を形成する。そして、接合層828と絶縁層820（及び導電層814）を密接させる（図10（C）参照）。接合層828と絶縁層820とを密接させて圧力をかけることで、水素結合や共有結合による強固な接合を形成することが可能である。なお、接合層828と絶縁層820を密接させた後には、加熱処理を行うことが好ましい。加熱処理を行うことで接合強度をより向上させることができる。なお、単結晶半導体層826と接合層828との間に下地層を形成する構成としても良いが、接合層828のみをゲート絶縁層として用いたい場合には、下地層は形成しない。下地層を形成する場合には、窒化シリコン、窒化酸化シリコン若しくは酸化窒化シリコンから選ばれた一又は複数の材料を用いて形成すると良い。ここで、接合層828は絶縁性材料より形成されるため、絶縁層と呼ぶことができる。

10

## 【0097】

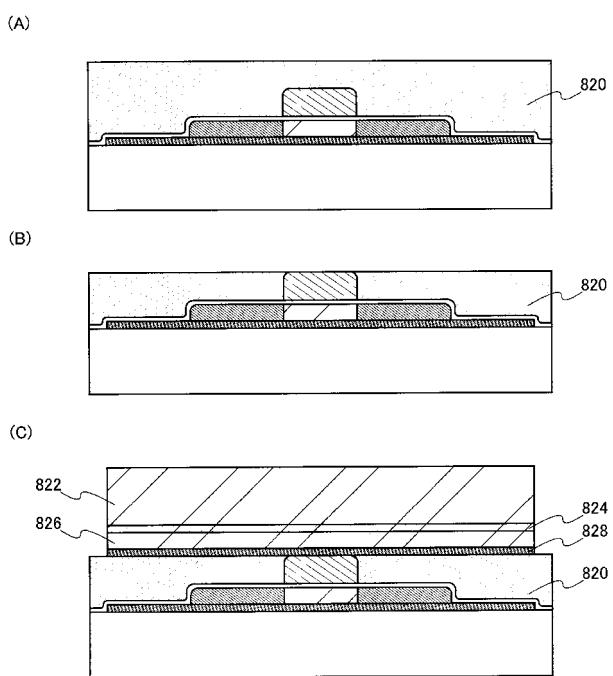

次に、加熱処理を行い、損傷領域824の一部を分離面として単結晶半導体層826を単結晶半導体基板822から分離する（図11（A）参照）。例えば、400乃至600の熱処理を行うことにより、損傷領域824に形成された微小な空洞の体積変化を誘起して分離させることができる。これにより、絶縁層820上には単結晶半導体層826が残存することとなる。なお、図11においては、損傷領域824と単結晶半導体層826との界面にて分離した様子を図示したが、本発明はこれに限られない。例えば、損傷領域824と単結晶半導体基板822との界面にて分離しても良いし、損傷領域824の一部にて分離しても良い。分離が生じる領域は、損傷領域824を形成する際の条件により異なるものと考えられる。

20

## 【0098】

なお、詳細な条件等については、実施の形態1等を参照できるため、ここでは省略する。以上の工程により、絶縁層820上に単結晶半導体層826を形成することができる（図11（B）参照）。

## 【0099】

次に、単結晶半導体層826を所望の形状にパターニングして、島状の単結晶半導体層830を形成する（図11（C）参照）。詳細については、実施の形態1を参照すればよい。

## 【0100】

単結晶半導体層826をパターニングして、島状の単結晶半導体層830を形成した後には、しきい値電圧を制御するために、硼素、アルミニウム、ガリウムなどのp型不純物を添加すると良い。例えば、p型不純物として、硼素を $1 \times 10^{16} \text{ cm}^{-3}$ 以上 $1 \times 10^{18} \text{ cm}^{-3}$ 以下の濃度で添加することができる。なお、適切な不純物濃度の単結晶半導体基板を用いることにより、しきい値電圧制御のためのドーピング工程は省略することができる。

30

## 【0101】

次に、フォトリソグラフィ法を用いて、島状の単結晶半導体層830上にレジスト材料からなるマスク832を形成する（図12（A）参照）。そして、マスク832を用いて、p型を付与する不純物元素を添加し、不純物領域834及びチャネル形成領域836を形成する（図12（B）参照）。本実施の形態では、不純物元素を含むドーピングガスとしてジボラン（ $\text{B}_2\text{H}_6$ ）を用いてドーピングを行う。ここでは、不純物領域834にボロン（B）が $1 \times 10^{20} / \text{cm}^3$ 以上 $5 \times 10^{21} / \text{cm}^3$ 以下程度の濃度で含まれるようにする。

40

## 【0102】

なお、本実施の形態においては、島状の単結晶半導体層830にp型を付与する不純物元素を添加する構成としたが、本発明はこれに限られない。n型を付与する不純物元素を添加する構成としても良い。また、不純物領域834とチャネル形成領域836との間にLDD領域を形成する構成としても良い。

## 【0103】

その後、マスク832を除去する（図12（C）参照）。マスク832の除去後には、

50

不純物領域 834 の活性化のための加熱処理等を施しても良い。以上により、第 2 のトランジスタを構成する島状の単結晶半導体層 830、接合層 828（絶縁層）、導電層 814 が形成されたことになる。

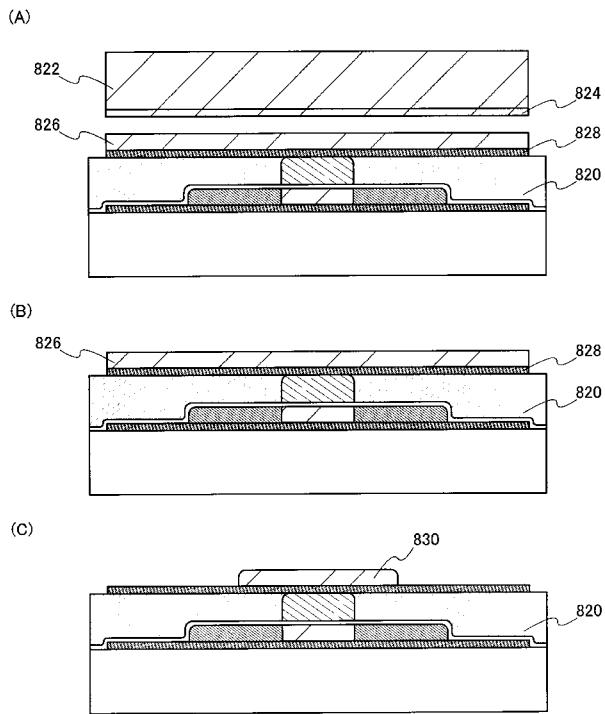

#### 【0104】

次に、島状の単結晶半導体層 830 及び接合層 828 を覆うように絶縁層 838 を形成する（図 13（A）参照）。詳細については、実施の形態 1 を参照することができる。

#### 【0105】

次に、レジスト材料からなるマスクを用いて絶縁層 812、絶縁層 820、接合層 828、絶縁層 838 にコンタクトホール（開口部）を形成する（図 13（B）参照）。エッチングは、用いる材料の選択比によって、一回で行う構成としても良いし、複数回にて行う構成としても良い。

10

#### 【0106】

その後、開口部を覆うように導電層を形成し、該導電層をエッチングする。これにより、ソース領域又はドレイン領域の一部とそれぞれ電気的に接続するソース電極又はドレイン電極 840（ソース配線又はドレイン配線とも言う）、ソース電極又はドレイン電極 842、ソース電極又はドレイン電極 844 を形成する（図 13（C）参照）。詳細については、実施の形態 1 を参照することができる。

#### 【0107】

以上の工程で、第 1 のトランジスタ及び第 2 のトランジスタからなる相補型回路 846（CMOS 回路）が形成された（図 13（C）参照）。なお、本実施の形態においては、第 1 のトランジスタを n 型とし、第 2 のトランジスタを p 型としたが本発明はこれに限られない。第 1 のトランジスタを p 型とし、第 2 のトランジスタを n 型としても良い。また、異なる極性の二つのトランジスタを用いて相補型回路 846 を形成することに限られない。同じ極性のトランジスタを積層して形成しても良い。

20

#### 【0108】

また、本実施の形態においては、実施の形態 1 とは異なり、単結晶半導体基板側に接合層を設ける構成としたが、本発明はこれに限られない。実施の形態 1 の如く絶縁表面を有する基板側に接合層を設ける構成としても良い。また、第 1 のトランジスタの単結晶半導体層を形成する際の接合層は絶縁表面を有する基板側に形成し、第 2 のトランジスタの単結晶半導体層を形成する際の接合層は単結晶半導体基板側に形成し、第 2 のトランジスタの単結晶半導体層を形成する際の接合層は絶縁表面を有する基板側に形成する構成としても良い。もちろん、第 1 のトランジスタの単結晶半導体層を形成する際の接合層は単結晶半導体基板側に形成し、第 2 のトランジスタの単結晶半導体層を形成する際の接合層は絶縁表面を有する基板側に形成する構成としても良い。

30

#### 【0109】

本発明の如く、単結晶半導体層を積層して半導体素子（例えば、トランジスタ）を形成することにより、プロセスルールの微細化に頼らずに、高度に集積化した半導体装置を作製することができる。つまり、プロセスルールの微細化に起因する様々な問題点を解消することができる。また、すべての半導体素子を単結晶半導体を用いて形成するため、アモルファス半導体や多結晶半導体を用いる場合と比較して、優れた特性の半導体装置を提供することができる。

40

#### 【0110】

また、本発明においては、単結晶半導体層に電界を加える導電層（いわゆるゲート電極）を共通化する。これにより、複数の導電層を形成する必要がないため、低コストに半導体装置を作製することができる。特に、相補型回路（CMOS 回路、相補型半導体装置とも言う）を形成する場合には、そのメリットは顕著である。例えば 2 層の単結晶半導体層にて形成されるすべての回路を相補型回路とした場合には、従来の如く 1 層の半導体層により相補型回路を形成する場合と比較して、実に 2 倍の集積度を実現することができる。しかも、ゲート電極はその大部分が共通化されるため、非常に低コストである。

#### 【0111】

もちろん、3 層以上の多層構造とすることにより、さらなる集積化を容易に実現するこ

50

とができる。この場合にも、本実施の形態にて説明した作製方法を参照してさらなる多層構造を実現することができる。

【0112】

本実施の形態は、実施の形態1と適宜組み合わせて用いることができる。

【0113】

(実施の形態3)

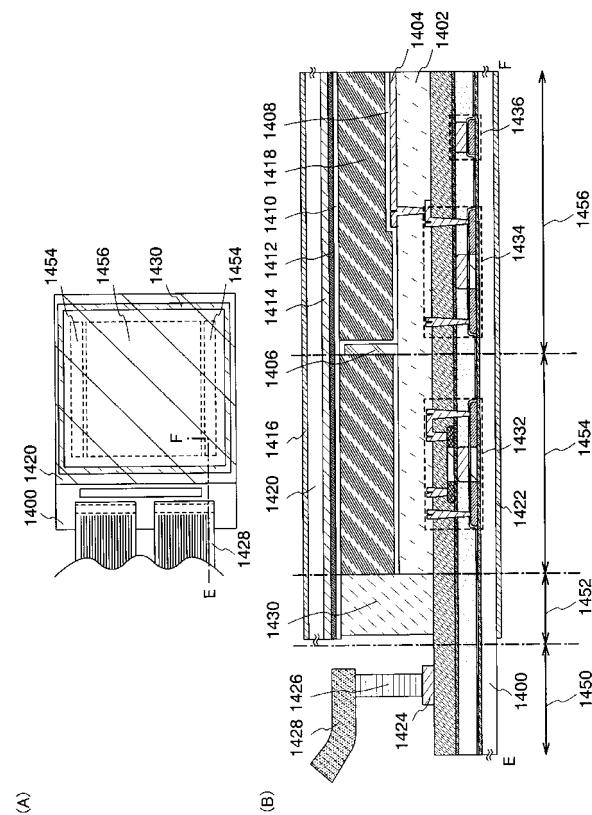

本実施の形態では、本発明の半導体装置の一例を、図14を参照して説明する。なお、本実施の形態においては、半導体装置の一例として液晶表示装置を挙げて説明するが、本発明により作製できる半導体装置は液晶表示装置に限られるものではない。

【0114】

10

図14に、本発明の液晶表示装置の一例を示す。図14(A)は液晶表示装置の平面図であり、図14(B)は図14(A)のE-Fにおける断面図である。該液晶表示装置は、実施の形態1や実施の形態2などに示した方法を用いて絶縁表面を有する基板1400上にトランジスタを形成した後、層間絶縁層1402、画素電極1404、スペーサ1406、配向膜として機能する絶縁層1408等を形成し、配向膜として機能する絶縁層1410、対向電極として機能する導電層1412、カラーフィルターとして機能する着色層1414、偏光子1416(偏光板ともいう)等が設けられた対向基板1420を貼り合わせ、空隙に液晶層1418を設けることで作製することができる。なお、絶縁表面を有する基板1400にも偏光子1422(偏光板)を設けるが、本発明はこれに限られない。例えば、反射型の液晶表示装置においては、偏光子は、一方に設ければ良い。

20

【0115】

上記において、画素電極1404は、インジウム錫酸化物(ITO)、酸化インジウムに酸化亜鉛(ZnO)を混合したIZO(indium zinc oxide)、酸化インジウムに酸化珪素(SiO<sub>2</sub>)を混合した導電性材料、有機インジウム、有機スズ、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、又はタンゲステン(W)、モリブデン(Mo)、ジルコニウム(Zr)、ハフニウム(Hf)、バナジウム(V)、ニオブ(Nb)、タンタル(Ta)、クロム(Cr)、コバルト(Co)、ニッケル(Ni)、チタン(Ti)、白金(Pt)、アルミニウム(Al)、銅(Cu)、銀(Ag)等の金属又はその合金、若しくはその金属窒化物を用いて形成することができる。また、導電性高分子(導電性ポリマーともいう)を含む導電性組成物を用いることもできる。導電性組成物は、薄膜におけるシート抵抗が10000 /sq.以下であることが好ましい。また、光透過性を有する画素電極層として薄膜を形成する場合には、波長550nmにおける透光率が70%以上であることが好ましい。また、含まれる導電性高分子の抵抗率が0.1 · cm以下であることが好ましい。

30

【0116】

配向膜として機能する絶縁層1408や、配向膜として機能する絶縁層1410には、ラビング処理が施されている。これにより、液晶分子の配向を制御することができる。

【0117】

本実施の形態にて示した液晶表示装置は、外部端子接続領域1450、封止領域1452、駆動回路領域1454、及び画素領域1456より構成されている。

40

【0118】

外部端子接続領域1450では、画素領域1456と電気的に接続された端子電極層1424に、異方性導電体層1426を介してFPC1428が接続されている。FPC1428は、外部からの信号を伝達する役目を担う。封止領域1452ではシール材1430を用いて絶縁表面を有する基板1400と対向基板1420との封止が行われている。駆動回路領域1454にはnチャネル型トランジスタとpチャネル型トランジスタからなるCMOS回路1432が設けられている。また、画素領域1456にはnチャネル型トランジスタ1434、及び容量配線1436が形成されている。なお、画素領域1456におけるnチャネル型トランジスタ1434は、CMOS回路1432のnチャネル型ト

50

ランジスタ（第1のトランジスタ）と同様にして作製することができる。また、容量配線1436は、各トランジスタにおいてゲート電極として機能する導電層と同じ層にて形成される。

#### 【0119】

本実施の形態においては、画素領域1456のトランジスタとして、nチャネル型トランジスタを用いる構成としているが、これに限られず、pチャネル型トランジスタを用いる構成としても良い。pチャネル型トランジスタを用いる場合には、CMOS回路1432のpチャネル型トランジスタ（第2のトランジスタ）と同様にして作製することができる。

#### 【0120】

なお、画素領域1456に形成されるトランジスタを単結晶半導体にて形成する必要がない場合には、非晶質半導体、微結晶半導体、多結晶半導体等を適宜用いて画素領域1456のトランジスタを作製しても良い。

#### 【0121】

本発明の如く、単結晶半導体層を積層してCMOS回路1432を作製することにより、ICチップを外付けで設ける必要が無いため、半導体装置の厚み及び額縁部分の面積を低減し、画素領域を有効に活用した半導体装置を低成本に提供することができる。特に、積層によりCMOS回路1432を設けているため、单層にて同様の回路を形成する場合と比較して、回路の面積を低減することができる。すなわち、額縁の領域を十分に小さくすることができ、画素領域を最大限に活用することができる。

#### 【0122】

なお、本実施の形態においては液晶表示装置の一例について説明したが、本発明はこれに限られるものではない。例えば、エレクトロルミネッセンス表示装置（発光装置、EL表示装置とも呼ばれる）や、電気泳動素子を用いる表示装置（電子ペーパ、電気泳動表示装置ともいわれる）等についても、同様の構成にて提供することができる。本実施の形態は、実施の形態1及び実施の形態2と適宜組み合わせて用いることができる。

#### 【0123】

##### （実施の形態4）

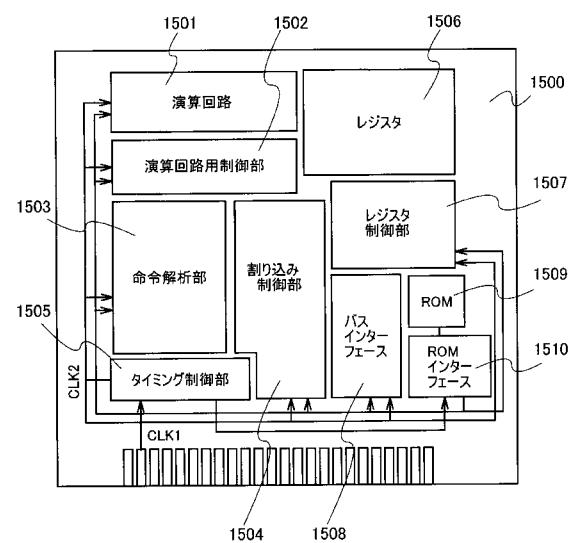

本実施の形態では、本発明に係る半導体装置の別の例について、図15及び16を参照して説明する。なお、本実施の形態においては、マイクロプロセッサ及び電子タグを例に挙げて説明するが、本発明の半導体装置はこれらに限られるものではない。

#### 【0124】

図15に、本発明のマイクロプロセッサの構成の一例を示す。図15のマイクロプロセッサ1500は、本発明の半導体基板を用いて製造されるものである。該マイクロプロセッサ1500は、演算回路1501(Arithmetic logic unit(ALU))、演算回路制御部1502(ALU Controller)、命令解析部1503(Instruction Decoder)、割り込み制御部1504(Interrupt Controller)、タイミング制御部1505(Timing Controller)、レジスタ1506(Register)、レジスタ制御部1507(Register Controller)、バスインターフェース1508(Bus I/F)、読み出し専用メモリ1509(Read Only Memory(ROM))、及びメモリインターフェース1510(ROM I/F)を有している。

#### 【0125】

バスインターフェース1508を介してマイクロプロセッサ1500に入力された命令は、命令解析部1503に入力され、デコードされた後、演算回路制御部1502、割り込み制御部1504、レジスタ制御部1507、タイミング制御部1505に入力される。演算回路制御部1502、割り込み制御部1504、レジスタ制御部1507、タイミング制御部1505は、デコードされた命令に基づき各種制御を行う。具体的に演算回路制御部1502は、演算回路1501の動作を制御するための信号を生成する。また、割り込み制御部1504は、マイクロプロセッサ1500のプログラム実行中に、外部の入

10

20

30

40

50

出力装置や周辺回路からの割り込み要求を、その優先度等から判断して処理する。レジスタ制御部 1507 は、レジスタ 1506 のアドレスを生成し、マイクロプロセッサ 1500 の状態に応じてレジスタ 1506 の読み出しや書き込みを行う。タイミング制御部 1505 は、演算回路 1501、演算回路制御部 1502、命令解析部 1503、割り込み制御部 1504、レジスタ制御部 1507 の動作のタイミングを制御する信号を生成する。例えばタイミング制御部 1505 は、基準クロック信号 CLK1 を元に、内部クロック信号 CLK2 を生成する内部クロック生成部を備えており、クロック信号 CLK2 を上記各種回路に供給する。なお、図 15 に示すマイクロプロセッサ 1500 の構成は、あくまで一例であり、その用途によって適宜構成を変更することができる。

## 【0126】

本発明のマイクロプロセッサ 1500 は、絶縁性表面を有する基板上に接合された結晶方位が一定の単結晶半導体層を用いて集積回路を形成しているため、処理速度の高速化、低消費電力化を実現できる。さらに、本発明の半導体基板を用いて作製されたマイクロプロセッサ 1500 では、単結晶半導体層の表面と裏面にレーザー光を照射して、単結晶半導体層の結晶性や活性化率等を均一にしている。これにより、半導体素子の特性が向上するため、非常に高性能且つ信頼性の高いマイクロプロセッサを提供することができる。

## 【0127】

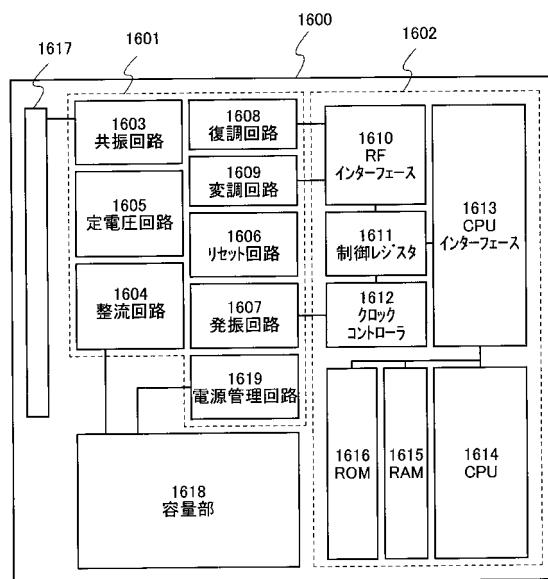

次に、非接触でデータの送受信を行うことのできる演算機能を備えた半導体装置の一例について図 16 を参照して説明する。図 16 は無線通信により外部装置と信号の送受信を行って動作する無線タグの一例である。なお、本発明の無線タグは内部に中央処理装置 (CPU) を有しており、いわば小型のコンピュータである。無線タグ 1600 は、アナログ回路部 1601 とデジタル回路部 1602 を有している。アナログ回路部 1601 として、共振容量を有する共振回路 1603、整流回路 1604、定電圧回路 1605、リセット回路 1606、発振回路 1607、復調回路 1608、変調回路 1609 を有している。デジタル回路部 1602 は、RFインターフェース 1610、制御レジスタ 1611、クロックコントローラ 1612、インターフェース 1613、中央処理装置 1614、ランダムアクセスメモリ 1615、読み出し専用メモリ 1616 を有している。

## 【0128】

このような構成の無線タグ 1600 の動作は概略以下の通りである。アンテナ 1617 が信号を受信すると、共振回路 1603 により誘導起電力が発生する。誘導起電力は、整流回路 1604 を経て容量部 1618 に充電される。この容量部 1618 はセラミックコンデンサーや電気二重層コンデンサーなどのキャパシタで形成されていることが好ましい。容量部 1618 は無線タグ 1600 と一緒に形成されていても良いし、別の部品として無線タグ 1600 を構成する絶縁性表面を有する基板に取り付けられていても良い。

## 【0129】

リセット回路 1606 は、デジタル回路部 1602 をリセットし初期化する信号を生成する。例えば、電源電圧の上昇に遅延して立ち上がる信号をリセット信号として生成する。発振回路 1607 は、定電圧回路 1605 により生成される制御信号に応じて、クロック信号の周波数とデューティー比を変更する。ローパスフィルタで形成される復調回路 1608 は、例えば振幅変調 (ASK) 方式の受信信号の振幅の変動を二値化する。変調回路 1609 は、振幅変調 (ASK) 方式の送信信号の振幅を変動させて送信する。変調回路 1609 は、共振回路 1603 の共振点を変化させることにより通信信号の振幅を変化させている。クロックコントローラ 1612 は、電源電圧又は中央処理装置 1614 における消費電流に応じてクロック信号の周波数とデューティー比を変更するための制御信号を生成している。電源電圧の監視は電源管理回路 1619 が行っている。

## 【0130】

アンテナ 1617 から無線タグ 1600 に入力された信号は復調回路 1608 で復調された後、RFインターフェース 1610 で制御コマンドやデータなどに分けられる。制御コマンドは制御レジスタ 1611 に格納される。制御コマンドには、読み出し専用メモリ 1616 に記憶されているデータの読み出し、ランダムアクセスメモリ 1615 へのデー

10

20

30

30

40

50

タの書き込み、中央処理装置 1614 への演算命令などが含まれている。中央処理装置 1614 は、インターフェース 1613 を介して読み出し専用メモリ 1616、ランダムアクセスメモリ 1615、制御レジスタ 1611 にアクセスする。インターフェース 1613 は、中央処理装置 1614 が要求するアドレスより、読み出し専用メモリ 1616、ランダムアクセスメモリ 1615、制御レジスタ 1611 のいずれかに対するアクセス信号を生成する機能を有している。

#### 【0131】

中央処理装置 1614 の演算方式は、読み出し専用メモリ 1616 に OS (オペレーティングシステム) を記憶させておき、起動とともにプログラムを読み出し実行する方式を採用することができる。また、演算回路を構成して、演算処理をハードウェア的に処理する方式を採用することもできる。ハードウェアとソフトウェアを併用する方式では、専用の演算回路で一部の処理を行い、残りの演算を、プログラムを用いて中央処理装置 1614 が実行する方式を適用することができる。

10

#### 【0132】

本発明の無線タグ 1600 は、絶縁性表面を有する基板上に接合された結晶方位が一定の単結晶半導体層を用いて集積回路を形成しているため、処理速度の高速化、低消費電力化を実現できる。さらに、本発明の半導体基板を用いて作製された無線タグ 1600 では、単結晶半導体層を積層することにより、高度の集積化を実現している。これにより、高性能な半導体素子の面積を低減することができるため、高性能かつ小型の無線タグを提供することができる。

20

#### 【0133】

本実施の形態は、実施の形態 1 乃至 3 と適宜組み合わせて用いることができる。

#### 【0134】

##### (実施の形態 5)

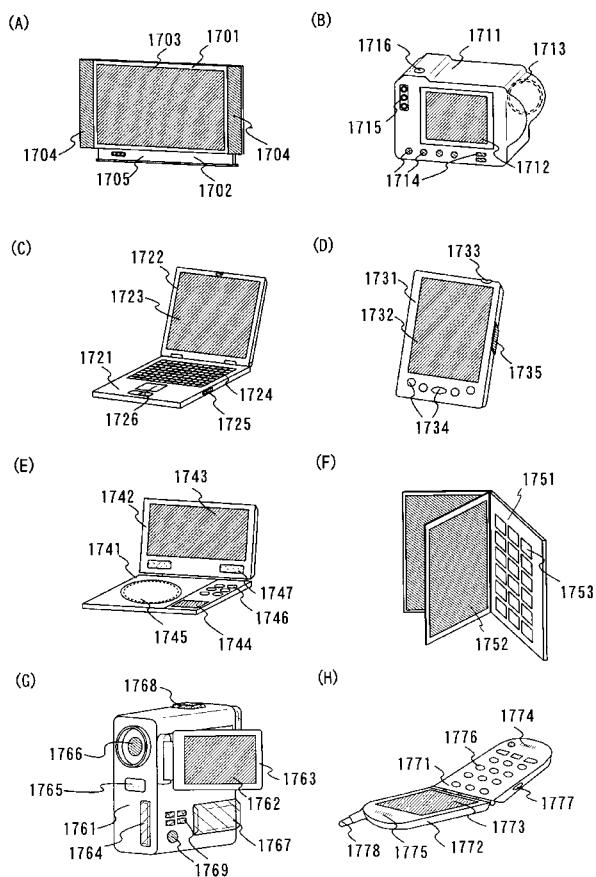

本実施の形態では、本発明の半導体装置、特に表示装置を用いた電子機器について、図 17 を参照して説明する。

#### 【0135】

本発明の半導体装置を用いて作製される電子機器として、ビデオカメラ、デジタルカメラ等のカメラ、ゴーグル型ディスプレイ (ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置 (カーオーディオコンポ等)、コンピュータ、ゲーム機器、携帯情報端末 (モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置 (具体的には Digital Versatile Disc (DVD) 等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置) などが挙げられる。

30

#### 【0136】

図 17 (A) はテレビ受像器又はパーソナルコンピュータのモニタである。筐体 1701、支持台 1702、表示部 1703、スピーカー部 1704、ビデオ入力端子 1705 等を含む。表示部 1703 には、本発明の半導体装置が用いられている。本発明により、高性能且つ高信頼性のテレビ受像器又はパーソナルコンピュータのモニタを提供することができる。

40

#### 【0137】

図 17 (B) はデジタルカメラである。本体 1711 の正面部分には受像部 1713 が設けられており、本体 1711 の上面部分にはシャッター ボタン 1716 が設けられている。また、本体 1711 の背面部分には、表示部 1712、操作キー 1714、及び外部接続ポート 1715 が設けられている。表示部 1712 には、本発明の半導体装置が用いられている。本発明により、高性能且つ高信頼性のデジタルカメラを提供することができる。

#### 【0138】

図 17 (C) はノート型パーソナルコンピュータである。本体 1721 には、キーボード 1724、外部接続ポート 1725、ポインティングデバイス 1726 が設けられてい

50

る。また、本体 1721 には、表示部 1723 を有する筐体 1722 が取り付けられている。表示部 1723 には、本発明の半導体装置が用いられている。本発明により、高性能且つ高信頼性のノート型パーソナルコンピュータを提供することができる。

#### 【0139】

図 17 (D) はモバイルコンピュータであり、本体 1731、表示部 1732、スイッチ 1733、操作キー 1734、赤外線ポート 1735 等を含む。表示部 1732 にはアクティブマトリクス表示装置が設けられている。表示部 1732 には、本発明の半導体装置が用いられている。本発明により、高性能且つ高信頼性のモバイルコンピュータを提供することができる。

#### 【0140】

図 17 (E) は画像再生装置である。本体 1741 には、表示部 1744、記録媒体読み込み部 1745 及び操作キー 1746 が設けられている。また、本体 1741 には、スピーカー部 1747 及び表示部 1743 それぞれを有する筐体 1742 が取り付けられている。表示部 1743 及び表示部 1744 それぞれには、本発明の半導体装置が用いられている。本発明により、高性能且つ高信頼性の画像再生装置を提供することができる。

#### 【0141】

図 17 (F) は電子書籍である。本体 1751 には操作キー 1753 が設けられている。また、本体 1751 には複数の表示部 1752 が取り付けられている。表示部 1752 には、本発明の半導体装置が用いられている。本発明により、高性能且つ高信頼性の電子書籍を提供することができる。

#### 【0142】

図 17 (G) はビデオカメラであり、本体 1761 には外部接続ポート 1764、リモコン受信部 1765、受像部 1766、バッテリー 1767、音声入力部 1768、操作キー 1769 が設けられている、また、本体 1761 には、表示部 1762 を有する筐体 1763 が取り付けられている。表示部 1762 には、本発明の半導体装置が用いられている。本発明により、高性能且つ高信頼性のビデオカメラを提供することができる。

#### 【0143】

図 17 (H) は携帯電話であり、本体 1771、筐体 1772、表示部 1773、音声入力部 1774、音声出力部 1775、操作キー 1776、外部接続ポート 1777、アンテナ 1778 等を含む。表示部 1773 には、本発明の半導体装置が用いられている。本発明により、高性能且つ高信頼性の携帯電話を提供することができる。

#### 【0144】

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器に用いることが可能である。なお、本実施の形態は、実施の形態 1 乃至 4 と適宜組み合わせて用いることができる。

#### 【0145】

##### (実施の形態 6)

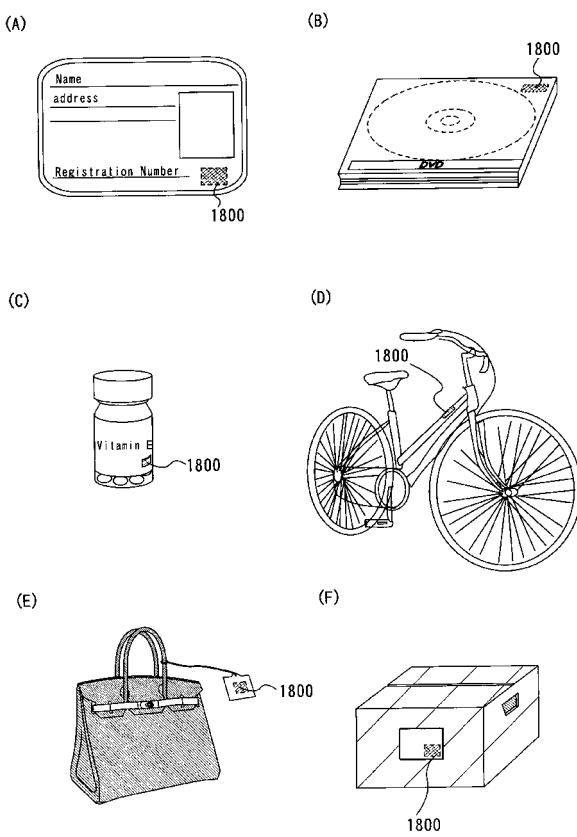

本実施の形態では、本発明の半導体装置、特に無線タグの用途について、図 18 を参照して説明する。

#### 【0146】

本発明により無線タグとして機能する半導体装置を形成することができる。無線タグの用途は多岐にわたるが、例えば、紙幣、硬貨、有価証券類、無記名債券類、証書類（運転免許証や住民票等、図 18 (A) 参照）、包装用容器類（包装紙やボトル等、図 18 (C) 参照）、記録媒体（DVD ソフトやビデオテープ等、図 18 (B) 参照）、乗物類（自転車等、図 18 (D) 参照）、身の回り品（鞄や眼鏡等）、食品類、植物類、衣類、生活用品類、電子機器等の商品や荷物の荷札（図 18 (E)、(F) 参照）等の物品に設けて使用することができる。なお、図 18 において、無線タグは 1800 で示すものである。

#### 【0147】

なお、電子機器とは、例えば、液晶表示装置、EL 表示装置、テレビジョン装置（単にテレビ、テレビ受像機、テレビジョン受像機とも呼ぶ）、携帯電話の他、実施の形態 5 に

て示した物品等を指す。また、上記半導体装置を、動物類、人体等に用いることもできる。

#### 【0148】

無線タグは、物品の表面に貼ったり、物品に埋め込んだりして、物品に固定される。例えば、本であれば紙に埋め込み、有機樹脂からなる包装用容器等であれば当該有機樹脂に埋め込むとよい。紙幣、硬貨、有価証券類、無記名債券類、証書類等にRFIDタグを設けることにより、偽造を防止することができる。また、包装用容器類、記録媒体、身の回り品、食品類、衣類、生活用品類、電子機器等にRFIDタグを設けることにより、検品システムやレンタル店のシステムなどの効率化を図ることができる。本発明により作製することが可能な無線タグは、高い性能且つ信頼性を有しており、さまざまな物品に対して適用することができる。

10

#### 【0149】

本発明により形成することができる無線タグを、物の管理や流通のシステムに応用することで、システムの高機能化を図ることができる。例えば、荷札に設けられるRFIDタグに記録された情報を、ベルトコンベアの脇に設けられたリーダライタで読み取ることにより、流通過程及び配達先等の情報が読み出され、商品の検品や荷物の分配を容易に行うことができる。

20

#### 【0150】

以上の様に、本発明の適用範囲は極めて広く、あらゆる物品に対して用いることが可能である。なお、本実施の形態は、実施の形態1乃至5と適宜組み合わせて用いることができる。

20

#### 【図面の簡単な説明】

#### 【0151】

【図1】本発明の半導体装置の一例を示す図である。

30

【図2】本発明の半導体装置の作製工程を示す図である。

【図3】本発明の半導体装置の作製工程を示す図である。

【図4】本発明の半導体装置の作製工程を示す図である。

【図5】本発明の半導体装置の作製工程を示す図である。

【図6】本発明の半導体装置の作製工程を示す図である。

【図7】本発明の半導体装置の作製工程を示す図である。

【図8】本発明の半導体装置の作製工程を示す図である。

【図9】本発明の半導体装置の作製工程を示す図である。

【図10】本発明の半導体装置の作製工程を示す図である。

【図11】本発明の半導体装置の作製工程を示す図である。

【図12】本発明の半導体装置の作製工程を示す図である。

【図13】本発明の半導体装置の作製工程を示す図である。

【図14】本発明の半導体装置の一例を示す図である。

【図15】本発明の半導体装置の一例を示す図である。

【図16】本発明の半導体装置の一例を示す図である。

40

【図17】本発明の半導体装置を用いた電子機器を示す図である。

【図18】本発明の半導体装置の用途を示す図である。

【図19】本発明の半導体装置の一例を示す図である。

#### 【符号の説明】

#### 【0152】

100 単結晶半導体層

102 単結晶半導体層

104 絶縁層

106 導電層

108 パワートランジスタ

110 絶縁層

50

|       |               |    |

|-------|---------------|----|

| 1 1 2 | トランジスタ        |    |

| 1 1 4 | ソース電極又はドレイン電極 |    |

| 1 1 6 | ソース電極又はドレイン電極 |    |

| 1 1 8 | ソース電極又はドレイン電極 |    |

| 2 0 0 | 単結晶半導体基板      |    |

| 2 0 2 | 損傷領域          |    |

| 2 0 4 | 単結晶半導体層       |    |

| 2 0 6 | 基板            |    |

| 2 0 8 | 接合層           |    |

| 2 1 0 | 単結晶半導体層       | 10 |

| 2 1 2 | 絶縁層           |    |

| 2 1 4 | 導電層           |    |

| 2 1 6 | 不純物領域         |    |

| 2 1 8 | チャネル形成領域      |    |

| 2 2 0 | 絶縁層           |    |

| 2 2 2 | 接合層           |    |

| 2 2 4 | 単結晶半導体基板      |    |

| 2 2 6 | 損傷領域          |    |

| 2 2 8 | 単結晶半導体層       |    |

| 2 3 0 | 単結晶半導体層       | 20 |

| 2 3 2 | マスク           |    |

| 2 3 4 | 不純物領域         |    |

| 2 3 6 | チャネル形成領域      |    |

| 2 3 8 | 絶縁層           |    |

| 2 4 0 | ソース電極又はドレイン電極 |    |

| 2 4 2 | ソース電極又はドレイン電極 |    |

| 2 4 4 | ソース電極又はドレイン電極 |    |

| 2 4 6 | 相補型回路         |    |

| 8 0 0 | 単結晶半導体基板      |    |

| 8 0 2 | 損傷領域          | 30 |

| 8 0 4 | 単結晶半導体層       |    |

| 8 0 6 | 接合層           |    |

| 8 0 8 | 基板            |    |

| 8 1 0 | 単結晶半導体層       |    |

| 8 1 2 | 絶縁層           |    |

| 8 1 4 | 導電層           |    |

| 8 1 6 | 不純物領域         |    |

| 8 1 8 | チャネル形成領域      |    |

| 8 2 0 | 絶縁層           |    |

| 8 2 2 | 単結晶半導体基板      | 40 |

| 8 2 4 | 損傷領域          |    |

| 8 2 6 | 単結晶半導体層       |    |

| 8 2 8 | 接合層           |    |

| 8 3 0 | 単結晶半導体層       |    |

| 8 3 2 | マスク           |    |

| 8 3 4 | 不純物領域         |    |

| 8 3 6 | チャネル形成領域      |    |

| 8 3 8 | 絶縁層           |    |

| 8 4 0 | ソース電極又はドレイン電極 |    |

| 8 4 2 | ソース電極又はドレイン電極 | 50 |

8 4 4 ソース電極又はドレイン電極

8 4 6 相補型回路

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図15】

【図16】

【図17】

【図18】

【図19】

---

フロントページの続き

(51) Int.Cl. F I テーマコード(参考)

*H 01 L 21/336 (2006.01) H 01 L 29/78 627D*

F ターム(参考) 5F110 AA04 BB01 BB04 BB11 CC02 DD01 DD02 DD03 DD04 DD11

EE02 EE03 EE04 EE06 EE09 EE14 EE29 EE43 EE44 EE45

FF02 FF03 FF04 FF09 FF28 FF29 GG02 GG03 GG04 GG12

GG30 GG32 GG34 HJ01 HJ04 HJ12 HJ23 HK01 HK02 HK03

HK04 HK05 HK06 HK09 HK25 HM15 NN02 NN22 NN23 NN24

NN27 NN33 NN34 NN35 NN36 NN72 NN78 QQ11 QQ17 QQ19