(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7536541号**

**(P7536541)**

(45)発行日 令和6年8月20日(2024.8.20)

(24)登録日 令和6年8月9日(2024.8.9)

(51)国際特許分類

F I

|         |                  |         |        |

|---------|------------------|---------|--------|

| H 0 4 N | 25/771 (2023.01) | H 0 4 N | 25/771 |

| H 0 4 N | 23/54 (2023.01)  | H 0 4 N | 23/54  |

| H 0 4 N | 23/71 (2023.01)  | H 0 4 N | 23/71  |

| H 0 4 N | 23/745 (2023.01) | H 0 4 N | 23/745 |

| H 0 4 N | 25/60 (2023.01)  | H 0 4 N | 25/60  |

請求項の数 13 (全19頁)

|          |                             |

|----------|-----------------------------|

| (21)出願番号 | 特願2020-122346(P2020-122346) |

| (22)出願日  | 令和2年7月16日(2020.7.16)        |

| (65)公開番号 | 特開2022-18906(P2022-18906A)  |

| (43)公開日  | 令和4年1月27日(2022.1.27)        |

| 審査請求日    | 令和5年7月7日(2023.7.7)          |

|          |                                            |

|----------|--------------------------------------------|

| (73)特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74)代理人  | 110003281<br>弁理士法人大塚国際特許事務所                |

| (72)発明者  | 唐橋 文人<br>東京都大田区下丸子3丁目30番2号<br>キヤノン株式会社内    |

| 審査官      | 三沢 岳志                                      |

最終頁に続く

(54)【発明の名称】 撮像装置およびその制御方法

**(57)【特許請求の範囲】****【請求項1】**

撮像素子と、

前記撮像素子の動作を制御する制御手段と、を有する撮像装置であって、

前記撮像素子は複数の画素を有し、

前記複数の画素のそれぞれは、

光電変換手段と、

前記光電変換手段によって得られた電荷を保持する第1の保持手段とを備え、

前記第1の保持手段に保持された電荷を読み出す第1の読み出し経路と、前記光電変換手段によって得られた電荷を前記第1の保持手段を経由せずに読み出す第2の読み出し経路とを有し、

前記制御手段は、

ユーザの指示に基づく撮影に関して前記光電変換手段によって得られた電荷は前記第1の読み出し経路によって読み出し、

情報検出のための画像の撮影に関して前記光電変換手段によって得られた電荷は前記第2の読み出し経路によって読み出し、

前記情報検出のための画像の撮影と、該撮影に関して前記光電変換手段によって得られた電荷の前記第2の読み出し経路による読み出しどと、前記第1の読み出し経路による電荷の読み出し期間中に複数回実行する、

ように前記撮像素子の動作を制御することを特徴とする撮像装置。

**【請求項 2】**

前記ユーザの指示に基づく撮影が連続的に行われ、前記情報検出のための画像の撮影が、前記ユーザの指示に基づく撮影の合間に行われることを特徴とする請求項 1 に記載の撮像装置。

**【請求項 3】**

前記第 1 の読み出し経路による読み出しが所定の周期で行われ、前記制御手段は、前記ユーザの指示に基づく撮影の蓄積期間が予め定められた閾値より大きい場合は、前記所定の周期を延長するように前記撮像素子の動作を制御する、請求項 1 または 2 に記載の撮像装置。

**【請求項 4】**

前記制御手段は、前記第 1 の読み出し経路による読み出しと、前記第 2 の読み出し経路による読み出しどと、並行して実行するように前記撮像素子の動作を制御することを特徴とする請求項 1 から 3 のいずれか 1 項に記載の撮像装置。

**【請求項 5】**

前記制御手段は、前記第 1 の読み出し経路による読み出しと、前記第 2 の読み出し経路による読み出しどと、排他的に実行するように前記撮像素子の動作を制御することを特徴とする請求項 1 から 3 のいずれか 1 項に記載の撮像装置。

**【請求項 6】**

前記制御手段は、前記第 1 の読み出し経路による読み出しにおいて、前記情報検出のための画像の撮影に用いられる画素に対応する画素の電荷を読み出してから、前記第 2 の読み出し経路による読み出しを実行するように前記撮像素子の動作を制御することを特徴とする請求項 5 に記載の撮像装置。

10

**【請求項 7】**

前記複数の画素のそれぞれが、前記光電変換手段によって得られた電荷を保持する第 2 の保持手段をさらに備え、

前記第 2 の読み出し経路による読み出しが、前記第 2 の保持手段に保持された電荷の読み出しである、ことを特徴とする請求項 1 から 6 のいずれか 1 項に記載の撮像装置。

20

**【請求項 8】**

前記情報検出のための画像が、フリッカ光源に関する情報の検出のための画像であることを特徴とする請求項 1 から 7 のいずれか 1 項に記載の撮像装置。

30

**【請求項 9】**

前記フリッカ光源に関する情報が、フリッカ光源の有無およびフリッカ光源の特性を含むことを特徴とする請求項 8 に記載の撮像装置。

**【請求項 10】**

前記フリッカ光源の特性が、フリッカの周期およびピークタイミングの少なくとも 1 つを含むことを特徴とする請求項 9 に記載の撮像装置。

**【請求項 11】**

前記制御手段は、前記フリッカ光源に関する情報に基づいて、フリッカ光源による影響を抑制するように前記ユーザの指示に基づく撮影の条件を設定することを特徴とする請求項 8 から 10 のいずれか 1 項に記載の撮像装置。

40

**【請求項 12】**

前記ユーザの指示に基づく撮影において、前記複数の画素の電荷蓄積期間が共通であることを特徴とする請求項 1 から 11 のいずれか 1 項に記載の撮像装置。

**【請求項 13】**

撮像素子と、

前記撮像素子の動作を制御する制御手段と、を有する撮像装置の制御方法であって、前記撮像素子は複数の画素を有し、

前記複数の画素のそれぞれは、

光電変換手段と、

前記光電変換手段によって得られた電荷を保持する第 1 の保持手段とを備え、

50

前記第1の保持手段に保持された電荷を読み出す第1の読み出し経路と、前記光電変換手段によって得られた電荷を前記第1の保持手段を経由せずに読み出す第2の読み出し経路とを有し、

前記制御方法は、

ユーザの指示に基づく撮影に関して前記光電変換手段によって得られた電荷を前記第1の読み出し経路によって読み出すことと、

情報検出のための画像の撮影に関して前記光電変換手段によって得られた電荷を前記第2の読み出し経路によって読み出すことと、を有し

前記情報検出のための画像の撮影と、該撮影に関して前記光電変換手段によって得られた電荷を前記第2の読み出し経路によって読み出すこととが、前記第1の読み出し経路によって読み出すことを行う期間中に複数回実行される、

ことを特徴とする撮像装置の制御方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、撮像装置およびその制御方法に関する。

【背景技術】

【0002】

蛍光灯や一部のLED照明などは、高速に点滅する光源（フリッカ光源）である。そして、フリッカ光源の点滅（フリッカ）が撮影画像に与える影響を抑制するため、シャッタースピードや撮影開始タイミングを調整するフリッカ補正が知られている（特許文献1）。

【先行技術文献】

【特許文献】

【0003】

【文献】特開2019-126014号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

フリッカ補正を行うためにはフリッカ光源の特性（フリッカの周期やピークタイミングなど）を検出する必要がある。フリッカ光源の特性は、経時的に撮影された画像の輝度変化に基づいて検出することができる（フリッカ検出）。しかしながら、連写速度が速くなると、静止画撮影の合間に実行するフリッカ検出用の画像を撮影のための時間が減少するため、静止画の連写中にフリッカ検出を実施することが困難になる。その結果、連写される静止画に対するフリッカ補正の精度が低下する場合がある。

【0005】

本発明の目的は、高速連写時においてもフリッカ検出が可能な撮像装置およびその制御方法を提供することである。

【課題を解決するための手段】

【0006】

上述の目的は、撮像素子と、撮像素子の動作を制御する制御手段と、を有する撮像装置であって、撮像素子は複数の画素を有し、複数の画素のそれぞれは、光電変換手段と、光電変換手段によって得られた電荷を保持する第1の保持手段とを備え、第1の保持手段に保持された電荷を読み出す第1の読み出し経路と、光電変換手段によって得られた電荷を第1の保持手段を経由せずに読み出す第2の読み出し経路とを有し、制御手段は、ユーザの指示に基づく撮影に関して光電変換手段によって得られた電荷は第1の読み出し経路によって読み出し、情報検出のための撮影に関して光電変換手段によって得られた電荷は第2の読み出し経路によって読み出し、情報検出のための画像の撮影と、該撮影に関して光電変換手段によって得られた電荷の第2の読み出し経路による読み出しとを、第1の読み出し経路による電荷の読み出し期間中に複数回実行する、ように撮像素子の動作を制御する、ことを特徴とする撮像装置によって達成される。

10

20

30

40

50

**【発明の効果】****【0007】**

本発明によれば、高速連写時においてもフリッカ検出が可能な撮像装置およびその制御方法を提供することができる。

**【図面の簡単な説明】****【0008】**

【図1】実施形態に係る撮像装置の一例であるデジタルカメラ1000の機能構成例を示すブロック図

**【図2】実施形態に係る撮像装置が用いる像素子の構成例を示す回路図**

10

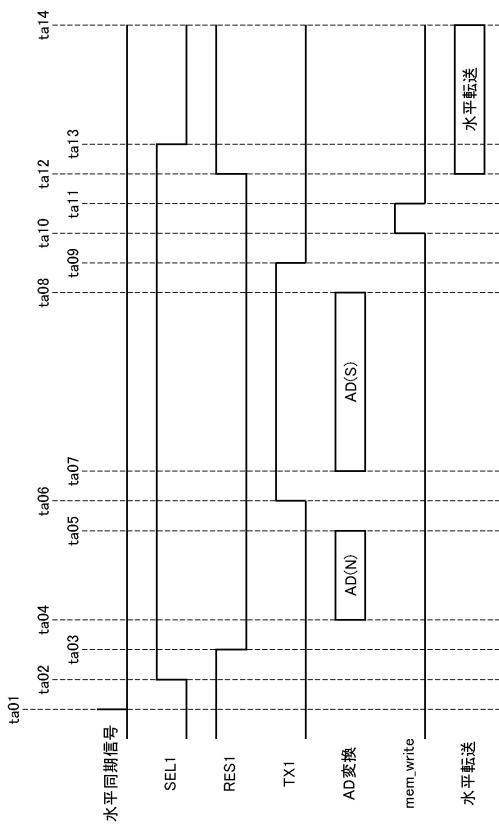

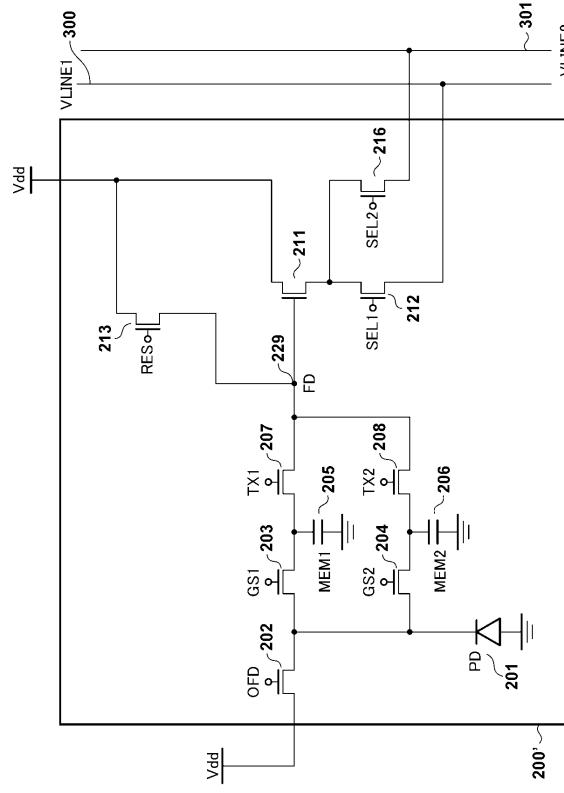

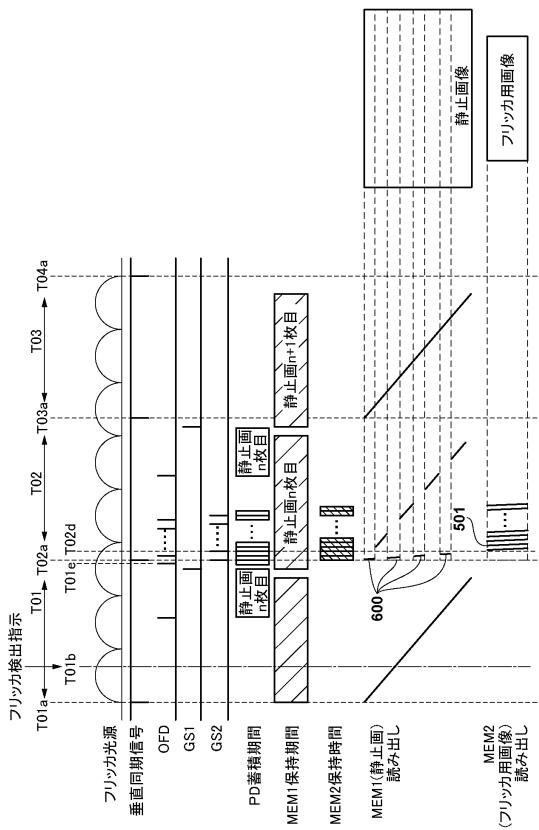

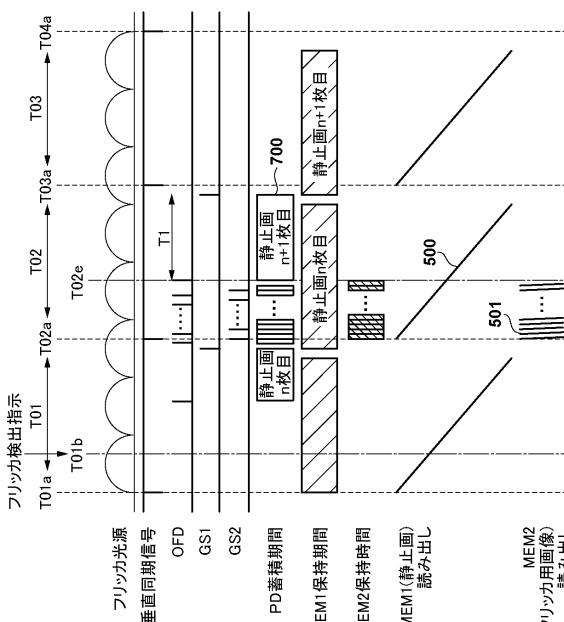

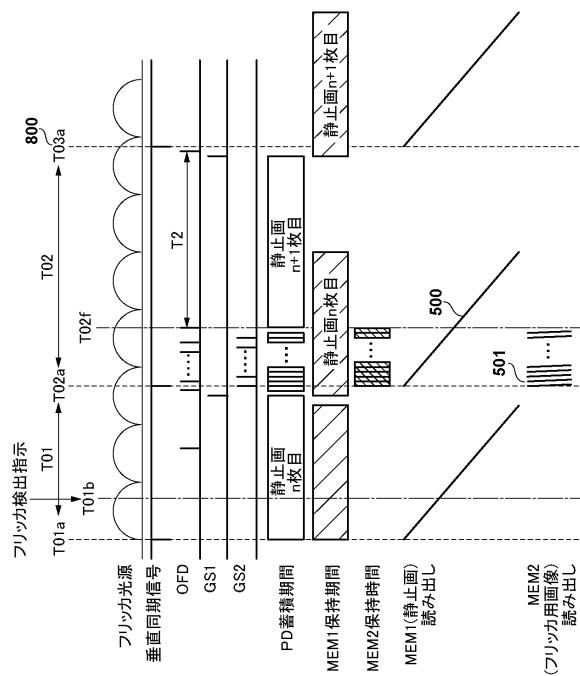

**【図3】図2の像素子が有する画素の構成例を示す回路図****【図4】第1実施形態における静止画連写動作に関する示すタイミングチャート****【図5】第1実施形態における像素子の動作に関するタイミングチャート****【図6】第2実施形態における画素の構成例を示す回路図****【図7】第2実施形態における静止画連写動作に関する示すタイミングチャート****【図8】第3実施形態における静止画連写動作に関する示すタイミングチャート****【図9】第3実施形態における静止画連写動作に関する示すタイミングチャート****【発明を実施するための形態】****【0009】**

以下、添付図面を参照して本発明をその例示的な実施形態に基づいて詳細に説明する。なお、以下の実施形態は特許請求の範囲に係る発明を限定しない。また、実施形態には複数の特徴が記載されているが、その全てが発明に必須のものとは限らず、また、複数の特徴は任意に組み合わせられてもよい。さらに、添付図面においては、同一若しくは同様の構成に同一の参照番号を付し、重複した説明は省略する。

20

**【0010】**

なお、以下の実施形態では、本発明をデジタルカメラで実施する場合について説明する。しかし、本発明は撮像機能を有する任意の電子機器でも実施可能である。このような電子機器には、ビデオカメラ、コンピュータ機器（パソコンコンピュータ、タブレットコンピュータ、メディアプレーヤ、PDAなど）、携帯電話機、スマートフォン、ゲーム機、ロボット、ドローン、ドライブレコーダが含まれる。これらは例示であり、本発明は他の電子機器でも実施可能である。

30

**【0011】****(第1実施形態)**

図1は、第1実施形態におけるデジタルカメラ1000の機能構成例を示すブロック図である。デジタルカメラ1000の撮影光学系120は着脱可能であってもなくてもよい。撮影光学系120は、第1レンズ100、第2レンズ102、第3レンズ103を含む複数のレンズを有する。第2レンズ102および第3レンズ103は撮影光学系120の合焦距離を調節するフォーカスレンズとして機能する。

**【0012】**

第2レンズ102および第3レンズ103の光軸方向の位置は、フォーカス駆動回路115およびフォーカスアクチュエータ116を通じてCPU109によって制御される。絞り101の開口量は絞り駆動回路117および絞りアクチュエータ118を通じてCPU109によって制御される。なお、絞りアクチュエータ118は撮影光学系120に含まれてもよい。

40

**【0013】**

フォーカルプレーンシャッタ104はメカニカルシャッタであり、静止画撮影時の露光時間を調節する。フォーカルプレーンシャッタ104の動作はシャッタ駆動回路114を通じてCPU109によって制御される。なお、フォーカルプレーンシャッタ104は必須でなく、像素子106の動作を制御することにより実現される電子シャッタ機能を用いて露光時間を調節してもよい。光学的ローパスフィルタ105は撮影画像に生じる偽色やモアレを低減するために用いることができる。

50

**【 0 0 1 4 】**

撮像素子 106 は、例えば C M O S イメージセンサである。撮像素子 106 は 2 次元的に配列された複数の画素を有する。撮像素子 106 は、撮影光学系 120 が形成する光学像を複数の画素によって電気信号群（アナログ画像信号）に変換する。本実施形態では撮像素子 106 が A / D 変換機能を有し、アナログ画像信号を A / D 変換したデジタル画像信号（画像データ）を出力する。なお、アナログ画像信号の A / D 変換は D S P 107 で行ってもよい。撮像素子 106 の動作は、C P U 109 によって制御される。

**【 0 0 1 5 】**

D S P ( D i g i t a l S i g n a l P r o c e s s o r ) 107 は画像処理回路である。D S P 107 は、撮像素子 106 から読み出される画像データに対して予め定められた画像処理を適用し、各種の信号、データ、情報を生成および／または取得する。10

**【 0 0 1 6 】**

ここで、D S P 107 が適用する画像処理には、例えば、前処理、色補間処理、補正処理、検出処理、データ加工処理、評価値算出処理、特殊効果処理などが含まれる。前処理には、信号増幅、欠陥画素補正などが含まれる。色補間処理は、撮影時に得られない色成分の値を補間する処理であり、デモザイク処理や同時化処理とも呼ばれる。

**【 0 0 1 7 】**

補正処理には、ホワイトバランス調整、階調補正（ガンマ処理）、撮影光学系 120 の光学収差や周辺減光の影響を補正する処理、色を補正する処理などが含まれる。検出処理には、特徴領域（たとえば顔領域や人体領域）やその動きの検出、人物の認識処理、後述するフリッカ検出などが含まれる。20

**【 0 0 1 8 】**

データ加工処理には、合成処理、スケーリング処理、符号化および復号処理、ヘッダ情報生成処理などが含まれる。評価値算出処理には、自動焦点検出（A F）に用いる信号や評価値の生成、自動露出制御（A E）に用いる評価値の算出処理などが含まれる。

**【 0 0 1 9 】**

特殊効果処理には、ぼかしの付加、色調の変更、リライティング処理などが含まれる。なお、これらは D S P 107 が適用可能な画像処理の例示であり、D S P 107 が適用する画像処理を限定するものではない。

**【 0 0 2 0 】**

R A M 108 は、撮像素子 106 から読み出した画像データのバッファメモリ、D S P 107 や C P U 109 の作業用メモリなどとして用いられる。また、R A M 108 は表示部 110 のためのビデオメモリとして用いられてもよい。なお、R A M 108 の代わりに他の記憶装置を用いてもよい。また、R A M 108 の少なくとも一部が、D S P 107 および C P U 109 に含まれてもよい。30

**【 0 0 2 1 】**

C P U 109 は、ハードウェアプロセッサであり、デジタルカメラ 1000 の主制御部として機能する。C P U 109 は、R O M 113 に記憶されたプログラムを R A M 108 にロードして実行することにより、デジタルカメラ 1000 の機能を実現させる。C P U 109 はその動作の一部として、D S P 107 から得られる評価値に基づいて露出条件を決定する A E 処理や、撮影光学系 120 の合焦距離を調整する A F 処理を実行する。40

**【 0 0 2 2 】**

また、C P U 109 は、例えば D S P 107 から得られる輝度情報に基づいて、フリッカ光源の有無やフリッカ光源の特性を検出する。フリッカ光源の特性は例えばフリッカ周期とタイミングである。C P U 109 は検出したフリッカ光源の特性に基づいて撮像素子 106 の動作を制御することにより、撮影で得られる画像に対するフリッカ光源の影響を抑制する。フリッカ光源の有無やフリッカ光源の特性を検出する機能は撮像素子 106 が有してもよい。

**【 0 0 2 3 】**

表示部 110 は、例えば液晶ディスプレイであり、撮影によって得られた画像データ、50

デジタルカメラ 1000 の各種情報、メニュー画面などを表示する。

#### 【0024】

操作部 111 は、ユーザがデジタルカメラ 1000 に各種の指示を入力するために設けられた入力デバイス（ボタン、スイッチ、ダイヤルなど）の総称である。操作部 111 を構成する入力デバイスは、割り当てられた機能に応じた名称を有する。例えば、操作部 111 には、レリーズスイッチ、動画記録スイッチ、撮影モードを選択するための撮影モード選択ダイヤル、メニューボタン、方向キー、決定キーなどが含まれる。

#### 【0025】

レリーズスイッチは静止画記録用のスイッチであり、CPU109 はレリーズスイッチの半押し状態を撮影準備指示、全押し状態を撮影開始指示と認識する。また、CPU109 は、動画記録スイッチが撮影スタンバイ状態で押下されると動画の記録開始指示と認識し、動画の記録中に押下されると記録停止指示と認識する。

10

#### 【0026】

なお、同一の入力デバイスに割り当てられる機能は可変であってよい。また、入力デバイスはタッチディスプレイを用いたソフトウェアボタンもしくはキーであってもよい。また、操作部 111 は、音声入力や視線入力など、非接触な入力方法に対応した入力デバイスを含んでもよい。

#### 【0027】

記録媒体 112 は、撮影で得られた画像データの記録先である。記録媒体 112 は例えば着脱可能な半導体メモリカードであってよい。

20

#### 【0028】

ROM113 は、CPU109 が実行可能な命令を有するプログラム、デジタルカメラ 1000 の設定値、GUI データなどを記憶する。ROM113 は書き換え可能であってよい。

#### 【0029】

シャッタ駆動回路 114 は、CPU109 の制御にしたがい、フォーカルプレーンシャッタ 104 を駆動する。フォーカス駆動回路 115 は、CPU109 の制御にしたがってフォーカスアクチュエータ 116 を制御し、第 2 レンズ 102 および第 3 レンズ 103 を光軸方向の位置を調節する。絞り駆動回路 117 は、CPU109 の制御にしたがって絞りアクチュエータ 118 を制御し、絞り 101 の開口量を調節する。

30

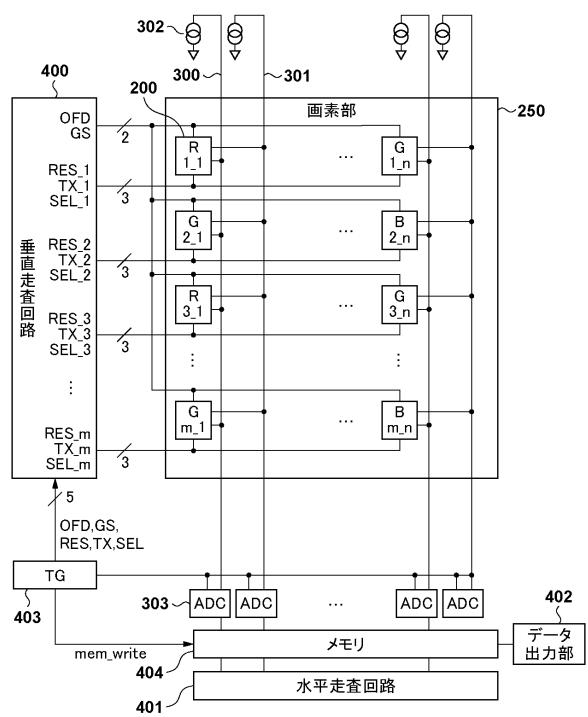

#### 【0030】

図 2 は、撮像素子 106 の回路構成例を示す図である。画素部 250（画素アレイとも呼ばれる）には、複数の画素 200 が行列状に配置されている。図 2 では、画素 200 が m 行 n 列（m, n は 2 以上の整数）に配列されている。また、画素 200 には赤（R）、青（B）、緑（G）のいずれか 1 色のカラーフィルタが、原色ベイヤ配列にしたがって設けられている。図 2 において、画素 200 ごとに記載されている R, G, B は設けられているカラーフィルタの色を示している。また、i\_j (1\_i\_m, 1\_j\_n) は画素座標（第 i 行第 j 列）を示している。例えば、R3\_1 と記載された画素 200 は、赤のカラーフィルタが設けられ、第 3 行第 1 列に位置する。

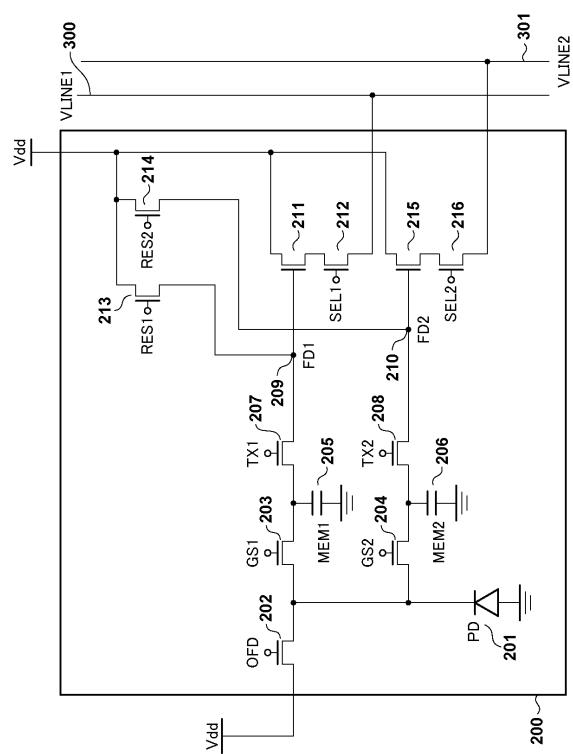

#### 【0031】

図 3 は、画素 200 の構成例を示す回路図である。第 1 実施形態では、画素 200 が 1 つの光電変換手段（フォトダイオード（PD））と、2 つの電荷保持部を有する。PD201 は、画素 200 に入射した光量に応じた電荷を生成する。生成された電荷は、2 つの電荷保持部である MEM1\_205, MEM2\_206 に転送可能である。各トランジスタ（スイッチ）は、N チャンネルであり、ゲートにハイレベルの信号が入力されるとオンし、導通状態になるものとする。

40

#### 【0032】

駆動信号 GS1 がハイレベルになり、転送ゲート 203 がオンになると、PD201 で生成された電荷は MEM1\_205 に転送される。そして、駆動信号 TX1 がハイレベルになり、転送ゲート 207 がオンになると、MEM1\_205 に保持されている電荷が第

50

1 フローティングディフュージョン ( F D 1 \_ 2 0 9 ) に転送される。

#### 【 0 0 3 3 】

以下、 P D 2 0 1 から M E M 1 \_ 2 0 5 、 F D 1 \_ 2 0 9 、 増幅 M O S トランジスタ 2 1 1 、 画素選択スイッチ 2 1 2 を経由して列出力線 V L I N E 1 \_ 3 0 0 に至る経路を第 1 の読み出し経路と呼ぶ。

#### 【 0 0 3 4 】

F D 1 \_ 2 0 9 は増幅 M O S トランジスタ 2 1 1 のゲートに接続されている。増幅 M O S トランジスタ 2 1 1 は、 M E M 1 \_ 2 0 5 から F D 1 \_ 2 0 9 に転送された電荷量に応じた電圧を出力する。したがって、 F D 1 \_ 2 0 9 および増幅 M O S トランジスタ 2 1 1 は電荷を電圧に変換する回路である。

10

#### 【 0 0 3 5 】

駆動信号 G S 2 がハイレベルになり、転送ゲート 2 0 4 がオンになると、 P D 2 0 1 で生成された電荷は M E M 2 \_ 2 0 6 に転送される。そして、駆動信号 T X 2 がハイレベルになり、転送ゲート 2 0 8 がオンになると、 M E M 2 \_ 2 0 6 に保持されている電荷が第 2 フローティングディフュージョン ( F D 2 \_ 2 1 0 ) に転送される。

#### 【 0 0 3 6 】

以下、 P D 2 0 1 から M E M 2 \_ 2 0 6 、 F D 2 \_ 2 1 0 、 増幅 M O S トランジスタ 2 1 5 を経由して V L I N E 2 \_ 3 0 1 に至る経路を第 2 の読み出し経路と呼ぶ。なお、第 2 の読み出し経路に M E M 2 \_ 2 0 6 はなくてもよい。

20

#### 【 0 0 3 7 】

F D 2 \_ 2 1 0 は増幅 M O S トランジスタ 2 1 5 のゲートに接続されている。増幅 M O S トランジスタ 2 1 5 は、 M E M 2 \_ 2 0 6 から F D 2 \_ 2 1 0 に転送された電荷量に応じた電圧を出力する。したがって、 F D 2 \_ 2 1 0 および増幅 M O S トランジスタ 2 1 5 は電荷を電圧に変換する回路である。

#### 【 0 0 3 8 】

リセットスイッチ 2 0 2 は、 P D 2 0 1 と V d d ( 電源電圧 ) とに接続され、ゲートに入力される駆動信号 O F D がハイレベルになるとオンし、 P D 2 0 1 を V d d でリセットする。

#### 【 0 0 3 9 】

第 1 の読み出し経路に関してさらに説明する。リセットスイッチ 2 1 3 は、 F D 1 \_ 2 0 9 と V d d とに接続され、ゲートに入力される駆動信号 R E S 1 がハイレベルになるとオンし、 F D 1 \_ 2 0 9 を V d d でリセットする。また、駆動信号 R E S 1 に加え、転送ゲート 2 0 7 のゲートに入力される駆動信号 T X 1 がハイレベルになると、リセットスイッチ 2 1 3 と転送ゲート 2 0 7 の両方がオンし、 F D 1 \_ 2 0 9 経由で M E M 1 \_ 2 0 5 が V d d でリセットされる。

30

#### 【 0 0 4 0 】

画素選択スイッチ 2 1 2 は、ゲートに入力される駆動信号 S E L 1 がハイレベルになるとオンし、増幅 M O S トランジスタ 2 1 1 と列出力線 V L I N E 1 \_ 3 0 0 とを接続する。これにより、 M E M 1 \_ 2 0 5 の電荷量に応じた増幅 M O S トランジスタ 2 1 1 の電圧が、画素信号として列出力線 V L I N E 1 \_ 3 0 0 を通じて出力される。

40

#### 【 0 0 4 1 】

第 2 の読み出し経路に関してさらに説明する。リセットスイッチ 2 1 4 は、 F D 2 \_ 2 1 0 と V d d とに接続され、ゲートに入力される駆動信号 R E S 2 がハイレベルになるとオンし、 F D 2 \_ 2 1 0 を V d d でリセットする。また、駆動信号 R E S 2 に加え、転送ゲート 2 0 8 のゲートに入力される駆動信号 T X 2 がハイレベルになると、リセットスイッチ 2 1 4 と転送ゲート 2 0 8 の両方がオンし、 F D 2 \_ 2 1 0 経由で M E M 2 \_ 2 0 6 が V d d でリセットされる。

#### 【 0 0 4 2 】

画素選択スイッチ 2 1 6 は、ゲートに入力される駆動信号 S E L 2 がハイレベルになるとオンし、増幅 M O S トランジスタ 2 1 5 と列出力線 V L I N E 2 \_ 3 0 1 とを接続する

50

。これにより、MEM2\_206の電荷量に応じた増幅MOSトランジスタ215の電圧が、画素信号として列出力線VLINE2\_301を通じて出力される。

#### 【0043】

図2に戻り、垂直走査回路400は、タイミングジェネレータ(TG)403から出力される駆動信号OFD、GS、RES、TX、SELに基づいて、画素200の駆動信号RES、TX、SEL、OFD、GS等を生成する。駆動信号OFDおよびGSは全画素共通であるが、他の駆動信号は画素行ごとに生成される。画素行ごとに生成される駆動信号については行番号が付してある。

#### 【0044】

同じ画素行に配列された複数の画素200は、共通の駆動信号によって駆動され、画素信号は画素行ごとに列出力線VLINE1\_300またはVLINE2\_301に出力される。なお、図2では、便宜上、同じ種類の駆動信号は1つにまとめて記載してある。例えば、1行目の画素に供給する駆動信号SEL1と駆動信号SEL2は、まとめてSEL\_1と記載してある。

10

#### 【0045】

本実施形態では、リセットスイッチ202の駆動信号OFDと、転送ゲート203、204の駆動信号GS1、GS2は画素部250の画素200すべてに共通するタイミングで供給される。したがって、すべての画素200について、電荷蓄積タイミングは共通である。

20

#### 【0046】

ADC303は、列出力線ごとに設けられ、画素部250から出力される画素信号とノイズ信号との差分をアナログ-デジタル変換し、画素データを出力する。列出力線VLINE1\_300、VLINE2\_301には、それぞれ電流源302が接続されている。

#### 【0047】

メモリ404は、それぞれのADC303が出力する画素データを、タイミングジェネレータ(TG)403から出力される書き込み信号mem\_writeに従って保持する。したがって、メモリ404には画素行単位で画素データが保持される。メモリ404に保持された画素データは、水平走査回路401の走査により、データ出力部402へ順次転送される。データ出力部402は、L V D S (Low Voltage Differential Signaling)等の伝送方式により、撮像素子106の外部へ画素データを出力する。

30

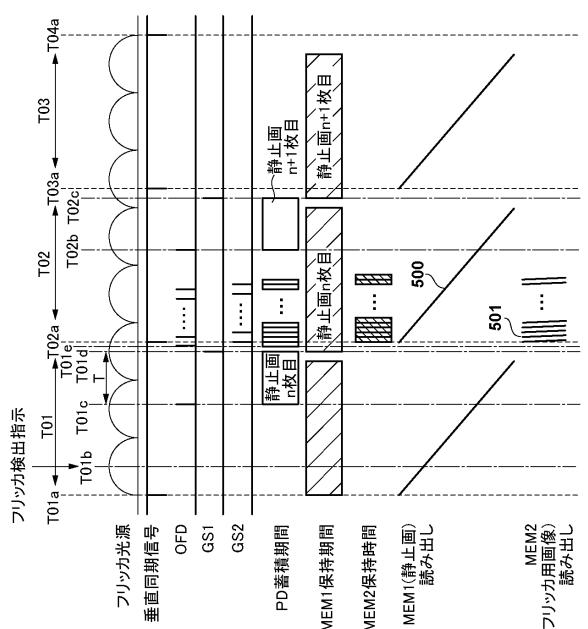

#### 【0048】

次に、デジタルカメラ1000の静止画連写時における撮像素子106の動作制御について、図4に示すタイミングチャートを用いて説明する。ここで、静止画連写は、ユーザの指示に基づく撮影の一例である。

#### 【0049】

デジタルカメラ1000は、例えば操作部111に含まれるレリーズスイッチが全押しされている間、所定の周期(フレーム周期)で静止画を連続的に撮影、記録する。なお、撮影開始のタイミングは露光時間に応じて変動するため、静止画の撮影開始タイミングは撮影ごとに異なり得る。

#### 【0050】

また、操作部111に含まれる動画記録スイッチの押下によって行われる動画撮影も、ユーザの指示に基づく撮影である。以下の説明における静止画撮影を動画フレームの撮影に置き換えることによって、動画撮影時にも同様にフリッカ検出を行うことができる。ユーザの指示に基づく撮影は主に記録を目的とした静止画、動画の撮影ともいえる。

40

#### 【0051】

図4では、時刻T01bで操作部111を通じたユーザ指示を受け付けたことに応じてフリッカ検出を実施するものとしている。しかし、フリッカ検出はユーザの指示なしに実行してもよい。フリッカ検出のために行われる撮影は、主に情報検出を目的とした静止画もしくは動画の撮影といえる。

#### 【0052】

50

なお、図4では撮像素子106の動作に関する説明および理解を容易にするため、フォーカルプレーンシャッタ104や絞り101の駆動といった、静止画撮影に伴って実行される機構部品の制御については記載を省略してある。

#### 【0053】

時刻T01a、T02a、T03a、T04aは静止画撮影によってPD201に蓄積され、MEM1\_205に転送された電荷の読み出しを開始するタイミングを示している。また、期間T01～T03は、静止画の読み出し周期（フレーム周期）である。

#### 【0054】

CPU109は、フレーム周期の終了タイミングと、シャッタースピードとの関係から、PD201のリセットタイミングである時刻T01cを決定する。CPU109は、撮像素子106のタイミングジェネレータ（TG）403に、シャッタースピード（露光時間）とリセットタイミングを設定する。また、CPU109は、フリッカ検出の実行についてもTG403に指示する。

10

#### 【0055】

CPU109は、フリッカ検出の実行指示を、操作部111を通じて指示を受け付けた時点でTG403に通知することができる。あるいはCPU109は、時刻T01cを通知する時点でフリッカ検出することが分かっている場合にはフリッカ検出の実行指示を時刻T01cと併せてTG403に通知してもよい。垂直走査回路400は、CPU109からの設定に基づいて、各種の駆動信号を適切なタイミングで出力する。

20

#### 【0056】

垂直走査回路400は、時刻T01cに駆動信号OFDを所定期間ハイレベルとして、画素部250に含まれるすべての画素200について、PD201をリセットする。これにより、PD201での電荷蓄積が開始される。

#### 【0057】

垂直走査回路400は、時刻T01dで駆動信号GS1を所定時間ハイレベルとし、転送ゲート203をオンにする。時刻T01dは、時刻T01cから時刻T01dの期間がシャッタースピード（蓄積時間）Tとなるように決定される。図4では蓄積時間Tを静止画n枚目の蓄積時間として示している。駆動信号GS1がハイレベルになることで、蓄積時間Tの間にPD201に蓄積された電荷はMEM1\_205に転送される。第1実施形態では静止画撮影に係る電荷をMEM1\_205に転送するものとしたが、MEM2\_206に転送してもよい。

30

#### 【0058】

その後、時刻T01eで垂直走査回路400は、駆動信号OFDを所定期間ハイレベルにして、PD201をリセットする。これにより、PD201ではフリッカ検出用の電荷蓄積を開始する。詳細については後述する。

#### 【0059】

図5を参照して、画素部250の1行目の画素データの読み出し動作について説明する。図4に示した垂直同期信号の1周期の間に周期的に水平同期信号が生成され、画素行ごとに画素データの読み出しが順次行われる。

40

#### 【0060】

図5に示すタイミングチャートにおいて、時刻ta01は図4のT02aと同じタイミングを示している。図5の時刻ta02に、垂直走査回路400は、画素部250の1行目について駆動信号SEL1をハイレベルとして、1行目に配列されたn個の画素200の画素選択スイッチ212をオンする。これにより、増幅MOSトランジスタ211と電流源302によって構成されるソースフォロア回路が動作状態となる。時刻ta02において駆動信号RES1はハイレベルのため、リセットスイッチ213はオンであり、FD1\_209はVddでリセットされている。

#### 【0061】

時刻ta03に垂直走査回路400は、駆動信号RES1をローレベルにして、FD1\_209のリセットを解除する。これにより、列出力線VLINE1\_300には1行目

50

の画素 200 についてのノイズレベルが出力される。

#### 【0062】

次に、時刻  $t_{a04}$  に TG403 は、ADC303 を駆動して AD 変換を開始する。ADC303 は、各画素のノイズレベルを AD 変換する。

時刻  $t_{a05}$  に AD 変換が終了し、各 ADC303 は、AD 変換したノイズレベルを保持する。

#### 【0063】

時刻  $t_{a06}$  に垂直走査回路 400 は、駆動信号 TX1 をハイレベルにし、1 行目の画素 200 の転送ゲート 207 をオンする。

#### 【0064】

そして、各画素 200 の MEM1\_205 に保持されている信号電荷が増幅 MOS トランジスタ 211 によって構成されるソースフォロアのゲートに転送される。ソースフォロアは転送された信号電荷に見合う分だけリセットレベルから変化した電位（信号レベル）を列 output 線 VLINE1\_300 に出力する。

10

#### 【0065】

次に、時刻  $t_{a07}$  に TG403 は、ADC303 を駆動して AD 変換を開始する。ADC303 は、各画素信号のレベルを AD 変換する。

時刻  $t_{a08}$  に AD 変換が終了し、各 ADC303 は、AD 変換した画素信号レベルを保持する。

#### 【0066】

時刻  $t_{a09}$  に垂直走査回路 400 は、駆動信号 TX1 をローレベルにする。そして、時刻  $t_{a10}$  に TG403 が書き込み信号 mem\_writel をハイレベルにする。書き込み信号 mem\_writel がハイレベルになると、ADC303 は、保持している信号レベルとノイズレベルとの差をメモリ 404 に出力する。

20

#### 【0067】

時刻  $t_{a11}$  に TG403 は、書き込み信号 mem\_writel をローレベルにする。これにより、メモリ 404 への画素データの格納が終了する。

時刻  $t_{a12}$  に垂直走査回路 400 は、駆動信号 RES1 をハイレベルにする。また、水平走査回路 401 によってメモリ 404 から画素データの転送（水平転送）を開始する。

#### 【0068】

時刻  $t_{a13}$  に垂直走査回路 400 は、駆動信号 SEL1 をローレベルにする。これにより、画素選択スイッチ 212 がオフし、列 output 線 VLINE1\_300 への画素信号の出力が終了する。

30

時刻  $t_{a14}$  にメモリ 404 から 1 画素行分の画素 200 から得られた画素データの転送が終了すると、1 行目の読み出し動作が終了する。

#### 【0069】

同様の読み出し動作を、2 行目から m 行目まで繰り返すことにより、画素部 250 全体の画素 200 についての画素データ（1 フレーム分の画像データ）の読み出しが完了する。

#### 【0070】

図 4 に戻って、フリッカ検出用の静止画の取得動作について説明する。フリッカ検出用の画像の撮影は、PD201 が静止画連写に使用されない、静止画撮影の合間に行われる。フリッカ検出用の画像を何フレーム撮影するかは、予め定めておくことができる。フリッカの周期は光源を駆動する交流電源の周波数に依存するため、想定されるフリッカの半周期以上の所定期間をカバーするように撮影フレーム数を定めてもよい。なお、撮影フレーム数は他の方法で定めてもよい。

40

#### 【0071】

時刻  $T_{02a}$  で MEM1\_205 から n 枚目の静止画の画素信号の読み出しが開始される。また、垂直走査回路 400 は、駆動信号 GS2 を所定期間ハイレベルにして、転送ゲート 204 をオンにする。これにより、時刻  $T_{01e}$  から時刻  $T_{02a}$  に PD201 で蓄積された電荷が MEM2\_206 に転送される。なお、転送ゲート 207 をオンにするタ

50

イミングを静止画の読み出し開始タイミングと合わせなくてよい。また、上述したように、MEM2\_206は必須でなく、PD201から電荷を直接FD2\_210（増幅MOSトランジスタ215のゲート）に転送してもよい。

#### 【0072】

このように、第1の読み出し経路および第2の読み出し経路の一方をフリッカ検出用の画像の取得に用い、他方を記録用または表示用の静止画や動画の取得に用いる。したがって、静止画の高速連写時のように、1つの読み出し経路がほぼ継続的に占有されるような状況であっても、フリッカ検出用の画像を取得することが可能である。

#### 【0073】

なお、フリッカ検出用の画像は、フリッカ光源の有無や特性（フリッカ周期およびピークタイミング）を検出できればよく、露出が適正であること、高解像度であることよりも、高速に複数フレームを取得できることが優先される。したがって、フリッカ検出用の画像は、露出アンダーおよび／または低解像度の画像であってよい。

#### 【0074】

図4に示す例では、予め定められた所定の複数フレームをフリッカ検出用の画像として取得するため、垂直走査回路400は、駆動信号OFDおよび駆動信号GS2を、それぞれ一定間隔で繰り返し生成する。これにより、フリッカ検出用の画像の露出条件をフレーム間で共通とすることができます。

#### 【0075】

フリッカ検出用画像の画素信号の読み出し501は、列出力線VLINE1\_300を用いたn枚目の静止画の画素信号の読み出し500と並行して列出力線VLINE2\_301を通じて順次行われる。撮像素子106は、読み出し500と501とが並行に実施される期間、メモリ404から静止画の画素データと、フリッカ検出用の画像の画素データとを例えば時分割的に画素行単位で出力する。

#### 【0076】

フリッカ検出用の画像データはDSP107に供給される。DSP107はフリッカ検出用の画像の露出時間と、フレーム間の輝度変化とに基づいて、フリッカ光源の有無を判定する。DSP107は例えばフレーム間の輝度変化が閾値未満である場合にはフリッカ光源が存在しないと判定することができる。

#### 【0077】

DSP107はフリッカ光源が存在すると判定される場合には、例えば同様の平均輝度が得られるフレームの間隔からフリッカ周期を、平均輝度が最大となるフレームの撮影タイミングから、フリッカ光源のピークタイミングを検出することができる。なお、フリッカ光源の有無やフリッカ光源の特性の検出方法はこれらに限らず、公知の任意の方法を用いることができる。

#### 【0078】

DSP107は、フリッカ光源の有無に関する判定結果、およびフリッカ光源の特性に関する検出結果を、フリッカ検出結果としてCPU109に通知する。CPU109は、DSP107から通知されたフリッカ検出結果に基づいて、次の静止画撮影における露出動作を調整することができる。

#### 【0079】

具体的には、CPU109は、DSP107によってフリッカ光源がないと判定された場合には次の静止画撮影の露出動作について変更しない。この場合、予め定められたタイミングおよび露出条件で静止画撮影を実行する。一方、CPU109は、DSP107によってフリッカ光源があると判定され、フリッカの周期およびピークタイミングが検出されている場合、静止画撮影の露出時間や露出開始タイミングを調整することができる。

#### 【0080】

CPU109は例えば、現在設定されている静止画撮影の露出時間がフリッカの1周期より短い場合には、露出期間にフリッカ光源のピークタイミングが含まれるように露出の開始タイミングを調整することができる。なお、露出時間をフリッカの1周期以上となる

10

20

30

40

50

ように調整するなど、他の方法で露出動作を調整して、フリッカが撮影画像に与える影響を低減させてもよい。

#### 【0081】

したがって、時刻  $T_{02b}$  から開始される  $n+1$  枚目の静止画撮影において得られる静止画におけるフリッカ光源の影響を抑制することが可能になる。

#### 【0082】

なお、フリッカ検出用の画像データは、DSP107において評価値の生成など、フリッカ検出以外の用途に用いられてもよい。例えば、フリッカ検出用の画像データから、DSP107はAFやAE用の評価値を算出し、CPU109が評価値を次回の静止画撮影における露出条件や合焦距離の調整に用いてもよい。また、フリッカ検出用の画像データからDSP107で表示用の画像データを生成して、表示部110におけるライブビュー表示などに用いてもよい。

10

#### 【0083】

第1実施形態によれば、画素が有する電荷保持部から記録もしくは表示用の画像信号を読み出している間に、情報検出用の画像信号を取得してフリッカ検出処理を実行するようにした。そのため、記録もしくは表示用の画像が高速で連写される場合であってもフリッカ検出が可能であり、記録もしくは表示用の画像におけるフリッカ光源の影響を適切に抑制することが可能になる。また、記録もしくは表示用の画像の撮影に係る電荷蓄積期間を画素行間で共通とすることにより、ローリングシャッタ歪みが抑制された画像を得ることができる。

20

#### 【0084】

##### (第2実施形態)

次に、本発明の第2実施形態について説明する。第2実施形態は、画素構造において第1実施形態と異なる。第1実施形態の画素200は、第1の読み出し経路と、第2の読み出し経路とでそれぞれ独立したFD1\_209、FD2\_210を有していた(図3)。

#### 【0085】

しかしながら、画素におけるFDの面積とPDの面積はトレードオフの関係にある。そのため、1画素にFDを2つ設けると、1画素にFDを1つ設けた場合よりもPDの面積が減少する。PDの面積が減少すると、単位時間当たりの最大受光量が減少するため、画素のダイナミックレンジが狭くなる。

30

#### 【0086】

第2実施形態では、画素に設けるFDを1つとして、第1の読み出し経路と、第2の読み出し経路で同じFDを共用する構成とすることで、画素のダイナミックレンジを低減させずに第1実施形態と同様の効果を実現する。

#### 【0087】

画素の構成を除き、第2実施形態は第1実施形態と同様の構成を有するデジタルカメラ1000で実施可能である。そのため、以下では第2実施形態における画素の構成について説明したのち、撮像素子106動作制御について説明する。

#### 【0088】

図6は、第2実施形態における撮像素子106の画素部250に配列される画素200'の構成例を示す回路図である。図6において、第1実施形態と同様の構成については図3と同じ参照数字を付して説明を省略する。画素200'は、第1実施形態の画素200が有していたFD2\_210、リセットスイッチ214、増幅MOSトランジスタ215を有していない。また、画素選択スイッチ216が増幅MOSトランジスタ211を列信号線LINE2\_301に選択的に接続する。なお、第2実施形態においても、第2の読み出し経路における電荷保持部MEM2\_206は必須でない。

40

#### 【0089】

第2実施形態では、駆動信号TX1がハイレベルになり、転送ゲート207がオンになると、MEM1\_205に保持されている電荷がFD\_229に転送される。第2実施形態では、PD201からMEM1\_205、FD\_229、増幅MOSトランジスタ21

50

1、画素選択スイッチ 212 を経由して列信号線 VLINE1\_300 に至る経路を第 1 の読み出し経路と呼ぶ。

#### 【0090】

また、駆動信号 TX2 がハイレベルになり、転送ゲート 208 がオンになると、MEM2\_206 に保持されている電荷が FD\_229 に転送される。第 2 実施形態では、PD201 から FD\_229、増幅MOSトランジスタ 211、画素選択スイッチ 216 を経由して列信号線 VLINE2\_301 に至る経路を第 2 の読み出し経路と呼ぶ。

#### 【0091】

第 2 実施形態では 1 つの FD を 2 つの読み出し経路が共用するため、MEM1\_205 の読み出しと MEM2\_206 の読み出しどと並列に実行することができない（並列に読み出しを実行すると、FD209 で電荷が加算されてしまう）。したがって、基本的に MEM1\_205 の読み出しと MEM2\_206 の読み出しどとは排他的に実行する。

10

#### 【0092】

第 2 実施形態における、静止画連写時における撮像素子 106 の動作制御について、図 7 に示すタイミングチャートを用いて説明する。図 7 において、第 1 実施形態と共通する事項については図 4 と同じ参照符号を付してある。

#### 【0093】

第 1 実施形態と同様、時刻 T01a、T02a、T03a、T04a に、MEM1\_205 から静止画の読み出しが開始される。また、T01 ~ T03 は、静止画読み出しの開始周期（フレーム周期）である。

20

#### 【0094】

第 2 実施形態では、フリッカ検出を実行するフレームでは、MEM1\_205 から静止画を読み出す際に、フリッカ検出用の画像データの取得に用いる画素行について先に読み出しを行う。図 7 に示す例では、フリッカ検出用の画像の垂直方向の解像度が、静止画の垂直方向の解像度より低い。したがって、図 7 の 600 で示すように、フリッカ検出用の画像取得に用いられる画素行についてまず先に静止画読み出しを実行する。このような読み出しへは、CPU109 の制御に従って TG403 および垂直走査回路 400 が画素 200' に駆動信号を供給することによって実現することができる。

#### 【0095】

一方、n 枚目の静止画撮影の露光期間終了後、垂直走査回路 400 は、時刻 T01e に駆動信号 OFD を所定期間ハイレベルとして、画素部 250 に含まれるすべての画素 200 について、PD201 をリセットしている。これにより、PD201 でフリッカ検出用の画像の電荷蓄積（撮像）が開始されている。

30

#### 【0096】

垂直走査回路 400 は時刻 T02a に駆動信号 GS2 を所定時間ハイレベルにして、転送ゲート 204 をオンにする。これにより、時刻 T01e から時刻 T02a に PD201 で蓄積された電荷が MEM2\_206 に転送される。

#### 【0097】

時刻 T02d の時点では、MEM1\_205 から、フリッカ検出用の画像に用いる画素行についての静止画読み出しが完了している。そのため、垂直走査回路 400 は MEM2\_206 からのフリッカ検出用の画像の読み出しを、MEM1\_205 からの静止画の読み出しどと時分割的に実行する。

40

#### 【0098】

フリッカ検出用の画像を取得するために用いる画像行については MEM2\_206 から読み出した信号を列出力線 VLINE2\_301 に出力し、それ以外の画素行については MEM1\_205 から読み出した信号を列出力線 VLINE1\_300 に出力する。MEM2\_206 がない場合には、フリッカ検出用の画像を取得するために用いる画像行については PD201 から転送された電荷を蓄積することなく列出力線 VLINE2\_301 に出力する。

#### 【0099】

50

垂直走査回路 400 は、時刻 T02d 以降、このような読み出し制御を行うための駆動信号を画素行ごとに供給する。フリッカ検出用の画像を複数フレーム取得することを優先するため、図 7 に示すように、フリッカ検出用の画像を取得するために用いる画素行の読み出し 501 (MEM2\_206 からの読み出し) だけを繰り返し実行してもよい。この場合、フリッカ検出用の画像データの取得が所定フレーム分完了するまで、MEM1\_205 からの静止画の読み出しが中断される。

#### 【0100】

図 7 では便宜上、フリッカ検出用の画像の読み出し 501 が、静止画の読み出しと時間的に重複しているように見えるが、実際には時刻 T02d 以降の静止画の読み出しとフリッカ検出用の画像の読み出しとは実質的に排他的に実行される。ここで、実質的にとは、既に 600 で示した読み出しによって読み出し済みの画素行に関する MEM1\_205 の読み出しが、MEM2\_206 からのフリッカ検出用の画像の読み出しと並行に実行されてもよいからである。この場合、MEM1\_205 から読み出された信号は FD209 で加算されても MEM2\_206 から読み出された信号に影響を与えない。

10

#### 【0101】

第 2 実施形態によれば、1つの FD を 2 つの読み出し経路で共用するようにすることでき、画素に占める PD の面積を第 1 実施形態よりも大きくすることができる。そのため、静止画の読み出しと並行してフリッカ検出が可能であることに加え、画素のダイナミックレンジを拡げることが可能になる。

20

#### 【0102】

##### (第 3 実施形態)

次に、本発明の第 3 の実施形態について説明する。第 3 実施形態は、静止画撮影の露出時間が長い場合のフリッカ検出動作に関する。第 3 実施形態は第 1 実施形態と同様のデジタルカメラ 1000 を対象とする。

#### 【0103】

第 3 実施形態における、静止画連写時における撮像素子 106 の動作制御について、図 8 および図 9 に示すタイミングチャートを用いて説明する。図 8 および図 9 において、第 1 実施形態と共通する事項については図 4 と同じ参照符号を付してある。

30

#### 【0104】

第 1 実施形態と同様、時刻 T01a、T02a、T03a、T04a に、MEM1\_205 から静止画の読み出しが開始される。また、T01 ~ T03 は、静止画読み出しの開始周期（フレーム周期）である。

#### 【0105】

図 4 では、時刻 T02b から時刻 T02c までの期間を静止画の蓄積時間 T としているが、MEM2\_206 からのフリッカ検出用の画像の読み出し 501 の完了後であれば、静止画撮影の蓄積期間の開始（撮影の開始）が可能である。図 8 は、第 1 実施形態と同じフレーム周期における最大蓄積時間 T1 での静止画撮影を行う場合のタイミングチャートである。また図 9 は、フレーム期間を延長することにより、T1 よりも長い蓄積時間 T2 で静止画撮影を行う場合のタイミングチャートである。

40

#### 【0106】

第 3 実施形態では、

フレーム周期（フリッカ検出用の画像読み出しにかかる時間 + 次の静止画蓄積時間）の場合は図 8 を用いて、

フレーム周期 < (フリッカ検出用の画像読み出しにかかる時間 + 次の静止画蓄積時間) の場合は図 9 を用いて説明する。

#### 【0107】

図 8、図 9 とも、第 1 実施形態（図 4）との差異を分かりやすくするため、時刻 T01b で操作部 111 を通じたユーザ指示を受け付けたことに応じてフリッカ検出を実施するものとしている。しかし、フリッカ検出はユーザの指示なしに実行してもよい。また、動画撮影も連続的に撮影が行われる点において静止画連写と同様である。

50

**【0108】**

$n$  枚目の静止画の撮影完了までの動作は第1実施形態と同一であるため説明を省略する。時刻 T<sub>02a</sub>に、MEM1\_205に保持された、静止画撮影によって得られた電荷の読み出しを開始する。図4および図5を用いて説明したように、MEM1\_205からの電荷の読み出しと並行して、フリッカ検出用の画像の撮影と読み出し S<sub>01</sub>を複数フレーム分繰り返して実行する。

**【0109】**

図8では、フリッカ検出用の画像の読み出しが時刻 T<sub>02e</sub>に完了したものとする。CPU109は、フリッカ検出用の画像の読み出しが完了すると、 $n+1$ 枚目の静止画の撮影 S<sub>00</sub>を開始する。これにより、静止画撮影に係る蓄積時間（シャッタースピード）を  $n$ 枚目の静止画撮影に係る蓄積時間 T よりも長い（遅い）蓄積時間 T<sub>1</sub>とすることができます。なお、蓄積時間 T<sub>1</sub>はフレーム周期を変更することなく実現可能な最大蓄積時間である。蓄積時間 T<sub>1</sub>は、フレーム周期と、フリッカ検出用の画像の1フレームあたりの取得時間（電荷蓄積、電荷転送、および読み出しに要する時間）と、フリッカ検出用の画像のフレーム数に応じて定まる。

10

**【0110】**

T<sub>1</sub>よりも長い蓄積時間 T<sub>2</sub>で静止画を撮影する必要がある場合には、図9に S<sub>00</sub>で示すように、静止画の読み出し開始タイミングである時刻 T<sub>03a</sub>を遅らせる（撮影周期を延長する）。この場合も、時刻 T<sub>03a</sub>の遅延時間をできるだけ少なくするように、静止画撮影の開始タイミングはフリッカ検出用の画像の読み出し完了直後の時刻 T<sub>02f</sub>とする。

20

**【0111】**

CPU109は、例えば A<sub>E</sub>で決定したシャッタースピードもしくはユーザが設定したシャッタースピードが T<sub>1</sub>よりも長い場合には、撮影した静止画の読み出し開始タイミングを遅らせるように TG403 の動作を制御する。この場合、フレーム周期が延びるため、結果として連写速度が低下することになる。

**【0112】**

第3実施形態によれば、第1実施形態の効果に加え、より長いシャッタースピードを許容することにより、より柔軟な静止画撮影に対応することが可能になる。なお、第3実施形態は第2実施形態に基づいて実行することも可能である。

30

**【0113】****（その他の実施形態）**

本発明は、上述の実施形態の1以上の機能を実現するプログラムを、ネットワーク又は記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータにおける1つ以上のプロセッサーがプログラムを読み出し実行する処理でも実現可能である。また、1以上の機能を実現する回路（例えば、ASIC）によっても実現可能である。

**【0114】**

本発明は上述した実施形態の内容に制限されず、発明の精神および範囲から離脱することなく様々な変更及び変形が可能である。したがって、発明の範囲を公にするために請求項を添付する。

40

**【符号の説明】****【0115】**

106...撮像素子、109...CPU、205...電荷保持部、300...第1の列出力線、301...第2の列出力線

50

【図面】

【図 1】

【図 2】

10

20

30

40

【図 3】

【図 4】

50

【図 5】

【図 6】

【図 7】

【図 8】

10

20

30

40

50

【図 9】

10

20

30

40

50

---

フロントページの続き

(56)参考文献      特開2016-189557(JP,A)

特開2020-096212(JP,A)

特開2017-126964(JP,A)

特開2016-034110(JP,A)

特開2019-126014(JP,A)

特開2019-201335(JP,A)

(58)調査した分野 (Int.Cl., DB名)

H04N 25/771

H04N 23/54

H04N 23/71

H04N 23/745

H04N 25/60