(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5949879号

(P5949879)

(45) 発行日 平成28年7月13日(2016.7.13)

(24) 登録日 平成28年6月17日(2016.6.17)

(51) Int.Cl.

F 1

G 1 O H 1/34 (2006.01)

G 1 O H 1/18 (2006.01)G 1 O H 1/34

G 1 O H 1/18 1 O 1

請求項の数 4 (全 22 頁)

(21) 出願番号 特願2014-232343 (P2014-232343)

(22) 出願日 平成26年11月17日 (2014.11.17)

(62) 分割の表示 特願2012-61882 (P2012-61882)

の分割

原出願日 平成24年3月19日 (2012.3.19)

(65) 公開番号 特開2015-64595 (P2015-64595A)

(43) 公開日 平成27年4月9日 (2015.4.9)

審査請求日 平成27年3月13日 (2015.3.13)

(73) 特許権者 000001443

カシオ計算機株式会社

東京都渋谷区本町1丁目6番2号

(72) 発明者 坂田 吾朗

東京都羽村市栄町3丁目2番1号 カシオ

計算機株式会社羽村技術センター内

審査官 千本 潤介

最終頁に続く

(54) 【発明の名称】タッチ検出装置、タッチ検出方法及び電子楽器

## (57) 【特許請求の範囲】

## 【請求項 1】

押鍵操作に応答して順次オンされる第1接点及び第2接点のうち、前記第1接点がオンされてから予め定められたバイアス時間経過後から前記第2接点がオンされるまでのベロシティ時間に対応するカウント値をカウントする第1カウンタと、

前記第2接点がオンされた時点からカウントを開始する第2カウンタと、

前記第2カウンタでカウントされたカウント値が、前記第1カウンタのカウント値に応じて設定された設定値に一致した時に、前記第1カウンタのカウント値に応じたタッチ情報を含み、発音制御部に対して発音を指示する発音情報を送信するコントローラと、

を有することを特徴とするタッチ検出装置。

10

## 【請求項 2】

前記第1カウンタはさらに、前記第1接点がオンされてからカウントを開始し、前記バイアス時間到達時に当該カウントをリセットしてから再度カウントを開始する、請求項1に記載のタッチ検出装置。

## 【請求項 3】

第1カウンタと、第2カウンタと、コントローラとを備えたタッチ検出回路にて用いられるタッチ検出方法であって、

押鍵操作に応答して順次オンされる第1接点及び第2接点のうち、前記第1接点がオンされてから予め定められたバイアス時間経過後から前記第2接点がオンされるまでのベロシティ時間に対応するカウント値を前記第1カウンタでカウントし、

20

前記第2接点がオンされた時点から前記第2カウンタのカウントを開始し、前記コントローラが、前記第2カウンタでカウントされたカウント値が、前記第1カウンタのカウント値に応じて設定された設定値に一致した時に、前記第1カウンタのカウント値に応じたタッチ情報を含み、発音制御部に対して発音を指示する発音情報を送信する、タッチ検出方法。

【請求項4】

請求項1に記載のタッチ検出装置と、複数の鍵と、前記複数の鍵毎に設けられ、押鍵操作に応じて順次オンされるとともに、当該オン検出信号を前記タッチ検出装置に出力する第1接点及び第2接点と、

前記タッチ検出装置から送信された発音情報に基づいて発音するための発音制御を実行する発音制御部と、

を備えたことを特徴とする電子楽器。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、タッチ検出装置、タッチ検出方法及び電子楽器に関する。

【背景技術】

【0002】

従来、電子楽器において再生される音の強弱を示すベロシティ情報は、例えば電子ピアノであれば、次のようにして検出される。即ち、電子ピアノの各鍵下には、鍵の押下量が相互に異なる状態でオンする第1接点と第2接点とが設けられている。電子ピアノは、第1接点と第2接点との各オンタイミングの時間差を計測し、この時間差に基づいてベロシティ情報を検出する。

その後即座に、電子ピアノは、このベロシティ情報に基づいて、音源から発音させる。

このため、電子ピアノの発音開始タイミングは、ベロシティ情報を検出した直後、即ち、ほぼ第2接点のオンタイミングとなる。この第2接点は、鍵の下限よりも幾分上側に設置される。つまり、従来の電子ピアノは、鍵が下限まで押し切られる前に発音が開始される。

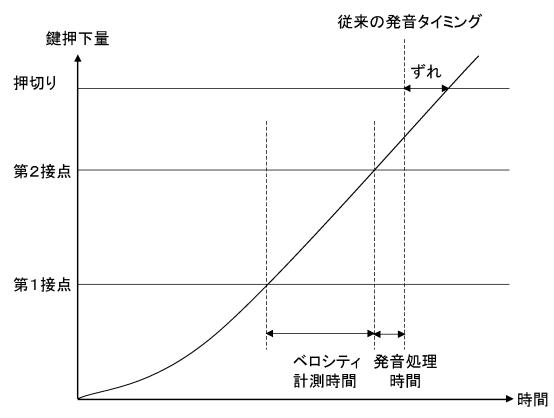

【0003】

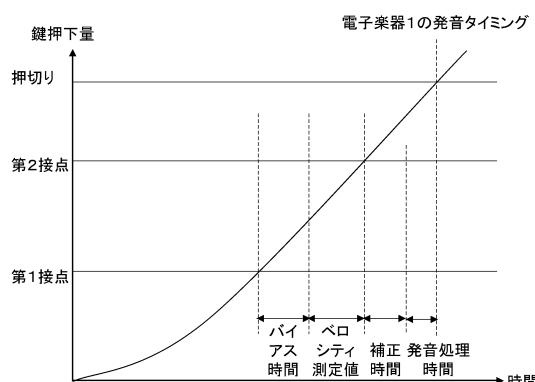

図18は、従来の電子ピアノにおける、押鍵されてから発音されるまでのタイミングを説明する図である。

図18に示すように、従来の電子ピアノは、第2接点がオンとなると発音処理を開始するため、鍵が下限まで押し切られる前に発音されていた。

【0004】

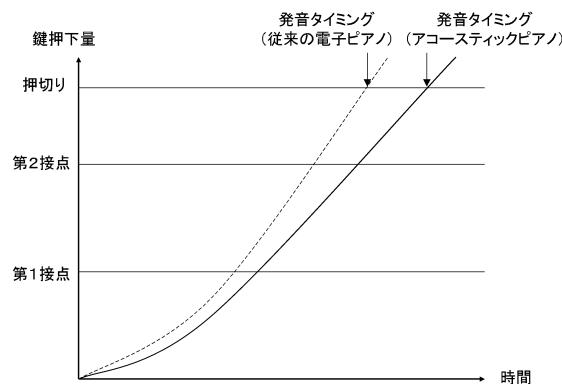

本来、電子ピアノの発音タイミングは、アコースティックピアノの発音タイミングと一致するのが理想である。ところが、アコースティックピアノでは、鍵が押下されると、その動きがアクションに伝達され、ハンマーを動かし、ヘッドが打弦し、その弦振動がピアノのブリッジ、板を通じて発音される。アコースティックピアノにおける、鍵の押下量と発音の関係は、調整されているものの、上記のとおり構造的に複雑である。このため、第2接点のオンタイミングで発音される従来の電子ピアノと、アコースティックピアノとでは構造が異なるため、各々の発音タイミングが異なる。

また、電子ピアノとアコースティックピアノとの発音タイミングの相違は、発音される音の音高、或いは押鍵の強さによっても異なる。

【0005】

更に、従来の電子ピアノにおいては、本体の重量の増加防止、鍵の戻り時間による連打性の維持、複雑なアクション構造による故障回避等の観点から、アコースティックピアノと比べ、静止状態における鍵の重さが軽く、押鍵時における鍵の慣性モーメントが低い。静止状態における鍵の重さは、静止状態から押鍵を開始するときの反力となり、ごく弱い押鍵操作に対して影響を与える。また、鍵の慣性モーメントは、押鍵操作時の反力となり

10

20

30

40

50

、強い押鍵操作に対して影響を与える。

図19は、従来の電子ピアノにおける発音タイミングとアコースティックピアノにおける発音タイミングとの相違を説明する図である。

図19は、電子ピアノとアコースティックピアノにおいて、同じ強さで押鍵した場合における、両者の発音タイミングを示している。

上記のとおり、電子ピアノは、アコースティックピアノと比べ鍵の重さが軽く押鍵時における鍵の慣性モーメントが低いため、アコースティックピアノと同じ強さで押鍵された場合でも、より早く押し切られてしまう。このため、電子ピアノの発音タイミングは、目指すべきアコースティックピアノの発音タイミングより早くなってしまう。

【0006】

10

そこで、特許文献1には、CPU(Central Processing Unit)が実行する時差発音処理により、発音指示情報を検出した後、実際に楽音を生成させるまでの時間を、発音する音の音高情報や音色情報に応じた時間だけ遅延させる電子楽器が開示されている。

また、特許文献2には、CPUが実行する発音タイミング補正処理により、ベロシティと遅延時間とが対応付けられたテーブルを用いて、遅延時間を設定し、当該遅延時間の経過後に発音する電子ピアノが提案されている。

特許文献1の電子楽器や特許文献2の電子ピアノによれば、CPUがソフトウェアによる処理を実行することで、押鍵されてから発音するまでの時間を調整できる。

【先行技術文献】

20

【特許文献】

【0007】

【特許文献1】特開平8-234733号公報

【特許文献2】特開平7-92971号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、近年、電子楽器は、同一タイミングで多くの音を発生させるため、搭載するCPUの処理負担が増大している。このため、特許文献1や2のようにCPUがソフトウェアを実行させることによる処理を単に採用しただけでは、発音タイミングの遅延時間を正確に管理することは困難な状態になっている。

30

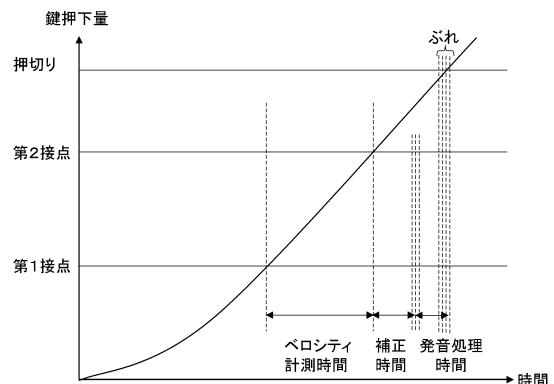

図20は、ソフトウェアによる処理で発音タイミングを遅延させる従来の電子ピアノにおける、押鍵されてから発音されるまでのタイミングを説明する図である。

ソフトウェアによる処理で発音タイミングを遅延させる従来の電子ピアノは、第2接点がオンされてから、発音タイミングを遅延させるための補正時間をカウントし、補正時間経過後に発音する。

ところが、当該電子ピアノのCPUの処理負担は、同一タイミングで発生させる音の数によって増減する。このため、CPUの処理負担の増減により、図20に示すように、補正時間のカウントにぶれが生じ、結果として、発音タイミングもぶれが生じる。この「ぶれ」は、CPUの処理負担の増減により変動するので、演奏者が調整できず、演奏の妨げになる。

40

【0009】

本発明は、このような状況に鑑みてなされたものであり、電子楽器において、同一タイミングで多くの音を発生させる場合でも、各鍵の押鍵に対して正確なタイミングで発音をすることを目的とする。

【課題を解決するための手段】

【0010】

上記目的を達成するため、本発明の一態様のタッチ検出装置は、

押鍵操作に応答して順次オンされる第1接点及び第2接点のうち、前記第1接点がオンされてから予め定められたバイアス時間経過後から前記第2接点がオンされるまでのベロ

50

シティ時間に対応するカウント値をカウントする第1カウンタと、

前記第2接点がオンされた時点からカウントを開始する第2カウンタと、

前記第2カウンタでカウントされたカウント値が、前記第1カウンタのカウント値に応じて設定された設定値に一致した時に、前記第1カウンタのカウント値に応じたタッチ情報を含み、発音制御部に対して発音を指示する発音情報を送信するコントローラと、

を有することを特徴とする。

【発明の効果】

【0011】

本発明によれば、電子楽器において、同じタイミングで多くの音を発生させる場合でも、鍵の押鍵に対して正確なタイミングで発音可能となる。

10

【図面の簡単な説明】

【0012】

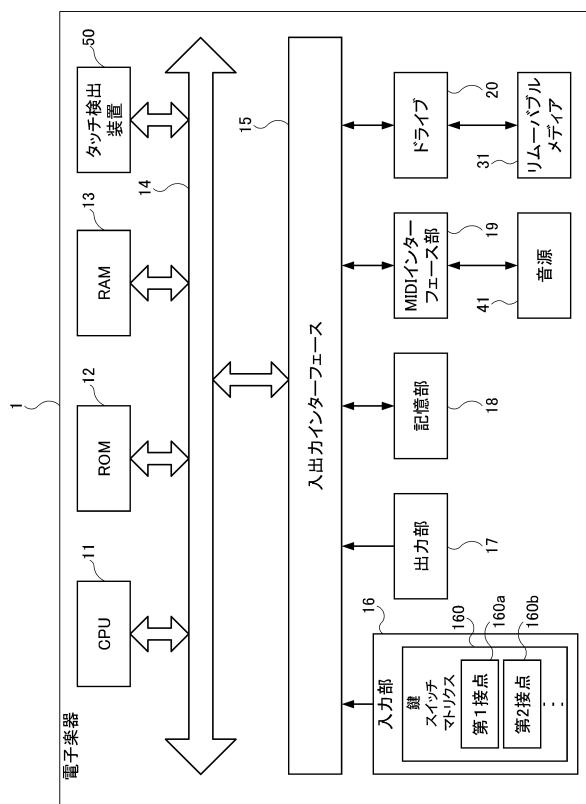

【図1】本発明の実施形態に係るタッチ検出装置が適用された電子楽器のハードウェアの構成を示すブロック図である。

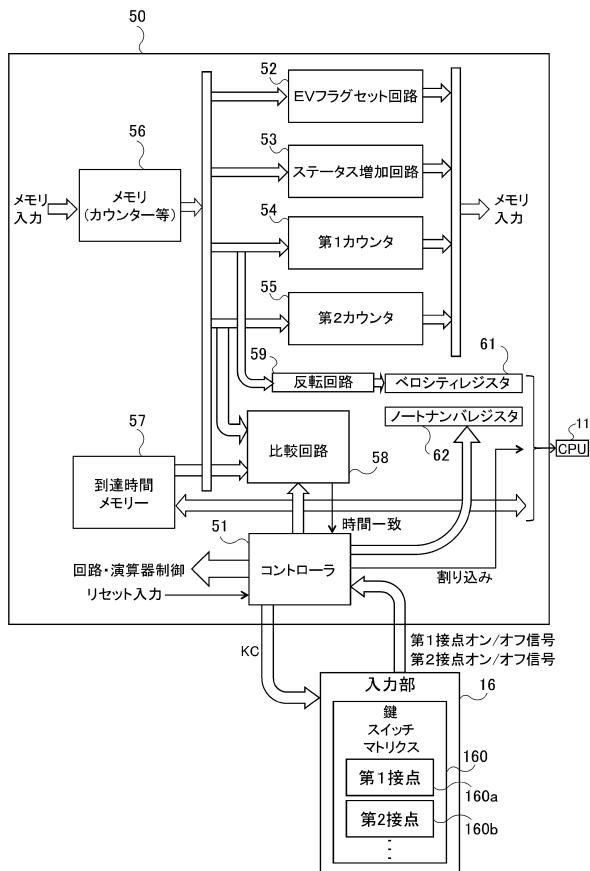

【図2】本発明の実施形態に係るタッチ検出装置のハードウェアの構成を示すブロック図である。

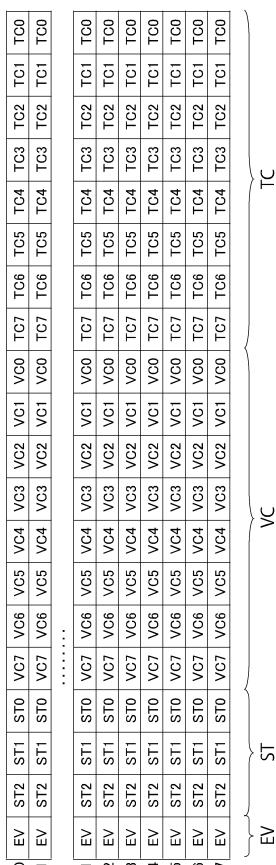

【図3】図2のタッチ検出装置のカウンタメモリのフォーマットを説明する図である。

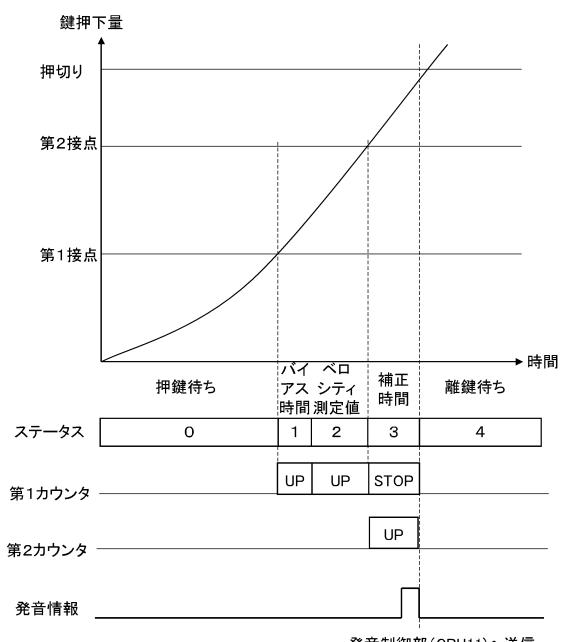

【図4】図2のタッチ検出装置の動作タイミングを説明する図である。

【図5】図2のタッチ検出装置によるタッチ検出動作処理が実行された場合における、押鍵されてから発音されるまでのタイミングを説明する図である。

20

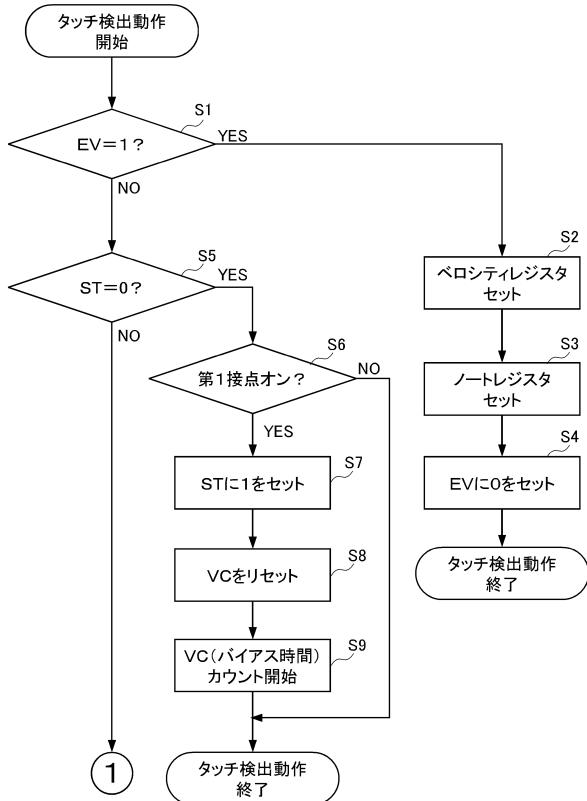

【図6】図2のタッチ検出装置が実行するタッチ検出動作処理の流れを説明するフローチャートである。

【図7】図2のタッチ検出装置が実行するタッチ検出動作処理の流れを説明するフローチャートである。

【図8】図2のタッチ検出装置が実行するタッチ検出動作処理の流れを説明するフローチャートである。

【図9】図2のタッチ検出装置が実行するタッチ検出動作処理の流れを説明するフローチャートである。

【図10】図2のタッチ検出装置が実行するタッチ検出動作処理の流れを説明するフローチャートである。

30

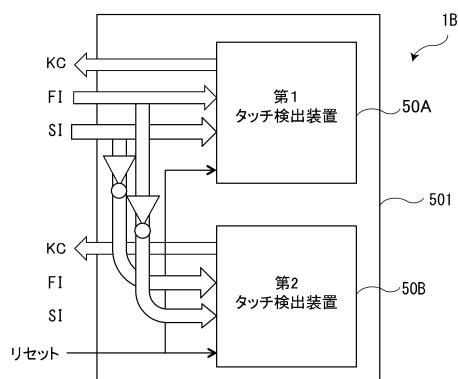

【図11】本発明の実施形態の第1応用例に係るタッチ検出ユニットにおける、第1タッチ検出装置と第2タッチ検出装置との接続を示すブロック図である。

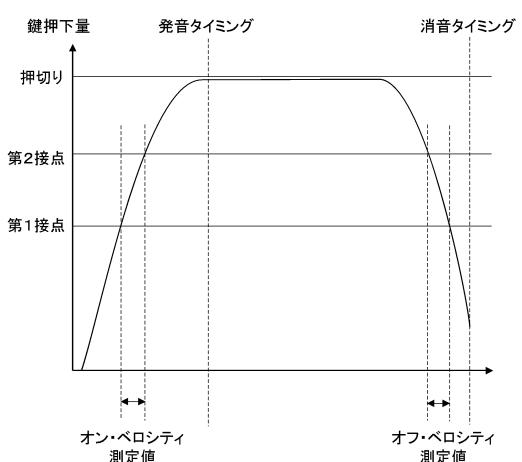

【図12】本発明の実施形態の第1応用例に係るタッチ検出ユニットが適用された電子楽器における、発音及び消音のタイミングを説明する図である。

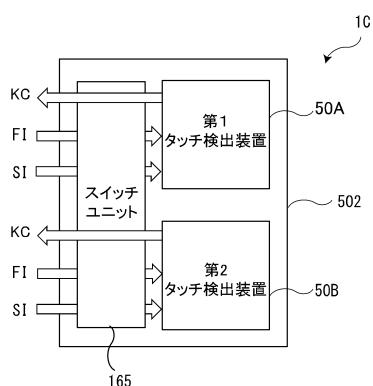

【図13】本発明の実施形態の第2応用例に係るタッチ検出ユニットにおける、第1タッチ検出装置と第2タッチ検出装置との接続を示すブロック図である。

【図14】本発明の実施形態の第2応用例に係るタッチ検出ユニットが適用された電子楽器における、発音及び消音のタイミングを説明する図である。

【図15】本発明の実施形態の第3応用例に係るタッチ検出ユニットにおける、第1タッチ検出装置と第2タッチ検出装置との接続を示すブロック図である。

40

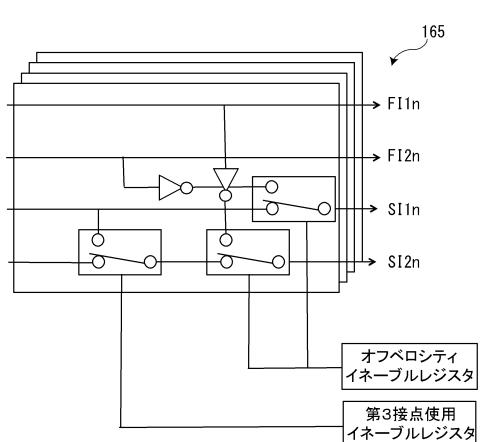

【図16】本発明の実施形態の第3応用例に係るスイッチユニットの構成を示す回路図である。

【図17】本発明の実施形態の第3応用例に係るタッチ検出ユニットが適用された電子楽器における、発音及び消音のタイミングの一例を説明する図である。

【図18】従来の電子ピアノにおける、押鍵されてから発音されるまでのタイミングを説明する図である。

【図19】従来の電子ピアノにおける発音タイミングとアコースティックピアノにおける発音タイミングとの相違を説明する図である。

【図20】ソフトウェアによる処理で発音タイミングを遅延させる従来の電子ピアノにおける、押鍵されてから発音されるまでのタイミングを説明する図である。

50

**【発明を実施するための形態】****【0013】**

以下、図面に基づいて、本発明の実施形態に係るタッチ検出装置を説明する。

**【0014】**

図1は、本発明の実施形態に係るタッチ検出装置50が適用された電子楽器1のハードウェアの構成を示すブロック図である。

図1において、電子楽器1は、CPU11と、ROM(Read Only Memory)12と、RAM(Random Access Memory)13と、バス14と、入出力インターフェース15と、入力部16と、出力部17と、記憶部18と、MIDI(Musical Instrument Digital Interface)インターフェース部19と、ドライブ20と、タッチ検出装置50と、を備えている。

10

**【0015】**

CPU11は、ROM12に記録されているプログラム、又は、記憶部18からRAM13にロードされたプログラムに従って各種の処理を実行する。例えばCPU11は、タッチ検出装置50から送信された発音情報(詳細については後述する)に基づいて発音するための制御、即ち発音制御を実行する。

RAM13には、CPU11が各種の処理を実行する上において必要なデータ等が適宜記憶される。

**【0016】**

CPU11、ROM12、RAM13、及び後述のタッチ検出装置50は、バス14を介して相互に接続されている。このバス14にはまた、入出力インターフェース15も接続されている。入出力インターフェース15には、入力部16、出力部17、記憶部18、MIDIインターフェース部19、及びドライブ20が接続されている。

20

**【0017】**

入力部16は、複数種類の音が夫々対応付けられた複数の鍵(例えば、88個の鍵)を有するMIDIキーボードを含む。電子楽器1において、複数の鍵に対応づけられた複数種類の音は、ノートナンバにより識別される。この鍵の押離鍵操作は、後述するタッチ検出装置50に検出される。

**【0018】**

具体的には、入力部16は、複数の鍵毎に設けられ、押鍵操作に応じて、順次オンされる第1接点160a及び第2接点160bが、マトリクス状に接続された鍵スイッチマトリクス160を備える。

30

鍵スイッチマトリクス160は、タッチ検出装置50から送信されたコモン側スイッチ入力信号(KC)に応じて、オンされた第1接点160a又は第2接点160bを検出する。そして、鍵スイッチマトリクス160は、オンされた第1接点160aを示す第1接点オン信号又はオンされた第2接点160bを示す第2接点オン信号をタッチ検出装置50に送信する。

一方、鍵スイッチマトリクス160は、鍵が押切られた状態からの離鍵操作に応じて、第2接点160b、第1接点160aの順にオフされたことを検出する。そして、鍵スイッチマトリクス160は、オフされた第1接点160aを示す第1接点オフ信号又はオフされた第2接点160bを示す第2接点オフ信号をタッチ検出装置50に送信する。

40

**【0019】**

また、入力部16は、各種情報を入力するためのスイッチを備えている。そして、入力部16は、ユーザによって入力された各種情報をCPU11に出力する。

出力部17は、ディスプレイや、スピーカ及びD/A変換回路等を有しており、画像や音声を出力する。

記憶部18は、ハードディスク或いはDRAM(Dynamic Random Access Memory)等で構成され、電子楽器1の制御のための各種プログラムを記憶する。

**【0020】**

MIDIインターフェース部19は、楽音を発生する音源41と発音制御部としてのCPU11とを接続するインターフェースである。音源41は、入力部16の複数の鍵に夫々対応付けられた複数種類の音を識別するノートナンバに対応付けた音源データを記憶し、CPU11の制御により、音源データを読み出し楽音を出力する。

【0021】

ドライブ20には、磁気ディスク、光ディスク、光磁気ディスク、或いは半導体メモリ等よりなる、リムーバブルメディア31が適宜装着される。ドライブ20によってリムーバブルメディア31から読み出されたプログラムは、必要に応じて記憶部18にインストールされる。また、リムーバブルメディア31は、記憶部18に記憶されている各種データも、記憶部18と同様に記憶することができる。

10

【0022】

次に、図2を参照して、本実施形態に係るタッチ検出装置50のハードウェアの構成について説明する。

図2は、本発明の一実施形態に係るタッチ検出装置50のハードウェア構成を示すプロック図である。

タッチ検出装置50は、制御回路としてのコントローラ51と、イベントフラグセット回路52（以下、「EVフラグセット回路52」とも呼ぶ）と、ステータス増加回路53と、第1カウンタ54と、第2カウンタ55と、カウンタメモリ56と、到達時間メモリ57と、比較回路58と、反転回路59と、ペロシティレジスタ61と、ノートナンバレジスタ62と、を備える。

20

【0023】

コントローラ51は、鍵スイッチマトリクス160の第1接点160a又は第2接点160bと接続され、第1接点オン信号又は第2接点オン信号を受信する。

また、コントローラ51は、タッチ検出装置50におけるその他のハードウェアを制御し、発音制御部としてのCPU11による発音の契機となる発音情報を生成し、バス14を介して発音制御部に送信する。

【0024】

本実施形態において、「発音情報」は、CPU11の処理に対する割り込み情報、入力部16の鍵が押下された場合におけるその鍵のノートナンバ、及び鍵の押下の強さを示すタッチ情報としてのペロシティ値を含む。

30

なお、発音制御部としてのCPU11は、発音情報を受信したときには、音源41と協働して、当該発音情報に含まれるノートナンバに対応する音を、ペロシティに応じた強さで発音する制御を実行する。

【0025】

また、コントローラ51は、鍵スイッチマトリクス160にコモン側スイッチ入力信号（K C）を送信し、鍵スイッチマトリクス160から、第1接点オン信号又は第2接点オン信号を受信する。

【0026】

また、コントローラ51は、イベントフラグ（以下、「EV」とも呼ぶ）及びステータスフラグ（以下、「ST」とも呼ぶ）に応じて、タッチ検出装置50を構成する上記回路や加算器を制御する。

40

本実施形態において、EVの値としては、“0”又は“1”が取り得る。

EVの値“0”は、いずれの鍵も押鍵又は離鍵されていない状態であることを示す。

EVの値“1”は、いずれかの鍵が押鍵又は離鍵されている状態であることを示す。

【0027】

また、本実施形態において、STの値は、“0”、“1”、“2”、“3”又は“4”が取り得る。

STの値“0”は、押鍵待ち状態であることを示す。

STの値“1”は、後述するバイアス時間をカウント中であることを示す。

STの値“2”は、後述するペロシティ測定値をカウント中であることを示す。

50

S T の値 “ 3 ” は、後述する補正時間用カウンタ値をカウント中であることを示す。

S T の値 “ 4 ” は、離鍵待ちの状態であることを示す。

#### 【 0 0 2 8 】

コントローラ 5 1 は、これら E V 及び S T の値を、カウンタメモリ 5 6 に記憶し、適宜参考するとともに、E V フラグセット回路 5 2 及びステータス増加回路 5 3 を制御して更新させる。

#### 【 0 0 2 9 】

図 3 は、本実施形態に係るカウンタメモリ 5 6 のフォーマットを説明する図である。

カウンタメモリ 5 6 は、複数の鍵の夫々対応した複数のアドレス、具体的には本実施形態では 8 8 個の鍵の夫々に対応した 8 8 個のアドレスを有する。各アドレスには、対応付けられた鍵における E V の値、S T の値、第 1 カウンタ値としてのベロシティカウンタ値、及び第 2 カウンタ値としての補正時間用カウンタ値が記憶されている。詳しくは後述するが、ベロシティカウンタ値（以下、「 V C 」とも呼ぶ）は第 1 カウンタ 5 4 により加算され、補正時間用カウンタ値（以下、「 T C 」とも呼ぶ）は第 2 カウンタ 5 5 により加算される。

また、各アドレスには、鍵に対応付けられたノートナンバ（図示せず）が記憶せっている。

#### 【 0 0 3 0 】

E V フラグセット回路 5 2 は、コントローラ 5 1 の制御により、カウンタメモリ 5 6 に記憶された E V の値を更新する。

ステータス増加回路 5 3 は、コントローラ 5 1 の制御により、カウンタメモリ 5 6 に記憶された S T の値を更新する。

#### 【 0 0 3 1 】

第 1 カウンタ 5 4 は、コントローラ 5 1 の制御により、第 1 接点 1 6 0 a がオンされてから第 2 接点 1 6 0 b がオンされるまでの時間を、カウンタメモリ 5 6 の V C において加算する。また、第 1 カウンタ 5 4 は、コントローラ 5 1 の制御により、カウンタメモリ 5 6 の V C をリセットする。

ここで、カウンタメモリ 5 6 の V C は、S T の値 “ 1 ” のときはバイアス時間を示し、S T の値 “ 2 ” のときはベロシティ測定値を示す。即ち、ベロシティ測定値は、第 1 接点 1 6 0 a がオンされてから第 2 接点 1 6 0 b がオンされるまでの時間から、予め設定されたバイアス時間が除外された時間を示す値である。

#### 【 0 0 3 2 】

第 2 カウンタ 5 5 は、コントローラ 5 1 の制御により、第 1 カウンタ 5 4 による加算が完了してからの時間を、カウンタメモリ 5 6 の T C において加算する。また、第 2 カウンタ 5 5 は、コントローラ 5 1 の制御により、カウンタメモリ 5 6 の T C をリセットする。

#### 【 0 0 3 3 】

到達時間メモリ 5 7 は、V C のベロシティ測定値に応じて、予め設定された第 2 カウンタ 5 5 による加算終了時間を示す到達時間値を記憶する。

比較回路 5 8 は、到達時間メモリ 5 7 に記憶された到達時間値と T C とを比較し、到達時間値と T C とが一致した時に、一致信号をコントローラ 5 1 に送信する。

反転回路 5 9 は、カウンタメモリ 5 6 に記憶された V C （ベロシティ測定値）を読み込み、反転処理によりベロシティ値を算出し、ベロシティレジスタ 6 1 に格納する。

#### 【 0 0 3 4 】

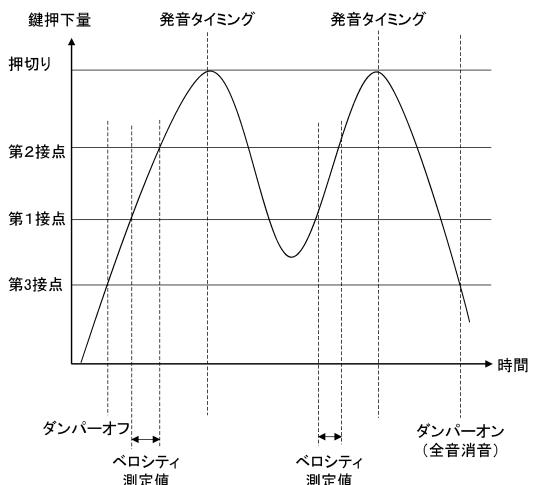

次に、図 4 を参照して、本実施形態に係るタッチ検出装置 5 0 を構成するハードウェアの動作タイミングについて説明する。

図 4 は、本実施形態に係るタッチ検出装置 5 0 を構成するハードウェアの動作タイミングを説明する図である。

まず、図 4 に示すグラフの左下において、演奏者による鍵の押鍵操作が開始される。このとき、カウンタメモリ 5 6 に記憶された E V の値は、“ 0 ” である。

更に押鍵され、第 1 接点 1 6 0 a がオンされると、鍵スイッチマトリクス 1 6 0 は、第

10

20

30

40

50

1接点オン信号をコントローラ51に送信する。

【0035】

ここで、コントローラ51は、第1接点オン信号を受信すると、当該第1接点オン信号が送信された鍵を特定し、カウンタメモリ56(図3参照)において、特定した鍵のアドレスに記憶された各種値を更新させる制御を実行する。また、コントローラ51は、特定した鍵のノートナンバをノートナンバレジスタ62に格納する。

【0036】

そして、コントローラ51は、第1接点オン信号を受信すると、EVフラグセット回路52にEVの値“1”をセットさせ、ステータス増加回路53にSTの値“1”をセットさせ、第1カウンタ54にVCをリセットさせてからカウントを開始させVCを加算させる。この間におけるカウンタメモリ56のVCは、バイアス時間を示す。

10

【0037】

次に、コントローラ51は、カウンタメモリ56におけるVCの値がバイアス時間として予め設定された所定値となった場合には、ステータス増加回路53にSTの値“2”をセットさせ、第1カウンタ54にVCをリセットさせてからカウントを開始させVCを加算させる。この間におけるVCは、ベロシティ測定値を示す。

【0038】

更に押鍵され、第2接点160bがオンされると、鍵スイッチマトリクス160は、第2接点オン信号をコントローラ51に送信する。

そして、コントローラ51は、第2接点オン信号を受信すると、ステータス増加回路53にSTの値“3”をセットさせ、第1カウンタ54にVCのカウントを終了させ、第2カウンタ55にTCをリセットさせてからカウントを開始させTCを加算させる。この間におけるTCは、補正時間を示す。

20

また、この間において、反転回路59は、カウンタメモリ56に記憶されたVC(ベロシティ測定値)を読み込み、反転処理によりベロシティ値を算出し、ベロシティレジスタ61に格納する。そして、コントローラ51は、割り込み信号、ノートナンバレジスタ62に格納されたノートナンバ及びベロシティレジスタ61に格納されたベロシティ値を含む発音情報を生成する。

【0039】

次に、比較回路58は、到達時間メモリ57に予め設定され記憶された到達時間値とTCとを比較し、到達時間値とTCとが一致した時に、一致信号をコントローラ51に送信する。コントローラ51は、一致信号を受信すると、発音制御部としてのCPU11に、ベロシティ値を含む発音情報を送信する。

30

そして、CPU11は、コントローラ51から送信された発音情報に基づく音を発音する発音処理を実行する。

なお、以上のタッチ検出装置50が実行する一連の処理を、以下、「タッチ検出動作処理」と呼ぶ。

【0040】

図5は、本発明の一実施形態に係るタッチ検出装置50によるタッチ検出動作処理が実行された場合における、押鍵されてから発音されるまでのタイミングを説明する図である。

40

図4に示すタイミングで、タッチ検出装置50の各ハードウェアが動作することで、電子楽器1は、図5に示すように発音する。詳細には、押鍵され第1接点160aがオンされると、バイアス時間が加算され、次にベロシティ測定値が加算される。そして、更に押鍵され第2接点160bがオンされると、ベロシティ測定値に応じた補正時間が加算され、この補正時間経過後に発音制御部において発音処理が実行される。これにより、鍵が押し切られたタイミングで発音される。

【0041】

次に、図6から図10を参照して、本実施形態に係るタッチ検出装置50を構成するハードウェアのタッチ検出動作処理について説明する。

50

図6乃至図10は、本実施形態に係るタッチ検出装置50のタッチ検出動作処理の流れを説明するフローチャートである。

【0042】

図6に示すように、ステップS1において、コントローラ51は、カウンタメモリ56のEVの値が“1”であるか否かを判定し、EVの値が“1”であると判定した場合はステップS2に処理を移し、EVの値が“1”でないと判定した場合はステップS5に処理を移す。

【0043】

ステップS2において、反転回路59は、カウンタメモリ56に記憶されたVC(ペロシティ測定値)を読み込み、反転処理によりペロシティ値を算出し、ペロシティレジスタ61に格納する。

【0044】

ステップS3において、コントローラ51は、第1接点オン信号又は第2接点オン信号を受信した鍵のノートナンバをノートナンバレジスタ62に格納する。

ステップS4において、EVフラグセット回路52は、カウンタメモリ56に記憶されたEVの値を“0”に更新する。

【0045】

ステップS5において、コントローラ51は、カウンタメモリ56のSTの値が“0”であるか否かを判定し、STの値が“0”であると判定した場合はステップS6に処理を移し、STの値が“0”でないと判定した場合はステップS10に処理を移す。

【0046】

ステップS6において、コントローラ51は、第1接点オン信号を受信したか否かを判定し、第1接点オン信号を受信したと判定した場合はステップS7に処理を移し、第1接点オン信号を受信していないと判定した場合はタッチ検出動作を終了させる。

【0047】

ステップS7において、ステータス増加回路53は、カウンタメモリ56に記憶されたSTの値を“1”に更新する。

ステップS8において、第1カウンタ54は、カウンタメモリ56のVCをリセットする。

ステップS9において、第1カウンタ54は、カウンタメモリ56のVC(バイアス時間)の加算を開始する。

【0048】

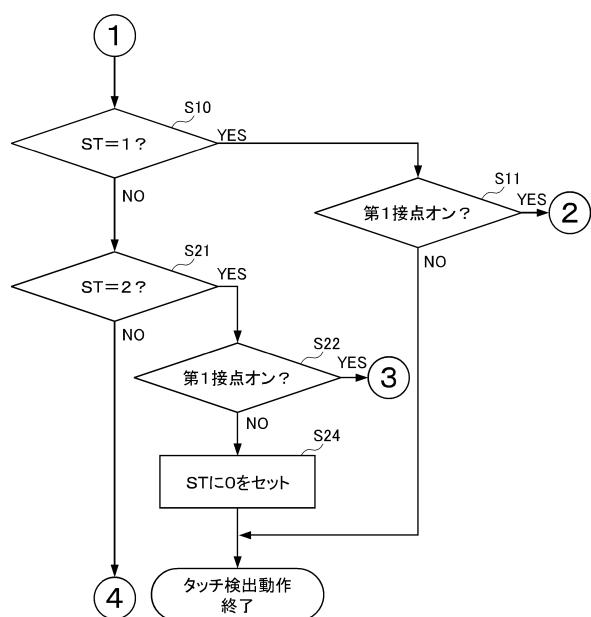

図7に示すように、ステップS10において、コントローラ51は、カウンタメモリ56のSTの値が“1”であるか否かを判定し、STの値が“1”であると判定した場合はステップS11に処理を移し、STの値が“1”でないと判定した場合はステップS21に処理を移す。

【0049】

ステップS11において、コントローラ51は、第1接点オン信号を受信したか否かを判定し、第1接点オン信号を受信したと判定した場合はステップS12に処理を移し、第1接点オン信号を受信していないと判定した場合はタッチ検出動作を終了させる。

【0050】

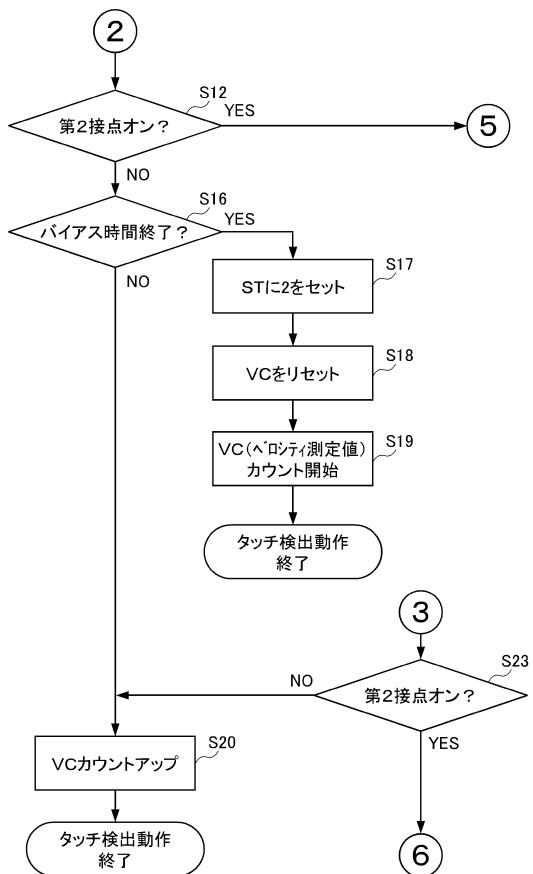

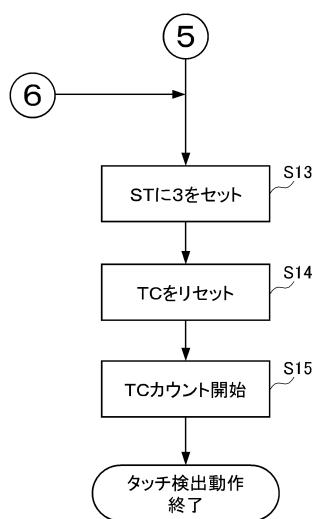

図8に示すように、ステップS12において、コントローラ51は、第2接点オン信号を受信したか否かを判定し、第2接点オン信号を受信したと判定した場合はステップS13に処理を移し、第2接点オン信号を受信していないと判定した場合はステップS16に処理を移す。

【0051】

図9に示すように、ステップS13において、ステータス増加回路53は、カウンタメモリ56に記憶されたSTの値を“3”に更新する。

ステップS14において、第2カウンタ55は、カウンタメモリ56のTCをリセットする。

10

20

30

40

50

ステップ S 15において、第2カウンタ55は、カウンタメモリ56のTCの加算を開始する。

【0052】

図8に戻って、ステップS16において、コントローラ51は、カウンタメモリ56のVCが予め設定されたバイアス時間と一致するか否かを判定し、一致すると判定した場合はステップS17に処理を移し、一致しないと判定した場合はステップS20に処理を移す。

【0053】

ステップS17において、ステータス増加回路53は、カウンタメモリ56に記憶されたSTの値を“2”に更新する。

ステップS18において、第1カウンタ54は、カウンタメモリ56のVCをリセットする。

【0054】

ステップS19において、第1カウンタ54は、カウンタメモリ56のVC(ベロシティ測定値)の加算を開始する。

ステップS20において、第1カウンタ54は、カウンタメモリ56のVCの加算を継続する。

【0055】

図7に戻って、ステップS21において、コントローラ51は、カウンタメモリ56のSTの値が“2”であるか否かを判定し、STの値が“2”であると判定した場合はステップS22に処理を移し、STの値が“2”でないと判定した場合はステップS25に処理を移す。

【0056】

ステップS22において、コントローラ51は、第1接点オン信号を受信したか否かを判定し、第1接点オン信号を受信したと判定した場合はステップS23に動作を移し、第1接点オン信号を受信していないと判定した場合はステップS24に動作を移す。

【0057】

図8に示すように、ステップS23において、コントローラ51は、第2接点オン信号を受信したか否かを判定し、第2接点オン信号を受信したと判定した場合はステップS13に動作を移し、第2接点オン信号を受信していないと判定した場合はステップS20に動作を移す。

ステップS24において、ステータス増加回路53は、カウンタメモリ56に記憶されたSTの値を“0”に更新する。

【0058】

図10に示すように、ステップS25において、コントローラ51は、カウンタメモリ56のSTの値が“3”であるか否かを判定し、STの値が“3”であると判定した場合はステップS26に処理を移し、STの値が“3”でないと判定した場合はステップS29に処理を移す。

【0059】

ステップS26において、比較回路58は、到達時間メモリ57に記憶された到達時間値と、カウンタメモリ56のTCと、を比較し、到達時間値とTCとが一致するか否かを判定し、一致すると判定した場合はステップS27に処理を移し、一致しないと判定した場合はステップS28に処理を移す。

【0060】

ステップS27において、EVフラグセット回路52は、カウンタメモリ56に記憶されたEVの値を“1”に更新する。

ステップS28において、第2カウンタ55は、カウンタメモリ56のTCの加算を継続する。

【0061】

ステップS29において、コントローラ51は、カウンタメモリ56のSTの値が“4”

10

20

30

40

50

”であるか否かを判定し、S Tの値が“4”であると判定した場合はステップS 3 0に処理を移し、S Tの値が“4”でないと判定した場合はタッチ検出動作を終了させる。

【0062】

ステップS 3 0において、コントローラ5 1は、第1接点オフ信号を受信したか否かを判定し、第1接点オフ信号を受信したと判定した場合はタッチ検出動作を終了させ、第1接点オフ信号を受信していないと判定した場合はステップS 3 1に処理を移す。

【0063】

ステップS 3 1において、コントローラ5 1は、第2接点オフ信号を受信したか否かを判定し、第2接点オフ信号を受信したと判定した場合はタッチ検出動作を終了させ、第2接点オフ信号を受信していないと判定した場合はステップS 3 2に処理を移す。

ステップS 3 2において、ステータス増加回路5 3は、カウンタメモリ5 6に記憶されたS Tの値を“0”に更新する。

【0064】

以上説明したように、本実施形態のタッチ検出装置5 0は、コントローラ5 1と、第1接点1 6 0 a及び第2接点1 6 0 bと、第1カウンタ5 4と、第2カウンタ5 5と、カウンタメモリ5 6と、到達時間メモリ5 7と、比較回路5 8と、を備える。

コントローラ5 1は、鍵スイッチマトリクス1 6 0の第1接点1 6 0 a及び第2接点1 6 0 bと接続され、第1接点オン信号又は第2接点オン信号を受信する。

第1接点1 6 0 a及び第2接点1 6 0 bは、複数の鍵毎に設けられ、押鍵操作に応じて、順次オンされる。

第1カウンタ5 4は、第1接点1 6 0 aがオンされてから第2接点1 6 0 bがオンされるまでの時間を、カウンタメモリ5 6のVCにおいて加算する。

第2カウンタ5 5は、第1カウンタ5 4による加算が完了してからの時間を、カウンタメモリ5 6のTCにおいて加算する。

カウンタメモリ5 6は、複数の鍵毎に夫々対応したアドレスを有する。各アドレスには、対応付けられた鍵における第1カウンタ値としてのベロシティカウンタ値及び第2カウンタ値としての補正時間用カウンタ値が記憶されている。

比較回路5 8は、到達時間メモリ5 7に記憶された到達時間値とTCとを比較し、到達時間値とTCとが一致した時に、一致信号をコントローラ5 1に送信する。

そして、コントローラ5 1は、一致信号を受信すると、発音制御部としてのCPU 1 1に、ベロシティ値を含む発音情報を送信する。

【0065】

このようにして、第1カウンタ5 4により、ベロシティ値を算出するためのベロシティ測定値がカウントされる。第2カウンタ5 5により、発音タイミングを鍵が押し切られるタイミングに合わせるための補正時間がカウントされる。そして、補正時間経過後に、コントローラ5 1により、ベロシティ値を含む発音情報が、発音制御部としてのCPU 1 1に送信される。

このため、発音制御部としてのCPU 1 1とは別に設けられたタッチ検出装置5 0により、ベロシティ値を含む発音情報を、正確な発音タイミングで、発音制御部としてのCPU 1 1に送信できる。

【0066】

よって、ベロシティ値の測定や、発音タイミングを押鍵操作に合わせるための時間のカウント等による制御負荷を、発音制御部としてのCPU 1 1にかけることがない。

従って、電子楽器において、同一のタイミングで多くの音を発生させる場合でも、鍵の押鍵に対して正確なタイミングで発音が可能となる。

更に、発音制御部(CPU 1 1)とは別にタッチ検出装置5 0が設けられているので、発音制御部としてはCPU 1 1等の従来のものをそのまま流用できるため、開発にかかる工数やコストを削減できる。また、カウンタメモリ5 6において、ベロシティカウンタ値及び補正時間用カウンタ値を記憶するので、これらの値を夫々別のメモリに記憶した場合に比べ、メモリを含む部品数を抑えることができる。

10

20

30

40

50

## 【0067】

また、到達時間メモリ57は、VCのベロシティ測定値に応じて、予め設定された第2カウンタ55による加算終了時間を示す到達時間値を記憶する。

比較回路58は、到達時間メモリ57に記憶された到達時間値とTCとを比較する。

これにより、到達時間メモリに記憶された到達時間値を書き換えることで、発音するまでの補正時間を調整できる。このため、ユーザの趣向や、音色によって、補正時間の変更が適宜可能となる。

## 【0068】

次に、本実施形態の応用例として、第1応用例、第2応用例及び第3応用例について説明する。以下、本実施形態の応用例について説明するが、本実施形態と同一構成要件については同一符号を付し、その説明を省略若しくは簡略化する。

10

## 【0069】

第1応用例、第2応用例及び第3応用例の電子楽器は、本実施形態のタッチ検出装置50を2つ有するタッチ検出ユニットを備える。具体的には、第1応用例、第2応用例及び第3応用例のタッチ検出ユニットは、第1タッチ検出装置50Aと、第2タッチ検出装置50Bと、を備える。これにより、押鍵操作に応じて、最大で4つの接点の信号を処理できる。なお、第1タッチ検出装置50A及び第2タッチ検出装置50Bは、上記実施形態のタッチ検出装置50と同様のハードウェア構成を備える。

## 【0070】

まず、第1応用例について説明する。

20

第1応用例の電子楽器1Aは、発音時間を延長するダンパー機能を有する。電子楽器1Aは、このダンパー機能をオフ（以降、ダンパーオフとも言う）にすることで、鍵が連打されても各音を消音せずに、連続して発音する。また、電子楽器1Aは、ダンパー機能をオン（以降、ダンパーオンとも言う）にすることで、全音消音する。

## 【0071】

電子楽器1Aは、鍵スイッチマトリクスにおいて、第1接点及び第2接点に加え、第3接点を有する。電子楽器1Aは、第3接点がオンされることでダンパーオフとなり、第3接点がオフされることでダンパーオンとなる。

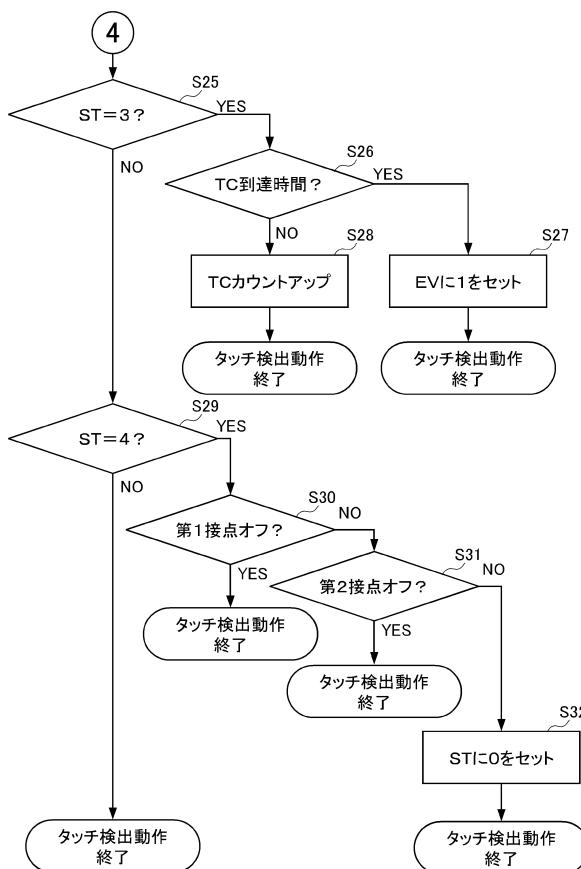

図11は、本発明の実施形態の第1応用例に係るタッチ検出ユニット500における、第1タッチ検出装置50Aと第2タッチ検出装置50Bとの接続を示すブロック図である。

30

図11において、KCは、コモン側のスイッチ入力を示し、FIは鍵スイッチマトリクスからの第1接点から出力された信号を示し、SIは鍵スイッチマトリクスからの第2接点から出力された信号を示す。

## 【0072】

タッチ検出ユニット500において、第1タッチ検出装置50Aは、上記実施形態のタッチ検出装置50と同様に、FI及びSIに基づき、ベロシティ値の測定や、発音タイミングを押鍵操作に合わせるための補正時間のカウントを行い、発音情報を生成し、発音情報をCPU11に送信する。一方、第2タッチ検出装置50Bは、FI及びSIの端子がショートされて、第3接点と接続され、この第3接点から出力された信号を受信する。

40

## 【0073】

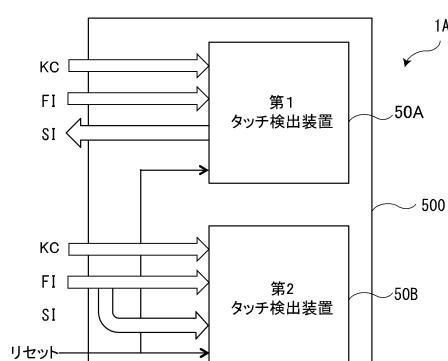

図12は、本発明の実施形態の第1応用例に係るタッチ検出ユニット500が適用された電子楽器1Aにおける、発音及び消音のタイミングを説明する図である。

図12に示すように、電子楽器1Aは、第2タッチ検出装置50Bが第3接点から出力された信号を受信することでダンパーオフとなる。そして、電子楽器1Aは、第1タッチ検出装置50Aにより、ベロシティ値を測定し、補正時間のカウントを行い、鍵が押し切られたタイミングで音を発音する。そして、図12に示すように、第1接点と第2接点のオンとオフが繰り返された場合、夫々鍵が押し切られたタイミングで音を発音するが、ダンパーオフなので、各音を消音せずに、連続して発音する。そして、電子楽器1Aは、第2タッチ検出装置50Bが再度第3接点から出力された信号を受信することでダンパーオ

50

ンとなり、全音が消音する。

【0074】

このように、タッチ検出ユニット500は、第1タッチ検出装置50Aと第2タッチ検出装置50Bとを備える。

第1タッチ検出装置50Aは、発音情報を生成し、発音情報を発音制御部としてのCPU11に送信する。

第2タッチ検出装置50Bは、第1接点又は前記第2接点と接続が切断され、第1接点及び第2接点とショートされ、第3接点と接続されている。

これにより、例えば、第3接点がダンパーのオン又はオフのスイッチであれば、同じタイミングで多くの音を発生させる場合でも、鍵の押鍵に対して正確なタイミングで発音可能な電子楽器において、ダンパーのオン又はオフが可能となる。

【0075】

次に、第2応用例について説明する。

第2応用例の電子楽器1Bは、タッチ検出ユニット501によりオフベロシティ値を測定し、このオフベロシティ値に基づき、適切なタイミングで発音した音を消音する。

【0076】

図13は、本発明の実施形態の第2応用例に係るタッチ検出ユニット501における、第1タッチ検出装置50Aと第2タッチ検出装置50Bとの接続を示すブロック図である。

図13において、KCは、コモン側のスイッチ入力を示し、FIは鍵スイッチマトリクスからの第1接点から出力された信号を示し、SIは鍵スイッチマトリクスからの第2接点から出力された信号を示す。

【0077】

タッチ検出ユニット501において、第1タッチ検出装置50Aは、上記実施形態のタッチ検出装置50と同様に、FI及びSIに基づき、ベロシティ値の測定や、発音タイミングを押鍵操作に合わせるための補正時間のカウントを行う。一方、第2タッチ検出装置50Bは、FIを反転した信号及びSIを反転した信号に基づき、オフベロシティ値を測定し、消音タイミングを離鍵操作に合わせるために、オフベロシティ値に基づく補正時間のカウントを行う。そして、第2タッチ検出装置50Bは、補正時間経過後、消音情報を、発音制御部としてのCPU11に送信する。この消音情報を受信した発音制御部としてのCPU11は、発音していた音を消音する制御を行う。

【0078】

図14は、本発明の実施形態の第2応用例に係るタッチ検出ユニット501が適用された電子楽器1Bにおける、発音及び消音のタイミングを説明する図である。

図14に示すように、電子楽器1Bは、第1タッチ検出装置50Aにより、ベロシティ値を測定し、補正時間のカウントを行い、鍵が押し切られたタイミングで発音する。そして、電子楽器1Bは、第2タッチ検出装置50Bにより、オフベロシティ値を測定し、補正時間のカウントを行い、離鍵操作に伴う適宜なタイミングで消音する。

【0079】

このように、タッチ検出ユニット501は、第1タッチ検出装置50Aと第2タッチ検出装置50Bとを備える。

第1タッチ検出装置50Aは、発音情報を生成し、発音情報を発音制御部としてのCPU11に送信する。

第2タッチ検出装置50Bは、第1接点又は第2接点からの信号を夫々反転した信号に基づき消音情報を生成し、この消音情報を発音制御部としてのCPU11に送信する。

これにより、同じタイミングで多くの音を発生させる場合でも、鍵の押鍵に対して正確なタイミングで発音可能な電子楽器において、鍵の離鍵に対して正確なタイミングで消音可能となる。

【0080】

次に、第3応用例について説明する。

10

20

30

40

50

第3応用例の電子楽器1Cは、タッチ検出ユニット503を備える。

図15は、本発明の実施形態の第3応用例に係るタッチ検出ユニット503における、第1タッチ検出装置50Aと第2タッチ検出装置50Bとの接続を示すブロック図である。

第3応用例のタッチ検出ユニット503は、第1タッチ検出装置50Aと、第2タッチ検出装置50Bと、電子楽器1CのCPU11(図1参照)により制御され、押鍵操作に応じて、順次オンされる上記第1接点及び第2接点を含む4つの接点と第1タッチ検出装置50Aと第2タッチ検出装置50Bとの接続を適宜切り替えるスイッチユニット165を備える。

【0081】

10

図16は、本発明の実施形態の第3応用例に係るスイッチユニット165の構成を示す回路図である。

スイッチユニット165は、CPU11により制御され、最大4つの接点のいずれか2つの接点からの信号を第1タッチ検出装置50Aに送信し、他の2つの接点を第2タッチ検出装置50Bに送信するように、回路を切り替える。第1タッチ検出装置50A又は第2タッチ検出装置50Bに送信される接点からの2つの信号の組み合わせは、CPU11の制御により決定される。なお、スイッチユニット165は、回路をショートすることで、例えば、第1応用例の電子楽器1Aにより、第1タッチ検出装置50Aには2つの接点からの信号を送信可能とし、第2タッチ検出装置50Bには1つの接点から信号を送信可能とすることができる。

【0082】

20

図17は、本発明の実施形態の第3応用例に係るタッチ検出ユニット502が適用された電子楽器1Cにおける、発音及び消音のタイミングの一例を説明する図である。

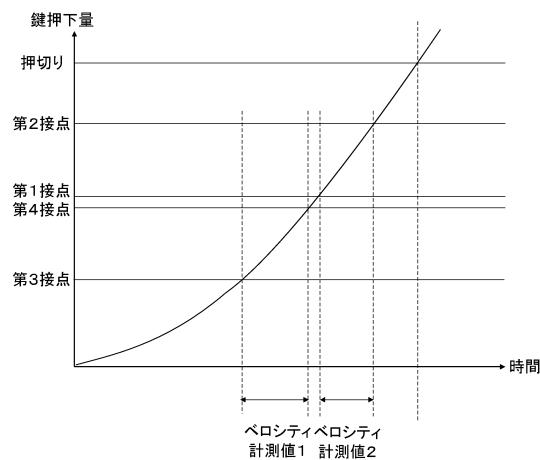

図17に示す例では、スイッチユニット165は、第3接点及び第4接点と第1タッチ検出装置50Aとを接続し、第1接点及び第2接点と第2タッチ検出装置50Bとを接続している。これにより、電子楽器1Cは、第1タッチ検出装置50Aにより、ベロシティ測定値1を測定し、第2タッチ検出装置50Bにより、ベロシティ測定値2を測定し、ベロシティ測定値1及びベロシティ測定値2からベロシティ値を算出し、補正時間のカウントを行い、鍵が押し切られたタイミングで発音する。

【0083】

30

このように、タッチ検出ユニット502は、第1タッチ検出装置50Aと第2タッチ検出装置50Bと、スイッチユニット165と、を備える。

スイッチユニット165は、第1タッチ検出装置50A及び第2タッチ検出装置50Bと第1接点及び第2接点を含む4つの接点との接続を切り替える。

これにより、同じタイミングで多くの音を発生させる場合でも、鍵の押鍵に対して正確なタイミングで発音可能な電子楽器において、1つのハードウェア構成で、第1応用例に係る電子楽器1Aのようにダンパーのオン又はオフが可能であり、第2応用例に係る電子楽器1Bのように鍵の離鍵に対して正確なタイミングで消音可能であり、図17に示す例のように、複数のベロシティ測定値からベロシティ値を算出可能となる。

【0084】

40

なお、本発明は、上述の実施形態に限定されるものではなく、本発明の目的を達成できる範囲での変形、改良等は本発明に含まれるものである。

【0085】

例えば、上述の実施形態では、鍵の数を88個とし、カウンタメモリに88個の特定のアドレスを設けたが、これに限らず、例えば、カウンタメモリの特定のアドレスは、鍵の数以上であれば任意の数としてもよい。

【0086】

また、上述の実施形態では、カウンタメモリと到達時間メモリとを夫々設けたが、これに限らず、例えば、カウンタメモリと到達時間メモリとを含む1つのメモリを設けてよい。

50

## 【0087】

また、上述の実施形態の応用例では、タッチ検出ユニットにおける2つのタッチ検出装置を同様の構成としているが、これに限らず、例えば、いずれか一方のタッチ検出装置の比較回路が用いる到達時間値を一定とすることで、到達時間メモリを設けないこともできる。

## 【0088】

また、上述の実施形態では、本発明に係るタッチ検出装置が適用される電子楽器は、電子ピアノを例として説明したが、特にこれに限定されない。

例えば、本発明は、タッチ検出機能を有する電子機器一般に適用することができる。具体的には、例えば、本発明は、ノート型のパーソナルコンピュータ、プリンタ、テレビジョン受像機、ビデオカメラ、携帯型ナビゲーション装置、携帯電話機、ポータブルゲーム機等に適用可能である。

換言すると、図1のハードウェア構成は例示に過ぎず、特に限定されない。

## 【0089】

以上、本発明のいくつかの実施形態について説明したが、これらの実施形態は、例示に過ぎず、本発明の技術的範囲を限定するものではない。本発明はその他の様々な実施形態を取ることが可能であり、更に、本発明の要旨を逸脱しない範囲で、省略や置換等種々の変更を行うことができる。これら実施形態やその変形は、本明細書等に記載された発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

## 【0090】

以下に、本願の出願当初の特許請求の範囲に記載された発明を付記する。

## [付記1]

複数種類の音が夫々対応付けられた複数の鍵と、前記複数の鍵毎に設けられ、押鍵操作に応じて、順次オンされる第1接点及び第2接点と、前記鍵の押鍵操作に応じて所定種類の音を発音させる発音制御部と、を備えた電子楽器のタッチ検出装置であって、

前記第1接点又は前記第2接点のオン検出信号を受信する制御回路と、

前記制御回路の制御により、前記第1接点及び前記第2接点の夫々のオン検出信号に基づいて、前記第1接点がオンされてから前記第2接点がオンされるまでの時間をカウントする第1カウンタと、

前記制御回路の制御により、前記第1カウンタによるカウントが完了してからの時間をカウントする第2カウンタと、

複数の前記鍵に夫々対応した複数のアドレスを有し、前記複数のアドレスに、前記第1カウンタによりカウントされた時間を示す第1カウンタ値と、前記第2カウンタによりカウントされた時間を示す第2カウンタ値と、を記憶するカウンタメモリと、

予め設定された到達時間値と前記第2カウンタ値とを比較し、前記到達時間値と前記第2カウンタ値とが略一致した時に、一致信号を前記制御回路に送信する比較回路と、を備え、

前記制御回路は、前記比較回路から前記一致信号を受信した時に、前記第1カウンタ値に応じたタッチ情報を含み、前記発音制御部による発音を指示する発音情報を、前記発音制御部に送信する、

ことを特徴とするタッチ検出装置。

## [付記2]

前記第1カウンタ値に応じて、予め設定された前記第2カウンタによるカウント終了時間を示す到達時間値を記憶する到達時間メモリを、更に備え、

前記比較回路は、前記到達時間メモリに記憶された前記到達時間値と前記第2カウンタ値とを比較する、

ことを特徴とする付記1に記載のタッチ検出装置。

## [付記3]

付記1又は2に記載のタッチ検出装置を2つ備えるタッチ検出ユニットであって、

10

20

30

40

50

一方の前記タッチ検出装置は、前記発音情報を生成し、前記発音情報を前記発音制御部に送信し、

他方の前記タッチ検出装置は、前記第1接点又は前記第2接点と接続が切断され、前記電子楽器に設けられた第3接点と接続される、

ことを特徴とするタッチ検出ユニット。

[付記4]

付記1又は2に記載のタッチ検出装置を2つ備えるタッチ検出ユニットであって、

一方の前記タッチ検出装置は、前記発音情報を生成し、前記発音情報を前記発音制御部に送信し、

他方の前記タッチ検出装置は、前記第1接点又は前記第2接点からの信号を夫々反転した信号に基づき消音情報を生成し、前記消音情報を前記発音制御部に送信する、

ことを特徴とするタッチ検出ユニット。

[付記5]

付記1又は2に記載のタッチ検出装置を2つと、

2つの前記タッチ検出装置と前記電子楽器に設けられた前記第1接点及び前記第2接点を含む4つの接点との接続を切り替えるスイッチユニットと、

を備えることを特徴とするタッチ検出ユニット。

[付記6]

複数種類の音が夫々対応付けられた複数の鍵と、前記複数の鍵毎に設けられ、押鍵操作に応じて、順次オンされる第1接点及び第2接点と、前記鍵の押鍵操作に応じて所定種類の音を発音させる発音制御部と、を備えた電子楽器のタッチ検出装置が実行するタッチ検出方法において、

前記第1接点及び前記第2接点の夫々のオン検出信号に基づいて、前記第1接点がオンされてから前記第2接点がオンされるまでの時間をカウントする第1カウンタステップと、

前記第1カウンタステップの処理によるカウントが完了してからの時間をカウントする第2カウンタ加算ステップと、

複数の前記鍵に夫々対応した複数のアドレスを有し、前記複数のアドレスに、前記第1カウンタステップの処理により加算された時間を示す第1カウンタ値と、前記第2カウンタステップの処理により加算された時間を示す第2カウンタ値と、を記憶するカウンタメモリを用いて、予め設定された到達時間値と前記第2カウンタ値とを比較し、前記到達時間値と前記第2カウンタ値とが略一致した時に、一致信号を送信する比較ステップと、

前記比較ステップの処理によって前記一致信号が送信されたときに、前記第1カウンタ値に応じたタッチ情報を含み、前記発音制御部による発音を指示する発音情報を、前記発音制御部に送信する送信ステップと、

を含むことを特徴とするタッチ検出方法。

【符号の説明】

【0091】

1, 1A, 1B, 1C . . . 電子楽器、11 . . . C P U、12 . . . R O M、13 . . . R A M、14 . . . バス、15 . . . 入出力インターフェース、16 . . . 入力部、17 . . . 出力部、18 . . . 記憶部、19 . . . M I D I インターフェース部、20 . . . ドライブ、31 . . . リムーバブルメディア、41 . . . 音源、50 . . . タッチ検出装置、50A . . . 第1タッチ検出装置、50B . . . 第2タッチ検出装置、51 . . . コントローラ、52 . . . E V フラグセット回路、53 . . . ステータス増加回路、54 . . . 第1カウンタ、55 . . . 第2カウンタ、56 . . . カウンタメモリ、57 . . . 到達時間メモリ、58 . . . 比較回路、59 . . . 反転回路、61 . . . ベロシティレジスタ、62 . . . ノートナンバーレジスタ、160 . . . 鍵スイッチマトリクス、160a . . . 第1接点、160b . . . 第2接点、165 . . . スイッチユニット、500, 501, 502, 503 . . . タッチ検出ユニット

【 四 1 】

【 図 2 】

( 3 )

〔 4 〕

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

---

フロントページの続き

(56)参考文献 特許第5 6 5 2 4 1 5 (JP, B2)

特開2 0 1 1 - 0 6 4 7 2 8 (JP, A)

特開2 0 0 8 - 0 4 6 2 4 9 (JP, A)

米国特許第0 5 8 2 4 9 3 8 (US, A)

(58)調査した分野(Int.Cl., DB名)

G 1 0 H 1 / 3 4

G 1 0 H 1 / 1 8