(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7546628号

(P7546628)

(45)発行日 令和6年9月6日(2024.9.6)

(24)登録日 令和6年8月29日(2024.8.29)

(51)国際特許分類

|         |                 |         |       |         |

|---------|-----------------|---------|-------|---------|

| B 4 1 J | 2/447(2006.01)  | B 4 1 J | 2/447 | 1 0 1 D |

| B 4 1 J | 2/455(2006.01)  | B 4 1 J | 2/455 |         |

| G 0 3 G | 15/04 (2006.01) | G 0 3 G | 15/04 |         |

| H 0 4 N | 1/036(2006.01)  | H 0 4 N | 1/036 |         |

F I

請求項の数 13 (全20頁)

(21)出願番号 特願2022-132718(P2022-132718)

(22)出願日 令和4年8月23日(2022.8.23)

(65)公開番号 特開2024-30133(P2024-30133A)

(43)公開日 令和6年3月7日(2024.3.7)

審査請求日 令和5年8月14日(2023.8.14)

(73)特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 110003281

弁理士法人大塚国際特許事務所

赤木 太輔

東京都大田区下丸子3丁目30番2号

(72)発明者 キヤノン株式会社内

審査官 上田 正樹

最終頁に続く

(54)【発明の名称】 露光装置及び画像形成装置

## (57)【特許請求の範囲】

## 【請求項1】

画像形成装置に実装される露光装置であって、

複数の発光素子と、

前記画像形成装置から周期的に送信される同期信号と、前記同期信号の周期内において前記画像形成装置から送信される前記複数の発光素子それぞれに対応する画像データと、を受信して、前記複数の発光素子を駆動するための、前記複数の発光素子それぞれに対応する駆動信号を出力する出力手段と、

前記複数の発光素子それぞれに対応する前記駆動信号に基づき前記複数の発光素子を駆動する駆動手段と、

を備えた発光チップを、1つ以上、有し、

前記出力手段は、前記複数の発光素子それぞれに対応する前記画像データをラッチして前記複数の発光素子それぞれに対応する駆動信号を出力するための、前記複数の発光素子それぞれに対応する複数のラッチ回路を有し、

前記発光チップは、制御情報を格納する格納手段をさらに備え、

前記駆動手段は、前記制御情報に基づき、前記駆動信号により当該駆動信号に対応する発光素子を駆動するか、前記駆動信号によらず当該駆動信号に対応する発光素子を駆動するかを切り替える切替手段を備えている、露光装置。

## 【請求項2】

前記同期信号は、前記画像形成装置に実装される感光体の1ラインの露光タイミングを示す

す信号である、請求項 1 に記載の露光装置。

【請求項 3】

前記出力手段は、前記複数の発光素子それぞれに対応する前記駆動信号を前記同期信号の周期と同じ期間だけ出力する、請求項 1 に記載の露光装置。

【請求項 4】

前記複数のラッチ回路には前記複数の発光素子それぞれに対応する前記画像データが順に入力され、

前記出力手段は、前記同期信号に基づき、前記画像データをラッチするタイミングを前記複数のラッチ回路それぞれに示す、前記複数のラッチ回路それぞれに対応するラッチ信号を生成する、請求項 1 に記載の露光装置。

10

【請求項 5】

前記複数のラッチ回路それぞれに対応する前記ラッチ信号の周期は、前記同期信号の周期に等しい、請求項 4 に記載の露光装置。

【請求項 6】

前記複数のラッチ回路は、2つ以上のラッチ回路を含む複数のグループにグループ化されており、

前記出力手段は、前記同期信号に基づき、同じグループに含まれる前記2つ以上のラッチ回路それぞれに対応する前記ラッチ信号を同じタイミングで生成する、請求項 4 に記載の露光装置。

20

【請求項 7】

前記複数のグループそれぞれのグループに含まれる前記2つ以上のラッチ回路の数は同じであり、

前記出力手段は、前記複数の発光素子それぞれに対応する前記画像データを受信し、前記画像データを、前記複数のグループそれぞれのグループに含まれる前記2つ以上のラッチ回路の数と同じ数の複数の信号線それぞれに順に出力する転送手段を有し、

前記複数のグループそれぞれのグループに含まれる前記2つ以上のラッチ回路それぞれは、前記複数の信号線の内の1つの信号線から前記画像データを受信する、請求項 6 に記載の露光装置。

【請求項 8】

前記転送手段が前記複数の信号線それぞれに同じタイミングにおいて出力する前記画像データに対応する発光素子は異なる、請求項 7 に記載の露光装置。

30

【請求項 9】

前記複数の発光素子は、前記画像形成装置に実装される感光体の回転軸と平行な主走査方向と、前記主走査方向とは直交する副走査方向との両方に沿って二次元状に配置され、

前記複数のグループそれぞれのグループに含まれる前記2つ以上のラッチ回路の数は、前記副走査方向に沿って配置される発光素子の数の整数倍である、請求項 7 に記載の露光装置。

【請求項 10】

前記制御情報は、前記駆動信号によらず当該駆動信号に対応する前記発光素子を駆動する場合には、当該発光素子を発光させる、請求項 1 に記載の露光装置。

40

【請求項 11】

前記制御情報は、前記複数の発光素子の内の前記駆動信号によらずに駆動する1つ以上の前記発光素子を一括して示す、請求項 1 に記載の露光装置。

【請求項 12】

前記複数の発光素子は、有機 E L 膜を含む、請求項 1 に記載の露光装置。

【請求項 13】

感光体と、

前記感光体を露光する請求項 1 から 12 のいずれか1項に記載の露光装置と、を備えている、画像形成装置。

【発明の詳細な説明】

50

**【技術分野】****【0001】**

本発明は、複数の発光素子を有する露光装置と、当該露光装置を使用して画像を形成する画像形成装置に関する。

**【背景技術】****【0002】**

電子写真方式の画像形成装置は、回転駆動される感光体を露光することで感光体に静電潜像を形成し、当該静電潜像をトナーで現像することにより画像を形成する。なお、感光体の回転軸に平行な方向は主走査方向として参照される。特許文献1は、複数の発光部が主走査方向に複数個配列された発光部の列が、感光体の回転方向に対応する副走査方向に複数配列された露光装置を用いて露光を行う画像形成装置を開示している。特許文献1では、電極、有機EL(Electro-Luminescence)膜及び有機EL膜を発光させるための回路部がシリコンウェハ上に形成された発光チップが基板上に複数実装されている。回路部には、入力された画像データを主走査方向に転送するためのフリップフロップ回路及び当該画像データを保持するためのフリップフロップ回路が発光部の数だけそれぞれ設けられており、画像データを保持するためのフリップフロップ回路のすべてに画像データが保持されると、発光部の制御が一斉に行われる。

10

**【先行技術文献】****【特許文献】****【0003】**

【文献】特開2021-35765号公報

20

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

特許文献1では、入力された画像データを主走査方向に転送するためのフリップフロップ回路が発光部の数だけ設けられることに起因して発光チップが大型化したり発光チップのコストが増大したりしてしまう。

**【0005】**

上記課題に鑑み、本発明は、発光チップの大型化及びコストの増大を抑制することを目的とする。

30

**【課題を解決するための手段】****【0006】**

本開示の一態様によると、画像形成装置に実装される露光装置は、複数の発光素子と、前記画像形成装置から周期的に送信される同期信号と、前記同期信号の周期内において前記画像形成装置から送信される前記複数の発光素子それぞれに対応する画像データと、を受信して、前記複数の発光素子を駆動するための、前記複数の発光素子それぞれに対応する駆動信号を出力する出力手段と、前記複数の発光素子それぞれに対応する前記駆動信号に基づき前記複数の発光素子を駆動する駆動手段と、を備えた発光チップを、1つ以上、有し、前記出力手段は、前記複数の発光素子それぞれに対応する前記画像データをラッチして前記複数の発光素子それぞれに対応する駆動信号を出力するための、前記複数の発光素子それぞれに対応する複数のラッチ回路を有し、前記発光チップは、制御情報を格納する格納手段をさらに備え、前記駆動手段は、前記制御情報に基づき、前記駆動信号により当該駆動信号に対応する発光素子を駆動するか、前記駆動信号によらず当該駆動信号に対応する発光素子を駆動するかを切り替える切替手段を備えている。

40

**【発明の効果】****【0007】**

本開示によると、発光チップが大型化することを抑制することができる。

**【図面の簡単な説明】****【0008】**

【図1】一実施形態による、画像形成装置の概略的な構成図。

50

- 【図 2】一実施形態による、露光ヘッド及び感光体を示す図。

- 【図 3】一実施形態による、露光ヘッドのプリント基板を示す図。

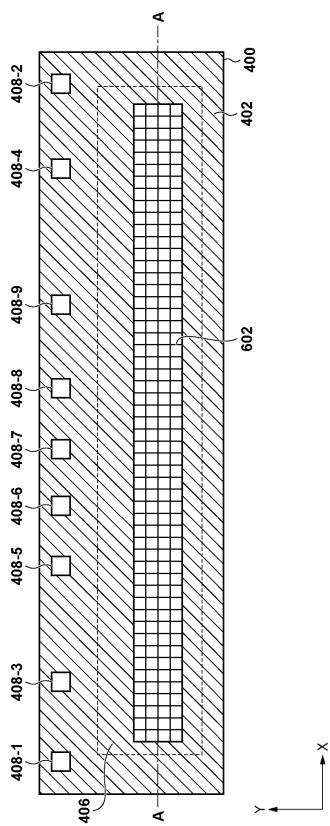

- 【図 4】一実施形態による、発光チップ内における発光素子の配置の説明図。

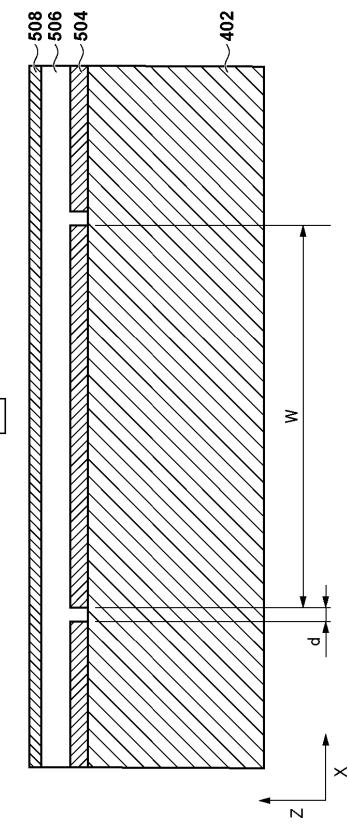

- 【図 5】一実施形態による、発光チップの平面図。

- 【図 6】一実施形態による、発光チップの断面図。

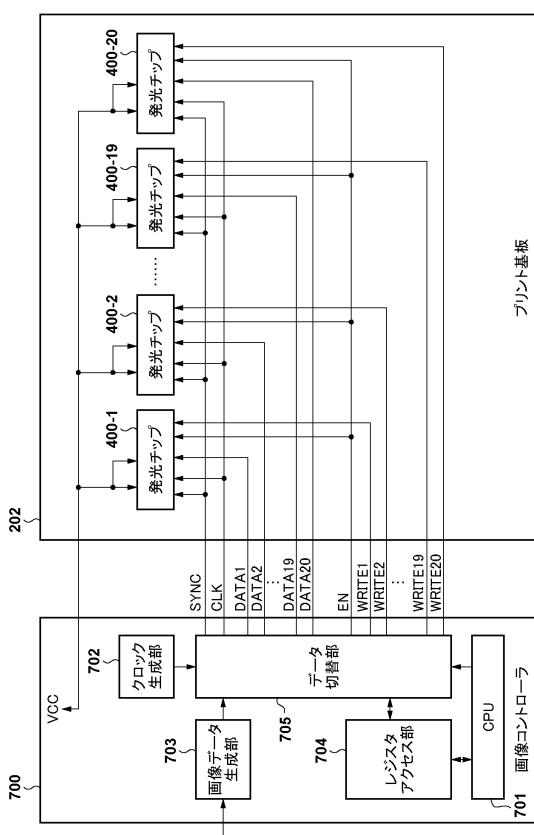

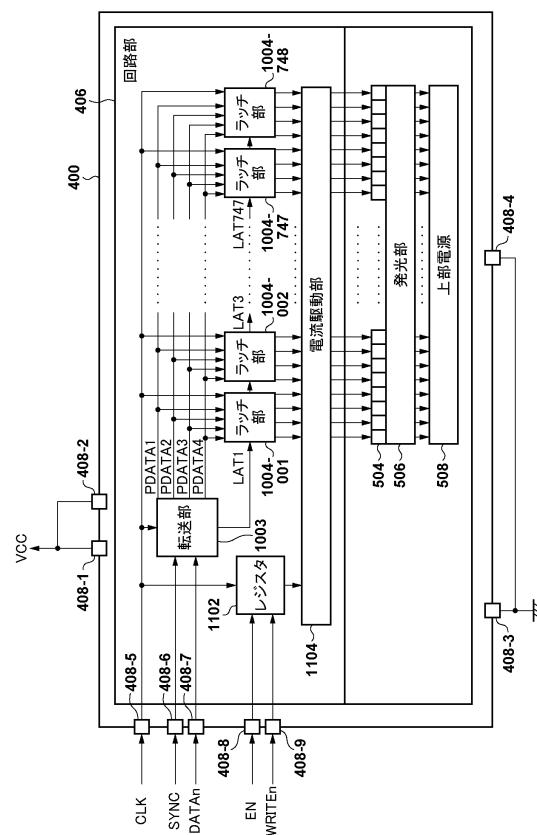

- 【図 7】一実施形態による、発光チップの制御構成図。

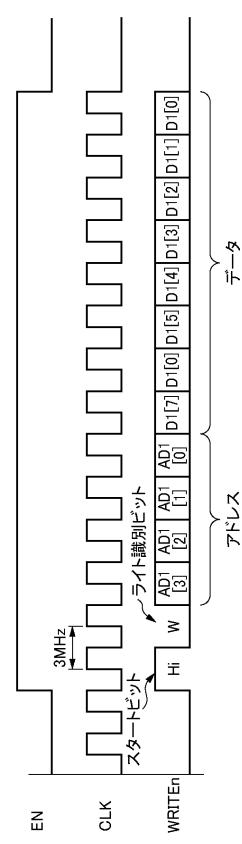

- 【図 8】一実施形態による、発光チップのレジスタにアクセスする際の各信号線の信号例を示す図。

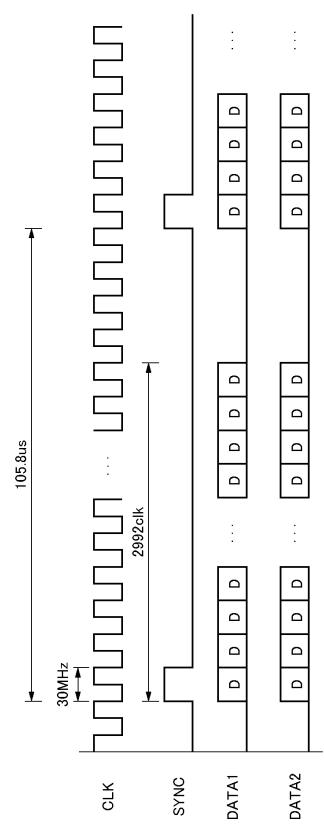

- 【図 9】一実施形態による、発光チップに画像データを送信する際の各信号線の信号例を示す図。

- 【図 10】一実施形態による、発光チップの機能ブロック図。

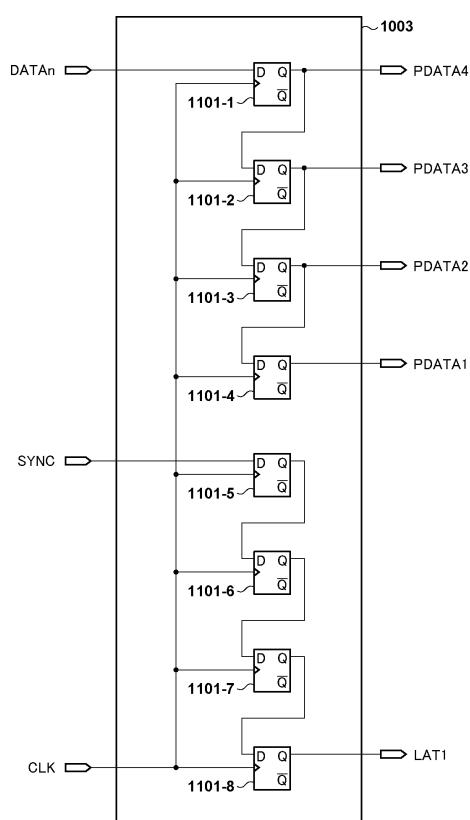

- 【図 11】一実施形態による、転送部の構成図。

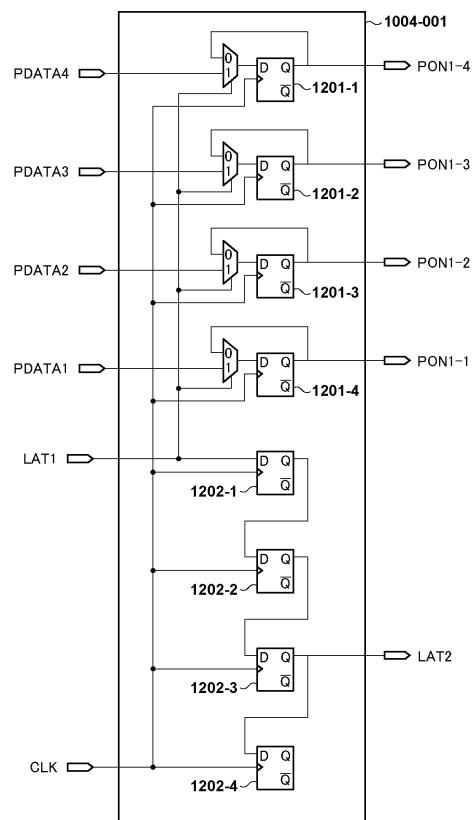

- 【図 12】一実施形態による、ラッチ部の構成図。

- 【図 13】一実施形態による、他のラッチ部の構成図。

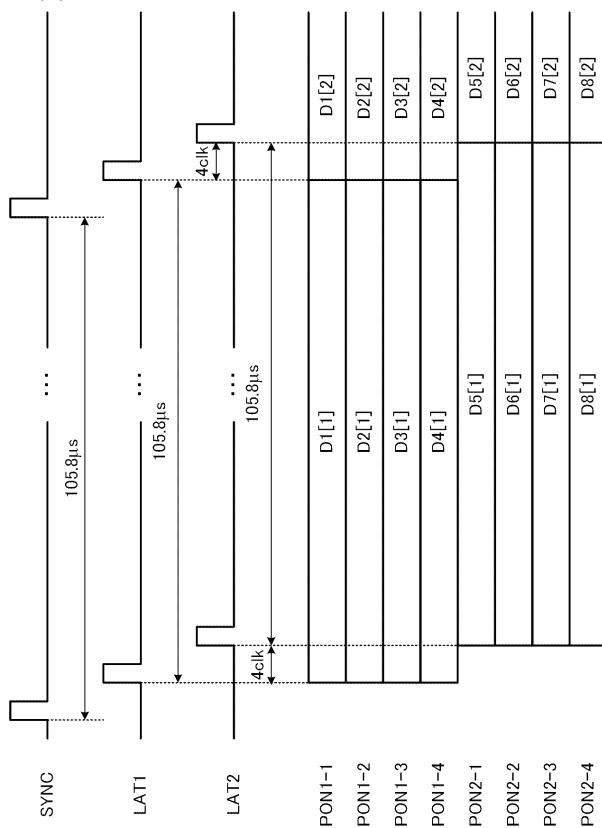

- 【図 14】一実施形態による、回路部における各信号のタイミングチャート。

- 【図 15】一実施形態による、電流駆動部の構成図。

- 【図 16】一実施形態による、画像コントローラが実行する処理のフローチャート。

- 【図 17】一実施形態による、回路部における各信号の他のタイミングチャート。

**【発明を実施するための形態】**

**【0009】**

以下、添付図面を参照して実施形態を詳しく説明する。なお、以下の実施形態は特許請求の範囲に係る発明を限定するものではない。実施形態には複数の特徴が記載されているが、これらの複数の特徴の全てが発明に必須のものとは限らず、また、複数の特徴は任意に組み合わせられてもよい。さらに、添付図面においては、同一若しくは同様の構成に同一の参照番号を付し、重複した説明は省略する。

**【0010】**

**<第一実施形態>**

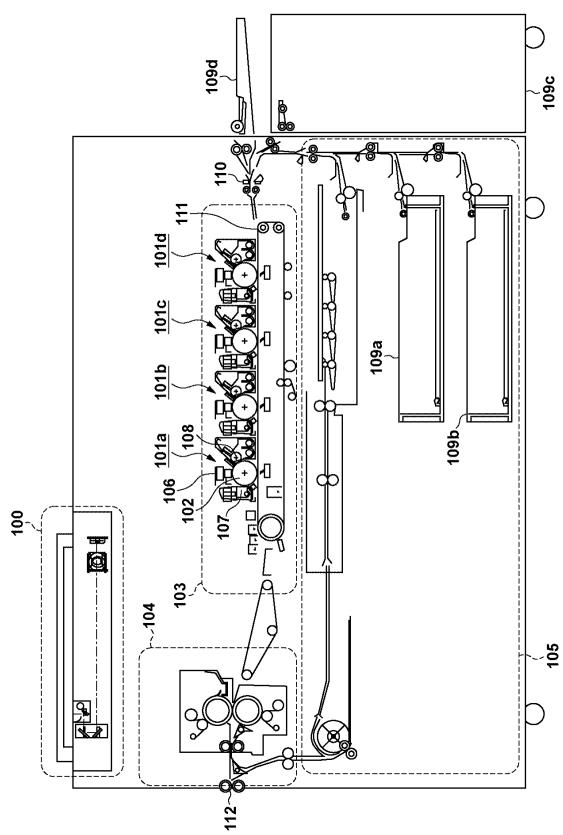

図1は、本実施形態による画像形成装置の概略的な構成図である。読み取部100は、原稿台に置かれた原稿を光学的に読み取って、読み取結果を表す画像データを生成する。作像部103は、例えば、読み取部100によって生成された画像データに基づき、或いは、ネットワークを介して外部装置から受信する画像データに基づき、シートに画像を形成する。

**【0011】**

作像部103は、画像形成部101a、101b、101c及び101dを有する。画像形成部101a、101b、101c及び101dは、それぞれ、ブラック、イエロー、マゼンタ及びシアンのトナー像を形成する。画像形成部101a、101b、101c及び101dの構成は同様であり、以下では、総称して画像形成部101とも表記する。画像形成部101の感光体102は、画像形成時、図の時計回り方向に回転駆動される。帯電器107は、感光体102を帯電させる。露光装置である露光ヘッド106は、画像データに応じて感光体102を露光し、感光体102に静電潜像を形成する。現像器108は、感光体102の静電潜像をトナーで現像する。感光体102のトナー像は、転写ベルト111上を搬送されるシートに転写される。なお、各感光体102のトナー像を重ねてシートに転写することで、ブラック、イエロー、マゼンタ及びシアンとは異なる色を再現することができる。

**【0012】**

搬送部105は、シートの給送及び搬送を制御する。具体的には、搬送部105は、内部格納ユニット109a及び109bと、外部格納ユニット109cと、手差しユニット109dと、の内の指定されたユニットから画像形成装置の搬送路にシートを給送する。給送されたシートは、レジストレーションローラ110まで搬送される。レジストレーションローラ110は、各感光体102のトナー像がシートに転写される様に、所定タイミングでシートを転写ベルト111上に搬送する。上述した様に、転写ベルト111上を搬

10

20

30

40

50

送されている間に、シートにはトナー像が転写される。定着部 104 は、トナー像が転写されたシートを加熱・加圧することによりトナー像をシートに定着させる。トナー像の定着後、シートは排出口ーラ 112 によって画像形成装置の外部に排出される。

【0013】

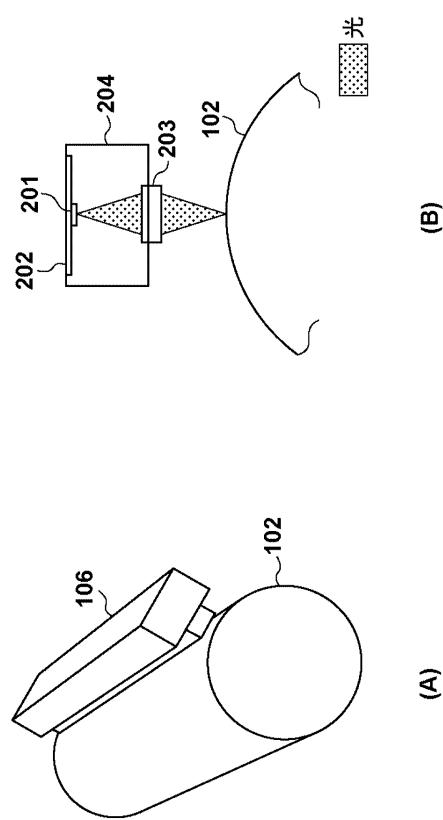

図 2 (A) 及び図 2 (B) は、感光体 102 及び露光ヘッド 106 を示している。露光ヘッド 106 は、発光点群 201 と、発光点群 201 が実装されるプリント基板 202 と、ロッドレンズアレイ 203 と、ロッドレンズアレイ 203 及びプリント基板 202 を保持するハウジング 204 と、を有する。ロッドレンズアレイ 203 は、発光点群 201 から射出された光を感光体 102 上に集光して、感光体 102 に所定サイズの結像スポットを形成する。

10

【0014】

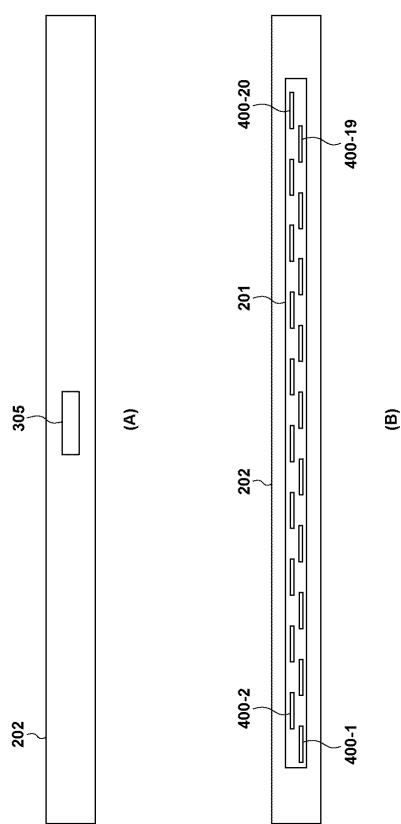

図 3 (A) 及び図 3 (B) は、プリント基板 202 を示している。なお、図 3 (A) は、コネクタ 305 が実装されている面を示し、図 3 (B) は、発光点群 201 が実装されている面 (コネクタ 305 が実装されている面とは反対側の面) を示している。本実施形態において、発光点群 201 には、20 個の発光チップ 400-1~400-20 が含まれる。発光チップ 400-1~400-20 は、主走査方向に沿って、2 列の千鳥状に配列される。以下の説明において、発光チップ 400-1~400-20 を総称して発光チップ 400 とも表記する。各発光チップ 400 は、複数の発光点 (発光素子) を有する。プリント基板 202 の各発光チップ 400 は、コネクタ 305 を介して、制御部である画像コントローラ 700 (図 7) に接続される。

20

【0015】

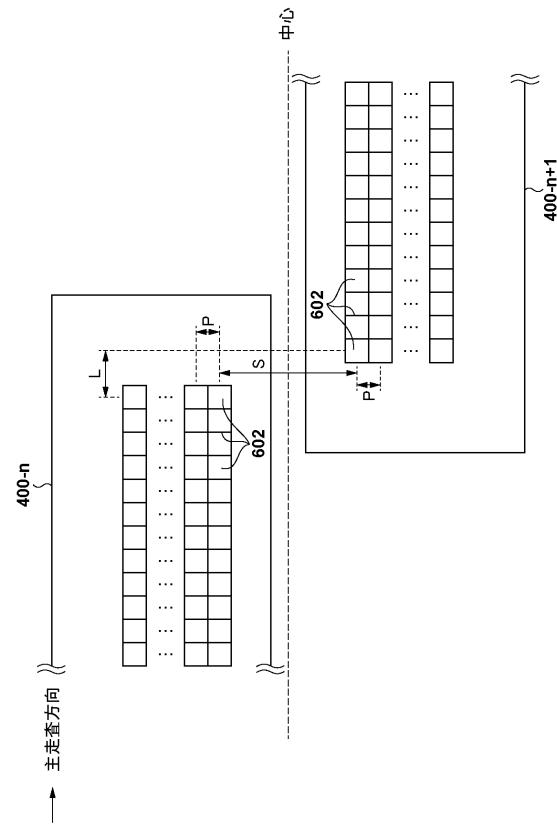

図 4 は、発光チップ 400 と、発光チップ 400 に設けられた発光点 602 の配置の説明図である。1 つの発光チップ 400 は、主走査方向に沿って配列された 748 個の発光点 602 のセットを、複数、有する。なお、複数のセットは、主走査方向とは直交する副走査方向に沿って配列される。この様に、発光チップ 400 は、主走査方向と副走査方向の両方に沿って二次元状に配置される。以下の説明においては、一例として、セット数を 4 とする。つまり、以下の例示的な実施形態において、発光チップ 400 は、主走査方向に沿って配列された 748 個の発光点 602 のセットを 4 つ、つまり、計 2992 個の発光点 602 を有するものとする。主走査方向において隣接する発光点 602 のピッチは、1200 dpi の解像度に対応する約 21.16 μm である。したがって、1 セットの 748 個の発光点 602 の主走査方向の長さは約 15.8 mm である。また、副走査方向において隣接する発光点 602 のピッチ (図 4 の長さ P) も、1200 dpi の解像度に対応する約 21.16 μm である。さらに、主走査方向において隣接する 2 つの発光チップ 400 の発光点 602 間のピッチ (図 4 の長さ L) も 1200 dpi の解像度に対応する約 21.16 μm である。

30

【0016】

図 5 は、発光チップ 400 の平面図である。発光チップ 400 の複数の発光点 602 は、例えば、シリコン基板である発光基板 402 の上に形成される。また、発光基板 402 には、複数の発光点 602 を制御するための回路部 406 が形成される。パッド 408-1~408-9 には、画像コントローラ 700 と通信するための信号線や、電源に接続するための電源線や、グラウンドに接続するためのグラウンド線が接続される。信号線や、電源線や、グラウンド線は、例えば、金でできたワイヤである。

40

【0017】

図 6 は、図 5 の A-A 線での断面の一部を示している。発光基板 402 上には複数の下部電極 504 が形成される。隣接する 2 つの下部電極 504 の間には、長さ d のギャップが設けられる。下部電極 504 の上には発光層 506 が設けられ、発光層 506 の上には上部電極 508 が設けられる。上部電極 508 は、複数の下部電極 504 に対する 1 つの共通電極である。下部電極 504 と上部電極 508 との間に所定の電圧が印加されると、下部電極 504 から上部電極 508 に電流が流れることで発光層 506 が発光する。したがって、1 つの下部電極 504 の領域に対応する発光層 506 の領域が 1 つの発光点 60

50

2に対応する。即ち、本実施形態では、発光基板402は複数の発光点を含む。なお、発光点は発光部と呼ばれても良い。

【0018】

発光層506には、例えば、有機EL膜を使用することができる。また、発光層506には、無機EL膜を使用することができる。上部電極508は、発光層506の発光波長を透過させる様に、例えば、酸化インジウム錫(ITO)などの透明電極で構成される。なお、本実施形態では、上部電極508の全体が発光層506の発光波長を透過させているが、上部電極508の全体が発光波長を透過させる必要はない。具体的には、各発光点602からの光が射出される領域が発光波長を透過させれば良い。

【0019】

なお、図6では、1つの連続的な発光層506が形成されているが、下部電極504の幅Wと同等の幅を各々が有する複数の発光層506が下部電極504の上にそれぞれ形成されても良い。また、図6では、上部電極508は複数の下部電極504に対する1つの共通電極であるが、下部電極の幅Wと同等の幅を各々が有する複数の上部電極508が下部電極504のそれぞれに対応して形成されてもよい。また、各発光チップ400の下部電極504のうち第1の複数の下部電極504が第1の発光層506により覆われ、第2の複数の下部電極504が第2の発光層506により覆われてもよい。また、各発光チップ400の下部電極504のうち第1の複数の下部電極504に対応して第1の上部電極508が共通に形成され、第2の複数の下部電極504に対応して第2の上部電極508が共通に形成されてもよい。これらのような構成においても、1つの下部電極504と、当該下部電極504に対応する発光層506及び上部電極508の領域が1つの発光点(発光素子)602を構成する。

10

【0020】

図7は、発光チップ400の制御構成を示している。データ切替部705と、各発光チップ400とは、複数の信号線(ワイヤ)により接続される。具体的には、データ切替部705と、発光チップ400-n(nは1から20までの整数)は、信号線DATA\_nと、信号線WRITE\_nと、により接続される。信号線DATA\_nは、データ切替部705が画像データを発光チップ400-nに送信するために使用される。信号線WRITE\_nは、データ切替部705が発光チップ400-nのレジスタに制御データを書き込むために使用される。

20

【0021】

また、データ切替部705と、総ての発光チップ400は、1つの信号線CLK、1つの信号線SYNC及び1つの信号線ENにより接続される。信号線CLKは、信号線DATA\_n及びWRITE\_nでのデータの送信におけるクロック信号を送信するために使用される。データ切替部705は、クロック生成部702からの基準クロック信号に基づき生成したクロック信号を信号線CLKに出力する。信号線SYNC及び信号線ENに送信される信号については後述する。

【0022】

CPU701は、画像形成装置の全体を制御する。画像データ生成部703は、読み取り部100又は外部装置から受信した画像データに対して中間調処理等の各種画像処理を行つて、各発光チップ400の発光点602の発光のオン・オフを制御するための画像データを生成する。画像データ生成部703は、生成した画像データをデータ切替部705に送信する。レジスタアクセス部704は、各発光チップ400内のレジスタに書き込む制御データをCPU701から受信してデータ切替部705に送信する。

40

【0023】

図8は、発光チップ400のレジスタに制御データを書き込む場合における各信号線の信号を示している。信号線ENには、通信の間、ハイレベルとなって通信中であることを示すイネーブル信号が出力される。データ切替部705は、イネーブル信号の立ち上がりに同期して、スタートビットを信号線WRITE\_nに送信する。続いて、データ切替部705は、書き込み動作であることを示すライト識別ビットを送信し、その後、制御データ

50

を書き込むレジスタのアドレス（本例では4ビット）と、制御データ（本例では8ビット）を送信する。データ切替部705は、レジスタに書き込む際、例えば、信号線CLKに送信するクロック信号の周波数を3MHzとする。

#### 【0024】

図9は、各発光チップ400に画像データを送信する場合における各信号線の信号を示している。信号線SYNCには、感光体102における1ラインの露光タイミングを示す周期的なライン同期信号が出力される。感光体102の周速度を200mm/sとし、副走査方向の解像度を1200dpi（約21.16μm）とすると、ライン同期信号は、約105.8μsの周期で出力される。データ切替部705は、ライン同期信号の立ち上がりに同期して、画像データを信号線DATA1～DATA20に送信する。本実施形態において、各発光チップ400は、2992個の発光点602を有するため、約105.8μsの周期内に計2992個の発光点602それぞれの発光・非発光を示す画像データを各発光チップ400に送信する必要がある。約105.8μsの期間内に計2992個の発光点602に対する画像データを送信するため、本例では、図9に示す様に、画像データの送信の際、データ切替部705は、信号線CLKに送信するクロック信号の周波数を30MHzに設定する。

10

#### 【0025】

図10は、1つの発光チップ400-nの機能ブロック図である。図5にも示す様に、発光チップ400は、9個のパッド408-1～408-9を有する。パッド408-1及びパッド408-2は、電源線により、電源電圧VCCに接続される。発光チップ400の回路部406の各回路には、この電源電圧VCCによる電力が供給される。パッド408-3及びパッド408-4は、グラウンド線により、グラウンドに接続される。回路部406の各回路及び上部電極508は、パッド408-3及びパッド408-4を介してグラウンドに接続される。信号線CLKは、パッド408-5を介して、転送部1003、レジスタ1102及びラッチ部1004-001～748に接続される。信号線SYNC及びDATA\_nは、パッド408-6及び408-7を介して、転送部1003に接続される。信号線EN及びWRITE\_nは、パッド408-8及び408-9を介して、レジスタ1102に接続される。上述した様に、レジスタ1102には、制御情報を示す制御データが格納される。制御情報の詳細については後述する。

20

#### 【0026】

30

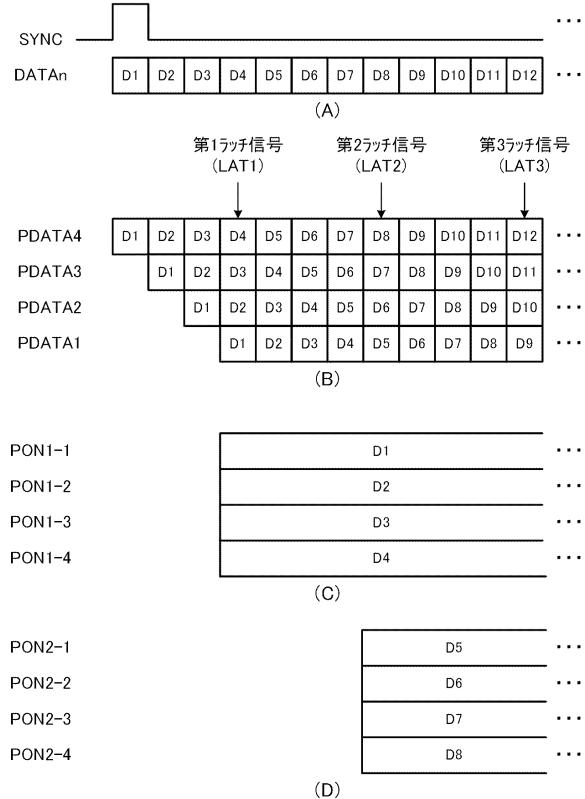

以下、図11～図14を用いて転送部1003及びラッチ部1004-001～1004-748（総称してラッチ部1004とも表記する。）の動作について説明する。なお、転送部1003は、信号線SYNCからのライン同期信号を起点として、クロック信号に同期して、それが1つの発光点602の発光・非発光を示す画像データをD1、D2、D3…D2992の順で受信するものとする。図14（A）は、転送部1003が画像データD1～D12までを受信した状態を示している。

#### 【0027】

図11は、転送部1003の構成図である。転送部1003には、信号線CLKからのクロック信号と、信号線SYNCからのライン同期信号と、信号線DATA\_nからの画像データが入力される。Dフリップフロップ1101-1～1101-8は、クロック信号に従い動作する。Dフリップフロップ1101-1は、DATA\_nから受信する画像データを順に信号線PDATA4に出力する。Dフリップフロップ1101-2は、DATA\_nから受信する画像データをDフリップフロップ1101-1が出力する画像データより1クロック分だけ遅延させて信号線PDATA3に出力する。同様に、Dフリップフロップ1101-3及び1101-4は、DATA\_nから受信する画像データをDフリップフロップ1101-1が出力する画像データより2クロック分及び3クロック分だけ遅延させて信号線PDATA2及びPDATA1に出力する。

40

#### 【0028】

図14（B）は、転送部1003が信号線PDATA1～PDATA4に出力する画像データを示している。図14（B）に示す様に、転送部1003が信号線PDATA4に

50

画像データD4を出力するタイミングにおいて、転送部1003は信号線PDATA3、PDATA2、PDATA1に、画像データD3、D2、D1を出力している。より一般的には、転送部1003が信号線PDATA4に画像データD(4m)(mは、1~748までの整数)を出力するタイミングにおいて、転送部1003は信号線PDATA3、PDATA2、PDATA1に、画像データD(4m-1)、D(4m-2)、D(4m-3)を出力する。

#### 【0029】

転送部1003は、Dフリップフロップ1101-5~1101-8により、ライン同期信号を遅延させ、転送部1003が信号線PDATA4にD4を出力するタイミングにおいて、信号線LAT1に第1ラッチ信号を出力する。

10

#### 【0030】

図12は、ラッチ部1004-001の構成図である。Dフリップフロップ1202-1~1202-4及びラッチ回路1201-1~1201-4は、信号線CLKからのクロック信号に従い動作する。ラッチ回路1201-1~1201-4には、信号線PDATA4~PDATA1からの画像データと、信号線LAT1からの第1ラッチ信号が入力される。ラッチ回路1201-1~1201-4は、信号線LAT1からの第1ラッチ信号を受信すると、そのときに信号線PDATA4~PDATA1に出力されている値をラッチし、図14(C)に示す様に、ラッチした値に基づく駆動信号を信号線PON1-4~PON1-1に出力する。図14(C)によると、信号線PON1-1~PON1-4は、画像データD1~D4に基づく駆動信号を出力している。本実施形態では、図4を用いて説明した様に、1つの発光チップ400は、主走査方向に沿って配列された748個の発光点602のセットを、副走査方向に沿って4つ配列した構造を有する。例えば、図5のX方向(主走査方向に対応)に沿って各セットの発光点602に1番から748番の番号を付与する。この場合、信号線PON1-4~PON1-1に出力される駆動信号は、それぞれ、4つのセットそれぞれの1番目の発光点602の駆動信号である。駆動信号は、電流駆動部1104に入力される。ラッチ部1004-001は、次のライン同期信号に基づく第1ラッチ信号を受信するまで、画像データD1~D4に基づく駆動信号を出力し続ける。つまり、画像データD1~D4に基づく駆動信号は、連続する2つのライン同期信号の期間(本例では、約105.8μs)だけ出力される。また、ラッチ部1004-001は、Dフリップフロップ1202-1~1202-4により、第1ラッチ信号を遅延させ、転送部1003が信号線PDATA4にD8を出力するタイミングにおいて、信号線LAT2に第2ラッチ信号を出力する。

20

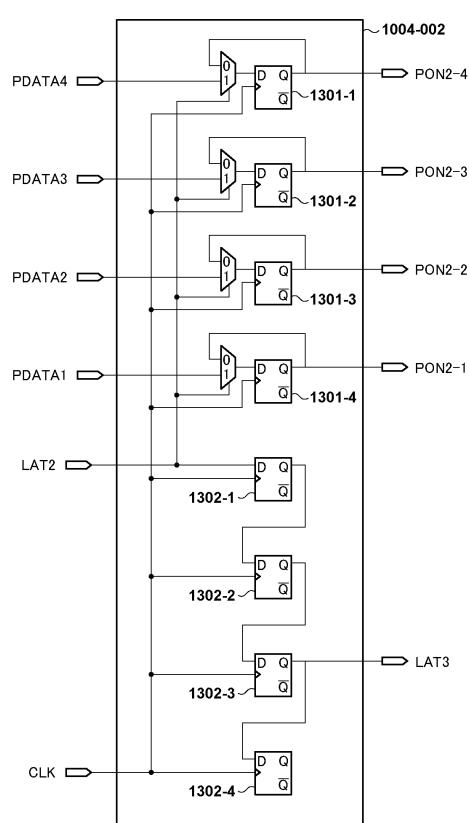

#### 【0031】

図13は、ラッチ部1004-002の構成図である。Dフリップフロップ1302-1~1302-4及びラッチ回路1301-1~1301-4は、信号線CLKからのクロック信号に従い動作する。ラッチ回路1301-1~1301-4には、信号線PDATA4~PDATA1からの画像データと、信号線LAT2からの第2ラッチ信号が入力される。ラッチ回路1301-1~1301-4は、信号線LAT2からの第2ラッチ信号を受信すると、そのときに信号線PDATA4~PDATA1に出力されている値をラッチし、図14(D)に示す様に、ラッチした値に基づく駆動信号を信号線PON2-4~PON2-1に出力する。信号線PON2-4~PON2-1に出力される駆動信号は、それぞれ、信号線PON1-4~PON1-1に出力される駆動信号により駆動される発光点602に対して主走査方向において隣側(図5の右側)の発光点602の駆動信号である。つまり、信号線PON2-4~PON2-1に出力される駆動信号は、それぞれ、4つのセットそれぞれの2番目の発光点602の駆動信号である。図14(D)によると、信号線PON2-1~PON2-4は、画像データD5~D8に基づく駆動信号を出力している。駆動信号は、電流駆動部1104に入力される。ラッチ部1004-002は、次のライン同期信号に基づく第2ラッチ信号を受信するまで、画像データD5~D8に基づく駆動信号を出力し続ける。つまり、画像データD5~D8に基づく駆動信号は、連続する2つのライン同期信号の期間(本例では、約105.8μs)だけ出力される。

40

50

また、ラッチ部 1004-002 は、D フリップフロップ 1302-1 ~ 1302-4 により、第 2 ラッチ信号を遅延させ、転送部 1003 が信号線 PDATA4 に画像データ D12 を出力するタイミングにおいて、信号線 LAT3 に第 3 ラッチ信号を出力する。

#### 【0032】

ラッチ部 1004-003 ~ 1004-748 の動作についても同様である。纏めると、ラッチ部 1004-m (m は、1 から 748 までの整数) は、それぞれ、4 つのラッチ回路を有する。ラッチ部 1004-m の 4 つのラッチ回路は、それぞれ、第 m ラッチ信号に基づき画像データ D(4m)、D(4m-1)、D(4m-2) 及び D(4m-3) をラッチし、連続する 2 つのライン同期信号の期間だけ、ラッチした画像データに基づく駆動信号を電流駆動部 1104 に出力する。なお、ラッチ部 1004-m の 4 つのラッチ回路は、第 1 セットから第 4 セットそれぞれの、主走査方向に沿って配列された 748 個の発光点 602 の内の m 番目の発光点 602 に対応する。つまり、ラッチ部 1004-m の 4 つのラッチ回路は、第 1 セットから第 4 セットそれぞれの m 番目の発光点 602 の駆動信号を出力する。また、m = 748 以外のラッチ部 1004-m は、第 m ラッチ信号に基づき、第 (m+1) ラッチ信号を生成して、ラッチ部 1004-(m+1) に出力する。この様に、ラッチ部 1004-001 ~ 1004-748 は、それぞれ、各発光点 602 の発光・非発光を制御する駆動信号を、連続する 2 つのライン同期信号の期間だけ電流駆動部 1104 に出力する。

10

#### 【0033】

図 17 は、信号線 SYNC のライン同期信号と、信号 LAT1 及び LAT2 の第 1 ラッチ信号及び第 2 ラッチ信号と、信号線 PON1-1 ~ PON1-4 及び PON2-1 ~ PON2-4 に出力される駆動信号との関係を示している。ライン同期信号の周期は、上述した様に約 105.8 μs である。第 1 ラッチ信号及び第 2 ラッチ信号の周期は、ライン同期信号と同じ約 105.8 μs である。なお、第 2 ラッチ信号のタイミングは、第 1 ラッチ信号より 4 クロック分だけ後になる。より一般的には、第 q+1 ラッチ信号 (q は 1 ~ 747 までの整数) のタイミングは、第 q ラッチ信号より 4 クロック分だけ後になる。

20

#### 【0034】

転送部 1003 は、図 17 の最初のライン同期信号に同期して画像データ D1[1] ~ D2992[1] を順に受信する。また、転送部 1003 は、図 17 の 2 番目のライン同期信号に同期して画像データ D1[2] ~ D2992[2] を順に受信する。ラッチ部 1004-001 の 4 つのラッチ回路は、図 17 の最初のライン同期信号に基づく第 1 ラッチ信号のタイミングから信号線 PON1-1 ~ PON1-4 に画像データ D1[1] ~ D4[1] に基づく駆動信号を出力する。画像データ D1[1] ~ D4[1] に基づく駆動信号の出力は、2 番目のライン同期信号に基づく第 1 ラッチ信号を受信するまで継続される。ラッチ部 1004-001 の 4 つのラッチ回路は、2 番目のライン同期信号に基づく第 1 ラッチ信号を受信すると、信号線 PON1-1 ~ PON1-4 に画像データ D1[2] ~ D4[2] に基づく駆動信号を出力する。同様に、ラッチ部 1004-002 の 4 つのラッチ回路は、最初のライン同期信号に基づく第 2 ラッチ信号のタイミングから信号線 PON2-1 ~ PON2-4 に画像データ D5[1] ~ D8[1] に基づく駆動信号を出力する。画像データ D5[1] ~ D8[1] に基づく駆動信号の出力は、2 番目のライン同期信号に基づく第 2 ラッチ信号を受信するまで継続される。ラッチ部 1004-002 の 4 つのラッチ回路は、2 番目のライン同期信号に基づく第 2 ラッチ信号を受信すると、信号線 PON2-1 ~ PON2-4 に画像データ D5[2] ~ D8[2] に基づく駆動信号を出力する。ラッチ部 1004-003 ~ 1004-748 についても同様である。

30

#### 【0035】

本実施形態において、転送部 1003 及びラッチ部 1004 は、複数の発光点 602 それぞれに対応する画像データを受信して、受信した画像データに基づき対応する発光点 602 の駆動信号を出力する出力部を構成している。より具体的には、本実施形態の 748 個のラッチ部 1004-001 ~ 1004-748 は、それぞれ、4 つのラッチ回路を有し、よって、出力部は、計 2992 個のラッチ回路を有する。各ラッチ回路は、1 つの発

40

50

光チップ400が有する2992個の発光点602の内の1つに対応する。各ラッチ回路は、対応する発光点602の画像データをラッチして、ラッチした画像データに基づき対応する発光点602のための駆動信号を出力する。

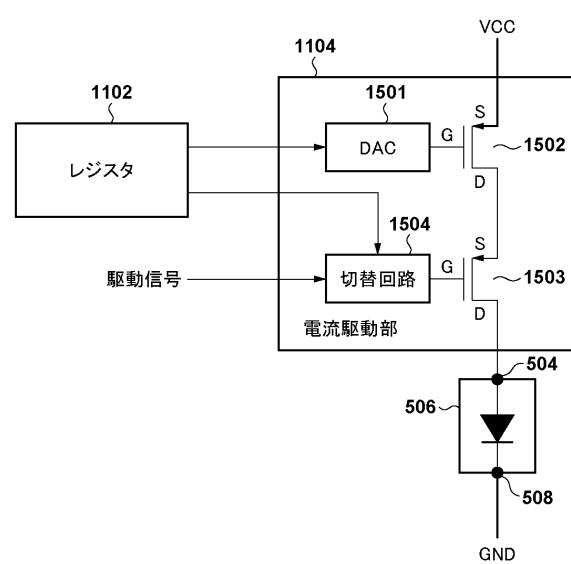

#### 【0036】

図15は、電流駆動部1104の構成を示している。なお、図15は、1つの発光点602に対応する回路部分のみを示している。本実施形態による発光チップ400は、計2992個の発光点602を有し、よって、発光チップ400は、図15に示す回路部分を2992個有する。DAC1501は、レジスタ1102に格納されている制御データが示すデジタル値に応じたアナログ電圧を出力する。FET1502は、PchのMOSFETであり、ソース端子は、電源電圧VCCに接続され、ドレイン端子は、FET1503のソース端子に接続されている。DAC1501が出力するアナログ電圧はFET1502のゲート端子に印加される。また、FET1503も、PchのMOSFETであり、ドレイン端子は、下部電極504に接続される。FET1503のゲート端子には、切替回路1504を介して、画像データ保持部1103から出力される駆動信号が入力される。駆動信号は、ハイレベル又はローレベルの2値信号であり、ハイレベルの間、FET1503はオンとなり、ローレベルの間、FET1503はオフとなる。

#### 【0037】

FET1503がオンの間、電源電圧VCCからFET1502、FET1503を介して発光層506に電流が流れ発光点602が発光する。発光点602の発光強度は、発光層506を流れる電流に応じて変化し、当該電流の値は、DAC1501が出力するアナログ電圧により制御される。つまり、各発光点602の発光強度は、レジスタ1102に格納される制御データにより制御される。なお、制御データは、各発光点602に対応するDAC1501それぞれのデジタル値を個別に示すものであっても、複数の発光点602のグループ毎に1つのデジタル値を示すものであっても良い。

#### 【0038】

なお、切替回路1504は、駆動信号をFET1503のゲート端子に印加する通常状態と、テスト状態と、を切り替えるために設けられる。テスト状態において、切替回路1504は、ハイレベルの信号をFET1503のゲート端子に印加して、FET1503を強制的にオン状態にする。なお、通常状態と、テスト状態の切替も、レジスタ1102に格納されている制御データに基づき行われる。テスト状態は、露光ヘッド106の製造の際に、任意の発光点602を発光させるため等に使用され得る。

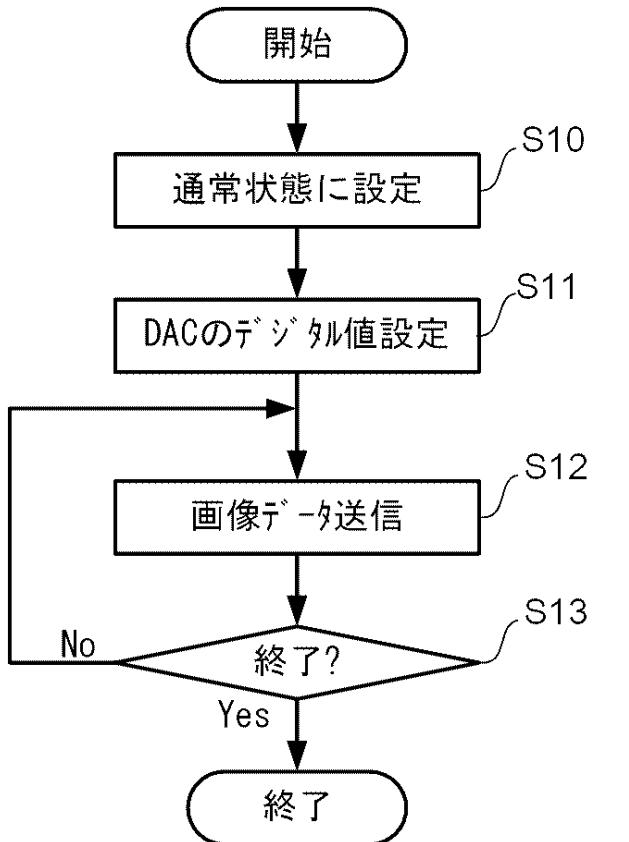

#### 【0039】

図16は、ユーザから印刷要求があった場合に画像コントローラ700が実行する処理のフローチャートである。画像コントローラ700は、S10において、各発光チップ400のレジスタ1102に、各切替回路1504の状態を通常状態にするための制御データの書き込みを行う。画像コントローラ700は、S11において、各発光点602に対応するDAC1501に設定するデジタル値を各発光チップ400のレジスタ1102に設定する。続いて、画像コントローラ700は画像形成の開始タイミングになると、S12で画像データを送信し、感光体102の露光を開始する。画像コントローラ700は、S13において、画像形成が完了したかを判定し、画像形成が完了していない場合、S12から処理を繰り返す。一方、画像形成が完了した場合、画像コントローラ700は、図13の処理を終了する。

#### 【0040】

なお、露光ヘッド106の製造時等において各発光点602を発光させる場合、画像コントローラ700は、まず、対象とする発光点602に対応するDAC1501に設定するデジタル値をレジスタ1102に設定する。その後、画像コントローラ700は、レジスタ1102に、切替回路1504の状態をテスト状態にするための制御データの書き込みを行う。試験の終了後、画像コントローラ700は、切替回路1504の状態を通常状態にするための制御データの書き込みを行う。なお、テスト状態とする発光点602についても、各発光点602それぞれに独立して指定する構成であっても、2つ以上の発光点

602を含む発光点グループ毎に指定する構成、例えば、総ての発光点602を一括して指定する構成であっても良い。

#### 【0041】

以上のように、本実施形態では、ラッチ部1004mは、第mラッチ信号が入力されたときの画像データD(4m)、D(4m-1)、D(4m-2)及びD4(m-3)をラッチし、ラッチした画像データに基づく駆動信号を電流駆動部1104に出力する。このような構成により、入力された画像データを主走査方向に転送するためのフリップフロップ回路を発光部の数に対応させて設けることなく、シリアル通信で送信されてくる画像データに基づいて、複数の発光点602を点灯させることができる。即ち、入力された画像データを主走査方向に転送するためのフリップフロップ回路が発光部の数に対応させて設けられていることに起因して発光チップが大型化したり発光チップのコストが増大したりしてしまうことを抑制することができる。即ち、従来よりも発光チップの大型化及びコストの増大を抑制することができる。

#### 【0042】

一般に、有機EL膜による発光量は、例えばガリウムヒ素等により形成されたLEDの発光量よりも小さい。本実施形態では、各発光点602の発光・非発光を制御する駆動信号が、連続する2つのライン同期信号の期間だけ電流駆動部1104に出力される。つまり、本実施形態では、連続する2つのライン同期信号の期間、発光点602を発光させることができる。この結果、連続する2つのライン同期信号の期間のうちの一部の期間だけ発光点602が発光する構成に比べて、感光体102を露光する時間を長くすることができる。その結果、トナー像が形成されるために必要な分、感光体102を露光することができ、感光体102上にトナー像が適切に形成される。即ち、連続する2つのライン同期信号の期間のうちの一部の期間だけ発光点602が発光することに起因してトナー像が形成されるために必要な分、感光体102が露光されないことを抑制することができる。

#### 【0043】

FET1503をONにする際には、電源VCCから出力される電流を発光点602に供給することに起因して電源ラインの電圧が変動し、電源ラインから放射ノイズが生じる可能性がある。本実施形態では、発光チップ400に設けられた発光点602のすべてが同時に点灯するのではなく、発光点602が4個ずつ順次点灯される。この結果、発光チップ400に設けられた発光点602のすべてを同時に点灯させるためにそれぞれの発光点602に対応するFET1503を同時にONにする場合に比べて、電源ラインの電圧の変動が抑制される。その結果、電源ラインから生じる放射ノイズを低減することができる。

#### 【0044】

なお、本実施形態において、1つの発光チップ400は、主走査方向に沿って配列された748個の発光点602のセットを4つ有するものであった。このため、各発光点602に対応する計2992個のラッチ回路を、セット数に対応する4つ毎にグループ化して計748個のグループとし、1つのグループに対応させて1つのラッチ部1004を設けていた。また、1つのグループに4つのラッチ回路が含まれるため、転送部1003は、4つの信号線PDATA1～PDATA4に画像データを順に転送していた。しかしながら、例えば、1つのグループに含まれるラッチ回路の数をセット数の整数倍にする構成であっても良い。例えば、主走査方向に沿って配列された748個の発光点602のセットを4つ有する発光チップ400に対して、1つのグループに含まれるラッチ回路の数をセット数の2倍にすると、グループ数は374となり、ラッチ部1004の数も374となる。また、この場合、転送部1003は、8つの信号線に画像データを順に転送する。なお、本発明は、1つのグループに含まれるラッチ回路の数をセット数の整数倍にすることに限定されず、例えば、セット数の整数分の1とすることもできる。また、1つのグループに含まれるラッチ回路の数をセット数とは無関係に設定することもできる。さらに、各グループに含まれる発光点602の数（又は、ラッチ回路の数）は同じでなくても良い。つまり、各グループに含まれる発光点602の数（又は、ラッチ回路の数）は、1つ以上

の任意の数にできる。

【 0 0 4 5 】

上記実施形態においては、説明のために具体的な数値を用いたが、これら具体的な数値は、例示であり、本発明は、実施形態に用いられた具体的な数値に限定されない。具体的には、1つのプリント基板202に設けられる発光チップ400の数は20に限定されず、1つ以上の任意の数とすることができます。また、各発光チップ400に含まれる発光点602の数も2992個に限定されず、他の数であっても良い。また、本実施形態において、1つの発光チップ400は、主走査方向に沿って配置された748個の発光点を4セット有していたが、セット数は1以上の任意の数とし得る。また、発光点602を主走査方向において1200 dpiの解像度に対応する約21.16 μmのピッチで配置していたが、発光点602の配置間隔も他の値であっても良い。

【 0 0 4 6 】

また、上記実施形態において、画像形成装置は、転写ベルト111を搬送されるシートに各感光体102に形成されたトナー像を転写するものであった。しかしながら、画像形成装置は、中間転写体を介して、各感光体102のトナー像をシートに転写するものであっても良い。また、画像形成装置は、複数の色のトナーを用いて画像を形成するカラー画像形成装置であっても、1つの色のトナーを用いて画像を形成するモノクロ画像形成装置であっても良い。

【 0 0 4 7 】

[ その他の実施形態 ]

本発明は、上述の実施形態の1以上の機能を実現するプログラムを、ネットワーク又は記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータにおける1つ以上のプロセッサーがプログラムを読み出し実行する処理でも実現可能である。また、1以上の機能を実現する回路（例えば、ASIC）によっても実現可能である。

【 0 0 4 8 】

本実施形態の開示は、以下の構成を含む。

( 構成 1 )

画像形成装置に実装される露光装置であって、

複数の発光素子と、

前記画像形成装置から周期的に送信される同期信号と、前記同期信号の周期内において前記画像形成装置から送信される前記複数の発光素子それぞれに対応する画像データと、を受信して、前記複数の発光素子を駆動するための、前記複数の発光素子それぞれに対応する駆動信号を出力する出力手段と、

前記複数の発光素子それぞれに対応する前記駆動信号に基づき前記複数の発光素子を駆動する駆動手段と、

を備えた発光チップを、1つ以上、有し、

前記出力手段は、前記複数の発光素子それぞれに対応する前記画像データをラッチして前記複数の発光素子それぞれに対応する駆動信号を出力するための、前記複数の発光素子それぞれに対応する複数のラッチ回路を有する、露光装置。

( 構成 2 )

前記同期信号は、前記画像形成装置に実装される感光体の1ラインの露光タイミングを示す信号である、構成1に記載の露光装置。

( 構成 3 )

前記出力手段は、前記複数の発光素子それぞれに対応する前記駆動信号を前記同期信号の周期と同じ期間だけ出力する、構成1又は2に記載の露光装置。

( 構成 4 )

前記複数のラッチ回路には前記複数の発光素子それぞれに対応する前記画像データが順に入力され、

前記出力手段は、前記同期信号に基づき、前記画像データをラッチするタイミングを前記複数のラッチ回路それぞれに示す、前記複数のラッチ回路それぞれに対応するラッチ信

10

20

30

40

50

号を生成する、構成 1 から構成 3 のいずれか 1 つに記載の露光装置。

(構成 5)

前記複数のラッチ回路それぞれに対応する前記ラッチ信号の周期は、前記同期信号の周期に等しい、構成 4 に記載の露光装置。

(構成 6)

前記複数のラッチ回路は、2 つ以上のラッチ回路を含む複数のグループにグループ化されており、

前記出力手段は、前記同期信号に基づき、同じグループに含まれる前記 2 つ以上のラッチ回路それぞれに対応する前記ラッチ信号を同じタイミングで生成する、構成 4 又は 5 に記載の露光装置。

(構成 7)

前記複数のグループそれぞれのグループに含まれる前記 2 つ以上のラッチ回路の数は同じであり、

前記出力手段は、前記複数の発光素子それぞれに対応する前記画像データを受信し、前記画像データを、前記複数のグループそれぞれのグループに含まれる前記 2 つ以上のラッチ回路の数と同じ数の複数の信号線それぞれに順に出力する転送手段を有し、

前記複数のグループそれぞれのグループに含まれる前記 2 つ以上のラッチ回路それぞれは、前記複数の信号線の内の 1 つの信号線から前記画像データを受信する、構成 6 に記載の露光装置。

(構成 8)

前記転送手段が前記複数の信号線それぞれに同じタイミングにおいて出力する前記画像データに対応する発光素子は異なる、構成 7 に記載の露光装置。

(構成 9)

前記複数の発光素子は、前記画像形成装置に実装される感光体の回転軸と平行な主走査方向と、前記主走査方向とは直交する副走査方向との両方に沿って二次元状に配置され、

前記複数のグループそれぞれのグループに含まれる前記 2 つ以上のラッチ回路の数は、前記副走査方向に沿って配置される発光素子の数の整数倍である、構成 7 又は 8 に記載の露光装置。

(構成 10)

前記発光チップは、制御情報を格納する格納手段をさらに備え、

前記駆動手段は、前記制御情報に基づき、前記駆動信号により当該駆動信号に対応する発光素子を駆動するか、前記駆動信号によらず当該駆動信号に対応する発光素子を駆動するかを切り替える切替手段を備えている、構成 1 から 9 のいずれか 1 つに記載の露光装置。

(構成 11)

前記制御情報は、前記駆動信号によらず当該駆動信号に対応する前記発光素子を駆動する場合には、当該発光素子を発光させる、構成 10 に記載の露光装置。

(構成 12)

前記制御情報は、前記複数の発光素子の内の前記駆動信号によらずに駆動する 1 つ以上の前記発光素子を一括して示す、構成 10 又は 11 に記載の露光装置。

(構成 13)

前記複数の発光素子は、有機 E L 膜を含む、構成 1 から 12 のいずれか 1 つに記載の露光装置。

(構成 14)

感光体と、

前記感光体を露光する構成 1 から 13 のいずれか 1 つに記載の露光装置と、を備えている、画像形成装置。

【0049】

発明は上記実施形態に制限されるものではなく、発明の精神及び範囲から離脱することなく、様々な変更及び変形が可能である。従って、発明の範囲を公にするために請求項を添付する。

10

20

30

40

50

【符号の説明】

【0 0 5 0】

6 0 2 : 発光点、1 0 0 3 : 転送部、1 0 0 4 - 0 0 1 ~ 1 0 0 4 - 7 4 8 : ラッチ部

10

20

30

40

50

【図面】

【図 1】

【図 2】

10

20

30

40

50

【図 3】

【図 4】

【図5】

【 四 6 】

【図7】

【図8】

10

20

30

40

50

【図 9】

【図 10】

【図 11】

【図 12】

10

20

30

40

50

【図 1 3】

【図 1 4】

【図 1 5】

【図 1 6】

【図 1 7】

10

20

30

40

50

---

フロントページの続き

(56)参考文献 特開2022-096967 (JP, A)

米国特許第05389953 (US, A)

(58)調査した分野 (Int.Cl., DB名)

B41J 2/447

B41J 2/455

G03G 15/04

H04N 1/036