(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2010년12월16일

(11) 등록번호 10-1001530

(24) 등록일자 2010년12월09일

(51) Int. Cl.

*H01L 21/301* (2006.01)

(21) 출원번호 10-2005-7013873

(22) 출원일자(국제출원일자) 2004년01월23일

심사청구일자 2009년01월23일

(85) 번역문제출일자 2005년07월27일

(65) 공개번호 10-2005-0095630

(43) 공개일자 2005년09월29일

(86) 국제출원번호 PCT/US2004/001925

(87) 국제공개번호 WO 2004/073014

국제공개일자 2004년08월26일

(30) 우선권주장

10/351,798 2003년01월27일 미국(US)

(56) 선행기술조사문헌

US20040219776 A1

US20030197289 A1

전체 청구항 수 : 총 3 항

심사관 : 남인호

## (54) 웨이퍼 스크라이브 영역 내의 금속 감소

## (57) 요약

반도체 웨이퍼(101)의 스크라이브 영역(103)으로부터 금속을 제거하는 처리를 개시한다. 제거된 금속은 스크라이브 영역의 톱 경로(saw path; 111) 내의 노출된 금속 및 스크라이브 영역의 크랙 정지 트렌치(crack stop trench) 내의 금속을 포함할 수 있다. 일례에서, 구리는 웨이퍼를 습식 에칭함으로써 스크라이브 영역으로부터 제거된다. 일례에서, 습식 에칭 처리는 웨이퍼 표면상의 노출된 장벽 응착층(exposed barrier adhesion layer; 203)의 제거 이후 수행된다. 톱 경로(111)에서의 금속 제거는, 웨이퍼의 다이 영역들(die areas; 1007)의 싱글레이션(singulation) 동안 투날(903) 상에 축적된 금속의 양을 감소시킬 수 있다.

## 대 표 도

## 특허청구의 범위

### 청구항 1

반도체 다이를 형성하는 방법에 있어서:

웨이퍼를 제공하는 단계로서, 상기 웨이퍼는 기판 및 스택층을 포함하고, 상기 스택층은 상기 기판을 덮는 상호 접속 금속을 가진 복수의 층들을 포함하고, 상기 스택층은, 복수의 다이를 분리하는 스크라이브 영역(scribe area) 내의 톱 경로(saw path)의 표면의 일부에 노출된 금속을 포함하고, 상기 노출된 금속의 일부는 상기 복수의 층들로 확장하는, 상기 웨이퍼 제공 단계;

상기 스택층을 선택적으로 덮는 유전체 패시베이션층(dielectric passivation layer)을 형성하는 단계; 및

상기 톱 경로에 리세스된 영역들(recessed regions)을 형성하기 위해, 상기 스크라이브 영역의 톱 경로에서 상기 노출된 금속을 적어도 제 1 깊이로 제거하는 단계를 포함하는, 반도체 다이 형성 방법.

### 청구항 2

삭제

### 청구항 3

삭제

### 청구항 4

삭제

### 청구항 5

삭제

### 청구항 6

삭제

### 청구항 7

삭제

### 청구항 8

삭제

### 청구항 9

삭제

### 청구항 10

삭제

### 청구항 11

삭제

### 청구항 12

삭제

### 청구항 13

삭제

#### 청구항 14

삭제

#### 청구항 15

반도체 웨이퍼에 있어서:

기판;

스택층으로서, 상기 스택층은 상기 기판을 덮고 상호접속 금속을 포함하는 복수의 층들을 포함하고, 상기 웨이퍼는 스크라이브 영역에 의해 분리된 제 1 다이 영역 및 제 2 다이 영역을 포함하는, 상기 스택층;

상기 스택층을 선택적으로 덮는 유전체 패시베이션층; 및

상기 스크라이브 영역내의 텁 경로로서, 상기 텁 경로는 금속이 제거된 상기 스택층에 적어도 하나의 리세스된 영역을 갖는, 상기 텁 경로를 포함하는, 반도체 웨이퍼.

#### 청구항 16

삭제

#### 청구항 17

삭제

#### 청구항 18

삭제

#### 청구항 19

삭제

#### 청구항 20

반도체 다이를 형성하는 방법에 있어서:

각각 텁 경로를 갖는 복수의 스크라이브 영역들에 의해 물리적으로 분리된 다수의 다이 영역들을 갖는 웨이퍼 상에 기판을 제공하는 단계;

상기 기판을 덮고 유전체 물질 및 상호접속 금속을 갖는 스택층을 형성하는 단계로서, 상기 스택층은 복수의 스크라이브 영역의 텁 경로의 표면의 일부에 노출된 금속을 포함하는, 상기 스택층 형성 단계; 및

상기 텁 경로에 리세스된 영역을 형성하기 위해 상기 노출된 금속을 적어도 제 1 깊이로 에칭함으로써 상기 스크라이브 영역 내의 상기 텁 경로를 처리하는 단계를 포함하는, 반도체 다이 형성 방법.

#### 청구항 21

삭제

#### 청구항 22

삭제

#### 청구항 23

삭제

#### 청구항 24

삭제

**청구항 25**

삭제

**청구항 26**

삭제

**청구항 27**

삭제

## 명세서

### 기술 분야

[0001]

본 발명은 일반적으로 반도체 디바이스들의 제작에 관한 것으로, 특히 웨이퍼의 반도체 다이 영역들 사이의 스크라이브 영역에서의 금속의 감소에 관한 것이다.

### 배경 기술

[0002]

구리는 반도체 웨이퍼의 스크라이브 영역 상호접속층들에서 예컨대, 테스트 구조들 및 정렬 키들을 위해 사용된다. 웨이퍼의 다이 영역들의 싱글레이션(singulation) 동안, 스크라이브 영역 상호접속층의 구리는 톱날(saw blade) 상에 축적될 수 있다. 톱날 상에 축적된 상기 구리는 웨이퍼의 크래킹(cracking) 및 칩핑(chipping)을 야기한다. 크랙들 및 칩들은 그 응용 동안 다이의 기계적 실패를 초래할 수 있다.

### 발명의 상세한 설명

[0003]

톱날 상에 축적된 구리로 인한 웨이퍼 기판의 손상을 감소시키기 위해, 각종 톱날들이 스크라이브 영역을 절삭하는데 사용될 수 있다. 제 1 톱날은 상호접속층을 절삭하기 위해 사용된다. 상호접속층으로부터 축적된 구리는 제 1 톱날 상에 누적된다. 제 2 톱날은 아래에 놓인 기판을 절삭하도록 동일한 톱 경로를 따른다. 상기 제 2 톱날은 어떠한 구리도 절삭하지 않기 때문에, 상기 톱날 상에는 구리가 거의 축적되지 않는다. 그러나, 두 개의 톱날들을 사용하는 것은 톱 부정합(misalignment)으로 인한 다른 문제들을 야기할 수 있다. 또한, 다이 에지의 레지들(ledges)은, 제 2 톱날보다 더 폭이 넓은, 축적된 구리를 갖는 톱날인, 제 1 톱날 상에 축적된 구리로 인해 생성될 수 있다.

[0004]

다이 에지에 위치하는 크랙 정지 트렌치들(crack stop trenches)은 다이의 크래킹을 방지하기 위해 사용될 수 있다. 그러나, 이러한 트렌치들은 패턴화, 패턴의 에칭, 마스크의 제거, 및 에칭을 위한 부가적 처리들을 필요로 할 수 있다. 더욱이, 크랙들은 트렌치 밑에 다이의 활성 영역으로 확산될 수 있다. 부가하여, 상호접속층에서 낮은 유전율을 갖는 저밀도의 유전 물질들의 사용으로, 다이의 트렌치들은 다이를 습기에 노출시킬 수 있다. 따라서, 웨이퍼 제작에서 크래킹의 원인을 감소시키는 것이 바람직하다.

[0005]

크래킹, 칩핑, 또는 웨이퍼에 대한 다른 손상들을 감소시키도록, 웨이퍼 절삭 디바이스의 톱날 또는 다른 형태상의 금속의 누적을 방지하기 위해 톱 경로 내의 구리 또는 다른 물질들의 양을 감소시키는 개선된 방법이 요구된다.

[0006]

본 발명은 첨부 도면들을 참조함으로써 당업자들에게 더욱 잘 이해되고, 그 새로운 대상들, 특징들, 및 이점들이 명백해질 수 있다.

### 실시예

[0017]

다른 도면들에서의 동일한 참조 기호들의 사용은 명시되지 않는 한 동일한 항목들을 나타낸다.

[0018]

다음은 본 발명을 수행하는 모드의 상세 설명을 기술한다. 설명은 제한하는 것이 아닌 본 발명을 설명하는 것으로 의도된다.

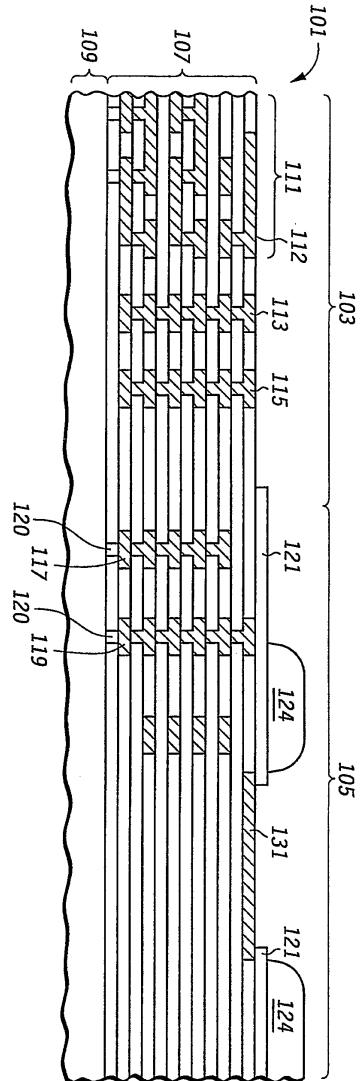

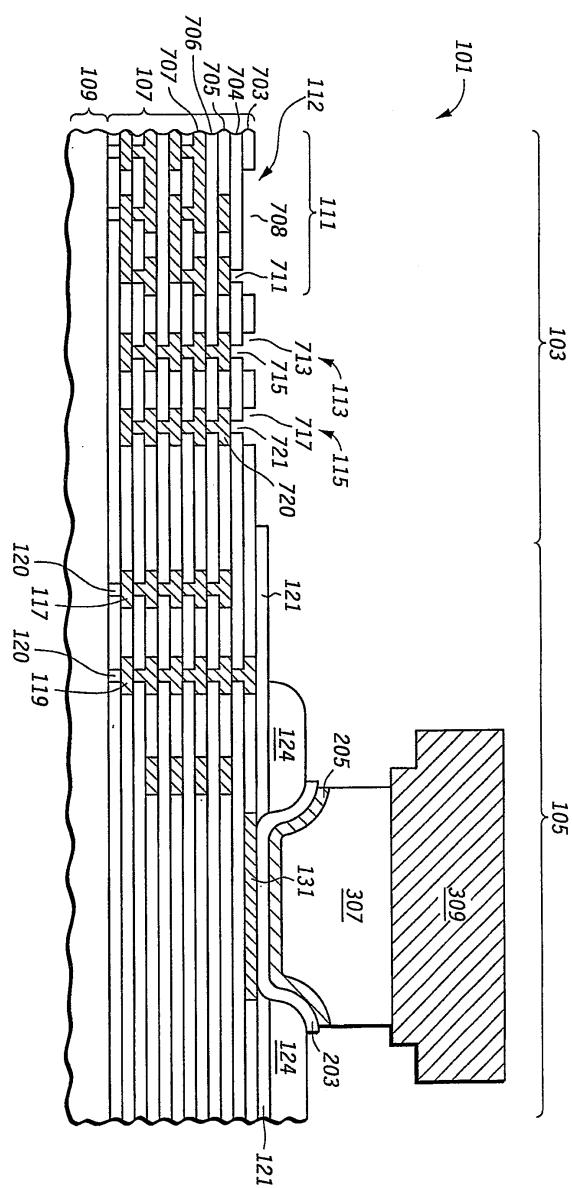

[0019]

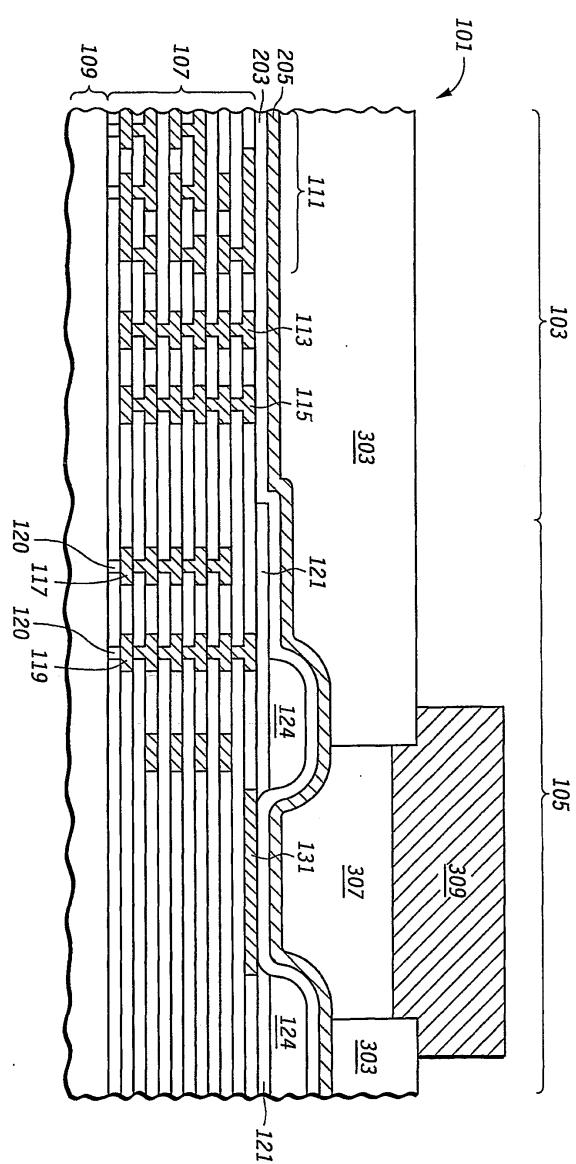

도 1은 본 발명에 따른 제조 동안 반도체 웨이퍼의 일 실시예의 부분 단면도이다. 도 1은 솔더 볼들의 형성(또는 다른 실시예들에서 외부 도전성 연결 구조들을 패키징하는 다른 다이(die-to-package)의 형성) 이전의 웨이퍼(101) 부분을 도시한다. 웨이퍼(101)의 다이 영역(105)은 반도체 다이(도시되지 않음)가 형성되는 웨이퍼

(101)의 일부이다. 웨이퍼(101)는 스크라이브 영역들(도시되지 않음)에 의해 분리된 다수의 다이 영역들(도시되지 않음)을 포함한다. 도 1은 다이 영역(105)에 인접하여 위치하는 스크라이브 영역(103) 부분을 도시한다. 제 2 다이 영역(도시되지 않음)은 도 1에 도시된 뷰에 상대적으로 스크라이브 영역(103)의 왼쪽에 위치한다. 일 실시예에서, 다이 영역(105)으로부터 형성된 다이는 반도체 패키지의 플립 칩 구성에 사용된다.

[0020] 웨이퍼(101)는 기판(109) 상부에 위치된 상호접속 스택층(107)을 포함한다. 도 1에서, 스택층(107)은 유전체 물질의 복수의 층들 및 비아들(vias) 및 트레이스(trace) 층들과 같은 상호접속 전기 도전성 구조들을 포함한다. 이러한 상호접속 전기적 도전성 구조들은 예컨대 솔더 볼들과 같은 외부 도전성 연결 구조들을 갖는 기판(109)에 형성된 전기적 결합 디바이스들(도시되지 않음) 및 금속(예컨대, 구리, 알루미늄, 은, 또는 금)으로 만들어진다. 상호접속 스택층(107)의 복수의 층들은 일 실시예에서 듀얼 상감 처리에 의해 형성되지만, 다른 실시예들에서는 예컨대 단일 상감 처리와 같은 다른 처리들에 의해 형성된다.

[0021] 웨이퍼의 다이를 싱글레이트하기 위해, 텁날 또는 다른 절삭 디바이스들이 이후의 제조 단계들 동안 다이 영역들(예컨대 105)을 서로 분리하기 위해 사용된다(도 9 참조). 도 1에서, 텁날은 텁 경로(111)에서 웨이퍼를 절삭한다. 일 실시예에서 구리로 만들어진 도전성 구조들(112)은 텁 경로(111)에 위치된다. 이러한 도전성 구조들은 제조 동안 테스트 및 정합 가이드들을 위해 사용되지만, 일반적으로 다이 영역(105)의 기판(109)에 형성된 디바이스들에 전기적으로 결합되지 않고, 그 최종 사용에서 다이의 동작 동안 이용되지 않는다.

[0022] 다이의 싱글레이션 동안, 텁 경로(111)의 이러한 도전성 구조들(112)의 구리는 텁날 상에 축적될 수 있고, 그에 따라 싱글레이션 동안 문제들을 야기할 수 있다. 다음에 기술되는 바와 같이, 텁 경로(111)의 금속 부분들은 텁날 상에 축적된 금속을 감소시키기 위해 제거된다.

[0023] 패시베이션층(passivation layer; 121)은 상호접속층(107) 상에 위치된다. 패시베이션층(121)은 예컨대 질화 실리콘과 같은 유전체 패시베이션 물질로 만들어진다. 패시베이션층(121)은 웨이퍼(101)의 다이 영역들, 예컨대 105 상에 형성되고, 다이 영역의 보호 층으로서 사용된다. 패시베이션층(121)은 외부 도전성 결합 구조들(예컨대, 솔더 볼들)을 상호접속 스택층(107)의 전기적 도전성 패드들(예컨대, 131)에 결합하기 위한 개구부들(openings)을 포함한다. 도시되는 실시예에서, 폴리아미드 층(124)은 다이 영역(105) 상에 형성되고, 스트레스 경감(stress relief) 및 다이 보호를 위해 사용된다. 폴리아미드 층(124)은 외부 도전성 연결 구조들을 상호접속 스택층(107)의 전기적 도전성 패드들(예컨대, 131)에 결합하기 위한 개구부들을 포함한다. 일부 실시예들에서 패시베이션층(121)은, 텁 경로에 제거될 금속들을 포함하지 않는 스크라이브 영역 부분들 상에 위치될 수 있다.

[0024] 에지 실 링(edge seal ring; 119) 및 크랙 정지 링(117)은 다이 영역(105)의 경계 둘레로 확장되었다. 이러한 구조들은 트레이스들 사이에 위치된 트렌치 비아들과 함께 금속 트레이스들로 만들어졌다. 실 링(119) 및 크랙 정지 링(117)의 접촉 비아들(120)은 텁스텐과 같은 다른 물질로 만들어질 수 있다.

[0025] 도전성 구조들(113 및 115)은 다이 영역(105) 주변 및 스택층(107)의 텁 경로(111)의 에지 상에 위치된 링 구조들이다. 텁날의 폭이 50 마이크론이고 스크라이브 영역의 폭이 100 마이크론인 일 실시예에서, 구조들(113 및 115)은 각각 크랙 정지(117)로부터 20 및 15 마이크론의 위치에 있게 된다. 도시되는 바와 같이, 이후 처리들에서, 도전성 구조들(113 및 115)은 스크라이브 영역의 크랙 정지 트렌치들로부터 제거된다.

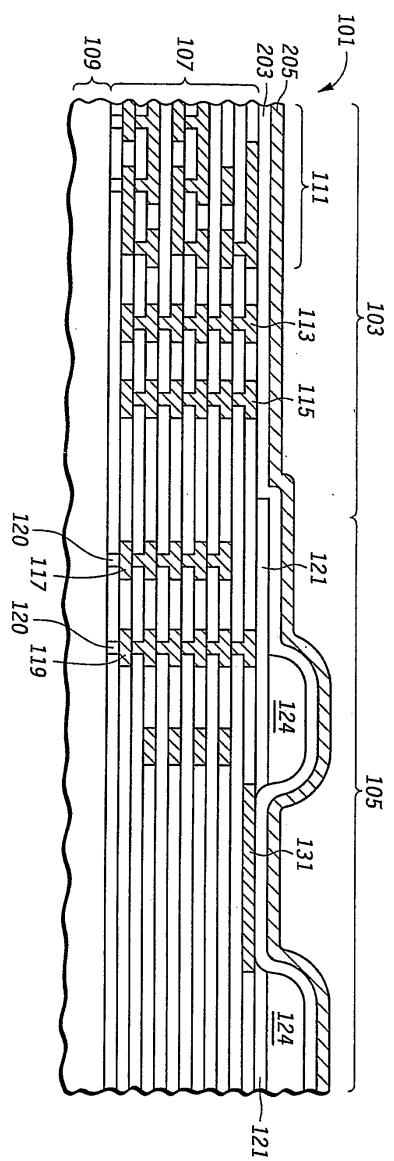

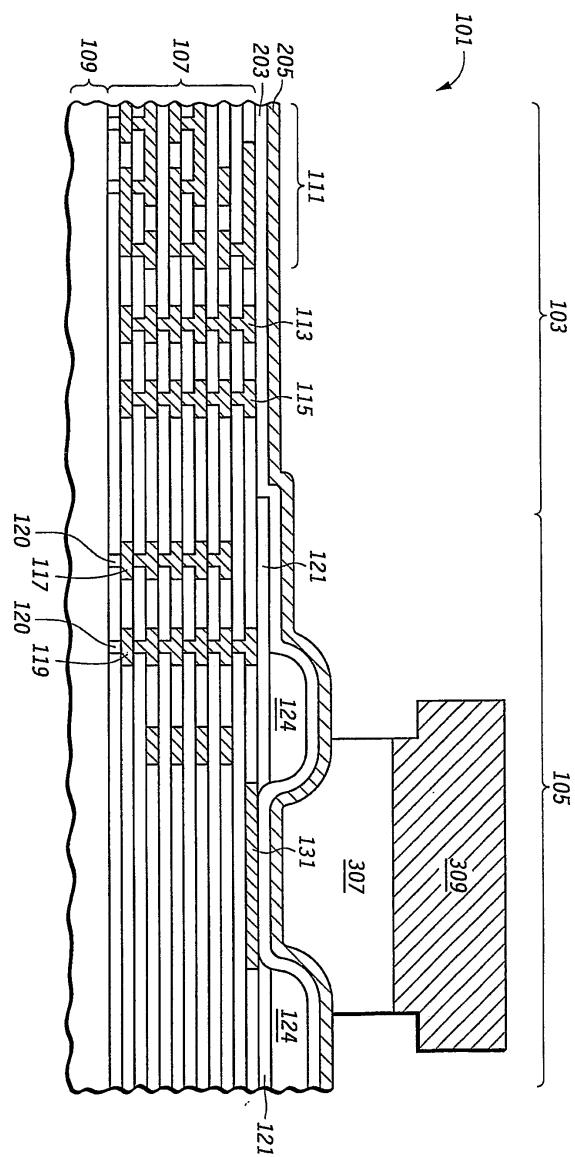

[0026] 도 2는 장벽 응착층(barrier adhesion layer; 203) 및 장벽 응착층(203) 상의 전기적 버스층(205)의 응용 이후 웨이퍼(101) 부분의 부분 단면도를 도시한다. 일 실시예에서, 층(203)은 물리적 증기 증착 처리에 의해 형성된 티타늄 텁스텐(TiW) 층이고, 2700 옹스트롬이다. 다른 실시예들에서, 층(203)은 니켈을 포함할 수 있다. 또 다른 실시예들에서, 층(203)은 질화 티타늄(Tin), 탄탈륨(Ta), 니켈(N), 또는 텁스텐(W)의 층일 수 있다. 층(205)은 구리를 포함하고, 또한 일 실시예에서, 물리적 증기 증착 처리에 의해 전체 웨이퍼 상에 적용된다. 다른 실시예들에서, 층(205)은 예컨대, 무전해도금(electroless plating) 또는 화학적 증기 증착과 같은 다른 처리들에 의해 적용될 수 있다. 층(205)은 구리 스터드(copper stud; 307)와 같은 다른 구조들을 형성하는 다른 전해도금(electroplating)을 위한 전기적 버스로서 작용한다(도 3 참조). 일 실시예에서, 층(205)은 5300 옹스트롬의 두께이다.

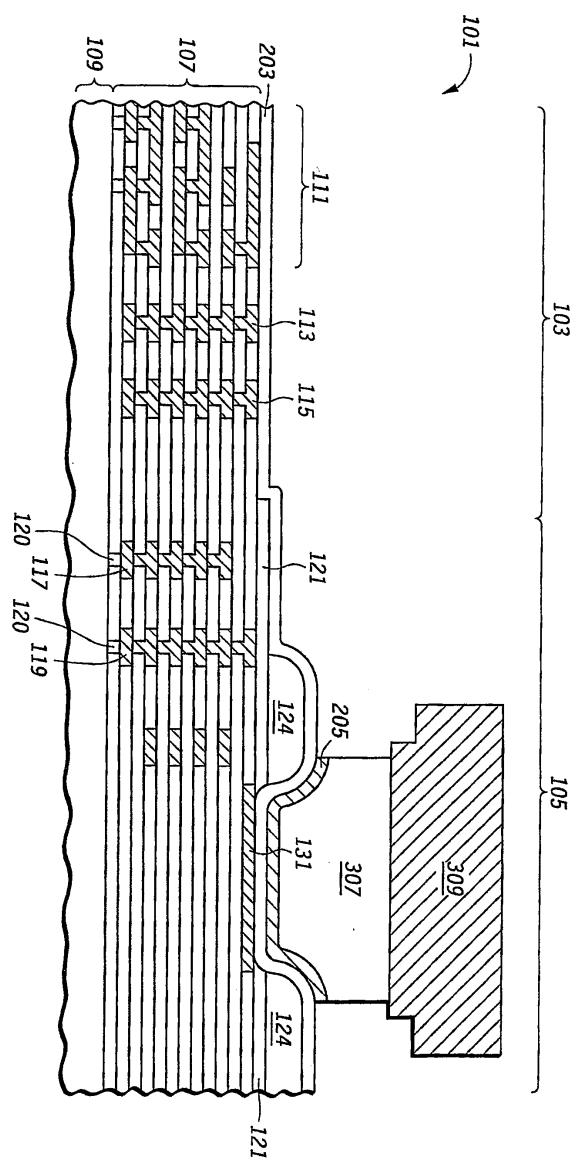

[0027] 도 3은 기판(109)의 다이의 디바이스들을 외부에 결합하기 위한 외부 도전성 접합 구조들을 형성하기 위한 구리 스터드들(예컨대, 307) 및 솔더 캡들(예컨대, 309)의 형성 이후의 웨이퍼(101)의 부분 단면도를 도시한다. 먼저 포토 레지스트층(303)은 도전성 패드들(예컨대, 131) 상의 위치들에 개구부 노출 층(205)을 갖는 층(205) 상에 패턴화된다. 이후, 구리 스터드들(예컨대, 307)은 전해도금에 의해 포토 레지스트의 개구부들에 형성된다.

다음으로, 솔더 캡들(예컨대, 309)이 또한 전해도금에 의해 형성된다.

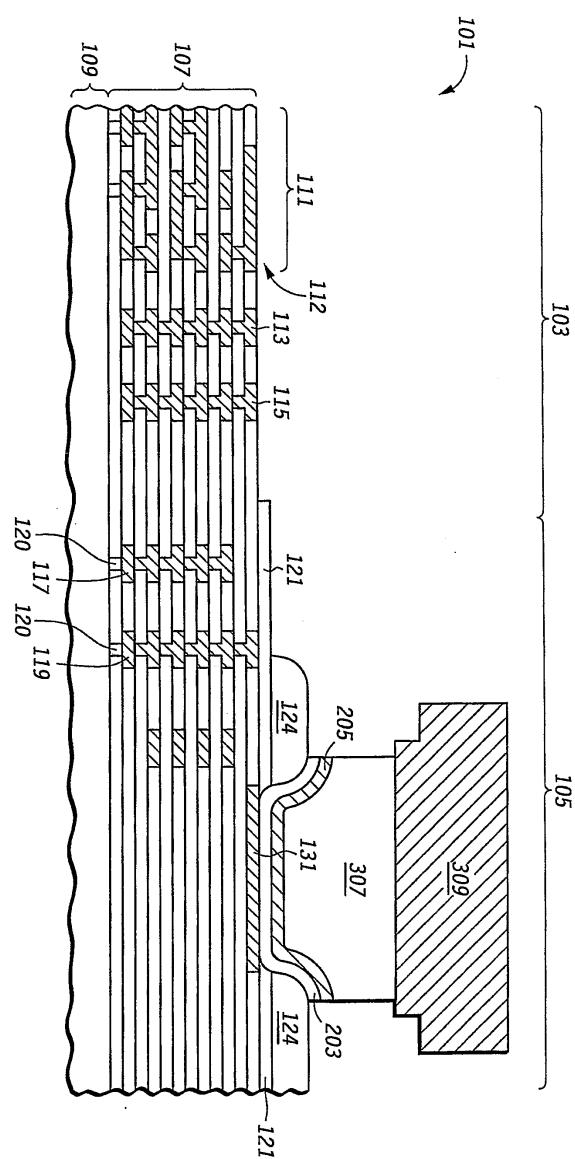

[0028] 도 4는 포토 레지스트(303)가 제거된 웨이퍼(101)의 부분 단면도를 도시한다. 포토 레지스트(303)의 제거 이후, 웨이퍼의 표면은 구리층(205)을 선택적으로 제거하기 위해 습식 에칭된다. 일 실시예에서, 습식 에칭은 코네티컷의 MACDERMID 사에 의한 METEX FA 및 METEX FB 솔더와 같은 암모니아성 인챈트(ammonical enchant)를 사용하여 수행된다. 또한, 상기 처리 동안 제거된 것은 구리 스터드들(예컨대, 307)의 측벽 부분이다. 제거된 측벽들의 부분은 대략 층(205)의 두께와 동일한 폭을 갖는다.

[0029] 도 5는 층(205)의 제거 이후의 웨이퍼(101)의 부분 단면도를 도시한다. 이후 스터드(307) 하부에 있지 않은 층(203)의 부분은 예컨대, 과산화수소를 사용한 화학 용액(chemical bath)으로 제거된다. 결과적 구조가 도 6에 도시된다.

[0030] 도 6은 층(203) 부분의 제거 이후의 웨이퍼(101)의 부분 단면도를 도시한다. 층(203) 부분의 제거 이후, 패시베이션층(121) 및/또는 솔더 캡(309) 하부에 위치하지 않는 스택층(107) 부분들이 노출된다. 이 경우, 웨이퍼(101)는 테스트 구조(112) 및 도전성 구조들(113 및 115)에서 노출된 구리를 제거하도록 습식 에칭된다. 상기 습식 에칭 처리 이후의 결과적 구조가 도 7에 도시된다.

[0031] 도 7에 도시되는 바와 같이, 상호접속층(703) 상부의 테스트 구조(112), 도전성 구조(113) 및 도전성 구조(115)의 노출된 구리는 개구부들(708, 713, 및 717)을 남기도록 습식 에칭 처리에 의해 각각 제거된다. 상호접속층(107)이 듀얼 상감 처리로 형성되었기 때문에, 층(704)의 비아들(711, 715, 및 721)의 구리 또한 제거된다. 도시되는 본 실시예에서, 스택층(705)의 테스트 구조(112), 도전성 구조(113) 및 도전성 구조(115)의 구리는, 비아 스택층(704)의 도전성 구조들(도 7에서 제거된 것으로 도시됨)과 스택층(705)의 도전성 구조들(예컨대 720) 사이에 위치된 도전성 장벽 응착층(도시되지 않음)이 존재하는 곳에서 제거되지 않는다. 장벽 응착층은 티타늄, 탄탈륨, 및 텉스텐 중 적어도 하나를 포함한다.

[0032] 스택층들(703 및 704)의 노출된 금속의 습식 에칭은 또한, 층(203)의 상부 및 솔더 캡(309)의 하부를 노출시키는, 아래에 위치된 구리층(205) 및 구리 스터드들(예컨대 307)의 측벽들로부터 구리를 제거한다. 더욱이, 스택층들(703 및 704)에서 노출된 금속을 제거하기 위해 사용되는 습식 에칭의 암모늄 이온들은 또한 노출된 패시베이션층(121) 및 폴리이미드층(124) 상에 위치된 리드(lead)의 복합 트레이스 양을 제거할 수 있다.

[0033] 습식 에칭이 스택층들(703 및 704)에서 노출된 금속을 제거한 이후, 웨이퍼(101)는 스택층(705)의 도전성 금속(예컨대, 720) 상의 장벽 응착층(도시되지 않음)을 제거하기 위해 예컨대, 과산화수소를 사용하는 다른 화학 용액으로 처리된다. 상기 용액은 또한 층(203)의 노출된 부분을 제거한다. 그 후, 웨이퍼(101)는 스택층들(705 및 706)에서 노출된 구리 예컨대, 720을 제거하도록 다른 습식 에칭 처리된다. 다음 두 스택층들에서 노출된 구리를 제거하기 위한 습식 에칭에 앞서는 도전성 장벽 응착층을 제거하기 위한 화학 용액 처리를 반복함으로써, 도전성 구조(113 및 115)의 모든 구리뿐만 아니라 톱 경로(111)의 어떠한 노출된 구리도 제거될 수 있다.

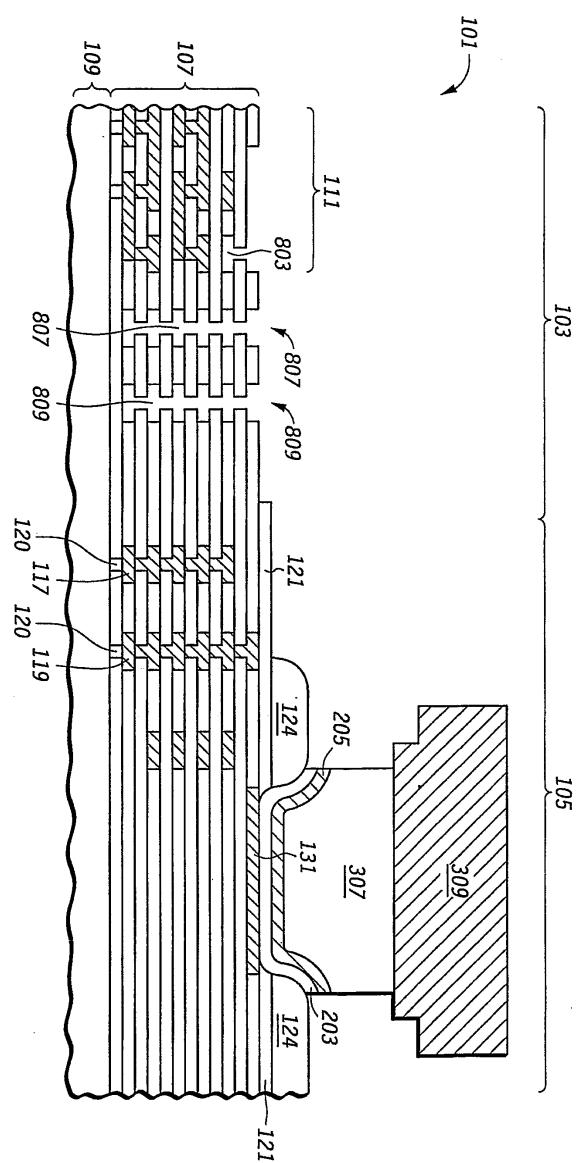

[0034] 도 8은 크랙 정지 트렌치들(807 및 809)을 각각 형성하도록 도전성 구조들(113 및 115)의 모든 구리들이 제거되는 웨이퍼(101)의 부분 단면도를 도시한다. 톱 경로(111)의 노출된 구리 또한 제거된다. 톱 경로(111)의 낮은 레벨들에 위치된 구리들이 존재할 수 있을지라도, 일부 실시예들에서 낮은 스택층들의 구리는 금속 트레이스들이 낮은 레벨들에서 더욱 제한적이고 톱날 폭의 더 작은 프랙션 인해, 층(703)의 톱날 경로의 구리의 양이 낮은 레벨들에서 보다 더 큰, 톱 상에 축적을 발생하지 않을 수 있다.

[0035] 반복되는 화학 용액 및 습식 에칭 처리들 동안, 구리 스터드(예컨대 307)뿐만 아니라 층들(205 및 203)의 노출된 부분들의 직경 또한 감소된다.

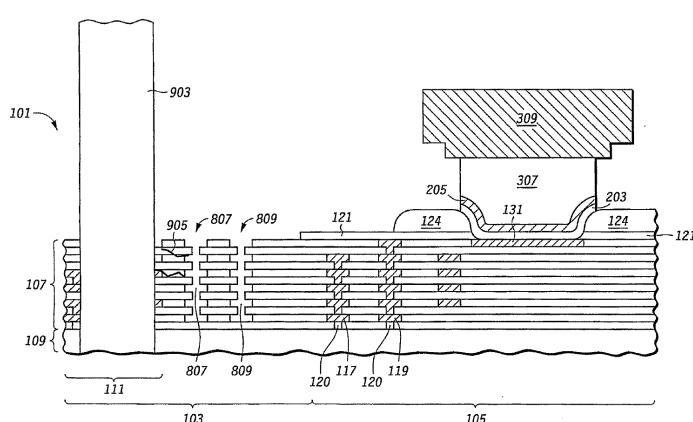

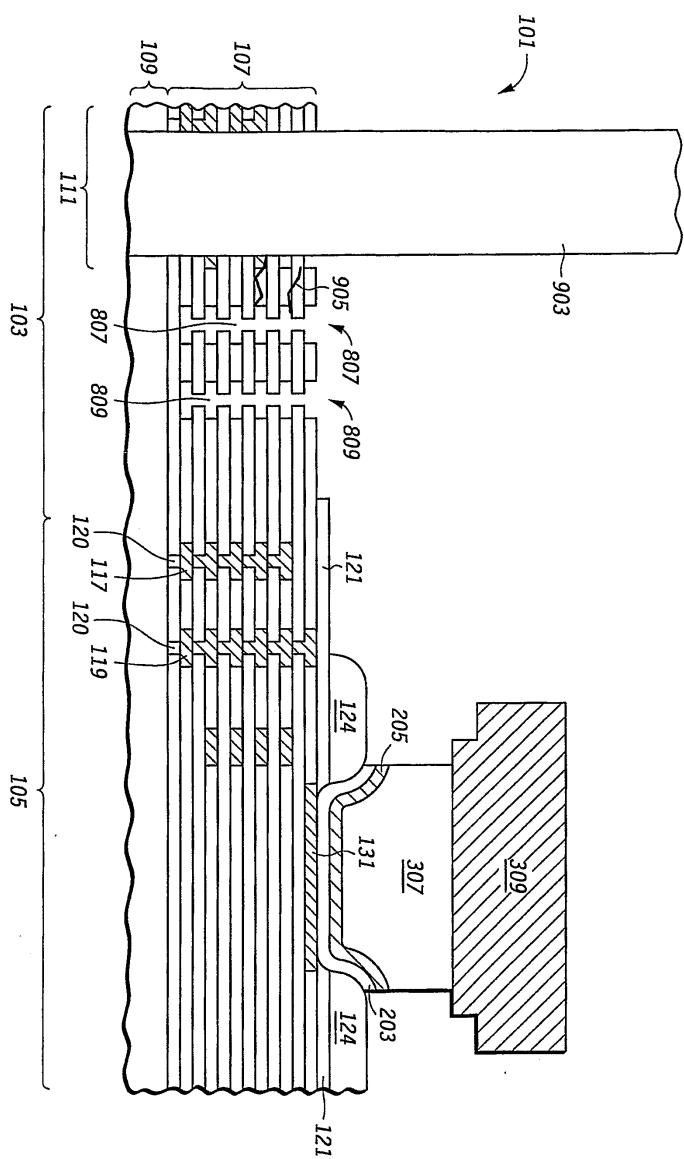

[0036] 도 9는 톱 경로(111)를 따라 톱날(903)로 절삭되는 웨이퍼(101)의 부분 단면도를 도시한다. 도시되는 본 실시예에서, 톱날(903)은 스택층(107) 및 기판(109) 양측 모두를 절삭한다. 본 실시예와 함께, 단일 톱날(예컨대 903)은, 톱 경로로부터 축적된 구리가 톱 경로의 노출된 구리의 제거로 인해 최소화되는, 전체 웨이퍼를 통해 절삭하도록 사용될 수 있다. 따라서, 싱글레이션 처리를 위한 시간이 감소될 수 있다. 부가하여, 다중 톱날들을 사용하는 정합 문제들이 마찬가지로 제거될 수 있다. 그러나, 다른 실시예들에서, 다중 톱날들은 웨이퍼를 절삭하기 위해 사용될 수 있다.

[0037] 또한, 톱 경로(111)를 통해 절삭하는 톱날(903)로 인한 크래킹은 크랙 정지 트렌치들로서 작용하는 구조들(113 및 115)에 의해 다이 영역(105)으로 확산되는 것이 억제될 수 있다.

- [0038] 다이가 싱글레이트된 이후, 캡(예컨대 309)의 솔더는 구리 스터들(예컨대 307) 상에 솔더 볼을 형성하도록 수소 퍼니스(hydrogen furnace)로 환류(reflow)된다. 다른 실시예들에서, 캡들의 솔더는 싱글레이션 이전에 환류된다. 다른 실시예들에서, 캡들의 솔더는 층(205)의 에칭 이후, 층(203)의 제거 이전에 환류된다.

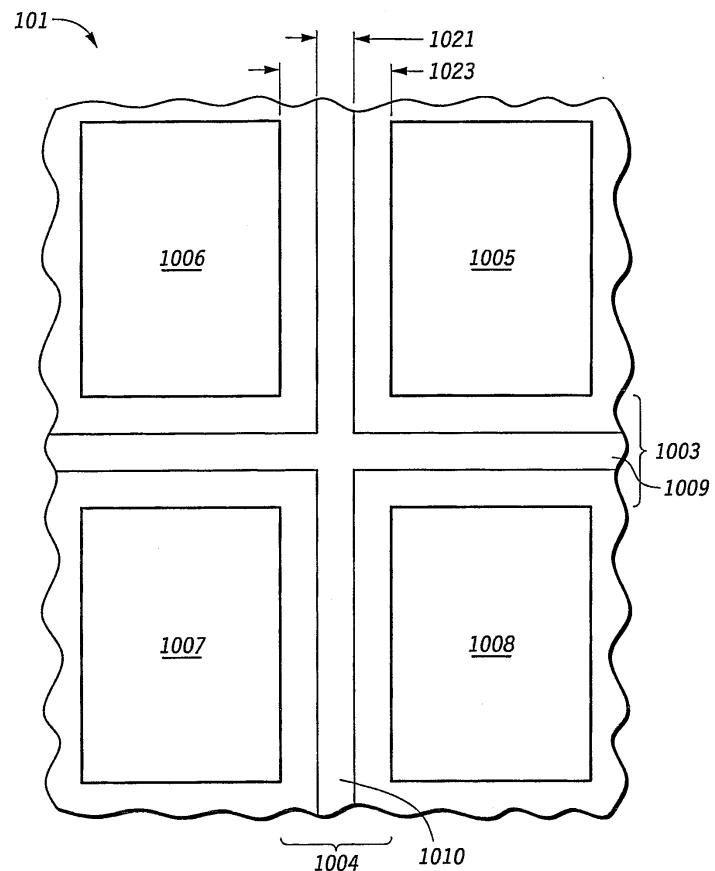

- [0039] 도 10은 웨이퍼(101)의 상부를 도시한다. 웨이퍼(101)는 도 10에 도시되는 다이 영역들(1005, 1006, 1007, 및 1008)을 갖는 다수의 다이 영역들을 포함한다. 다이 영역들 사이에 도시되는 것은 스크라이브 영역들(1003 및 1004)이다. 스크라이브 영역들(1003 및 1004) 내에 위치되는 것은 각각 톱 경로들(1009 및 1010)이다. 스크라이브 영역(1004)은 일 실시예에서 100 마이크론인 1023의 폭을 갖는다. 톱 경로(1010)는 일 실시예에서 50 내지 55 마이크론인 1021의 폭을 갖는다. 일 실시예에서, 톱 경로(1010)의 폭은 정합 및 배치를 위한 텁날(예컨대 903)의 폭 더하기 허용한계이다. 일 실시예에서, 상기 허용한계는 5 마이크론이다. 다이 영역들(1005 내지 1008)을 다이 내에 싱글레이트하기 위해, 텁날(예컨대 903)은 톱 경로(1010 및 1009)를 따라 웨이퍼(101)를 통해 절삭된다.

- [0040] 다른 실시예들에서, 도전성 구조들(113 및 115)의 모든 금속 및 톱 경로(111)의 모든 노출된 금속이 다이 영역들의 싱글레이션 이전에 제거되는 것은 아니다. 예를 들어, 싱글레이션은, 스택층들(703 및 704)(또는 일부 실시예들에서는, 층(703))에 위치된 구리만이 제거되는, 도 7에 도시되는 바와 같이 웨이퍼 구조 상에서 수행될 수 있다. 다른 실시예들에서, 일부 낮은 층들의 도전성 물질은 원활히 제거될 수 있다. 다른 예에서, 톱 경로(111)의 노출된 구리 및 스택층들(703, 704, 705 및 706)의 도전성 구조들(113 및 115) 내의 구리는 제거될 수 있고, 스택층들(707) 및 그 하부의 구리는 잔존할 것이다.

- [0041] 다른 실시예들에서, 스크라이브 영역의 도전성 구조들은 금, 은, 또는 알루미늄과 같은 다른 금속 유형들로 만들어질 수 있다. 또한, 스크라이브 영역으로부터의 금속의 제거는 다른 유형들 및/또는 구성들의 다이 구조들이 사용될 수 있다. 예를 들어, 스크라이브 영역으로부터의 금속의 제거는 폴리이미드층(124)을 갖지 않는 다이 구조를 위해 사용될 수 있다. 또한, 스크라이브 영역으로부터의 금속의 제거는 예컨대, 와이어 본드가 구리 스터드들(예컨대 307)에 부착된 솔더 캡(예컨대 309)을 사용하지 않는 다이와 같이 외부 도전성 연결 구조들의 다른 유형들을 갖는 다이 구조와 함께 사용될 수 있다. 일 실시예에서, 와이어 본드 웨이퍼의 스크라이브 영역 폭은 80  $\mu\text{m}$ 이 될 수 있고, 웨이퍼는 0.35 mm 두께이고, 30 내지 35  $\mu\text{m}$ 의 텁날이 싱글레이션을 위해 사용된다. 또한 다른 실시예들에서, 톱 경로로부터의 노출된 금속의 제거는 크랙 정지 트렌치들(807 및 809)을 구현하지 않는 다이에서 만들어질 수 있다. 다른 실시예들에서, 층들(203 및 205) 및 스터드(307)는 니켈로 만들어질 수 있다.

- [0042] 본 발명의 일 양상에서, 반도체 다이를 형성하는 방법은 웨이퍼를 제공하는 단계를 포함한다. 웨이퍼는 기판을 덮는 상호접속 금속과 함께 복수의 층들을 포함하는 스택층 및 기판을 포함한다. 스택층은 복수의 다이를 분리하는 스크라이브 영역 내의 톱 경로의 표면 부분에 노출된 금속을 포함한다. 노출된 금속의 일부는 다수의 유전체 층들로 확장한다. 방법은 스택층을 선택적으로 덮는 유전체 패시베이션층을 형성하는 단계 및 톱 경로에 리세스된 영역들(recessed regions)을 형성하도록 상기 스크라이브 영역의 톱 경로에 적어도 제 1 깊이로 노출된 금속을 제거하는 단계를 더 포함한다.

- [0043] 본 발명의 다른 양상에서, 반도체 웨이퍼는 기판 및 스택층을 포함한다. 스택층은 기판을 덮는 복수의 층들을 포함하고 상호접속 금속을 포함한다. 웨이퍼는 스크라이브 영역에 의해 분리된 제 1 다이 영역 및 제 2 다이 영역을 포함한다. 웨이퍼는 스크라이브 영역 내의 톱 경로 및 스택층을 선택적으로 덮는 유전체 패시베이션층을 더 포함한다. 톱 경로는 금속이 제거된 스택층에 적어도 하나의 리세스된 영역을 갖는다.

- [0044] 다른 양상에서, 반도체 다이의 형성 방법은 각각 톱 경로를 갖는 복수의 스크라이브 영역들로 물리적으로 분리되는 다수의 다이 영역들을 갖는 웨이퍼 상에 기판을 제공하는 단계를 포함한다. 방법은 또한 기판을 덮고 유전체 물질 및 상호접속 금속을 갖는 스택층을 형성하는 단계를 포함한다. 스택층은 복수의 스크라이브 영역의 톱 경로의 표면부에 노출된 금속을 포함한다. 방법은 또한 톱 경로에 리세스된 영역을 형성하도록 적어도 제 1 깊이로, 노출된 금속을 애칭함으로써 스크라이브 영역 내의 톱 경로를 처리하는 단계를 포함한다.

- [0045] 본 발명의 특정 실시예들이 도시되고 설명되는 동안, 본 명세서의 설명들에 기초하여 당업자들에게 이해될 것이고, 다른 변화들 및 변경들이 본 발명 및 그 광범위한 양상들을 벗어나지 않고 이루어지며, 그에 따라 청구범위가 본 발명의 실제 정신 및 범위 내의 모든 상기 변화들 및 변경들에 포함된다.

## 도면의 간단한 설명

- [0007] 도 1은 본 발명에 따른 제조 동안의 단계에서 반도체 웨이퍼의 일 실시예의 부분 단면도.

- [0008] 도 2는 본 발명에 따른 제조 동안의 다른 단계에서 반도체 웨이퍼의 일 실시예의 부분 단면도.

- [0009] 도 3은 본 발명에 따른 제조 동안의 다른 단계에서 반도체 웨이퍼의 일 실시예의 부분 단면도.

- [0010] 도 4는 본 발명에 따른 제조 동안의 다른 단계에서 반도체 웨이퍼의 일 실시예의 부분 단면도.

- [0011] 도 5는 본 발명에 따른 제조 동안의 다른 단계에서 반도체 웨이퍼의 일 실시예의 부분 단면도.

- [0012] 도 6은 본 발명에 따른 제조 동안의 다른 단계에서 반도체 웨이퍼의 일 실시예의 부분 단면도.

- [0013] 도 7은 본 발명에 따른 제조 동안의 다른 단계에서 반도체 웨이퍼의 일 실시예의 부분 단면도.

- [0014] 도 8은 본 발명에 따른 제조 동안의 다른 단계에서 반도체 웨이퍼의 일 실시예의 부분 단면도.

- [0015] 도 9는 본 발명에 따른 제조 동안의 다른 단계에서 반도체 웨이퍼의 일 실시예의 부분 단면도.

- [0016] 도 10은 본 발명에 따른 반도체 웨이퍼의 일 실시예의 부분 상단도.

### 도면

**도면1**

도면2

## 도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10