(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

20 January 2005 (20.01.2005)

PCT

(10) International Publication Number

WO 2005/006183 A2

(51) International Patent Classification<sup>7</sup>:

G06F 9/30

(21) International Application Number:

PCT/US2004/020601

(22) International Filing Date: 24 June 2004 (24.06.2004)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

10/611,344 30 June 2003 (30.06.2003) US

(71) Applicant (for all designated States except US): INTEL CORPORATION [US/US]; 2200 Mission College Boulevard, Santa Clara, CA 95052 (US).

(72) Inventors: MACY, William, Jr.; 151 Melville Avenue, Palo Alto, CA 94301 (US). DEBES, Eric; 1365 Lexington Street, Santa Clara, CA 95052 (US). ROUSSEL, Patrice; 2034 NE 37th Avenue, Portland, OR 97212 (US). NGUYEN, Huy; 16909 Isle Of Man Road, Pflugerville, TX 78660 (US).

(74) Agent: VINCENT, Lester, J.; Blakely Sokoloff Taylor & Zafman, 12400 Wilshire Boulevard, 7th Floor, Los Angeles, CA 90025 (US).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IT, LU, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

Published:

— without international search report and to be republished upon receipt of that report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

WO 2005/006183 A2

(54) Title: METHOD AND APPARATUS FOR SHUFFLING DATA

(57) Abstract: Method, apparatus, and program means for shuffling data. The method of one embodiment comprises receiving a first operand having a set of L data elements and a second operand having a set of L control elements. For each control element, data from a first operand data element designated by the individual control element is shuffled to an associated resultant data element position if its flush to zero field is not set and a zero is placed into the associated resultant data element position if its flush to zero field is not set.

## METHOD AND APPARATUS FOR SHUFFLING DATA

[0001] This patent application is a Continuation In Part of U.S. Patent Application No.

09/952,891, entitled “An Apparatus And Method For Efficient Filtering And Convolution

5 Of Content Data”, filed October 29, 2001.

[0002] The patent application is related to the following: co-pending U.S. Patent

Application No. \_\_/\_\_\_,\_\_\_, entitled “Method And Apparatus For Parallel Table Lookup

Using SIMD Instructions” filed on June 30, 2003; and co-pending U.S. Patent Application

No. \_\_/\_\_\_,\_\_\_, entitled “Method And Apparatus For Rearranging Data Between Multiple

10 Registers” filed on June 30, 2003.

### **FIELD OF THE INVENTION**

[0003] The present invention relates generally to the field of microprocessors and

computer systems. More particularly, the present invention relates to a method and

15 apparatus for shuffling data.

### **BACKGROUND OF THE INVENTION**

[0004] Computer systems have become increasingly pervasive in our society. The

processing capabilities of computers have increased the efficiency and productivity of

workers in a wide spectrum of professions. As the costs of purchasing and owning a

20 computer continues to drop, more and more consumers have been able to take advantage

of newer and faster machines. Furthermore, many people enjoy the use of notebook

computers because of the freedom. Mobile computers allow users to easily transport their

data and work with them as they leave the office or travel. This scenario is quite familiar

with marketing staff, corporate executives, and even students.

**[0005]** As processor technology advances, newer software code is also being generated to run on machines with these processors. Users generally expect and demand higher performance from their computers regardless of the type of software being used. One such issue can arise from the kinds of instructions and operations that are actually 5 being performed within the processor. Certain types of operations require more time to complete based on the complexity of the operations and/or type of circuitry needed. This provides an opportunity to optimize the way certain complex operations are executed inside the processor.

**[0006]** Media applications have been driving microprocessor development for more 10 than a decade. In fact, most computing upgrades in recent years have been driven by media applications. These upgrades have predominantly occurred within consumer segments, although significant advances have also been seen in enterprise segments for entertainment enhanced education and communication purposes. Nevertheless, future media applications will require even higher computational requirements. As a result, 15 tomorrow's personal computing experience will be even richer in audio-visual effects, as well as being easier to use, and more importantly, computing will merge with communications.

**[0007]** Accordingly, the display of images, as well as playback of audio and video data, which is collectively referred to as content, have become increasingly popular 20 applications for current computing devices. Filtering and convolution operations are some of the most common operations performed on content data, such as image audio and video data. Such operations are computationally intensive, but offer a high level of data parallelism that can be exploited through an efficient implementation using various data storage devices, such as for example, single instruction multiple data (SIMD) registers. A 25 number of current architectures also require unnecessary data type changes which

minimizes instruction throughput and significantly increases the number of clock cycles required to order data for arithmetic operations.

### **BRIEF DESCRIPTION OF THE DRAWINGS**

5    [0008]    The present invention is illustrated by way of example and not limitations in the figures of the accompanying drawings, in which like references indicate similar elements, and in which:

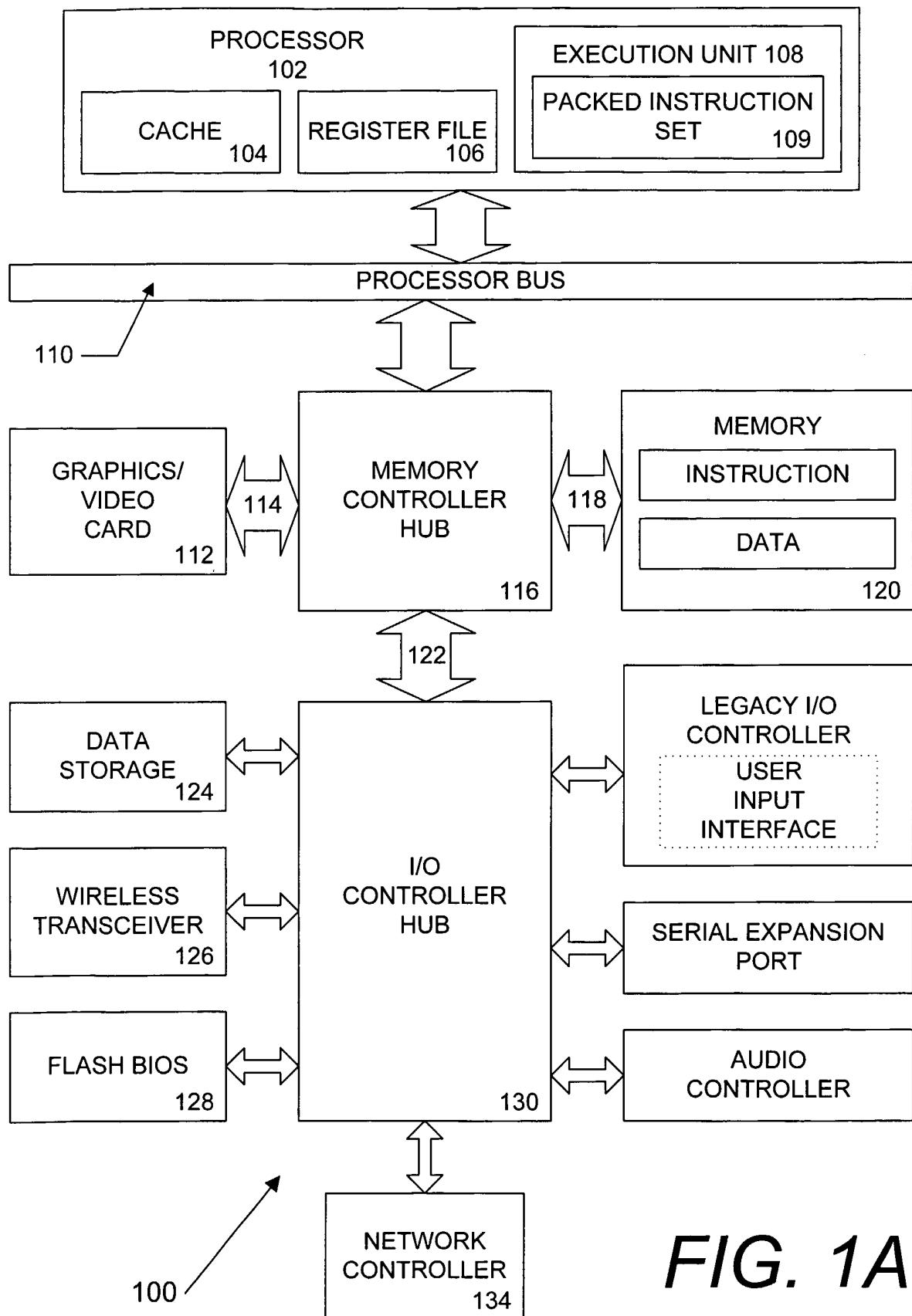

[0009]    **Figure 1A** is a block diagram of a computer system formed with a processor that includes execution units to execute an instruction for shuffling data in accordance

10    with one embodiment of the present invention;

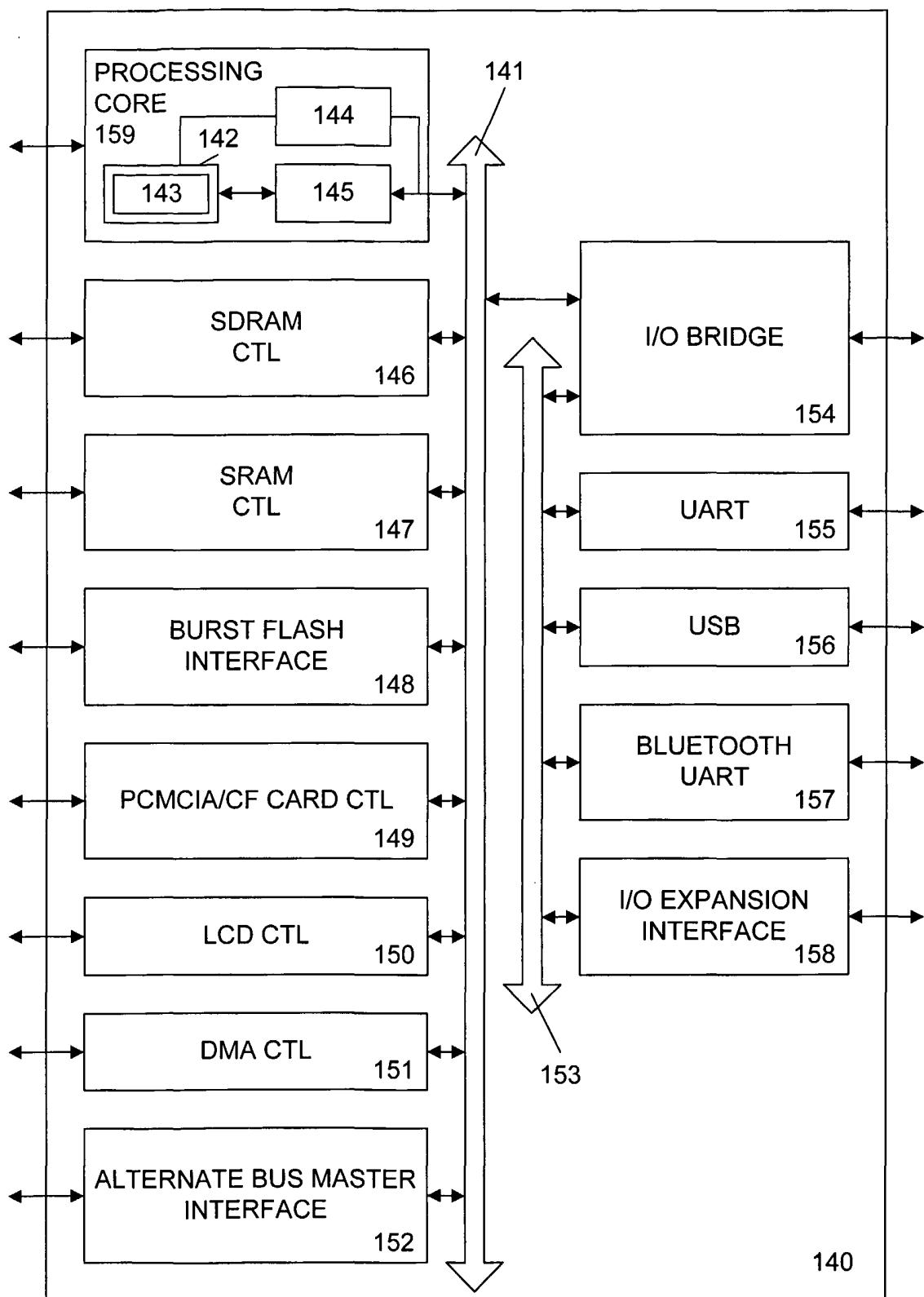

[0010]    **Figure 1B** is a block diagram of another exemplary computer system in accordance with an alternative embodiment of the present invention;

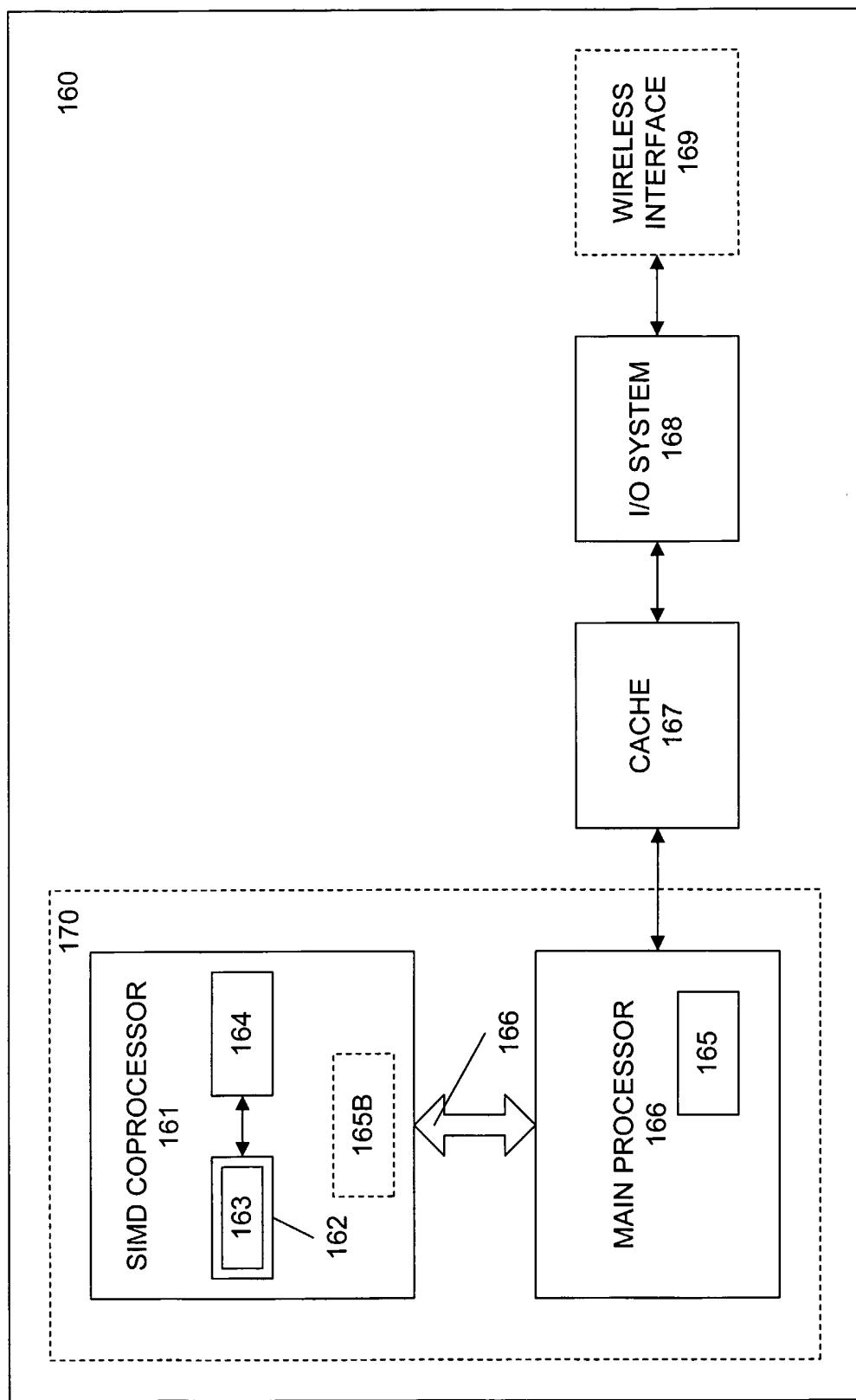

[0011]    **Figure 1C** is a block diagram of yet another exemplary computer system in accordance with another alternative embodiment of the present invention;

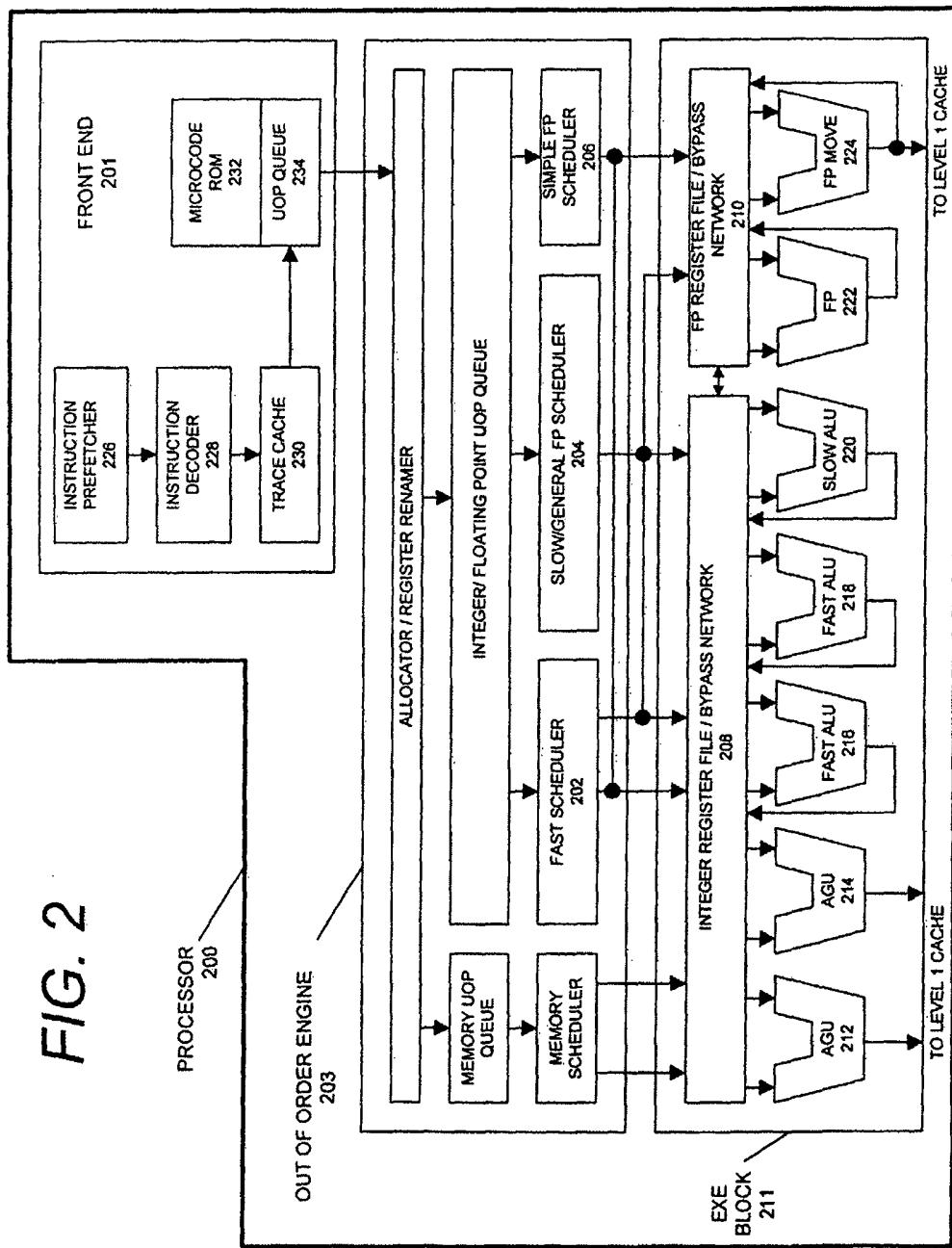

15    [0012]    **Figure 2** is a block diagram of the micro-architecture for a processor of one embodiment that includes logic circuits to perform data shuffle operations in accordance with the present invention;

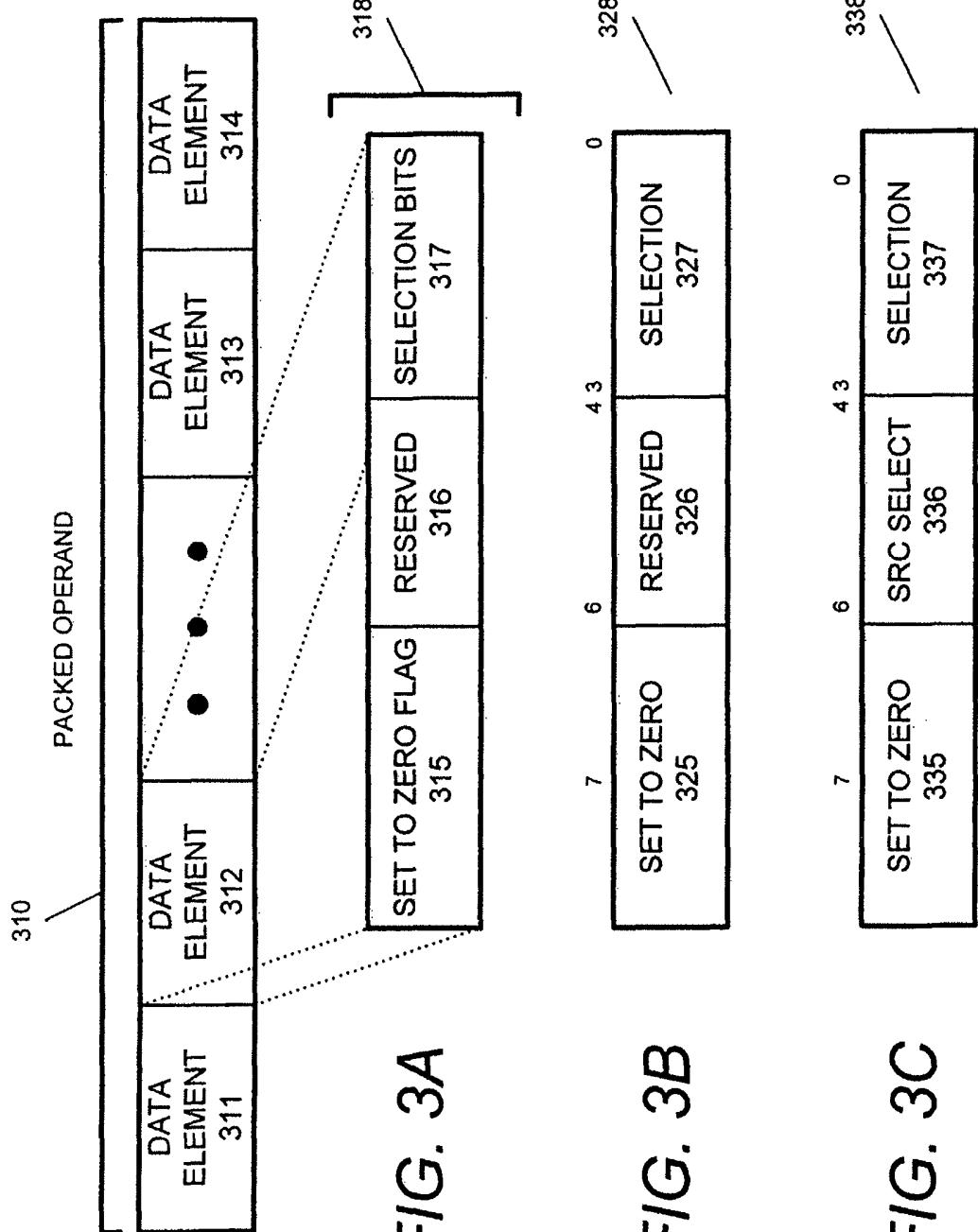

[0013]    **Figures 3A-C** are illustrations of shuffle masks according to various embodiments of the present invention;

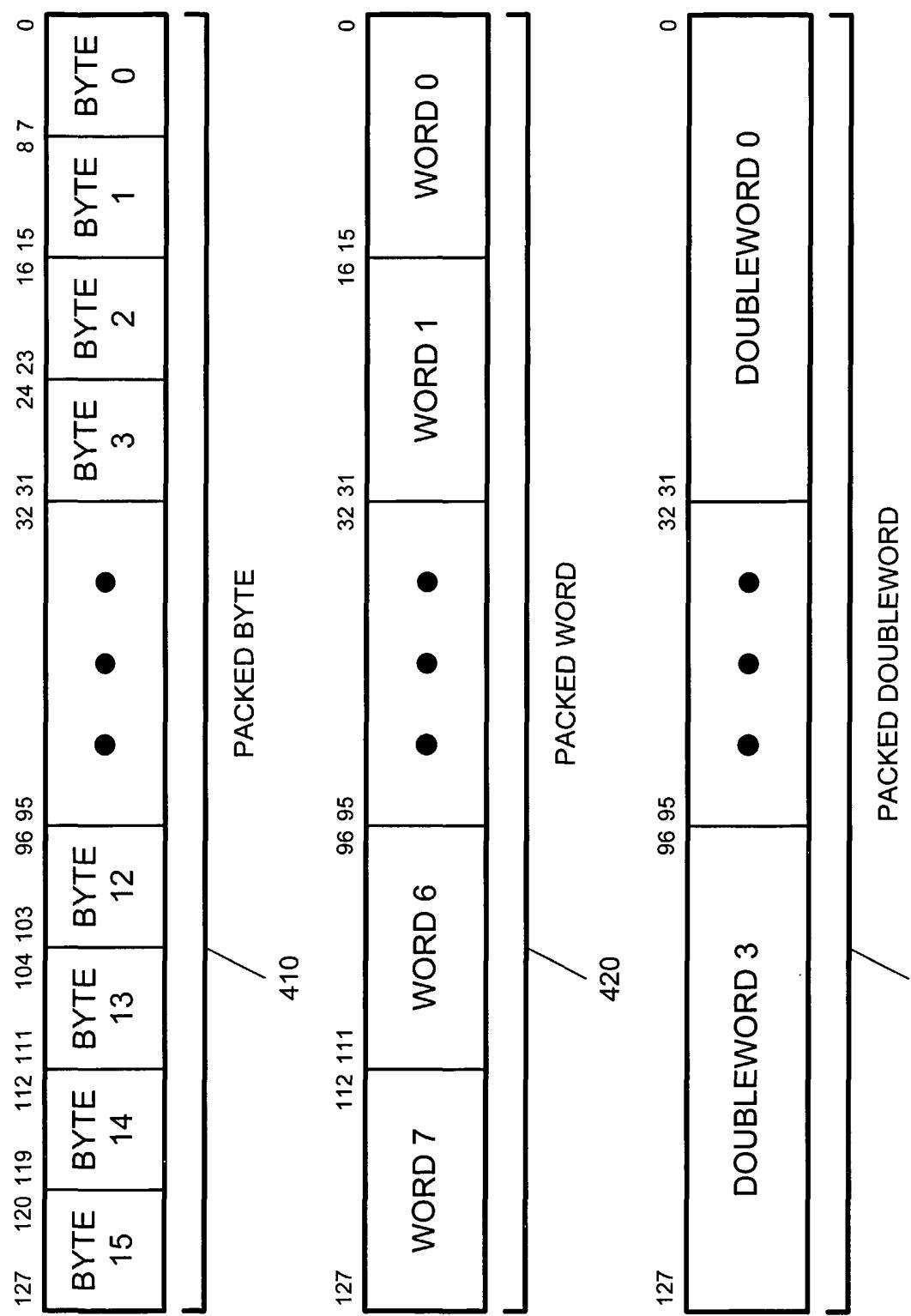

20    [0014]    **Figure 4A** is an illustration of various packed data type representations in multimedia registers according to one embodiment of the present invention;

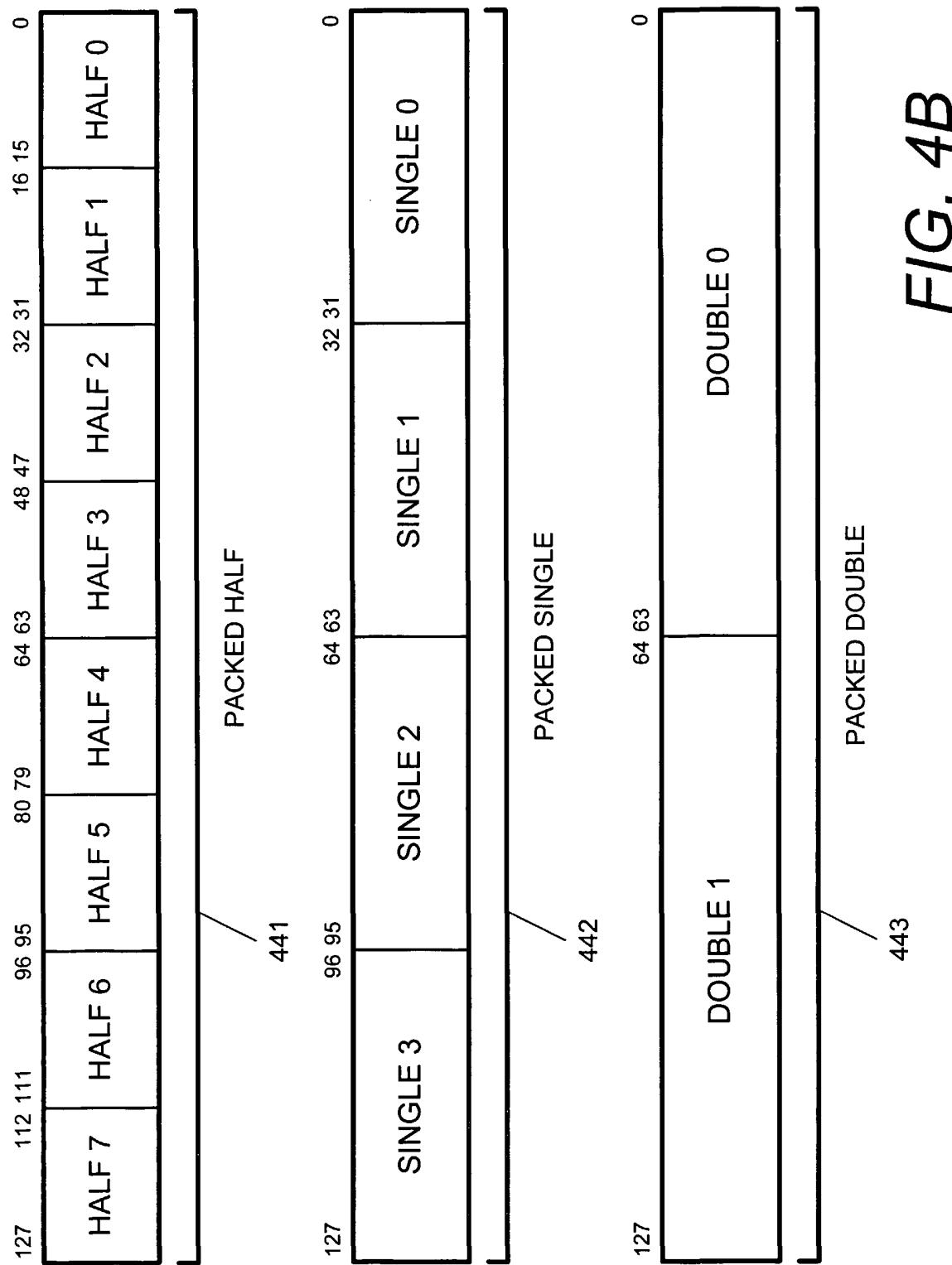

[0015]    **Figure 4B** illustrates packed data-types in accordance with an alternative embodiment;

[0016]    **Figure 4C** illustrates one embodiment of an operation encoding (opcode)

25    format for a shuffle instruction;

[0017] **Figure 4D** illustrates an alternative operation encoding format;

[0018] **Figure 4E** illustrates yet another alternative operation encoding format;

[0019] **Figure 5** is a block diagram of one embodiment of logic to perform a shuffle operation on a data operand based on a shuffle mask in accordance with the present invention;

5 [0020] **Figure 6** is a block diagram of one embodiment of a circuit for performing a data shuffling operation in accordance with the present invention;

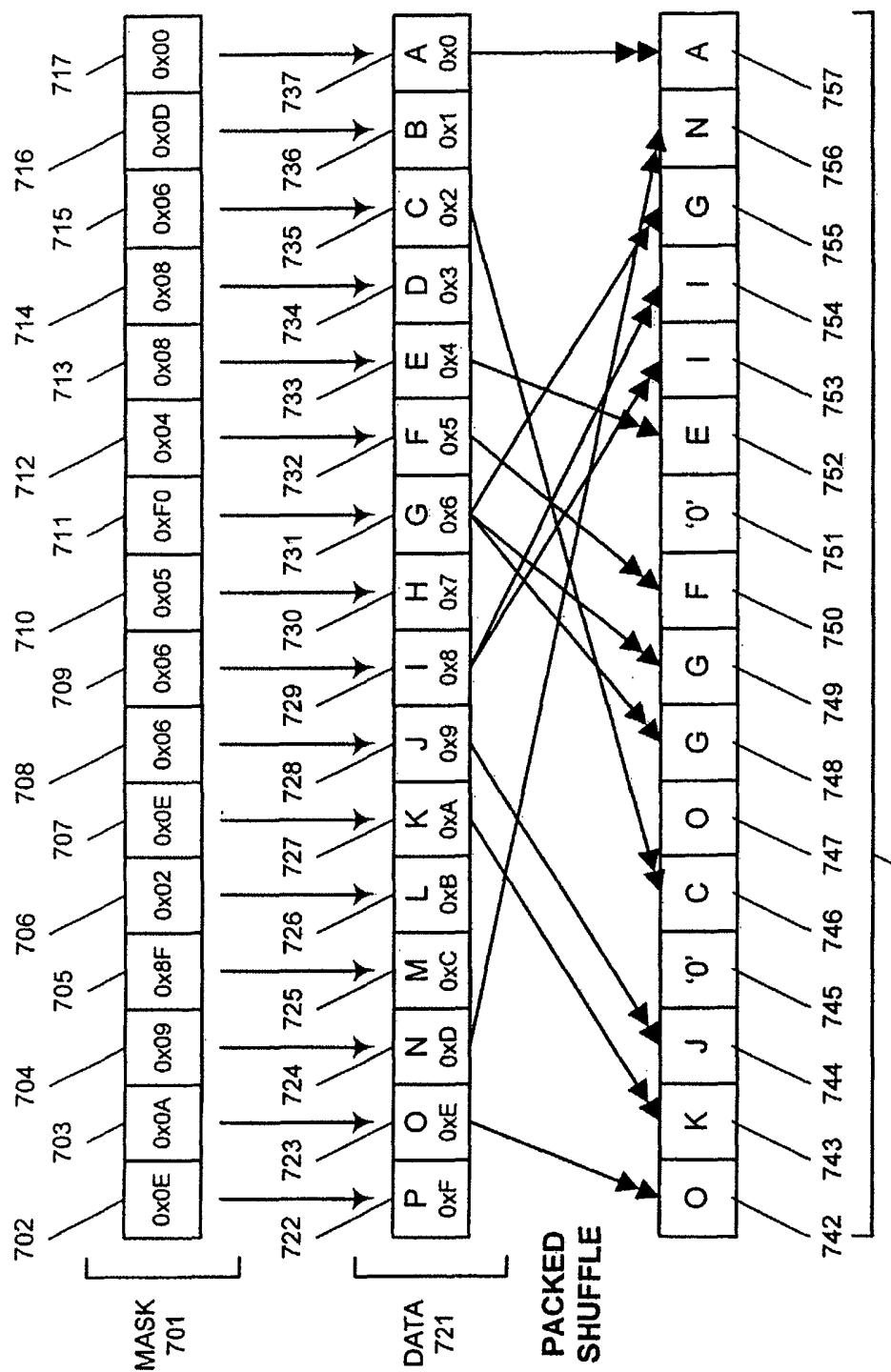

[0021] **Figure 7** illustrates the operation of a data shuffle on byte wide data elements in accordance with one embodiment of the present invention;

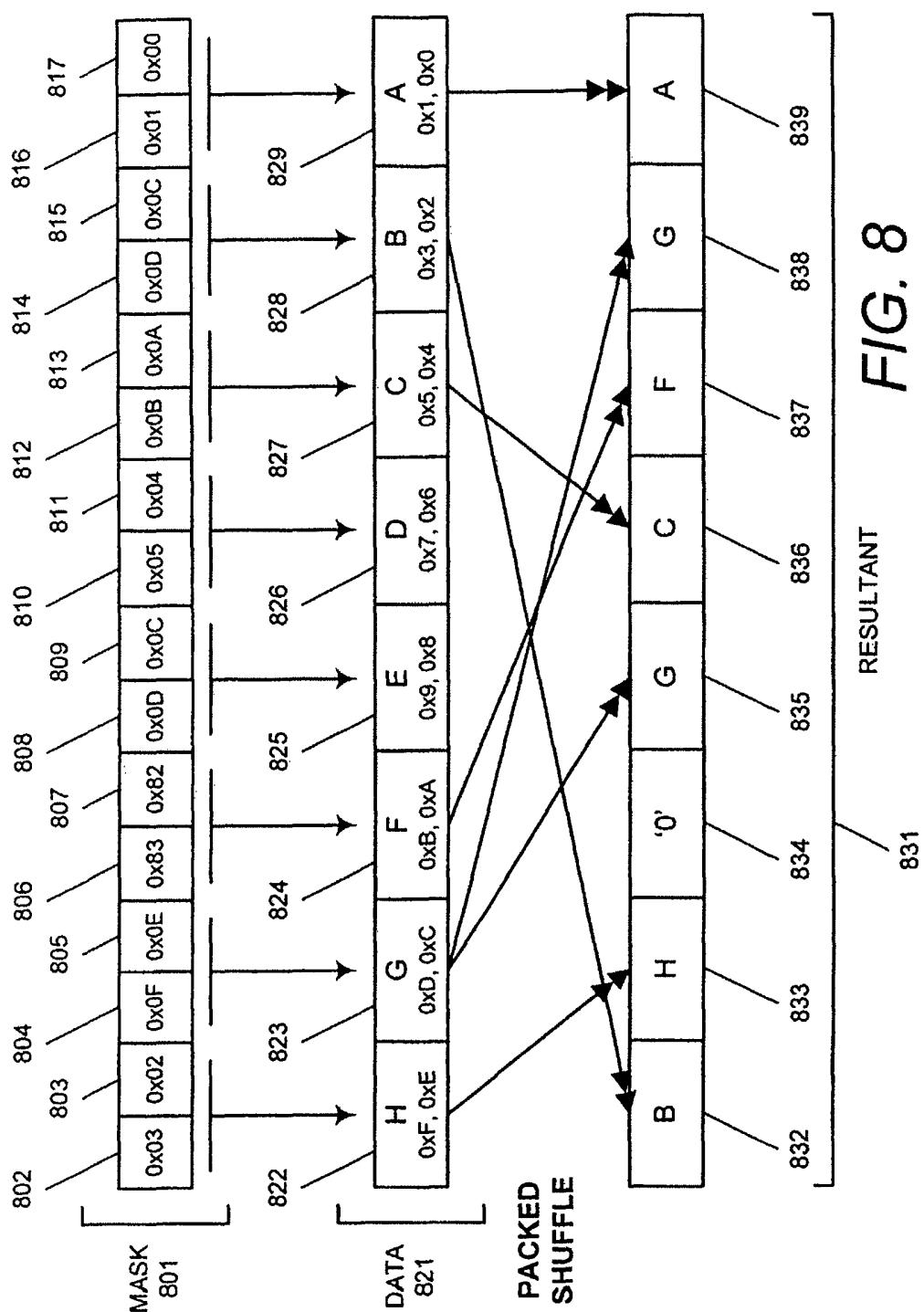

10 [0022] **Figure 8** illustrates the operation of a data shuffle operation on word wide data elements in accordance with another embodiment of the present invention;

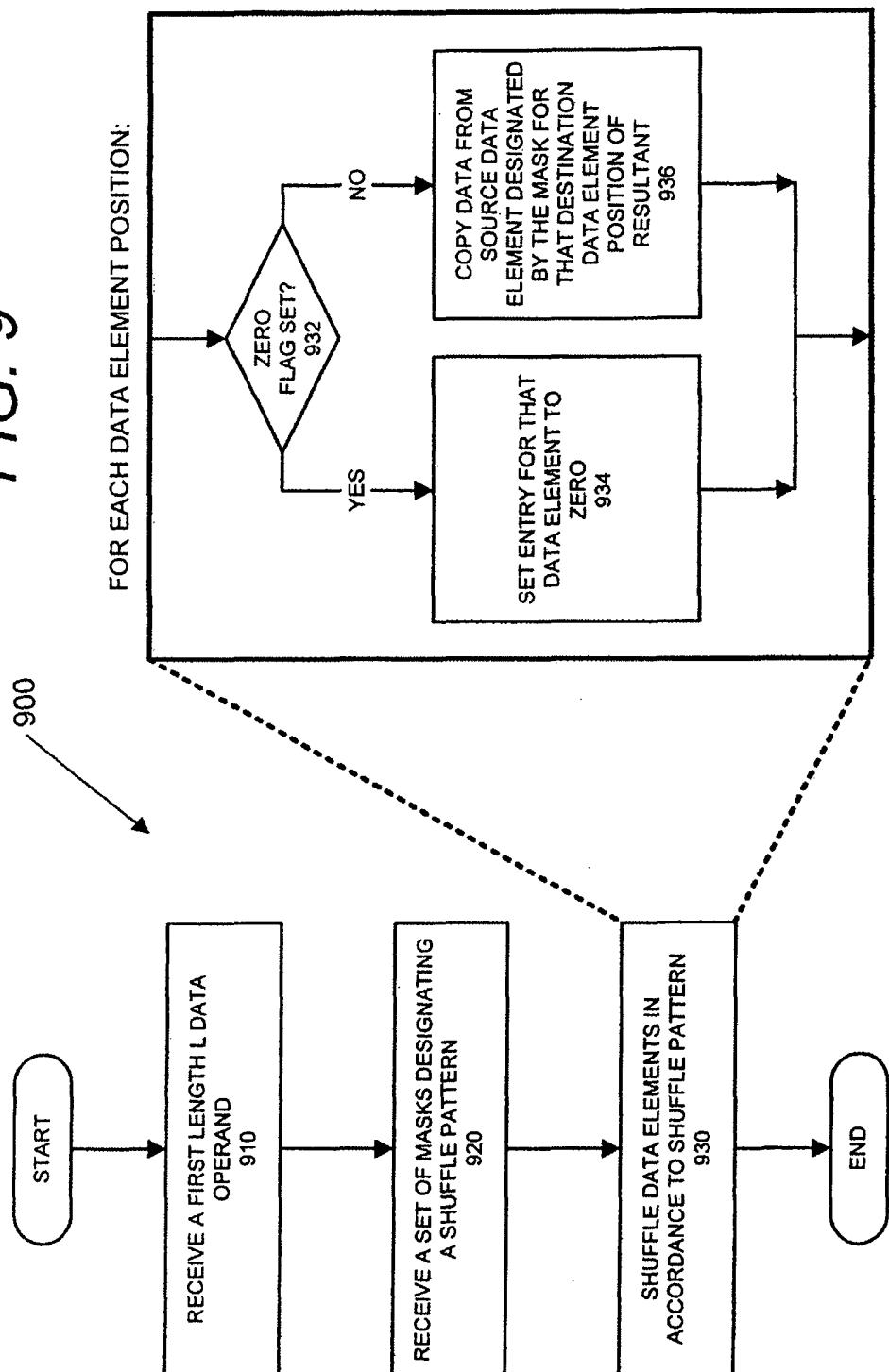

[0023] **Figure 9** is a flow chart illustrating one embodiment of a method to shuffle data;

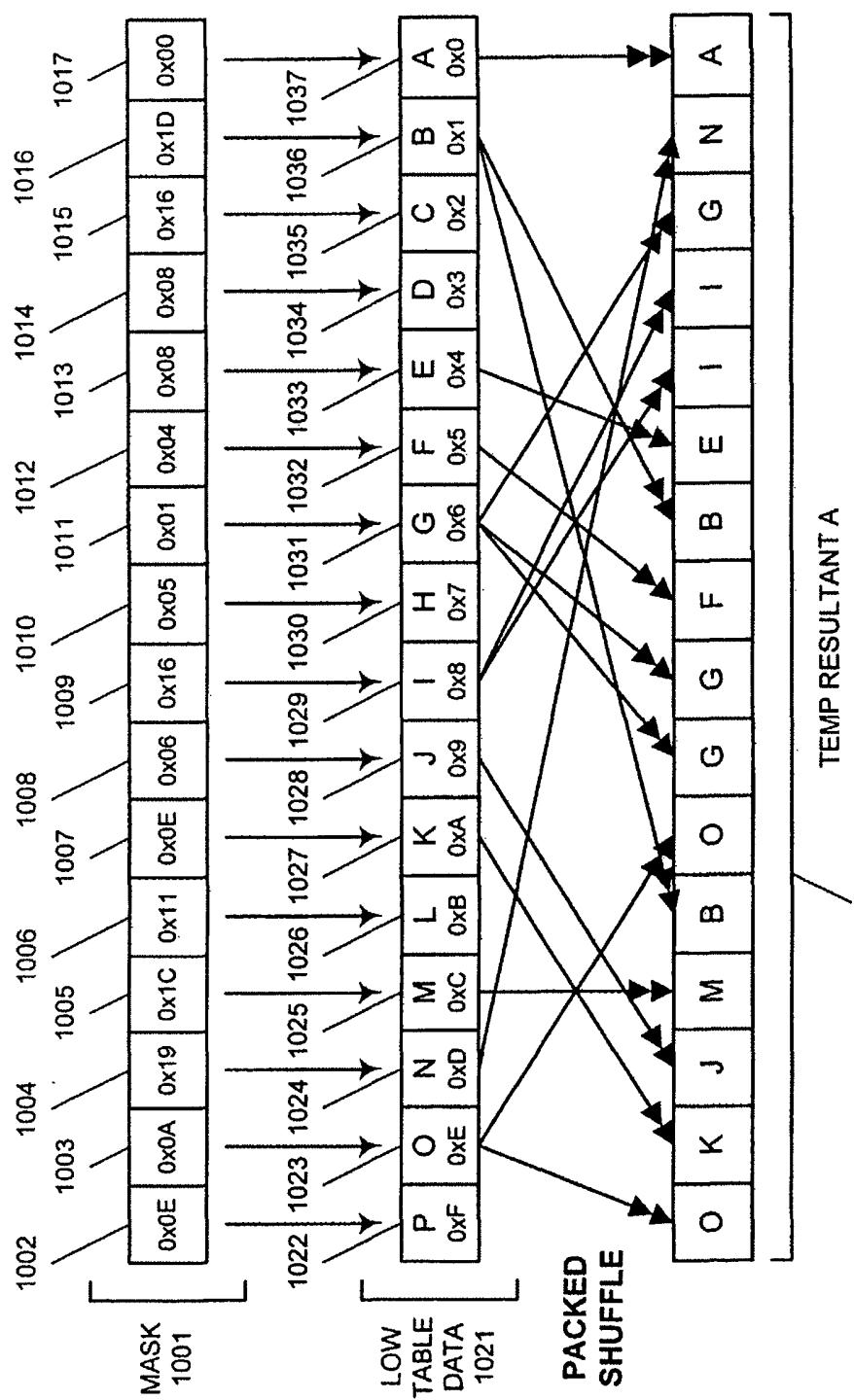

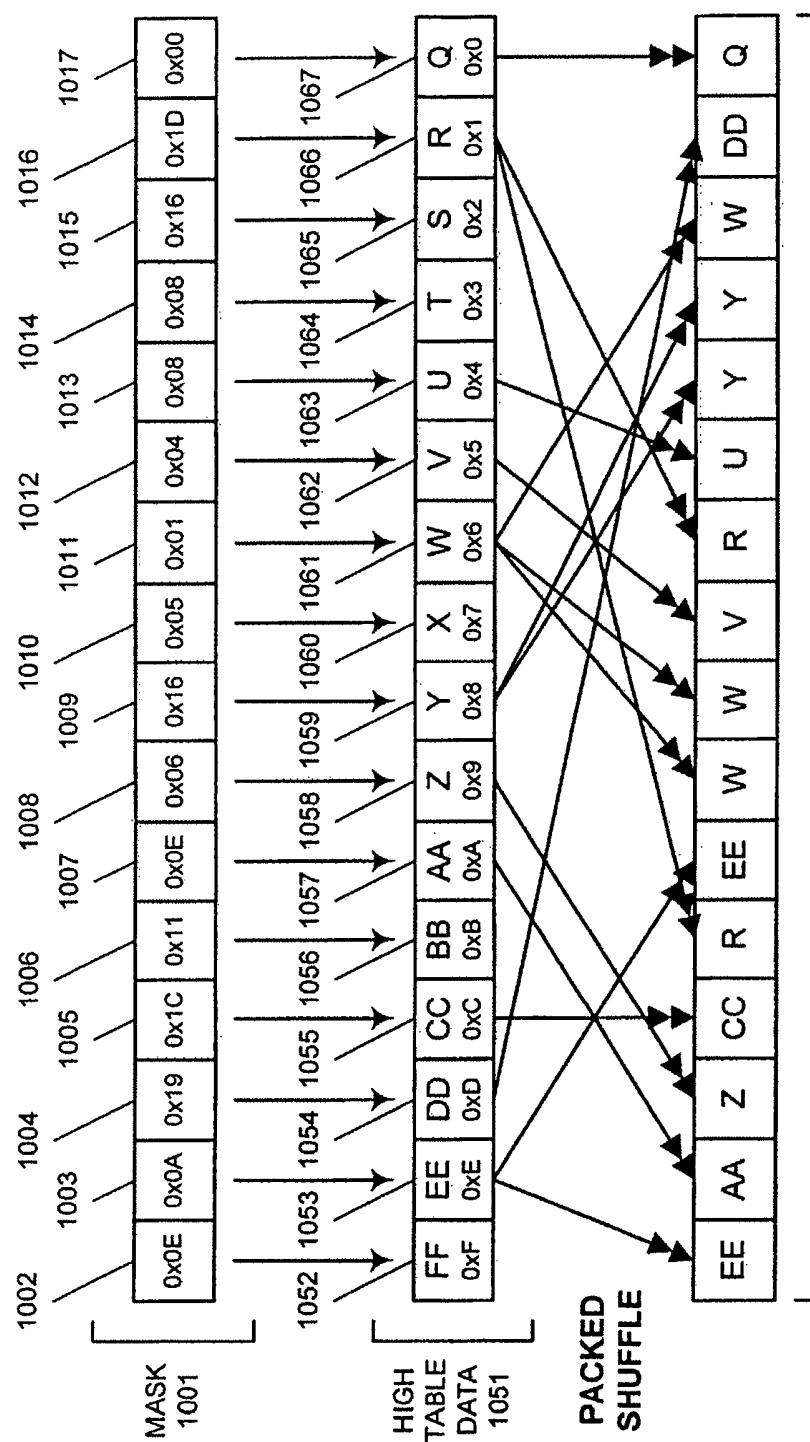

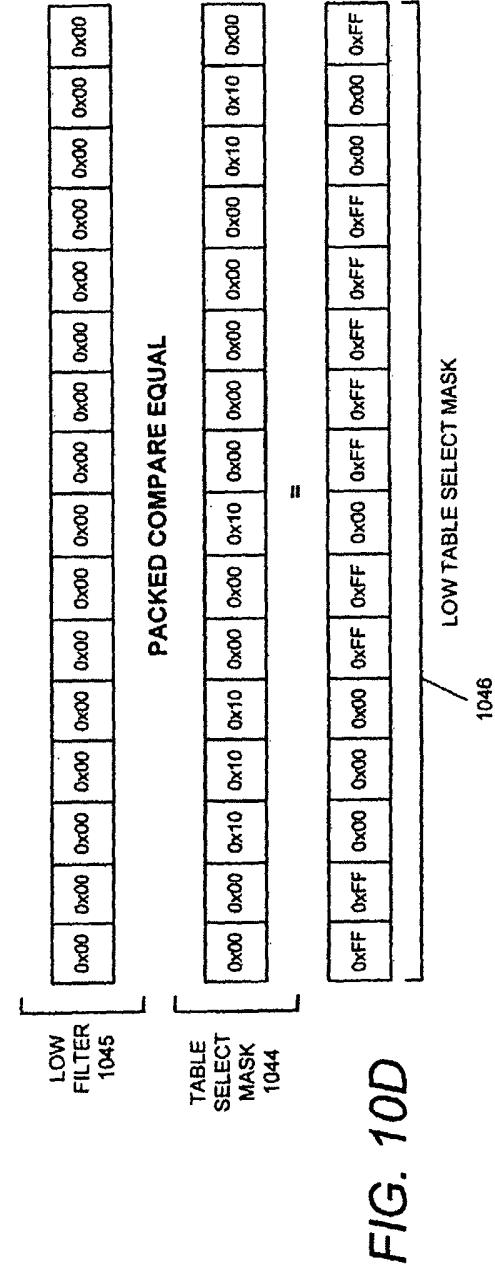

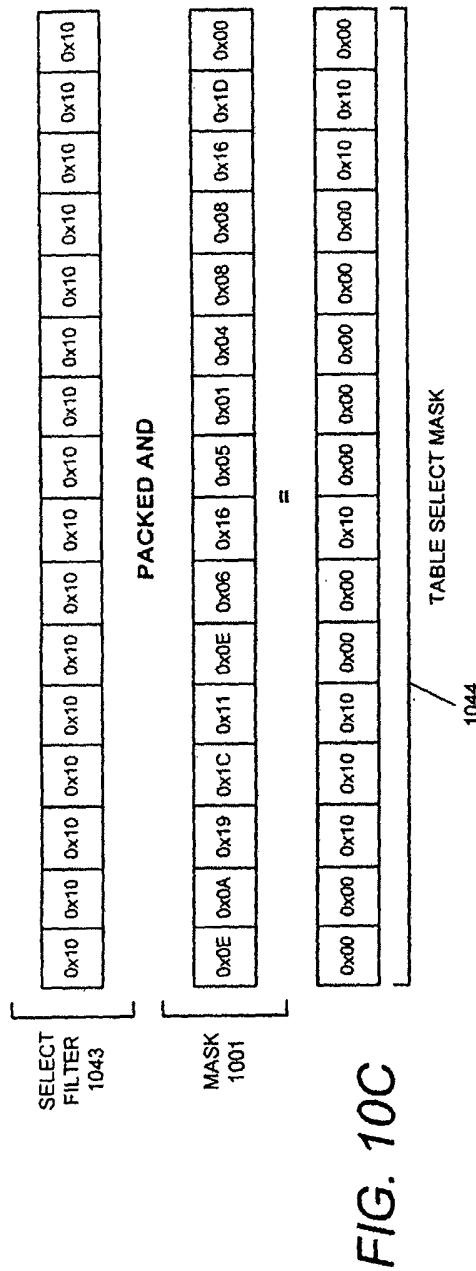

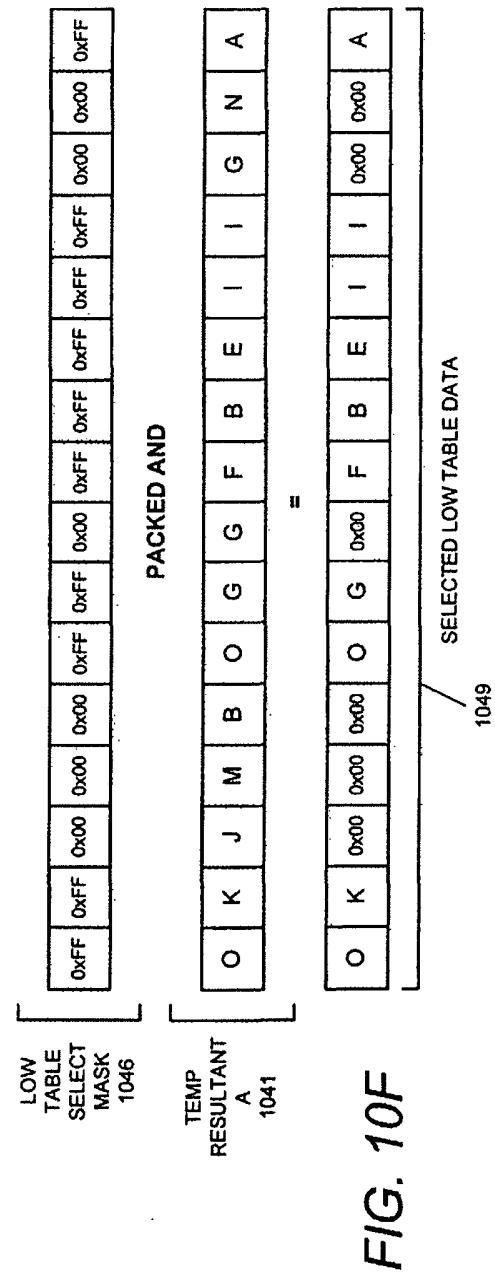

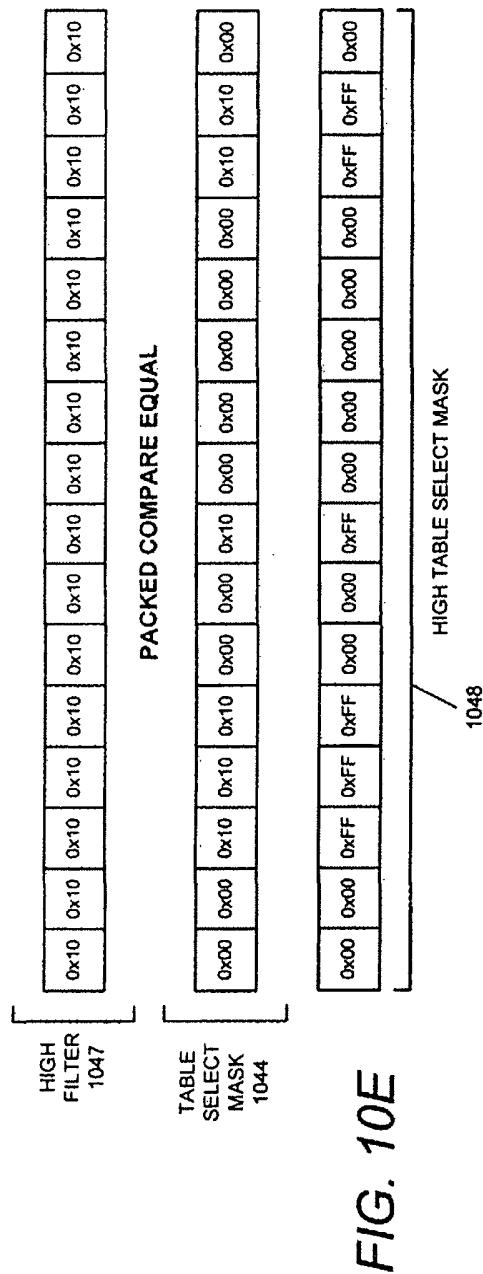

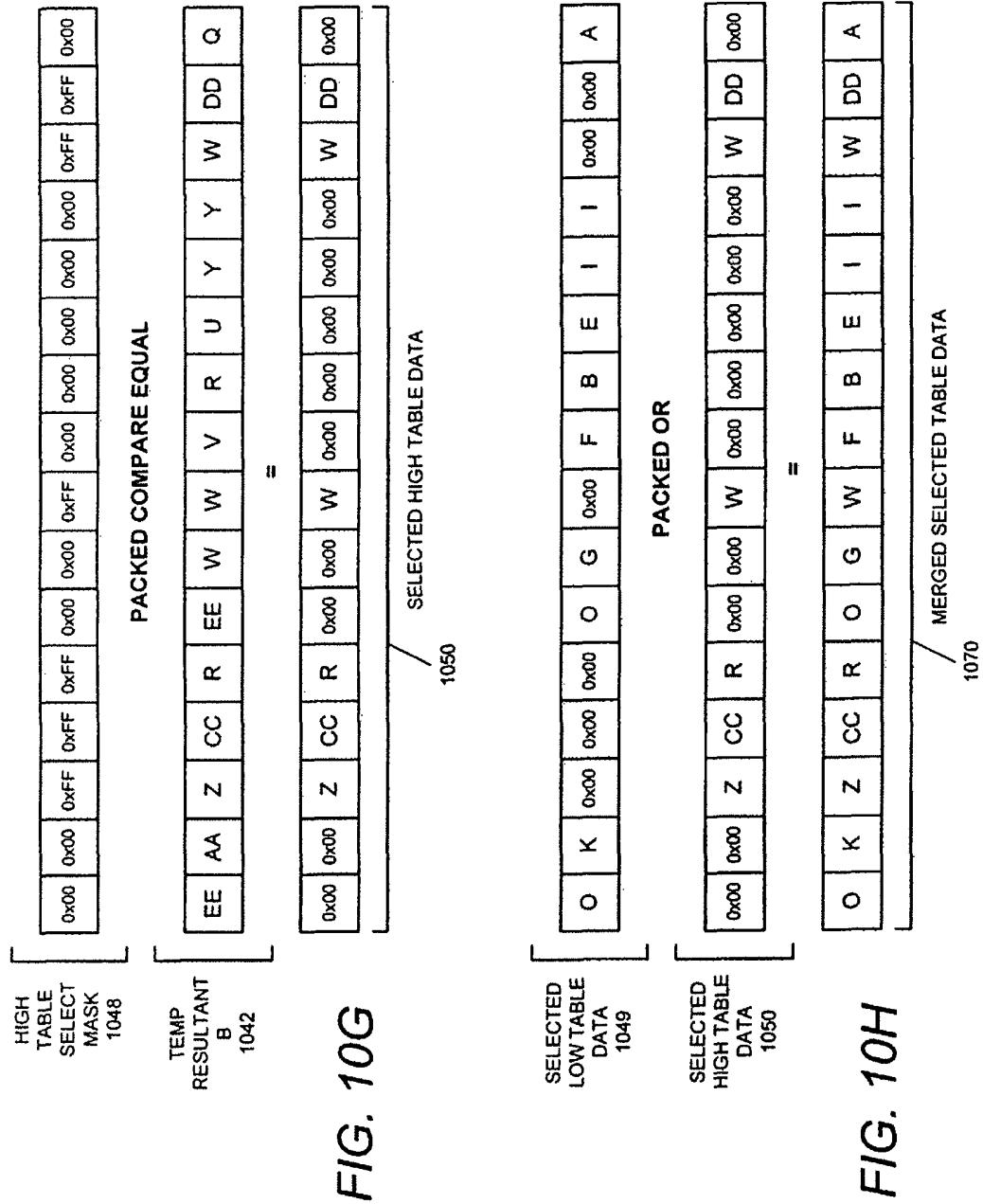

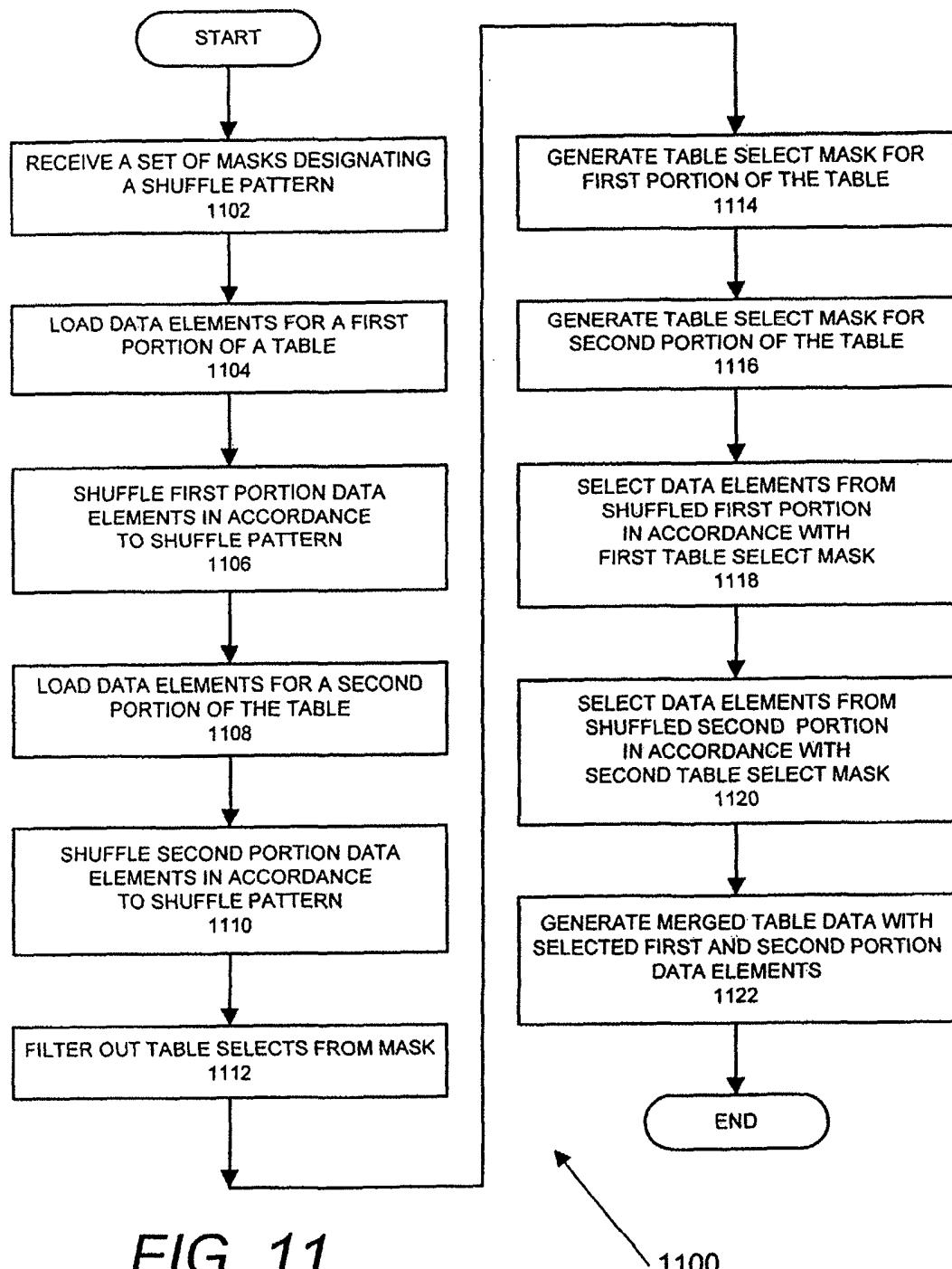

[0024] **Figures 10A-H** illustrate the operation of a parallel table lookup algorithm using SIMD instructions;

15 [0025] **Figure 11** is a flow chart illustrating one embodiment of a method to perform a table lookup using SIMD instructions;

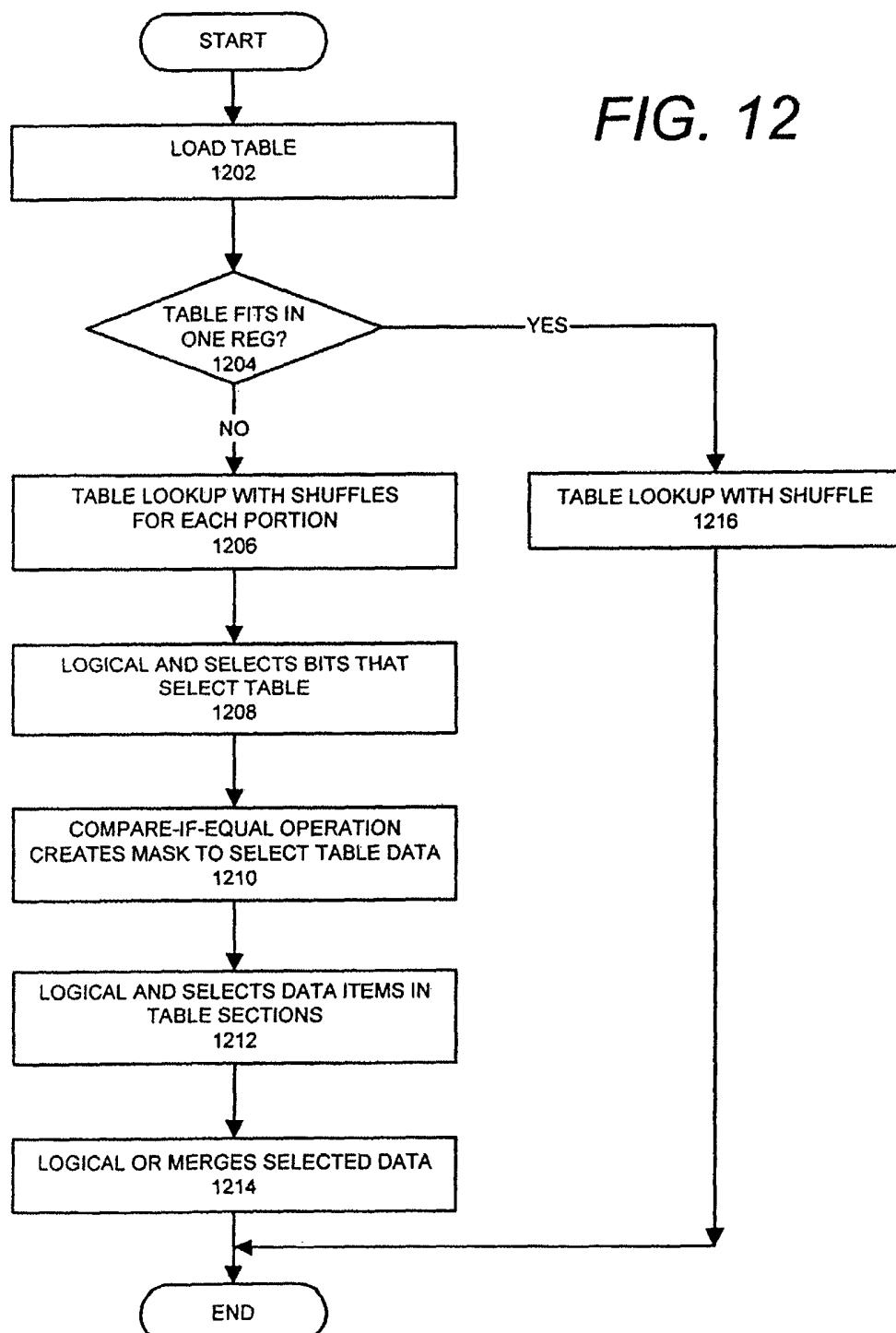

[0026] **Figure 12** is a flow chart illustrating another embodiment of a method to perform a table lookup;

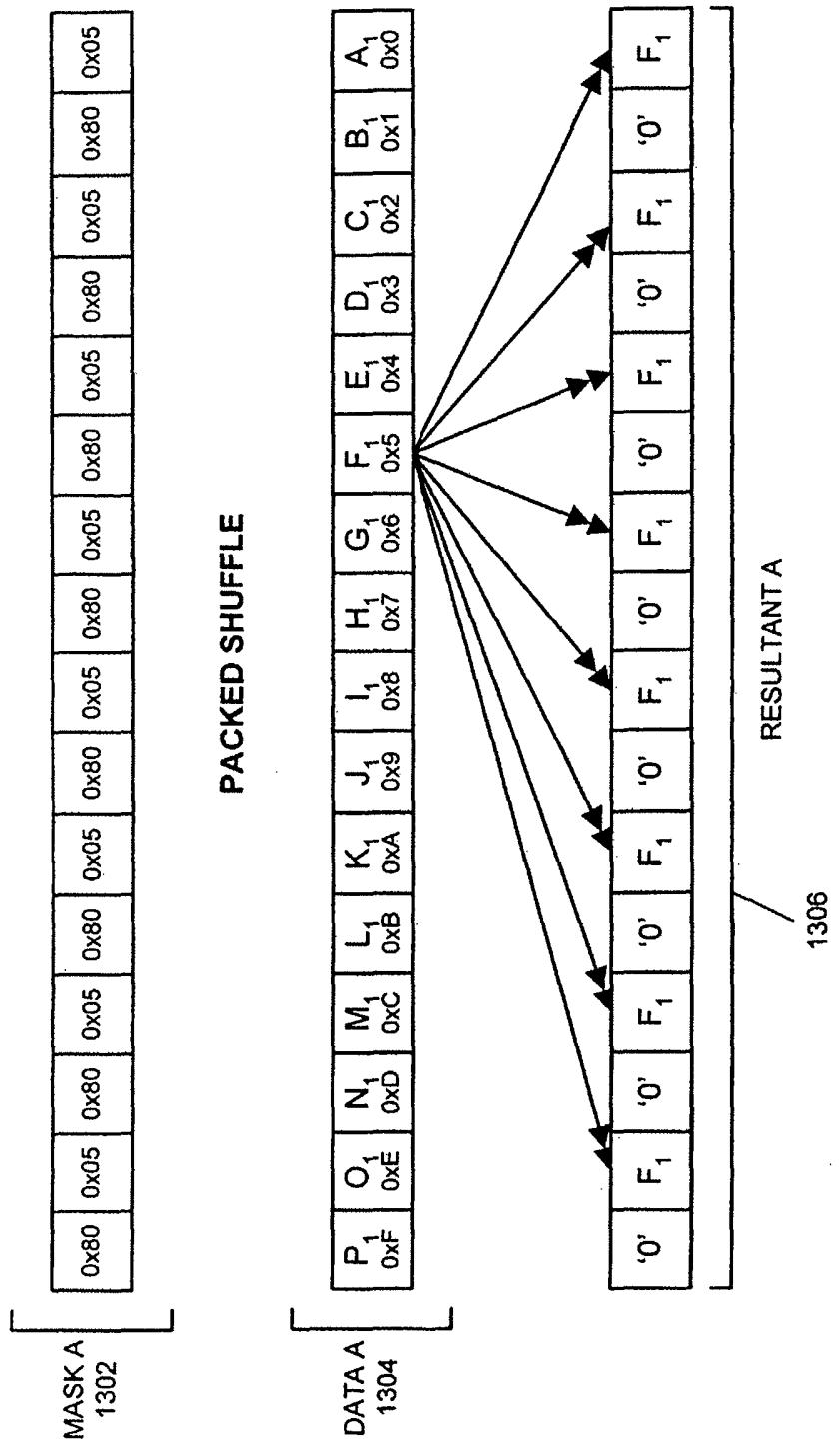

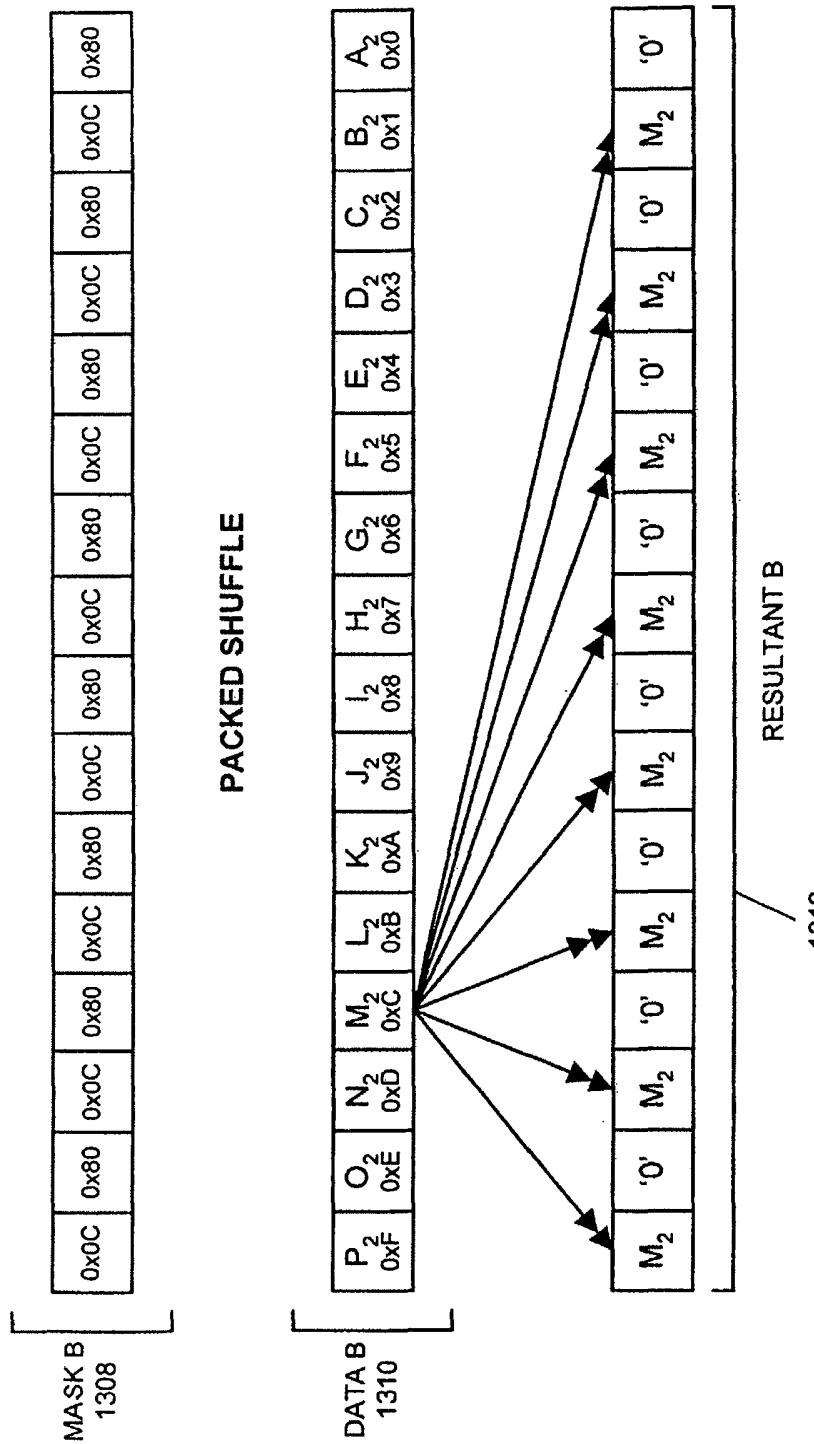

20 [0027] **Figures 13A-C** illustrates an algorithm for rearranging data between multiple registers;

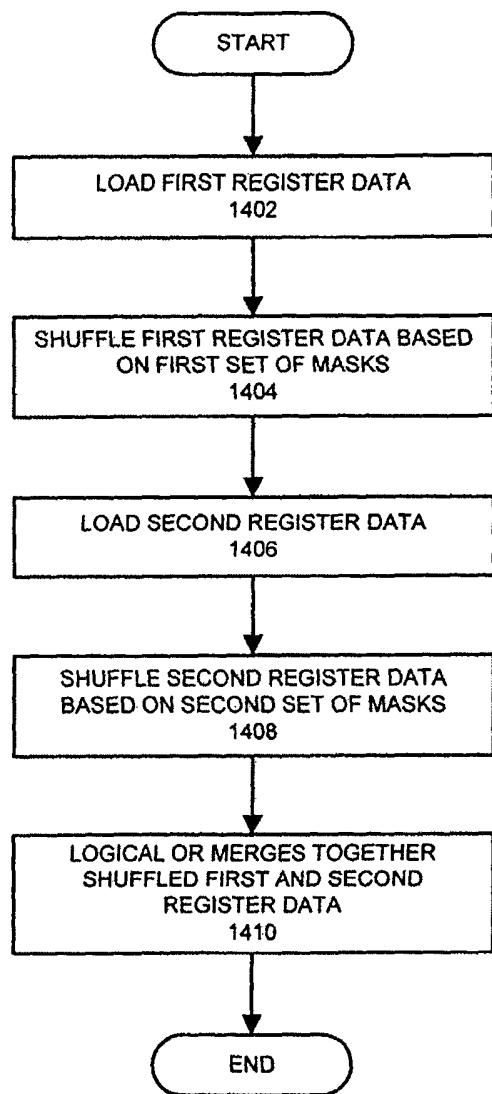

[0028] **Figure 14** is a flow chart illustrating one embodiment of a method to rearrange data between multiple registers;

[0029] **Figures 15A-K** illustrates an algorithm for shuffling data between multiple registers to generate interleaved data; and

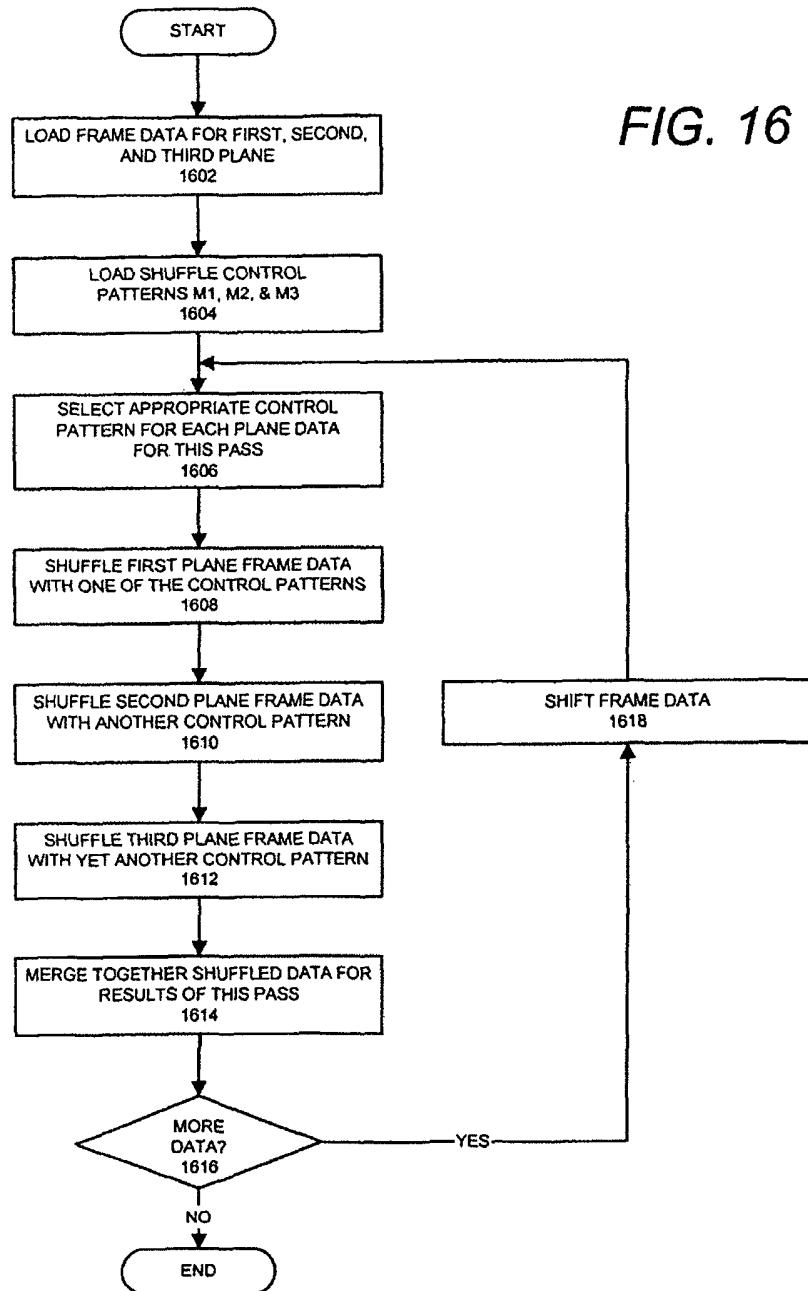

[0030] **Figure 16** is a flow chart illustrating one embodiment of a method to shuffle data between multiple registers to generate interleaved data.

### **DETAILED DESCRIPTION**

5 [0031] A method and apparatus for shuffling data is disclosed. A method and apparatus for parallel table lookup using SIMD instructions are also described. A method and apparatus for rearranging data between multiple registers is also disclosed. The embodiments described herein are described in the context of a microprocessor, but are not so limited. Although the following embodiments are described with reference to a

10 processor, other embodiments are applicable to other types of integrated circuits and logic devices. The same techniques and teachings of the present invention can easily be applied to other types of circuits or semiconductor devices that can benefit from higher pipeline throughput and improved performance. The teachings of the present invention are applicable to any processor or machine that performs data manipulations. However, the

15 present invention is not limited to processors or machines that perform 256 bit, 128 bit, 64 bit, 32 bit, or 16 bit data operations and can be applied to any processor and machine in which shuffling of data is needed.

[0032] In the following description, for purposes of explanation, numerous specific details are set forth in order to provide a thorough understanding of the present invention.

20 One of ordinary skill in the art, however, will appreciate that these specific details are not necessary in order to practice the present invention. In other instances, well known electrical structures and circuits have not been set forth in particular detail in order to not necessarily obscure the present invention. In addition, the following description provides examples, and the accompanying drawings show various examples for the purposes of

25 illustration. However, these examples should not be construed in a limiting sense as they

are merely intended to provide examples of the present invention rather than to provide an exhaustive list of all possible implementations of the present invention.

[0033] In an embodiment, the methods of the present invention are embodied in machine-executable instructions. The instructions can be used to cause a general-purpose or special-purpose processor that is programmed with the instructions to perform the steps of the present invention. Alternatively, the steps of the present invention might be performed by specific hardware components that contain hardwired logic for performing the steps, or by any combination of programmed computer components and custom hardware components.

10 [0034] Although the below examples describe instruction handling and distribution in the context of execution units and logic circuits, other embodiments of the present invention can be accomplished by way of software. The present invention may be provided as a computer program product or software which may include a machine or computer-readable medium having stored thereon instructions which may be used to program a computer (or other electronic devices) to perform a process according to the present invention. Such software can be stored within a memory in the system. Similarly, the code can be distributed via a network or by way of other computer readable media. Thus a machine-readable medium may include any mechanism for storing or transmitting information in a form readable by a machine (e.g., a computer), but is not limited to, 15 floppy diskettes, optical disks, Compact Disc, Read-Only Memory (CD-ROMs), and magneto-optical disks, Read-Only Memory (ROMs), Random Access Memory (RAM), Erasable Programmable Read-Only Memory (EPROM), Electrically Erasable 20 Programmable Read-Only Memory (EEPROM), magnetic or optical cards, flash memory, a transmission over the Internet, electrical, optical, acoustical or other forms of propagated 25 signals (e.g., carrier waves, infrared signals, digital signals, etc.) or the like.

**[0035]** Accordingly, the computer-readable medium includes any type of media/machine-readable medium suitable for storing or transmitting electronic instructions or information in a form readable by a machine (e.g., a computer). Moreover, the present invention may also be downloaded as a computer program product. As such, 5 the program may be transferred from a remote computer (e.g., a server) to a requesting computer (e.g., a client). The transfer of the program may be by way of electrical, optical, acoustical, or other forms of data signals embodied in a carrier wave or other propagation medium via a communication link (e.g., a modem, network connection or the like).

**[0036]** Furthermore, embodiments of integrated circuit designs in accordance with the 10 present inventions can be communicated or transferred in electronic form as a database on a tape or other machine readable media. For example, the electronic form of an integrated circuit design of a processor in one embodiment can be processed or manufactured via a fab to obtain a computer component. In another instance, an integrated circuit design in electronic form can be processed by a machine to simulate a computer component. Thus 15 the circuit layout plans and/or designs of processors in some embodiments can be distributed via machine readable mediums or embodied thereon for fabrication into a circuit or for simulation of an integrated circuit which, when processed by a machine, simulates a processor. A machine readable medium is also capable of storing data representing predetermined functions in accordance with the present invention in other 20 embodiments.

**[0037]** In modern processors, a number of different execution units are used to process and execute a variety of code and instructions. Not all instructions are created equal as some are quicker to complete while others can take an enormous number of clock cycles. The faster the throughput of instructions, the better the overall performance of the 25 processor. Thus it would be advantageous to have as many instructions execute as fast as

possible. However, there are certain instructions that have greater complexity and require more in terms of execution time and processor resources. For example, there are floating point instructions, load/store operations, data moves, etc.

[0038] As more and more computer systems are used in internet and multimedia applications, additional processor support has been introduced over time. For instance, Single Instruction, Multiple Data (SIMD) integer/floating point instructions and Streaming SIMD Extensions (SSE) are instructions that reduce the overall number of instructions required to execute a particular program task. These instructions can speed up software performance by operating on multiple data elements in parallel. As a result, performance gains can be achieved in a wide range of applications including video, speech, and image/photo processing. The implementation of SIMD instructions in microprocessors and similar types of logic circuit usually involve a number of issues. Furthermore, the complexity of SIMD operations often leads to a need for additional circuitry in order to correctly process and manipulate the data.

[0039] Embodiments of the present invention provide a way to implement a packed byte shuffle instruction with a flush to zero capability as an algorithm that makes use of SIMD related hardware. For one embodiment, the algorithm is based on the concept of shuffling data from a particular register or memory location based on the values of a control mask for each data element position. Embodiments of a packed byte shuffle can be used to reduce the number of instructions required in many different applications that rearrange data. A packed byte shuffle instruction can also be used for any application with unaligned loads. Embodiments of this shuffle instruction can be used for filtering to arrange data for efficient multiply-accumulate operations.

Similarly, a packed shuffle instruction can be used in video and encryption applications for ordering data and small lookup tables. This instruction can be used

to mix data from two or more registers. Thus embodiments of a packed shuffle with a flush to zero capability algorithm in accordance with the present invention can be implemented in a processor to support SIMD operations efficiently without seriously compromising overall performance.

5 [0040] Embodiments of the present invention provide a packed data shuffle instruction (PSHUFB) with a flush to zero capability for efficiently ordering and arranging data of any size. In one embodiment, data is shuffled or rearranged in a register with byte granularity. The byte shuffle operation orders data sizes, which are larger than bytes, by maintaining the relative position of bytes within the larger data during the shuffle

10 operation. In addition, the byte shuffle operation can change the relative position of data in an SIMD register and can also duplicate data. This PSHUFB instruction shuffles bytes from a first source register in accordance to the contents of shuffle control bytes in a second source register. Although the instruction permutes the data, the shuffle mask is left unaffected and unchanged during this shuffle operation of this

15 embodiment. The mnemonic for the one implementation is “PSHUFB register 1, register 2 / memory”, wherein the first and second operands are SIMD registers. However, the register of the second operand can also be replaced with a memory location. The first operand includes the source data for shuffling. For this embodiment, the register for the first operand is also the destination register.

20 Embodiments in accordance to the present invention also include a capability of setting selected bytes to zero in addition to changing their position.

[0041] The second operand includes the set of shuffle control mask bytes to designate the shuffle pattern. The number of bits used to select a source data element is  $\log_2$  of the number of data elements in the source operand. For instance, the

25 number of bytes in a 128 bit register embodiment is sixteen. The  $\log_2$  of sixteen is

four. Thus four bits, or a nibble, is needed. The [3:0] index in the code below refers to the four bits. If the most significant bit (MSB), bit 7 in this embodiment, of the shuffle control byte is set, a constant zero is written in the result byte. If the least significant nibble of byte I of the second operand, the mask set, contains the integer J, then the shuffle instruction causes the J<sup>th</sup> byte of the first source register to be copied to the I<sup>th</sup> byte position of the destination register. Below is example pseudo-code for one embodiment of a packed byte shuffle operation on 128 bit operands:

```

10   For i = 0 to 15 {

if (SRC2[(i*8)+7] == 1 )

DEST[(i*8)+7...(i*8)+0] ← 0

else

index[3:0] ← SRC2[(i*8)+3 ... SRC2(i*8)+0]

DEST[(i*8)+7...(i*8)+0] ← SRC1/DEST[(index*8+7)... (index*8+0)]

}

15

```

[0042] Similarly, this is example pseudo-code for another embodiment of a packed byte shuffle operation on 64 bit operands:

```

20   For i = 0 to 7 {

if (SRC2[(i * 8)+7] == 1 )

DEST[(i*8)+7...(i*8)+0] ← 0

else

index[2:0] ← SRC2[(i*8)+2 ... SRC2(i*8)+0]

DEST[(i*8)+7...(i*8)+0] ← SRC1/DEST[(index*8+7)... (index*8+0)]

}

25

```

Note that in this 64 bit register embodiment, the lower three bits of the mask are used as there are eight bytes in a 64 bit register. The log<sub>2</sub> of eight is three. The [2:0] index in the code above refers to the three bits. In alternative embodiments, the number of bits in a mask can vary to accommodate the number of data elements available in the source data.

30 For example, a mask with lower five bits is needed to select a data element in a 256 bit register.

[0043] Presently, it is somewhat difficult and tedious to rearrange data in a SIMD register. Some algorithms require more instructions to arrange data for arithmetic

operations than the actual number of instructions to execute those operations. By implementing embodiments of a packed byte shuffle instruction in accordance with the present invention, the number of instructions needed to achieve data rearrangement can be drastically reduced. For example, one embodiment of a packed 5 byte shuffle instruction can broadcast a byte of data to all positions of a 128 bit register. Broadcasting data in a register is often used in filtering applications where a single data item is multiplied by many coefficients. Without this instruction, the data byte would have to be filtered from its source and shifted to the lowest byte position. Then, that single byte would have to be duplicated first as a byte, then that 10 those two bytes duplicated again to form a doubleword, and that doubleword duplicated to finally form a quadword. All these operations can be replaced with a single packed shuffle instruction.

**[0044]** Similarly, the reversing of all the bytes in a 128 bit register, such as in changing between big endian and little endian formats, can be easily performed with 15 a single packed shuffle instruction. Whereas even these fairly simple patterns require a number of instructions if a packed shuffle instruction were not used, complex or random patterns require even more inefficient instruction routines. The most straight forward solution to rearrange random bytes in a SIMD register is to write them to a buffer and then use integer byte reads/writes to rearrange them and read them back 20 into a SIMD register. All these data processing would require a lengthy code sequence, while a single packed shuffle instructions can suffice. By reducing the number of instructions required, the number of clock cycles needed to produce the same result is greatly reduced. Embodiments of the present invention also use shuffle instructions to access multiple values in a table with a SIMD instructions. Even in the 25 case where the a table is twice the size of a register, algorithms in accordance with the

present invention allow for accesses to data elements at a faster rate than the one data element per instruction as with integer operations.

[0045] **Figure 1A** is a block diagram of an exemplary computer system formed with a processor that includes execution units to execute an instruction for shuffling data in accordance with one embodiment of the present invention. System **100** includes a component, such as a processor **102** to employ execution units including logic to perform algorithms for shuffling data, in accordance with the present invention, such as in the embodiment described herein. System **100** is representative of processing systems based on the PENTIUM® III, PENTIUM® 4, Celeron®, Xeon™, Itanium®, XScale™ and/or 10 StrongARM™ microprocessors available from Intel Corporation of Santa Clara, California, although other systems (including PCs having other microprocessors, engineering workstations, set-top boxes and the like) may also be used. In one embodiment, sample system **100** may execute a version of the WINDOWS™ operating system available from Microsoft Corporation of Redmond, Washington, although other 15 operating systems (UNIX and Linux for example), embedded software, and/or graphical user interfaces, may also be used. Thus, the present invention is not limited to any specific combination of hardware circuitry and software.

[0046] The present enhancement is not limited to computer systems. Alternative embodiments of the present invention can be used in other devices such as handheld 20 devices and embedded applications. Some examples of handheld devices include cellular phones, Internet Protocol devices, digital cameras, personal digital assistants (PDAs), and handheld PCs. Embedded applications can include a micro controller, a digital signal processor (DSP), system on a chip, network computers (NetPC), set-top boxes, network hubs, wide area network (WAN) switches, or any other system that performs integer 25 shuffle operations on operands. Furthermore, some architectures have been implemented

to enable instructions to operate on several data simultaneously to improve the efficiency of multimedia applications. As the type and volume of data increases, computers and their processors have to be enhanced to manipulate data in more efficient methods.

[0047] **Figure 1A** is a block diagram of a computer system **100** formed with a processor **102** that includes one or more execution units **108** to perform a data shuffle algorithm in accordance with the present invention. The present embodiment is described in the context of a single processor desktop or server system, but alternative embodiments can be included in a multiprocessor system. System **100** is an example of a hub architecture. The computer system **100** includes a processor **102** to process data signals.

10 The processor **102** can be a complex instruction set computer (CISC) microprocessor, a reduced instruction set computing (RISC) microprocessor, a very long instruction word (VLIW) microprocessor, a processor implementing a combination of instruction sets, or any other processor device, such as a digital signal processor, for example. The processor **102** is coupled to a processor bus **110** that can transmit data signals between the processor **102** and other components in the system **100**. The elements of system **100** perform their conventional functions that are well known to those familiar with the art.

15 [0048] In one embodiment, the processor **102** includes a Level 1 (L1) internal cache memory **104**. Depending on the architecture, the processor **102** can have a single internal cache or multiple levels of internal cache. Alternatively, in another embodiment, the cache memory can reside external to the processor **102**. Other embodiments can also include a combination of both internal and external caches depending on the particular implementation and needs. Register file **106** can store different types of data in various registers including integer registers, floating point registers, status registers, and instruction pointer register.

[0049] Execution unit **108**, including logic to perform integer and floating point operations, also resides in the processor **102**. The processor **102** also includes a microcode (ucode) ROM that stores microcode for certain macroinstructions. For this embodiment, execution unit **108** includes logic to handle a packed instruction set **109**. In one embodiment, the packed instruction set **109** includes a packed shuffle instruction for organizing data. By including the packed instruction set **109** in the instruction set of a general-purpose processor **102**, along with associated circuitry to execute the instructions, the operations used by many multimedia applications may be performed using packed data in a general-purpose processor **102**. Thus, many multimedia applications can be accelerated and executed more efficiently by using the full width of a processor's data bus for performing operations on packed data. This can eliminate the need to transfer smaller units of data across the processor's data bus to perform one or more operations one data element at a time.

[0050] Alternate embodiments of an execution unit **108** can also be used in micro controllers, embedded processors, graphics devices, DSPs, and other types of logic circuits. System **100** includes a memory **120**. Memory **120** can be a dynamic random access memory (DRAM) device, a static random access memory (SRAM) device, flash memory device, or other memory device. Memory **120** can store instructions and/or data represented by data signals that can be executed by the processor **102**.

[0051] A system logic chip **116** is coupled to the processor bus **110** and memory **120**. The system logic chip **116** in the illustrated embodiment is a memory controller hub (MCH). The processor **102** can communicate to the MCH **116** via a processor bus **110**. The MCH **116** provides a high bandwidth memory path **118** to memory **120** for instruction and data storage and for storage of graphics commands, data and textures. The MCH **116** is to direct data signals between the processor **102**, memory **120**, and other components in

the system **100** and to bridge the data signals between processor bus **110**, memory **120**, and system I/O **122**. In some embodiments, the system logic chip **116** can provide a graphics port for coupling to a graphics controller **112**. The MCH **116** is coupled to memory **120** through a memory interface **118**. The graphics card **112** is coupled to the

5 MCH **116** through an Accelerated Graphics Port (AGP) interconnect **114**.

[0052] System **100** uses a proprietary hub interface bus **122** to couple the MCH **116** to the I/O controller hub (ICH) **130**. The ICH **130** provides direct connections to some I/O devices via a local I/O bus. The local I/O bus is a high-speed I/O bus for connecting peripherals to the memory **120**, chipset, and processor **102**. Some examples are the audio controller, firmware hub (flash BIOS) **128**, wireless transceiver **126**, data storage **124**, legacy I/O controller containing user input and keyboard interfaces, a serial expansion port such as Universal Serial Bus (USB), and a network controller **134**. The data storage device **124** can comprise a hard disk drive, a floppy disk drive, a CD-ROM device, a flash memory device, or other mass storage device.

15 [0053] For another embodiment of a system, an execution unit to execute an algorithm with a shuffle instruction can be used with a system on a chip. One embodiment of a system on a chip comprises of a processor and a memory. The memory for one such system is a flash memory. The flash memory can be located on the same die as the processor and other system components. Additionally, other logic blocks such as a memory controller or graphics controller can also be located on a system on a chip.

20 [0054] **Figure 1B** illustrates an alternative embodiment of a data processing system **140** which implements the principles of the present invention. One embodiment of data processing system **140** is an Intel® Personal Internet Client Architecture (Intel® PCA) applications processors with Intel XScale™ technology (as described on the world-wide web at developer.intel.com). It will be readily appreciated by one of skill in the art that

the embodiments described herein can be used with alternative processing systems without departure from the scope of the invention.

[0055] Computer system **140** comprises a processing core **159** capable of performing SIMD operations including a shuffle. For one embodiment, processing core **159**

5 represents a processing unit of any type of architecture, including but not limited to a CISC, a RISC or a VLIW type architecture. Processing core **159** may also be suitable for manufacture in one or more process technologies and by being represented on a machine readable media in sufficient detail, may be suitable to facilitate said manufacture.

[0056] Processing core **159** comprises an execution unit **142**, a set of register file(s)

10 **145**, and a decoder **144**. Processing core **159** also includes additional circuitry (not shown) which is not necessary to the understanding of the present invention. Execution unit **142** is used for executing instructions received by processing core **159**. In addition to recognizing typical processor instructions, execution unit **142** can recognize instructions in packed instruction set **143** for performing operations on packed data formats. Packed

15 instruction set **143** includes instructions for supporting shuffle operations, and may also include other packed instructions. Execution unit **142** is coupled to register file **145** by an internal bus. Register file **145** represents a storage area on processing core **159** for storing information, including data. As previously mentioned, it is understood that the storage area used for storing the packed data is not critical. Execution unit **142** is coupled to

20 decoder **144**. Decoder **144** is used for decoding instructions received by processing core **159** into control signals and/or microcode entry points. In response to these control signals and/or microcode entry points, execution unit **142** performs the appropriate operations.

[0057] Processing core **159** is coupled with bus **141** for communicating with various

25 other system devices, which may include but are not limited to, for example, synchronous

dynamic random access memory (SDRAM) control **146**, static random access memory (SRAM) control **147**, burst flash memory interface **148**, personal computer memory card international association (PCMCIA)/compact flash (CF) card control **149**, liquid crystal display (LCD) control **150**, direct memory access (DMA) controller **151**, and alternative bus master interface **152**. In one embodiment, data processing system **140** may also comprise an I/O bridge **154** for communicating with various I/O devices via an I/O bus **153**. Such I/O devices may include but are not limited to, for example, universal asynchronous receiver/transmitter (UART) **155**, universal serial bus (USB) **156**, Bluetooth wireless UART **157** and I/O expansion interface **158**.

10 [0058] One embodiment of data processing system **140** provides for mobile, network and/or wireless communications and a processing core **159** capable of performing SIMD operations including a shuffle operation. Processing core **159** may be programmed with various audio, video, imaging and communications algorithms including discrete transformations such as a Walsh-Hadamard transform, a fast Fourier transform (FFT), a discrete cosine transform (DCT), and their respective inverse transforms; compression/decompression techniques such as color space transformation, video encode motion estimation or video decode motion compensation; and modulation/demodulation (MODEM) functions such as pulse coded modulation (PCM).

15 [0059] **Figure 1C** illustrates yet alternative embodiments of a data processing system capable of performing SIMD shuffle operations. In accordance with one alternative embodiment, data processing system **160** may include a main processor **166**, a SIMD coprocessor **161**, a cache memory **167**, and an input/output system **168**. The input/output system **168** may optionally be coupled to a wireless interface **169**. SIMD coprocessor **161** is capable of performing SIMD operations including data shuffles. Processing core **170** may be suitable for manufacture in one or more process technologies and by being

represented on a machine readable media in sufficient detail, may be suitable to facilitate the manufacture of all or part of data processing system **160** including processing core **170**.

**[0060]** For one embodiment, SIMD coprocessor **161** comprises an execution unit **162** and a set of register file(s) **164**. One embodiment of main processor **165** comprises a decoder **165** to recognize instructions of instruction set **163** including SIMD shuffle instructions for execution by execution unit **162**. For alternative embodiments, SIMD coprocessor **161** also comprises at least part of decoder **165B** to decode instructions of instruction set **163**. Processing core **170** also includes additional circuitry (not shown)

10 which is not necessary to the understanding of the present invention.

**[0061]** In operation, the main processor **166** executes a stream of data processing instructions that control data processing operations of a general type including interactions with the cache memory **167**, and the input/output system **168**. Embedded within the stream of data processing instructions are SIMD coprocessor instructions. The decoder **165** of main processor **166** recognizes these SIMD coprocessor instructions as being of a type that should be executed by an attached SIMD coprocessor **161**. Accordingly, the main processor **166** issues these SIMD coprocessor instructions (or control signals representing SIMD coprocessor instructions) on the coprocessor bus **166** where from they are received by any attached SIMD coprocessors. In this case, the SIMD coprocessor **161** 20 will accept and execute any received SIMD coprocessor instructions intended for it.

**[0062]** Data may be received via wireless interface **169** for processing by the SIMD coprocessor instructions. For one example, voice communication may be received in the form of a digital signal, which may be processed by the SIMD coprocessor instructions to regenerate digital audio samples representative of the voice communications. For another 25 example, compressed audio and/or video may be received in the form of a digital bit

stream, which may be processed by the SIMD coprocessor instructions to regenerate digital audio samples and/or motion video frames. For one embodiment of processing core 170, main processor 166, and a SIMD coprocessor 161 are integrated into a single processing core 170 comprising an execution unit 162, a set of register file(s) 164, and a 5 decoder 165 to recognize instructions of instruction set 163 including SIMD shuffle instructions.

[0063] Figure 2 is a block diagram of the micro-architecture for a processor 200 of one embodiment that includes logic circuits to perform shuffle operations in accordance with the present invention. The shuffle operation may also be referred to as a packed data 10 shuffle operation and packed shuffle instruction as in the discussion above. For one embodiment of the shuffle instruction, the instruction can shuffle packed data with a byte granularity. That instruction can also be referred to as PSHUFB or packed shuffle byte. In other embodiments, the shuffle instruction can also be implemented to operate on data elements having sizes of word, doubleword, quadword, etc. The in-order front end 201 is 15 the part of the processor 200 that fetches the macro-instructions to be executed and prepares them to be used later in the processor pipeline. The front end 201 of this embodiment includes several units. The instruction prefetcher 226 fetches macro-instructions from memory and feeds them to an instruction decoder 228 which in turn decodes them into primitives called micro-instructions or micro-operations (also called 20 micro op or uops) that the machine know how to execute. The trace cache 230 takes decoded uops and assembles them into program ordered sequences or traces in the uop queue 234 for execution. When the trace cache 230 encounters a complex macro-instruction, the microcode ROM 232 provides the uops needed to complete the operation.

[0064] Many macro-instructions are converted into a single micro-op, and others need 25 several micro-ops to complete the full operation. In this embodiment, if more than four

micro-ops are needed to complete a macro-instruction, the decoder **228** accesses the microcode ROM **232** to do the macro-instruction. For one embodiment, a packed shuffle instruction can be decoded into a small number of micro ops for processing at the instruction decoder **228**. In another embodiment, an instruction for a packed data shuffle 5 algorithm can be stored within the microcode ROM **232** should a number of micro-ops be needed to accomplish the operation. The trace cache **230** refers to a entry point programmable logic array (PLA) to determine a correct micro-instruction pointer for reading the micro-code sequences for the shuffle algorithms in the micro-code ROM **232**. After the microcode ROM **232** finishes sequencing micro-ops for the current macro- 10 instruction, the front end **201** of the machine resumes fetching micro-ops from the trace cache **230**.

**[0065]** Some SIMD and other multimedia types of instructions are considered complex instructions. Most floating point related instructions are also complex instructions. As such, when the instruction decoder **228** encounters a complex macro- 15 instruction, the microcode ROM **232** is accessed at the appropriate location to retrieve the microcode sequence for that macro-instruction. The various micro-ops needed for performing that macro-instruction are communicated to the out-of-order execution engine **203** for execution at the appropriate integer and floating point execution units.

**[0066]** The out-of-order execution engine **203** is where the micro-instructions are prepared for execution. The out-of-order execution logic has a number of buffers to 20 smooth out and re-order the flow of micro-instructions to optimize performance as they go down the pipeline and get scheduled for execution. The allocator logic allocates the machine buffers and resources that each uop needs in order to execute. The register renaming logic renames logic registers onto entries in a register file. The allocator also 25 allocates an entry for each uop in one of the two uop queues, one for memory operations

and one for non-memory operations, in front of the instruction schedulers: memory scheduler, fast scheduler 202, slow/general floating point scheduler 204, and simple floating point scheduler 206. The uop schedulers 202, 204, 206, determine when a uop is ready to execute based on the readiness of their dependent input register operand sources and the availability of the execution resources the uops need to complete their operation.

5 The fast scheduler 202 of this embodiment can schedule on each half of the main clock cycle while the other schedulers can only schedule once per main processor clock cycle.

The schedulers arbitrate for the dispatch ports to schedule uops for execution.

[0067] Register files 208, 210, sit between the schedulers 202, 204, 206, and the execution units 212, 214, 216, 218, 220, 222, 224 in the execution block 211. There is a separate register file 208, 210, for integer and floating point operations, respectively. Each register file 208, 210, of this embodiment also includes a bypass network that can bypass or forward just completed results that have not yet been written into the register file to new dependent uops. The integer register file 208 and the floating point register file 210 are also capable of communicating data with the other. For one embodiment, the integer register file 208 is split into two separate register files, one register file for the low order 32 bits of data and a second register file for the high order 32 bits of data. The floating point register file 210 of one embodiment has 128 bit wide entries because floating point instructions typically have operands from 64 to 128 bits in width.

20 [0068] The execution block 211 contains the execution units 212, 214, 216, 218, 220, 222, 224, where the instructions are actually executed. This section includes the register files 208, 210, that store the integer and floating point data operand values that the micro-instructions need to execute. The processor 200 of this embodiment is comprised of a number of execution units: address generation unit (AGU) 212, AGU 214, fast ALU 216, fast ALU 218, slow ALU 220, floating point ALU 222, floating point move unit 224. For

this embodiment, the floating point execution blocks **222**, **224**, execute floating point, MMX, SIMD, and SSE operations. The floating point ALU **222** of this embodiment includes a floating point divider to execute divide, square root, and remainder micro-ops. For embodiments of the present invention, any act involving a floating point value occurs 5 with the floating point hardware. For example, conversions between integer format and floating point format involve a floating point register file. Similarly, a floating point divide operation happens at a floating point divider. On the other hand, non-floating point numbers and integer type are handled with integer hardware resources. The simple, very frequent ALU operations go to the high-speed ALU execution units **216**, **218**. The fast 10 ALUs **216**, **218**, of this embodiment can execute fast operations with an effective latency of half a clock cycle. For one embodiment, most complex integer operations go to the slow ALU **220** as the slow ALU **220** includes integer execution hardware for long latency type of operations, such as a multiplier, shifts, flag logic, and branch processing. Memory load/store operations are executed by the AGUs **212**, **214**. For this embodiment, the 15 integer ALUs **216**, **218**, **220**, are described in the context of performing integer operations on 64 bit data operands. In alternative embodiments, the ALUs **216**, **218**, **220**, can be implemented to support a variety of data bits including 16, 32, 128, 256, etc. Similarly, the floating point units **222**, **224**, can be implemented to support a range of operands 20 having bits of various widths. For one embodiment, the floating point units **222**, **224**, can operate on 128 bits wide packed data operands in conjunction with SIMD and multimedia instructions.

**[0069]** In this embodiment, the uops schedulers **202**, **204**, **206**, dispatch dependent operations before the parent load has finished executing. As uops are speculatively scheduled and executed in processor **200**, the processor **200** also includes logic to handle 25 memory misses. If a data load misses in the data cache, there can be dependent operations

in flight in the pipeline that have left the scheduler with temporarily incorrect data. A replay mechanism tracks and re-executes instructions that use incorrect data. Only the dependent operations need to be replayed and the independent ones are allowed to complete. The schedulers and replay mechanism of one embodiment of a processor are 5 also designed to catch instruction sequences for shuffle operations.

**[0070]** The term “registers” is used herein to refer to the on-board processor storage locations that are used as part of macro-instructions to identify operands. In other words, the registers referred to herein are those that are visible from the outside of the processor (from a programmer’s perspective). However, the registers of an embodiment should not 10 be limited in meaning to a particular type of circuit. Rather, a register of an embodiment need only be capable of storing and providing data, and performing the functions described herein. The registers described herein can be implemented by circuitry within a processor using any number of different techniques, such as dedicated physical registers, dynamically allocated physical registers using register renaming, combinations of 15 dedicated and dynamically allocated physical registers, etc. In one embodiment, integer registers store 32 bit integer data. A register file of one embodiment also contains eight multimedia SIMD registers for packed data. For the discussions below, the registers are understood to be data registers designed to hold packed data, such as 64 bits wide MMX<sup>TM</sup> registers (also referred to as ‘mm’ registers in some instances) in microprocessors enabled 20 with MMX technology from Intel Corporation of Santa Clara, California. These MMX registers, available in both integer and floating point forms, can operate with packed data elements that accompany SIMD and SSE instructions. Similarly, 128 bits wide XMM registers relating to SSE2 technology can also be used to hold such packed data operands. In this embodiment, in storing packed data and integer data, the registers do not need to 25 differentiate between the two data types.

[0071] In the examples of the following figures, a number of data operands are described. For simplicity, the initial source data segments are labeled from letter A onwards alphabetically, wherein A is located at the lowest address and Z would be located at the highest address. Thus, A may initially be at address 0, B at address 1, C at address 5 3, and so on. Conceptually, a shuffle operation, as in the packed byte shuffle for one embodiment, entails shuffling data segments from a first operand and rearranging one or more of the source data elements into a pattern specified by a set of masks in a second operand. Thus, a shuffle can rotate or completely rearrange a portion of or all of the data elements into any desired order. Furthermore, any particular data element or number of 10 data elements can be duplicated or broadcasted in the resultant. Embodiments of the shuffle instruction in accordance with the present invention include a flush to zero functionality wherein the mask for each particular data element can cause that data element position to be zeroed out in the resultant.

[0072] Figures 3A-C are illustrations of shuffle masks according to various 15 embodiments of the present invention. A packed data operand **310** comprised of a plurality of individual data elements **311**, **312**, **313**, **314**, is shown in this example. The packed operand **310** of this example is described in the context of a packed data operand for containing a set of masks to indicate a shuffle pattern for corresponding packed data 20 elements of another operand. Thus, the mask in each of the data elements **311**, **312**, **313**, **314**, of packed operand **310** designates the contents in the corresponding data element position of the resultant. For example, data element **311** is in the leftmost data element position. The mask in data element **311** is to designate what data should be shuffled or placed in the leftmost data element position of the resultant for the shuffle operation. Similarly, data element **312** is the second leftmost data element position. The mask in data 25 element **312** is to designate what data should be placed in the second leftmost data element

position of the resultant. For this embodiment, each of the data elements in the packed operand containing the shuffle masks has a one to one correspondence to a data element position in the packed resultant.

[0073] In **Fig. 3A**, data element **312** used to describe the contents of an example shuffle mask for one embodiment. The shuffle mask **318** for one embodiment is comprised of three portions: a ‘set to zero flag’ field **315**, a ‘reserved’ field **316**, and a ‘selections bits’ field **317**. The ‘set to zero flag’ field **315** is to indicate whether the resultant data element position designated by the present mask should be zeroed out, or in other words, replaced with a value of zero (‘0’). In one embodiment, the ‘set to zero flag’ field is dominant wherein if the ‘set to zero flag’ field **315** is set, the rest of the fields in the mask **318** are ignored and the resultant data element position is filled with ‘0’. The ‘reserved’ field **316** includes one or more bits that may or may not be used in alternative embodiments or may have been reserved for future or special use. The ‘selection bits’ field **317** of this shuffle mask **318** is to designate the source of the data for the corresponding data element position in the packed resultant.

[0074] For one embodiment of a packed data shuffle instruction, one operand is comprised of a set of masks and another operand is comprised of a set of packed data elements. Both operands are of the same size. Depending on the number of the data elements in the operands, a varying number of selection bits are needed to select an individual data element from the second packed data operand for placement in the packed resultant. For example, with a 128 bit source operand of packed bytes, at least four selection bits are needed as sixteen byte data elements are available for selection. Based on the value indicated by the selection bits of the mask, the appropriate data element from the source data operand is placed in the corresponding data element position for that mask.

25 For example, the mask **318** of data element **312** corresponds to the second leftmost data

element position. If the selection bits **317** of this mask **318** contain a value of 'X', the data element from data element position 'X' in the source data operand is shuffled into the second leftmost data element position in the resultant. But if the 'set to zero flag' field **315** is set, the second leftmost data element position in the resultant is replaced with '0' 5 and the designation of the selection bits **317** ignored.

[0075] **Fig. 3B** illustrates the structure of a mask **328** for one embodiment that operates with byte size data elements and 128 bit wide packed operands. For this embodiment, the 'set to zero' field **325** is comprised of bit 7 and the 'selection' field **327** is comprised of bits 3 through 0 as there are sixteen possible data element selections. Bits 10 6 through 4 are not used in this embodiment and reside in the 'reserved' field **326**. In another embodiment, the number of bits used in the 'selection' field **327** can be increased or decreased as needed in order to accommodate the number of possible data element selections available in the source data operand.

[0076] **Fig. 3C** illustrates the structure of a mask **338** for another embodiment that 15 operates with byte size data elements and 128 bit wide packed operands, but with multiple data element sources. In this embodiment, the mask **338** is comprised of a 'set to zero' field **335**, a 'source (src) select' field **336**, and a 'selection' field **337**. The 'set to zero' field **335** and 'selection' field **337** function similar to the descriptions above. The 'source select' field **336** of this embodiment is to indicate from which data source the data operand 20 specified by the selection bits should be obtained. For example, the same set of masks may be used with multiple data sources such as a plurality of multimedia registers. Each source multimedia register is assigned a numeric value and the value in the 'source select' field **336** points to one of these source registers. Depending on the contents of the 'source select' field **336**, the selected data element is selected from the appropriate data source for 25 placement at that corresponding data element position in the packed resultant.

[0077] **Figure 4A** is an illustration of various packed data type representations in multimedia registers according to one embodiment of the present invention. **Fig. 4A** illustrates a data types for packed byte **410**, packed word **420**, and a packed doubleword (dword) **430** for 128 bits wide operands. The packed byte format **410** of this example is 128 bits long and contains sixteen packed byte data elements. A byte is defined here as 8 bits of data. Information for each byte data element is stored in bit 7 through bit 0 for byte 0, bit 15 through bit 8 for byte 1, bit 23 through bit 16 for byte 2, and finally bit 120 through bit 127 for byte 15. Thus, all available bits are used in the register. This storage arrangement increases the storage efficiency of the processor. As well, with sixteen data elements accessed, one operation can now be performed on sixteen data elements in parallel.

[0078] Generally, a data element is an individual piece of data that is stored in a operand (single register or memory location) with other data elements of the same length. In packed data sequences relating to SSE2 technology, the number of data elements stored 15 in an operand (XMM register or memory location) is 128 bits divided by the length in bits of an individual data element. Similarly, in packed data sequences relating to MMX and SSE technology, the number of data elements stored in an operand (MMX register or memory location) is 64 bits divided by the length in bits of an individual data element. The packed word format **420** of this example is 128 bits long and contains eight packed 20 word data elements. Each packed word contains sixteen bits of information. The packed doubleword format **430** of **Fig. 4A** is 128 bits long and contains four packed doubleword data elements. Each packed doubleword data element contains thirty two bits of information. A packed quadword is 128 bits long and contains two packed quad-word data elements.

[0079] **Figure 4B** illustrates alternative in-register data storage formats. Each packed data can include more than one independent data element. Three packed data formats are illustrated; packed half **441**, packed single **442**, and packed double **443**. One embodiment of packed half **441**, packed single **442**, and packed double **443** contain fixed-point data elements. For an alternative embodiment one or more of packed half **441**, packed single **442**, and packed double **443** may contain floating-point data elements. One alternative embodiment of packed half **441** is one hundred twenty-eight bits long containing eight 16-bit data elements. One embodiment of packed single **442** is one hundred twenty-eight bits long and contains four 32-bit data elements. One embodiment of packed double **443** is one hundred twenty-eight bits long and contains two 64-bit data elements. It will be appreciated that such packed data formats may be further extended to other register lengths, for example, to 96-bits, 160-bits, 192-bits, 224-bits, 256-bits or more.

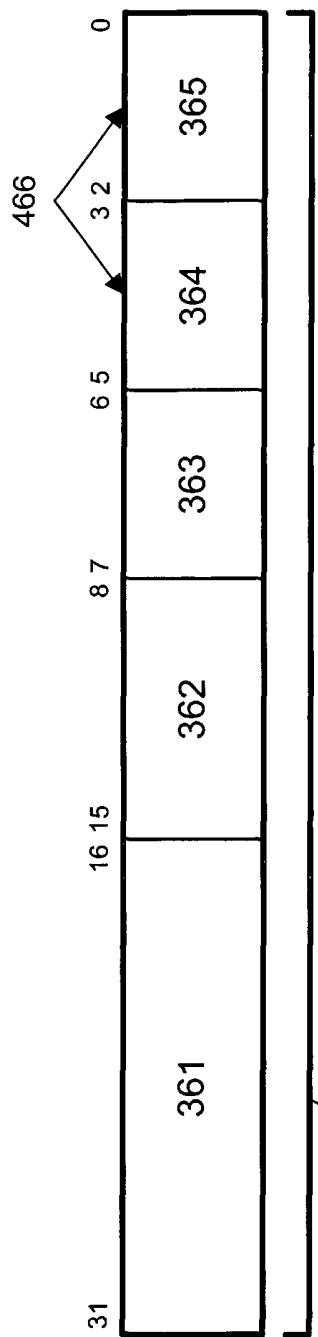

[0080] **Figure 4C** is a depiction of one embodiment of an operation encoding (opcode) format **460**, having thirty-two or more bits, and register/memory operand addressing modes corresponding with a type of opcode format described in the "IA-32 Intel Architecture Software Developer's Manual Volume 2: Instruction Set Reference," which is available from Intel Corporation, Santa Clara, CA on the world-wide-web ([www.intel.com/design/litcentr](http://www.intel.com/design/litcentr)). The type of shuffle operation, may be encoded by one or more of fields **461** and **462**. Up to two operand locations per instruction may be identified, including up to two source operand identifiers **464** and **465**. For one embodiment of a shuffle instruction, destination operand identifier **466** is the same as source operand identifier **464**. For an alternative embodiment, destination operand identifier **466** is the same as source operand identifier **465**. Therefore, for embodiments of a shuffle operation, one of the source operands identified by source operand identifiers **464** and **465** is overwritten by the results of the shuffle operations. For one embodiment

of the shuffle instruction, operand identifiers **464** and **465** may be used to identify 64-bit source and destination operands.

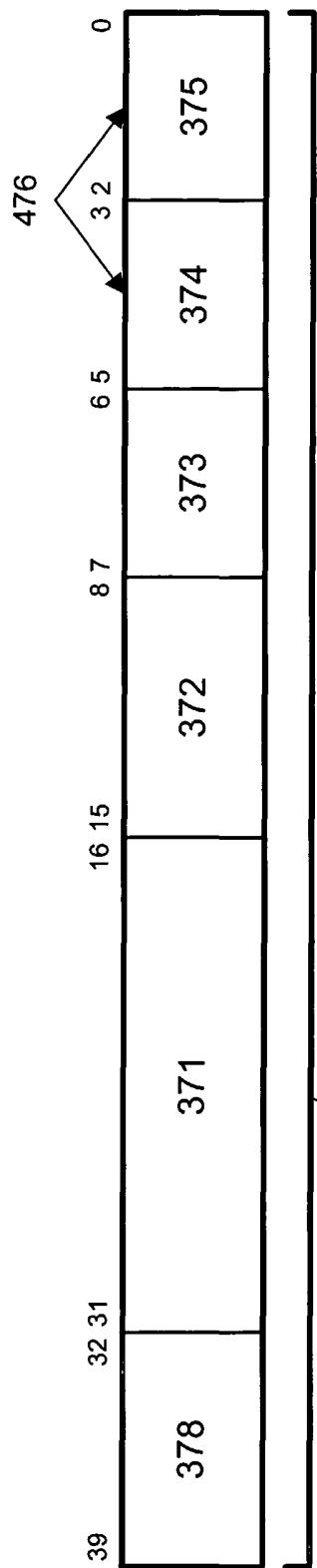

[0081] **Figure 4D** is a depiction of another alternative operation encoding (opcode) format **470**, having forty or more bits. Opcode format **470** corresponds with opcode format **460** and comprises an optional prefix byte **478**. The type of shuffle operation, may be encoded by one or more of fields **478**, **471**, and **472**. Up to two operand locations per instruction may be identified by source operand identifiers **474** and **475** and by prefix byte **478**. For one embodiment of the shuffle instruction, prefix byte **478** may be used to identify 128-bit source and destination operands. For one embodiment of the shuffle instruction, destination operand identifier **476** is the same as source operand identifier **474**.

For an alternative embodiment, destination operand identifier **476** is the same as source operand identifier **475**. Therefore, for embodiments of shuffle operations, one of the source operands identified by source operand identifiers **474** and **475** is overwritten by the results of the shuffle operations. Opcode formats **460** and **470** allow register to register, memory to register, register by memory, register by register, register by immediate, register to memory addressing specified in part by MOD fields **463** and **473** and by optional scale-index-base and displacement bytes.

[0082] Turning next to **Figure 4E**, in some alternative embodiments, 64 bit single instruction multiple data (SIMD) arithmetic operations may be performed through a coprocessor data processing (CDP) instruction. Operation encoding (opcode) format **480** depicts one such CDP instruction having CDP opcode fields **482** and **489**. The type of CDP instruction, for alternative embodiments of shuffle operations, may be encoded by one or more of fields **483**, **484**, **487**, and **488**. Up to three operand locations per instruction may be identified, including up to two source operand identifiers **485** and **490** and one destination operand identifier **486**. One embodiment of the coprocessor can

operate on 8, 16, 32, and 64 bit values. For one embodiment, the shuffle operation is performed on fixed-point or integer data elements. In some embodiments, a shuffle instruction may be executed conditionally, using condition field **481**. For some shuffle instructions source data sizes may be encoded by field **483**. In some embodiments of a 5 shuffle instruction, Zero (Z), negative (N), carry (C), and overflow (V) detection can be done on SIMD fields. For some instructions, the type of saturation may be encoded by field **484**.

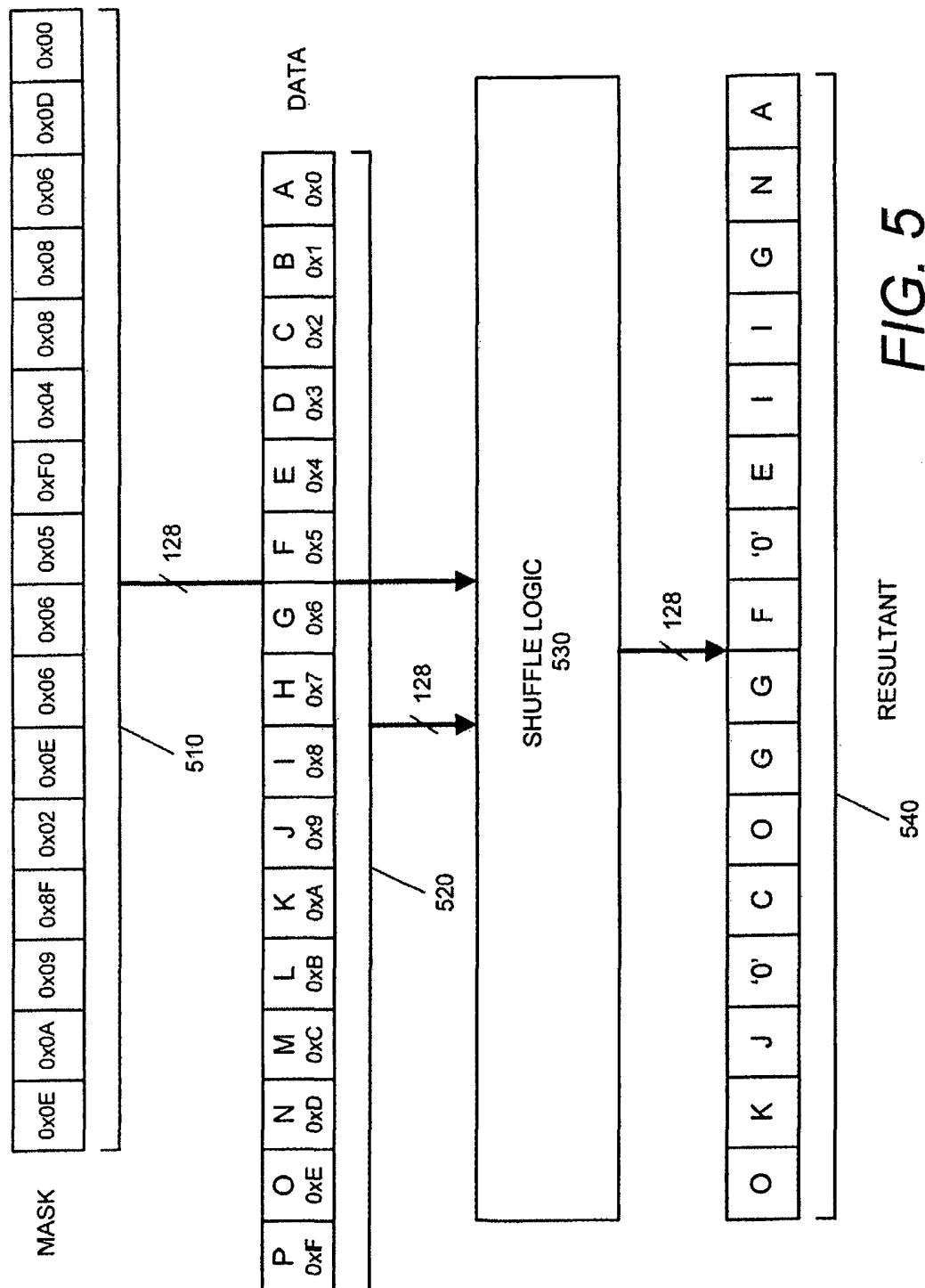

[0083] **Figure 5** is a block diagram of one embodiment of logic to perform a shuffle operation on a data operand based on a shuffle mask in accordance with the present 10 invention. The instruction (PSHUFB) for shuffle operation with a set to zero capability of this embodiment begins with two pieces of information a first (mask) operand **510** and a second (data) operand **520**. For the following discussions, MASK, DATA, and RESULTANT are generally referred to as operands or data blocks, but not restricted as such, and also include registers, register files, and memory locations. In one embodiment, 15 the shuffle PSHUFB instruction is decoded into one micro-operation. In an alternative embodiment, the instruction may be decoded into a various number of micro-ops to perform the shuffle operation on the data operands. For this example, the operands **510**, **520**, are 128 bit wide pieces of information stored in a source register/memory having byte wide data elements. In one embodiment, the operands **510**, **520**, are held in 128 bit long 20 SIMD registers, such as 128 bit SSE2 XMM registers. However, one or both of the operands **510**, **520**, can also be loaded from a memory location. For one embodiment, the RESULTANT **540** is also a MMX or XMM data register. Furthermore, RESULTANT **540** may also be the same register or memory location as one of the source operands. Depending on the particular implementation, the operands and registers can be other 25 widths such as 32, 64, and 256 bits, and have word, doubleword, or quadword sized data

elements. The first operand **510** in this example is comprised of a set of sixteen masks (in hexadecimal format): 0x0E, 0x0A, 0x09, 0x8F, 0x02, 0x0E, 0x06, 0x06, 0x06, 0xF0, 0x04, 0x08, 0x08, 0x06, 0x0D, and 0x00. Each individual mask is to specify the contents of its corresponding data element position in the resultant **540**.

5 [0084] The second operand **520** is comprised of sixteen data segments: P, O, N, M, L, K, J, I, H, G, F, E, D, C, B, and A. Each data segment in the second operand **520** is also labeled with a data element position value in hex format. The data segments here are of equal length and each comprise of a single byte (8 bits) of data. If each data element was a word (16 bits), doubleword (32 bits), or a quadword (64 bits), the 128 bit operands

10 would have eight word wide, four doubleword wide, or two quadword wide data elements, respectively. However, another embodiment of the present invention can operate with other sizes of operands and data segments. Embodiments of the present invention are not restricted to particular length data operands, data segments, or shift counts, and can be sized appropriately for each implementation.

15 [0085] The operands **510**, **520**, can reside either in a register or a memory location or a register file or a mix. The data operands **510**, **520**, are sent to the shuffle logic **530** of an execution unit in the processor along with a shuffle instruction. By the time the shuffle instruction reaches the execution unit, the instruction should have been decoded earlier in the processor pipeline. Thus the shuffle instruction can be in the form of a micro

20 operation (uop) or some other decoded format. For this embodiment, the two data operands **510**, **520**, are received at shuffle logic **530**. The shuffle logic **530** selects data elements from the source data operand **520** based on the values in the mask operand **510** and arranges/shuffles the selected data elements into the appropriate positions in the resultant **540**. The shuffle logic **530** also zeroes out the given data element positions in the

resultant **540** as specified. Here, the resultant **540** is comprised of sixteen data segments: O, K, J, '0', C, O, G, G, F, '0', E, I, I, G, N, and A.

[0086] The operation of the shuffle logic **530** is described here with a couple few of the data elements. The shuffle mask for the leftmost data element position in the mask operand **510** is 0x0E. The shuffle logic **530** interprets the various fields of the mask described as above in **Fig. 3A-C**. In this case, the 'set to zero' field is not set. The selection field, comprising the lower four bits or nibble, has a hex value of 'E'. The shuffle logic **530** shuffles the data, O, in the data element position '0xE' of the data operand **520** to the leftmost data element position of the resultant **540**. Similarly, the mask at the second leftmost data element position in the mask operand **510** is 0x0A. The shuffle logic **530** interprets the mask for that position. This selection field has a hex value of 'A'. The shuffle logic **530** copies the data, K, in the data element position '0xA' of the data operand **520** to the second leftmost data element position of the resultant **540**.

[0087] The shuffle logic **530** of this embodiment also supports the flush to zero function of the shuffle instruction. The shuffle mask at the fourth data element position from the left for the mask operand **510** is 0x8F. The shuffle logic **510** recognizes that the 'set to zero' field is set as indicated by a '1' at bit 8 of the mask. In response, the flush to zero directive trumps the selection field and the shuffle logic **510** ignores the hex value 'F' in the selection field of that mask. A '0' is placed in the corresponding fourth data element position from the left in the resultant **540**. For this embodiment, the shuffle logic **530** evaluates the 'set to zero' and selection fields for each mask and does not care about the other bits that may exist outside of those fields in the mask, such as reserved bits or a source select field. This processing of the shuffle masks and data shuffling is repeated for the entire set of masks in the mask operand **510**. For one embodiment, the masks are all

processed in parallel. In another embodiment, a certain portion of the mask set and data elements can be processed together at a time.

[0088] With embodiments of the present shuffle instruction, data elements in an operand can be rearranged in various ways. Furthermore, certain data from particular data element can be repeated at multiple data element positions or even broadcasted to every position. For instance, the fourth and fifth masks both have a hex value of 0x08. As a

5 element can be repeated at multiple data element positions or even broadcasted to every position. For instance, the fourth and fifth masks both have a hex value of 0x08. As a result, the data, I, at data element position 0x8 of the data operand **520** is shuffled into both the fourth and fifth data element positions from the right side of the resultant **540**.

With the set to zero functionality, embodiments of the shuffle instruction can force any of

10 the data element positions in the resultant **540** to '0'.

[0089] Depending on the particular implementation, each shuffle mask can be used to designate the content of a single data element position in the resultant. As in this example, each individual byte wide shuffle mask corresponds to a byte wide data element position

in the resultant **540**. In another embodiment, combinations of multiple masks can be used

15 to designate blocks of data elements together. For example, two byte wide masks can be used together to designate a word wide data element. Shuffle masks are not restricted to being byte wide and can be any other size needed in that particular implementation.

Similarly, data elements and data element positions can possess other granularities other than bytes.

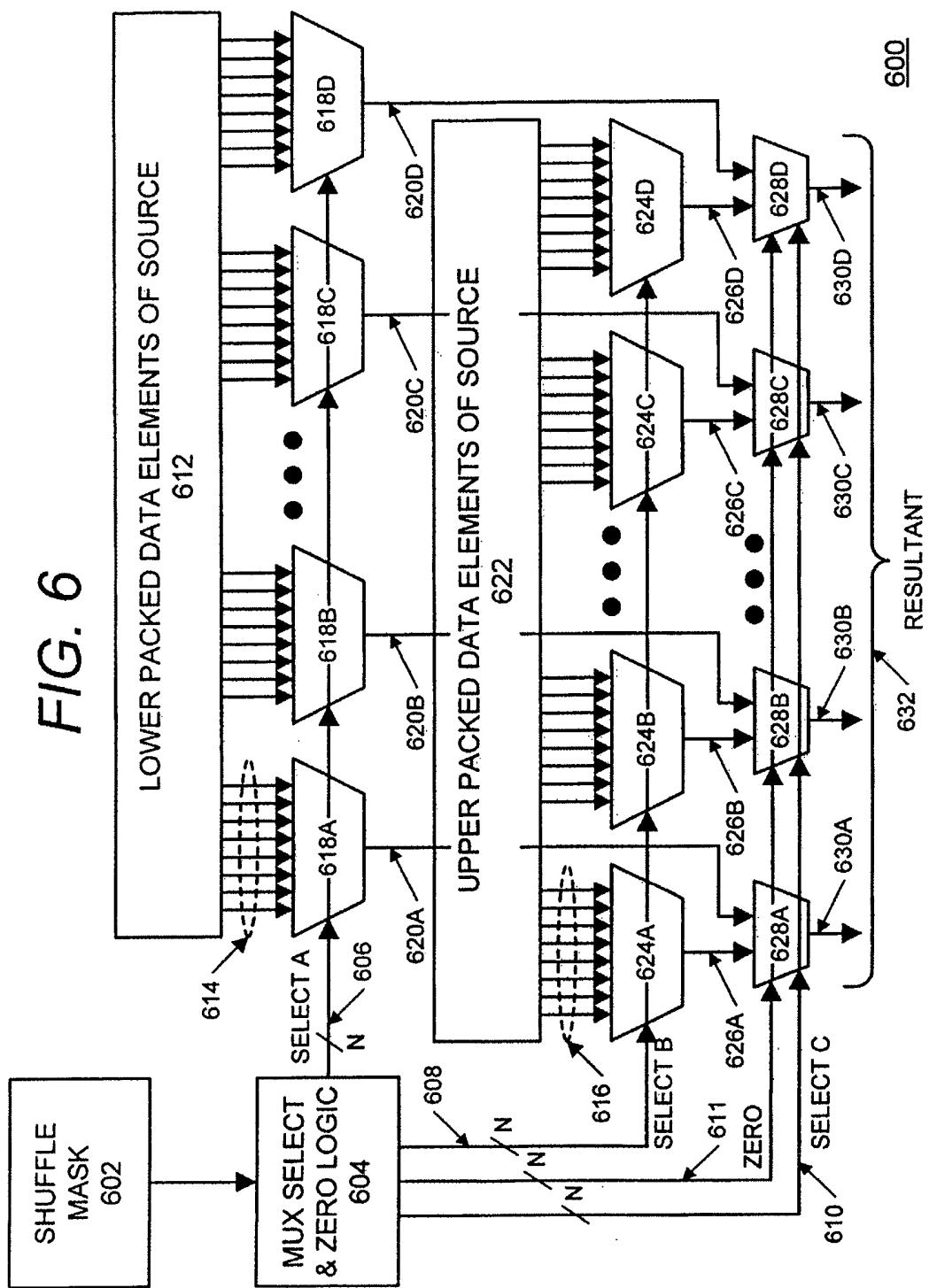

20 [0090] **Figure 6** is a block diagram of one embodiment of a circuit **600** for performing a data shuffling operation in accordance with the present invention. The circuit of this embodiment comprises a multiplexing structure to select the correct result byte from the first source operand based on decoding shuffle mask of the second operand. The source data operand here is comprised of the upper packed data elements and the lower packed data elements. The multiplexing structure of this embodiment is relatively simpler than

other multiplexing structures used to implement other packed instructions. As a result, the multiplexing structure of this embodiment does not introduce any new critical timing path.

The circuit **600** of this embodiment includes a shuffle mask block, blocks to hold lower/upper packed data elements from source operands, a first plurality of eight to one

5 (8:1) muxes for initial selection of data elements, another plurality of three to one (3:1) muxes for selection of upper and lower data elements, mux select & zero logic and a multitude of control signals. For simplicity, a limited number of the 8:1 and 3:1 muxes are shown in **Fig. 6** and represented by dots. However, their function is similar to those illustrated and can be understood from the description below.

10 [0091] During a shuffle operation in this example, two operands are received at this shuffle handling circuit **600**: a first operand with a set of packed data elements and a second operand with a set of shuffle masks. The shuffle masks are propagated to shuffle mask block **602**. The set of shuffle masks are decoded at the mux select and zero logic block **604** to generate a variety of select signals (SELECT A **606**, SELECT B **608**, SELECT C **610**) and a set to zero signal (ZERO) **611**. These signals are used to control the operation of the muxes in piecing together the resultant **632**.

15 [0092] For this example, the mask operand and data operand are both 128 bits long and each are packed with of sixteen byte size data segments. The value N as shown on various signals is sixteen in this case. In this embodiment, the data elements are separated 20 into a set of lower and upper packed data elements, each set having eight data elements.

This allows for the use of smaller 8:1 muxes during the data element selection rather than 16:1 muxes. These lower and upper sets of packed data elements are held at lower and upper storage areas **612**, **622**, respectively. Starting with the lower data set, each of the 25 eight data elements are sent to the first set of sixteen individual 8:1 muxes **618A-D** via a set of lines such as routing lines **614**. Each of the sixteen 8:1 muxes **618A-D** are

controlled with one of the N SELECT A signals **606**. Depending on the value of its SELECT A **606**, that mux is to output one of the eight lower data elements **614** for further processing. There are sixteen 8:1 muxes for the set of lower packed data elements as it is possible to shuffle any of the lower data elements into any of the sixteen resultant data 5 element positions. Each of the sixteen 8:1 muxes is for one of the sixteen resultant data element positions. Similarly, sixteen 8:1 muxes are present for the upper packed data elements. The eight upper data elements are sent to each of the second set of sixteen 8:1 muxes **624A-D**. Each of the sixteen 8:1 muxes **624A-D** are controlled with one of the N SELECT B signals **608**. Based on the values of its SELECT B **608**, that 8:1 mux is to 10 output one of the eight upper data elements **616** for further processing.

[0093] Each of the sixteen 3:1 muxes **628A-D** corresponds to a data element position in the resultant **632**. The sixteen outputs **620A-D** from the sixteen lower data muxes **618A-D** are routed to a set of sixteen 3:1 upper/lower selection muxes **628A-D** as are the outputs **626A-D** from the upper data muxes **624A-D**. Each of these 3:1 selection muxes 15 **628D-D** receives its own SELECT C **610** and a ZERO **611** signals from the mux select & zero logic **604**. The value on the SELECT C **610** for that 3:1 mux is to indicate whether the mux is to output the selected data operand from the lower data set or from the upper data set. The control signal ZERO **611** to each 3:1 mux is to indicate whether that mux should force its output to zero ('0'). For this embodiment, the control signal ZERO **611** 20 supercedes the selection on SELECT C **610** and forces the output for that data element position to '0' in the resultant **632**.

[0094] For example, 3:1 mux **628A** receives the selected lower data element **620A** from 8:1 mux **618A** and the selected upper data element **626A** from 8:1 mux **624A** for that data element position. SELECT C **610** controls which of the data elements to shuffle at its 25 output **630A** into the data element position it manages in the resultant **632**. However, if

signal ZERO **611** to the mux **628A** is active, indicated that the shuffle mask for that data element position states that a ‘0’ is desired, the mux output **630A** is ‘0’ and neither of the data element inputs **620A**, **626A**, are used. The resultant **632** of the shuffle operation is composed of the outputs **630A-D** from the sixteen 3:1 muxes **628A-D**, wherein each

5 output corresponds to a specific data element position and is either a data element or a ‘0’.

In this example, each 3:1 mux output is a byte wide and the resultant is a data block composed of sixteen packed bytes of data.

[0095] **Figure 7** illustrates the operation of a data shuffle on byte wide data elements in accordance with one embodiment of the present invention. This is an example of the

10 instruction “PSHUFB DATA, MASK”. Note that the most significant bit of shuffle masks for byte positions 0x6 and 0xC of MASK **701** are set so the result in resultant **741** for those positions are zero. In this example, source data is organized into a destination data storage device **721**, which in one embodiment is also the source data storage device **721**, in view of a set of masks **701** that specify the address wherein

15 respective data elements from the source operand **721** are to be stored in the destination register **741**. The two source operands, mask **701** and data **721**, each comprise of sixteen packed data elements in this example, as does the resultant **741**. In this embodiment, each of the data elements involved is a eight bits or a byte wide. Thus mask **701**, data **721**, and resultant **741** data blocks are each 128 bits long. Furthermore, these data blocks can reside

20 in memory or registers. For one embodiment, the arrangement of the masks is based on the desired data processing operation, which may include for example, a filtering operation or a convolution operation.

[0096] As shown in **Fig. 7**, mask operand **701** includes data elements with shuffle masks of: 0x0E **702**, 0x0A **703**, 0x09 **704**, 0x8F **705**, 0x02 **706**, 0x0E **707**, 0x06 **708**, 0x06

25 **709**, 0x05 **710**, 0xF0 **711**, 0x04 **712**, 0x08 **713**, 0x08 **714**, 0x06 **715**, 0x0D **716**, 0x00 **717**.

Similarly, data operand **721** includes source data elements of: P **722**, O **723**, N **724**, M **725**, L **726**, K **727**, J **728**, I **729**, H **730**, G **731**, F **732**, E **733**, D **734**, C **735**, B **736**, A **737**.

In the representations of data segments of **Fig. 7**, the data element position is also noted under the data as a hex value. Accordingly, a packed shuffle operation is performed with 5 the mask **701** and data **721**. Using the set of shuffle masks **701**, processing of the data **721** can be performed in parallel.