【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第7部門第3区分

【発行日】平成23年9月15日(2011.9.15)

【公開番号】特開2011-40826(P2011-40826A)

【公開日】平成23年2月24日(2011.2.24)

【年通号数】公開・登録公報2011-008

【出願番号】特願2009-183673(P2009-183673)

【国際特許分類】

H 03 K 3/3562 (2006.01)

H 01 L 21/82 (2006.01)

H 01 L 27/04 (2006.01)

H 01 L 21/822 (2006.01)

【F I】

H 03 K 3/356 C

H 01 L 21/82 B

H 01 L 27/04 A

H 01 L 27/04 D

H 01 L 21/82 W

【手続補正書】

【提出日】平成23年8月1日(2011.8.1)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

C M O S 半導体集積回路内に構成されたフリップフロップ回路を備える半導体装置であつて、

前記フリップフロップ回路は、少なくとも、

第1のクロック信号を生成する、第1のクロック生成インバーターと、

前記第1のクロック信号を反転させた第2のクロック信号を生成する、第2のクロック生成インバーターと、

を備え、

前記第1及び第2のクロック生成インバーターは、前記フリップフロップ回路のマスター・ラッチ部とスレーブラッチ部とから構成されるラッチ部を挟むように配置され、

前記第1のクロック生成インバーターと、前記第1のクロック生成インバーターに隣り合う前記フリップフロップ回路内の第1の他の回路とは、ソース領域を共有し、

前記第2のクロック生成インバーターと、前記第2のクロック生成インバーターに隣り合う前記フリップフロップ回路内の第2の他の回路とは、ソース領域を共有する、

ものとして構成されていることを特徴とする、半導体装置。

【請求項2】

前記フリップフロップ回路は、

入力信号に基づいて前記ラッチ部に信号を供給する、前記第2の他の回路としての入力回路部と、

前記ラッチ部からの信号に基づいて出力信号を出力する、前記第1の他の回路としての出力回路部と、

を更に備え、

回路配置が、

前記入力回路部、前記第2のクロック生成インバーター、前記マスター・ラッチ部、前記スレーブ・ラッチ部、前記第1のクロック生成インバーター、及び、前記出力回路部の順であることを特徴とする、請求項1に記載の半導体装置。

【請求項3】

前記第1及び第2のクロック生成インバーター間は、金属配線とゲート配線との少なくとも何れかで接続されていることを特徴とする、請求項1又は請求項2に記載の半導体装置。

【請求項4】

前記第1のクロック生成インバーターと、前記第1の他の回路とにおける、PMOSトランジスタの拡散領域は一体に形成され、NMOSトランジスタの拡散領域は一体に形成されており、

前記第2のクロック生成インバーターと、前記第2の他の回路とにおける、PMOSトランジスタの拡散領域は一体に形成され、NMOSトランジスタの拡散領域は一体に形成されており、

前記ラッチ部における、PMOSトランジスタの拡散領域は一体に形成され、NMOSトランジスタの拡散領域は一体に形成されていることを特徴とする、請求項1から請求項3の何れかに記載の半導体装置。

【請求項5】

前記第1のクロック生成インバーターと、前記第1の他の回路とにおける、PMOSトランジスタの拡散領域は一体に形成され、NMOSトランジスタの拡散領域は一体に形成されており、

前記第2のクロック生成インバーターと、前記第2の他の回路と、前記ラッチ部とにおける、PMOSトランジスタの拡散領域は一体に形成され、NMOSトランジスタの拡散領域は一体に形成されていることを特徴とする、請求項1に記載の半導体装置。

【手続補正2】

【補正対象書類名】図面

【補正対象項目名】図5

【補正方法】変更

【補正の内容】

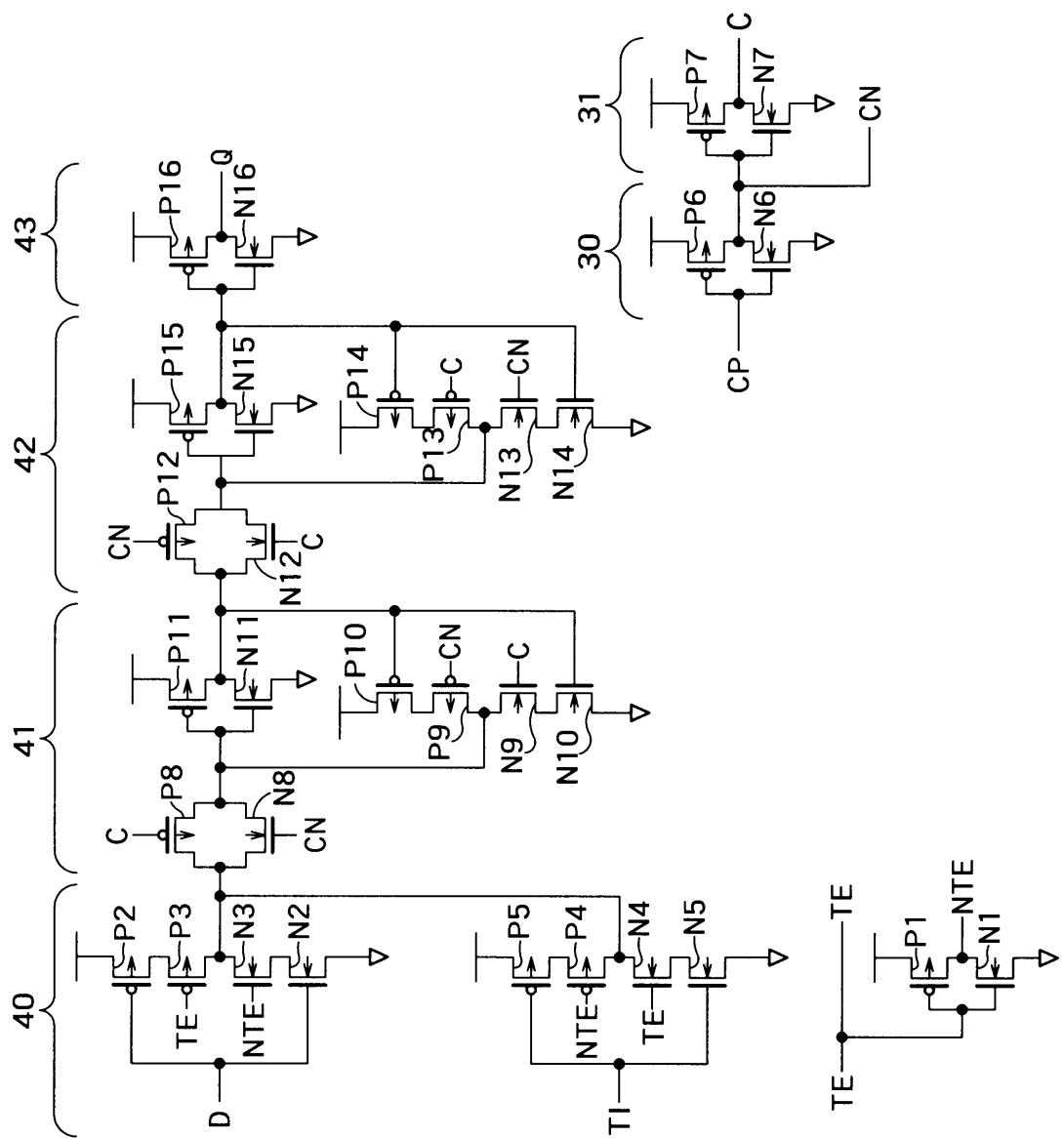

【図 5】

【手続補正 3】

【補正対象書類名】図面

【補正対象項目名】図 10

【補正方法】変更

【補正の内容】

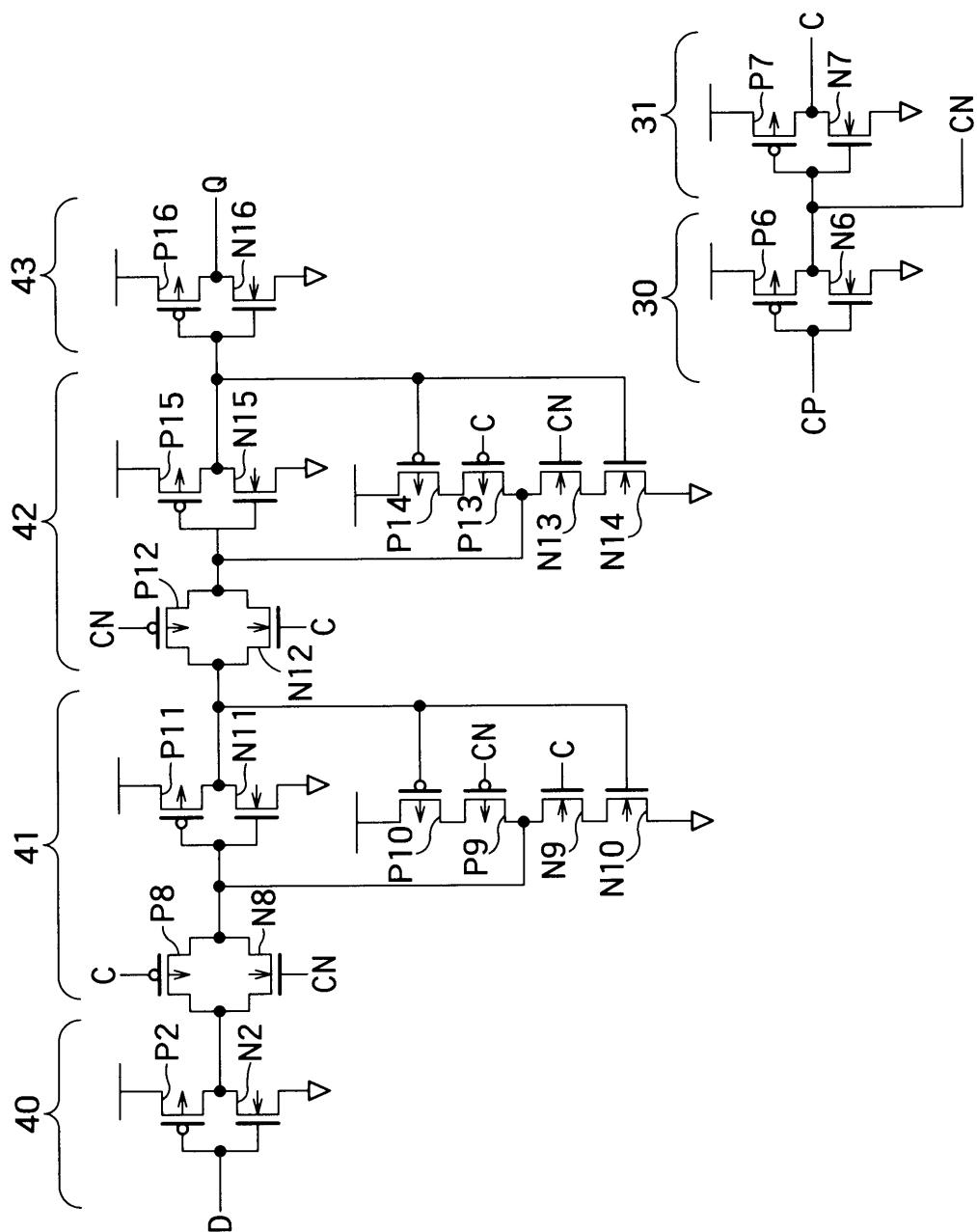

【図 10】