(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4884586号

(P4884586)

(45) 発行日 平成24年2月29日(2012.2.29)

(24) 登録日 平成23年12月16日(2011.12.16)

(51) Int.Cl.

F 1

G02F 1/1368 (2006.01)

G02F 1/1368

G02F 1/1345 (2006.01)

G02F 1/1345

請求項の数 7 (全 35 頁)

(21) 出願番号 特願2000-384173 (P2000-384173)

(22) 出願日 平成12年12月18日 (2000.12.18)

(65) 公開番号 特開2002-182221 (P2002-182221A)

(43) 公開日 平成14年6月26日 (2002.6.26)

審査請求日 平成19年11月13日 (2007.11.13)

(73) 特許権者 502356528

株式会社 日立ディスプレイズ

千葉県茂原市早野3300番地

(73) 特許権者 506087819

パナソニック液晶ディスプレイ株式会社

兵庫県姫路市飾磨区妻鹿日田町1-6

(74) 代理人 100083552

弁理士 秋田 収喜

(74) 代理人 110000154

特許業務法人はるか国際特許事務所

(72) 発明者 柳川 和彦

千葉県茂原市早野3300番地 株式会社

日立製作所 ディスプレイグループ内

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

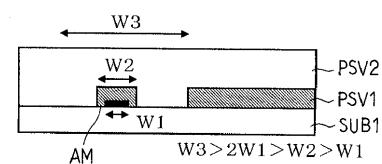

液晶を介して対向配置される各基板のうち一方の基板に、複数のゲート信号線及びドレン信号線を形成し、無機材料層と有機材料層との順次積層体を形成し、前記基板端に、前記ゲート信号線或いは前記ドレン信号線に接続されるドライバチップを搭載したフィルム状基板が接続されているとともに、

該ドライバチップの近傍の前記積層体の下層にアライメントマークが形成され、このアライメントマークを被う前記無機材料層は中心軸をほぼ一致させて該アライメントマークより大きな面積で、かつ、相似的なパターンで残存する領域が形成され、更に当該残存領域周辺に前記無機材料層の除去領域が形成されていることを特徴とする液晶表示装置。

## 【請求項 2】

前記アライメントマークの幅をW1、前記残存領域の幅をW2、前記除去領域の幅をW3とした時、

$$W3 > 2W1 > W2 > W1$$

の関係を満たすように、前記アライメントマーク、前記残存領域、前記除去領域が形成されることを特徴とする請求項1に記載の液晶表示装置。

## 【請求項 3】

前記アライメントマークの幅をW1、前記残存領域の幅をW2、前記除去領域の幅をW3とした時、

$$W2 < 2W1、かつW3 > 3W1$$

の関係を満たすように、前記アライメントマーク、前記残存領域、前記除去領域が形成されることを特徴とする請求項 1 に記載の液晶表示装置。

【請求項 4】

前記除去領域内の有機材料層が除去されていることを特徴とする請求項 1 に記載の液晶表示装置。

【請求項 5】

前記アライメントマークは、円形であることを特徴とする請求項 1 に記載の液晶表示装置。

【請求項 6】

前記アライメントマークは、矩形であることを特徴とする請求項 1 に記載の液晶表示装置。 10

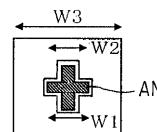

【請求項 7】

前記アライメントマークは、十文字形であることを特徴とする請求項 1 に記載の液晶表示装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は液晶表示装置に係り、アクティブ・マトリクス型と称される液晶表示装置に関する。 20

【0002】

【従来の技術】

アクティブ・マトリクス型の液晶表示装置は、液晶を介して対向配置される各基板のうち一方の基板の液晶の面側に、 $x$  方向に延在し  $y$  方向に並設されるゲート信号線と  $y$  方向に延在し  $x$  方向に並設されるドレイン信号線とで囲まれる各領域を画素領域としている。

【0003】

そして、各画素領域には片側のゲート信号線からの走査信号によって作動するスイッチング素子と、このスイッチング素子を介して片側のドレイン信号線からの映像信号が供給される画素電極とを備えている。

【0004】

この画素電極は対向電極との間に電界を発生せしめて液晶の光透過率を制御することになるが、この対向電極は他方の基板の液晶の面側に形成される種類のもの、あるいは前記一方の基板の液晶の面側に形成される種類のものが知られている。 30

【0005】

各基板の液晶の面側には所定のパターンで形成された導電層、半導体層、あるいは絶縁層等の積層体によって電子回路が組み込まれている。

【0006】

この場合、前記一方の基板の液晶の面側に形成される各信号線あるいは電極等との層間絶縁を図る絶縁層として有機絶縁膜を用いることが知られるに到っている。低誘電率の有機絶縁膜を用いることによって寄生容量を低減させるためである。

【0007】

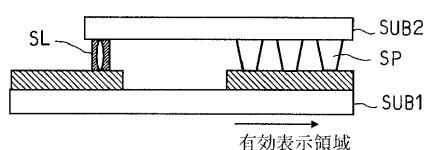

また、液晶を介して対向配置される各基板のギャップを確保するため、いずれかの基板の液晶の側面に形成された支柱でスペーサの機能を持たせるようにしたのも知られている。従前のビーズあるいはファイバと比較して、所定の位置に該支柱を形成でき各基板のギャップの均一性を確保しやすいからである。 40

【0008】

また、ゲート信号線あるいはドレイン信号線への信号の供給を行う駆動回路 I C ( ドライバチップ ) は、該各信号線が形成された一方の基板に実装されているが、近年になって、前記ドライバチップをそのままフェースダウンで搭載してその入力アンプおよび出力アンプを基板上の配線層 ( 信号線 ) に接続せしむるいわゆる F C A ( あるいは C O G ) 方式と称される実装が多く採用されている。 50

## 【0009】

液晶表示装置の高精細化にともない、外部への引出配線の本数を低減できるからである。

## 【0010】

さらに、前記ドライバチップへの信号および電源の供給として、前記基板に近接して配置されるプリント配線基板面に前記信号および電源の供給配線を形成し、ここから各ドライバチップに個別に信号および電源を供給する構成のものが一般的である。しかし、近年、低コスト化を図るため、前記信号および電源のうち少なくとも一方の伝達を前記プリント配線基板を経由しないで行う構成のものが知られてきている。

## 【0011】

## 【発明が解決しようとする課題】

10

しかし、上述した構成からなる液晶表示装置は、次に示すような各課題があることを見出した。

## 【0012】

## (参考課題1)

液晶表示パネルの上下基板間のギャップ(セルギャップ)を一方の基板面に形成された有機材料の支柱にて行う場合、その支柱の軸に交差する平面における面積が露光による最小加工寸法の関係でビーズよりも大きくなるため、支柱周辺での光漏れ領域がビーズ周辺よりも大きくなってしまうという不都合がある。

## 【0013】

## (参考課題2)

20

FCA方式の液晶表示装置では、基板上にドライバチップをそのまま実装するため、基板とドライバチップの接続部の面積が大幅に小さくなり、異物あるいはゴミにより接続不良が発生しやすいという不都合がある。

## 【0014】

また、この方式において、基板とドライバチップとの接続は異方性導電膜を介して行っているのが通常であるが、その接続不良が生じた場合には、該異方性導電膜を溶剤によって除去し、新たな異方性導電膜とドライバチップとを搭載するようにしてリペアしていた。

## 【0015】

一方、本発明者等は、液晶表示部に形成されるスイッチング素子を液晶との直接の接触を回避するための保護膜として有機絶縁膜を用い、この有機絶縁膜をドライバチップの実装領域にまで延在させる試みがなされている。

30

## 【0016】

この場合にあって、リペア時に前記異方性導電膜を除去する際に、該有機絶縁膜をも不均一に剥がれたりする不都合がある。そして、このような不都合をもたらさない場合でも、有機絶縁膜が前記溶剤によって溶け出し、端子部の表面に薄い絶縁層を形成し、これがドライバチップと配線層との接続抵抗を増大させていた。

## 【0017】

## (参考課題3)

FCA方式の液晶表示装置では、基板上にドライバチップをそのまま実装するため、液晶表示装置に過大な振動や衝撃が加わった場合に、その振動や衝撃が吸収され難いので、該ドライバチップに動作不良を起こしやすいという不都合があった。

40

## 【0018】

また、FCA方式の液晶表示装置では、ドライバチップが実装された側の基板を観察者側から遠い側の基板とすることが多い。この理由は、該基板はその液晶表示部に各種の信号線が形成され、その信号線による光反射を回避するためである。

## 【0019】

このため、いわゆる液晶表示モジュールとして構成するためのフレームを被せた場合、該ドライバチップは該フレームと対向して配置され、たとえば該フレームにその変形を及ぼす程度の圧力が加わった場合に、それがドライバチップにまで及んで動作不良を引き起こすという不都合があった。

50

## 【0020】

## (参考課題4)

上述したように、液晶表示部の保護膜として有機絶縁膜を用いる試みにあって、この有機絶縁膜は吸湿、発ガスしやすいという性質から、液晶中に気泡を発生せしめる不都合を見出した。

## 【0021】

その気泡は液晶の封入口から遠い側において多く発生し、またそのうち大きいものは液晶表示領域にまで現出するようになる。

## 【0022】

## (参考課題5)

10

液晶表示パネルの上下基板間のギャップを一方の基板側に形成した有機材料の支柱で行う場合、該支柱の接触する他方の基板側の位置は定まったものとなる。このため液晶表示装置に加わる振動および衝撃は該位置に集中する。

## 【0023】

この場合、配線層が設けられた基板上に支柱を設ける場合、支柱自体が衝撃を吸収する層になり、また、その固定された面積も比較的大きくなることから配線層の断線等の影響は回避できる。

## 【0024】

しかし、配線層が設けられた基板以外の他方の基板に設けられている場合、支柱の頂面側の基板との接触面積は比較的小さく、ここの個所にて圧力、衝撃が集中し、この部分に配線層が形成されている場合には、その断線にまで到るという不都合が生じる。

20

## 【0025】

## (課題)

基板上にドライバを実装する場合、精度よい搭載を行う必要があるが、そのために該基板上にアライメントマークが形成される。

## 【0026】

しかし、保護膜として無機材料層と有機材料層との順次積層体を用いる場合、それがアライメントマークの画像認識を不明瞭にし、精度よいアライメントが困難となる新たな不都合を見出した。

## 【0027】

30

基板に対するドライバの実装がFCAの場合、その端子ピッチが狭く、より高精度のアライメントが要求されるが、保護膜を上述した積層体で形成した場合には、特に反射モードでのアライメントマークの認識が極めて困難となる。

## 【0028】

## (参考課題6)

基板に実装されたドライバ(チップ)への信号および電源の供給として、低コスト化のため、チップ間の電源あるいは信号の少なくとも一方の伝達をプリント基板(PCB)を経由せずにを行うことが開発されつつある。

## 【0029】

しかし、この方法は、基板上にチップ間の電源あるいは信号の少なくとも一方の伝達配線を設けなければなくなるが、その距離は極めて長くなってしまう。

40

## 【0030】

ちなみに、液晶表示部から端子部まで延在される配線は、それが空気中の湿度に晒される環境にある長さが僅かであり、これと比べて上述した伝達配線は数倍から数十倍の長さに及ぶ。

## 【0031】

このことから、該伝達配線の劣化が憂慮され、特に電源伝送配線で電食の発生の畏れがあり、現在、その対策として信号配線のみ基板上に形成し、電源配線はPCBから供給する試みが本願出願人によりなされている。

## 【0032】

50

しかし、この方法は当初の目的である低コスト化の効果が充分でなく、信頼性の低下を回避しつつ電源配線も基板上に配置する必要性が生じてきている。

【0033】

本発明はこのような課題を解消すべくなされたものである。

【0034】

すなわち、本発明の参考目的は、セルギャップを確保するための支柱の周辺に生じる光漏れを低減させた液晶表示装置を提供することにある。

【0035】

本発明の他の参考目的は、液晶を介して対向配置される基板のうち一方の基板面に実装されるドライバチップの実装におけるリペアを信頼性よく行い得る液晶表示装置を提供することにある。 10

【0036】

本発明の他の参考目的は、ドライバチップへの振動あるいは衝撃を緩和させ該ドライバチップの動作不良を軽減させた液晶表示装置を提供することにある。

【0037】

本発明の他の参考目的は、液晶中に発生する気泡の不都合を解消させた液晶表示装置を提供することにある。

【0038】

本発明の他の参考目的は、セルギャップを確保するための支柱に集中する振動あるいは衝撃によって該支柱に間接的に当接する信号線等の破損を回避させた液晶表示装置を提供することにある。 20

【0039】

本発明の目的は、信頼性のあるアライメントマークを備える液晶表示装置を提供することにある。

【0040】

本発明の他の参考目的は、ドライバチップの実装領域の近傍にてたとえば電食等による破損のない配線層を形成することのできる液晶表示装置を提供することにある。

【0041】

【課題を解決するための手段】

本発明において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下のとおりである。 30

【0042】

(参考手段1)

参考発明は、対向配置された各基板に介在される液晶層をその層厚方向の電界によって光透過率を制御する液晶表示装置であって、

前記基板のうち一方の基板の液晶の面側に形成された支柱と、他方の基板の液晶の面側に形成された信号線と、この信号線をも被って形成された絶縁膜と、この絶縁膜の上面に形成され前記液晶層の光透過率の制御に寄与する一方の電極とを備え、

前記支柱はその頂面が前記信号線と対向して配置されるとともに、前記電極は前記信号線上まで延在しその延在部が前記支柱の頂面の一部と対向していることを特徴とするものである。 40

【0043】

(参考手段2)

参考発明による液晶表示装置は、液晶を介して対向配置される各基板のうち一方の基板の液晶側の面に、パターン化された複数の材料層が積層され、

前記各材料層のうち少なくとも信号線として形成された導電層と絶縁層として形成された有機材料層とを備えるとともに、

一方の基板の液晶の面側に搭載されて前記信号線の端子から信号を供給するドライバチップを備え、

前記ドライバチップは前記一方の基板との間に異方性導電膜が介在されて前記ドライバ

50

チップのバンプと前記端子との電気的接続が図れ正在ととともに、

前記ドライバチップの搭載領域は前記有機材料層の非形成領域となっていることを特徴とするものである。

【0044】

(参考手段3)

参考発明による液晶表示装置は、液晶を介して対向配置される各基板のうち一方の基板の液晶側の面に、パターン化された複数の材料層が積層され、

これら各材料層のうち少なくとも信号線として形成された導電層を備えるとともに、

一方の基板の液晶の面側に搭載されて前記信号線の端子から信号を供給するドライバチップを備え、

前記ドライバチップと前記一方の基板との間に衝撃吸収層が介在されていることを特徴とするものである。

【0045】

(参考手段4)

参考発明による液晶表示装置は、液晶を介して対向配置される一対の基板と、一方の基板に対する他方の基板の固定と前記液晶の封入を行うシール材と、前記一方の基板の少なくとも前記シール材に囲まれた領域に形成された有機材料層と、を備え、

前記有機材料層は該シール材の近傍においてその非形成領域が設けられていることを特徴とするものである。

【0046】

(参考手段5)

参考発明による液晶表示装置は、液晶を介して対向配置される各基板のうち一方の基板側に信号線およびこの信号線を被って無機材料層および有機材料層との順次積層体が形成され、

該一方の基板と他方の基板とのギャップを確保する支柱が前記一方の基板側に形成され正在ととともに、この支柱は前記積層体を介して前記信号線と重ねられるようにして形成されていることを特徴とするものである。

【0047】

(手段)

本発明による液晶表示装置は、液晶を介して対向配置される各基板のうち一方の基板であって該液晶を封入する領域以外の領域に無機材料層と有機材料層との順次積層体を介して該液晶を封入する領域内を走行する信号線と接続されるドライバチップが搭載されているとともに、

該ドライバチップの近傍の前記積層体の下層にアライメントマークが形成され、このアライメントを被う前記無機材料層は該アライメントマークと中心を一致させ該アライメントマークより大きな相似形をなして残存されてその近傍は除去されていることを特徴とするものである。

【0048】

(参考手段6)

参考発明による液晶表示装置は、液晶を介して対向配置される各基板のうち一方の基板であって該液晶を封入する領域以外の領域に有機材料層を介して該液晶を封入する領域内を走行する信号線と接続されるドライバチップが搭載され、前記有機材料層の下層側に配線層が前記ドライバチップの搭載領域を走行して形成されていることを特徴とするものである。

【0049】

【発明の実施の形態】

以下、本発明による液晶表示装置の実施例について図面を用いて説明をする。

【0050】

(参考実施例1)

《液晶表示装置の等価回路》

10

20

30

40

50

図2は、参考発明による液晶表示装置の一参考実施例を示す等価回路図である。同図は、回路図ではあるが、実際の幾何学的配置に対応して描かれている。

【0051】

この参考実施例では、広い視野角をもつものとして知られているいわゆる横電界方式を採用した液晶表示装置に参考発明を適用させている。

【0052】

まず、液晶表示パネルP N Lがあり、その液晶表示パネルP N Lは、液晶を介して互いに対向配置された透明基板S U B 1、S U B 2を外囲器としている。この場合、一方の透明基板S U B 1(図中下側の基板：マトリクス基板)は他方の透明基板S U B 2(図中上側の基板：カラーフィルタ基板)に対して若干大きく形成され、図中下側と右側の周辺端はほぼ面一に合わせて配置されている。10

【0053】

この結果、一方の透明基板S U B 1の図中左側の周辺および図中上側の周辺は他方の基透明板S U B 2に対して外方に延在されるようになっている。後に詳述するが、この部分はドライバチップであるゲート駆動I C 5およびドレイン駆動I C 6が搭載される領域となっている。

【0054】

各透明基板S U B 1、S U B 2の重畠する領域にはマトリクス状に配置された画素2が構成され、この画素2は、図中x方向に延在されy方向に並設されるゲート信号線G Lとy方向に延在されx方向に並設されるドレイン信号線D Lとで囲まれる領域に形成され、少なくとも、片側のゲート信号線G Lからの走査信号の供給によって駆動されるスイッチング素子T F Tと、このスイッチング素子T F Tを介して片側のドレイン信号線D Lから供給される映像信号が印加される画素電極P Xとが備えられている。20

【0055】

ここでは、上述したように、各画素2は、いわゆる横電界方式を採用したもので、後に詳述するように、上記のスイッチング素子T F Tおよび画素電極P Xの他に、基準電極C Tおよび保持容量C s t gが備えられるようになっている。

【0056】

そして、各ゲート信号線G Lはその一端(図中左側の端部)が透明基板S U B 1の周辺にまで延在され、透明基板S U B 1に搭載されたゲート駆動I C 5の出力端子に接続されるようになっている。30

【0057】

この場合、ゲート駆動I C 5は複数設けられているとともに、前記ゲート信号線G Lは互いに隣接するもの同士でグループ化され(図36参照)、これら各グループ化されたゲート信号線G Lが近接する各ゲート駆動I C 5にそれぞれ接続されるようになっている。

【0058】

また、同様に、各ドレイン信号線D Lはその一端(図中上側の端部)が透明基板S U B 1の周辺にまで延在され、透明基板S U B 1に搭載されたドレイン駆動回路(I C)6の出力端子に接続されるようになっている。

【0059】

この場合も、ドレイン駆動回路6は複数設けられているとともに、前記ドレイン信号線D Lは互いに隣接するもの同士でグループ化され、これら各グループ化されたドレイン信号線D Lが近接する各ドレイン駆動I C 6にそれぞれ接続されるようになっている。40

【0060】

一方、このようにゲート駆動I C 5およびドレイン駆動I C 6が搭載された液晶表示パネルP N Lに近接して配置されるプリント基板10(コントロール基板10)があり、このプリント基板10には電源回路11等の他に、前記ゲート駆動回路5およびドレイン駆動回路6に入力信号を供給するためのコントロール回路12が搭載されている。

【0061】

そして、このコントロール回路12からの信号はフレキシブル配線基板(ゲート回路基板50

15、ドレイン回路基板16A、ドレイン回路基板16B)を介してゲート駆動IC5およびドレイン駆動IC6に供給されるようになっている。

【0062】

すなわち、ゲート駆動IC5側には、これら各ゲート駆動IC5の入力側の端子にそれぞれ対向して接続される端子を備えるフレキシブル配線基板(ゲート回路基板15)が配置されている。

【0063】

そのゲート回路基板15は、その一部が前記コントロール基板10側に延在されて形成され、その延在部において、該コントロール基板10と接続部18を介して接続されている。

10

【0064】

コントロール基板10に搭載されたコントロール回路12からの出力信号は、該コントロール基板10上の配線層、前記接続部18、さらにはゲート回路基板15上の配線層を介して各ゲート駆動IC5に入力されるようになっている。

【0065】

また、ドレイン駆動IC6側には、これら各ドレイン駆動IC6の入力側の端子にそれぞれ対向して接続される端子を備えるドレイン回路基板16A、16Bが配置されている。

【0066】

このドレイン回路基板16A、16Bは、その一部が前記コントロール基板10側に延在されて形成され、その延在部において、該コントロール基板10と接続部19A、19Bを介して接続されている。

20

【0067】

コントロール基板10に搭載されたコントロール回路12からの出力信号は、該コントロール基板10上の配線層、前記接続部19A、19B、さらにはドレイン回路基板16A、16B上の配線層を介して各ドレイン駆動回路16A、16Bに入力されるようになっている。

【0068】

なお、ドレイン駆動回路6側のドレイン回路基板16A、16Bは、図示のように、2個に分割されて設けられている。液晶表示パネル1の大型化にともなって、たとえばドレイン回路基板の図中x方向への長さの増大による熱膨張による弊害を防止する等のためである。

30

【0069】

そして、コントロール基板10上のコントロール回路12からの出力は、ドレイン回路基板16Aの接続部19A、およびドレイン回路基板16Bの接続部19Bをそれぞれ介して、対応するドレイン駆動IC6に入力されている。

【0070】

さらに、コントロール基板10には、映像信号源22からケーブル23によってインターフェース基板24を介して映像信号が供給され、該コントロール基板10に搭載されたコントロール回路12に入力されるようになっている。

【0071】

なお、この図では、液晶表示パネルPNL、ゲート回路基板15、ドレイン回路基板16A、16B、およびコントロール基板10がほぼ同一平面内に位置づけられるように描かれているが、実際には該コントロール基板10はゲート回路基板15、ドレイン回路基板16A、16Bの部分で屈曲されて液晶表示パネル1に対してほぼ直角になるように位置づけられるようになっている。

40

【0072】

いわゆる額縁の面積を小さくさせる趣旨からである。ここで、額縁とは、液晶表示パネルPNLの外枠の輪郭と表示領域ARの輪郭の間の領域をいい、この領域を小さくすることによって、外枠に対して表示部の面積を大きくできる効果を得ることができる。

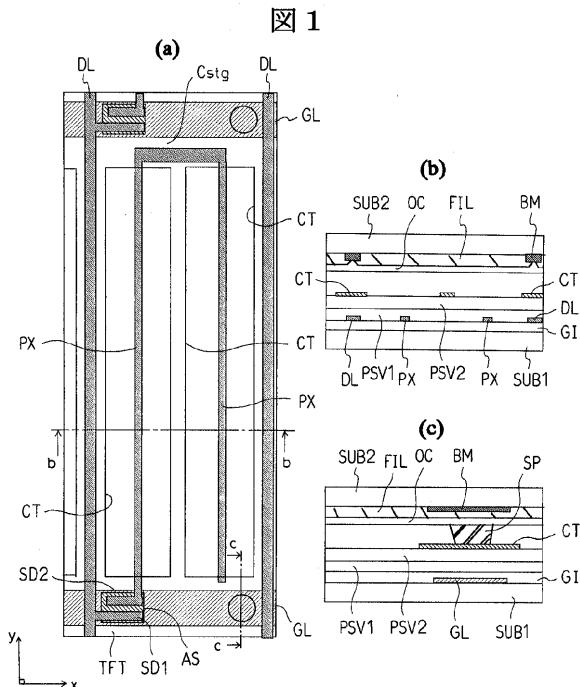

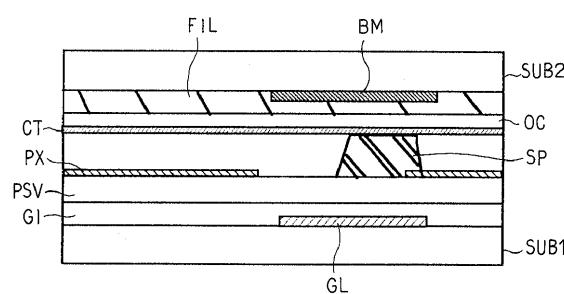

前記液晶表示パネル P N L は、上述したように、その液晶表示領域 A R がマトリクス状に配置された多数の画素 2 から構成され、このうちの一の画素の構成は図 1 ( a ) に示すようになっている。また、図 1 ( b ) は図 1 ( a ) の b - b 線における断面図を、図 1 ( c ) は図 1 ( a ) の c - c 線における断面図を示している。

【 0 0 7 3 】

同図において、透明基板 S U B 1 の主表面に、x 方向に延在し y 方向に並設されるゲート信号線 G L が形成されている。そして、これらゲート信号線 G L とドレイン信号線 D L とで囲まれる領域が画素領域として形成されることになる。

【 0 0 7 4 】

そして、このようにゲート信号線 G L が形成された透明基板 S U B 1 の主表面には、これらゲート信号線 G L をも被ってたとえばシリコン窒化膜からなる絶縁膜 G I が形成されている。この絶縁膜 G I は後述するドレイン信号線 D L に対してはゲート信号線 G L との絶縁を図るための層間絶縁膜として、後述の薄膜トランジスタ T F T の形成領域に対してはゲート絶縁膜として、後述の容量素子 C s t g に対しては誘電体膜として機能するようになっている。

【 0 0 7 5 】

この絶縁膜 G I の表面には、まず、その薄膜トランジスタ T F T の形成領域において半導体層 A S が形成されている。この半導体層 A S はたとえばアモルファス S i からなり、ゲート信号線 G L 上において後述するドレイン信号線 D L に近接された部分に重畠されて形成されている。これにより、ゲート信号線 G L の一部が薄膜トランジスタ T F T のゲート電極を兼ねた構成となっている。

【 0 0 7 6 】

そして、この絶縁膜 G I の表面にはその y 方向に延在しかつ x 方向に並設されるドレイン信号線 D L が形成されている。このドレイン信号線 D L は、薄膜トランジスタ T F T を構成する前記半導体層 A S の表面の一部にまで延在されて形成されたドレイン電極 S D 1 が一体となって備えられている。

【 0 0 7 7 】

さらに、画素領域における絶縁膜 G I の表面には前記ドレイン電極 S D 1 の形成とともに薄膜トランジスタ T F T のソース電極 S D 2 が形成され、このソース電極 S D 2 と一緒に形成された画素電極 P X が形成されている。

【 0 0 7 8 】

なお、前述した薄膜トランジスタ T F T のドレイン電極 S D 1 とソース電極 S D 2 との界面に相当する半導体層 A S の表面にはリン ( P ) がドープされて高濃度層となっており、これにより前記各電極におけるオーミックコンタクトを図っている。この場合、半導体層 A S の表面の全域には前記高濃度層が形成されており、前記各電極を形成した後に、該電極をマスクとして該電極形成領域以外の高濃度層をエッチングするようにして上記の構成とすることができます。

【 0 0 7 9 】

前記画素電極 P X は、その一端を前記薄膜トランジスタ T F T のソース電極 S D 2 とし、そのまま y 方向に延在され、該薄膜トランジスタ T F T を駆動させるゲート信号線 G L とは異なる他方のゲート信号線 G L に近接して x 方向に延在された後に、y 方向に延在するコ字形状となっている。

【 0 0 8 0 】

すなわち、画素電極 P X は図中 y 方向に延在されて画素領域中に 2 本形成され、これら各画素電極 P X はゲート信号線 G L の近傍部で互いに接続されたパターンとなっている。

【 0 0 8 1 】

前記ドレイン信号線 D L および画素電極 P X が形成された透明基板 S U B 1 面には該ドレイン信号線 D L および画素電極 P X をも被って保護膜 P S V が形成され、この参考実施例では、この保護膜 P S V はたとえばシリコン窒化膜等からなる無機材料層の保護膜 P S V 1 と樹脂層等からなる有機材料層の保護膜 P S V 2 の順次積層体から構成されている。

10

20

20

30

30

40

40

50

## 【0082】

保護膜PSVをこのように有機材料層を含む積層体としたのは保護膜PSV自体の誘電率を小さくさせることにある。

## 【0083】

そして、このような保護膜PSVの形成は、薄膜トランジスタTFTの液晶との直接の接触による特性劣化を回避することにある。

## 【0084】

この保護膜PSV(正確には有機材料層からなる保護膜PSV2)の上面には基準電極CTが形成されている。

## 【0085】

この基準電極CTは、この参考実施例では、たとえばITO(Indium-Tin-Oxide)膜からなる透光性の導電膜で形成され、上述した2本の画素電極PXの両脇に位置づけられるようにして3本形成されている。

10

## 【0086】

すなわち、各基準電極CTのうちの1本は画素領域の中央部を図中y方向に走行して形成され、残りの2本はそれぞれドレイン信号線DL上をそれに沿って形成されている。

## 【0087】

基準電極CTをドレイン信号線DL上に形成することによって、ドレイン信号線DLからの電界を該基準電極CT側へ終端させることができ、前記画素電極CT側へノイズとしての電界を及ぼすことを防止する効果を奏する。

20

## 【0088】

このため、この参考実施例では該基準電極CTはドレイン信号線DL上を充分被うようにして形成され、その幅はドレイン信号線DLのそれよりも大きく形成されている。

## 【0089】

また、基準電極CTはこの参考実施例では透光性の導電膜で形成しているが、これに限定する必要はなく金属等の不透明な導電膜で形成してもよく、この場合において、該基準電極CTをドレイン信号線DL上に形成することは画素領域の開口率を向上させる効果も奏する。

## 【0090】

さらに、この基準電極CTは、ゲート信号線GLをも充分に被って形成された透光性の導電膜の一部として形成されている。

30

## 【0091】

このように構成することによって、透光性の導電膜は隣接する各画素領域において一体のものとして形成することができ、この透光性の導電膜を介してその一部である基準電極CTに基準電圧信号を供給させることができるようになる。

## 【0092】

このことは、画素領域内を走行する基準電圧信号線を特別に形成する必要がなく画素領域の開口率の向上を図ることができる。

## 【0093】

しかし、他の参考実施例として、基準電圧信号線を形成し、それが基準電極CTと層を異にして形成した場合スルホールを介してこの基準電圧信号線と基準電極CTとの接続を図るようにしてもよい。

40

## 【0094】

また、画素電極PXと基準電極CTとの間に電界が発生していない場合に液晶の光透過率を最小にする、いわゆるノーマリブラックモードとして構成することにより、前記透光性の導電膜は遮光膜として機能させることができる。

## 【0095】

ドレイン信号線DLあるいはゲート信号線GLの近傍部はそれら信号線からの電界によって液晶が駆動して光漏れが発生し易くなることから、前記透光性の導電膜を遮光膜として機能させることは表示の信頼性を向上させることができる。

50

## 【0096】

なお、ゲート信号線 G L を充分に被って形成される透光性の導電膜は画素電極 P X の一部（図中 y 方向に延在される 2 本の画素電極 P X の接続部）も被って形成され、それらの重なり部において容量素子 C s t g が形成されている。

## 【0097】

この容量素子 C s t g は、たとえば薄膜トランジスタ T F T がオフした際に画素電極 P X に映像信号を長く蓄積させる効果等を有するようになっている。

## 【0098】

そして、このように基準電極 C T が形成された透明基板 S U B 1 の表面には該基準電極 C T 等も被って配向膜（図示せず）が形成されている。この配向膜は液晶と直接に接触する膜で該液晶の初期配向方向を決定するようになっている。10

## 【0099】

なお、この参考実施例では、画素電極 P X はドレイン信号線 D L の材料と同一の材料で形成するようにしたが、これに限定されず、透光性の導電膜で形成するようにしてもよい。このようにすることによって画素領域の開口率が向上するからである。

## 【0100】

また、このように構成された透明基板 S U B 1 は液晶を介して透明基板 S U B 2 と対向配置され、この透明基板 S U B 2 の液晶側の面には、各画素領域に相当する部分に開口部を有するブラックマトリクス B M が形成されている。

## 【0101】

このブラックマトリクス B M は、上述したように基準電極 C T を一部として形成する透光性の導電膜に遮光機能をもたせるようにした場合（いわゆるノーマリブラックモードの構成とする）、その幅を従来よりも狭くして画素領域の開口率を向上させることができる。透明基板 S U B 1 と透明基板 S U B 2 の合わせずれを考慮する必要が比較的少なくなるからである。20

## 【0102】

さらに、このブラックマトリクス B M の画素領域に相当する部分に形成された開口部を被ってカラーフィルタ F I L が形成されている。このカラーフィルタ F I L は x 方向に隣接する画素領域におけるそれとは異なった色（R、G、B）を備えるとともに、それぞれブラックマトリクス B M 上において境界部を有するようになっている。30

## 【0103】

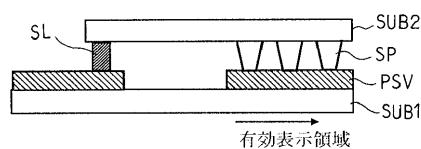

また、このようにブラックマトリクス B M 、およびカラーフィルタ F I L が形成された面には樹脂膜等からなる平坦化膜 O C が形成され、この平坦化膜 O C 上の一部には支柱 S P が形成されている。

## 【0104】

この支柱 S P は、液晶表示領域 A R において透明基板 S U B 1 と透明基板 S U B 2 とのギャップを確保するためのもので、透明基板 2 側に形成したたとえば樹脂材料層をフォトリソグラフィ技術による選択エッチングをすることによって形成される。

## 【0105】

そして、この支柱 S P は、その頂面が前記ゲート信号線 G L および基準電極 C T を一部とする透光性の導電膜に対向するようにして配置されている。40

## 【0106】

上述したように、該透光性の導電膜はゲート信号線 G L を充分被うようにして、換言すれば、該透光性の導電膜の幅はゲート信号線 G L のそれよりも充分大きく形成されていることから、ゲート信号線 G L と重畠されて形成される支柱の周辺は前記透光性の導電膜が充分な径を有して取り巻くようになる。

## 【0107】

このことは、支柱 S P の周囲の液晶が配向乱れによるドメインによって該支柱 S P の周囲に生じる光漏れを防止することができる。基準電極 C T を一部とする透光性の導電膜は遮光膜として機能できるからである。50

## 【0108】

この場合、ゲート信号線 G L を被う透光性の導電膜は該ゲート信号線 G L からの電界をシールドする機能をも有するが、この電界が該透光性の導電膜から漏れる（該透光性の導電膜の周辺で迂回して周り込む）場合には支柱 S P の周囲におけるドメインによる影響は広がるようになる。

## 【0109】

ここで、支柱 S P の周囲におけるドメインによる影響を抑止する方法を示す。

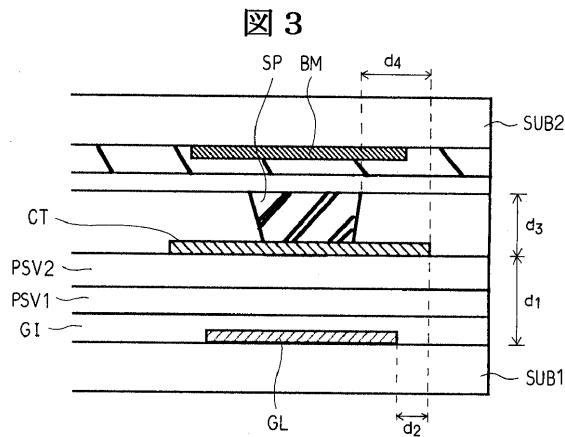

## 【0110】

図 3 に示すように、ゲート信号線 G L と対向電極 C T を一部にもつ透光性の導電層の間の絶縁膜の厚さを  $d_1$ 、液晶の層厚を  $d_3$ 、とした場合に、該ゲート信号線 G L からの電界が支柱 S P の周辺に影響を与えないようにするためには、対向電極 C T を一部にもつ透光性の導電層のゲート信号線 G L に対するはみ出し量を  $d_2$  を、次式（1）

10

## 【0111】

## 【数1】

$$d_2 > d_1 \times d_3 \quad \dots \dots \dots (1)$$

に示すように設定すればよいことが確かめられた。さらに  $d_2$  の値として  $4.7 \mu m$  を設定すれば、殆どの構成においてドメインの抑止を実現できる。

## 【0112】

このため、前記透光性の導電膜の幅をゲート信号線 G L の延在方向の各辺からそれぞれ  $4.7 \mu m$  以上はみ出すように設定することにより、支柱 S P の周辺に生じるドメインをほぼ完全に遮光できるようになる。

20

## 【0113】

なお、この参考実施例では、支柱 S P はゲート信号線 G L と重畳する個所に設けたものであるが、これに限定されることはなく、ドレイン信号線 D L と重畳する個所に設けるようにもよい。

## 【0114】

この場合においても、基準電極 C T である透光性の導電膜の幅をドレイン信号線 D L の延在方向の各辺からそれぞれ  $4.7 \mu m$  以上はみ出すように設定することにより、該支柱 S P の周辺に生じるドメインを充分に遮光できるようになる。

30

## 【0115】

また、本参考実施例の効果は、支柱 S P が透明基板 S U B 1 側に配置させた場合においても同様の効果を有する。

## 【0116】

また、上式（1）において、支柱 S P に対して基準電極 C T を一部とする透光性の導電層のはみ出し量を  $d_4$  とした場合、 $d_4 > d_2$  となるようにすることができる。

## 【0117】

また、上述した参考実施例では、支柱 S P は透明基板 S U B 2 側に設けたものであるが、対応する個所にて透明基板 S U B 1 側に設けるようにしてもよい。このようにした場合でも同様の効果を奏することはいうまでもない。この場合、支柱 S P の底面、すなわち支柱 S P の透明基板 S U B 1 側の固着面の近傍が、上述した参考実施例の支柱 S P の頂面の近傍に示した構成と同様になっていればよい。

40

## (参考実施例 2)

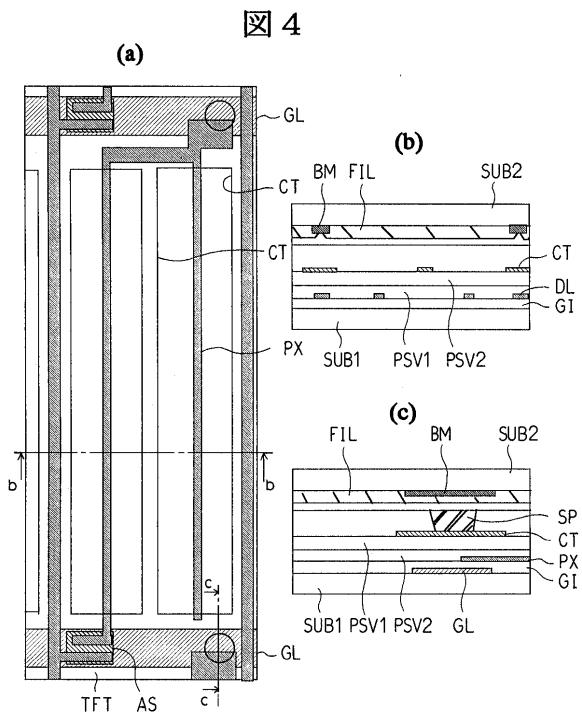

図 4 は参考発明による液晶表示装置の他の参考実施例を示す構成図で、図 1 に対応した図となっている。

## 【0118】

図 1 と異なる構成は画素電極 P X にあり、この画素電極 P X はその一部がゲート信号線 G L と重畳されるように延在され、また、その重畳部において比較的面積が広く形成されている。

## 【0119】

これにより、画素電極 P X は対向電極 C T との間に容量素子 C s t g を構成するとともに

50

、ゲート信号線 G L との間に容量素子 C a d d をも構成するようになる。

【 0 1 2 0 】

そして、この容量素子 C a d d は容量素子 C s t g の形成領域内に形成されることから占有面積を大きくすることなく容量を大きくすることができる。

【 0 1 2 1 】

なお、この場合において、容量素子 C a d d を形成する画素電極 P X からの電界が、基準電極 C T を一部とする透光性の導電膜から漏れて支柱 S P の周辺の液晶に配向乱れを生じさせないために、該透光性の導電膜の幅を考慮する必要が生じる。

【 0 1 2 2 】

すなわち、支柱 S P の配置個所にゲート信号線 G L と重畳する画素電極 P X の延在部が存在する場合、前記ゲート信号線 G L と前記延在部の外側の各辺からそれぞれ 4 . 7  $\mu$  m 以上はみ出すように、透光性の導電膜の幅を設定することにより、支柱 S P の周辺に生じるドメインをほぼ完全に遮光できるようになる。

【 0 1 2 3 】

また、本参考実施例の効果は、支柱 S P が透明基板 S U B 1 側に配置させた場合であっても同様である。

【 0 1 2 4 】

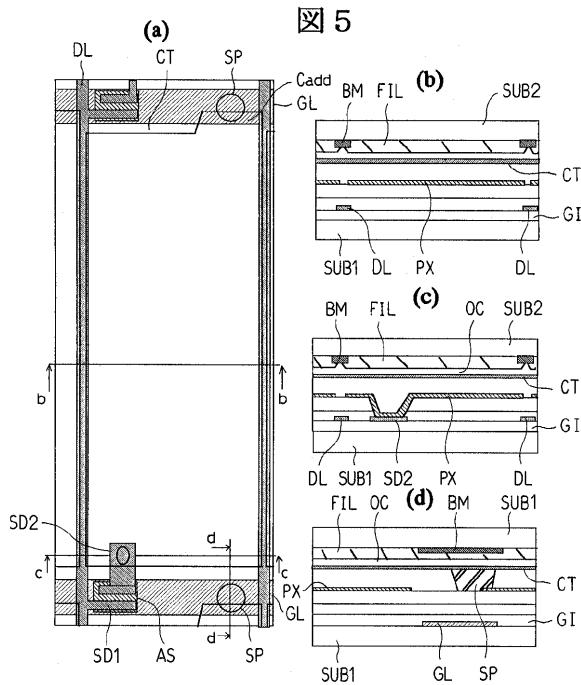

( 参考実施例 3 )

図 5 ( a ) は、いわゆる縦電界方式と称される画素を有する液晶表示装置の構成について示したものである。また、図 5 ( b ) は図 5 ( a ) の b - b 線における断面図、図 5 ( c ) は c - c 線における断面図、図 5 ( d ) は d - d 線における断面図を示している。

【 0 1 2 5 】

参考実施例 1 に示した横電界方式と異なる構成は、いずれも透光性の導電膜からなる画素電極 P X と対向電極 C T を備え、該画素電極 P X は透明基板 S U B 1 の液晶側の面の各画素領域に平面的に形成され、対向電極は透明基板 S U B 2 の液晶側の面に各画素領域に共通に形成されていることがある。

【 0 1 2 6 】

透明基板 S U B 1 の液晶側の面に、ゲート信号線 G L 、絶縁膜 G I 、薄膜トランジスタ T F T およびドレイン信号線 D L が順次形成されているのは参考実施例 1 の場合と同様となっている。

【 0 1 2 7 】

参考実施例 1 と異なる構成は、薄膜トランジスタ T F T を被って形成される保護膜 P S V に該薄膜トランジスタ T F T のソース電極 ( ドレイン信号線の形成の際に同時に形成される ) の一部を露出させるためのコンタクト孔が形成され、該保護膜 P S V の上面に形成される画素電極 P X はこのコンタクト孔を通して前記ソース電極 S D 2 と接続されている。

【 0 1 2 8 】

なお、ここでも該保護膜 P S V は無機材料層からなる保護膜 P S V 1 と有機材料層からなる保護膜 P S V 2 の順次積層体から構成されて、保護膜 P S V 自体の誘電率の低減を図っている。

【 0 1 2 9 】

この画素電極 P X は、その一部が前記薄膜トランジスタ T F T を駆動させるゲート信号線 G L とは異なる他方のゲート信号線 G L に重畳されるようにして延在し、該重畳部に容量素子 C a d d を形成している。

【 0 1 3 0 】

また、透明基板 S U B 2 の液晶側の面に形成された平坦化膜 O C の表面には各画素領域に共通に対向電極 C T が形成されている。

【 0 1 3 1 】

そして、この対向電極 C T が形成された透明基板 S U B 2 の面には、前記ゲート信号線 G L には完全に、前記画素電極 P X の延在部にはその一部が対向するようにして支柱 S P が

10

20

30

40

50

設けられている。

【0132】

すなわち、ゲート信号線 G L に対向するようにして支柱 S P を設けるにしても、容量素子 C a d d の一方の電極を構成する画素電極 P X の延在部と一部対向するようにして、前記支柱 S P の配置個所を選定している。

【0133】

このようにした場合、支柱 S P の周辺の液晶の配向乱れによる光漏れの領域を縮小させる効果を得ることができる。

【0134】

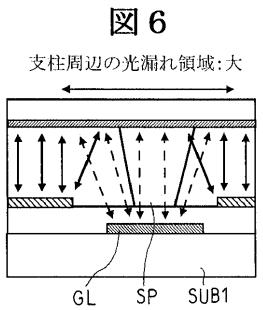

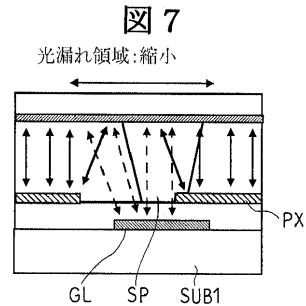

図 6 は容量素子 C a d d の一方の電極を構成する画素電極 P X の延在部が形成されていない部分に支柱 S P を形成した図、図 7 は容量素子 C a d d の一方の電極を構成する画素電極 P X の延在部が形成されている部分に支柱 S P を形成した図である。 10

【0135】

図 7 では、支柱 S P の周辺の画素電極 P X の延在部付近には電界の乱れが生ぜず、このため、光漏れの領域が縮小されるようになる。

【0136】

また、支柱 S P が透明基板 S U B 1 側に配置させた場合であっても同様である。

【0137】

(参考実施例 4)

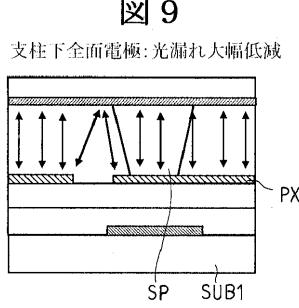

この参考実施例は参考実施例 3 のさらなる改良を施したもので、図 9 に示すように、支柱 S P はゲート信号線 G L はもちろんのこと、容量素子 C a d d の一方の電極を構成する画素電極 P X の延在部にも完全に対向するように構成している。 20

【0138】

換言すれば、該画素電極 P X の延在部は支柱 S P の頂面の当接領域の全てに及んで延在されて形成されている。

【0139】

このように構成した理由は、画素電極 P X は無機材料層と有機材料層との順次積層体からなる保護膜 P S V 上に形成されていることによる。

【0140】

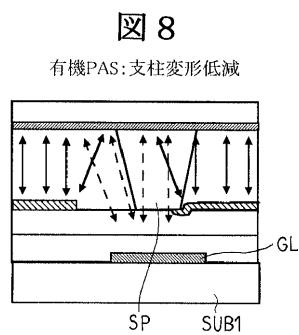

上述した参考実施例で示したように、支柱 S P を画素電極 P X の延在部と一部対向するようにした場合、図 8 に示すように無機材料層が有する弾力性のために支柱 S P の頂面のエッジ部において該画素電極 P X の延在部とともに変形が生じやすくなり、これによる支障が発生するからである。 30

【0141】

この場合においても、該支柱 S P は上記対応する個所にて透明基板 S U B 1 側に設けても同様の効果を有することはいうまでもない。

【0142】

(参考実施例 5)

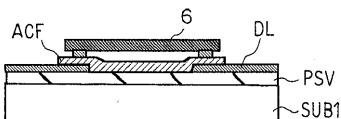

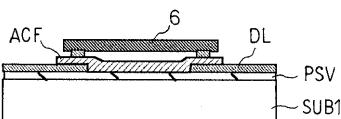

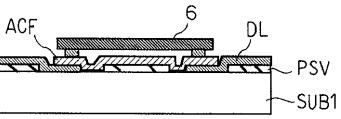

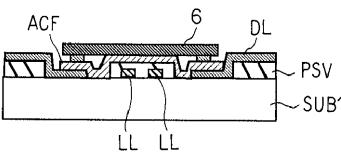

図 10 は、たとえばドレン駆動 I C 6 の実装部分における断面を示し、図 2 の X - X 線における断面図を示している。 40

【0143】

透明基板 S U B 1 の表面には液晶表示領域 A R の領域内で形成した保護膜 P S V が延在されて形成されている。この保護膜 P S V は上述したように無機材料層の保護膜 P S V 1 と有機材料層の保護膜 P S V 2 との順次積層体から構成されている。

【0144】

そして、この保護膜 P S V の上面にはドレン信号線 D L が形成され、その端部はドレン駆動 I C 6 のバンプ（出力バンプ）の個所にまで延在されて端子部を構成している。

【0145】

なお、この参考実施例の場合、前記保護膜 P S V は該ドレン駆動 I C 6 の実装領域およびその近傍部に相当する部分に開口が形成され、このため前記ドレン信号線 D L は該 50

保護膜 P S V 上から該保護膜 P S V の非形成領域に及ぶようにして前記端子に到っている。

【 0 1 4 6 】

なお、ドレイン信号線 D L は液晶表示領域 A R においては前記保護膜 P S V の下層に位置づけられているが、ドレイン駆動 I C 6 の近傍においては該保護膜 P S V に形成されたスルホール(図示せず)を通して保護膜 P S V の上層に位置づけられている。

【 0 1 4 7 】

この理由は、該スルホールから端子までの間のドレイン信号線 D L をたとえば I T O 等の透光性の導電層で形成し、電食の発生を回避するためである。

【 0 1 4 8 】

また、ドレイン駆動 I C 6 の入力バンプ側においても同様の構成となっており、ドレイン回路基板 1 6 B に接続される配線層が保護膜 P S V 上から該保護膜 P S V の非形成領域に及ぶようにして前記入力バンプに接続される端子に到っている。透明基板 S U B 1 とドレイン駆動 I C 6 の間には異方性導電膜 A C F が介在されている。

【 0 1 4 9 】

この異方性導電膜 A C F は導電性粒子が混在されたシート状の樹脂膜からなり、少なくともこの異方性導電膜 A C F を加熱してドレイン駆動 I C 6 を加圧することにより、透明基板 S U B 1 に対するドレイン駆動 I C 6 の固着がなされ、かつドレイン駆動 I C 6 の各バンプとそれに対応する端子との電気的接続がなされている。

【 0 1 5 0 】

このようなドレイン駆動 I C 6 の実装構造は、該ドレイン駆動 I C 6 の実装後において、該ドレイン駆動 I C 6 を取替える必要が生じた場合にその周辺を破損させることなく、信頼性あるリペアができる効果を奏する。

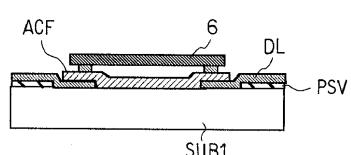

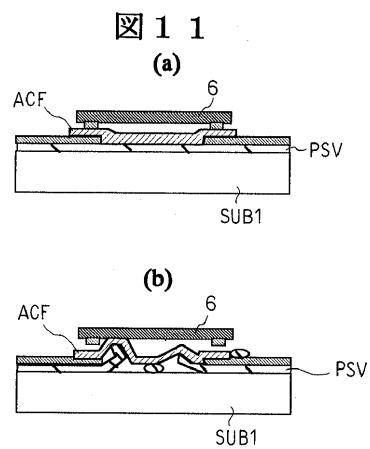

【 0 1 5 1 】

すなわち、たとえば図 1 1 ( a ) に示すように、保護膜 P S V がドレイン駆動 I C 6 の実装領域にまで形成されている場合、異方性導電膜 A C F を溶剤で溶かし、新たな異方性導電膜 A C F とドレイン駆動 I C 6 を搭載する際に、図 1 1 ( b ) に示すように、保護膜 P S V の上層に形成されている有機材料層も不均一に剥がれ、あるいは残渣として残ってしまう不都合が生じる。

【 0 1 5 2 】

のことから、上述した参考実施例では、保護膜 P S V は無機材料層と有機材料層の順次積層体で構成したが、これに限定されることはなく有機材料層のみであっても同様の効果が得られるることはいうまでもない。

【 0 1 5 3 】

また、ドレイン駆動 I C 6 の実装構造に限定されることはなく、ゲート駆動 I C 5 の実装構造にも適用できることはもちろんである。また、以下の参考実施例においても同様に適用できる。

【 0 1 5 4 】

( 参考実施例 6 )

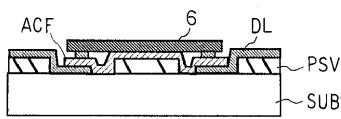

図 1 2 は、ドレイン駆動 I C 6 の実装構造の他の参考実施例を示す断面図である。

【 0 1 5 5 】

同図は、参考実施例 5 と異なりドレイン駆動 I C 6 の実装領域にも無機材料層と有機材料層との順次積層体が形成されているが、該有機材料層の層厚が 6 0 0 n m 以上、望ましくは 9 0 0 n m 以上に設定されていることがある。

【 0 1 5 6 】

このような厚さを有する有機材料層はその膜強度が強化され、下地層に対して剥がれ難くなり、リペア時の再生率を向上させることができる。

【 0 1 5 7 】

( 参考実施例 7 )

図 1 3 は、参考実施例 6 と比較して、有機材料層の層厚に制限がなく、ドレイン駆動 I

10

20

30

40

50

C 6 の実装領域にも無機材料層と有機材料層との順次積層体である保護膜 P S V が形成されていることがある。

【 0 1 5 8 】

このように構成されたドレン駆動 I C 6 の実装構造は、前記有機材料層が衝撃緩衝材の機能を有するようになり、外部からの振動、衝撃、あるいは押圧によるドレン駆動 I C 6 への障害を緩和できるようになる。

【 0 1 5 9 】

( 参考実施例 8 )

図 1 4 は、無機材料層と有機材料層との順次積層体はドレン駆動 I C 6 の実装領域にまで及んで形成されているが、ドレン駆動 I C 6 のバンプ（入力バンプ、出力バンプ）およびその近傍に対向する部分には開口が形成されていることがある。 10

【 0 1 6 0 】

これにより、リペア時の再生率を向上させることができ、また押圧によるドレン駆動 I C 6 への障害を緩和できるようになる。

【 0 1 6 1 】

( 参考実施例 9 )

図 1 5 は、上記参考実施例 8のさらなる改良を示した図で、無機材料層と有機材料層との順次積層体からなる保護膜 P S V の厚さを大きくしたことを除き、参考実施例 8の構成と同様となっている。 20

【 0 1 6 2 】

すなわち、保護膜の厚さをドレン駆動 I C 6 のバンプの高さと該バンプと電気的に接続される端子の層厚の合計値とほぼ等しく設定している。

【 0 1 6 3 】

これにより、ドレン駆動 I C 6 は、その入力バンプと出力バンプの間の領域にて、透明基板 S U B 1 との間の空間をほぼ埋めるようにして保護膜 P S V および異方性導電膜 A C F が介在されることから、押圧によるドレン駆動 I C 6 への障害を緩和できるようになる。 20

【 0 1 6 4 】

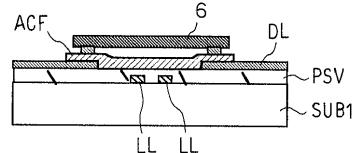

( 参考実施例 10 )

図 1 6 は、参考実施例 5に示した図 1 0 に対応する図で、保護膜 P S V の下層においてドレン駆動 I C 6 の入力バンプと出力バンプの間の領域に配線層 L L が走行されて構成されている。 30

【 0 1 6 5 】

このように構成した場合、ドレン駆動 I C 6 の近傍のスペースを有效地に利用できることになり、また、いわゆる額縁と称される領域（透明基板 S U B 1 の外輪郭と表示部 A R の外輪郭の間の領域）を小さくすることができる。

【 0 1 6 6 】

なお、前記配線層 L L としては、たとえば共通配線、信号ライン、あるいは検査用の引出配線等のいずれか、またはこれらのうち少なくとも 2 種の配線であってもよい。

【 0 1 6 7 】

また、保護膜 P S V 1 の下層に位置づけられる各配線層 L L は該保護膜 P S V 1 によってその損傷を回避できるようになる。 40

【 0 1 6 8 】

この保護膜 P S V は無機材料層および有機材料層の順次積層体から構成され、たとえ無機材料層にクラックが発生しても、このクラックは有機材料層によって閉塞され、たとえば電食等によって前記配線層 L L が腐食するのを回避することができる。

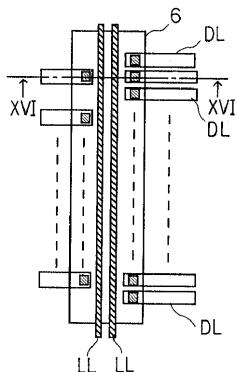

【 0 1 6 9 】

なお、前記配線層 L L は、図 1 7 に示す平面図に示すように、ドレン駆動 I C の入力バンプ群と出力バンプ群との間に走行され、場合によっては並設される他のドレン駆動 I C 6 にまで及んで形成されている。ちなみに図 1 6 は平面図である図 1 7 のXVI - XVI 線に 50

おける断面図となっている。

【0170】

(参考実施例11)

図18は、図15に対応する図で、保護膜PSVの下層においてドレイン駆動IC6の入力バンプと出力バンプの間の領域に配線層LLが走行して構成されている。

【0171】

そして、保護膜PSVの厚さをドレイン駆動IC6のバンプの高さと該バンプと電気的に接続される端子の層厚の合計値とほぼ等しく設定し、この保護膜PSVの該ドレイン駆動IC6のバンプ(入力バンプ、出力バンプ)およびその近傍に対向する部分には開口が形成されている。

10

【0172】

このように構成することによって、参考実施例12および参考実施例11に示した各効果を兼ね備えることになる。

【0173】

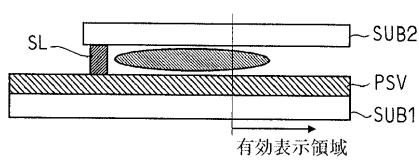

(参考実施例12)

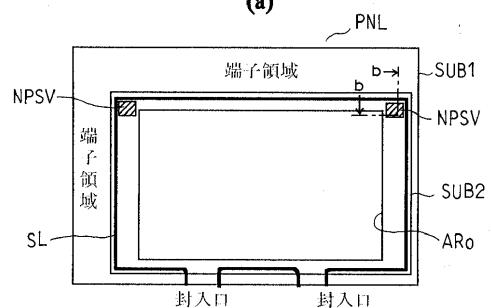

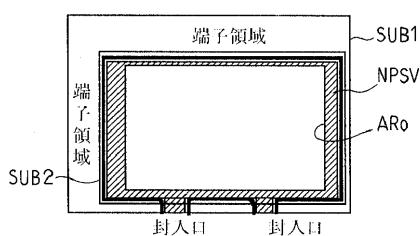

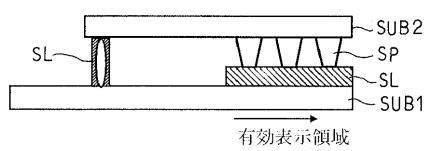

図19(a)は、液晶表示パネルPNLの概略構成を示す平面図で、そのb-b線における断面図を図19(b)に示している。

【0174】

同図は、透明基板SUB1に対する透明基板SUB2の固定はシール材SLによってなされ、このシール材SLは液晶を封入する機能も兼ね備えている。

20

【0175】

シール材SLは透明基板SUB2の周辺に沿って形成され、そのパターンは矩形状となっている。

【0176】

そして、このシール材SLの各辺のうち透明基板SUB1と透明基板SUB2の端面がほぼ面一となっている部分の辺に液晶を封入するための液晶封入口(この参考実施例では2個設けられている)が形成され、この封入口は液晶の封入後において図示しない封止剤によって封止されるようになっている。

【0177】

そして、シール材SLの内側であって、前記液晶封入口が形成された辺と対向する辺とこの辺に交差する辺とで形成される角部に、透明基板SUB1の液晶の側面に形成されている保護膜PSVのうち上層の有機材料層からなる保護膜PSV2の非形成領域NPSVが設けられている。なお、場合によっては、前記非形成領域NPSVから露出する無機材料からなる保護膜PSV1も除去するようにしてもよい。

30

【0178】

また、この保護膜PSV2の非形成領域NPSVはシール材SLの内側に形成される有効表示領域AR<sub>0</sub>(各画素領域の集合体の外輪郭内の領域、またはブラックマトリクスBMの開口の集合体の外輪郭内の領域)の外側に形成されている。

【0179】

保護膜PSV2の前記非形成領域NPSVを有効表示領域AR<sub>0</sub>の外側に形成した理由は、この部分はブラックマトリクスBM等によって被われ該非形成領域NPSVを観察者側から目視できないようにするためである。

40

【0180】

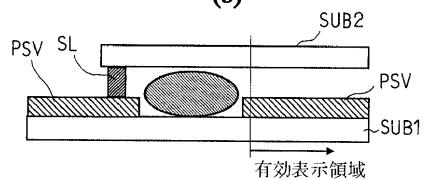

このような保護膜PSV2の非形成領域NPSVは、液晶中に含まれる気泡を集中的に集めさせ、しかもその位置から移動し難くしている。換言すれば、保護膜PSV2の非形成領域NPSVは該気泡の捕獲領域としての機能を有する。

【0181】

ここで、前記気泡の発生について詳述する。まず、液晶表示パネルPNLへの液晶封入の過程は、1)液晶表示パネルPNLと液晶が充満された液晶皿を真空容器の中に配置する、2)真空容器を減圧する、これにより液晶表示パネルPNL内も減圧される、3)液晶

50

表示パネル P N L の液晶封入口を液晶皿の液晶に当接させる、4) 真空容器に大気あるいは不活性ガスを導入する、ことによってなされる。

【0182】

液晶表示パネル P N L の内外に圧力差が生じるため、液晶は液晶封入口から液晶表示パネル P N L 内に除々に充填され、最終的に封入口より遠い辺全体にまで充填される。

【0183】

この液晶封入過程で液晶が上昇するとともに、液晶表示パネル内での残留ガスあるいは発生ガスの圧力も上昇し、たとえば図 20 (a) に示すように、該ガスが気泡として残存し、この気泡は図 20 (a) の b - b 線における断面図である図 20 (b) に示すように有効表示領域 A R<sub>0</sub> の部分にまで及んで体積が大きくなり、これが目視されるようになる。

10

【0184】

この気泡は、保護膜 P S V を無機材料層と有機材料層の順次積層体で形成した場合に、該有機材料層の存在が原因となって多く発生するようになることから、上記構成は極めて効果的となる。

【0185】

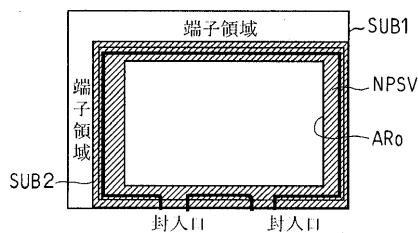

なお、この参考実施例の場合において、保護膜 P S V の有機材料層の非形成領域 N P S V はシール材 S L の全周にわたって形成されていてもよく、この場合に、図 21 に示すように、該非形成領域はシール材 S L の形成領域およびシール材の外側にまで及んで形成されていてもよい。

20

【0186】

このようにした場合、シール材 S L の透明基板 S U B 1 の液晶の側の面との接着性が強固になるという効果を奏する。

【0187】

(参考実施例 13)

上述した参考実施例 12では、気泡の捕獲領域を透明基板 S U B 1 側に形成したものである。しかし、透明基板 S U B 2 側に設けても同様の効果を得ることができる。

【0188】

透明基板 S U B 2 の液晶の面側には、ブラックマトリクス B M、カラーフィルタ F I L、平坦化膜 O C 等が形成され、少なくともこれらのうちの一つに、図 19 (a) に示した非形成領域 N P S V と対向する位置に非形成領域を形成すればよい。

30

【0189】

(参考実施例 14)

また、参考実施例 12あるいは参考実施例 13に示した構成は、特に、図 1 に示した構成に適用することによって効果的となる。

【0190】

すなわち、図 1 に示す構成は、無機材料層および有機材料層の順次積層体からなる保護膜 P S V の上面に対向電極 C T が形成されたものであり、前記有機材料層中から液晶への放出ガスを該対向電極 C T が障壁となって抑制できるからである。

【0191】

すなわち、対向電極 C T の形成領域以外の領域において露出された前記有機材料層から放出されるガスによる液晶中の比較的少量の気泡が確実に捕獲される構成となっているからである。

40

【0192】

また、該対向電極 C T は複数の帯状の電極からなり、この電極によって表面の段差による起伏が多く存在するようになる。このため、有機材料層からの放出ガスが、液晶封入過程において、最大でも数  $\mu m$  程度の微小な気泡として有効表示領域内に分散することで、大きな気泡の発生を抑制することができる。

【0193】

実験によると、この参考実施例の場合、該対向電極 C T の本数を 1 画素領域当たり 5 以上とする、あるいは各対向電極 C T の間の間隔を 13  $\mu m$  以下とすることによって、観察

50

に支障のない程度に気泡の抑制を達成できた。

【0194】

なお、この参考実施例では、無機材料層および有機材料層の順次積層体からなる保護膜P S Vの上面に対向電極C Tが形成されたものであるが、対向電極C Tに限らず画素電極P Xであってもよく、また、対向電極C Tおよび画素電極P Xが形成されたものであってもよいことはもちろんである。

【0195】

なお、上記電極によって気泡の発生を充分に抑制できる構成とした場合、参考実施例12あるいは参考実施例13に示した有機材料層の非形成領域を特に設ける必要がないのはいうまでもない。

10

【0196】

(参考実施例15)

また、参考実施例12等の場合、画素電極P Xおよび対向電極C Tの延在方向はシール材S Lのうち液晶封入口が形成された辺と直交するようにして形成されたものである。

【0197】

しかし、画素電極P Xおよび対向電極C Tの延在方向をシール材S Lのうち液晶封入口が形成された辺とほぼ平行となるようにして形成することによって、気泡のさらなる低減が達成できることが確かめられている。

【0198】

(参考実施例16)

20

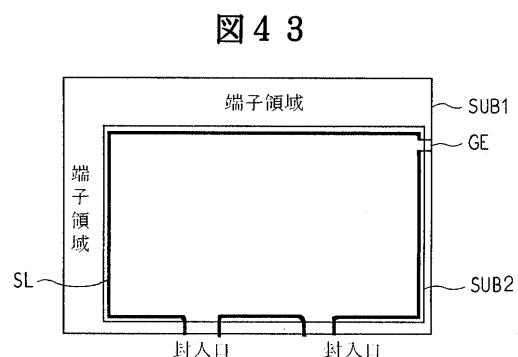

図43は液晶中に含まれる気泡の除去に効果的な他の参考実施例を示す平面図である。

【0199】

同図に示すように、シール材S Lには液晶封入口の他に気泡排出口G Eをも形成されている。

【0200】

液晶を封入する際に、該液晶中に含まれる気泡をこの気泡排出口G Eによって排出しようとするものである。

【0201】

図20に示したように、気泡の発生領域が、液晶封入口が形成されたシール材の辺と対向する辺と他の交差する辺との角部であることから、この角部の近傍に該気泡排出口G Eを設けることが効果的となる。

30

【0202】

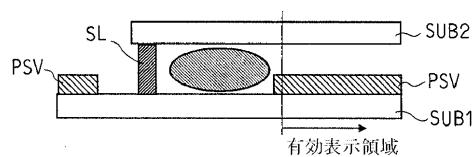

(参考実施例17)

この参考実施例では、図22(a)に示すように、シール材S Lの一部に形成された液晶封入口内(液晶の導入部分)において、有機材料層の非形成領域N P S Vを設けたことがある。

【0203】

このように構成することによって、図22(a)のb-b線における断面図に示すように、液晶封入口の径(断面積)が大きくなる。このことは、液晶の封入の際にその封入速度が大きくなり、スループットの向上を図ることができる。

40

【0204】

(参考実施例18)

また、図23は参考実施例17をさらに改良したもので、有機材料層の非形成領域N P S Vを液晶封入口内に限らず、シール材S Lの内部であってその周辺に及んで非形成領域N P S Vを設けている。

【0205】

(参考実施例19)

さらに、図24は参考実施例18をさらに改良したもので、シール材S Lの形成領域を含むようにして該シール材S Lの周辺にも及んで、有機材料層の非形成領域N P S Vを設けている。

50

## 【0206】

このように構成することによって、液晶の封入速度が大きくなり、またシール材 S L の透明基板 S U B 1 側への接着強度を向上させることができる。

## 【0207】

## (参考実施例 20)

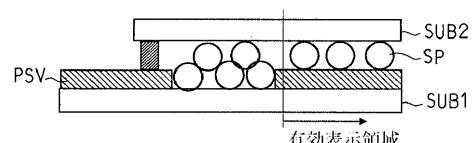

図 25 は、上述したように液晶中の気泡による不都合を解消するために保護膜 P S V 中にその非形成領域 N P S V を形成した場合に、透明基板 S U B 1 と透明基板 S U B 2 とのギャップを確保するスペーサとして一方の透明基板側に支柱 S P を設けたことにある。

## 【0208】

たとえば該スペーサとしてビーズを用いた場合、該ビーズはその動きを規制されていないために、図 26 に示すように、保護膜 P S V の非形成領域 N P S V に集中してしまう畏れが生じ、これにより、透明基板 S U B 1 と透明基板 S U B 2 とのギャップを確保するスペーサの量が減少してしまう不都合が生じてしまうからである。さらに、この場合、保護膜 P S V の非形成領域 N P S V の実効容量が減少するため、気泡による不都合の解消効果が減じてしまうからである。

## 【0209】

図 27 は、図 25 に示した構成において、シール材 S L 内にたとえばビーズあるいはファイバからなるスペーサを混入させていることにある。

## 【0210】

図 28 は、保護膜 P S V の非形成領域 N P S V をシール材 S L の形成領域にまで及ぼした場合に、シール材 S L 内にたとえばビーズあるいはファイバからなるスペーサを混入させる際に、該スペーサの径を支柱 S P の高さよりも大きくしていることにある。

## 【0211】

## (参考実施例 21)

図 29 は、透明基板 S U B 2 側に形成された支柱の近傍を示す断面図である。この部分はたとえば図 5 (a) の d - d 線の部分 (あるいは図 1 (a) の c - c 線の部分) の断面図に対応している。

## 【0212】

図 25 に示す支柱 S P は特に透明基板 S U B 1 側に形成していることにある。これにより該支柱 S P はその中心軸と交差する平面内の面積が透明基板 S U B 1 側において大きく透明基板 S U B 2 側において小さく形成されるようになる。

## 【0213】

このことは、液晶表示パネル P N L に振動、衝撃が生じた場合、それ自体が衝撃吸収層として機能し、透明基板 S U B 1 側の該支柱 S P の下方に位置づけられる信号線 (この場合、ゲート信号線 G L) にまで該振動、衝撃が伝達するのを抑制でき、該信号線の断線等の不都合を回避できる。

## 【0214】

## (参考実施例 22)

そして、図 29 のように構成した場合、透明基板 S U B 1 側に形成する保護膜 P S V が無機材料層および有機材料層の順次積層体として形成されているため、該有機材料層も衝撃吸収層として機能することになり、該保護膜 P S V の下方に位置づけられる信号線 (この場合、ゲート信号線 G L) の断線等の不都合を確実に回避できることになる。

## 【0215】

## (参考実施例 23)

この参考実施例では、無機材料層および有機材料層の順次積層体からなる保護膜 P S V において、有機材料層の層厚を無機材料層のそれよりも大きくなるように構成したものである。

## 【0216】

これにより、該有機材料層の衝撃吸収層としての機能をさらに向上させることができる。

## 【0217】

10

20

30

40

50

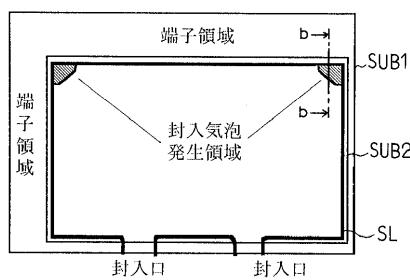

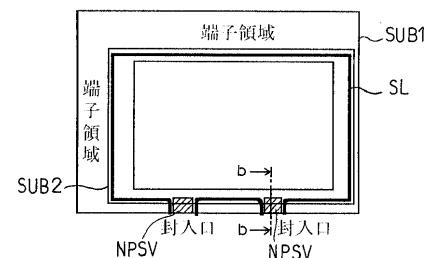

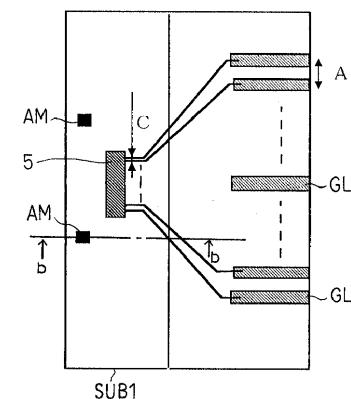

(実施例1)

この実施例は、ゲート駆動IC5あるいはドレイン駆動IC6の実装において、該ゲート駆動IC5あるいはドレイン駆動IC6の位置決めの際に要するアライメントマークに関するものである。

【0218】

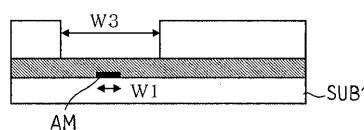

図30(a)に示すように、透明基板SUB1のたとえばゲート駆動IC5の実装領域の近傍には該アライメントマークAMが形成されている。このアライメントマークAMは、透明基板SUB1面にたとえばゲート信号線GLの形成と同時に形成される所定パターンの金属材料からなる層が形成され、たとえば図1および図5に示す画素を有する場合に、該パターンの上面に無機材料層からなる層、有機材料層からなる層が順次積層されている。

10

【0219】

所定パターンの金属材料層からなる層は、たとえば図31(a)、(b)、(c)のような形状からなっている。

【0220】

そして、図30(a)のb-b線における断面図である図30(b)に示すように、無機材料層からなる層は該金属材料層からなる層と相似的なパターンからなっており、それらの中心軸をほぼ一致させて該金属材料層からなる層よりも幅広になって形成されている。そして、この無機材料層からなる層は、その周辺の無機材料層との間に充分な間隙を有するようになっている。

20

【0221】

すなわち、たとえば図31(c)に示すパターンの場合、金属材料層からなる層の幅をW1、無機材料層からなる層の幅をW2、周辺の無機材料層で囲まれる領域の幅をW3とした場合、次式(2)、

【0222】

【数2】

$$W3 > 2W1 > W2 > W1 \dots \dots \dots (2)$$

の関係を成立するようになっている。

【0223】

そして、この無機材料層からなる層の上面およびその周辺には画素領域から延在された有機材料層が形成されている。

30

【0224】

このように形成されたアライメントマークは、それをたとえば画像装置に接続されたカメラで映像(反射モード)させる場合において、無機材料層および有機材料層を介して金属材料層からなる層が認識される。

【0225】

この場合において、無機材料層からなる層は金属材料層からなる層とほぼ同一のパターンから構成されているために、この無機材料層からなる層をアライメントマークとして機能させることができる。

【0226】

たとえば、金属材料層からなる層をアライメントマークAMとし、その上に無機材料層および有機材料層が順次形成されている場合、該金属材料層の表面からの反射ばかりでなく、透明基板SUB1の表面からの反射、無機材料層の表面からの反射、有機材料層の表面からの反射が加わって、認識画像が歪んだ画像として映り全体的にぼやけたものとなって正確に認識することができなくなる。

40

【0227】

特に、無機材料層の表面からの反射と有機材料層の表面の反射のピークとなる波長が互いに異なり、かつそれぞれの反射波長領域は可視光域の広い範囲に及ぶため、アライメントマークの領域以外の領域からの反射の強度が見かけ上広い領域で2倍近くとなり、該アライメントマークの正確な認識を阻害する原因ともなっている。

50

## 【0228】

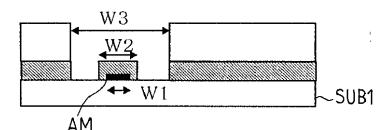

## (実施例2)

上述した実施例1では、金属材料層からなる層の幅をW1、無機材料層からなる層の幅をW2、周辺の無機材料層で囲まれる領域の幅をW3とした場合に、上式(2)の関係が成立するようにしたものであるが、たとえば、次式(3)

## 【0229】

## 【数3】

$W2 < 2W1$ 、かつ  $W3 > 3W1$  ..... (3)

の関係が成立するように設定してもよい。

## 【0230】

この場合においてもアライメントマークを良好に認識できた。

10

## 【0231】

## (実施例3)

図32は、アライメントマークAMの近傍の構成の他の実施例を示す断面図である。同図から明らかとなるように、金属材料層からなるアライメントマークAMを被って無機材料層、有機材料層が順次積層され、該アライメントマークAMの形成領域およびその周囲における有機材料層に開口を設けている。

## 【0232】

これにより、有機材料層の表面からの反射が除去され、アライメントマークAMの認識が明瞭となる。

20

## 【0233】

この場合、金属材料層からなる層の幅をW1、有機材料層の開口の幅をW3とした場合、 $W3 > 3W1$ の関係が成立するように設定することにより、アライメントマークが歪むことなく映像されることが確認された。

## 【0234】

## (実施例4)

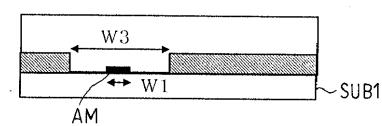

図33は、アライメントマークAMの近傍の構成の他の実施例を示す断面図である。同図は実施例3の構成をさらに改良したもので、有機材料層にも孔開けを行い、有機材料層の表面からの反射が除去されるようにしている。

## 【0235】

30

この場合の有機材料層の開口の幅はW3としている。

## 【0236】

## (実施例5)

図34は、アライメントマークAMの近傍の構成の他の実施例を示す断面図である。

## 【0237】

同図は、金属材料層からなるアライメントマークを被って無機材料層、有機材料層が順次積層する場合に、無機材料層の形成の際に該アライメントマークの形成領域およびその近傍の領域に相当する部分に開口を設けている。

## 【0238】

この場合アライメントマークの幅をW1、無機材料層の前記開口の幅をW3とした場合、 $W3 > 3W1$ の関係が成立するように設定した。

40

## 【0239】

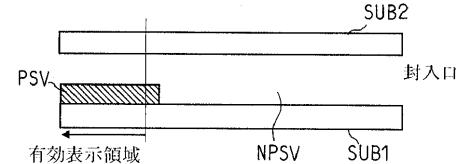

## (実施例6)

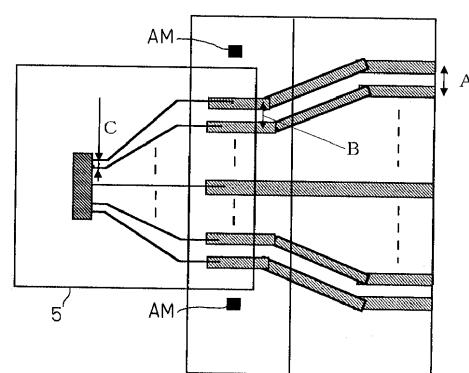

図35は、ゲート駆動IC5として、いわゆるテープキャリア方式で形成したものを見た図である。

## 【0240】

フィルム状の基板に半導体集積回路が搭載されており、この半導体集積回路のバンプは該基板に形成された配線層を介して基板周辺にまで引き出された構成となっている。

## 【0241】

この場合においても、透明基板SUB1とゲート駆動IC5との接続の際には、アライメ

50

ントマーク A M を必要とし、このアライメントマーク A M の構成は上述した実施例のようになっている。

【 0 2 4 2 】

( 参考実施例 2 4 )

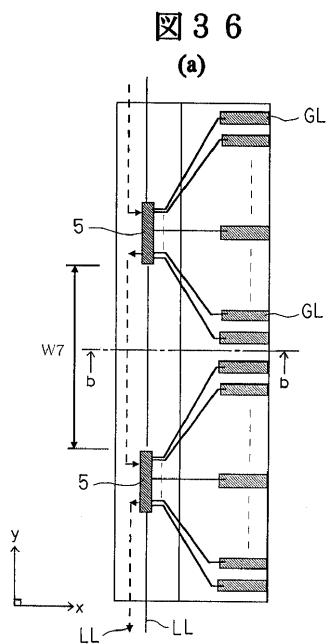

図 3 6 ( a ) は、たとえばゲート駆動 I C 5 の実装部分の平面図を示し、図 2 の点線枠 A に相当する部分の構成図である。図 3 6 ( b ) は図 3 6 ( a ) の b - b 線における断面図である。

【 0 2 4 3 】

図 3 6 ( a ) において、図中 x 方向に延在し y 方向に並設されるゲート信号線 G L が形成されている。これら各ゲート信号線 G L は液晶表示領域 A R からシール材 S L を超えて延在されるものである。 10

【 0 2 4 4 】

そして、これら各ゲート信号線 G L は隣接するもの同士でグループ化され、各グループの各ゲート信号線 G L は互いに収束されて延在し、その延在端は半導体チップからなるゲート駆動 I C 5 の出力バンプに接続される端子が形成されている。

【 0 2 4 5 】

各ゲート信号線 G L がゲート駆動 I C 5 の近傍で収束されたパターンとして形成されるのは、液晶表示領域 A R における各ゲート信号線 G L の信号間隔よりもゲート駆動 I C 5 のバンプのピッチが小さいからである。

【 0 2 4 6 】

そして、このゲート信号線 G L は、上述したように液晶表示領域 A R において透明基板 S U B 1 面に直接（換言すれば、保護膜 P S V 、絶縁膜 G I よりも下層に）形成されているが、ゲート駆動 I C 5 の近傍ではスルホールを介して保護膜 P S V の上面に形成するようになっている。 20

【 0 2 4 7 】

このため、各ゲート駆動 I C 5 が搭載される領域は前記保護膜 P S V が形成された領域となっている。

【 0 2 4 8 】

また、保護膜 P S V は上述したように無機材料層と有機材料層との順次積層体から構成されており、該保護膜 P S V 上に搭載される各ゲート駆動 I C 5 は前記有機材料層が緩衝材として働き振動、衝撃に対して強くなるという効果をもたらす。 30

【 0 2 4 9 】

そして、この参考実施例では、各ゲート駆動 I C 5 の直下を走行するようにしてたとえばゲート信号線 G L （あるいはドレン信号線 D L ）の形成の際に同時に形成される配線層 L L が形成されている。

【 0 2 5 0 】

すなわち、この配線層 L L は、保護膜 P S V の下層に形成され、この保護膜によって直接大気に晒されないようになっている。

【 0 2 5 1 】

この配線層 L L は、たとえば電源ライン、検査用の配線あるいは他の信号線として用いられるもので、たとえば従来透明基板 S U B 1 の近傍に配置されるプリント基板上に形成されていた電源ラインあるいは他の信号線等を透明基板 S U B 1 上に配置させた構成となっている。 40

【 0 2 5 2 】

これによって、透明基板 S U B 1 のいわゆるデッドスペースを有効に使用することができるようになる。

【 0 2 5 3 】

また、図 3 6 ( a ) に示すように、ゲート駆動 I C 5 の実装領域は比較的小さいため、各ゲート駆動 I C 5 の離間距離 W 7 は比較的大きくなる。この場合、前記配線層を保護膜 P S V 上に形成した場合を考えると、該配線層 L L はそのほぼ全長にわたって大気に晒され 50

、電食等による断線等が発生する確率が大幅に増加することになる。

【0254】

しかし、この参考実施例の場合、保護膜PSVの下層に形成されているため、このような支障がなくなり、また、保護膜PSVの有機材料層によって外部からの振動、衝撃による不都合も生じなくなる。

【0255】

本参考実施例では、ゲート駆動IC5の実装領域およびその近傍の構成について説明したものである。しかし、ドレイン駆動IC6の実装領域およびその近傍においても適用できることはいうまでもない。また、以下に示す参考実施例についても同様なことがいえる。

10

【0256】

(参考実施例25)

参考実施例24では、配線層LLを被う保護膜PSVは無機材料層と有機材料層との順次積層体として形成したものである。

【0257】

しかし、該保護膜PSVは有機材料層のみ(液晶表示領域ARにおいても)であってもよく、前記配線層を被う部分およびその近傍部に有機材料層のみで形成してもよいことはいうまでもない。

【0258】

しかし、保護膜PSVを無機材料層と有機材料層との順次積層体とすることにより、無機材料層にたとえクラックが生じてもそのクラックは有機材料層によって塞がれることになり、配線層は電食に対して強固に保護されることになる。

20

【0259】

(参考実施例26)

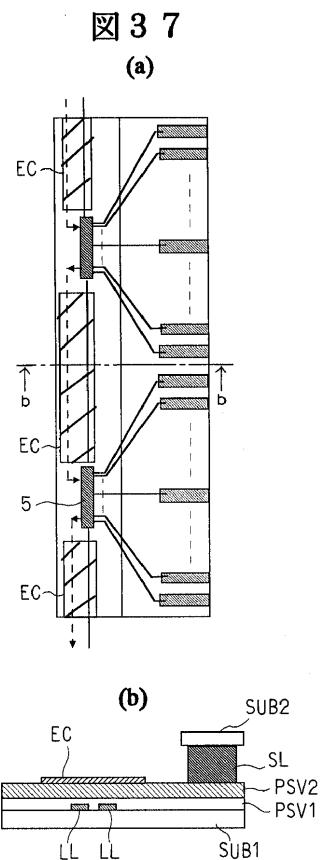

図37は、ゲート駆動IC5の実装領域およびその近傍における他の参考実施例を示す構成図で、図36に対応した図となっている。

【0260】

図36と異なる構成は、保護膜PSVの上面において導電層ECが形成され、この導電層ECはゲート駆動IC5の実装領域を回避して、前記配線層LLを被うようにして形成されている。この導電層ECは接地されていてもよい。

30

【0261】

このような導電層ECを設けることによって、いわゆるEMI対策が図れるようになる。そして、保護膜PSVは無機材料層と有機材料層との順次積層体で構成されているため、前記配線層LLと導電層ECとの容量の結合が減少され、配線層LLの電位を安定させることができる。

【0262】

(参考実施例27)

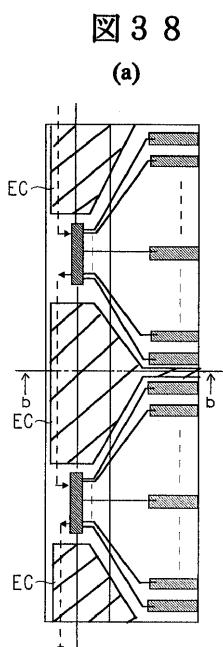

図38は、参考実施例26のさらなる改良を施した構成図で、図37に対応した図となっている。

【0263】

図37と異なる構成は前記導電層ECは液晶表示領域ARに形成された電極(たとえば図1においては基準電極CT)をシール材を超えて延在させていることにある。

40

【0264】

また、該導電層ECは、ゲート駆動IC5の実装領域および該ゲート駆動IC5に接続されるゲート信号線GLの形成領域以外の比較的大きな面積の領域にまで到って形成されたパターンとして形成されている。

【0265】

これにより導電層ECのシールド機能を向上させている。しかし、このような導電層ECのパターンとすることにより、必ずしも液晶表示領域ARに形成された電極等と一体に形成する必要はない。

50

## 【0266】

(参考実施例28)

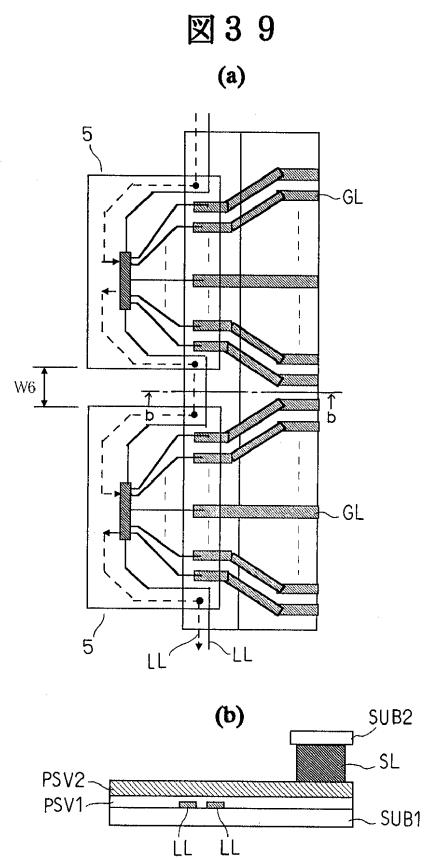

図39は、ゲート駆動IC5の実装領域およびその近傍の構成を示した構成を示し、図36と対応した図となっている。

## 【0267】

図36と異なる構成は、ゲート駆動IC5はいわゆるフィルムキャリア方式によって形成された回路で、フィルム状の基板に半導体ICが搭載されて構成されている。その入力端子は透明基板SUB1の近傍に配置されるプリント基板(図示せず)の端子に接続され、出力端子は該透明基板SUB1の端子に接続されている(いわゆるTCP方式と称される)。

10

## 【0268】

このような場合でも、各ゲート駆動IC5を接続させる配線層LLは、前記フィルム状の基板および透明基板SUB1に形成されている。この場合、フィルム状の基板の配線層LLおよび透明基板SUB1の配線層LLの接続は、ゲート駆動IC5の透明基板SUB1への実装の際になされるようになっている。

## 【0269】

なお、この場合にあっても上述した導電層を形成してシールド機能をもたせるようにしてもよいことはいうまでもない。

## 【0270】

(参考実施例29)

20

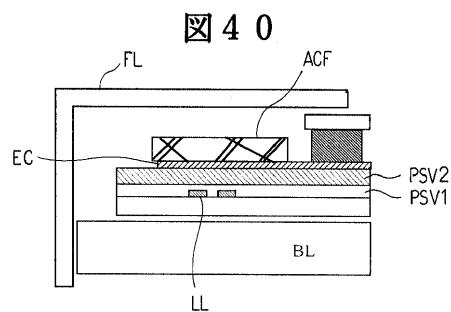

図40は、液晶表示パネルPNLの背面にバックライトBLを配置させ、それらを金属からなるフレームFLを外枠としてモジュール化した構成において、ゲート駆動IC5(あるいはドレイン駆動IC6)の搭載付近の断面を示した図である。

## 【0271】

ゲート駆動IC5の近傍は、図37あるいは図38に示したように、EMI対策の導電層ECが形成され、この導電層ECの上面には該導電層ECをも被って異方性導電膜ACFが被着されている。

## 【0272】

この異方性導電膜ACFはそれに熱処理がなされていないうちは絶縁膜として機能し、前記導電層ECとフレームFLとの直接の接触を回避させるようになっている。

30

## 【0273】

フレームはその重量をできるだけ軽減させるため比較的薄く形成され、これにより外部からの力が加って撓みやすく、この際の前記導電層ECとの接触を防止した構成となっている。

## 【0274】

(参考実施例30)

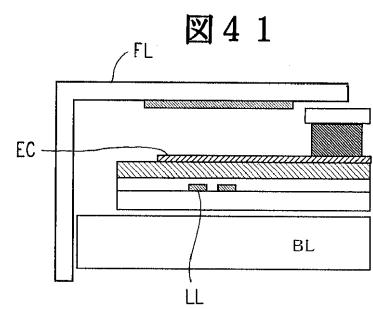

図41は、図40と対応する図で、フレームFLの前記導電層ECと対向する面にたとえば絶縁テープ等の絶縁膜を貼付することにより、該導電層ECとフレームFLとの直接の接触を回避させるようになっている。

## 【0275】

40

(参考実施例31)

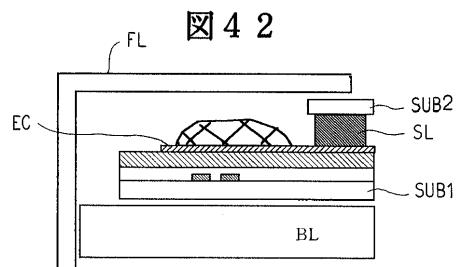

図42は、図40と対応する図で、導電層ECの上面に該導電層ECをも被ってたとえばエポキシ等の樹脂膜をたとえばポッティング等によって形成することによって、該導電層ECとフレームFLとの直接の接触を回避させるようになっている。

## 【0276】

## 【発明の効果】

以上説明したことから明らかなように、参考発明による液晶表示装置によれば、セルギヤップを確保するための支柱の周辺に生じる光漏れを低減させることができる。

## 【0277】

また、液晶を介して対向配置される基板のうち一方の基板面に実装されるドライバチップ

50

の実装におけるリペアを信頼性よく行い得る。

【0278】

また、ドライバチップへの振動あるいは衝撃を緩和させ該ドライバチップの動作不良を軽減させることができる。

【0279】

また、液晶中に発生する気泡の不都合を解消させることができる。

【0280】

また、セルギャップを確保するための支柱に集中する振動あるいは衝撃によって該支柱に間接的に当接する信号線等の破損を回避させることができる。

【0281】

また、本発明による液晶表示装置によれば、信頼性のあるアライメントマークを備えることができる。

【0282】

さらに、参考発明による液晶表示装置によれば、ドライバチップの実装領域の近傍にてたとえば電食等による破損のない配線層を形成することができる。

【図面の簡単な説明】

【図1】 参考発明による液晶表示装置の画素領域の一参考実施例を示す構成図である。

【図2】 参考発明による液晶表示装置の一参考実施例を示す全体構成図である。

【図3】 参考発明による液晶表示装置のスペーサおよびその近傍の一参考実施例を示す要部構成図である。

【図4】 参考発明による液晶表示装置の画素領域の他の参考実施例を示す構成図である。

【図5】 参考発明による液晶表示装置の画素領域の他の参考実施例を示す構成図である。

【図6】 参考発明による液晶表示装置のスペーサおよびその近傍の他の参考実施例を示す要部構成図である。

【図7】 参考発明による液晶表示装置のスペーサおよびその近傍の他の参考実施例を示す要部構成図である。

【図8】 参考発明による液晶表示装置のスペーサおよびその近傍の他の参考実施例を示す要部構成図である。

【図9】 参考発明による液晶表示装置のスペーサおよびその近傍の他の参考実施例を示す要部構成図である。

【図10】 参考発明による液晶表示装置のドライバチップの実装構造の一参考実施例を示す構成図である。

【図11】 ドライバチップの実装構造の一例とそれによる不都合を示す説明図である。

【図12】 参考発明による液晶表示装置のドライバチップの実装構造の他の参考実施例を示す構成図である。

【図13】 参考発明による液晶表示装置のドライバチップの実装構造の他の参考実施例を示す構成図である。

【図14】 参考発明による液晶表示装置のドライバチップの実装構造の他の参考実施例を示す構成図である。

【図15】 参考発明による液晶表示装置のドライバチップの実装構造の他の参考実施例を示す構成図である。

【図16】 参考発明による液晶表示装置のドライバチップの実装構造の他の参考実施例を示す構成図である。

【図17】 参考発明による液晶表示装置のドライバチップの実装構造の他の参考実施例を示す平面図で、そのXVI-XVI線における断面図が図16に相当する。

【図18】 参考発明による液晶表示装置のドライバチップの実装構造の他の参考実施例を示す構成図である。

【図19】 参考発明による液晶表示装置の他の参考実施例を示す構成図である。

10

20

30

40

50

- 【図 2 0】 図 1 9 に示す構成にすべく理由を示す説明図である。

- 【図 2 1】 参考発明による液晶表示装置の他の参考実施例を示す構成図である。

- 【図 2 2】 参考発明による液晶表示装置の他の参考実施例を示す構成図である。

- 【図 2 3】 参考発明による液晶表示装置の他の参考実施例を示す構成図である。

- 【図 2 4】 参考発明による液晶表示装置の他の参考実施例を示す構成図である。

- 【図 2 5】 参考発明による液晶表示装置の他の参考実施例を示す構成図である。

- 【図 2 6】 図 2 5 に示す構成にすべく理由を示す説明図である。

- 【図 2 7】 参考発明による液晶表示装置の他の参考実施例を示す構成図である。

- 【図 2 8】 参考発明による液晶表示装置の他の参考実施例を示す構成図である。

- 【図 2 9】 参考発明による液晶表示装置の他の参考実施例を示す構成図である。 10

- 【図 3 0】 本発明による液晶表示装置のドライバチップ実装付近のアライメントマークの一実施例を示す構成図である。

- 【図 3 1】 アライメントマークのパターンを示した説明図である。

- 【図 3 2】 本発明による液晶表示装置のドライバチップ実装付近のアライメントマークの他の実施例を示す構成図である。

- 【図 3 3】 本発明による液晶表示装置のドライバチップ実装付近のアライメントマークの他の実施例を示す構成図である。

- 【図 3 4】 本発明による液晶表示装置のドライバチップ実装付近のアライメントマークの他の実施例を示す構成図である。

- 【図 3 5】 本発明による液晶表示装置のドライバチップ実装付近のアライメントマークの他の実施例を示す構成図である。 20

- 【図 3 6】 参考発明による液晶表示装置のドライバチップ実装付近の他の参考実施例を示す構成図である。

- 【図 3 7】 参考発明による液晶表示装置のドライバチップ実装付近の他の参考実施例を示す構成図である。

- 【図 3 8】 参考発明による液晶表示装置のドライバチップ実装付近の他の参考実施例を示す構成図である。

- 【図 3 9】 参考発明による液晶表示装置のドライバチップ実装付近の他の参考実施例を示す構成図である。

- 【図 4 0】 参考発明による液晶表示装置のドライバチップ付近のフレームをも含めた構成の一参考実施例を示す構成図である。 30

- 【図 4 1】 参考発明による液晶表示装置のドライバチップ付近のフレームをも含めた構成の他の参考実施例を示す構成図である。

- 【図 4 2】 参考発明による液晶表示装置のドライバチップ付近のフレームをも含めた構成の他の参考実施例を示す構成図である。

- 【図 4 3】 参考発明による液晶表示装置の他の参考実施例を示す平面図である。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

図12

【図13】

図13

【図14】

図14

【図15】

図15

【図16】

図16

【図17】

図17

【図18】

図18

【図19】

図19

(a)

(b)

【図20】

図20

(a)

(b)

【図21】

図21

【図22】

図22

(a)

(b)

【図23】

図23

【図24】

図24

【図25】

図25

【図26】

図26

【図27】

図27

【図28】

図28

【図29】

図29

【図30】

図30

(a)

(b)

【図31】

図31

(a)

(b)

(c)

【図32】

図32

【図33】

図33

【図34】

図34

【図35】

図35

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

図40

【図42】

図42

【図43】

図43

図41

---

フロントページの続き

(72)発明者 岩壁 靖

千葉県茂原市早野3300番地 株式会社日立製作所 ディスプレイグループ内

(72)発明者 仲吉 良彰

千葉県茂原市早野3300番地 株式会社日立製作所 ディスプレイグループ内

(72)発明者 若木 政利

茨城県日立市大みか町七丁目1番1号 株式会社日立製作所 日立研究所内

審査官 山口 裕之

(56)参考文献 特開平09-026586 (JP, A)

国際公開第98/047044 (WO, A1)

特開平03-027015 (JP, A)

特開平10-239689 (JP, A)

特開平08-248431 (JP, A)

特開平04-058217 (JP, A)

特開2000-098406 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G02F 1/1368

G02F 1/1345