(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3930454号

(P3930454)

(45) 発行日 平成19年6月13日(2007.6.13)

(24) 登録日 平成19年3月16日(2007.3.16)

(51) Int.C1.

F 1

|                      |                  |               |         |

|----------------------|------------------|---------------|---------|

| <b>G 1 1 C 16/06</b> | <b>(2006.01)</b> | G 1 1 C 17/00 | 6 3 4 Z |

| <b>G 1 1 C 16/04</b> | <b>(2006.01)</b> | G 1 1 C 17/00 | 6 2 4   |

|                      |                  | G 1 1 C 17/00 | 6 2 2 Z |

請求項の数 11 (全 18 頁)

(21) 出願番号 特願2003-131767 (P2003-131767)

(22) 出願日 平成15年5月9日 (2003.5.9)

(65) 公開番号 特開2003-331592 (P2003-331592A)

(43) 公開日 平成15年11月21日 (2003.11.21)

審査請求日 平成16年9月6日 (2004.9.6)

(31) 優先権主張番号 10/143449

(32) 優先日 平成14年5月10日 (2002.5.10)

(33) 優先権主張国 米国(US)

(73) 特許権者 504378124

スパンション エルエルシー

アメリカ合衆国 カリフォルニア州 94

088-3453 サニー・ベイル デグウ

イン ドライブ 915 ピー・オー・ボ

ックス 3453

(74) 代理人 100087480

弁理士 片山 修平

(72) 発明者 山田 重和

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

審査官 滝谷 亮一

最終頁に続く

(54) 【発明の名称】 2ビット型メモリセルの読み出し方法及び回路と半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項1】

ノーマルビットである第1のビット及び相補ビットである第2のビットの2ビットを電圧閾値として記憶する2ビット型コアセルと、

2ビット型コアセルと関連した2個の2ビット型リファレンスセルと、を含み、

各2ビット型リファレンスセルは、所定のリファレンス閾値として第1のリファレンスビット及び第2のリファレンスビットを記憶している、記憶装置の2ビット型コアセルを読み出す方法であって、

コアセルの第1のビットを読み出す手順と、

各2ビット型リファレンスセルの第1のリファレンスビットを読み出す手順と、

コアセルの第1のビットを、2個の2ビット型リファレンスセルの各々の第1のリファレンスビットと同時に比較する手順と、

コアセルの第2のビットを、対応する第1のビットが読み出された方向とは逆の方向に読み出す手順と、

各2ビット型リファレンスセルの第2のリファレンスビットを、対応する第1のリファレンスビットが読み出された方向とは逆の方向に読み出す手順と、

コアセルの第2のビットを、2個の2ビット型リファレンスセルの各々の第2のリファレンスビットと同時に比較する手順と、を有し、

比較の結果に基づいて、2ビット型コアセルのビットの2進数値が決定される、方法。

## 【請求項2】

10

20

2ビット型フラッシュメモリの第2のビットを読み出すためのアクセス時間が最小限に抑えられるように2ビット型メモリセルの2ビットを読み出す回路であって、

電圧閾値としてノーマルビット及び相補ビットを記憶する2ビット型記憶セルと、

第1の2ビット型リファレンスセル及び第2の2ビット型リファレンスセルと、を含み、

各2ビット型リファレンスセルは、ノーマルビットである第1のリファレンスピットと相補ビットである第2のリファレンスピットの2個のリファレンスピットを記憶し、

第1の2ビット型リファレンスセルのノーマルビット及び相補ビットは第1の所定のリファレンス閾値として記憶され、

第2の2ビット型リファレンスセルのノーマルビット及び相補ビットは第2の所定のリファレンス閾値として記憶され、

2ビット型記憶セルのノーマルビット及び相補ビットと第1の所定のリファレンス閾値との差、並びに、2ビット型記憶セルのノーマルビット及び相補ビットと第2の所定のリファレンス閾値との差を検出し増幅するセンスアンプ回路が設けられ、

ノーマルビットと相補ビットがセンスアンプ回路へ供給されるように、記憶セルとセンスアンプ回路の間にコネクションを設定する複数のトランジスタを備えたデータ回路が設けられ、

第1のリファレンス回路及び第2のリファレンス回路が設けられ、

各リファレンス回路は、各リファレンスセルの所定のリファレンス閾値がセンスアンプ回路へ供給されるように、対応したリファレンスセルとセンスアンプ回路の間にコネクションを設定する複数のトランジスタを備え、

対応した記憶セルのノーマルビット及び相補ビット、並びに、対応したリファレンスセルのノーマルビット及び相補ビットは、順番に読み出され、リファレンス回路及びデータ回路は、各相補ビットが、対応したノーマルビットが読み出された後に、対応したノーマルビットが読み出された方向とは逆の方向に読み出され、

これにより、記憶セルのノーマルビットと相補ビットの読み出しの間に電圧オーバーシュートが発生し、各2ビット型リファレンスセルのノーマルビットと相補ビットの読み出しの間に対応した電圧オーバーシュートが発生し、記憶セルの相補ビットの読み出しのための回復時間が最小限に抑えられている、回路。

#### 【請求項3】

センスアンプ回路は、複数のセンスアンプと複数の比較器を含む、請求項2記載の回路。

#### 【請求項4】

センスアンプは、

データ回路に接続された第1のセンスアンプと、

第1のリファレンス回路に接続された第2のセンスアンプと、

第2のリファレンス回路に接続された第3のセンスアンプと、

第1のセンスアンプ及び第2のセンスアンプに接続され、記憶セルのノーマルビット及び相補ビットを、第1の所定のリファレンス閾値と比較する第1の比較器と、

第1のセンスアンプ及び第3のセンスアンプに接続され、記憶セルのノーマルビット及び相補ビットを、第2の所定のリファレンス閾値と比較する第2の比較器と、を含む、請求項3記載の回路。

#### 【請求項5】

第1のリファレンス回路及び第2のリファレンス回路の対応した複数のトランジスタは、対応したリファレンスピットがセンスアンプ回路によって検出されるように向きが合わされている、請求項4記載の回路。

#### 【請求項6】

第1のリファレンス回路及び第2のリファレンス回路の複数のトランジスタは、各リファレンスセルのノーマルビットを読み出す際に、対応したリファレンスセルのソース端子とグラウンドの間、並びに、対応したリファレンスセルのドレイン端子とセンスアンプ回

10

20

30

40

50

路の間にパスが設定され、各リファレンスセルの相補ビットを読み出す際に、対応したリファレンスセルのドレイン端子とグラウンドの間、並びに、対応したリファレンスセルのソース端子とセンスアンプ回路の間にパスが設定されるように制御される、請求項 5 記載の回路。

【請求項 7】

記憶セルのノーマルビットの読み出しと対応した相補ビットの読み出しの間に電圧オーバーシュートが発生し、

リファレンスセルのノーマルビットの読み出しと対応した相補ビットの読み出しの間に対応した電圧オーバーシュートが発生し、

記憶セルの相補ビットの読み出しに要する回復時間が最小限に抑えられている、請求項 6 記載の回路。 10

【請求項 8】

データ回路の複数のトランジスタは、記憶セルのソースとグラウンドの間、並びに、記憶セルのドレインと第 1 のセンスアンプの間にパスを設定し、これにより、記憶セルの相補ビットの読み出しが行えるようになる、請求項 4 記載の回路。

【請求項 9】

第 1 のリファレンスピットはノーマルビットであり、第 2 のリファレンスピットは相補ビットであり、

2 ビット型コアセルは、ソース端子、ドレイン端子及びゲート端子を具備し、

コアセルの第 2 のビットを読み出す手順は、コアセルが第 1 のビットを読み出す方向とは逆の方向へ読み出されるように、2 ビット型コアセルのソース端子とドレイン端子を入れ替える手順を含み、 20

2 ビット型リファレンスセルは、ソース端子、ドレイン端子及びゲート端子を含み、

第 2 のリファレンスピットを読み出す手順は、各 2 ビット型リファレンスセルが第 1 のリファレンスピットを読み出す方向とは逆の方向へ読み出されるように、各 2 ビット型リファレンスセルのソース端子とドレイン端子を入れ替える手順を含み、

2 ビット型リファレンスセルのソース端子とドレイン端子を入れ替えることにより生じた電圧アンダーシュートは、2 ビット型コアセルの第 2 のビットの読み出し前に要する回復時間が最小限に抑えられるように、2 ビット型コアセルのソース端子とドレイン端子を入れ替えることにより生じた電圧アンダーシュートに追従する、請求項 1 記載の方法。 30

【請求項 10】

電圧閾値としてノーマルビット及び相補ビットを記憶する 2 ビット型記憶セルと、

第 1 の 2 ビット型リファレンスセル及び第 2 の 2 ビット型リファレンスセルと、を含み、

各 2 ビット型リファレンスセルは、ノーマルビットである第 1 のリファレンスピットと相補ビットである第 2 のリファレンスピットの 2 個のリファレンスピットを記憶し、

第 1 の 2 ビット型リファレンスセルのノーマルビット及び相補ビットは第 1 の所定のリファレンス閾値として記憶され、

第 2 の 2 ビット型リファレンスセルのノーマルビット及び相補ビットは第 2 の所定のリファレンス閾値として記憶され、 40

2 ビット型記憶セルのノーマルビット及び相補ビットと第 1 の所定のリファレンス閾値との差、並びに、2 ビット型記憶セルのノーマルビット及び相補ビットと第 2 の所定のリファレンス閾値との差を検出し増幅するセンスアンプ回路が設けられ、

ノーマルビットと相補ビットがセンスアンプ回路へ供給されるように、記憶セルとセンスアンプ回路の間にコネクションを設定する複数のトランジスタを備えたデータ回路が設けられ、

第 1 のリファレンス回路及び第 2 のリファレンス回路が設けられ、

各リファレンス回路は、各リファレンスセルの所定のリファレンス閾値がセンスアンプ回路へ供給されるように、対応したリファレンスセルとセンスアンプ回路の間にコネクションを設定する複数のトランジスタを備え、 50

対応した記憶セルのノーマルビット及び相補ビット、並びに、対応したリファレンスセルのノーマルビット及び相補ビットは、順番に読み出され、リファレンス回路及びデータ回路は、各相補ビットが、対応したノーマルビットが読み出された後に、対応したノーマルビットが読み出された方向とは逆の方向に読み出され、

これにより、記憶セルのノーマルビットと相補ビットの読み出しの間に電圧オーバーシュートが発生し、各 2 ビット型リファレンスセルのノーマルビットと相補ビットの読み出しの間に対応した電圧オーバーシュートが発生し、記憶セルの相補ビットの読み出しのための回復時間が最小限に抑えられている、半導体記憶装置。

#### 【請求項 11】

ノーマルビットである第 1 のビット及び相補ビットである第 2 のビットの 2 ビットを電圧閾値として記憶する 2 ビット型記憶セルと、 10

前記 2 ビット型記憶セルと関連し、所定のリファレンス閾値として第 1 のリファレンスビット及び第 2 のリファレンスビットを記憶する 2 個の 2 ビット型リファレンスセルと、

前記 2 ビット型記憶セルの前記第 1 ビットまたは前記第 2 ビットと前記 2 個の 2 ビット型リファレンスセルの各々の前記第 1 のリファレンスビットまたは第 2 リファレンスビットとをそれぞれ比較する比較器と、を具備し、

前記 2 ビット型記憶セルの前記第 1 のビットと前記 2 個の 2 ビット型リファレンスセル各々の第 1 のリファレンスビットとが前記比較器に読み出され、その後、前記 2 ビット型記憶セルの前記第 2 のビットと前記 2 個の 2 ビット型リファレンスセル各々の前記第 2 のリファレンスビットとが前記第 1 のビットと前記第 1 のリファレンスビットとがそれぞれ読み出された方向とは逆の方向で前記比較器に読み出される半導体記憶装置。 20

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は、一般的に不揮発性半導体記憶装置に係り、特に、2 ビット型メモリセル及び関連したリファレンス側セルにおけるビット読み出しシステムに関する。

##### 【0002】

##### 【従来の技術】

従来のフラッシュメモリのような不揮発性半導体記憶装置の場合、各メモリセルは 1 ビットのデータだけを記憶する。従来の 1 セル毎に 1 ビットのフラッシュメモリ構成の場合、各セルは、典型的に、金属酸化膜半導体トランジスタ構造を具備し、この金属酸化膜半導体トランジスタは、ソース、ドレイン、及び、基板内のチャネルと、チャネル上のスタックトゲート構造とを備えている。スタックトゲート構造は、典型的に、チャネルの表面に形成されたトンネル酸化膜と、トンネル酸化膜上の浮遊ゲートと、酸化膜に重なる制御ゲートと、を含む。情報は、個別のコアセル毎に浮遊ゲートを所定の電圧閾値まで充電することによって、フラッシュメモリにプログラムされる。1 ビット型メモリセルの場合、データビットが 2 進の "0" 又は 2 進の "1" の何れかである閾値でプログラムされるよう、2 個の電圧閾値が規定される。 30

##### 【0003】

不揮発性メモリを具備した最新の装置は、外形の小さいパッケージにより大容量のメモリを収容するという要求を拡大し続けている。このような高密度メモリに対する要求を満たすため、1 セル毎に 2 ビットの(2 ビット型セル)フラッシュメモリが開発されている。2 ビット型セルとは、一つのメモリセルに 2 ビットのデータを記憶させることができるセルを意味する。

##### 【0004】

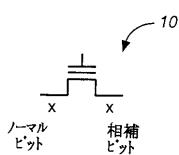

図 1 は、本発明と同じ 2 ビット型コアセル構造の略構成図である。2 ビット型コアセル 10 毎に、2 ビットが格納され、プログラムされる。この 2 ビットのうちの一方の第 1 ビットは標準ビットと呼ばれ、他方の第 2 ビットは相補("comp")ビットと呼ばれる。フラッシュメモリのような不揮発性メモリの場合、データの完全性は、ユーザに悪影響を与える可能性のあるデータ誤りを回避するため、装置の耐用期間中に亘って維持されるべきであ

10

20

30

40

50

る。フラッシュメモリセルの耐用期間中、データに影響を与えるセル特性に変化が生じる可能性がある。セルに対するこのような変化の一つは、近隣セルの状態を妨害する長期の隣接セルのプログラミングに起因して起こり得る。フラッシュメモリの耐用期間中の充電損失もセル特性に影響を与える可能性がある。これらのセル特性の変化は、セル電圧閾値のシフトを生じさせる。このシフトは、メモリセルの状態に影響を与え、データ誤りを引き起こす可能性がある。その結果として、長期間に亘ってセルのデータビットの完全性を保証する技術が必要になる。

#### 【0005】

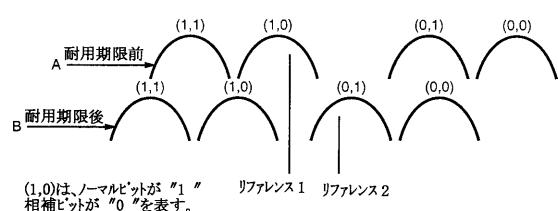

図2Aは、長期間に亘る2ビット型セルの閾値の分布の変動の一例を示す波形図である。セルには2ビットが存在するので、2ビットの組合せに対して4種類の閾値分布が使用される。軌跡Aは、新しいメモリセルに対する電圧閾値分布の状態の一例を示している（図2Aでは、耐用期限前として示されている。）。アレイ内のメモリセルがセルアレイの耐用期間中に繰返し使用されると、装置特性に影響を与える充電損失、メモリ障害、及び、その他の変化が長期間に亘って生じる。装置特性が変化すると、閾値分布は異なる状態へ移行する。移行した状態の一例（図2Aでは、耐用期限後として示されている。）が軌跡Bに示されている。例えば、図2Aの軌跡において、（1, 0）は、標準ビットが1に一致し、第2の相補ビットが0に一致することを表している。フラッシュメモリのような不揮発性メモリは、1回だけプログラムされ、長期間に亘って断続的に読まれるであろう。従って、軌跡Aと軌跡Bに示された両方の閾値分布に関して正確に2ビット型セルのデータビット値を決定することが必要である。ある解決技術は、2個のリファレンス閾値（REF1及びREF2）を準備し、セルデータを決定するためコアセル閾値と比較する。

図2Bには、この技術がリファレンス閾値を正常ビット及び相補ビットと比較することにより、コアセルデータを決定する方法が示されている。

#### 【0006】

図2Aと、図2Bの上部データ行及び下部データ行に示されているように、コアセル閾値が分布の両極端の何れか、即ち、（1, 1）又は（0, 0）にあるならば、データを決定するために標準ビットの方だけを2個のリファレンス閾値と比較すればよい。この場合、セルデータを決定するために相補ビットを比較する必要がないので、図2Bの相補ビットの列は、「ドントケア」状態を表す”×”としてマークされている。例えば、コアセル閾値電圧が2個のリファレンス閾値よりも高い（”0”として表される）場合、図2Bの一番下の行に示されているように、コアセルデータは”0”になる。反対に、コアセル閾値電圧がリファレンス1及びリファレンス2の2個の閾値よりも低い場合、データは”1”になる。

#### 【0007】

図2Aの例に示されているように、時間経過によって閾値分布が軌跡Aから軌跡Bへ移行することは、様々なコアセル閾値に対するデータを決定する際に難しい問題を引き起こす。コアセル閾値が2個のリファレンス閾値の間の区域に収まるとき、データは、標準ビットを2個のリファレンス閾値と比較するだけでは決定できない。このことは、図2Aと図2Bに示されているように、軌跡Aの（1, 0）における標準ビットの1、並びに、軌跡Bの（0, 1）における標準ビットの0に対して、2個のリファレンス閾値電圧REF1及びREF2との比較によって同じ結果が生じる、ということから分かる。両方のケースでデータの適切な決定を行うために、2個のリファレンスセルから2個のリファレンス閾値を読み出すのと同時に2個の順次データを読み出す技術が開発された。標準ビットと相補ビットの両方がリファレンスセルと共に読み出されるならば、軌跡A（耐用期限前）と軌跡B（耐用期限後）の何れかの分布に対するセルデータは、後で詳述するように決定することができる。

#### 【0008】

標準ビットのほかに相補ビットを設けることによる効果は図2Bに示されている。この技術のため、コアセル閾値がREF1とREF2の2個のリファレンス閾値の間に収まる場合、標準ビット及び相補ビットは、リファレンス閾値REF1及びREF2と比較される

10

20

30

40

50

。例えば、上述の軌跡 B において、(0, 1) の標準ビットが 0 の場合、相補ビット閾値は(1, 0) 分布の下にあり、(0, 1) 分布の逆である。従って、リファレンス閾値 R E F 1 と R E F 2 の間に収まるコアセル閾値に対して、相補ビット閾値は、2 個の閾値の間に収まらない。例示的に、コアセル閾値が、リファレンス閾値 R E F 1 と R E F 2 の間で、軌跡 B における(0, 1) 分布の下の区域に収まるケースを考える。このケースは、図 2 B の下から 2 行目に示されている。標準ビットに対し、コアセル閾値はリファレンス閾値 R E F 1 (図 2 B の表中では、"0" として示されている。) よりも高く、リファレンス閾値 R E F 2 (表中、"1" として示されている。) よりも低い。軌跡 B に対し、このコアセル閾値に対応した相補ビットは、(1, 0) 閾値の下に収まる。この相補ビット閾値 ("1") は、両方のリファレンス閾値 R E F 1 及び R E F 2 よりも低い。これにより、図 2 B に示されるようにセルデータは 0 になる。10

#### 【0009】

同様に、図 2 B の下から 3 行目に示されるように、比較は、軌跡 A の(1, 0) 分布の下でリファレンス閾値 R E F 1 と R E F 2 の間にある区域に対する標準ビットとリファレンス閾値 R E F 1 及び R E F 2 の場合に同じである。相補ビットを使用することにより、このケースのセルデータが "1" であることが決定される。

#### 【0010】

上記の技術の場合、相補ビットの付加的な比較をリファレンスセル R E F 1 及び R E F 2 に追加することにより、たとえ、コアセル閾値が 2 個のリファレンスセル閾値の間に収まるとしても、セルデータは、セルの耐用期間中、正確に決定される。上記方法において、各ビット (標準ビット及び相補ビット) は、リファレンス閾値 R E F 1 及び R E F 2 のための 2 個のリファレンスセルと共に読み出される。リファレンスセルに対するデータ読み出しの組合せによって、実際のセルデータを決定する。必要な比較を行うため相補ビットを読み出すためのシステム及び方法は、後で詳細に説明される。20

#### 【0011】

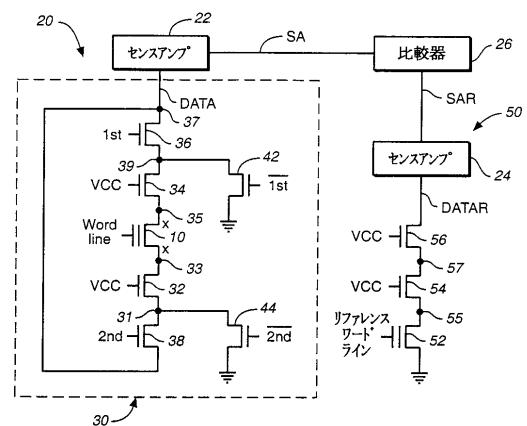

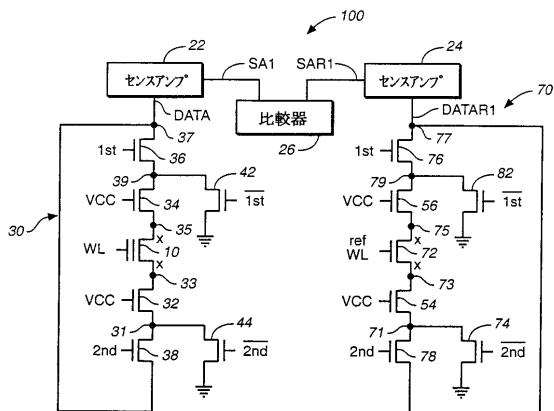

図 3 は、上述の方法に対応するセンス回路の回路図である。図 3 から分かるように、センス回路 20 は、センスアンプ 22 に接続されたデータ回路 30 と、リファレンスセンスアンプ 24 に接続されたリファレンス回路 50 と、を含む。ライン S A 上のセンスアンプ 22 の出力、及び、ライン S A R 上のセンスアンプ 24 の出力は、比較器 26 の入力へ接続される。比較器 26 は、データを決定するために、センスアンプ 22 からの出力信号 S A を、リファレンスセンスアンプ 24 からの出力信号 S A R と比較する。30

#### 【0012】

データ回路 30 は、ワードラインに接続された制御ゲート、ノード 35 に接続されたドレイン、及び、ノード 33 に接続されたソースを有するコアセル 10 を具備する。セルアレイ内のメモリセルは、典型的に行と列によって編成される。共通ワードラインは、アレイ内のセルの行を選択する制御回路 (図示しない) によって設けられる。V C C 信号は、アクセスされるメモリセルの列を選択するため制御回路によって与えられる。メモリアレイ内の個別のセルの復号化及びアドレッシング用回路の詳細は、当業者に周知の事項である。本発明は、一つのコアセル 10 に関して更に詳細に記述される。

#### 【0013】

相補ビットの読み出しのため、コアセル 10 のドレイン及びソースは、標準ビットの読み出しの場合と比較して、入れ替える必要がある。したがって、標準ビットの読み出しのため設けられたデータ (D A T A) ビットラインへのバスと、相補ビットを読み出すため設けられた別のバスと、が存在する。図 3 に示され、後で詳述するように、付加的なトランジスタは、典型的に、2 本の導電バスをデータビットラインへ繋ぐパストランジスタとして設けられる。40

#### 【0014】

図 3 のデータ回路 30 において、コアセル 10 のソース端子は、ノード 33 で、パストランジスタ 32 のドレイン端子に繋がる。パストランジスタ 32 は、V C C に接続されたゲートと、ノード 31 に接続されたソースとを有する。トランジスタ 38 は、ノード 31 に

10

20

30

40

50

接続されたドレインと、ノード37でセンスアンプ22の入力へ接続されたソースと、2番目のラインへ接続されたゲートとを有する。この2番目のラインは、制御回路（図示しない）によって設けられ、2ビット型セルにおける2ビットのうちの2番目のビット（相補ビット）の読み出し用のパスを選択するための制御を行う。かくして、コアセル10の2番目のビットを読み出す必要がある場合、データ回路30内のトランジスタのゲート入力は、ノード33におけるコアセル10のソース端子から、トランジスタ32及び38を経由して、ノード37へ至る接続バスが得られるように制御される。ノード37は、データセンスアンプ22の入力でデータビットラインへ繋がる。ノード31は、トランジスタ44のドレインにも接続されている。図3に示されるように、トランジスタ44のソースは接地され、ゲートは2番目のバーライン（2番目のラインの反転ライン）に接続される。トランジスタ44は、標準ビット（第1ビット）を読み出すために必要なグラウンドへのバスを設ける。10

#### 【0015】

ノード35は、コアセル10のドレイン端子で、パストランジスタ34のソース端子に繋がる。パストランジスタ34は、VCCに接続されたゲートと、ノード39でトランジスタ36のソースに接続されたドレインと、を含む。トランジスタ36は、ノード37でセンスアンプ22の入力におけるデータビットラインへ接続されたドレインを含む。トランジスタ36のゲートは、1番目のラインへ接続される。この1番目のラインは、2ビットのうちの第1ビット（標準ビット）の読み出しを制御する。ノード39はトランジスタ42のドレインにも接続される。トランジスタ42のソースは接地され、ゲートは1番目のバーライン（1番目のラインの反転ライン）に接続される。トランジスタ42は、相補ビット（第2ビット）の読み出し用のセル10のドレインにグラウンドまでのバスを設ける。1番目の信号と2番目のバー信号（2番目の信号の反転信号）は、標準ビットの読み出しのためアクティブ状態になり、2番目の信号と1番目のバー信号（1番目の信号の反転信号）は、相補ビットの読み出しのためアクティブ状態になる。上述のVCC信号及びワードライン信号は、コアセル10が選択されているとき、アクティブ状態にセットされる。20

#### 【0016】

次に、図3を参照してリファレンス回路50を説明する。図3には、1個のリファレンス回路50（例えば、REF1用のリファレンス回路）と、センスアンプ24と、比較器26しか表示されていないが、センス回路20は、第2のリファレンス閾値REF2のための第2のリファレンスセルに関連した同一の回路（図示しない）を具備する。リファレンス回路50は、リファレンスワードラインに接続された制御ゲートと、グラウンドに接続されたソースと、ノード55に接続されたドレインとを有するリファレンスセル52を含む。2個のトランジスタ54及び56は、ノード55と、センスアンプ24の入力との間に直列に接続される。トランジスタ54及び56のゲートは、VCCに接続されている。トランジスタ54のソースは、リファレンスセル52のドレイン端子でノード55に接続される。トランジスタ54のドレイン及びトランジスタ56のソースは、共に、ノード57で接続される。トランジスタ56のドレインは、図3にリファレンス信号DATARとして示されるように、センスアンプ24の入力に繋がる。30

#### 【0017】

次に、図3及び4を参照してセンス回路20の動作を説明する。図3に対応した方法の場合、各ビット（標準ビット及び相補ビット）は、2個のリファレンスセルと共に読み出される。2回の読み出しに対するビットの電圧とリファレンスセルの電圧を比較することにより、実際のコアセルデータが決まる。図3に示された回路において、標準ビット及び相補ビットは、同時に読み出すことができない。なぜならば、第2ビット（相補ビット）を読み出すためには、コアセル10のソースとドレインを入れ替えなければならないからである。回路20用の2ビット型セルにおいて両方のビットを獲得するため、標準ビット（及びリファレンスセル）のための1回目の読み出しどと、相補ビット（及びリファレンスセル）のための2回目の読み出しどの2回の別々の読み出しが必要である。2回の読み出しが40

必要になるので、両方の読み出しを完了するために必要とされるアクセス時間は、両方のビットを正確に読み出す高速性を決める際に重要である。

#### 【0018】

##### 【発明が解決しようとする課題】

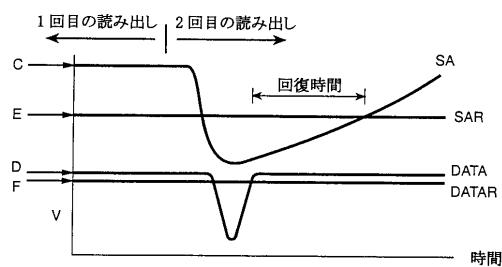

総読み出しアクセス時間における重要な決定要因は、1回目（標準ビット）の読み出し後に、2回目（相補ビット）の読み出しの高速性である。図3におけるセンス回路20と方法の欠点は、2回目の読み出しの実行を遅らせるビットラインのアンダーシュートである。図4には、このアンダーシュートの欠点が示されている。図4における電圧軌跡は、1回目の読み出しが完了し、2回目の読み出しが実行される期間の電圧を示している。図4における軌跡Cは、データセンスアンプ22の出力を表す図3からのセンスアンプ信号（S A）の波形を示している。軌跡Dは、ビットラインにおける対応したデータ（D A T A）に対する電圧の波形である。軌跡Eは、リファレンスセンスアンプ24からのS A R信号に対する電圧の波形であり、軌跡Fは、センスアンプ24へ入力されたリファレンスセルデータ電圧（D A T A R）を表している。動作時に、第2ビットを読み出す必要があるとき、ソースとドレインが入れ替えられる。その結果として、コアセル10のドレインは充電を開始し、ソースは放電を開始する。この遷移期間は、ビットライン（D A T A）に非常に大きい電圧降下を生じさせ、これは、図4に軌跡Cとして示されているように、回路20の対応したセンス信号S Aで非常に大きい電圧降下（アンダーシュート）となって現れる。

#### 【0019】

図4に示されているように、センス信号S Aにこのようなアンダーシュートが現れた後、2回目の読み出しを実行するためセンス信号S Aが望ましいレベルへ戻る前に、重大な時間間隔が存在する。動作中に、センス信号S Aは、十分に回復することが必要であり、そのため、2回目の読み出しを続行するために、信号S Aと信号S A Rの間に余裕が必要とされる。この長時間の回復時間は、図3の回路20の欠点である。なぜならば、この回復時間は、必要な2回の読み出しを完了するために、総アクセス時間に膨大な時間損失が生じるからである。

#### 【0020】

最新の装置は、ユーザが要求した応答を与えることができる速度でデータを処理するため、より高速のアクセス時間を益々要求している。フラッシュメモリのアクセス時間は、密度が増大している間に最適化される必要がある。従って、2ビット型フラッシュメモリにおいて、メモリの耐用期間中にメモリデータの完全性を維持すると共に、メモリアクセス時間を最適化することが求められている。

#### 【0021】

よって、本発明は、不揮発性記憶装置において2ビット型メモリセルの2回の読み出しを実行するためのアクセス時間を高速化するため、2回目の読み出しの回復時間を短縮するシステム及び方法の提供を目的とする。

#### 【0022】

##### 【課題を解決するための手段】

上記目的を達成するため、本発明は、原理的に、2ビット型セルの両端のビットを読むことで特定のビットデータを確定する読み出し方式において、2回目のリード時に生じるコア側のデータドロップをリファレンス側にも生じさせることにより、2回目のリードを高速化する。

#### 【0023】

本発明は、フラッシュメモリのような不揮発性記憶装置において、2ビット型セル用の2回目の読み出しのための回復時間を短縮するためリファレンスセルを入れ替えるシステム及び方法を提供する。回復時間の短縮によって、2回の読み出しのための全体的な読み出し時間が他の技術よりも実質的に短縮される。本発明では、2回の連続的な読み出しが実行され、2ビット型セルの各ビットが2個のリファレンスセルと共に読み出される。

#### 【0024】

10

20

30

40

50

本発明のシステムは、効率的かつ正確にデータを読み出すため、リファレンス回路とデータ回路の両方の回路のソース端子とドレイン端子の入れ替えを行う回路を含む。本発明のシステムは、メモリセル特性の時間的な変化を考慮し、これにより、データ誤りを取り除く回路及び方法を含む。

#### 【0025】

本発明の一実施例は、2ビットのデータビットと2個のリファレンスセルを読み出す装置である。各データビットの閾値電圧と2個のリファレンスセルの閾値電圧が検出される。2個のリファレンスセル閾値電圧は、データビット・センス電圧閾値と個別に比較される。2ビット型セルの第2の相補ビットは、コアセルのドレイン端子とソース端子を入れ替えることによって標準ビットの後に読み出される。2回目の読み出しの回復時間を実質的に短縮するため、リファレンスセルのドレイン及びソースは、センスリファレンス閾値電圧が入れ替えによって降下（アンダーシュート）し、このアンダーシュートがセンスデータ閾値電圧の対応したアンダーシュートを追尾するように、2回目の読み出しのために入れ替えられる、これにより、本発明のシステムは、データのセンス信号とリファレンスセルのセンス信号が互いに追尾することを可能にさせることによって、2回目の読み出しのための回復時間を短縮する。与えられた電圧アンダーシュートの追尾は、2回目の読み出しを進め、従来のシステム及び方法よりも非常に高速に実行できるようにするために、センスデータ電圧信号を望ましいレベルに到達させる。

#### 【0026】

かくして、本発明のシステムは、2ビット型メモリセル内の2ビットが読み出し間に最小限の回復時間で読み出されるので、高速読み出しアクセス時間を達成し、同時に、データ値を読み出す際に、メモリセルの時間的な特性変化とは無関係に望ましい精度が得られる。

#### 【0027】

本発明の上記並びに関連した効果及び特徴は、以下の本発明の詳細な説明を添付図面と併せて精査することによって明らかになるであろう。尚、添付図面を通じて、類似の番号は類似の構成要素を表している。

#### 【0028】

##### 【発明の実施の形態】

本発明は、2ビット型セルにおける2回目の読み出しの回復時間を短縮するリファレンスセル入れ替え用のシステムを対象とする。本発明は、2ビット型セルに対し2回の読み出しを実行するため総アクセス時間を著しく短縮する効果を奏する。本発明は、障害、充電損失、及び、その他の変化に起因してメモリの耐用期間中に亘って生じるセル特性の変化を考慮に入れて、2ビット型セルのデータをメモリセルの耐用期間中に正確に読み出すことを可能にさせると共に、この読み出し時間を短縮する更なる効果を奏する。

#### 【0029】

以下、図5及び6を参照して本発明を説明する。図5は、本発明の一実施例の略構成図である。図5に示されたセンス回路100は、センスアンプ22に接続されたデータ回路30と、リファレンスセンスアンプ24に接続されたリファレンス回路70とを含む。図3の回路20と同じように、図5において、ラインS A 1上のセンスアンプ22の出力、及び、ラインS A R 1上のセンスアンプ24の出力は、比較器26の入力へ接続される。回路100の場合、データ回路30は、図3に関して説明したような回路である。

#### 【0030】

図3の回路20と回路100の相違点は、データ回路30内のコアセル10に関してドレイン端子とソース端子が入れ替えられるのと全く同様に、回路100がリファレンス回路70内のリファレンスセルのソース端子とドレイン端子を入れ替えることである。図5に示されたシステムのリファレンス回路70とデータ回路30の両方でソースとドレインを入れ替える結果として、2回目の読み出しへの移行中に起こる電圧降下は、後述するように、データセルとリファレンスセルの両方に適用可能である。図5に示された実施例において、データ回路30と、関連したコアセル10のドレインとソースの入れ替えは、図3

10

20

30

40

50

に関して説明した通りである。次に、図5に示された回路のための参照セル入れ替えについて説明する。

### 【0031】

図5に示されるように、リファレンス回路70は、リファレンスワードラインに接続された制御ゲートと、ノード75に接続されたドレインと、ノード73でバストランジスタ54のドレインに接続されたソースとを具備するリファレンスセル72を含む。図5には、(例えば、REF1のような第1の閾値のための)1個のリファレンス回路70と、センスアンプ24と、比較器26が示されているが、回路100は、第2のリファレンス閾値REF2のための第2のリファレンスセルと関連した同一の回路(図示せず)を含む。かくして、各データビットは、セルデータを決定するため、2個の検出されたリファレンス閾値と別々に比較される。リファレンス回路70では、2個のトランジスタ56及び76がノード75とセンスアンプ24の入力との間に直列接続される。トランジスタ54、56のゲートはVCCに接続される。トランジスタ54のソースは、トランジスタ78のドレインでノード71に接続される。トランジスタ78のソースは、図5にリファレンス信号DATA1として示されているように、ノード77でセンスアンプ24の入力に接続される。トランジスタ78は、「2番目のライン」に接続されたゲートを具備する。この2番目のラインは、データ回路30に関して説明したような制御回路(図示せず)によって駆動され、2ビット型リファレンスセルの2ビットのうちの第2ビット(リファレンス相補ビット)を読み出すためのパスの選択を制御する。2番目のラインがアクティブ状態であるとき、2番目のラインは、リファレンスセル72のソース端子からトランジスタ54及び78を介してノード77への接続パスを準備することによってリファレンス相補ビットを選択する。これにより、第2のリファレンス閾値ビットは、データセンスアンプ24への入力でDATA1ビットラインへ接続される。ノード71はトランジスタ74のドレインにも接続される。トランジスタ74のソースは接地され、ゲートは「2番目のバーライン(2番目のラインの反転ライン)」に接続される。上述の通り、1番目の信号及び2番目のバー信号は、このようにしてノーマルビットの読み出しの際にアクティブ状態になり、2番目の信号及び1番目のバー信号は、相補ビットの読み出しの際にアクティブ状態になる。VCC信号及びリファレンスワードライン(WL)信号は、コアセル10が選択されているときにアクティブ状態になる。トランジスタ74は、第1の(ノーマル)リファレンス閾値を読み出すためグラウンドへのパスを準備する。

### 【0032】

図5に示されているように、ノード77は、データセンスアンプ24への入力でDATA1ビットラインに接続される。トランジスタ76は、ノード77に接続されたドレインを具備する。トランジスタ76のゲートは、1番目のラインに接続される。この1番目のラインは、2つのリファレンス閾値ビットのうちの第1(ノーマル)のリファレンス閾値ビットを選択するための制御を行う。1番目のラインがセットされたとき、トランジスタ76は、リファレンスセル72からの第1の(ノーマル)リファレンス閾値ビットがデータビットとの比較のためにデータセンスアンプ24で検出できるように、(トランジスタ56を通る)パスを設定すべく導通する。トランジスタ76のソースは、ノード79でトランジスタ56のドレインと接続される。ノード79は、トランジスタ82のドレインにも接続される。トランジスタ82のソースは接地され、ゲートは1番目のバーラインに接続される。トランジスタ82は、第2の(相補)閾値を読み出すため要求されるリファレンスセル72のドレインの接地を行う。

### 【0033】

次に、図5及び6を参照して、センス回路100の動作を更に説明する。図5に対応した方法の場合、各ビット(ノーマルビット及び相補ビット)は、2個のリファレンスセルと共に読み出される。各ビットの電圧と2個の読み出されたリファレンスセルの電圧との比較によって、実際のコアセルデータが決まる。図5に示された回路の場合、ノーマルビット及び相補ビットは、同時に読み出すことができない。なぜならば、ノーマルビットの読み出し後に第2の(相補)ビットを読み出すためには、ソースとドレインを入れ替える必

10

20

30

40

50

要があるからである。回路 100 の 2 ビット型セルにおいて両方のビットを獲得するためには、ノーマルビット（及びリファレンスセル）のための 1 回目の読み出しと、相補ビット（及びリファレンスセル）のための 2 回目の読み出しの 2 回の別々の読み出しが必要である。

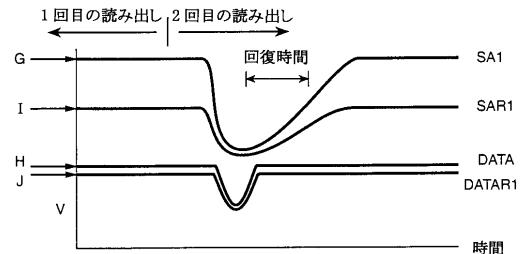

#### 【 0 0 3 4 】

図 6 は、図 5 に示された本発明の回路 100 における回復時間の短縮を説明するための電圧の時間的な変動を表すタイミングチャートである。図 6 における軌跡 G は、図 5 に示された回路におけるデータセンスアンプ 22 の出力のセンスアンプ信号（S A 1）を表す。軌跡 H は、ビットラインにおける対応したデータ（D A T A 1）を表す。トレース I は、リファレンスセンスアンプ 24 からの S A R 信号に対する電圧を表す波形である。軌跡 J は、センスアンプ 24 へ入力されるリファレンスセルデータ電圧（D A T A R）を表す波形である。

#### 【 0 0 3 5 】

図 5 に示された実施例の場合、2 回目の読み出しの際に、データセル 10 のソースとドレインを入れ替えることに加えて、リファレンスセル 72 のソースとドレインも入れ替えられる。図 6 に示されるように、回路 70 におけるリファレンスビットの 1 回目の読み出しから 2 回目の読み出しへの移行中に、リファレンス側で非常に大きい電圧降下アンダーシュートが発生する。上述の通り、回路 30 のためのドレインとソースが入れ替えられるので、同様の非常に大きい電圧降下アンダーシュートがコアセル側の 1 回目の読み出しから 2 回目の読み出しへの移行中に発生する。図 6 に示されるように、センス信号 S A 1 及び S A R 1 は、共に、1 回目の読み出し後にこのアンダーシュートを生じ、センス信号 S A 1 と S A R 1 は、図 4 に示された対応したセンス信号 S A と S A R よりも近い軌跡を通る。2 回目の読み出しの前に必要とされる回復時間は、信号 S A 1 と信号 S A R 1 の間に十分なマージンが存在するかどうかに依存して満たされる。このマージンが出現すると、2 回目の読み出しの条件が満たされる。図 6 に示されるように、信号 S A R 1 は、信号 S A 1 に生じる電圧降下と同じ相対的な電圧降下が生じるので、図 5 の回路 100 におけるこのマージンは、図 3 の回路 22 におけるマージンよりも遙かに迅速に現れる。したがって、図 5 に示された実施例の場合、2 回目の読み出しのための回復時間は最小限に抑えられる。図 4 に示されるように、センス回路 20 では、このような追従が得られないので、回復時間は増加し、2 回目の読み出し時間は非常に遅れる。これに対して、本発明の場合、第 1 の所定のリファレンス閾値（R E F 1 として記されている）のためプログラムされた一方のリファレンスセルと、第 2 の所定のリファレンス閾値（R E F 2 として記されている）のためプログラムされたもう一方のリファレンスセルの 2 個のリファレンスセルが設けられている。各リファレンスセルは、ノーマルビットと相補ビットを含む 2 ビット型セルである。コアセル閾値と各ビットとの比較を行うため、ノーマルビット及び相補ビットは、共に、セル内で同じ閾値（例えば、一方のリファレンスセルのための閾値 R E F 1 及びもう一方のリファレンスセルのための閾値 R E F 2 ）までプログラムされる。上述の通り、図 5 には、（例えば、第 1 の閾値 R E F のための）1 個のリファレンス回路と、センスアンプ 24 と、比較器 26 だけが示されているが、回路 100 は、第 2 のリファレンス閾値 R E F 2 用の第 2 のリファレンスセルに関連した同じ回路（図示せず）を含む。第 2 のリファレンス回路の場合、リファレンスのノーマルビット及び相補ビットは、同一の所定の閾値（例えば、R E F 2 ）に設定される。特定のメモリセル、並びに、2 ビット型セルにおける特定のビットのアドレス指定及び選択の制御に関する詳細は明らかにされていないが、このような詳細は当業者にとって公知の事項であろう。

#### 【 0 0 3 6 】

図 5 に示された本発明のリファレンスセル入れ替えシステムは、2 回目の読み出しへの移行中に、セル特性の時間的な変化を考慮して、リファレンスセンス信号 S A R 1 とコアセル・センス信号 S A 1 との間でより良好な追従を実現することにより、2 回目の読み出し時間を著しく短縮する効果を奏する。

#### 【 0 0 3 7 】

10

20

30

40

50

本発明は典型的な実施例に関して記述されているが、本発明が上述の実施例に限定されることなく、典型的な実施例の変更が請求項に記載された事項の精神及び範囲を逸脱すること無くなされることは、当業者に明らかであろう。したがって、以上の記述は、限定的な記述ではなく、例示的な記述であることに注意する必要がある。

【0038】

以上の説明に関して更に以下のような態様が考えられる。

【0039】

(付記1) ノーマルビットである第1のビット及び相補ビットである第2のビットの2ビットを電圧閾値として記憶する2ビット型コアセルと、

2ビット型コアセルと関連した2個の2ビット型リファレンスセルと、

を含み、

10

各2ビット型リファレンスセルは、所定のリファレンス閾値として第1のリファレンスピット及び第2のリファレンスピットを記憶している、

記憶装置の2ビット型コアセルを読み出す方法であって、

コアセルの第1のビットを読み出す手順と、

各2ビット型リファレンスセルの第1のリファレンスピットを読み出す手順と、

コアセルの第1のビットを、2個の2ビット型リファレンスセルの各々の第1のリファレンスピットと同時に比較する手順と、

コアセルの第2のビットを読み出す手順と、

各2ビット型リファレンスセルの第2のリファレンスピットを読み出す手順と、

20

コアセルの第2のビットを、2個の2ビット型リファレンスセルの各々の第2のリファレンスピットを同時に比較する手順と、

を有し、

比較の結果に基づいて、2ビット型コアセルのビットの2進数値が決定される、

方法。

【0040】

(付記2) 記憶装置は不揮発性半導体装置である、付記1記載の方法。

【0041】

(付記3) 記憶装置はフラッシュメモリである、付記2記載の方法。

【0042】

30

(付記4) 第1のリファレンスピットはノーマルビットであり、第2のリファレンスピットは相補ビットである、付記1記載の方法。

【0043】

(付記5) 2ビット型コアセルは、ソース端子、ドレイン端子及びゲート端子を具備し、

コアセルの第2のビットを読み出す手順は、コアセルが第1のビットを読み出す方向とは逆の方向へ読み出されるように、2ビット型コアセルのソース端子とドレイン端子を入れ替える手順を含む、

付記4記載の方法。

【0044】

40

(付記6) 2ビット型コアセルのソース端子とドレイン端子を入れ替える手順は電圧アンダーシュートを生じさせる、付記5記載の方法。

【0045】

(付記7) 2ビット型リファレンスセルは、ソース端子、ドレイン端子及びゲート端子を含み、

第2のリファレンスピットを読み出す手順は、各2ビット型リファレンスセルが第1のリファレンスピットを読み出す方向とは逆の方向へ読み出されるように、各2ビット型リファレンスセルのソース端子とドレイン端子を入れ替える手順を含む、

付記6記載の方法。

【0046】

50

(付記 8) 2 ビット型リファレンスセルのソース端子とドレイン端子を入れ替える手順は電圧アンダーシュートを生じさせる、付記 7 記載の方法。

【0047】

(付記 9) 2 ビット型リファレンスセルのソース端子とドレイン端子を入れ替えることにより生じた電圧アンダーシュートは、2 ビット型コアセルの第 2 のビットの読み出し前に要する回復時間が最小限に抑えられるように、2 ビット型コアセルのソース端子とドレイン端子を入れ替えることにより生じた電圧アンダーシュートに追従する、付記 8 記載の方法。

【0048】

(付記 10) 2 ビット型フラッシュメモリの第 2 のビットを読み出すためのアクセス時間が最小限に抑えられるように 2 ビット型メモリセルの 2 ビットを読み出す回路であって、

電圧閾値としてノーマルビット及び相補ビットを記憶する 2 ビット型記憶セルと、第 1 の 2 ビット型リファレンスセル及び第 2 の 2 ビット型リファレンスセルと、を含み、

各 2 ビット型リファレンスセルは、ノーマルビットである第 1 のリファレンスピットと相補ビットである第 2 のリファレンスピットの 2 個のリファレンスピットを記憶し、

第 1 の 2 ビット型リファレンスセルのノーマルビット及び相補ビットは第 1 の所定のリファレンス閾値として記憶され、

第 2 の 2 ビット型リファレンスセルのノーマルビット及び相補ビットは第 2 の所定のリファレンス閾値として記憶され、

2 ビット型記憶セルのノーマルビット及び相補ビットと第 1 の所定のリファレンス閾値との差、並びに、2 ビット型記憶セルのノーマルビット及び相補ビットと第 2 の所定のリファレンス閾値との差を検出し増幅するセンスアンプ回路が設けられ、

ノーマルビットと相補ビットがセンスアンプ回路へ供給されるように、記憶セルとセンスアンプ回路の間にコネクションを設定する複数のトランジスタを備えたデータ回路が設けられ、

第 1 のリファレンス回路及び第 2 のリファレンス回路が設けられ、

各リファレンス回路は、各リファレンスセルの所定のリファレンス閾値がセンスアンプ回路へ供給されるように、対応したリファレンスセルとセンスアンプ回路の間にコネクションを設定する複数のトランジスタを備え、

対応した記憶セルのノーマルビット及び相補ビット、並びに、対応したリファレンスセルのノーマルビット及び相補ビットは、順番に読み出され、リファレンス回路及びデータ回路は、各相補ビットが、対応したノーマルビットが読み出された後に、対応したノーマルビットが読み出された方向とは逆の方向に読み出され、

これにより、記憶セルのノーマルビットと相補ビットの読み出しの間に電圧オーバーシュートが発生し、各 2 ビット型リファレンスセルのノーマルビットと相補ビットの読み出しの間に対応した電圧オーバーシュートが発生し、記憶セルの相補ビットの読み出しのための回復時間が最小限に抑えられている、

回路。

40

【0049】

(付記 11) 2 ビット型記憶セル及び 2 ビット型リファレンスセルは、それぞれ、ソース端子とドレイン端子と制御ゲート端子を具備している、付記 10 記載の回路。

【0050】

(付記 12) センスアンプ回路は、複数のセンスアンプと複数の比較器を含む、付記 10 記載の回路。

【0051】

(付記 13) センスアンプは、データ回路に接続された第 1 のセンスアンプと、第 1 のリファレンス回路に接続された第 2 のセンスアンプと、

50

第2のリファレンス回路に接続された第3のセンスアンプと、

第1のセンスアンプ及び第2のセンスアンプに接続され、記憶セルのノーマルビット及び

相補ビットを、第1の所定のリファレンス閾値と比較する第1の比較器と、

第1のセンスアンプ及び第3のセンスアンプに接続され、記憶セルのノーマルビット及び

相補ビットを、第2の所定のリファレンス閾値と比較する第2の比較器と、

を含む。

付記12記載の回路。

【0052】

(付記14) 第1のリファレンス回路及び第2のリファレンス回路の対応した複数のトランジスタは、対応したリファレンスビットがセンスアンプ回路によって検出されるよう10

に向きが合わされている、付記13記載の回路。

【0053】

(付記15) 第1のリファレンス回路及び第2のリファレンス回路の複数のトランジスタは、各リファレンスセルのノーマルビットを読み出す際に、対応したリファレンスセルのソース端子とグラウンドの間、並びに、対応したリファレンスセルのドレイン端子とセンスアンプ回路の間にパスが設定され、各リファレンスセルの相補ビットを読み出す際に、対応したリファレンスセルのドレイン端子とグラウンドの間、並びに、対応したリファレンスセルのソース端子とセンスアンプ回路の間にパスが設定されるように制御される、付記14記載の回路。

【0054】

(付記16) 記憶セルのノーマルビットの読み出しと対応した相補ビットの読み出しの間に電圧オーバーシュートが発生し、

リファレンスセルのノーマルビットの読み出しと対応した相補ビットの読み出しの間に対応した電圧オーバーシュートが発生し、

記憶セルの相補ビットの読み出しに要する回復時間が最小限に抑えられている、

付記15記載の回路。

【0055】

(付記17) データ回路の複数のトランジスタは、記憶セルのソースとグラウンドの間、並びに、記憶セルのドレインと第1のセンスアンプの間にパスを設定し、これにより、記憶セルの相補ビットの読み出しが行えるようになる、付記13記載の回路。

【0056】

(付記18) 第1のリファレンスビットはノーマルビットであり、第2のリファレンスビットは相補ビットであり、

2ビット型コアセルは、ソース端子、ドレイン端子及びゲート端子を具備し、

コアセルの第2のビットを読み出す手順は、コアセルが第1のビットを読み出す方向とは逆の方向へ読み出されるように、2ビット型コアセルのソース端子とドレイン端子を入れ替える手順を含み、

2ビット型リファレンスセルは、ソース端子、ドレイン端子及びゲート端子を含み、第2のリファレンスビットを読み出す手順は、各2ビット型リファレンスセルが第1のリファレンスビットを読み出す方向とは逆の方向へ読み出されるように、各2ビット型リファレンスセルのソース端子とドレイン端子を入れ替える手順を含み、

2ビット型リファレンスセルのソース端子とドレイン端子を入れ替えることにより生じた電圧アンダーシュートは、2ビット型コアセルの第2のビットの読み出し前に要する回復時間が最小限に抑えられるように、2ビット型コアセルのソース端子とドレイン端子を入れ替えることにより生じた電圧アンダーシュートに追従する、

付記1記載の方法。

【0057】

(付記19) 電圧閾値としてノーマルビット及び相補ビットを記憶する2ビット型記憶セルと、

第1の2ビット型リファレンスセル及び第2の2ビット型リファレンスセルと、

10

20

30

40

50

を含み、

各 2 ビット型リファレンスセルは、ノーマルビットである第 1 のリファレンスピットと相補ビットである第 2 のリファレンスピットの 2 個のリファレンスピットを記憶し、

第 1 の 2 ビット型リファレンスセルのノーマルビット及び相補ビットは第 1 の所定のリファレンス閾値として記憶され、

第 2 の 2 ビット型リファレンスセルのノーマルビット及び相補ビットは第 2 の所定のリファレンス閾値として記憶され、

2 ビット型記憶セルのノーマルビット及び相補ビットと第 1 の所定のリファレンス閾値との差、並びに、2 ビット型記憶セルのノーマルビット及び相補ビットと第 2 の所定のリファレンス閾値との差を検出し増幅するセンスアンプ回路が設けられ、

10

ノーマルビットと相補ビットがセンスアンプ回路へ供給されるように、記憶セルとセンスアンプ回路の間にコネクションを設定する複数のトランジスタを備えたデータ回路が設けられ、

第 1 のリファレンス回路及び第 2 のリファレンス回路が設けられ、

各リファレンス回路は、各リファレンスセルの所定のリファレンス閾値がセンスアンプ回路へ供給されるように、対応したリファレンスセルとセンスアンプ回路の間にコネクションを設定する複数のトランジスタを備え、

対応した記憶セルのノーマルビット及び相補ビット、並びに、対応したリファレンスセルのノーマルビット及び相補ビットは、順番に読み出され、リファレンス回路及びデータ回路は、各相補ビットが、対応したノーマルビットが読み出された後に、対応したノーマルビットが読み出された方向とは逆の方向に読み出され、

20

これにより、記憶セルのノーマルビットと相補ビットの読み出しの間に電圧オーバーシュートが発生し、各 2 ビット型リファレンスセルのノーマルビットと相補ビットの読み出しの間に対応した電圧オーバーシュートが発生し、記憶セルの相補ビットの読み出しのための回復時間が最小限に抑えられている、

半導体記憶装置。

#### 【0058】

#### 【発明の効果】

本発明によれば、不揮発性記憶装置において 2 ビット型メモリセルの 2 回目の読み出しの回復時間を短縮することにより、2 回の読み出しを実行するためのアクセス時間を高速化することが可能である。

30

#### 【図面の簡単な説明】

【図 1】本発明と同じ 2 ビット型コアセル構造の略構成図である。

【図 2 A】2 ビット型セルの閾値分布の時間的な変動を示す二つの例示的な波形のタイミングチャートである。

【図 2 B】セルデータを決定するための相補ビット及び参照セルの使用法を説明する図表である。

【図 3】センス回路構造の略構成図である。

【図 4】第 2 ビットの読み出しの実行用の電圧の時間変動を表すタイミングチャートである。

40

【図 5】本発明の回路の一実施例の略構成図である。

【図 6】図 5 に示された本発明の一実施例の 2 回目の読み出しに対する縮小された回復時間を示す電圧の時間変動を表すタイミングチャートである。

#### 【符号の説明】

1 0 コアセル

2 2 センスアンプ

2 4 リファレンスセンスアンプ

2 6 比較器

3 0 データ回路

3 2 , 3 4 , 3 6 , 3 8 , 4 2 , 4 4 , 5 4 , 5 6 , 7 2 , 7 4 , 7 6 , 7 8 , 8 2

50

## トランジスタ

3 3 , 3 5 , 3 7 , 7 1 , 7 3 , 7 5 , 7 7 , 7 9 ノード

7 0 リファレンス回路

7 2 リファレンスセル

1 0 0 センス回路

【図1】

本発明と同じ2ビット型コアセル構造の略構成図

【図2 B】

セルデータを決定するための相補ビット及び参照セルの使用法を説明する図表

| ノーマルビット  | 相補ビット    | セル  |

|----------|----------|-----|

| リファレンス 1 | リファレンス 2 | データ |

| 1        | 1        | 1   |

| 0        | 1        | 1   |

| 0        | 1        | 0   |

| 0        | 0        | 0   |

【図2 A】

2ビット型セルの閾値分布の時間的な変動を示す二つの例示的な波形のタイミングチャート

【図3】

センス回路構造の略構成図

【図4】

第2ビットの読み出しの実行用の電圧の時間変動を表すタイミングチャート

【図6】

図5に示された本発明の一実施例の2回目の読み出しに対する縮小された回復時間を示す電圧の時間変動を表すタイミングチャート

【図5】

本発明の回路の一実施例の略構成図

---

フロントページの続き

(56)参考文献 特開2003-068087(JP,A)

特開平04-064997(JP,A)

特開昭64-023500(JP,A)

特表2001-512290(JP,A)

特開2001-028196(JP,A)

特開平08-190797(JP,A)

特表2005-526341(JP,A)

(58)調査した分野(Int.Cl., DB名)

G11C 16/02-16/06