(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5342143号

(P5342143)

(45) 発行日 平成25年11月13日(2013.11.13)

(24) 登録日 平成25年8月16日(2013.8.16)

(51) Int.Cl.

F 1

|               |           |               |   |

|---------------|-----------|---------------|---|

| HO 1 L 21/02  | (2006.01) | HO 1 L 27/12  | B |

| HO 1 L 27/12  | (2006.01) | HO 1 L 21/20  |   |

| HO 1 L 21/20  | (2006.01) | HO 1 L 21/205 |   |

| HO 1 L 21/205 | (2006.01) |               |   |

請求項の数 5 (全 15 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2007-546681 (P2007-546681)  |

| (86) (22) 出願日 | 平成17年11月18日 (2005.11.18)      |

| (65) 公表番号     | 特表2008-525998 (P2008-525998A) |

| (43) 公表日      | 平成20年7月17日 (2008.7.17)        |

| (86) 國際出願番号   | PCT/US2005/041889             |

| (87) 國際公開番号   | W02006/065444                 |

| (87) 國際公開日    | 平成18年6月22日 (2006.6.22)        |

| 審査請求日         | 平成20年11月18日 (2008.11.18)      |

| (31) 優先権主張番号  | 11/014,574                    |

| (32) 優先日      | 平成16年12月16日 (2004.12.16)      |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                       |

|-----------|-------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 500517248<br>イスコンシン アラムニ リサーチ フ<br>アンデーション<br>アメリカ合衆国 ウィスコンシン州 53<br>707-7365 マディソン ピー<br>オーブックス 7365 |

| (74) 代理人  | 100082005<br>弁理士 熊倉 賢男                                                                                |

| (74) 代理人  | 100067013<br>弁理士 大塚 文昭                                                                                |

| (74) 代理人  | 100065189<br>弁理士 宍戸 嘉一                                                                                |

| (74) 代理人  | 100088694<br>弁理士 弟子丸 健                                                                                |

最終頁に続く

(54) 【発明の名称】ひずみヘテロ接合構造体の製造

## (57) 【特許請求の範囲】

## 【請求項 1】

デバイスが形成されるひずみ結晶層を形成する方法であって、

(a) 結晶テンプレート層の一方の側に材料の層を成長させて多層構造体を形成し、前記結晶テンプレート層はその他の側でハンドル層を有する基板の犠牲層によって支持され、前記材料の層及び前記結晶テンプレート層は、前記材料の層が成長するときにひずむような格子不一致を有し、

(b) 前記犠牲層の一方の側に隣接した材料をパターニングし且つエッチングして前記犠牲層の領域を露出させ、

(c) 前記犠牲層の露出した領域で前記犠牲層を選択的にエッチングして、前記材料の層のひずみが緩和し、さらに前記材料の層が緩和するときに前記結晶テンプレート層がひずむように多層構造体を剥離する方法。

## 【請求項 2】

デバイスが形成されるひずみ結晶シリコン層を形成する方法であって、

(a) シリコンオンインシュレータ基板のシリコンテンプレート層の一方の側にシリコン-ゲルマニウム合金の層を成長させて多層構造体を形成し、前記シリコンオンインシュレータ基板は、前記シリコン-ゲルマニウム合金の層が、成長するとき圧縮ひずみ状態にあるように、他方の側で、シリコンハンドル層の上に形成される二酸化シリコンの犠牲層上で支持された前記シリコンテンプレートの層を含み、

(b) 前記犠牲層の一方の側に隣接した材料をパターニングし且つエッチングして前記

10

20

二酸化シリコンの犠牲層の領域を露出させ、

(c) 前記シリコン-ゲルマニウム合金の層のひずみが緩和され且つ前記シリコン-ゲルマニウム合金の層が緩和するとき、前記シリコンテンプレートの層がひずまされるよう

に前記二酸化シリコンの犠牲層を選択的にエッチングして多層構造体を剥離する方法。

【請求項3】

ひずみ多層半導体構造体であって、

(a) 引っ張りひずみ結晶シリコンの最下層と、

(b) 前記結晶シリコンの最下層の上にあり、構造体内で転位を発生させる塑性緩和が生じる厚さよりも薄い部分的圧縮ひずみ緩和シリコン-ゲルマニウム合金の層と、

(c) 前記部分的圧縮ひずみ緩和シリコン-ゲルマニウム合金の層の上の引っ張りひずみ結晶シリコンの最上層と、を備え、

前記多層半導体構造のひずみ状態は、層の間の弾性ひずみの分配によって得られ、前記多層半導体構造は、さらに、前記多層半導体構造がエピタキシャル成長された下部基板から完全に剥離されている、ひずみ多層半導体構造体。

【請求項4】

ひずみ多層半導体構造体であって、

(a) 引っ張りひずみ結晶シリコンの最下層と、

(b) 前記結晶シリコンの最下層の上にあり、構造体内で転位を発生させる塑性緩和が生じる厚さよりも薄い部分的圧縮ひずみ緩和シリコン-ゲルマニウム合金の第1の層と、

(c) 前記部分的圧縮ひずみ緩和シリコン-ゲルマニウム合金の第1の層の上の引っ張りひずみ結晶シリコンの第2の層と、

(d) 引っ張りひずみ結晶シリコンの前記第2の層の上の部分的圧縮ひずみ緩和シリコン-ゲルマニウム合金の第2の層であって、前記部分的圧縮ひずみ緩和シリコン-ゲルマニウム合金の第2の層のGe含有量は、前記部分的圧縮ひずみ緩和シリコン-ゲルマニウム合金の第1の層のGe含有量と同じ或いはそれよりも高い第2の層と、

(e) 前記部分的圧縮ひずみ緩和シリコン-ゲルマニウム合金の第2の層の上の引っ張りひずみ結晶シリコンの層を含み、

前記多層半導体構造のひずみ状態は、層の間の弾性ひずみの分配によって得られ、前記多層半導体構造は、さらに、前記多層半導体構造がエピタキシャル成長された下部基板から完全に剥離されている、ひずみ多層半導体構造体。

【請求項5】

デバイスが形成されるひずみ結晶層を形成する方法であって、

(a) 結晶テンプレート層の一方の側にエピタキシャル法で第1の材料層を、前記第1の材料層が可塑的に緩和し且つ転位を発生し始める有効臨界膜厚以下の厚さまで成長させ、

前記結晶テンプレート層は、その他の側でハンドル層を有する基板の犠牲層によって支持され、前記第1の材料層及び前記結晶テンプレート層は、前記第1の材料層が成長するときに圧縮的にひずむような格子不一致を有し、

(b) 前記第1の材料層の上にエピタキシャル法で最上部の材料層を、前記最上部の材料層が可塑的に緩和し且つ転位を発生し始める有効膜厚以下の厚さまで成長させ、前記第1の材料層及び最上部の材料層は、テンプレート層を有する多層構造体を形成し、

(c) 前記犠牲層の一方の側に隣接する材料をパターニングし且つエッチングして前記犠牲層の領域を露出させ、

(d) 前記犠牲層の露出した領域で前記犠牲層を選択的にエッチングさせて、前記第1の材料層のひずみが緩和され且つ前記第1の材料層が緩和するときに前記結晶テンプレート層及び前記最上部の材料層がひずむように前記多層構造を剥離する方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般的に、半導体加工の技術、特にひずみヘテロ接合半導体構造体の形成に

10

20

30

40

50

関する。

【背景技術】

【0002】

ヘテロエピタキシャル半導体構造体のひずみと欠陥の数及び種類とを制御することは、高性能デバイスを形成するための好ましい特性を有する高品質半導体材料を得るために極めて重要である。シリコン／シリコン-ゲルマニウムヘテロシステムでは、半導体層のひずみの適切な制御は、バンドオフセット及びキャリア移動度に対する制御を提供する。代表的には、薄いひずみSi膜が形成される、ひずみ緩和SiGe仮想基板を得ることができるのが望ましい。高品質ひずみシリコンを得ることの主な障害は、最初に、完全ひずみ緩和SiGe膜を得ることにある。SiGe膜を緩和させるための代表的な方法は、厚いひずみグレーデッドSiGeをバルクシリコン基板に成長させることである。係る構造体では、緩和は、SiGe膜の中の転位の移動によって起る。層間のインターフェイスにおけるミスフィット転位は、ひずみ層のひずみを緩和する。転位駆動型緩和の難しさは、全てのミスフィット転位が、転位と関連した二つのスレッディングアームを有することである。スレッディングアームは、ひずみSi層を含む、膜システム全体を通して延びていて、キャリア移動度を劣化する。注意深く工作されたグレーデッドSiGe基板の転位の密度は、ひずみSiデバイスを生成するために十分に低いが、それにもかかわらず、転位が全くないか或いは転位がほとんどないSiGe基板を提供することができるのが好ましい。グレーデッドSiGe基板の使用の更なる制限は、Si層で少ない転位を達成するために、かなり厚いグレーデッドSiGe膜を成長させることが必要である、ということである。しかしながら、比較的厚い膜は、異なるひずみ状態にある隣接デバイスを有することを難しくする。緩和バッファ層を成長させることの別の重要性は、緩和加工が表面上に転位ループの開口を通してステップを起すということである。これらのステップは、一緒にになってこぶ(バンチ)になる傾向を有し、粗い成長界面を引き起す。シリコン層を成長させる前に研磨及び洗浄ステップを行わなければならないので、加工に対して費用が加わる。また、グレーデッド層の熱伝導率も悪くなる。

【発明の開示】

【発明が解決しようとする課題】

【0003】

転位に基づく緩和の制限を克服するための一つの方法では、転位なくひずみ制御を達成する方法としてコンプライアント基板が提案されている。コンプライアント基板は、厚い硬質基板によって支持された非常に薄いひずみ層システムで構成される。ひずみシステムは、コンプライアント基板上を滑ることによって異なる層の厚さに基づいてひずみを分配するものである。コンプライアントシステムでは、層の全ては、同じ面内格子定数を有するが異なるひずみ状態にある。コンプライアント基板方法による問題は、真のコンプライアント基板を達成することがかなり難しいということである。なぜならば、そのようにするには、ひずみシステムとコンプライアント層の間で大規模な滑りを必要とするからである。

【0004】

高コンプライアント基板の効果を得るための別な方法は、各メサを中央台座によって支持させておくようにアンダーカットされるパターン化されたメサを形成することにある。すると、メサは、SiGe成長のための自立基板として作用することができる。P.N. Mooney, 等による「自立SiGe構造体の弾性ひずみ緩和」, Applied Physics Letters, Vol. 84, No. 7, 16 February 2004, pp. 1093-1095. この方法で形成された支持メサは、位置が固定され且つデバイス形成に利用可能な表面積が制限される。

【課題を解決するための手段】

【0005】

本発明によれば、多層膜の成長は、成長層のひずみの厳密な制御及び成長膜の完全な剥離を可能にして選択された基板に剥離された多層構造体の取付けを可能にする方法で行なわれる。剥離された多層構造体は、永久基板の好ましい位置に配置することができる離散

的個別区分として形成することができ、或いは、構造体は、非平坦面を有する基板を含む、大面積基板の上に取付けることができる大きな、軟質膜として剥離することができる。本発明は、隣接層の一つ或いは両方がキャリア移動度をかなり増すようにひずまされる、ヘテロ接合を利用する、改良された特性を有する電子デバイスの製造を可能にする。本発明を利用して形成されるデバイスの例は、最終ひずみ状態が膜間で分配する弾性ひずみによって達成されるシリコン - ゲルマニウム合金を有するキャリアチャネルクラッドとしてひずみシリコン層を利用する、高移動度変調ドープ電界効果トランジスタ、及びキャリア移動度の増大によりより速いスピードを有する画像形成及び計算装置を含む。

## 【 0 0 0 6 】

本発明によるひずみ結晶層を形成する方法では、半導体のような材料の層を、結晶テンプレート層の一方の側で成長させて多層構造体を形成し、テンプレート層は、その他の側で基板の犠牲層によって支持され、成長層及びテンプレート層は、成長層が形成されるときに成長層がひずまされるように格子不一致を有する。結晶材料の最上層を、成長層に形成して成長層及びテンプレート層を有する多層構造体の一部を形成する。次いで、犠牲層の側の一つに隣接した材料を、リソグラフによってパターニングし且つエッティングして犠牲層のエリアを露出させる。次いで、犠牲層を、その露出された領域（エリア）で選択的にエッティングして多層構造体を剥離し、その結果、成長層（及びいかなる結晶最上層）のひずみが緩和され且つ成長層が緩和するときに結晶テンプレート層がひずまされる。

## 【 0 0 0 7 】

本発明の例として、選択されたシリコン対ゲルマニウム比のシリコン - ゲルマニウムの層を、シリコンオンインシュレータ（S O I ）基板のシリコンテンプレート層の上に成長させる。S O I 基板は、結晶シリコンハンドル層、ハンドル層の上の二酸化シリコン（S i O<sub>2</sub>）絶縁体の薄い層、及び二酸化シリコン層の上部側に形成された結晶シリコンの上部テンプレート層を含む。シリコン - ゲルマニウム層は、ゲルマニウムがシリコンよりも大きな格子定数を有するのでそれが成長するときに圧縮的にひずまされる。次いで、初期的にはひずまされていないシリコンの層をシリコン - ゲルマニウム層の上に形成するのがよい。再び圧縮的にひずまされる、シリコン - ゲルマニウムの追加の層を、上部シリコン層の上に成長させるのがよい。更に、シリコンとシリコン - ゲルマニウム或いは他の材料が交互に重なった層を必要に応じて堆積させるのがよい。次いで、二酸化シリコン犠牲層を、選択的にエッティングして多層構造体を剥離するのがよい。次いで、エッティングを可能にすべくS i O<sub>2</sub>犠牲層に接近するために、S i O<sub>2</sub>犠牲層の上の多層ヘテロ構造体の材料を、リソグラフィックパターニング及びエッティングを利用してS i O<sub>2</sub>犠牲層までパターニングし且つエッティングするのがよい。多層構造体のパターニングは、多層構造体の分離した離散アイランド、或いはパターンに形成され、多層構造体を通ってS i O<sub>2</sub>犠牲層まで延びている連続相互接続構造体を画成するために行なわれるがよい。変形例として、ハンドル層の材料を、犠牲層を通してエッティングすることを可能にするS i O<sub>2</sub>犠牲層を露出させる窓を形成するためにリソグラフ的にパターニングするのがよい。多層構造体をハンドル層から剥離するためにS i O<sub>2</sub>犠牲層を選択的にエッティングする（且つエッティング液にさらされた他の層の材料をほとんどエッティングしない）エッティング液を適用して、圧縮的にひずまされたシリコン - ゲルマニウム下部層（及びいかなる追加のシリコン - ゲルマニウム層）を部分的に緩和し且つシリコン - ゲルマニウム下部層に連結されるシリコンテンプレート層（及びいかなる追加のシリコン層）をひずませる。次いで、剥離された多層構造体を、結晶シリコン、二酸化シリコン、サファイア、G a N、等のような選択された基板の表面に転移して取付け、引き続いて、ひずみ層にデバイスを形成するように加工する。二酸化シリコン絶縁層のエッティングは、フッ化水素酸（H F ）のような、液体エッティング液、或いは気相のH F のような、蒸気ベースのエッティング液を用いて行なわれるがよい。

## 【 0 0 0 8 】

シリコンオンインシュレータに加えて、S i G e 膜システムのために、ひずみシリコンオンインシュレータ、シリコンオンサファイア、高濃度ドープ中間層或いは注入層を有す

10

20

30

40

50

るシリコン、シリコン／ゲルマニウムオンインシュレータ、ゲルマニウムオンインシュレータ、等のような、埋込犠牲層を提供するその他の基板を利用することができる。また、本発明は、適当な犠牲層及びエッティング液を利用して、シリコン及びシリコン・ゲルマニウムに加えて他の半導体（例えば、種々のIII-V半導体）、及び種々の強誘電材料、磁性金属、及び酸化物のような、望ましいひずみを有し且つ十分に欠陥のない基板が商業的に入手できない他の材料で利用されてもよい。

【0009】

加工の單一段で得られるひずみレベルよりも大きい最終膜のひずみレベルを達成するために、例えば、シリコン・ゲルマニウム及びシリコン、等の材料の追加層を加えるために加工を繰り返してもよい。

10

【0010】

本発明の更なる目的、特徴及び効果は、添付図面を一緒に参照して以下の詳細な説明から明らかであろう。

【発明を実施するための最良の形態】

【0011】

本発明は、ヘテロ構造体のひずみを制御するための新しい方法を提供する。本発明を例示する目的で、以下は、シリコンオンインシュレータ（SOI）基板の上に形成されそして剥離されるシリコン／シリコン・ゲルマニウムヘテロ構造体の製品を説明するが、本発明は、ここに説明されるようにひずみ制御を必要とするいかなる半導体システム或いはその他の材料システムで実施されてもよい。

20

【0012】

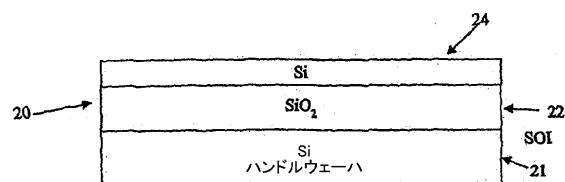

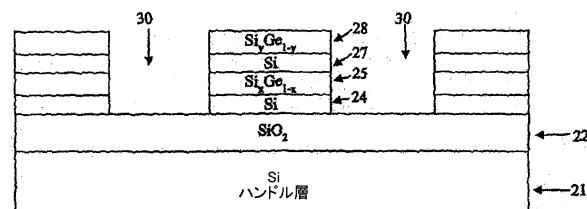

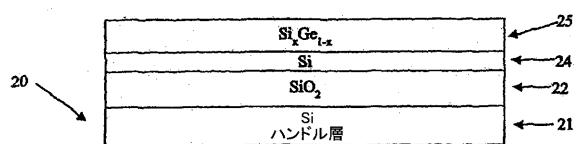

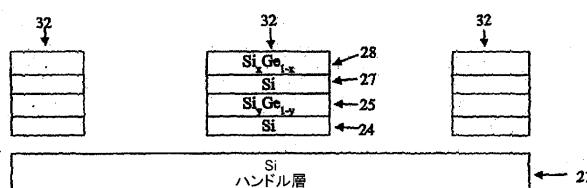

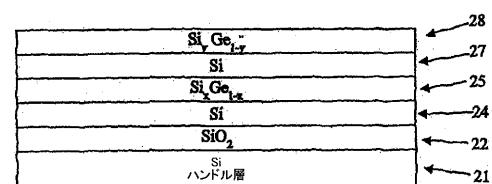

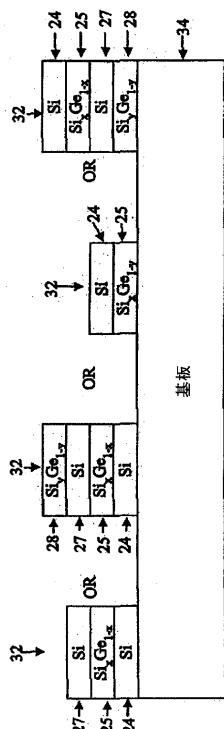

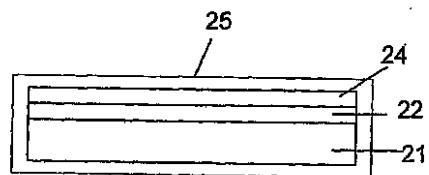

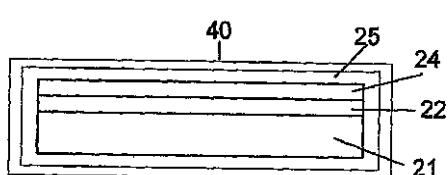

初期SOIウェーハが図1に20で一般的に断面図で示されおり、初期SOIウェーハは、結晶シリコンハンドルウェーハ21、 $\text{SiO}_2$ の絶縁（犠牲）層22、及び典型的には厚さ10～100nmである結晶シリコンのテンプレート層24を含む。図2に示すように、 $\text{SiGe}$ の初期層25を、分子線エピタキシー（MBE）、化学蒸着法（CVD）、スパッタ堆積法、等のような、いかなる適当な加工によって、シリコンテンプレート層24の上にエピタキシャル成長させ、シリコンテンプレート層24との格子不一致のために成長すると $\text{SiGe}$ 層25が内部圧縮ひずみの状態になる。図3に示すように、結晶シリコンの更なる層27を $\text{SiGe}$ 層25の上に成長させ、次いで $\text{SiGe}$ の任意の最上層28を上部シリコン層27の上に成長させてもよい。図示したように、二つのシリコン・ゲルマニウム層25及び28の組成は、同じでなくてもよい。例えば、第2の $\text{SiGe}$ 層28のゲルマニウム含有量は、第1の $\text{SiGe}$ 層25のゲルマニウム含有量よりも高くてよい。次いで、層24、25、好ましくは27（及び任意で28、並びに任意の追加層）を含む多層構造体を、図4に示すように $\text{SiO}_2$ 絶縁層22を露出させる領域30でリソグラフィ的にパターニングし且つエッティングする。次いで、図5に示すように、 $\text{SiO}_2$ を選択的にエッティングするエッティング液を、露出領域30を介して供給して多層構造体32の下の（犠牲層として機能する） $\text{SiO}_2$ 層をエッティングして離し、それにより多層構造体32を犠牲層22及びハンドル層21から剥離する。多層構造体が絶縁層22から離されたとき、 $\text{SiGe}$ 層が緩和すると、ひずみがシリコン層24及び27に転移される。

30

【0013】

次いで、フリーパターニングされた多層構造体32は、図6に示すように永久基板34に転移されて取付けられるのがよい。最初のシリコンハンドル層21及び様々な他の種類の基板を含む、様々な永久基板を利用してよい。様々な他の種類の基板の例としては、ガラス、水素を末端基とするシリコン、熱酸化物を有するシリコン、サファイア、 $\text{GaN}$ 、プラスチック及びグリッドを含む。離した構造体32を、ひずみシリコン層27或いは多層構造体の他の層にデバイスを形成する更なる加工の前に適切な基板に適用してもよい。図6に示すように、多層構造体32を、デバイスが形成される露出層が、シリコン層27、シリコンテンプレート層24、或いはひずみ緩和 $\text{SiGe}$ 層（25又は28）であるように基板34の上に取付けてもよい。また、離した構造体を、犠牲層を有するハンドル

40

50

ウェーハに取付けてもよく、上述した加工を繰り返して、より大きなひずみレベルで第2の（或いは第3の、等）SiGe層の上に成長されたSiを伴って、先に堆積させたSiGe層よりも高いGe含有量を有する追加SiGe層を加える。

【0014】

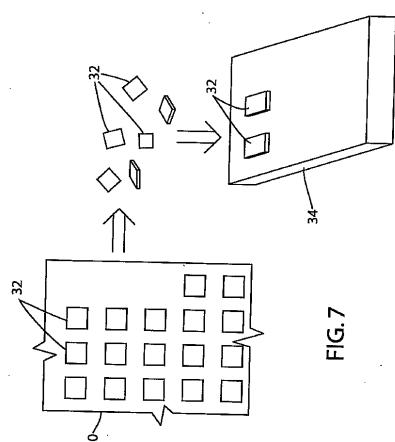

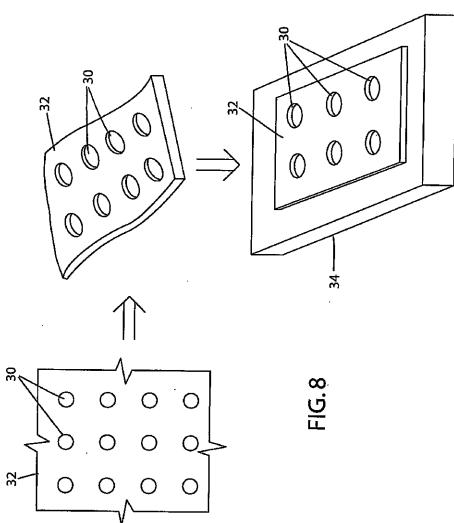

図7に示すように、多層構造体32を、個々の構造体部分32を永久基板34に転移してその上に取付けるために剥離される様々な形状（例えば、正方形、矩形、円板、等）の別々のアイランドとして形成してもよい。変形例として、図8に示すように、多層構造体32を、単一の大面積膜として離されるその中に形成された分離した開口30を形成した連続膜として形成してもよい。次いで、可撓性膜32を、永久基板34の表面に適用してその上に取付けてもよい。

10

【0015】

以下の例は、本発明の特定の実施を示すが、本発明が例に示した特定の材料及び条件に限定されないということは、言うまでもない。

【0016】

超薄Siテンプレート層を有するSOIを、厚さ100nmのSiテンプレート層及び厚さ1.3ミクロンの酸化物層を有する市販されている結合SOIを薄くすることによって準備する。初期の100nmテンプレート層から20nmテンプレート層までSOIを薄くするために、Siテンプレート層の乾燥熱酸化を、1050で3.5時間行った。次いで、熱成長した酸化物を、HFディップによって除去して、20nmのSiテンプレート層を残す。以下の特定の例では、XRD測定を行うのに都合のよいシリコン層の厚さをもたらすために追加の80nmのシリコンをシランガスからテンプレート層の上に成長させるが、係る追加の成長が一般には必要でないことは言うまでもない。

20

【0017】

$Si_{0.90}Ge_{0.10}$ 膜を、コールドウォール式超高真空CVD（UHV-CVD）リアクタで化学蒸着法によりSOI基板のSiテンプレート（層）の上にエピタキシャル成長させた。次いで、Si層をSiGe層の上に成長させた。X線回折測定に適する層の厚さの最終膜構造体は、100nmのSi、該Siの上の200nmの $Si_{0.90}Ge_{0.10}$ 、該 $Si_{0.90}Ge_{0.10}$ の上の100nmのSiで構成される。成長温度を、ストリップを580

まで抵抗加熱することによって制御し且つ背側の光学高温測定によって較正した。リアクタベース圧力は、13mTorr（ミリトル）の成長圧力のために $5 \times 10^{-10} mTorr$ であった。

30

【0018】

成長に続いて、サンプルを、光学リソグラフィを用いてパターニングし、サンプルを、大きさが7mm×7mmないし0.1mm×0.1mmの範囲であるメッシュスクウェアとして且つ14μmピッチで7μm程度の小さな（開口30に相当）穴をもって形成する。メッシュの穴30のピッチは、好みのHFエッチング時間に依存する。粗いピッチは、細かいピッチよりも長いエッチング時間を必要とする。

【0019】

パターニングの後、メッシュ膜を、化学エッチング手順を用いて剥離した。剥離の前に、サンプルを、アセトン及びメタノールで洗浄して残っているフォトレジストを除去し、次いで、10秒間HFディップで洗浄し、これに続いて10分間過酸化水素及び硫酸ピラニア洗浄を行なった。洗浄後、サンプルを、10%HF溶液の中に20分間置いた。次いで、サンプルを、HFビーカーから丁重に取り出してDI（脱イオン）水ビーカーに転移した。サンプルが水ビーカーの中へ落とされたとき、メッシュ膜は、水の表面に転移された。次いで、メッシュ膜を新しい基板の上に滑らせることによってメッシュ膜を水面から取り出した。この種類の膜は、スライドガラス、酸化Siウェーハ、バルク水素を末端基とするSiウェーハ、及びいかなる種類のグリッド、或いは水に溶けない他の望ましい基板に転移することができる。

40

【0020】

構造体の剥離前後の両方で実験源X線回折装置を用いてX線回折（XRD）逆格子空間

50

マップを作つて多層システムのひずみ、厚さ及び組成を決定した。XRD測定のために、メッシュを、Si(001)基板に転移してSiピークの零ひずみ位置を決定した。

#### 【0021】

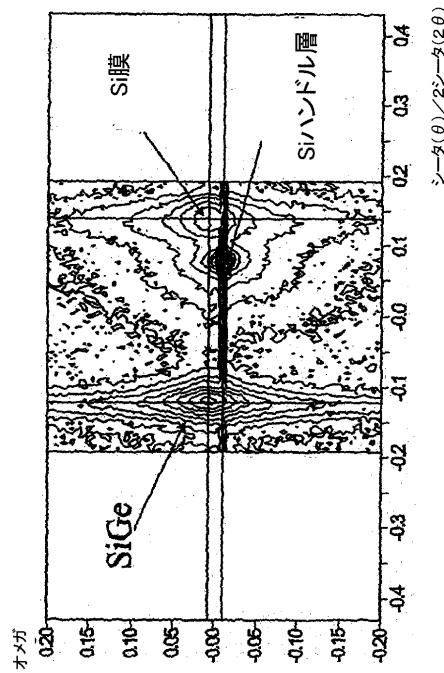

成長に続いて、(004)X線回折シータ( )/2シータ(2 )走査をオメガ( )を増分させながら行って成長中状態のひずみ及び配向に関する情報を含むマップを得た。成長の直後に、システムは基板と密着した。 /2 ライン走査をフィットさせて組成及び層の厚さを決定した。

#### 【0022】

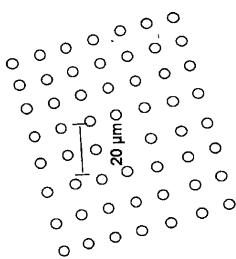

200nmのSi総計厚さ及び200nmのSiGe総計厚さを有する剥離したSi/SiGe/Si構造体の2mm×2mmメッシュ膜をSi基板に転移した。剥離したメッシュの光学顕微鏡的図を図9に示す。メッシュを、膜の2mm×2mmの領域にわたつてわずかな可視しわ或いは割れ目を有する新しい基板に転移した。メッシュ膜は、非常に柔軟であり、水が蒸発してしまつまで新しい基板上で調整することができる。大きいメッシュ膜に加えて、5~20ミクロンの正方形片のラフトが新しい基板に転移された。Si及びSiGeの厚さが等しく且つ対称的なので、準拠二層モデルに基づきSiとSiGeの間にひずみを均等に分けた平坦メンブレーンが期待される。しかしながら、膜厚が等しいことは必要ではなく、当初湾曲した膜が更なる加工の前に平坦にされるのがよい。

10

#### 【0023】

図10でわかるように、XRD逆格子空間マップを、剥離及び新しいSi基板への転移に続いてメッシュ上で測定する。剥離後のマップは、準拠基板によって予測されたひずみ分布に一致するひずみ分布を伴つて、部分的緩和SiGe、及び部分的ひずみSiを示す。 /2 走査におけるSiハンドルピークとSiメッシュピークの間の分離( )は、0.0630度であり且つ /2 走査におけるSi基板(新たなハンドル)とSiGeピークの間の分離( )は、0.200度である。これは、0.0560度Siハンドルの200nmのSi及び200nmのSi<sub>0.90</sub>Ge<sub>0.10</sub>を有する完全準拠二層と比較し、ひずまされたSi分離及び0.200度Siハンドルと比較し、SiGeピーク分離と比較する。Si層がひずまされたことを示すことに加えて、XRDマップは、回折ピークが局所的に小さいモザイクの傾斜だけを示唆するのに十分狭いことを示す。ピークの幅は、グレーデッドSiGe基板の上で成長させたひずみSiで典型的に観測されたものよりも実際には狭い。

20

#### 【0024】

これらの例は、二つの材料の好ましいひずみ状態を達成するために、ひずみSiGe膜をひずみのないSOI基板の上に成長させ、次いでSiハンドルウェーハからうまく剥離することができるということを示す。XRD測定は、剥離に先立つて、Si膜がひずみのないこと、そしてSiGe膜が基板に合致するようにコヒーレント的にひずまされることを示す。剥離されたメッシュ膜の大きさは、実験X線源を用いて剥離された材料の單一片上でXRDを行うのに十分大きい。メッシュの剥離に続いて、XRD測定は、Siがひずまされ且つSiGe膜が部分的に緩和されることを示す。Si及びSiGe層の測定されたひずみは、一方の層としてSi膜厚と他方の層としてSiGe膜厚の合計を用いて簡単な二層モデルによって予測されたものと一致する。

30

#### 【0025】

ひずみSiGe膜を標準SOI基板の上で成長させ、次いで犠牲層を取り除くことによつてSi/SiGeシステムを剥離することによって薄いSi層に転移することができるひずみの量は、累積的Si層の厚さ、累積的SiGe層の厚さ、及びSiGe層中のGe組成による。

40

#### 【0026】

最大ひずみをSiに転移するために、高品質の層構造体を依然として生成する最も薄い累積的Si厚さを有することが望ましい。Siテンプレート層の出発厚さは、典型的には20nmである。20nm未満の初期Siテンプレート層厚さは、薄くする加工中に膜に導入される欠陥のために、膜品質を減じてしまう。より高品質の商用的に薄くしたSO

50

I が入手可能になるとき将来この厚さを減じることが可能であるかもしれない。

【0027】

Si に転移されたひずみの量を制御するその他の変数は、厚さ及び SiGe 層中の Ge 濃度である。Si へのひずみの転移を最大にするために、SiGe 厚さは、Si 層の厚さよりもさらに厚くすべきであり、さらに高い Ge 濃度は、Si : SiGe 厚さの所定割合に対して両方の層にさらに多くのひずみをもたらす。最大 SiGe 厚さは、転位形成のオンセットによって制限される。SiGe 組成のための臨界厚さを超えるならば、構造体は、塑性的に緩和し始めて、転位を発生させ転移に利用可能なひずみを減じる。転位の存在とひずみの減少の両方が問題である。最大 Ge 濃度は、Ge 濃度が平坦合金成長に何をもたらすかに基づいて制限される。実際には、150 nm から 200 nm までの厚さ及び 18 % から 20 % までの Ge 濃度を有する準安定 SiGe 膜を、かなりの粗化或いは転位形成なしで、ひずまされていない Si の上に成長させることができる。好ましいが、それに限定しない、SiGe 層に対する下限は、約 5 % Ge である。一般的に、Si 層厚さが約 200 nm 未満であり且つ SiGe 層が少なくとも約 50 nm であることが好ましいが、それに限定されない。

【0028】

転位なしの円滑な成長に対して達成可能な Si : SiGe 層の厚さの比率及び SiGe の Ge 配合は、約 0.56 % の上限を初期的にひずみが生じていない Si の膜へ転移することが適度に期待できるひずみの量に置く。このひずみ転移の量は、電子移動度を向上させるには有利であるが、ホール移動度を向上させるためには、Si のより多くのひずみが望ましい。Si のひずみの量を増すために、複数の成長及び剥離段階を用いることができる。更に、初期的引張 - ひずみシリコンテンプレート層 (sSOI) を有する SOI 基板を基板として利用してもよい。この場合には、高い Ge 濃度、例えば、20 % ~ 35 % の Ge 範囲の Ge 濃度を、SiGe 層に利用することができ、シリコン層へのより大きなひずみ転移を可能にする。

【0029】

以下は、複数の成長及び剥離段階アプローチのための手順の例であるが、本発明が、本発明を例示する目的のために記述された特定の条件及び材料に限定されないということは言うまでもない。例えば、18 % Ge の 150 nm SiGe 膜を、CVD を用いて成長させた 10 nm の Si で覆われた、厚さ 25 nm の Si テンプレート層及び厚さ 1.3 ミクロンの埋め込み酸化物を有する薄い SOI 基板の上に成長させるのがよい。次いで Si / SiGe / Si 構造体をメッシュパターンで光学リソグラフィを用いて パターニング し、次いで、該構造体を、プラズマエッチングして後続の HF エッチングのために酸化物を露出させる穴を膜に開ける。犠牲的な埋め込み酸化物を 10 % HF 溶液でエッチングすることによってサンプルを剥離し且つこれをリンスビーカーの水の表面に転移する。次いで、メッシュ膜を、表面に 1 ミクロンの酸化物を有する新しく清潔な Si 水に転移することができる。酸化物層は、第 2 の剥離段階で犠牲層として作用する。追加の SOI ウェーハが複数の成長及び剥離段階のために不要である。厚い酸化物層を有する Si ウェーハは、薄い SOI ウェーハよりもかなり低いコストのものであり、且つ追加の Si 層の欠如は、合計 Si 厚さを減じて、Si 層へ転移されるひずみを増す。剥離及び転移に続いて、酸化 Si ウェーハに取付けられた多層構造体は、成長チャンバの中へ装填することができ、且つ新しくさらに高い Ge 濃度の、SiGe 膜を堆積させることができる。この成長に続いて、膜の パターニング、エッチング、及び HF 剥離を繰り返すことができる。Si 層のひずみは、今、以前よりも大きくなる。次いで、膜は、Si 層のひずみを増すために追加の成長及び剥離段階に対して別の酸化 Si ウェーハへ転移することができ、或いは、所望の最終基板に転移することができる。

【0030】

剥離されたメッシュ膜は、可撓性基板アプリケーションで用いるのにかなり有利である。現在、ポリシリコン膜を、可撓性基板を必要とするアプリケーションのために可撓性材料の上に直接成長させる。ポリシリコン基板の上に形成される装置の速さは、かなり

遅い。可撓性装置の現状は、可撓性基板として単結晶 Si を用いることができることが著しい改善であり、ひずみ層によってもたらされる移動度向上の必要性が現在未解決である。ひずみのない剥離単結晶 Si 片を可撓性基板に転移するいくつかの方法が E. Menard, K. J. Lee, D.-Y. Khang, R. G. Nuzzo, J. A. Rogers による “Plastic substrate上に高性能薄膜トランジスタのためのシリコンの印刷可能な形態 (A printable form of silicon for high performance thin film transistors on plastic substrates)” Appl. Phy. Lett., 84, 5398 (2004) に述べられている。この論文は、Si を SOI から可撓性基板に転移することを記述する。方法は、SOI 上で小さな構造を パターニング し且つ化学的にエッチングし、それから HF により埋め込み酸化物を取り除くことによって構造体を剥離することである。重要な点は、金のパッドを有する可撓性プラスチック基板に次いで配列される長細いストリップにある。

#### 【0031】

HF 蒸気エッティングか HF 液体エッティングのいずれかを剥離加工に利用してもよい。二つの方法は、その両方が利点及び欠点を有する。蒸気及び液体エッティング加工の例を説明だけの目的で以下に記述するが、本発明は、例示に対して記述されるそのような加工或いは条件に限定されることは、言うまでもない。

#### 【0032】

HF 蒸気エッティングでは、例えば、10 分間のピラニア、10 秒間の 10% HF、10 分間のピラニア、10 秒間の 10% HF 浸漬、及び 10 分間のピラニアからなる、例えば、典型的な成長前洗浄を用いて、サンプルを成長のために準備する。次いで、少量の 49% HF をテフロン (登録商標) ビーカーに入れる。このビーカーを、多くの穴を含む蓋で覆い且つストリップを、穴の上に面を上にして配置する。次いでシステムを覆い、HF 蒸気を上部カバーとストリップとの間に蓄積させる。ランプがセットアップの上に位置決めされて、サンプルの温度をサンプルとランプの距離を調整することによって制御する。サンプルの温度は、サンプルの表面の上に凝縮された水の量を制御することによってエッティング速度を制御する。低温は、更なる水凝縮及び高いエッティング速度を意味する。さらに高温でのエッティングは、酸化物表面上での水凝縮を減らし且つエッティング速度を下げる。

#### 【0033】

HF 液体でエッティングすることとは対照的に HF 蒸気でエッティングすることに利点及び欠点の両方が在る。主な利点は、静止摩擦を排除することである。静止摩擦は、装置をアンダーカットし且つ剥離する場合に MEMS (微小電子機械システム) 装置の一般的な問題である。水がサンプルから蒸発するときに、毛管力は、装置を基板に引き降ろす。ドライの間に剥離構造をエッティングすれば、毛管力によってもたらされる静止摩擦を除去することができる。

#### 【0034】

蒸気エッティングの主な欠点は、エッティング加工を制御することの難しさである。エッティング速度は、小さな温度変化、湿度変化、表面の上の炭素汚染、及びその他の局部変化にかなり敏感である。また、高いエッティング速度でシリコンの表面に残された残留物が存在しうる。これは、きれいな最終構造体をもたらすためにエッティング速度及び温度がよく制御されることを要求する。

#### 【0035】

蒸気エッティングを用いて 20 ~ 30 ミクロン程度の横方向距離に構造体を日常的にアンダーカットすることは、一般的に単に実用的である。更にアンダーカットすることは可能であるが、相応的に長いエッティング時間が必要とする。横方向に 20 ~ 30 ミクロンエッティングするのに、約 1 時間の蒸気エッティング時間が一般的にかかる。剥離することができる構造体の領域は、大きな構造体がある大きさのデッドエリアを有していなければならない範囲に限定される。図 9 に示すように、メッキ膜の場合のデッドエリアは、HF を酸化物に浸透させるために Si テンプレート層にエッティングされた小さな穴 30 からなる。

#### 【0036】

また、HF 液体で酸化物をエッティングすることによって構造体を剥離することも利点及

10

20

30

40

50

び欠点を有する。主な利点は、エッティング加工を制御することがずっと容易であることがある。蒸気エッティングの場合には、表面の上に凝縮した液体がエッティング速度を決定するが、液体エッティングでは、速度は、HF濃度によって制御される。更に、HF液体がエッティング加工によって消費されるように、pHを低く維持することによりエッティング速度をより一貫して維持するために、HF液体をフッ化アンモニウムで緩衝させることができる。更に、水がいかなる過剰反応物を除去することができるので、高いエッティング速度で残留物が取り残されない。

#### 【0037】

基板にある位置で取付けられたままにすることが必要な装置に対するHF液体エッティングによる主な問題は、乾燥加工中に遭遇される。サンプルをHFエッチ溶液から取り除いた後、サンプルは湿ったままである。水が蒸発すると、毛管力は、剥離された構造体をSi基板に向けて引っ張る。剥離された構造体の大きさ、構造体からSi基板までの距離、及び剥離された構造体の厚さにより、剥離された構造体は、Si基板に達して貼り付く。この事象は、静止摩擦と呼ばれMEM装置の一般的な問題である。静止摩擦による問題を克服するために、MEMは、典型的には臨界点乾燥を用いて乾燥される。臨界点乾燥では、剥離された構造体は、蒸気及び液体粒子が識別不能であるような高い温度及び圧力で、溶媒で乾燥される。しかしながら、臨界点乾燥は、良好な後続の成長を妨げうる炭素汚染を表面の上に残すことがある溶媒を必要とする。

10

#### 【0038】

しかしながら、水/HF溶液が膜と基板の間でバリアとして作用するので、液体エッティングは、膜の完全な除去のために有利である。剥離後、サンプルを、HF溶液から取り出して直ぐに水のビーカーの中に落し込む。サンプルが水に入ると、膜を、水の表面張力により基板の表面から取り出す。次いで膜は、水の表面に浮き新しい基板に転移することができる。

20

#### 【0039】

上述の例は、犠牲酸化物層に接近するために上部多層構造体のパターニングを示し、犠牲層のエッティングを可能にする。変形例として、多層構造体をパターニングせずに多層構造体をハンドル層から剥離すべく犠牲層に接近するためにハンドル層を通してエッティングを利用することができる。これは、シリコンをエッティングしてSiO<sub>2</sub>絶縁層で停止されるエッティング液を利用してハンドル層21に一連のウィンドウをSiO<sub>2</sub>層22までエッティングすることによって行なわれる。ハンドル層21の典型的な大きな厚さのために、犠牲層22までハンドル層を通してエッティングするには犠牲層の上の多層構造体を通してエッティングするよりも多くのエッティング時間を必要とするかもしれない。

30

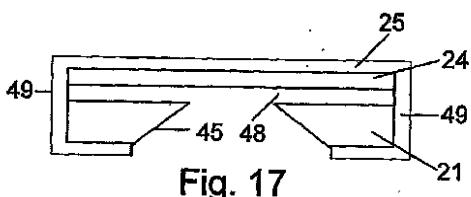

#### 【0040】

犠牲層21に接近するためにSOIウェーハのハンドル層21を通してエッティングするのに様々な加工を利用することができる。例示的加工を以下に記述し且つ図11～図17に関して説明するが、本発明は、そこに示した方法で加工を行うことに限定されないということを再び指摘しておく。多層構造体を剥離すべく犠牲層を選択的にエッティングするために犠牲層に接近を可能にするどんな加工をも利用してもよい。

#### 【0041】

40

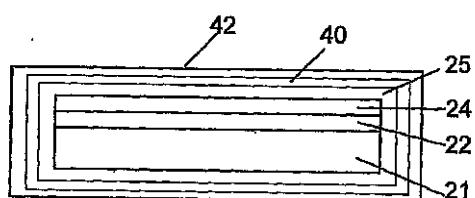

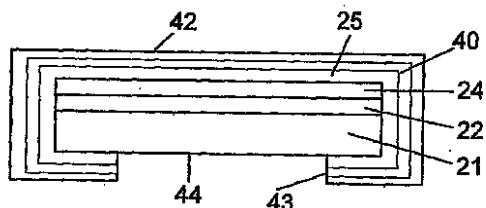

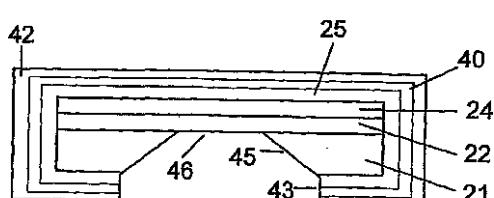

図11を参照して、第1の段階は、シリコン層24の上及び、ハンドル層21の底面及び層21、22及び24の縁を含む、SOIウェーハの他の全ての表面の上にも、上述したような、成長されたSiGeの層25の適用である。膜をウェーハの全ての表面の上に堆積させる方法でSOIウェーハを吊り下げて、CVDを利用して層25を成長させるのがよい。次いで、温度SiO<sub>2</sub>層40を、図12に示すように、SiGe層25の全ての表面の上に成長させて更なる加工中SiGe層の表面を保護する。酸化物層40は、例えば、100nmの厚さに成長されるのがよい。次いで、図13に示すように、CVD成長窒化シリコン(Si<sub>3</sub>N<sub>4</sub>)の薄い層(例えば、100nm)をSiO<sub>2</sub>層40の上に成長させて基板の化学エッティング中膜システムを保護する。次いで、図14に示すように、一つ以上の開口或いは窓43を、層42、40及び25を通してウェーハの裏側へエッキン

50

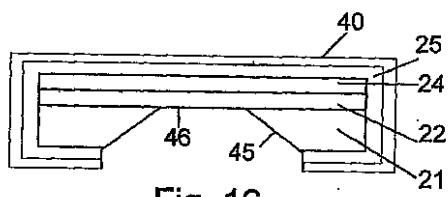

グし、領域 4 4 のハンドル層 2 1 の裏側を露出させる。一つの窓 4 3 が示されているが、一般的には窓のパターンは、ウェーハの裏面に形成されてハンドル層 2 1 への複数の接近領域 4 4 を可能にする。フォトレジストのパターニング及び現像は、標準リソグラフィック加工技法を用いて行われるのがよい。リソグラフィックパターニング後にフォトレジストによって保護されない領域では、窒化シリコン層 4 2 を、例えば、反応性イオンエッティング (R I E) を利用して、まずエッティングし、H F エッティングが続いて酸化物層 4 0 を除去し、R I E エッティングが続いて S i G e 層 2 5 (或いは複数の層) を除去する。次いで図 1 5 に示すように、K O H のような、S i O<sub>2</sub>と比較して S i を選択的にエッティングするエッティング液をウェーハに適用して、S i O<sub>2</sub>層 2 2 を露出する領域 4 6 で終るエッチピット 4 5 を形成するのがよい。次いで、図 1 6 に示すように、例えば、湿式リン酸エッチを用いて保護窒化シリコン層 4 2 を除去し、そして、次いで図 1 7 に示すように、ウェーハ全体を、上述したように、H F エッティングにさらして、シリコン層 2 4 の下に空隙 4 8 にして層 2 4 及び 2 5 で構成された多層構造体をハンドル層 2 1 から離す。多層構造体 2 4 及び 2 5 をウェーハの縁 4 9 でハンドル層 2 1 に接続する S i G e 材料は、一般的に多層構造体の剥離を可能にすべく容易に壊される。変形例として、縁 4 9 の材料は、取外しを容易にするためにパターニングすることができる。また、ハンドル層 2 1 のエッティングされた開口 4 5 は、S i G e 膜 2 5 が堆積される前に形成されるのがよい。また、ハンドル層 2 1 が予めパターニングされ、次いで多層構造体が M B E によって成長されて、成長を上部面だけに限定するのがよい。

## 【0042】

10

また、図 1 1 ~ 図 1 7 に示す層の全てがエピタキシャル的に堆積されるということも重要ではない。材料は、テンプレート層 2 4 或いはテンプレー層上の追加層の上に成長されるのがよく、追加層は、粒状物或いは欠陥を有してもよいし、或いは、アモルファスであってもよいが、それが剥離されるときに結晶層 2 4 をそれでもひずませるであろう。追加結晶層を非結晶層の上に成長させることは、一般的に可能ではないが、追加のひずみを多層膜構造体に追加するストレーナー層 (例えば、窒素) を成長させてもよい。

## 【0043】

20

本発明は、実例としてここに示された特定の実施形態に限定されないが、添付した特許請求の範囲内に付属しているその全ての係る形を含むことは、言うまでもない。

## 【図面の簡単な説明】

30

## 【0044】

【図 1】本発明用のシリコンオンインシュレータ (S O I) ウェーハの簡略断面図である。

【図 2】S i G e 層を追加させた図 1 に示すウェーハの図である。

【図 3】多層構造体を形成するために S i G e 層上に上部 S i 層の形成後の図 2 に示すウェーハの図であって、任意の S i G e 上部層を示す図である。

【図 4】S i O<sub>2</sub>犠牲層に多層構造体をパターン化しつつエッティングした後の図 3 のウェーハの図である。

【図 5】多層構造体を剥離するために S i O<sub>2</sub>犠牲層のエッティングの後の図 4 のウェーハの図である。

40

【図 6】永久基板上に取付けた後の本発明の多層構造体を示す断面図である。

【図 7】本発明の多層構造体の離散的セクションの剥離、及び永久基板への剥離された構造体の転移及び取付けを示す説明図である。

【図 8】本発明の多層構造体の大面積膜の剥離、及び永久基板への膜の転移及び取付けを示す説明図である。

【図 9】永久基板への膜の取付け後の本発明の大規模多層膜の図である。

【図 1 0】構造体の S i 膜部分の (ひっぱり) ひずみを記述する S i 膜ピークと S i 基板取扱い層ピークとの間で (x 軸に沿って) / 2 の分離を有し、S i G e 層の (圧縮) ひずみを記述する S i 取扱い層ピークからの S i G e ピークの分離を有する、S i 基板への転移及び取付け後の剥離された S i / S i G e / S i 多層構造体の X 線回折 (X R D )

50

逆空間マップを示す図である。

【図11】本発明による初期加工段階でSiGe層を成長させたSOIウェーハの簡略断面図である。

【図12】SiGe層に酸化層を追加した図11に示すウェーハの図である。

【図13】酸化層に堆積されたSiN層の形成後の図12に示すウェーハの図である。

【図14】ウェーハの裏側に堆積された層をパターン化しつつエッチングした後の図13に示すウェーハの図である。

【図15】SOIウェーハの露出シリコンハンドル層を通して好適なエッチの後の図14に示すウェーハの図である。

【図16】上部SiN層をエッチングして取り除いた後の図15に示すウェーハの図である。

10

【図17】シリコンハンドル層から上部多層構造体を取り除くためのSOIウェーハのSiO<sub>2</sub>絶縁層の好適なエッチングの後の図16に示すウェーハの図である。

【符号の説明】

【0045】

20 初期SOIウェーハ

21 結晶シリコンハンドルウェーハ

22 絶縁(犠牲)層

24 シリコンテンプレート層

【図1】

FIG. 1

【図4】

FIG. 4

【図2】

FIG. 2

【図5】

FIG. 5

【図3】

FIG. 3

【 図 6 】

FIG. 6

【 図 7 】

FIG. 7

【図8】

FIG. 8

【図9】

FIG. 9

【図10】

FIG. 10

【図 1 1】

Fig. 11

【図 1 2】

Fig. 12

【図 1 3】

Fig. 13

【図 1 4】

Fig. 14

【図 1 5】

Fig. 15

【図 1 6】

Fig. 16

【図 1 7】

Fig. 17

---

フロントページの続き

(74)代理人 100103609

弁理士 井野 砂里

(72)発明者 サヴェッジ ドナルド イー

アメリカ合衆国 ウィスコンシン州 53705 マディソン ヒルクレスト ドライヴ 431

8

(72)発明者 ロバーツ ミッケル エム

アメリカ合衆国 ウィスコンシン州 53715 マディソン チャンドラー ストリート 13

20 アパートメント 1

(72)発明者 ラガリー マックス ジー

アメリカ合衆国 ウィスコンシン州 53705 マディソン ジュノー ロード 5110

審査官 加藤 俊哉

(56)参考文献 特開2003-249641(JP, A)

米国特許出願公開第2004/0253792(US, A1)

特表2006-524427(JP, A)

国際公開第2004/095553(WO, A1)

特開平09-219524(JP, A)

特開2004-039735(JP, A)

特開2003-273017(JP, A)

特開2004-103805(JP, A)

特開2004-241507(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/02

H01L 21/20

H01L 21/205

H01L 27/12