(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5287508号

(P5287508)

(45) 発行日 平成25年9月11日(2013.9.11)

(24) 登録日 平成25年6月14日(2013.6.14)

(51) Int.Cl.

F 1

H04B 1/18 (2006.01)

H04N 5/44 (2011.01)H04B 1/18

H04N 5/44A

K

請求項の数 20 (全 23 頁)

(21) 出願番号 特願2009-128702 (P2009-128702)

(22) 出願日 平成21年5月28日 (2009.5.28)

(65) 公開番号 特開2010-278719 (P2010-278719A)

(43) 公開日 平成22年12月9日 (2010.12.9)

審査請求日 平成24年2月29日 (2012.2.29)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100082131

弁理士 稲本 義雄

(74) 代理人 100121131

弁理士 西川 孝

(72) 発明者 佐生 登

東京都港区港南1丁目7番1号 ソニー株式会社内

審査官 佐藤 敏介

最終頁に続く

(54) 【発明の名称】信号処理装置、フロントエンド回路、信号処理装置におけるスイッチ切替制御方法、フロントエンド回路におけるスイッチ切替制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

入力信号を、複数の出力端に分配して出力する信号分配手段と、

前記信号分配手段の前記複数の出力端のそれぞれに接続される信号処理部の複数個と、

前記複数個の信号処理部の少なくとも一つに設けられ、前記信号分配手段からの信号の

伝送路をオン・オフする1または複数の信号用スイッチと、

前記1または複数の信号用スイッチの切替信号を発生する切替信号発生部と、

前記切替信号により前記信号処理部の前記1または複数の信号用スイッチが切り替えられたときに、前記1または複数の信号用スイッチが切り替えられた信号処理部の入力インピーダンスが、急峻でない遷移をするように抑制するための抑制手段と、

を備える信号処理装置。

## 【請求項 2】

請求項1に記載の信号処理装置において、

前記抑制手段は、前記信号分配手段と前記信号処理部との間の信号伝送路に設けられる

インピーダンス遷移補正回路からなり、

前記インピーダンス遷移補正回路は、前記切替信号により前記信号処理部の前記1または複数の信号用スイッチが切り替えられるときに、前記信号処理部の入力インピーダンスが、急峻でない遷移をするように制御される

信号処理装置。

## 【請求項 3】

10

20

請求項 1 に記載の信号処理装置において、

前記抑制手段は、前記切替信号発生部からの急峻な遷移の前記切替信号を、急峻でない遷移をする切替信号に抑制して前記信号処理部の前記 1 または複数の信号用スイッチに供給する切替信号補正手段からなる

信号処理装置。

## 【請求項 4】

請求項 3 に記載の信号処理装置において、

前記切替信号補正手段は、前記切替信号の前記 1 または複数の信号用スイッチへの信号路に設けられる時定数回路からなる

信号処理装置。

10

## 【請求項 5】

請求項 3 に記載の信号処理装置において、

前記切替信号補正手段は、キャパシタ素子と、前記切替信号に基づいて駆動され、前記キャパシタ素子への充放電を行うチャージポンプ回路とから構成される

信号処理装置。

## 【請求項 6】

請求項 5 に記載の信号処理装置において、

前記切替信号補正手段を構成するチャージポンプ回路は、微小電流発生源から供給される微小電流を元に動作する

信号処理装置。

20

## 【請求項 7】

請求項 6 に記載の信号処理装置において、

前記微小電流発生源は、前記入力インピーダンスの遷移特性を可変するために、発生する前記微小電流を可変にする電流調節機能を備える

信号処理装置。

## 【請求項 8】

請求項 3 乃至請求項 7 のいずれかに記載の信号処理装置において、

前記 1 または複数の信号用スイッチは、電界効果トランジスタで構成されると共に、ゲート制御端子とドレイン制御端子とを備え、

前記切替信号補正手段は、前記切替信号に基づき、前記ゲート制御端子と前記ドレイン制御端子とに相補的な制御電位を与えることで、前記 1 または複数の信号用スイッチをオン・オフする

信号処理装置。

30

## 【請求項 9】

請求項 1 ~ 8 のいずれかに記載の信号処理装置は、放送信号の受信装置であって、

前記複数個の信号処理部はチューナのフロントエンド回路であって、前記信号用スイッチが設けられるフロントエンド回路は、受信信号の周波数帯域を複数に分割して、各分割周波数帯域毎に処理するようにするものであり、

前記信号分配手段は、受信した放送信号を、複数個のチューナのフロントエンド回路に分配して供給するものであり、

40

前記信号用スイッチは、前記信号分配手段からの受信信号の前記複数の周波数帯域のうちの前記信号処理部で処理する分割周波数帯域を選択するためのスイッチであり、

前記切替信号は、前記チューナにおける選局チャンネルが、いずれの分割周波数帯域に含まれるかにより、前記信号処理部に対して自動的に生成されて供給される

信号処理装置。

## 【請求項 10】

受信信号が分配されて入力される複数個の信号処理部のうちの 1 つの信号処理部であるフロントエンド回路であって、

入力端を通じて入力される受信信号の伝送路をオン・オフする 1 または複数の信号用スイッチと、

50

切替信号により、前記1または複数の信号用スイッチが切り替えられたときに、入力インピーダンスが、急峻でない遷移をするように抑制するための抑制手段と、

を備える受信装置のフロントエンド回路。

【請求項11】

請求項10に記載の受信装置のフロントエンド回路において、

前記受信信号の周波数帯域を複数に分割して、各分割周波数帯域毎に処理するよう<sup>するもの</sup>であり、

前記信号用スイッチは、前記受信信号の前記複数の周波数帯域のうちで処理する分割周波数帯域を選択するためのスイッチであり、

前記切替信号は、選局チャンネルが、いずれの分割周波数帯域に含まれるかにより、前記信号処理部に対して自動的に生成されて供給される

受信装置のフロントエンド回路。

【請求項12】

請求項10に記載の受信装置のフロントエンド回路において、

前記抑制手段は、急峻な遷移の前記切替信号を、急峻でない遷移をする切替信号に変更して前記1または複数の信号用スイッチに供給する切替信号補正手段からなる

受信装置のフロントエンド回路。

【請求項13】

請求項12に記載の受信装置のフロントエンド回路において、

前記切替信号補正手段は、前記切替信号の前記1または複数の信号用スイッチへの信号路に設けられる時定数回路からなる

受信装置のフロントエンド回路。

【請求項14】

請求項12に記載の受信装置のフロントエンド回路において、

前記切替信号補正手段は、キャパシタ素子と、前記切替信号に基づいて駆動され、前記キャパシタ素子への充放電を行うチャージポンプ回路とから構成される

受信装置のフロントエンド回路。

【請求項15】

請求項14に記載の受信装置のフロントエンド回路において、

前記切替信号補正手段を構成するチャージポンプ回路は、微小電流発生源から供給される微小電流を元に動作する

受信装置のフロントエンド回路。

【請求項16】

請求項15に記載の受信装置のフロントエンド回路において、

前記微小電流発生源は、前記入力インピーダンスの遷移特性を可変するために、発生する前記微小電流を可変にする電流調節機能を備える

受信装置のフロントエンド回路。

【請求項17】

請求項12乃至請求項16のいずれかに記載の受信装置のフロントエンド回路において、

前記1または複数の信号用スイッチは、電界効果トランジスタで構成されると共に、ゲート制御端子とドレイン制御端子とを備え、

前記切替信号補正手段は、前記切替信号に基づき、前記ゲート制御端子と前記ドレイン制御端子とに相補的な制御電位を与えることで、前記1または複数の信号用スイッチをオン・オフする

受信装置のフロントエンド回路。

【請求項18】

I C ( I n t e g r a t e d C i r c u i t ; 集積回路 ) 化されていることを特徴とする請求項12乃至請求項17のいずれかに記載の受信装置のフロントエンド回路。

【請求項19】

10

20

30

40

50

信号伝送路をオン・オフする 1 または複数の信号用スイッチを備える信号処理部の複数個に、入力信号を信号分配手段により分配して供給する信号処理装置におけるスイッチ切替制御方法であって、

制御手段が、切替信号により前記信号処理部の前記 1 または複数の信号用スイッチが切り替えられたときに、前記 1 または複数の信号用スイッチが切り替えられた信号処理部の入力インピーダンスが、急峻でない遷移をするように抑制するための抑制工程を有する

信号処理装置におけるスイッチ切替制御方法。

【請求項 20】

受信信号が分配されて入力される複数個の信号処理部のうちの 1 つの信号処理部であるフロントエンド回路であって、入力端を通じて入力される受信信号の伝送路をオン・オフする 1 または複数の信号用スイッチと、制御手段を備えるフロントエンド回路におけるスイッチ切替制御方法であって、

切替信号により、前記 1 または複数の信号用スイッチが切り替えられたときに、前記制御手段が、前記フロントエンド回路の入力インピーダンスが、急峻でない遷移をするように抑制するための抑制工程を有する

フロントエンド回路におけるスイッチ切替制御方法。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、例えば、広帯域のテレビ放送信号を複数の周波数帯域に分け、1 または複数のスイッチにより処理する周波数帯域を切り替え選択できるようにすることにより、各分割周波数帯域毎に処理ができるようにするチューナのフロントエンド回路におけるスイッチ切替制御方法に関する。また、このスイッチ切替制御方法が適用される信号処理装置、フロントエンド回路に関する。

【背景技術】

【0002】

テレビ放送受信用のチューナのフロントエンド回路は、各国のテレビ放送を、その放送形式に関わらず受信して処理することが可能である。しかし、各国のテレビ放送を受信使用とした場合には、その受信周波数帯域は、非常に広い。このため、通常は、一つのバンドパスフィルタで受信信号を選択することは困難である。

【0003】

そこで、各国のテレビ放送で使用されている周波数を、例えば、

- (A) 46 ~ 147 MHz (V L バンド)

- (B) 147 ~ 401 MHz (V H バンド)

- (C) 401 ~ 887 MHz (U バンド)

の 3 バンドに分割し、ユーザのチャンネル選択操作に応じて、受信バンドを切り替えるようにしたフロントエンド回路が提供されている。

【0004】

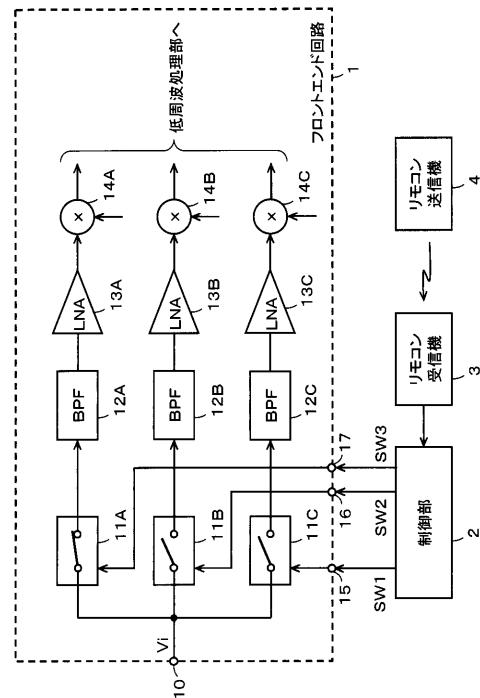

図 13 は、このように 3 バンドに周波数帯域が分割された場合のテレビチューナのフロントエンド回路の入力段の構成例を含む、テレビ放送受信機の一部の構成例を示す図である。この図 13 の例において、点線で囲んだフロントエンド回路 1 は、1 チップ IC ( Integrated Circuit ; 集積回路) として、IC 化されたものとされている。

【0005】

図 13 において、フロントエンド回路 1 の入力端子 10 には、アンテナで受信されたテレビ放送信号 Vi が入力される。このテレビ放送信号 Vi は、上記の 3 つのバンドのそれぞれに対応してオン・オフされる 3 個の信号用スイッチ 11A, 11B, 11C のそれぞれを通じて、上記の 3 つのバンド用のバンドパスフィルタ 12A, 12B, 12C に供給される。この場合、各バンドパスフィルタ 12A, 12B, 12C は、上述の VL バンド、VH バンド、U バンドのそれぞれの周波数帯域を選択周波数帯域とするバンドパスフィ

10

20

30

40

50

ルタとされる。

【0006】

信号用スイッチ 11A, 11B, 11C としては、半導体を使用した高周波スイッチが用いられている。この種の高周波スイッチは、近年非常に高頻度に使用されており、例えば特許文献 1 (特開平 9-139601 号公報) や特許文献 2 (特開平 10-284901 号公報) などにも示されている。

【0007】

各バンドパスフィルタ 12A, 12B, 12C のそれぞれの出力信号は、ローノイズアンプ 13A, 13B, 13C をそれぞれ通じて、ミキサ 14A, 14B, 14C のそれぞれに供給される。そして、ミキサ 14A, 14B, 14C のそれぞれには、局部発信信号が供給される。これにより、ミキサ 14A, 14B, 14C のそれぞれにおいては、ローノイズアンプ 13A, 13B, 13C のそれぞれの出力信号が、低周波の中間周波数に周波数変換される。そして、ミキサ 14A, 14B, 14C のそれからの中間周波数信号は、低周波処理部に供給され、テレビ信号が復調される。

【0008】

図 13 の例においては、例えばスイッチ回路 11A バンドパスフィルタ 12A ローノイズアンプ 13A ミキサ 14A の系は、VL バンド用である。また、スイッチ回路 11B バンドパスフィルタ 12B ローノイズアンプ 13B ミキサ 14B の系は、VH バンド用である。さらに、スイッチ回路 11C バンドパスフィルタ 12C ローノイズアンプ 13C ミキサ 14C の系は、U バンド用である。

【0009】

そして、例えばマイクロコンピュータで構成される制御部 2 からのバンド切替信号 SW1, SW2, SW3 が、端子ピン 15, 16, 17 をそれぞれ通じて、信号用スイッチ 11A, 11B, 11C のそれぞれに供給される。

【0010】

制御部 2 には、リモコン受信部 3 が接続されている。リモコン送信部 4 からのリモコン信号を受信するとリモコン受信部 3 は、その受信信号を制御部 2 に供給する。制御部 2 は、受信したリモコン信号を解析して、その解析結果に応じた制御処理をする。

【0011】

この場合に、リモコン送信部 4 からのリモコン信号が、ユーザのチャンネル変更操作に基づくチャンネル選択信号であるときには、制御部 2 は、先ず、当該チャンネル選択信号で示されるチャンネルが、VL, VH, U のいずれのバンドに含まれるかを判別する。

【0012】

そして、制御部 2 は、判別したバンドが、現在選択中のバンドであるときには、スイッチ 11A, 11B, 11C に供給するバンド切替信号 SW1, SW2, SW3 は変更しない。そして、制御部 2 は、選択中のバンドの系のミキサに供給する局部発信信号のみを、ユーザが選択したチャンネルを選局するように変更制御する。

【0013】

また、制御部 2 は、判別したバンドが、現在選択中のバンドとは異なるときには、その判別結果のバンドの選択状態になるように、スイッチ 11A, 11B, 11C を、バンド切替信号 SW1, SW2, SW3 により切替変更する。そして、制御部は、切替変更後のバンドの系のミキサに供給する局部発信信号を、ユーザが選択したチャンネルを選局するように変更制御する。

【0014】

この場合に、チャンネル変更の際には、当該変更時から、目的の放送チャンネルを正しく受信することができるまでに、局部発信信号生成用の PLL 回路の引き込み時間など、遅延が発生する。

【0015】

そのため、制御部 2 は、バンド切替時およびチャンネル変更時から前記遅延時間分の間は、フロントエンド回路の後段の復調部の動作を停止したり、復調部への信号をミュー

10

20

30

40

50

イングしたりして、再生画像が乱れたりするのを防止するようになっている。

【先行技術文献】

【特許文献】

【0016】

【特許文献1】特開平9-139601号公報

【特許文献2】特開平10-284901号公報

【発明の概要】

【発明が解決しようとする課題】

【0017】

ところで、近年のテレビ受信機は、複数個のチューナを内蔵するものが増加している。

これは、複数個のチューナのそれぞれで選局受信した放送チャンネルの番組映像を、1画面を複数個に分割して表示したり、いわゆる裏番組を録画記録したりする目的のためである。

【0018】

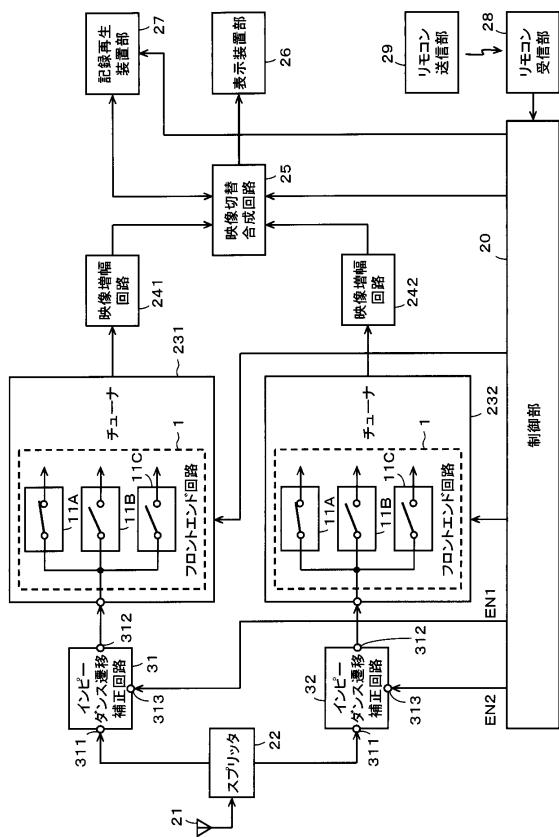

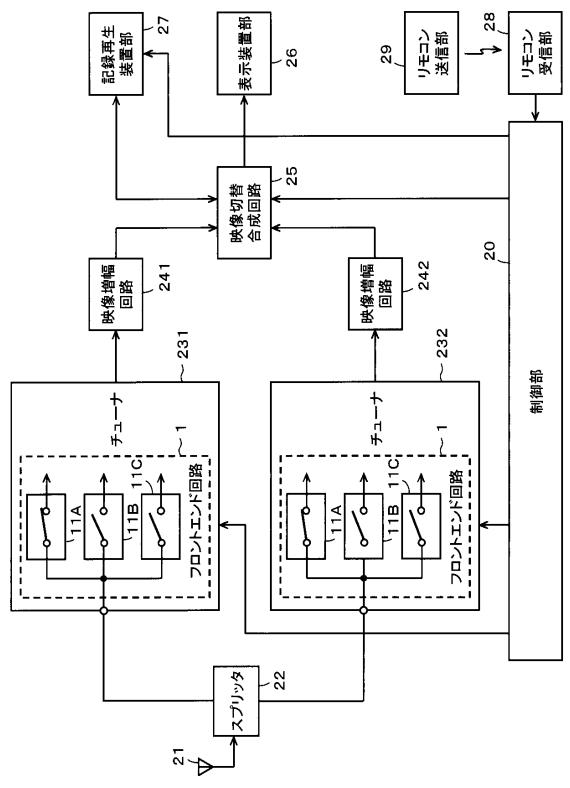

図14は、2個のチューナを備えるテレビ受信機の構成例を示すものである。この例は、受信アンテナ21で受信されたテレビ放送波信号は、信号分配手段としてのスプリッタ22により、第1のチューナ231と第2のチューナ232とに分配供給される。

【0019】

これら第1および第2のチューナ231および232は、図13を用いて前述したように、受信周波数帯域を3分割した3バンドを信号用スイッチ11A, 11B, 11Cにより切替選択する構成のフロントエンド回路1を備える。

【0020】

そして、第1および第2のチューナ231および232のフロントエンド回路1のそれぞれは、マイクロコンピュータで構成される制御部20から、独立に、バンド切替信号SW1, SW2, SW3(図14では図示は省略)を受けて、バンド切り替えを行う。また、第1および第2のチューナ231および232は、制御部20からのチャンネル選局信号に応じて局部発信信号を制御して、チャンネル選択を行う。

【0021】

制御部20には、前述の図13と同様に、リモコン送信部29からのリモコン信号を受けるリモコン受信部28が接続されている。制御部20は、リモコン送信部29でのユーザの、チャンネル切り替えや後述する出力モード切り替えの操作入力に応じた制御信号を生成して、チューナ231, 232や後述する映像切替合成回路25に供給する。

【0022】

この例の第1および第2のチューナ231および232のそれぞれは、制御部20からの制御信号に応じてチャンネル選択した受信信号を中間周波数信号に変換し、その変換した中間周波数信号から映像信号を復調(検波)して出力する。

【0023】

そして、第1のチューナ231および第2のチューナ232からの映像検波出力は、それぞれ映像增幅回路241および242を通じて映像切替合成回路25に供給される。この映像切替合成回路25には、制御部20から、ユーザの指示操作に応じた制御信号が供給される。

【0024】

映像切替合成回路25は、これに供給される制御信号に応じて、後述するような複数の出力モードで、表示装置部26および記録再生装置部27に、映像出力信号を供給する。

【0025】

表示装置部26は、例えばCRT(Cathode Ray Tube)や、LCD(Liquid Crystal Display)を表示素子として備え、映像出力信号に応じた映像を表示する。

【0026】

記録再生装置部27は、ハードディスク装置や、例えばDVD(Digital Ve

10

20

30

40

50

rsatile Disc) のようなリムーバル記録メディアを用いる光ディスクドライブなどを用いて、放送信号を記録再生する機能を備える。この記録再生装置部 27 には、制御部 20 からの記録 / 再生の制御信号が供給される。

【0027】

この例の映像合成切替回路 25 では、ユーザの指示操作に応じた、以下のような複数の出力モードを備える。

【0028】

(1) 第 1 のチューナ 231 と第 2 のチューナ 232 のいずれか一方の映像出力信号を選択して、表示装置部 26 あるいは記録再生装置部 27 のいずれかに供給する第 1 の出力モード。

10

(2) 第 1 のチューナ 231 と第 2 のチューナ 232 のいずれか一方の映像出力信号を表示装置部 26 に出力し、他方を記録再生装置部 27 に出力する第 2 の出力モード。

(3) 第 1 のチューナ 231 および第 2 のチューナ 232 の映像出力信号を合成し、その合成した映像出力信号を表示装置部 26 に供給する第 3 の出力モード。

【0029】

なお、制御部 20 からの制御信号により、記録再生装置部 27 が再生モードに切り替えるときには、映像合成切替回路 25 は、制御部 20 からの制御信号に従い、記録再生装置部 27 からの再生映像信号を、表示装置部 26 に供給する出力モードとなる。

【0030】

上述の第 1 のモードは、第 1 のチューナと第 2 のチューナのいずれかのみが動作状態となり、動作状態となっていないチューナは、通常は、省電力のためにスタンバイ状態とされている。この第 1 のモードのときには、ユーザにより、チャンネル選択切り替え操作がなされたときには、前述したように、ミューティングや復調部の動作停止制御がなされて、切り替え時の映像が乱れやノイズが防止される。

20

【0031】

しかし、第 2 の出力モードや第 3 の出力モードにおいては、第 1 のチューナ 231 と第 2 のチューナ 232 とが同時に動作状態となり、互いに独立にチャンネル切り替え選択がなされるために、バンド切り替えにより、次のような問題が生じることが判明した。

【0032】

例えば、第 2 の出力モードにおいて、第 1 のチューナ 231 で選択中のチャンネルの放送番組の映像を、表示装置部 26 の表示画面に表示しながら、第 2 のチューナ 232 で選択中のチャンネルの放送番組を録画する場合を考える。

30

【0033】

この場合において、ユーザが、第 1 のチューナ 231 あるいはチューナ 232 での選択チャンネルを変更したときに、そのチャンネル変更に伴って、バンド切り替えが生じる場合がある。

【0034】

このバンド切り替えにより、信号用スイッチ 11A, 11B, 11C のオン・オフ状態が変更されると、当該バンド切り替えがなされたチューナで扱う信号周波数が変化する。そして、その変化後の信号周波数についてのインピーダンスが、信号用スイッチ 11A, 11B, 11C の切り替え時に変化する。

40

【0035】

スプリッタ 22 のアイソレーションが十分でない場合には、このバンド切り替えがなされたチューナにおける入力インピーダンスの変化が、スプリッタ 22 を通じて他方のチューナに供給される信号を劣化させてしまうことがあることが判明した。このことについて、考えられる理由と共に説明する。

【0036】

前述したように、バンド切り替え用の信号用スイッチ 11A, 11B, 11C は、半導体からなる高周波スイッチが用いられる。特許文献 1, 2 などの公知例における通常の高周波スイッチでは、切替信号が与えられてから信号が切り替わる時間、すなわち信号バス

50

のインピーダンスが遷移する時間が極めて短いことが多い。

【0037】

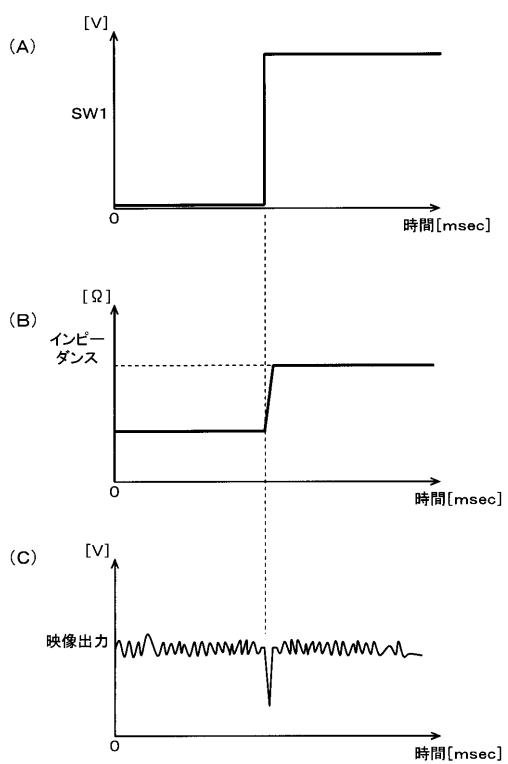

図15は、高周波スイッチの切替信号と、チューナの入力インピーダンスの切り替わりの様子を示したものである。

【0038】

図15の例は、信号用スイッチ11Aまたは11Bがオンになっている状態から、信号用スイッチ11Aがオンになる状態に切り替える場合を想定しており、図15(A)は、信号用スイッチ11Aの切替信号SW1を示している。

【0039】

そして、図15(B)は、信号用スイッチ11Aを含む系が受け持つ周波数における入力インピーダンスについて、信号用スイッチ11Bまたはスイッチ11Cのオン状態から、信号用スイッチ11Aがオン状態に切り替わるときの変化を示すものである。

【0040】

この場合、信号用スイッチ11Aがオン状態に切り替わる前においては、信号用スイッチ11Bまたは11Cを含む系の周波数帯域は、信号用スイッチ11Aを含む系が受け持つ周波数の帯域外であるので低いインピーダンスを示す。そして、信号用スイッチ11Aがオン状態に切り替わった後には、この信号用スイッチ11Aを含む系が受け持つ周波数についての共振インピーダンスが見えるために、高いインピーダンスとなる。

【0041】

そして、信号用スイッチ11Aの切り替え制御信号SW1は、図15(A)に示すように、ステップ状であるので、信号用スイッチ11Aのオン状態への切り替え前後のインピーダンス遷移も、図15(B)に示すように、ステップ状に近い応答波形となる。

【0042】

2個のチューナ231, 232は、スプリッタ22を介して接続されている。このため、スプリッタの2個の出力端子間のアイソレーションが十分でない場合、一方のチューナの入力インピーダンスのステップ状の遷移により、他方のチューナへの信号を瞬時劣化させてしまう可能性がある。

【0043】

例えば、アナログテレビ放送信号の場合、バンド切り替え時に、図15(C)に示すようなスパイクノイズが映像信号に乗り、それが表示画面の映像中にノイズとして現れると言う問題が発生する。

【0044】

例えばチューナ231で選択中のチャンネルの放送番組の映像を、表示装置部26の表示画面で観視しているときに、チューナ232での選局チャンネルを変更したときに、バンド切り替えがあると、その切り替え時に表示映像にノイズが表れる。

【0045】

また、例えばチューナ232で選択中のチャンネルの放送番組を記録再生装置部27で録画中に、チューナ231での選局チャンネルを変更したときに、バンド切り替えがあると、その切り替え時にノイズが記録信号に重畳されて記録されてしまう。

【0046】

この発明は、以上のような問題点にかんがみ、信号分配部を通じて入力信号が複数の信号処理部に分配されるときに、信号処理部に設けられている信号用スイッチの切り替えによる他の信号処理部の信号の劣化を軽減することを目的とする。

【課題を解決するための手段】

【0047】

上記の課題を解決するために、この発明は、

入力信号を、複数の出力端に分配して出力する信号分配手段と、

前記信号分配手段の前記複数の出力端のそれぞれに接続される信号処理部の複数個と、

前記複数個の信号処理部の少なくとも一つに設けられ、前記信号分配手段からの信号の

伝送路をオン・オフする1または複数の信号用スイッチと、

10

20

30

40

50

前記 1 または複数の信号用スイッチの切替信号を発生する切替信号発生部と、

前記切替信号により前記信号処理部の前記 1 または複数の信号用スイッチが切り替えられたときに、前記 1 または複数の信号用スイッチが切り替えられた信号処理部の入力インピーダンスが、急峻でない遷移をするように抑制するための抑制手段と、

を備える信号処理装置を提供する。

【0048】

上記の構成のこの発明によれば、信号処理部の 1 または複数の信号用スイッチが切り替えられたときに、当該 1 または複数の信号用スイッチが切り替えられた信号処理部の入力インピーダンスが、急峻でない遷移をする。このため、信号分配部のアイソレーションが良好でない場合であっても、当該信号分配部に接続される他の信号処理部に供給する信号の劣化が軽減される。

10

【発明の効果】

【0049】

この発明によれば、信号分配部のアイソレーションが良好でない場合であっても、一の信号処理部における信号用スイッチの切り替え時における、当該信号分配部に接続される他の信号処理部に供給する信号の劣化が軽減される。

【図面の簡単な説明】

【0050】

【図 1】この発明による信号処理装置の第 1 の実施形態のテレビ受信機の構成例を示すブロック図である。

20

【図 2】図 1 の第 1 の実施形態の一部回路の構成例を示す図である。

【図 3】図 1 の第 1 の実施形態の回路動作を説明するための図である。

【図 4】この発明による信号処理装置の第 2 の実施形態の要部回路の他の構成例を示す回路図である。

【図 5】この発明の第 2 の実施形態において用いられる信号用スイッチの回路例を示す図である。

【図 6】この発明の第 2 の実施形態の要部の動作を説明するために用いる図である。

【図 7】図 1 の実施形態の要部回路のさらに他の構成例を示す回路図である。

【図 8】図 7 の例の要部の回路例を示す図である。

【図 9】図 7 の例の場合における信号用スイッチの切り替え時の特性を説明するための図である。

30

【図 10】図 7 の例の場合における信号用スイッチの切り替え時の特性を説明するための図である。

【図 11】この発明による信号処理装置の実施形態の効果を説明するために用いる図である。

【図 12】この発明による信号処理装置の実施形態の効果を説明するために用いる図である。

【図 13】この発明が適用されるテレビ受信機に用いられるフロントエンド回路の一般的な構成例を示す図である。

【図 14】この発明が適用されるテレビ受信機の一般的な構成例を示す図である。

40

【図 15】この発明の課題を説明するために用いる図である。

【発明を実施するための形態】

【0051】

以下、この発明による信号処理装置の幾つかの実施形態を、前述した図 14 を用いて説明したテレビ受信機に適用した場合を例にとって、図を参照しながら説明する。

【0052】

【第 1 の実施形態】

図 1 は、この発明による信号処理装置の第 1 の実施形態としてのテレビ受信機の構成例を示すブロックである。この図 1 の例は、前述した図 14 を用いて説明したテレビ受信機に、この発明の第 1 の実施形態を適用したもので、図 14 の例と同一部分には、同一参照

50

符号を付して、その説明を省略する。

【0053】

この発明による第1の実施形態においては、信号分配部としてのスプリッタ22と、信号処理部の例としての第1および第2のチューナ231および232との間に、それぞれインピーダンス遷移補正回路31, 32を設ける。

【0054】

この例では、第1および第2のチューナ231, 232のIC化されているフロントエンド回路1の外部に、インピーダンス遷移補正回路31, 32は設けられる。

【0055】

そして、このインピーダンス遷移補正回路31, 32のそれぞれは、独立に、制御部20からの第1および第2の制御信号EN1およびEN2のそれぞれにより制御される。

10

【0056】

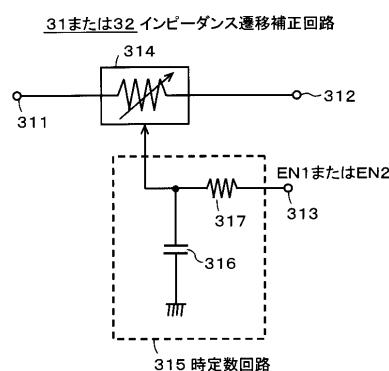

図2に、インピーダンス遷移補正回路31、32の構成例を示す。このインピーダンス遷移補正回路31, 32は、制御部20から受ける制御信号が、第1の制御信号EN1, 第2の制御信号EN2というように異なるのみで、同様の構成を備える。

【0057】

すなわち、このインピーダンス遷移補正回路31、32は、スプリッタ22からの信号を受ける入力端子311、チューナ231に供給する出力信号を出力する出力端子312および制御部20からの制御信号EN1を受ける制御端子313を備える。

【0058】

そして、入力端子311と出力端子312との間に、例えばMOS(Metal Oxide Semiconductor)型電界効果トランジスタ(以下、MOSトランジスタという)からなる可変抵抗素子314が接続される。この可変抵抗素子314の制御端子(例えばゲート)には、制御端子313を通じて、制御部20からの制御信号EN1またはEN2が、時定数回路315を通じて供給される。

20

【0059】

時定数回路315は、この例では、キャパシタ素子316と、抵抗317とからなる。可変抵抗素子314の制御端子は、キャパシタ素子316を通じて接地端に接続され、キャパシタ素子316と可変抵抗素子314の制御端子との接続点は、抵抗317を通じて制御端子313に接続されている。

30

【0060】

可変抵抗素子314は、バンド切り替えがなされないときには、所定の抵抗値とされる。例えば、可変抵抗素子314がMOSトランジスタにより構成されるときには、制御信号EN1またはEN2として、そのゲートに、ドレイン-ソース間の導通抵抗が所定の抵抗値となる電圧EAが供給される(図3参照)。

【0061】

そして、インピーダンス遷移補正回路31, 32の可変抵抗素子314は、その後段の第1、第2のチューナにおいて、バンド切り替えがなされる際に、当該バンド切り替えに先立ち、制御信号EN1、EN2のそれぞれによりオフ状態(インピーダンスが無限の状態)とされる。例えば、可変抵抗素子314がMOSトランジスタにより構成されるときには、そのゲートに供給される制御信号EN1またはEN2がゼロ電位とされて、MOSトランジスタがオフの状態となるようにされる。

40

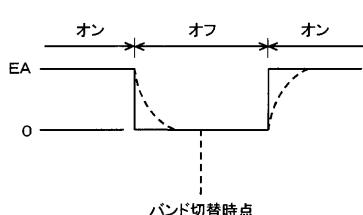

【0062】

ただし、このとき、図3で実線で示すように、制御信号EN1またはEN2は、ステップ状に変化するが、時定数回路315のため、MOSトランジスタのゲート電位の変化は、図3で破線で示すように急峻ではなく、連続的で、緩やかな変化となる。

【0063】

そして、バンド切り替えが完了した後、インピーダンス遷移補正回路31, 32の可変抵抗素子314は、制御信号EN1、EN2のそれぞれにより、元の所定の抵抗値の状態(オン状態)に戻るように制御される。

50

## 【0064】

そして、後述するように、インピーダンス遷移補正回路31, 32は、時定数回路を備え、インピーダンス遷移スイッチがオン状態からオフ状態への遷移時およびオフ状態からオン状態への遷移時に、その時定数回路の時定数に従って遷移する。

## 【0065】

このときにも、図3で実線で示すように、制御信号EN1またはEN2は、ステップ状に変化するが、時定数回路315のため、MOSトランジスタのゲート電位の変化は、図3で破線で示すように急峻ではなく、連続的で緩やかな変化となる。

## 【0066】

すなわち、時定数回路315により、ステップ状の急峻な変化が、急峻でない変化に抑制される。

10

## 【0067】

第1のチューナ231が動作中に、第2のチューナ232内のフロントエンド回路1の信号用スイッチ11A, 11B, 11Cが切り替えられる場合には、インピーダンス遷移補正回路32が、図3に示したように、制御信号EN2により制御される。

## 【0068】

また、第2のチューナ232が動作中に、第1のチューナ231内のフロントエンド回路1の信号用スイッチ11A, 11B, 11Cが切り替えられる場合には、インピーダンス遷移補正回路31が、図3に示したように、制御信号EN1により制御される。

## 【0069】

20

したがって、バンド切り替え時のインピーダンス遷移が急峻ではなく、連続的で緩やかな変化となる。これにより、図15を用いて説明したようなスパイク状ノイズが、バンド切り替えをしたチューナ以外の他のチューナへの信号に重畠されてしまうことが防止され、当該他のチューナの信号劣化が軽減される。すなわち、動作中の他のチューナに対してノイズの悪影響を与えることなく、チューナのフロントエンド回路1でバンド切替を行うことができる。

## 【0070】

## [第2の実施形態]

第1の実施形態では、チューナ231および232の信号入力側にインピーダンス遷移補正回路を設けるようにした。これに対して、第2の実施形態は、信号路中にインピーダンス遷移補正回路のような補正回路を設けることなく、バンド切替スイッチおよび当該バンド切替用スイッチに供給する切替信号のステップ状の急峻な変化を、急峻でない変化に抑制する構成とする。

30

## 【0071】

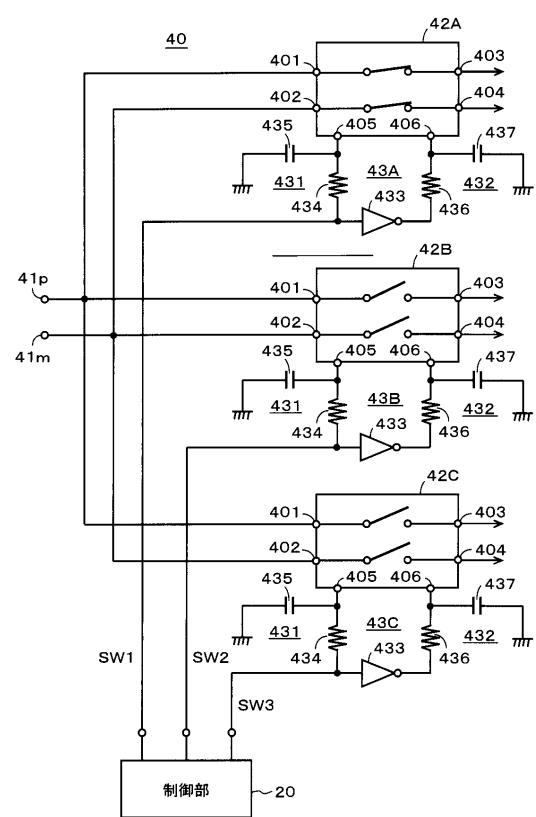

図4は、この第2の実施形態におけるフロントエンド回路のバンド切替スイッチおよびその切替信号の制御回路40の構成例を示す図である。図4の回路40は、制御部20を除き、1チップICとされているフロントエンド回路の一部の回路を示すものである。

## 【0072】

この図4の例は、信号が平衡形式(差動形式)の場合の例であり、フロントエンド回路の正側入力端子41pおよび負側入力端子41mには、スプリッタ22からの正側入力信号Vi pおよび負側入力信号Vi mが供給される。

40

## 【0073】

正側入力端子41pおよび負側入力端子41mを通じて入力された正側入力信号Vi pおよび負側入力信号Vi mは、信号用スイッチ42A, 42B, 42Cのそれぞれに供給される。

## 【0074】

信号用スイッチ42AはバンドVL用の信号用スイッチ、信号用スイッチ42BはバンドVH用の信号用スイッチ、信号用スイッチ42CはバンドU用の信号用スイッチ、である。制御部20は、バンド切替信号SW1を信号用スイッチ42Aに、バンド切替信号SW2を信号用スイッチ42Bに、バンド切替信号SW3を信号用スイッチ42Cに、それ

50

それ、切替信号補正回路 43A, 43B, 43C を通じて供給する。

【0075】

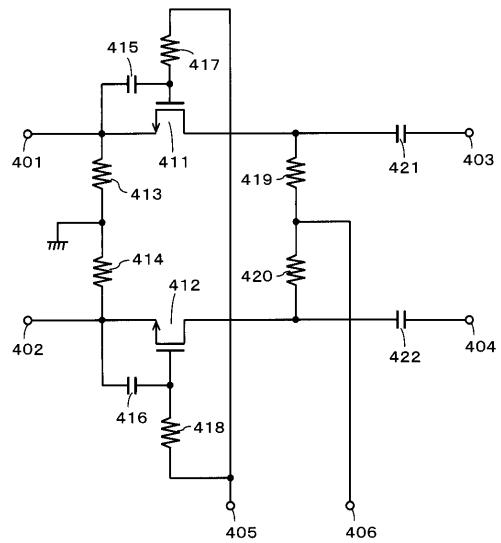

信号用スイッチ 42A, 42B, 42C は、全く同一の構成を備えるものである。図5 は、信号用スイッチ 42A, 42B, 42C の一つの構成例を示すものである。

【0076】

正側入力端子 401 は、半導体スイッチである n 型 MOS トランジスタ 411 のソースに接続され、負側入力端子 402 は、半導体スイッチである n 型 MOS トランジスタ 411 のソースに接続される。

【0077】

また、正側入力端子 401 と負側入力端子 402 との間には、抵抗 413 および 414 の直列回路が接続され、抵抗 413 と 414 の接続中点が接地される。 10

【0078】

MOS トランジスタ 411 のソースとゲートとの間にはキャパシタ素子 415 が接続され、トランジスタ 412 のソースとゲートとの間にはキャパシタ素子 416 が接続される。そして、MOS トランジスタ 411 のゲートは、抵抗 417 を通じてゲート制御端子 405 に接続される。また、MOS トランジスタ 412 のゲートは、抵抗 418 を通じてゲート制御端子 405 に接続される。

【0079】

MOS トランジスタ 411 のドレインと、MOS トランジスタ 412 のドレインとの間には、抵抗 419 および 420 の直列回路が接続され、抵抗 413 と 414 の接続中点がドレイン制御端子 406 に接続される。 20

【0080】

そして、MOS トランジスタ 411 のドレインは、キャパシタ素子 421 を介して正側出力端子 403 に接続され、MOS トランジスタ 412 のドレインは、キャパシタ素子 422 を介して負側出力端子 404 に接続される。

【0081】

抵抗 413, 414, 417, 418, 419, 420 は、全て信号源インピーダンスに対して十分大きな値、好適には 10k 以上の値とされている。

【0082】

図5の例においては、上述したように、MOS トランジスタ 411, 412 のソースの直流電位は、常に接地電位 (0V) に固定されている。 30

【0083】

そして、図4に示すように、バンド切替信号 SW1, SW2 または SW3 が、切替信号補正回路 43A, 43B または 43C を通じて、ゲート制御端子 405 およびドレイン制御端子 406 に供給される。

【0084】

切替信号補正回路 43A, 43B および 43C は同じ構成を示し、それぞれ時定数回路 431 と 432 とを備えると共に、インバータ 433 とを備える。時定数回路 431 は、抵抗 434 とキャパシタ素子 435 とからなり、また、時定数回路 432 は、抵抗 436 とキャパシタ素子 437 とからなる。 40

【0085】

そして、バンド切替信号 SW1, SW2 または SW3 は、時定数回路 431 を通じてゲート制御端子 405 に供給される。また、バンド切替信号 SW1, SW2 または SW3 は、インバータ 433 により極性判定された後、時定数回路 432 を通じてドレイン制御端子 406 に供給される。

【0086】

すなわち、信号用スイッチ 42A, 42B, 42C のゲート制御端子 405 とドレイン制御端子 406 とには、相補的に制御電位が与えられて、信号用スイッチ 42A, 42B, 42C の切替制御がなされる。

【0087】

半導体スイッチであるMOSトランジスタ411および412がオンとされるときには、ゲート制御端子405がハイレベルとなり、ドレイン制御端子406がローレベルとなるバンド切替信号SW1, SW2またはSW3が供給される。また、MOSトランジスタ411および412がオフとされるときには、その逆に、ゲート制御端子405がローレベルとなり、ドレイン制御端子406がハイレベルとなるバンド切替信号SW1, SW2またはSW3が供給される。

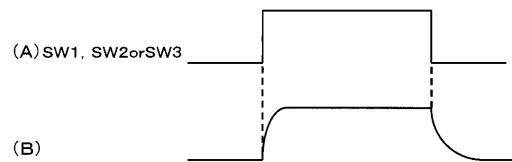

#### 【0088】

以上の第2の実施形態においては、バンド切替信号SW1, SW2またはSW3は、時定数回路431および432を備える切替信号補正回路43A, 43Bまたは43Cを通じて信号用スイッチ42A, 42B, 42Cのそれぞれに供給される。

10

#### 【0089】

このため、信号用スイッチ42A, 42B, 42Cのそれぞれには、図6(A)に示すようなステップ状のバンド切替信号SW1, SW2またはSW3は、時定数回路431, 432により、急峻な変化ではなく、連続的に緩やかに変化する信号に変換されて供給される。

#### 【0090】

したがって、図15を用いて説明したようなスパイク状ノイズが、バンド切り替えをしたチューナ以外の他のチューナへの信号に重畠されてしまうことが防止され、当該他のチューナの信号劣化が軽減される。

#### 【0091】

なお、信号用スイッチ42A, 42B, 42Cのオン・オフを制御するためには、ゲート制御端子405に、バンド切替信号SW1, SW2, SW3を切替信号補正回路43A, 43B, 43Cを通じて供給すればよい。

20

#### 【0092】

しかし、この実施形態のように、ドレイン制御端子406を、ゲート制御端子405とは相補的な電位変化をするように制御すれば、アナログスイッチとしての信号用スイッチ42A, 42B, 42Cの歪み特性を良好なものとすることができます。

#### 【0093】

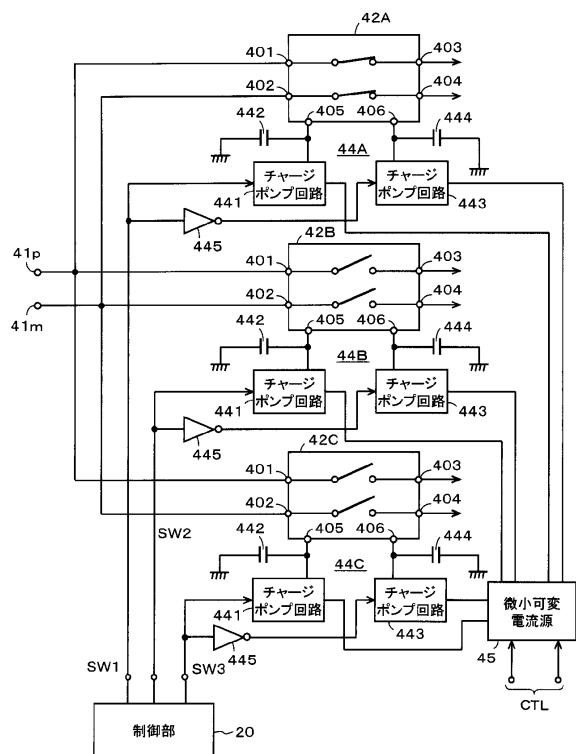

##### 【第3の実施形態】

第3の実施形態は、第2の実施形態の変形例である。第2の実施形態では、フロントエンド回路のバンド切替スイッチおよびその切替信号の制御回路40においては、時定数回路を備える切替信号補正回路43A, 43B, 43Cを用いた。

30

#### 【0094】

第3の実施形態では、時定数回路ではなく、チャージポンプ回路を用いた切替信号補正回路を備える。

#### 【0095】

図7は、この第3の実施形態の場合におけるフロントエンド回路のバンド切替スイッチおよびその切替信号の制御回路40の構成例を示す図である。この図7の回路40も、制御部20を除き、1チップIC化されており、図7に示される端子は、ICの端子ピンに相当する。

40

#### 【0096】

この図7において、図4の第2の実施形態の場合と同一部分には、同一参照符号を付してその詳細な説明は省略する。信号用スイッチ42A, 42B, 42Cは、図5に示した回路構成を備えるものとされている。

#### 【0097】

この第3の実施形態においては、第2の実施形態における切替信号補正回路43A, 43B, 43Cに代えて、信号用スイッチ42A, 42B, 42Cのそれに対して、切替信号補正回路44A, 44B, 44Cを設ける。そして、この第3の実施形態においては、微小可変電流源45からの微小電流が、切替信号補正回路44A, 44B, 44Cのそれぞれに供給される。その他の構成は、第2の実施形態と同様である。

50

## 【0098】

切替信号補正回路44A, 44B, 44Cのそれぞれは、同一の回路構成を備え、チャージポンプ回路441およびキャパシタ素子442と、チャージポンプ回路443およびキャパシタ素子444と、インバータ445とからなる。微小可変電流源45からの微小電流は、チャージポンプ回路443およびキャパシタ素子444のそれぞれに供給される。

## 【0099】

そして、バンド切替信号SW1, SW2, SW3は、切替信号補正回路44A, 44B, 44Cを介して、信号用スイッチ42A, 42B, 42Cのそれぞれのゲート制御端子405およびドレイン制御端子406に供給される。

10

## 【0100】

切替信号補正回路44A, 44B, 44Cにおいては、バンド切替信号SW1, SW2, SW3は、チャージポンプ回路441に供給されると共に、インバータ445により極性判定されてチャージポンプ回路443に供給される。

## 【0101】

チャージポンプ回路441および443は、これに入力されるバンド切替信号SW1, SW2, SW3に応じて、キャパシタ素子442の充放電を制御する。

## 【0102】

すなわち、バンド切替信号SW1, SW2, SW3がハイレベルのときには、チャージポンプ回路441は、キャパシタ素子442を、微小可変電流源45からの微小電流により充電するようとする。また、バンド切替信号SW1, SW2, SW3がローレベルのときには、チャージポンプ回路441は、キャパシタ素子442を、微小可変電流源45からの微小電流で放電するようとする。

20

## 【0103】

微小可変電流源45は、例えば特開平7-234731号公報などに記載されている周知の可変電流源の構成とすることができます。ここで、微小可変電流源45は、キャパシタ素子442および444を、ゆっくりと充電し、また、ゆっくりと放電させるようにするために微小電流を、チャージポンプ回路441, 443に供給する。

## 【0104】

なお、この図7の例では、微小可変電流源45は、端子ピンを通じてIC外から供給される複数ビットの電流値可変制御信号CTLにより、複数通りの電流値に制御可能とされている。図7の例では、2ビットの電流値可変制御信号CTLにより、4通りの電流値に制御可能とされている。

30

## 【0105】

そして、キャパシタ素子442の両端に得られる電圧が、ゲート制御端子405に印加される。

## 【0106】

バンド切り替え時に、信号用スイッチ42A, 42Bまたは42Cをオフからオンにするため、バンド切替信号SW1, SW2またはSW3をローレベルからハイレベルに変化させたときには、チャージポンプ回路441は、キャパシタ素子442の充電を開始する。このとき、バンド切替信号SW1, SW2またはSW3がステップ状に変化しても、キャパシタ素子442は、微小可変電流源45からの微小電流で充電がなされるため、キャパシタ素子442の両端電圧は、微小電流の電流値に応じて緩やかに上昇する。

40

## 【0107】

また、バンド切り替え時に、信号用スイッチ42A, 42Bまたは42Cをオンからオフにするため、バンド切替信号SW1, SW2またはSW3をハイレベルからローレベルに変化させたときには、チャージポンプ回路441は、キャパシタ素子442の放電を開始する。このとき、バンド切替信号SW1, SW2またはSW3がステップ状に変化しても、キャパシタ素子442は、微小可変電流源45からの微小電流で放電がなされるため、キャパシタ素子442の両端電圧は、微小電流の電流値に応じて緩やかに下降する。

50

## 【0108】

このため、バンド切替信号 SW1, SW2 または SW3 は、ステップ状に急峻に変化するものであっても、ゲート制御端子 405 のゲート制御電位は、緩やかに変化するものとなる。

## 【0109】

一方、チャージポンプ回路 443 には、インバータ 445 を通じてバンド切替信号 SW1, SW2, SW3 が供給される。したがって、チャージポンプ回路 443 は、チャージポンプ回路 441 とは、相補的な動作をする。つまり、ドレイン制御端子 406 のドレイン制御電位は、ゲート制御電位に対して相補的な変化をする。

## 【0110】

そして、このドレイン制御電位も、微小可変電流源 45 の微小電流でチャージポンプ回路 443 がドライブされるために、ゲート制御電位と同様に、ステップ状に急峻に変化するものであっても、連続的で緩やかに変化するものとなる。

## 【0111】

以上のように、この第3の実施形態においては、信号用スイッチ 42A, 42B, 42C のゲート制御端子 405 およびドレイン制御端子 406 に供給される切替制御信号は、緩やかに変化する信号である。したがって、この第3の実施形態においても、第2の実施形態と同様に、図15を用いて説明したようなスパイク状ノイズが、バンド切り替えをしたチューナ以外の他のチューナへの信号に重畠されてしまうことが防止され、当該他のチューナの信号劣化が軽減される。

## 【0112】

そして、この第3の実施形態においても、ドレイン制御端子 406 は、ゲート制御端子 405 とは相補的な電位変化をするように制御されるので、アナログスイッチとしての信号用スイッチ 42A, 42B, 42C の歪み特性を良好なものとすることができます。

## 【0113】

チャージポンプ回路 441 と 443 とは、同様の構成を備えるものである。このチャージポンプ回路 441, 443 の回路構成例を、図8に示す。

## 【0114】

図8に示すように、電源電圧 +Vcc が得られる電源端子 501 と接地端との間に、p型MOSトランジスタ 502 のソース - ドレイン間と、n型MOSトランジスタ 503 のドレイン - ソース間との直列回路が接続される。

## 【0115】

MOSトランジスタ 502 のドレインと、MOSトランジスタ 503 のドレインとの接続点は出力端子 504 に接続される。この出力端子 504 は、キャパシタ素子 442 または 444 を通じて接地されると共に、ゲート制御端子 405 またはドレイン制御端子 406 に接続される。

## 【0116】

また、電源端子 501 と接地端との間には、ゲートとドレインとが接続されてダイオード接続構成とされたp型MOSトランジスタ 505 のソース - ドレイン間と、n型MOSトランジスタ 503 のドレイン - ソース間との直列回路が接続される。そして、このMOSトランジスタ 505 のゲートと、MOSトランジスタ 502 のゲートとが接続されて、カレントミラー構成とされる。

## 【0117】

この例の場合、MOSトランジスタ 505 に流れる電流 Ia に対して、MOSトランジスタ 502 に流れる電流 Ib とは、Ia : Ic = M : 1 とされる。ここで、M は、1以上の整数である。

## 【0118】

また、電源端子 501 と接地端との間には、p型MOSトランジスタ 507 のドレイン - ソース間と、ゲートとドレインとが接続されてダイオード接続構成とされたn型MOSトランジスタ 508 のソース - ドレイン間との直列回路が接続される。そして、このMOSトランジスタ 507 のゲートと、MOSトランジスタ 502 のゲートとが接続されて、カレントミラー構成とされる。

10

20

30

40

50

Sトランジスタ508のゲートと、MOSトランジスタ503のゲートとが接続されて、カレントミラー構成とされる。

【0119】

この例の場合、MOSトランジスタ508に流れる電流 $I_c$ に対して、MOSトランジスタ503に流れる電流 $I_d$ とは、 $I_b : I_d = M : 1$ とされる。

【0120】

そして、p型MOSトランジスタ507のゲートが、スイッチ509を通じて電源端子501に接続されると共に、スイッチ510を通じてp型MOSトランジスタ511のゲートに接続される。

【0121】

また、n型MOSトランジスタ506のゲートが、スイッチ512を通じて接地端に接続されると共に、ダイオード接続されているn型MOSトランジスタ513のゲートに接続される。

10

【0122】

また、p型MOSトランジスタ511のソース-ドレイン間と、n型MOSトランジスタ513のドレイン-ソース間との直列回路が、電源端子501と接地端との間に接続される。

【0123】

さらに、電源端子501と、微小電流入力端子516との間には、ダイオード接続されたp型MOSトランジスタ514のソース-ドレイン間が接続される。微小電流入力端子516には、微小可変電流源45からの基準微小電流 $I_o$ が供給される。

20

【0124】

そして、p型MOSトランジスタ511のゲートは、ダイオード接続されたp型MOSトランジスタ514のゲートと接続されて、カレントミラー構成とされる。

【0125】

そして、切替信号入力端子517には、チャージポンプ回路441の場合には、制御部20からのバンド切替信号SW1, SW2またはSW3は、そのままの極性で入力される。また、チャージポンプ回路443の場合には、制御部20からのバンド切替信号SW1, SW2またはSW3は、極性反転されて切替信号入力端子517に供給される。

【0126】

30

切替信号入力端子517からの切替信号は、そのままの極性でスイッチ509に供給されると共に、インバータ515により極性反転された後、スイッチ510およびスイッチ512に供給される。

【0127】

次に、以上の構成のチャージポンプ回路の動作を、チャージポンプ回路441の場合を例に説明する。

【0128】

微小可変電流源45からは常時基準微小電流 $I_o$ が出力されているので、カレントミラー構成により、MOSトランジスタ511および513を通じても、微小電流 $I_o$ に対応する電流が流れている。

40

【0129】

バンド切替信号SW1、SW2またはSW3がローレベルからハイレベルになったときには、図8に示すように、スイッチ509がオン、スイッチ510および512はオフとされる。

【0130】

このため、このときには、カレントミラー構成により、MOSトランジスタ505および506の系に、対応する電流が流れる。そして、MOSトランジスタ505に対してカレントミラー構成とされているMOSトランジスタ502に電流 $I_c$ が流れ、この電流 $I_c$ によりキャパシタ素子442または444が0Vから充電される。

【0131】

50

また、バンド切替信号 SW1、SW2 または SW3 がハイレベルからローレベルになったときには、図 8 の状態とは逆に、スイッチ 509 がオフ、スイッチ 510 および 512 はオンとされる。

【0132】

すると、このときには、カレントミラー構成により、MOSトランジスタ 507 および 508 の系に、対応する電流が流れる。そして、MOSトランジスタ 508 に対してカレントミラー構成とされているMOSトランジスタ 503 に電流  $I_d$  が流れ、この電流  $I_d$  によりキャパシタ素子 442 または 444 は、電源電圧から放電される。

【0133】

キャパシタ素子 442 または 444 の充電または放電が完了する時間は、キャパシタ素子 442, 444 の値およびチャージポンプの電流  $I_c$ ,  $I_d$  の電流値により決まる。 10

【0134】

図 8 の例のチャージポンプ回路では、出力段のカレントミラー電流比  $M : 1$  を、最適設計することにより、キャパシタ素子 442 または 444 の充電または放電の電流値が定められる。そして、微小可変電流源 45 が、電流値可変制御信号 CTL により可変制御されることにより、基準微小電流  $I_o$  の値が可変される。

【0135】

チャージポンプ回路 443 の場合には、バンド切替信号 SW1, SW2, SW3 が極性反転されて供給されるので、バンド切替信号 SW1, SW2, SW3 のハイレベル、ローレベルに対する動作関係が逆になる。 20

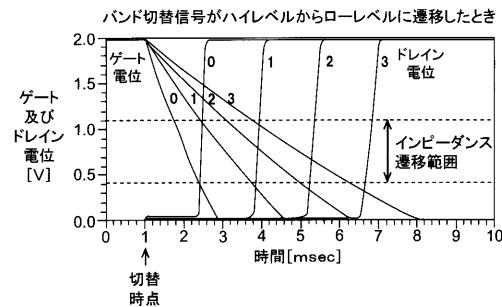

【0136】

図 9 は、バンド切替信号 SW1, SW2, SW3 がハイレベルからローレベルになったときの、信号用スイッチ 42A, 42B または 42C におけるMOSトランジスタ 411, 412 のゲートおよびドレインの電位変化を表したものである。この図 9 の例の場合は、時間 = 1 msec 時に、ハイレベル ローレベルのバンド切替信号 SW1, SW2 または SW3 が与えられている。

【0137】

図 9 に示されるように、ゲート電位は、2V (電源電圧) からキャパシタ素子 442 の放電により次第に低下し、数 msec 後には 0V (接地電位) に落ちる。逆に、ドレイン電位は、0V (接地電位) から 2V (電源電圧) まで上昇している。 30

【0138】

図 9において、インピーダンス遷移範囲とは、MOSトランジスタ 411, 412 のオン抵抗が変化する範囲に相当することを意味している。すなわち、図 9 の例によれば、信号用スイッチ 42A, 42B, 42C のインピーダンス遷移時間が、1 msec から数 msec 程度になっていることが判る。

【0139】

なお、図 9において、各ゲート電位の遷移曲線およびドレイン電位の遷移曲線の右横の数字は、微小可変電流源 45 における 2 ビットの電流値可変制御信号 CTL のコード値を示している。すなわち、この例では、電流値可変制御信号 CTL のコード値が大きくなると基準微小電流値が減少し、結果として充放電時間が長くなる。 40

【0140】

図 9 に示すように、ゲートとドレインの電位変化が対称的では無い。これは、MOSトランジスタ 411, 412 のゲート電位は、キャパシタ素子 442 の値とチャージポンプ回路の電流値  $I_c$  だけで決まるのに対し、MOSトランジスタ 411, 412 のドレイン電位は、ゲート電位に影響されるためである。

【0141】

具体的には、MOSトランジスタ 411, 412 のゲート電位が高いときは、MOSトランジスタ 411, 412 のオン抵抗が小さいため、チャージされる電流がキャパシタ素子 444 に蓄積されずに、MOSトランジスタを介して接地側に排出される。このため、キャパシタ素子 444 の電位は、時間に比例した上昇はしないのである。 50

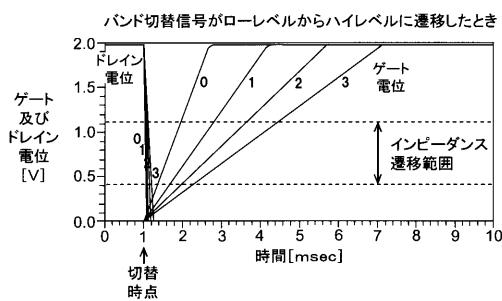

## 【0142】

図10は、図9とは反対に、バンド切替信号SW1, SW2, SW3がローレベルからハイレベルになったときの、信号用スイッチ42A, 42Bまたは42CにおけるMOSトランジスタ411, 412のゲートおよびドレインの電位変化を表したものである。この場合も、時間 = 1 msec 時に、ローレベル ハイレベルのバンド切替信号SW1, SW2またはSW3が与えられている。

## 【0143】

なお、前述もしたように、信号用スイッチ42A, 42B, 42Cのオン・オフを制御するためには、ゲート制御端子405に、バンド切替信号SW1, SW2, SW3を切替信号補正回路43A, 43B, 43Cを通じて供給すればよい。

10

## 【0144】

ただし、この実施形態のように、ドレイン制御端子406を、ゲート制御端子405とは相補的な電位変化をするように制御すれば、アナログスイッチとしての信号用スイッチ42A, 42B, 42Cの歪み特性を良好なものとすることができるものである。

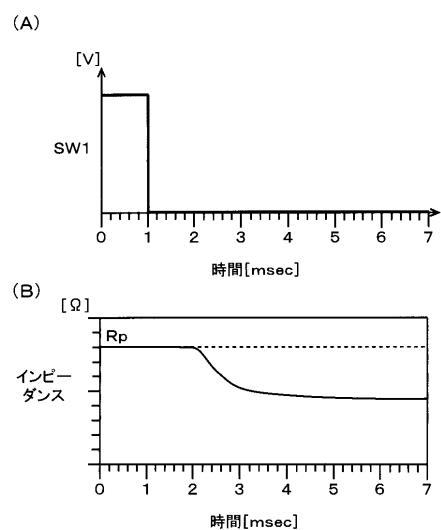

## 【0145】

図11は、例えば信号用スイッチ42Aへのバンド切替信号SW1がハイレベルからローレベルに切り替わる時のチューナのフロントエンド回路での入力インピーダンスの遷移状態を示している。時間 = 1 msec で、バンド切替信号SW1がハイレベルからローレベルに切り替わってから、インピーダンスはステップ状ではなく、緩やか（滑らか）に遷移し、ほぼ2 msec の遷移時間有している。

20

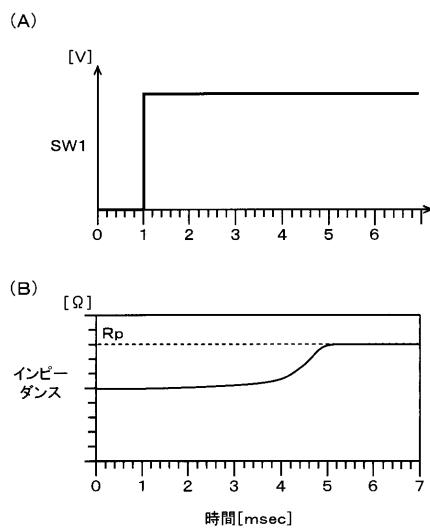

## 【0146】

また、図12は、例えば信号用スイッチ42Aへのバンド切替信号SW1がローレベルからハイレベルに切り替わる時のチューナのフロントエンド回路での入力インピーダンスの遷移状態を示している。この場合も、時間 = 1 msec で、バンド切替信号SW1がローレベルからハイレベルに切り替わってから、インピーダンスはステップ状ではなく、緩やか（滑らか）に遷移し、ほぼ4 msec の遷移時間有している。

30

## 【0147】

## [実施形態の効果]

以上説明したように、上述の実施形態によれば、図11および図12に示したように、チューナ231, 232において、バンド切り替えをした時に遷移する入力インピーダンスが、ステップ状の急峻な遷移ではなく、連続的で緩やかな遷移特性となる。

## 【0148】

このため、スプリッタ22が有する出力端子間のアイソレーションが良好でない場合においても、動作している他のチューナの受信信号に対して劣化を与えることなく、チューナにおいてバンド切替動作が可能となる。

## 【0149】

## [その他の実施形態および変形例]

信号用スイッチ42A, 42B, 42Cに供給するバンド切替信号SW1, SW2, SW3をステップ状のものから、連続的で緩やかな変化するものに抑制する切替信号補正回路としては、上述の実施形態に限られるものではない。

40

## 【0150】

例えば、ゲート制御端子405に供給するゲート制御電位およびドレイン制御端子406に供給するドレイン制御電位を、PWM (Pulse Width Modulation) 信号とし、スイッチ切替時に、そのパルス幅を連続的かつ緩やかに変化させようにもよい。

## 【0151】

なお、上述の説明においては、電界効果トランジスタは、MOS型としたが、MOS型にのみに限らないことは言うまでもない。

## 【0152】

上述の実施形態では、信号処理部としてのチューナは、3個の信号用スイッチを備えるものとしたが、信号用スイッチは、1個または2個でもよく、また、4個以上であっても

50

もちろんよい。1個の信号用スイッチの場合には、信号処理部が信号分配部の出力端に対して接続されるか否かの選択となる。

【 0 1 5 3 】

また、上述の実施形態では、信号分配部の複数個の出力側に接続されるすべての信号処理部に信号用スイッチが設けられる場合のみについて説明した。しかし、全ての信号処理部に信号用スイッチが設けられる必要はなく、信号分配部の複数個の出力側の、少なくとも一つの信号処理部に信号用スイッチが設けられていれば、この発明は適用可能となる。

【 0 1 5 4 】

上述の実施形態は、テレビ放送信号の受信装置の場合に、この発明を適用した例であるが、この発明は、テレビ放送を受信する場合に限られるものではないことは言うまでもない。この発明は、信号分配部を介して、受信信号を複数個の信号処理部に供給するものであって、信号処理部が1または複数個の信号用スイッチを備える場合の全てに適用可能である。

10

## 【符号の説明】

【 0 1 5 5 】

1 ... フロントエンド回路、 2 0 ... 制御部、 2 1 ... スプリッタ (信号分配手段)、 3 1 ,

3 2 ... インピーダンス遷移補正回路、 4 2 A , 4 2 B , 4 2 C ... 信号用スイッチ、 4 3 A

、 4 3 b , 4 3 C , 4 4 A , 4 4 B , 4 4 C ... 切替信号補正回路、 4 5 ... 微小可変電流源

、 3 1 5 , 4 3 1 , 4 3 2 ... 時定数回路、 4 4 1 , 4 4 3 ... チャージポンプ回路

( 1 )

〔 2 〕

【圖 3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

【図14】

【図15】

---

フロントページの続き

(56)参考文献 特開2006-197446(JP,A)

特表2009-505601(JP,A)

特開平04-241511(JP,A)

特開2007-143031(JP,A)

特開平07-107014(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04B 1/18

H04N 5/44