(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4856363号

(P4856363)

(45) 発行日 平成24年1月18日(2012.1.18)

(24) 登録日 平成23年11月4日(2011.11.4)

(51) Int.Cl.

H03M 3/02 (2006.01)

H03F 3/217 (2006.01)

F 1

H03M 3/02

H03F 3/217

請求項の数 10 (全 18 頁)

(21) 出願番号 特願2004-151328 (P2004-151328)

(22) 出願日 平成16年5月21日 (2004.5.21)

(65) 公開番号 特開2004-350295 (P2004-350295A)

(43) 公開日 平成16年12月9日 (2004.12.9)

審査請求日 平成19年3月20日 (2007.3.20)

審判番号 不服2010-8716 (P2010-8716/J1)

審判請求日 平成22年4月23日 (2010.4.23)

(31) 優先権主張番号 60/472488

(32) 優先日 平成15年5月22日 (2003.5.22)

(33) 優先権主張国 米国(US)

(73) 特許権者 500587067

アギア システムズ インコーポレーテッド

アメリカ合衆国, 18109 ペンシルヴァニア, アレンタウン, アメリカン パークウェイ エヌイー 1110

(74) 代理人 100094112

弁理士 岡部 謙

(74) 代理人 100064447

弁理士 岡部 正夫

(74) 代理人 100085176

弁理士 加藤 伸晃

(74) 代理人 100104352

弁理士 朝日 伸光

最終頁に続く

(54) 【発明の名称】 安定な高次デルタ・シグマ誤差フィードバック変調器およびそのような変調器において使用される雑音伝達関数

## (57) 【特許請求の範囲】

## 【請求項 1】

- a) 入力信号を受信する第1入力、第2入力および出力を有する第1の信号ミキサと、

- b) 前記第1の信号ミキサの出力と結合された入力および出力信号を規定するいくつかの高次ビットを有する出力を有する打切り要素と、

- c) 前記打切り要素によって出力された出力以外の前記第1信号ミキサの出力のビットを低次ビットとして提供する手段とを備え、前記提供する手段は、前記打切り要素と結合された入力および前記低次ビットを提供する出力を含み、さらに、

- d) 前記提供する手段の出力と結合された入力および前記第1信号ミキサの前記第2入力と結合された出力を有する雑音伝達関数要素を備え、雑音伝達関数がL次伝達関数であり、Lが少なくとも3であり、前記高次ビットの数がL+1であり、そして、前記雑音伝達関数の安定性が前記入力信号に依存しない、装置。

## 【請求項 2】

前記雑音伝達関数要素の帯域外利得が限定されない、請求項1に記載の装置。

## 【請求項 3】

- e) 前記打切り要素の前記出力と結合された入力を有するデジタル・アナログ変換器をさらに備える、請求項1に記載の装置。

## 【請求項 4】

- e) 前記打切り要素の前記出力と結合された入力を有するスクランプラーをさらに備える、請求項1に記載の装置。

10

20

## 【請求項 5】

L が 4 または 5 である、請求項 1 に記載の装置。

## 【請求項 6】

前記提供する手段が、前記第 1 信号ミキサの前記出力と結合された第 1 入力と、前記打切り要素の前記出力と結合された第 2 入力と、出力とを有する第 2 信号ミキサを含む、請求項 1 に記載の装置。

## 【請求項 7】

- a ) 入力信号を受信するステップと、

- b ) 前記入力信号を第 2 信号と混合して、第 3 信号を生成するステップと、

- c ) 前記第 3 信号を打ち切りして、出力信号を規定するいくつかの高次ビットを生成するステップと、

- d ) 前記第 3 信号の低次ビットを第 4 信号として提供するステップと、

- e ) 前記第 4 信号を雑音伝達関数に適用して前記第 2 信号を生成するステップとを有し、前記雑音伝達関数が L 次伝達関数であり、L が少なくとも 3 であり、前記高次ビットの数が L + 1 であり、前記雑音伝達関数要素の安定性が、前記入力信号に依存しない、方法。

## 【請求項 8】

前記雑音伝達関数の帯域外利得が限定されない、請求項 7 に記載の方法。

## 【請求項 9】

- f ) 前記出力信号をアナログ信号に変換するステップをさらに有する、請求項 7 に記載の方法。

## 【請求項 10】

L が 4 または 5 である、請求項 7 に記載の方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、デルタ - シグマ誤差フィードバック ( Δ - S I G M A ) 变調器に関する。より具体的には、本発明は、具体的にはデジタル・アナログ変換器 ( D A C ) および位相ロック・ループ ( P L L ) において使用される Δ - S I G M A 变調器である Δ - S I G M A 变調器の雑音伝達関数 ( N T F ) に関する。

## 【背景技術】

## 【0002】

## 優先権の主張

2003年5月22日に出願された「 S T A B L E H I G H - O R D E R D E L T A - S I G M A M O D U L A T O R S 」という名称であり、 Peter Kiss 、 Jesus Arias 、および Dandan Li を発明者として列挙する米国仮特許出願第 60/472,488 号明細書の出願日に対する利益を主張する。この仮出願は、明らかに参照によって本発明に組み込まれている。本発明は、仮出願において記載されている例示的な実施形態のいずれかの 1 つの任意の要件に限定されるものではない。

## 【0003】

デルタ - シグマ ( Δ - S I G M A ) 变調器が、下の § 1.2.1 において導入される。次いで、デジタル・アナログ変換器 ( D A C ) および位相ロック・ループ ( P L L ) における Δ - S I G M A 变調器の使用が、 § 1.2.2 において導入される。最後に、高性能 Δ - S I G M A 变調器を設計する課題について、 § 1.2.3 において議論する。

## 【0004】

## § 1.2.1 变調器

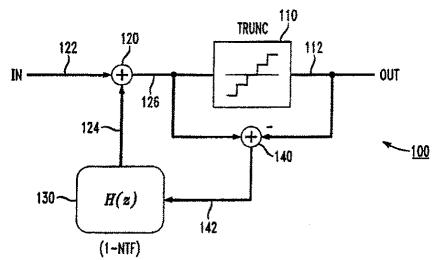

たとえば 变調器を使用する D A C などデータ変換器が、混合信号チップ ( すなわち、アナログ回路およびデジタル回路の両方を有するチップ ) においてブロックを構築する際に使用してきた。図 1 に示すように、 Δ - S I G M A 变調器 100 には、第 1 ミキサ ( アダ - など ) 120 と、打切り要素 110 と、第 2 ミキサ 140 と、雑音伝達関数 ( N T F )

10

20

30

40

50

要素 130 とが含まれる ( $H(z) = 1 - NTF$  であるが、簡略化のために「NTF」を使用することが可能である)。第 1 ミキサ 120 には、入力信号を受信する第 1 入力 122 と、NTF 要素 130 の出力と結合された第 2 入力 124 と、打切り要素 120 の入力と結合された出力 126 とが含まれる。打切り要素 110 の出力 112 は、出力として提供される。第 2 ミキサ 140 には、第 1 ミキサ 120 の出力 126 と結合された第 1 入力と、打切り要素 110 の出力 112 と結合された第 2 入力と、NTF 要素 130 の入力と結合された出力 142 とが含まれる。第 2 ミキサ 140 は、ビット 126 からより高次のビット 112 を減算して、より低次のビット 142 を出力として提供する。打切り要素 110 は、入力信号のビット数を低減する。また、変調器は、オーバーサンプリングを使用する。NTF 要素 130 を使用して、打切り(すなわち量子化)誤差整形を実施することが可能である。

10

#### 【0005】

変調器の設計には、速度と分解能との兼合い、アナログ回路の精度、およびデジタル回路の複雑性が含まれる可能性がある。高分解能で高速のアナログ・デジタル変換器(ADC)またはDACを獲得する1つの可能な方式は、高次および/またはマルチビット変調器を使用することである。高次量子化誤差整形は、単一ループまたは多重ループ(すなわち、カスケードまたはMASH)構造によって達成することができる(たとえば、参照によって本明細書に組み込まれ、かつこれ以後「ノーズワージ(Norsworthy)・テキスト」と呼ぶS.R.Norsworthy、R.Schreier、およびG.C.Temes、Eds.、Delta-Sigma Data Converters: Theory, Design, and Simulation. NY: IEEE Press、1996年参照)。

20

#### 【0006】

量子化誤差または量子化雑音伝達関数(NTF)の選択は、変調器の達成可能な性能において重要な役割を果たす。NTFの帯域内減衰は、ゼロ点によって提供されるが、NTFの帯域外利得(OBG)は、極によって制御される。OBGを低減することにより、ループの安定性が改善されるが、帯域内雑音は増大し、それにより、変調器の信号対雑音比(SNR)は悪化する。高次ループ(すなわち1より大きい)では、DCのゼロ点をNTFの外部に移動させ、ゼロ点を信号帯域に配置して、所与のオーバーサンプリング比(OSR)について最大雑音抑制を提供することによって、より高い性能を獲得することが可能である(たとえば、参照によって本明細書に組み込まれ、かつこれ以後「シュライヤ(Schreier)アーティクル」と呼ぶR.Schreier、「An empirical study of high-order single-bit delta-sigma modulators」、IEEE Trans. Circuits Syst. II, vol. 40, no. 8, 461~466ページ、1993年8月参照)。また、高次変調器は、大きな入力信号に対して不安定になり易い(たとえば、ノーズワージ・テキスト、第4~5章参照)。

30

#### 【0007】

打切り要素(または量子化装置)110が非線形であるということにより、高次ループの安定性の分析が課題となる。「不安定」は、変調器が、大きいが必ずしも非拘束ではない状態と、線形モデルによって予測されたSNRと比較して不十分なSNRとを提示することを意味する(たとえば、ノーズワージ・テキスト、セクション4.1参照)。

40

#### 【0008】

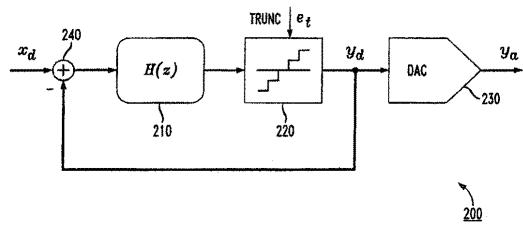

##### § 1.2.1.1 出力フィードバック 变调器

いわゆる「出力フィードバック」(OF)変調器が一般的である。デルタ・シグマADCおよびDAC(たとえば図2を参照)に使用されるOF変調器は、それぞれ、フィードバック合計またはフィードフォワード合計を有する積分器またはアキュムレータの鎖を含むことが可能である。現在、安定性を保証するために、保守的な経験則(たとえば、参照によって本明細書に組み込まれ、かつこれ以後「Leeアーティクル」と呼ぶW.L.Lee、「A novel higher-order interpolative

50

modulator topology for high resolution oversampling A/D converters」、Master's thesis、Massachusetts Institute of Technology、マサチューセッツ州ケンブリッジ、1987年6月参照)、および根軌跡法(たとえば、参照によって本明細書に組み込まれ、かつこれ以後「Ritonиемアーティクル」と呼ぶT. Ritonием、T. Karema、およびH. Tenhunen、「The design of stable high-order 1-bit sigma-delta modulators」、Proc. IEEE Int. Symp. Circuits Syst.、1990年5月、3267~3270ページ参照)を、拡大シミュレーションと共に使用することが可能である。リー・アーティクルにおいて提供される経験則は、単一ビット変調器に適用可能である。これは、NTFのOBGが1.5未満であることを必要とする。マルチビット高次変調器の設計では、NTFのOBGについてより緩和された値(3.5未満など)が安定のために十分である(たとえば、参照によって本明細書に組み込まれ、かつこれ以後「Rheeアーティクル」と呼ぶW. Rhee、A. Ali、およびB. Song、「A 1.1GHz CMOS fractional-N frequency synthesizer with a 3b 3rd-order delta-sigma modulator」、Dig. IEEE Int. Solid-State Circuits Conf.、2000年2月、198~199ページ参照)。OBGの低減は、NTF要素において実施される。

## 【0009】

10

残念ながら、安定性を保証する既存の技術は、少なくとも2つの些細とは言えない欠点を有する。第1に、単一ループ高次変調器の達成可能な性能を厳しく限定する。より具体的には、OBGを低減することにより、帯域内雑音が増大し、それにより分解能が低下する。第2に、H(z)要素によって使用されるNTFを設計するとき、変調器の安定性を保証するために、予防措置および長いシミュレーションが必要である。

## 【0010】

20

## § 1.2.1.2 誤差フィードバック 变調器

誤差フィードバック(EF)変調器が、DAC(たとえば、ノーズワージ・テキスト; 参照によって本明細書に組み込まれ、かつこれ以後「ムスマン(Musmann)特許」と呼ぶH. G. MusmannおよびW. Korte、「Generalized interpolative method for digital/analog conversion of PCM signals」、米国特許第4,467,316号明細書、1984年8月21日; および参照によって本明細書に組み込まれ、かつこれ以後「ノーズ(Naus)・アーティクル」と呼ぶP. J. Naus、E. C. Dijkmans、E. F. Stikvoort、A. J. McKnight、D. J. Holland、およびW. Bradinal、「A CMOS stereo 16-bit D/A converter for digital audio」、IEEE J. Solid-State Circuits、vol. 22、no. 3、390~395ページ、1987年6月参照)、およびフラクショナルN PLL(たとえば、参照によって本明細書に組み込まれ、かつこれ以後「ウィリングガム(Willingham)・アーティクル」と呼ぶS. Willingham、M. Perrott、B. Setteberg、A. Grzegorek、およびB. McFarland、[An integrated 2.5GHz delta-sigma frequency synthesizer with 5<sup>1</sup>s settling and 2Mb/s closed loop modulation]、Dig. IEEE Int. Solid-State Circuits Conf.、2000年2月、200~201ページ参照)において広く使用されている。

## 【0011】

30

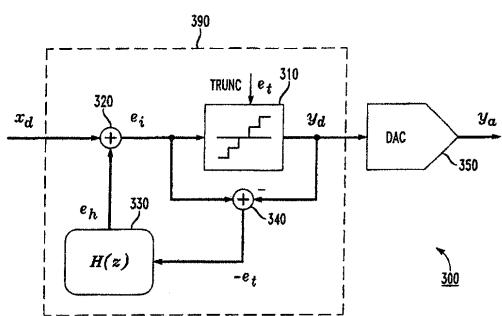

図3Aは、図1に示した変調器100などのEF変調器390を含むDAC300と、アナログDAC350とのブロック図である。EF変調器390を使用して、量

40

50

子化（すなわち打切り）雑音を形成する。（i）より簡単な回路を使用することが可能である、および／または（ii）アナログD A C 3 5 0 がより良好な線形性を有する（周波数に関して）ように、アナログD A C 3 5 0 がより少ないビットを処理することが望ましい可能性がある。図1のE F変調器100と同様に、E F変調器390には、第1混合要素320と、打切り要素310と、第2混合要素340と、N T F要素330とが含まれる。

【0012】

§ 1.2.1.3 高性能 E F変調器を設計する課題

高次N T F要素（ループ・フィルタなど）では、内部リミタをしばしば使用して、内部信号のオーバーフローを保護する（たとえば、ノーズ・アーティクル参照）。また、設計の安定性は、広範なシミュレーションによって一般的に慎重に確認される。

【0013】

ループ・フィルタ  $h(t)$  のインパルス応答のLノルムに基づくE F変調器の十分安定性試験が提案された（たとえば、参照によって本明細書に組み込まれ、かつこれ以後「シュライヤIIアーティクル」と呼ぶR. SchreierおよびY. Yang、「Stability tests for single-bit sigma-delta modulators with second-order FIR noise transfer functions」、Proc. IEEE Int. Symp. Circuits Syst. 1992年5月、1316～1319ページ参照）。シュライヤIIアーティクルは、具体的には2次N T Fを有する单一ビットの場合について、デルタ・シグマ・ループを安定に維持することを議論する。シュライヤIIアーティクルのこのLノルム試験は、ディザー信号も同様に含むように拡大された（たとえば、参照によって本明細書に組み込まれ、かつこれ以後「ノーズワージ・アーティクル」と呼ぶS. R. Norsworthy、「Optimal nonrecursive noise shaping filters for oversampling data converters, Part 1: Theory」、Proc. IEEE Int. Symp. Circuits Syst. 1993年5月、1353～1356ページ参照；また、ノーズワージ・テキストのセクション3.14.1参照）。残念ながら、これらの技術は、入力信号が、小さいまたは拘束された信号に制約されることを必要とする。

【特許文献1】米国仮特許出願第60/472,488号

【非特許文献1】S. R. Norsworthy, R. Schreier, およびG. C. Temes, Eds., Delta-Sigma Data Converters: Theory, Design, and Simulation. NY: IEEE Press, 1996年

【非特許文献2】R. Schreier, 「An empirical study of high-order single-bit delta-sigma modulators」、IEEE Trans. Circuits Syst. II, vol. 40, no. 8, 461～466ページ、1993年8月

【非特許文献3】W. L. Lee, 「A novel higher-order interpolative modulator topology for high resolution oversampling A/D converters」、Master's thesis, Massachusetts Institute of Technology、マサチューセッツ州ケンブリッジ、1987年6月

【非特許文献4】T. Ritonиеми, T. Karema, およびH. Tenhunen, 「The design of stable high-order 1-bit sigma-delta modulators」、Proc. IEEE Int. Symp. Circuits Syst. 1990年5月、3267～3270ページ

【非特許文献5】W. Rhee, A. Ali, およびB. Song, 「A 1.1 GHz CMOS fractional-N frequency synthesizer with a 3b 3rd-order delta-sigma modulat

10

20

30

40

50

or」、Dig. IEEE Int. Solid-State Circuits Conf.、2000年2月、198~199ページ

【特許文献2】米国特許第4,467,316号明細書

【非特許文献6】P. J. Naus、E. C. Dijkmans、E. F. Stikvoort、A. J. McKnight、D. J. Holland、およびW. Bradinal、「A CMOS stereo 16-bit D/A converter for digital audio」、IEEE J. Solid-State Circuits, vol. 22, no. 3, 390~395ページ、1987年6月

【非特許文献7】Willingham、M. Perrott、B. Setterberg、A. Grzegorek、およびB. McFarland、[An integrated 2.5 GHz delta-sigma frequency synthesizer with 51s settling and 2Mb/s closed loop modulation]、Dig. IEEE Int. Solid-State Circuits Conf.、2000年2月、200~201ページ

【非特許文献8】R. SchreierおよびY. Yang、「Stability tests for single-bit sigma-delta modulators with second-order FIR noise transfer functions」、Proc. IEEE Int. Symp. Circuits Syst.、1992年5月、1316~1319ページ

【非特許文献9】S. R. Norsworthy、「Optimal nonrecursive noise shaping filters for oversampling data converters, Part 1: Theory」、Proc. IEEE Int. Symp. Circuits Syst.、1993年5月、1353~1356ページ

【非特許文献10】R. Schreier、「The delta-sigma toolbox for Matlab」、マットラボ・コードおよび説明書、1997~2003ページ

【非特許文献11】T. BairdおよびT. S. Fiez、「Improved delta-sigma DAC linearity using data weighted averaging」、Proc. IEEE Int. Symp. Circuits Syst.、vol. 1、1995年5月、13~16ページ

【非特許文献12】O. Mencer、M. Platzner、M. Morf、およびM. Flynn、「Object-oriented domain specific compilers for programming FPGAs」、IEEE Trans. VLSI Syst.、vol. 9, no. 1, 205~210ページ、2001年2月

【発明の開示】

【発明が解決しようとする課題】

【0014】

以上を考慮すると、安定なシグマ変調器が必要である。安定なシグマ変調器は、そのような変調器がより大きなまたは拘束されない入力信号を備えることができる場合、有利である可能性がある。安定なシグマ変調器は、安定性を保証する技術がOBGを低減するときに生じるような帯域内雜音および分解能を犠牲にしない場合、有利である可能性がある。安定なシグマ変調器は、より高次のNTFを有する安定な変調器を提供することが有利である可能性がある。要するに、より良好な変調器が有用であり、DACおよびPLLなど、変調器を使用する装置を改良するために使用することができる。

【課題を解決するための手段】

【0015】

本発明によれば、デジタル・アナログ変換器および位相ロック・ループなどにおいて使

10

20

30

40

50

用されるような E F 变调器の安定性は、打切り要素からの  $L + 1$  高次ビットを備える  $L$  次雜音伝達関数 (NTF) を含むことによって保証することができる。そのような E F 变调器の安定性は、入力信号に依存しない。

本発明による少なくともいくつかの実施形態では、NTF の帯域外利得は限定されない。

本発明による少なくともいくつかの実施形態では、 $L$  は、少なくとも 4 である。本発明による少なくともいくつかの実施形態では、 $L$  は、4 または 5 である。

【発明を実施するための最良の形態】

【0016】

本発明は、安定な E F 变调器を提供する新規な方法および／または装置を含むことが可能である。以下の記述は、当業者が本発明を作成および使用するのを可能にするために提示され、かつ具体的な応用例およびその要件の文脈において提供されている。したがって、本発明による実施形態の以下の記述は、例示および記述を提供するが、開示する厳密な形態のみとする、またはそれで本発明を限定することを意図していない。開示する実施形態に対する様々な修正が、当業者には明らかになるであろう。また、以下で述べる一般的な原理は、他の実施形態および応用例に適用することが可能である。たとえば、一連の行為を記述することが可能であるが、行為の順序は、一行為の実施が他の行為の完了に依存しないとき、他の実施形態では異なることが可能である。さらに、非依存性の行為は、並行して実施することが可能である。記述において使用される要素、行為、または命令のいずれも、本発明に対して決定的または必須として明瞭に記述されない限り、そのように構築されるべきではない。また、本明細書において使用する際に、冠詞「a」は、1つまたは複数の項目を含むことを意図する。唯一の項目を意図する場合は、「一」という用語または同様の語を使用する。したがって、本発明は、示される実施形態に限定されることを意図せず、本発明者は、あらゆる特許にすることが可能な主題事項が記述されたものとして本発明を見なす。

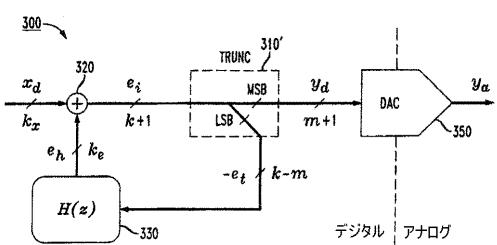

【0017】

§ 4.1 E F 变调器の例示的な雜音伝達関数

再び図 3 A のブロック図を参照すると、打切り要素 310 は、入力の最上位ビット  $y_d$  (MSB) をそれに続く DAC 350 に提供する。ミキサ 340 は、入力から MSB を除去して、最下位ビット (LSB) を NTF 要素 (デジタル・ループ・フィルタ H(z) など) 330 に供給する。LSB が NTF 要素 330 に提供されるということを、図 3 B の簡略的な機能図に示す。打切り要素 310 について追加の白色モデル (たとえば、ノーズワージ・テキストのセクション 2.3 参照) を使用して、デルタ-シグマ变调器を線形モデルによって記述することができる。この線形モデルによれば、打切り要素 310 の出力  $y_d$  は、以下のように表すことが可能である。

【数 1】

$$y_d(z) = x_d(z) + (1 - H(z))e_t(z) \\ = STF(z)x_d(z) + NTF(z)e_t(z) \quad (1)$$

上式で、 $STF(z) = 1$  は、信号伝達関数であり、 $NTF(z) = 1 - H(z)$  は、打切り誤差 (または打切り雜音) 伝達関数である。

【0018】

NTF(z) が、有限インパルス応答 (FIR) 伝達関数であるとき、H(z) も、E F 变调器の FIR 関数である (式 (1) 参照)。したがって、OFトポロジの場合とは対照的に、H(z) に累積はない。唯一の累積は、入力ノードにおける追加中に生じるが、これにはすぐ後に打切り動作が続く。したがって、各内部信号のビット長は、数値分析を必要とせずに、分析により精確に予測することができる。

10

20

30

40

50

## 【0019】

図3Bを参照すると、たとえば、NTF要素330は、mビットをビット長に追加するFIRループ・フィルタH(z)であると想定されている。入力合計320は、せいぜいもう1ビットを追加する。すべての内部信号を制限して維持するために、ループに入るいかなるものも出て行く必要がある。したがって、 $y_d$ は、少なくとも $m + 1$ ビットを有するはずである（すなわち、「m」はH(z)により、「1」は入力合計による）。表記によって、入力 $x_d$ は $k_x$ ビットを有し、フィードバック $c_h$ は $k_e$ ビットを有する。有効な初期条件である $k_c = k_x$ が保持され、かつ $y_d$ が $m + 1$ の最小値に維持される場合、 $e_i$ は、せいぜい $k_x + 1$ ビットを有し、 $k_x - m$ の LSB が、ループに送り返される。これは、 $k_x$ ビットの $e_h$ となる。したがって、 $k_x = k_e = k$ が定常状態について保持され、すべての内部信号は、図3Bに示すように制限される。実用的な利用のために $k > m$ であり、したがって $k - m$ は負になることがないことに留意されたい。すなわち、本発明によれば、E/F変調器の十分安定性基準は、以下のように表すことができる： $m + 1$ ビットのトランケータおよびFIRループ・フィルタH(z)を有し、データフローにおけるmビットの増大に寄与するE/F変調器が安定である。10

## 【0020】

低周波数信号帯域において低打切り誤差エネルギーを達成するために、NTF(z)は、高域通過特性を有するべきである。たとえば、L次微分器 $(1 - z^{-1})^L$ をNTF(z)として選択することが可能である。Lは、デルタ-シグマ・ループの次数をも決定する。このFIR NTF(z)のすべてのゼロ点は、DCにある。したがって、OBGは $2^L$ であり、これは、L次変調器の最大に可能なOBGである。最適化されたゼロ点がFIR NTF(z)において使用されるとき、OBGは、 $2^L$ の付近に留まり、ごくわずかにより小さい。本発明によれば、十分安定性基準は、無限インパルス応答(IIR)NTF(z)が使用される場合にも適用可能である。20

## 【0021】

比較において、上記の§1.2.1.1から、OF変調器は、安定性のためにはるかにより小さいOBG値(3.5など)を必要とすることを思い出されたい。したがって、有限値の極が、OF変調器のNTF(z)に追加され、それがIIRフィルタに変換された。30

## 【0022】

以上の議論は、トランケータを実用的な真に非線形の回路として扱い、したがって、式(1)において使用される追加の白色雑音モデルの簡略的な想定に依存しない。また、以上の内容は、十分な分析基準であるが、必ずしも必要基準および十分基準の両方ではないことに留意されたい。すなわち、トランケータにおいて $L + 1$ ビットを使用することは、すべての内部信号を制限して維持し、それにより高次ループを安定に維持するのに十分であるが、保存性ではない。

## 【0023】

## §4.1.1 本発明による例示的な安定E/F変調器

第1例として、 $NTF(z) = (1 - z^{-1})^L$ および $H(z) = 1 - NTF(z)$ を有するL次E/Fループを考慮する。最悪のシナリオでは、 $(1 - z^{-1})^L$ に適用される $a \pm 1$ 交代シーケンスは、 $2^L$ （すなわちLビットの出力）となる。したがって、 $H(z)$ のデータフローへの寄与は、Lビットより少なくなる。すなわち、mの最低値はLであり、したがって、 $y_d$ が $m + 1 = L + 1$ ビットを有する場合、すべての内部信号は制限される、すなわち、L次ループは安定である。 $NTF(z) = (1 - z^{-1})^4$ および $H(z) = z^{-1}(4 - 6z^{-1} + 4z^{-2} - z^{-3})$ を有する4次ループの場合では、mは4であり、 $y_d$ は、この場合に記述する基準により5ビットを有することになる。40

## 【数2】

\*最適ゼロ点FIR NTF(z) およびH(z) = 1 - NTF(z) m ≤ L ⇒

$y_d$ がL+1ビットを有する場合→安定な $\Delta\Sigma$

\*L=4およびOSR=8について：

NTF(z) = (1 - 1, 98z<sup>-1</sup> + z<sup>-2</sup>) \* (1 - 1, 88z<sup>-1</sup> + z<sup>-2</sup>) およびH(z) = z<sup>-1</sup> (3, 86 - 5, 72z<sup>-1</sup> + 3, 86z<sup>-2</sup> - z<sup>-3</sup>) m ≤ 4 ⇒  $y_d$ が5ビットを有する場合→安定な $\Delta\Sigma$

この第1の例示的なEF変調器は、ハードウェア効率が良い。

## 【0024】

第2例として、最適ゼロ点FIR NTF(z)を有するL次EFループを考慮する。ゼロ点は単位円内に留まるので、H(z) = 1 - NTF(z)の寄与は、Lビットを超えない。すなわち、最適ゼロ点をL次のNTF(z)において使用するとき、H(z)のmビットの寄与は、常にLよりわずかに小さい、すなわちm < Lである（至近整数に概数化されるmおよびLの値は、同じとすることが可能である）。4次ループでOSR = 8の場合では、(1 - 1, 98z<sup>-1</sup> + z<sup>-2</sup>) (1 - 1, 88z<sup>-1</sup> + z<sup>-2</sup>)のNTF(z)が得られる（たとえば、シュライヤ・アーティクル参照）。再び、mは4であり、 $y_d$ が5ビットを有する場合、変調器は、ここで記述する基準に基づいて安定である。

## 【数3】

\*最適ゼロ点FIR NTF(z) およびH(z) = 1 - NTF(z) m ≤ L ⇒

$y_d$ がL+1ビットを有する場合→安定な $\Delta\Sigma$

\*L=4およびOSR=8について：

NTF(z) = (1 - 1, 98z<sup>-1</sup> + z<sup>-2</sup>) \* (1 - 1, 88z<sup>-1</sup> + z<sup>-2</sup>) およびH(z) = z<sup>-1</sup> (3, 86 - 5, 72z<sup>-1</sup> + 3, 86z<sup>-2</sup> - z<sup>-3</sup>) m ≤ 4 ⇒  $y_d$ が5ビットを有する場合→安定な $\Delta\Sigma$

この第2例は、性能について最適化される。

## 【0025】

## §4.1.2 代替および改善

再び、(1 - z<sup>-1</sup>)<sup>L</sup> FIR NTF(z) およびL+1ビットを有するEF変調器が安定である。この安定なEF変調器は、2<sup>L</sup>のOBGを有する。一般に、OBGを低減することにより、安定性が改善される（たとえば、ノーズワージ・テキストのセクション5.5参照）。したがって、有限値の極をNTF(z)に追加することによって（すなわち、初期FIR NTFをIIRフィルタとすることによって）この変調器のOBGを低減しても、安定性が低下しないと想定することが妥当である。すなわち、安定なL次(L+1)ビットのEF変調器が、すべての可能なOBG値について予期される。

## 【0026】

本発明によるEF DACは、マルチビット・デジタル・アナログ変換を必要とする可能性がある。1ビットDACは本質的に線形なので、デジタル出力 $y_d$ において单一ビットデータフローを獲得することが一般に望ましい。しかし、非常に線形なマルチビットDACが利用可能である（たとえば、ノーズワージ・テキストの第8章参照）。代替として、そのような高次変調器は、カスケード構成において使用することが可能である（たとえば、ムスマン特許参照）。

## 【0027】

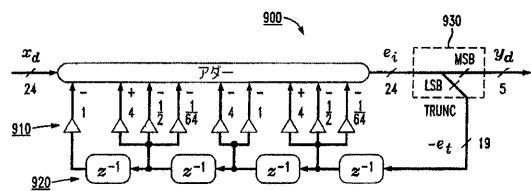

N T F の選択は、本発明の実施（たとえば回路として）に影響を与える可能性がある。たとえば、最適ゼロ点N T F の使用は、H ( z ) のデジタル回路実施態様において高価な乗算器を必要とする可能性があり、一方、純粋な微分装置N T F の実施には、乗算器は必要ではない。しかし、図9を参照する以下の§ 4 . 3において提示する設計例は、最適ゼロ点N T F でさえ、乗算器のない単一デジタル回路によって有効に実施することができることを実証する。

【0028】

§ 4 . 2 本発明による雑音伝達関数を有する E F 变調器の例示的な応用例

本発明による E F 变調器は、図3 A に示したアナログD A C に適用されるビット数を低減するようなD A C において使用することが可能である。そのような E F 变調器は、ウィリンガム・アーティクルにおいて記述したものなど、P L L において使用することも可能である。 10

【0029】

§ 4 . 3 本発明によるシミュレーションした例示的な E F 变調器の特性

§ 4 . 3 . 1 シミュレーションした E F 变調器

高次 E F D A C ( 図3 A および図3 B ) の振舞いを示すために、4次变調器をマットラボにおいてシミュレーションした。N T F の最適ゼロ点は、R . S chreier 、「The delta-sigma toolbox for Matlab」、マットラボ・コードおよび説明書、1997~2003ページに記載されたツールボックスを使用して設計された。このツールボックスは、<http://www.mathworks.com/matlabcentral/fileexchange>においてオンラインで利用可能であり、これ以後「マットラボ ツールボックス」と呼ぶ。E F N T F ( z ) の z 領域の式は、以下によって与えられる。 20

【数4】

$$E F : N T F ( z ) = \frac{(1 - 1.98 z^{-1} + 1.00 z^{-2})(1 - 1.88 z^{-1} + 1.00 z^{-2})}{1}$$

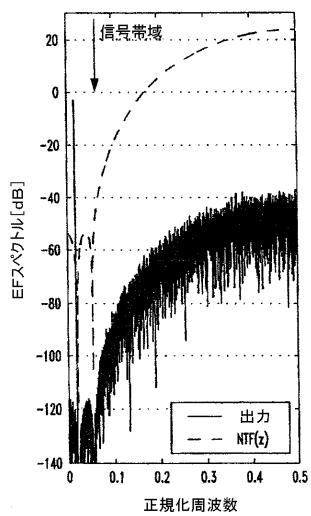

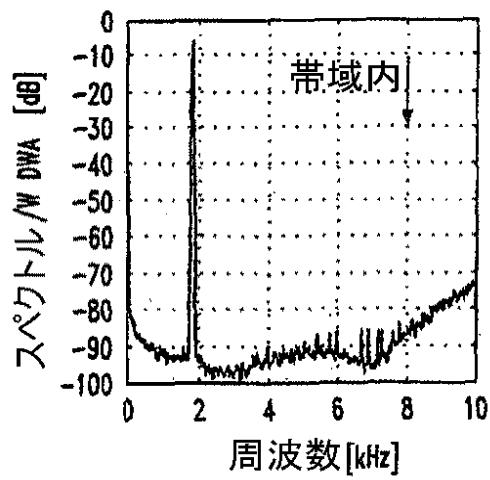

この式は、数百万のサンプルについて安定なままであった。5ビット出力データ・ストリーム  $y_d$  の  $2^{14}$  点ハン (Hann)・ウインドウFFTを図4に示す。デジタル入力  $x_d$  は、 $k_x = 24$  ビットであるように量子化された。5ビット打切り誤差は、4次FIR N T F で帯域から積極的に押し出されたので、93.1dBのピークS N R が、O S R が8の低い値についてさえ獲得された。 30

【0030】

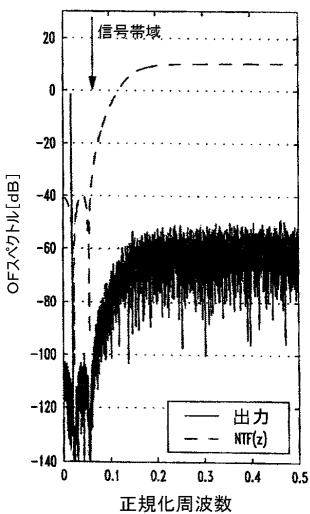

比較のために、図5は、同様の4次5ビットD A C の出力スペクトルを示すが、O F トポロジを使用して設計された（図2を思い出されたい）。ループを安定に維持するために、N T F のO B G を3 . 3 に限定しなければならなかった。O F N T F ( z ) の z 領域の式は、以下によって与えられる。

【数5】

$$O F : N T F ( z ) = \frac{(1 - 1.98 z^{-1} + 1.00 z^{-2})(1 - 1.88 z^{-1} + 1.00 z^{-2})}{(1 - 0.82 z^{-1} + 0.19 z^{-2})(1 - 0.88 z^{-1} + 0.46 z^{-2})}$$

この变調器は、シミュレーションした E F アーキテクチャより約12dB低い81.2dBのピークS N R を達成した。

【0031】

図6は、2つの4次5ビット最適ゼロ点のE F 变調器およびO F 变调器の達成可能な性能を比較する。これは、ピークS N R および対応する入力信号振幅  $A_u$  をO B G の関数として示す。図示したように、O F 变调器の性能は、O B G > 3 . 6 のとき、突然降下する。グラフは、そのようなO F システムは、O B G > 4 . 1 では安定な動作を全く維持する 50

ことができないことを示す。O B G が高い O F 变調器は、入力信号が鮮鋭な移行を含む場合、不安定になることに留意されたい。入力信号の帯域幅が限定されている場合でも、O F 变調器は、始動中に不安定になることがあり、回復しない可能性がある。

【0032】

一方、E F 变調器は、図示したように、利用可能な入力範囲が約 0.7 V / V (フル・スケールに正規化) まで小さく減少する O B G の可能な全範囲について安定なままである。E F 变調器は、入力信号の鮮鋭な移行および始動条件に対して反応しない。これらの 2 つの 4 次 5 ビット最適ゼロ点の E F 变調器および O F 变調器の最適な S N R シナリオを、それぞれ図 4 および 5 に示した。

【0033】

上記で記述した安定性の実験は、広範な O S R、ループ次数 (L)、および対応するビット数 (N = L + 1) について実施された。E F 变調器は、O B G = 1 . . . 2<sup>L</sup> の全範囲について大きな入力信号 (A<sub>u</sub> > 0.5 V / V) に対して安定なままであることが確認された。E F 变調器は、N T F が F I R 伝達関数であるとき、O B G = 2<sup>L</sup> について最適な性能を達成した (たとえば、図 6 の O B G = 16 = 2<sup>4</sup> 点参照)。

10

【0034】

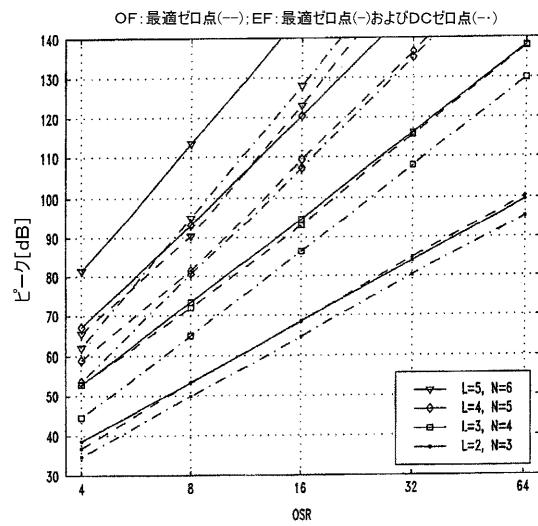

図 7 のグラフは、最適ゼロ点を有する様々な次数の E F 变調器および O F 变調器についてピーク S N R の比較を示す。N T F (z) = (1 - z<sup>-1</sup>)<sup>L</sup> を有する D C ゼロ点 E F 变調器は、簡単なデジタル回路で実施することができるので、魅力的である可能性がある。したがって、やはりプロットした。しかし、シミュレーションは、D C ゼロ点 E F 变調器の性能が、より高次において (L = 5 など) 最適ゼロ点 E F 变調器の性能より優れてい 20 るだけであることを示す。L = 2 では、O F 变調器も安定であり、したがって、E F 变調器を使用することは、大きな利点ではない。しかし、L = 3 では、O F 变調器の性能は、ループの安定性が脆弱であることによって限定されるので、E F 变調器は、明らかに O F 变調器より性能が優れている。

20

【0035】

大まかな定量的比較を表に示す。

【表 1】

| ΔSNR (dB)                               | L=2, N=3 | L=3, N=4 | L=4, N=5 | L=5, N=6 |

|-----------------------------------------|----------|----------|----------|----------|

| EF <sub>opt</sub> vs. OF <sub>opt</sub> | ±0       | +1       | +10      | +20      |

| EF <sub>dc</sub> vs. OF <sub>opt</sub>  | -4       | -7       | -2       | +4       |

30

表は、L = 2 . . . 5 および N = 3 . . . 6 について、最適ゼロ点 E F 变調器 (E F<sub>opt</sub>) の S N R 利得対最適ゼロ点 O F 变調器 (O F<sub>opt</sub>) の S N R 利得をまとめたものである。D C ゼロ点 E F 变調器 (E F<sub>dc</sub>) の S N R 利得も、図 7 に示され、かつ表の比較に含まれている。S N R は O S R と共に変化するので、平均概数値が表に含まれている。たとえば、4 次 5 ビット E F<sub>dc</sub> 变調器は、O F<sub>opt</sub> と比較して S N R がわずかに約 2 dB 足りないが、E F<sub>dc</sub> は、O F<sub>opt</sub> より実施が著しく簡単である。再び、4 次 5 ビット变調器が E F<sub>opt</sub> トポロジによって実施されるとき、表に示すように、O F<sub>opt</sub> より約 10 dB 大きい S N R を獲得することができる (図 4、5、および 7 は、この場合、S N R = 11.9 dB の「精確な」値を示す)。結果に対する变調器の非線形な振舞いおよび数値誤差の影響のために、所与の値は近似である。それにもかかわらず、図 7 および表は、本発明による E F<sub>opt</sub> 变調器を使用することによって S N R が劇的に改善されることを示す。

40

【0036】

§ 4.3.2 例示的な E F 变調器

本発明による 4 次 5 ビット E F D A C の原型が、離散構成要素から構築された。この原型を使用して、高次ループの安定性に関するシミュレーション結果を実験的に検証

50

し、マルチビットD A Cのアナログ回路の不全により起こり得る悪影響を調査した。

【0037】

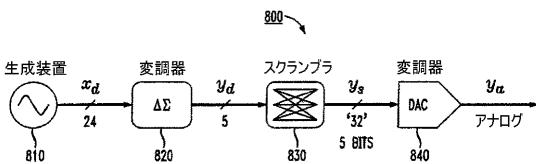

図8に示すように、原型800には、デジタル(正弦波など)信号生成装置810と、EF変調器820と、スクランブル830と、D A C(アナログD A Cなど)840とが含まれる。EF変調器820は、24ビット入力 $x_d$ (デジタル正弦波生成装置810によって提供される)および5ビット出力 $y_d$ を有する。出力 $y_d$ は、信号 $y_s$ を生成するスクランブル830によってスクランブルされる。次いで、信号 $y_s$ は、32要素(すなわち5ビット)D A C840によってアナログ信号 $y_a$ に変換される。

【0038】

図9は、図8の変調器820として使用することが可能である最適ゼロ点4次5ビットEF変調器のデジタル実施態様900を示す。4という非常に低いOSRを使用して、高速応用例について10ビットの精度を実証した。したがって、ループ・フィルタは、 $H(z) = 3.4883z^{-1} - 5.0071z^{-2} + 3.4883z^{-3} - z^{-4}$ によって(上記の式(1)から、マットラボツールボックスを使用して)与えられる。これらの係数は、2進演算をシフトおよび加算/減算することによって実施することができる、高価な乗算器を回避することができる(たとえば、図9のシフト要素910および遅延要素920参照)。たとえば、係数 $3.4883 \cdot 4 - 1 / 2 - 1 / 64$ および $-5 \cdot 0071 \cdot -4 - 1$ である。係数の近似誤差は、結果として得られるNTF(z)の著しい変化を回避するように十分小さく、約0.1dB SNRのペナルティとなるだけである。トランケータ930は、単にビットを分割する。5つのMSBは出力 $y_d$ を構成し、一方、19 LSB打切り誤差 $-e_L$ は、再びループ・フィルタ $H(z)$ に供給される。

【0039】

1%の許容度の抵抗器によって実施される要素間の不整合によるマルチビットD A Cの非線形性に対処するために、データ加重平均(DWA)(たとえば、参照によって組み込まれ、かつこれ以後「ベアード・アーティクル」と呼ぶR.T.BairdおよびT.S.Fiez、「Improved delta-sigma D A C linearity using data weighted averaging」、Proc.IEEE Int.Symp.Circuits Syst.、vol.1、1995年5月、13~16ページ参照)を使用することが可能である。10ビットの精度を目標としていたので、DWAによって提供される1次不整合の形成は十分であった。OSR > 4のとき、より高次の信号対雑音およびひずみ比(S N D R)を達成するために、2次不整合形成(たとえば、ノーズワージ・テキストのセクション8.3参照)を使用することができる。

【0040】

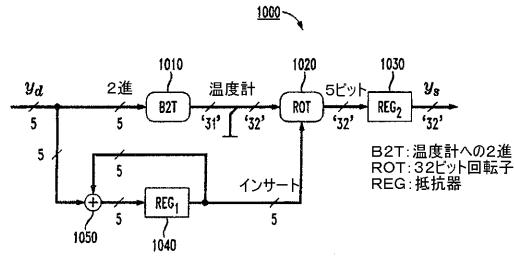

図10は、図8のD A C800においてスクランブル830として使用することが可能である例示的なDWAスクランブル1000のブロック図である。DWAスクランブル1000は、バレル・シフタ(ROT)1020を使用して温度計コード化ワードを回転させる。5ビット抵抗器(REG<sub>1</sub>)1040が、各サンプルの出力値 $y_d$ によって増大された回転指標を保持する。回転子が円形であるという性質により、指標アダーハ、出力を5ビットに打ち切る。スクランブルの最後の抵抗器(REG<sub>2</sub>)が、信号経路におけるデータ依存遅延を回避する。

【0041】

図8のシステム800では、 $\times 86$ プロセッサ上で整数算術を使用して、様々なデジタル論理(生成装置810、変調器820、および/またはスクランブル830など)を実施することが可能である。代替として、そのようなデジタル論理は、デジタル信号プロセッサ(D S P)および/またはフィールド・プログラミング可能ゲート・アレイ(F P G A)を使用して実施することが可能である。

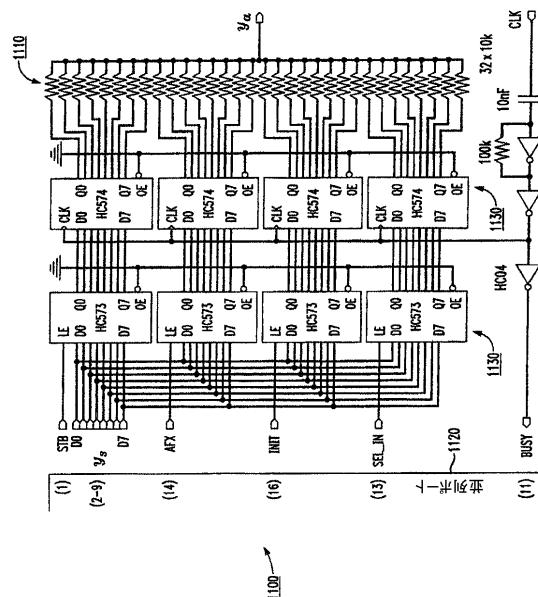

【0042】

図11は、図8のシステム800においてD A C840として使用することが可能である例示的な(アナログ)D A C1100を示す。32線温度計コード化デジタル出力 $y_s$

10

20

30

40

50

は、パーソナル・コンピュータ( P C )の並行ポート 1120 および 8 ビット・バッファ 1130 を使用して、32 抵抗器 1110 「アナログ」 D A C とインターフェースされる。抵抗器 1110 の共通ノードは、D A C のアナログ出力  $y_a$  を提供する。回路のタイミングは、精確な外部クロック( C L K )によって制御される。

#### 【 0043 】

離散構成要素の実験セットアップは、集積回路 I C シナリオを模倣する(商用の実施態様では、チップでなく集積回路を使用する可能性が高いことに留意されたい)。実験用の原型では、D A C のサンプリング率は、実験に使用される P C の並行ポートによって 64 k H z に限定された。サンプリング率を増大させるために、デジタル論理は、ベル研究所において開発されたストリーム・コンパイラ( A S C )を使用してザイリンクス・バーテックス( Xilinx Virtex ) 300 F P G A 上においても実施される(たとえば、参照によって組み込まれ、かつこれ以後「メンサー・アーティクル」と呼ぶ O . M e n c e r 、 M . P l a t z n e r 、 M . M o r f 、 および M . F l y n n 、「 O b j e c t - o r i e n t e d d o m a i n s p e c i f i c c o m p i l e r s f o r p r o g r a m m i n g F P G A s 」、 I E E E T r a n s . V L S I S y s t . , v o l . 9 、 n o . 1 、 2 0 5 ~ 2 1 0 ページ、 2 0 0 1 年 2 月 参照)。F P G A カードによって支持される最大クロック率は、 1 0 0 M H z である。A S C によって実施されるデジタル論理および最適化が簡単であることにより、ザイリンクス・バーテックス 300 F P G A 上で実行される 7 0 M H z 出力サンプリング率が獲得される。

#### 【 0044 】

図 8 ~ 11 を参照して上記で記述した最適ゼロ点を有するプロトタイプ 4 次 5 ビット E F D A C の実験結果について、図 12 a ~ 12 c を参照して記述する。効果的なサンプリング率は、 64 k H z であった。高次ループは、数時間の動作後依然として安定であった。マルチビット D A C のアナログ出力  $y_a$  は、ローデ( R o h d e ) & シュワルツ( S c h w a r z ) F S E A スペクトル分析装置によって獲得された。獲得されたスペクトルを P C において事後処理して、 8 k H z ( すなわち O S R = 4 ) の帯域幅において S N D R 値を獲得した。

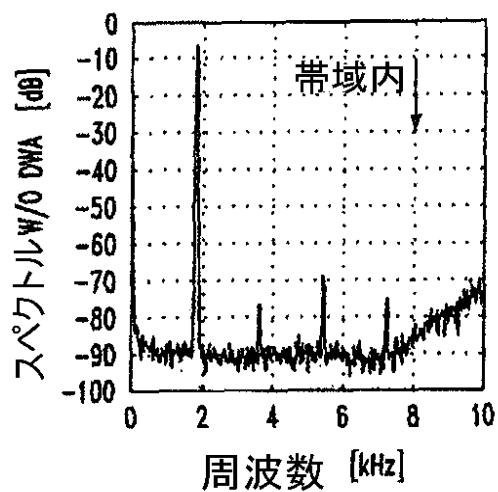

#### 【 0045 】

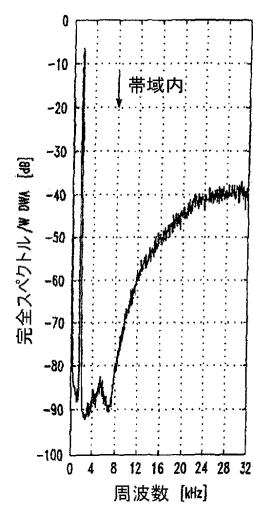

図 12 ( a ) は、 D W A スクランブル 830 ( 分解能帯域幅( R B W ) : 30 H z ) を使用しない帯域内出力スペクトルを示す。大きな高調波および増大した雑音フロアを獲得することができ、これにより、 S N D R は 58.7 d B に限定される。図 12 ( b ) に示すように、 D W A スクランブル 830 を稼動することによって、高調波の内容は無視できるようになり、雑音フロアは著しく減少する( R B W : 30 H z )。2 つの N T F ( z ) 最小値を明瞭に見ることができる。いくつかの小さい帯域内偽トーンが、1 次不整合形成のアイドル・トーンのために、第 2 N T F ( z ) ゼロ点の付近に存在する。これらのスパーは、たとえば、ノーズワージ・テキストのセクション 8.3 に記載されているような 2 次不整合形成を使用することによって、低減することができる。 64.1 d B の S N D R が獲得された。この測定値は、浮動点算術および理想的なアナログ D A C ( 図 7 を思い出されたい ) を想定したシミュレーションによって獲得される S N R より、 1.8 d B 低いだけである。最後に、図 12 ( c ) は、 R B W が 100 H z に増大されているが、 D W A スクランブル D A C の完全な 0 . . . 32 k H z 4 次雑音形成スペクトルを示す。

#### 【 0046 】

##### § 4.4 結論

L 次 F I R ( またはおそらくはさらに I I R ) 雑音伝達関数および  $L + 1$  ビットを有する E F 变調器が安定であることを述べた本発明による十分安定性基準を使用して設計された高次 E F D A C は、頑強であり、かつ O F アーキテクチャより優れた性能を達成することが判明した。そのような E F D A C は、低いオーバーサンプリング率についても高分解能を達成することができた。本発明により、 N T F の O B G を低減する必要性が排除される。 M A S H トポロジ变調器と同様に、本発明による高次 E F 变調器は、安定であり、かつ高次雑音形成マルチビット出力を生成する。しかし、本発明による高次 E

F変調器は、単一ループ内において実施することが可能であり、よりハードウェア効率がよく、かつMASHトポロジ変調器より低い電力を導出するように作成することができる。

【図面の簡単な説明】

【0047】

【図1】本発明による例示的な EF変調器のブロック図である。

【図2】例示的な OF DACのブロック図である

【図3A】本発明による例示的な EF DACのブロック図である。

【図3B】本発明による例示的な EF DACの機能図である。

【図4】93.1dBのSNRを示す、OSR=8について4次5ビット EF変調器 10のシミュレーションした高速フーリエ変換(FFT)の図である。

【図5】81.2dBのSNRを示す、OSR=8について4次5ビット OF変調器のシミュレーションしたFFTの図である。

【図6】 EF変調器と OF変調器とを比較するシミュレーション安定性試験の図である。

【図7】様々な変調器の可能な性能を示すグラフである。

【図8】本発明による実験用4次5ビット EF DACのブロック図である。

【図9】図8の EF DACにおいて使用することが可能である例示的な EF変調器のブロック図である。

【図10】図8の EF DACにおいて使用することが可能である例示的なスクランブラの概略図である。 20

【図11】図8の実験用 DF DACにおいて使用することが可能である例示的なアナログDACの概略図である。

【図12a】DWAスクランブラを有さず、SNDR=58.7dBである、図8~10において示したような、OSR=4の4次5ビット EF変調器の測定スペクトルのグラフである。

【図12b】DWAスクランブラを有し、SNDR=64.1dBである、図8~10において示したような、OSR=4の4次5ビット EF変調器の測定スペクトルのグラフである。

【図12c】分解能帯域幅が増大されているが、図12bにおいて測定した装置の完全スペクトル・バージョンである。 30

【図1】

【図2】

【図3 A】

【図3 B】

【図4】

【図5】

【図6】

【 図 7 】

【図8】

【図9】

【図10】

【図11】

【図 1 2 a】

【図 1 2 b】

【図 1 2 c】

---

フロントページの続き

(72)発明者 ピーター キス

アメリカ合衆国 07960 ニュージャージィ, モリスタウン, エルム ストリート 34 ア

パートメント 1

(72)発明者 ジェーサス アリアス

スペイン国, スペイン, ヴァラドリド, 47193, ラ システルニガ, シー / トレボル 19

(72)発明者 ダンダン リ

カナダ国 92127 サン ディエゴ, スモークシグナル ドライヴ 18296

合議体

審判長 藤井 浩

審判官 新川 圭二

審判官 田中 庸介

(56)参考文献 特開平5-235773 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H03M 3/00 - 11/00