(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5716637号

(P5716637)

(45) 発行日 平成27年5月13日(2015.5.13)

(24) 登録日 平成27年3月27日(2015.3.27)

(51) Int.Cl.

H01L 25/07 (2006.01)

H01L 25/18 (2006.01)

F 1

H01L 25/04

C

請求項の数 9 (全 24 頁)

(21) 出願番号 特願2011-241856 (P2011-241856)

(22) 出願日 平成23年11月4日 (2011.11.4)

(65) 公開番号 特開2013-98450 (P2013-98450A)

(43) 公開日 平成25年5月20日 (2013.5.20)

審査請求日 平成26年6月25日 (2014.6.25)

(73) 特許権者 000002130

住友電気工業株式会社

大阪府大阪市中央区北浜四丁目5番33号

(74) 代理人 100088155

弁理士 長谷川 芳樹

(74) 代理人 100113435

弁理士 黒木 義樹

(74) 代理人 100108257

弁理士 近藤 伊知良

(74) 代理人 100140453

弁理士 戸津 洋介

(72) 発明者 澤田 研一

大阪府大阪市此花区島屋一丁目1番3号

住友電気工業株式会社大阪製作所内

最終頁に続く

(54) 【発明の名称】半導体モジュール及び半導体モジュールの製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

ベースと、

少なくとも 1 つの回路基板と、

を備える半導体モジュールであって、

前記少なくとも 1 つの回路基板が、支持基板と前記支持基板によって支持される半導体素子とを有し、

前記ベースが、前記少なくとも 1 つの回路基板を前記ベースに嵌め合わせるための溝を有し、

前記溝が、前記溝の延在方向に沿って深くなっている、

10

半導体モジュール。

## 【請求項 2】

前記少なくとも 1 つの回路基板が複数の回路基板を備え、

前記複数の回路基板のそれぞれが、前記支持基板と前記半導体素子とを有する、請求項 1 に記載の半導体モジュール。

## 【請求項 3】

前記半導体素子と電気的に接続される端子を支持すると共に、前記ベースに取り付けられる絶縁支持体を更に備える、請求項 1 又は 2 に記載の半導体モジュール。

## 【請求項 4】

前記少なくとも 1 つの回路基板を前記ベースに固定する固定部材を更に備える、請求項

20

1 ~ 3 のいずれか一項に記載の半導体モジュール。

【請求項 5】

前記少なくとも 1 つの回路基板の正面の中心を通ると共に前記正面に垂直な軸線に対し

て、前記溝が非対称に形成されている、請求項 1 ~ 4 のいずれか一項に記載の半導体モジ

ュール。

【請求項 6】

前記半導体素子がワイドバンドギャップ半導体を含む、請求項 1 ~ 5 のいずれか一項に

記載の半導体モジュール。

【請求項 7】

前記ワイドバンドギャップ半導体が S i C 又は G a N である、請求項 6 に記載の半導体 10

モジュール。

【請求項 8】

溝を有するベースに、前記溝に対向配置された端子を支持する絶縁支持体を取り付ける

工程と、

前記端子と前記ベースとの間に、支持基板と前記支持基板によって支持される半導体素

子とを有する回路基板の第 1 の端部を挿入する工程と、

前記回路基板の第 1 の端部とは異なる第 2 の端部を固定部材によって前記ベースに固定

して、前記端子を前記半導体素子と電気的に接続すると共に、前記回路基板を前記ベース

の前記溝に嵌め合わせる工程と、

を含む、半導体モジュールの製造方法。 20

【請求項 9】

前記溝が、前記溝の延在方向に沿って前記端子に向かって深くなっている、請求項 8 に

記載の半導体モジュールの製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体モジュール及び半導体モジュールの製造方法に関する。

【背景技術】

【0002】

半導体素子が搭載されたセラミックス基板と、当該セラミックス基板が取り付けられた

金属ベースとを備える半導体モジュールが知られている（特許文献 1 参照）。

【先行技術文献】

【特許文献】

【0003】

【特許文献 1】特開平 6 - 85126 号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、上述の半導体モジュールでは、半田等によりセラミックス基板を金属ベ

ースに取り付ける際に、セラミックス基板が所望の位置からずれてしまうおそれがある。

このため、セラミックス基板と金属ベースとの間の位置決め精度を向上させるのは容易で

ない。

【0005】

本発明は、上記事情に鑑みて為されたものであり、半導体素子を有する回路基板とベ

ースとの間において高い位置決め精度を有する半導体モジュール及び半導体モジュールの製

造方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

上述の課題を解決するため、本発明の一側面に係る半導体モジュールは、ベースと、少 50

なくとも 1 つの回路基板と、を備える半導体モジュールであって、前記少なくとも 1 つの回路基板が、支持基板と前記支持基板によって支持される半導体素子とを有し、前記ベース及び／又は前記支持基板が、前記少なくとも 1 つの回路基板を前記ベースに嵌め合わせるための構造を有する。

【 0 0 0 7 】

この半導体モジュールでは、回路基板をベースに嵌め合わせることによって、回路基板とベースとの間において高い位置決め精度が得られる。

【 0 0 0 8 】

一実施形態において、半導体モジュールは、前記少なくとも 1 つの回路基板が複数の回路基板を備え、前記複数の回路基板のそれぞれが、前記支持基板と前記半導体素子とを有してもよい。10

【 0 0 0 9 】

半導体素子を支持基板に搭載する際に、実装によるストレスによって不良品の半導体素子が発生する可能性がある。半導体素子を直接検査することは困難であるため、通常、支持基板に搭載した後に半導体素子を検査する。ここで、複数の半導体素子が単一の支持基板によって支持されていると、検査により 1 つでも不良品の半導体素子が見つかると、支持基板によって支持された全ての半導体素子が無駄になってしまう。一方、上記半導体モジュールでは、個々の回路基板を検査して良品の回路基板を選別し、選別された良品の回路基板を選択的にベースに嵌め合わせることができる。このため、複数の半導体素子が単一の支持基板によって支持される場合に比べて、半導体モジュールの製造歩留まりを向上させることができる。20

【 0 0 1 0 】

また、複数の半導体素子が単一の支持基板によって支持される場合、不良品の半導体素子が見つかった場合に備えて、良品の半導体素子を新たに搭載するためのスペースを支持基板に設けることがある。この場合、支持基板のサイズは大きくなる。一方、上記半導体モジュールでは、そのようなスペースが必要ないので、半導体モジュールを小型化できる。

【 0 0 1 1 】

さらに、上記半導体モジュールでは、複数の半導体素子が単一の支持基板によって支持される場合に比べて、個々の回路基板のサイズを小さくすることができるので、回路基板が応力によって撓むことを抑制できる。30

【 0 0 1 2 】

一実施形態において、半導体モジュールは、前記半導体素子と電気的に接続される端子を支持すると共に、前記ベースに取り付けられる絶縁支持体を更に備えてもよい。

【 0 0 1 3 】

この場合、端子と絶縁支持体とが一体化しているので、半導体モジュールの組み立てが容易になる。

【 0 0 1 4 】

一実施形態において、前記ベースが、前記構造として凹部又は凸部を有してもよい。

【 0 0 1 5 】

一実施形態において、前記ベースが、前記構造として溝を有してもよい。この場合、溝に沿って回路基板をスライドさせてベースに嵌め合わせることができるので、半導体モジュールの組み立てが容易になる。40

【 0 0 1 6 】

一実施形態において、前記溝が、前記溝の延在方向に沿って深くなってもよい。この場合、溝が深くなっている部分に回路基板の端部を差し込み易くなるので、半導体モジュールの組み立てが容易になる。

【 0 0 1 7 】

一実施形態において、半導体モジュールは、前記少なくとも 1 つの回路基板を前記ベースに固定する固定部材を更にてもよい。この場合、回路基板とベースとの間においてより50

高い位置決め精度が得られる。

**【0018】**

一実施形態において、前記少なくとも1つの回路基板の正面の中心を通ると共に前記正面に垂直な軸線に対して、前記構造が非対称に形成されてもよい。この場合、ベースに対する回路基板の向きが1つに決まるので、間違った向きで回路基板をベースに嵌め合わせることを抑制できる。その結果、半導体モジュールの組み立てが容易になる。

**【0019】**

一実施形態において、前記半導体素子がワイドバンドギャップ半導体を含んでもよい。前記ワイドバンドギャップ半導体がSiC又はGaNであってもよい。

**【0020】**

本発明の一側面に係る半導体モジュールの製造方法は、支持基板と前記支持基板によって支持される半導体素子とを有する少なくとも1つの回路基板をベースに嵌め合わせる工程を含み、前記ベース及び／又は前記支持基板が、前記少なくとも1つの回路基板を前記ベースに嵌め合わせるための構造を有する。

**【0021】**

この半導体モジュールの製造方法では、回路基板をベースに嵌め合わせることによって、回路基板とベースとの間ににおいて高い位置決め精度を有する半導体モジュールが得られる。

**【0022】**

本発明の別の側面に係る半導体モジュールの製造方法は、溝を有するベースに、前記溝に対向配置された端子を支持する絶縁支持体を取り付ける工程と、前記端子と前記ベースとの間に、支持基板と前記支持基板によって支持される半導体素子とを有する回路基板の第1の端部を挿入する工程と、前記回路基板の第1の端部とは異なる第2の端部を固定部材によって前記ベースに固定して、前記端子を前記半導体素子と電気的に接続すると共に、前記回路基板を前記ベースの前記溝に嵌め合わせる工程とを含む。

**【0023】**

この半導体モジュールの製造方法では、回路基板をベースに嵌め合わせることによって、回路基板とベースとの間ににおいて高い位置決め精度を有する半導体モジュールが得られる。さらに、回路基板の第1の端部を端子とベースとの間に挿入する際に、端子が第1の端部を押圧することによって回路基板の反対側の端部が浮き上がってしまっても、固定部材によって回路基板をベースの溝に嵌め合わせることができる。

**【0024】**

一実施形態において、前記溝が、前記溝の延在方向に沿って前記端子に向かって深くなつてもよい。

**【0025】**

この場合、端子と溝の底との間のスペースを広く維持することができるので、回路基板の第1の端部を斜めに挿入することができる。その結果、半導体モジュールの組み立てが容易になる。また、固定部材によってベースに第2の端部を固定する際に、てこの原理によって端子と半導体素子との間の電気的接続がより確実に得られる。

**【発明の効果】**

**【0026】**

本発明によれば、半導体素子を有する回路基板とベースとの間ににおいて高い位置決め精度を有する半導体モジュール及び半導体モジュールの製造方法が提供され得る。

**【図面の簡単な説明】**

**【0027】**

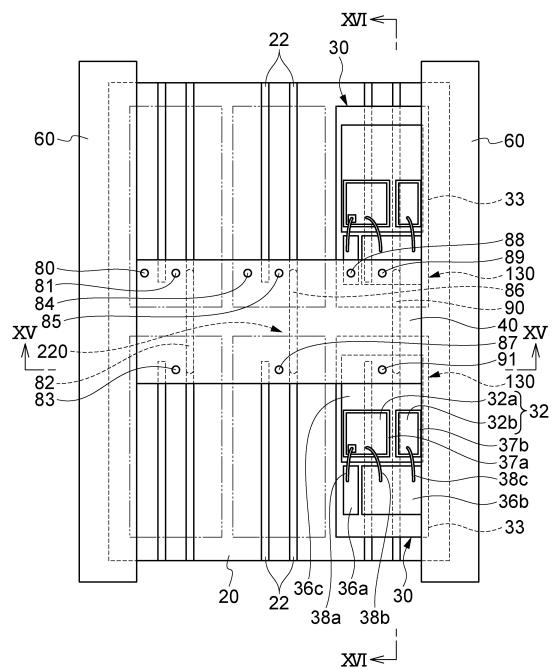

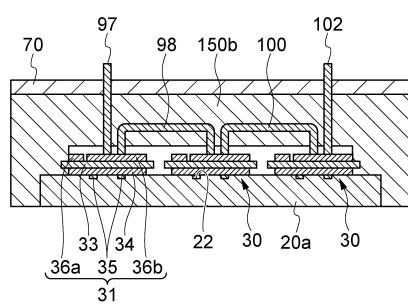

**【図1】** 第1実施形態に係る半導体モジュールを模式的に示す平面図である。

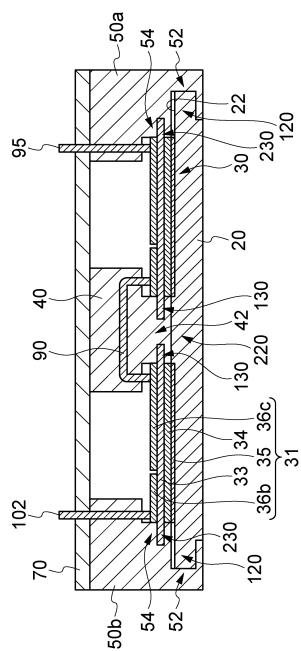

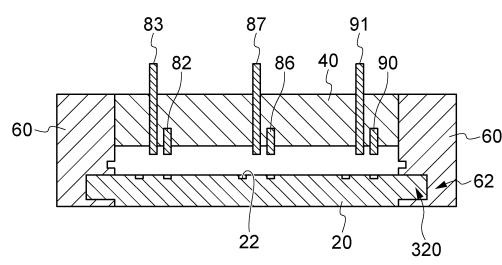

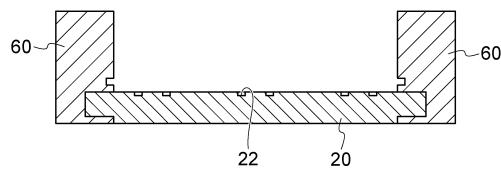

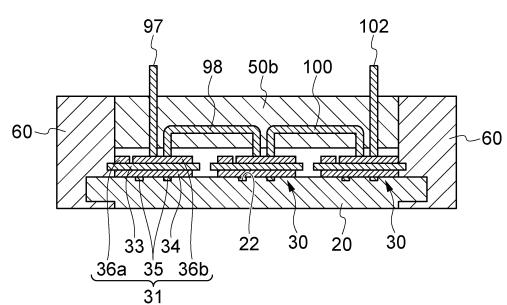

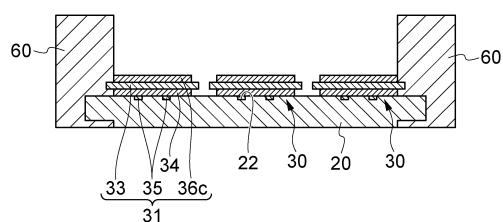

**【図2】** 図1のI—I - I—I線に沿った半導体モジュールの断面図である。

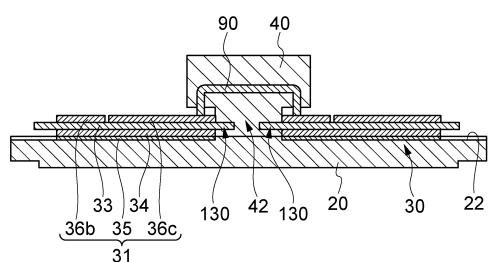

**【図3】** 図1のI—I—I - I—I—I線に沿った半導体モジュールの断面図である。

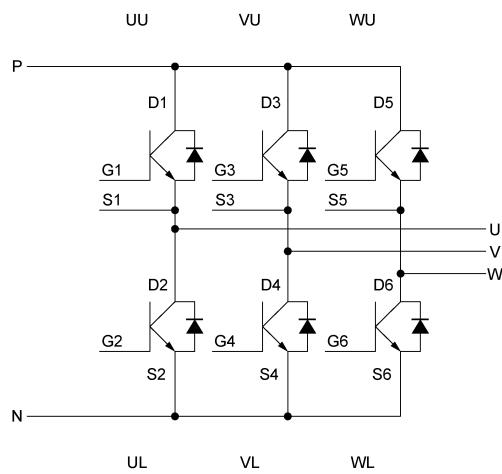

**【図4】** 図1の半導体モジュールの等価回路結線図である。

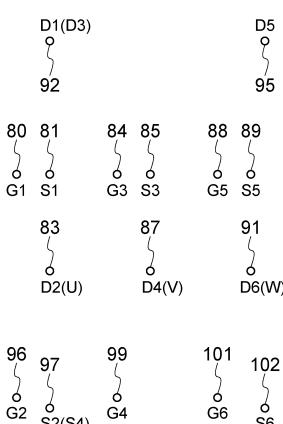

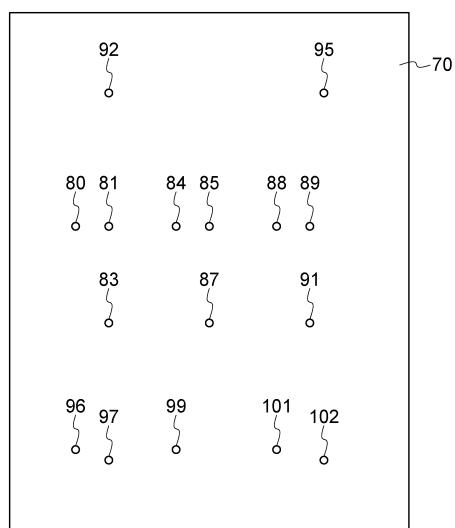

**【図5】** 図1の半導体モジュールの端子の配置を模式的に示す図である。

10

20

30

40

50

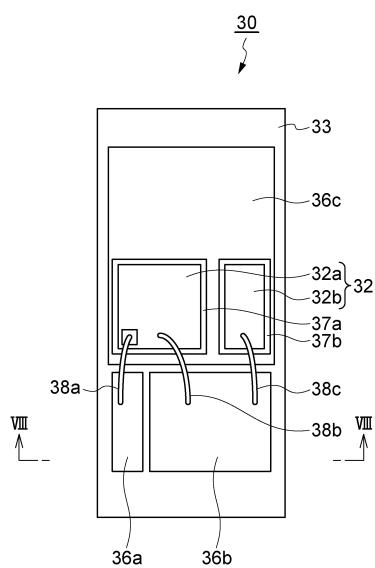

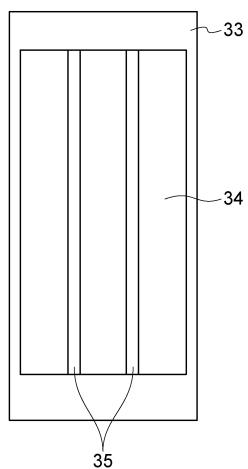

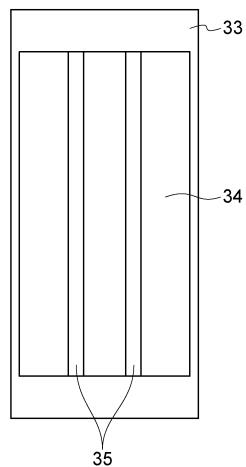

【図6】図1の半導体モジュールを構成する回路基板を模式的に示す平面図である。

【図7】図6の回路基板の裏面を模式的に示す平面図である。

【図8】図6のVIII-VIII線に沿った回路基板の断面図である。

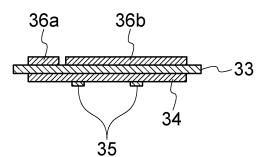

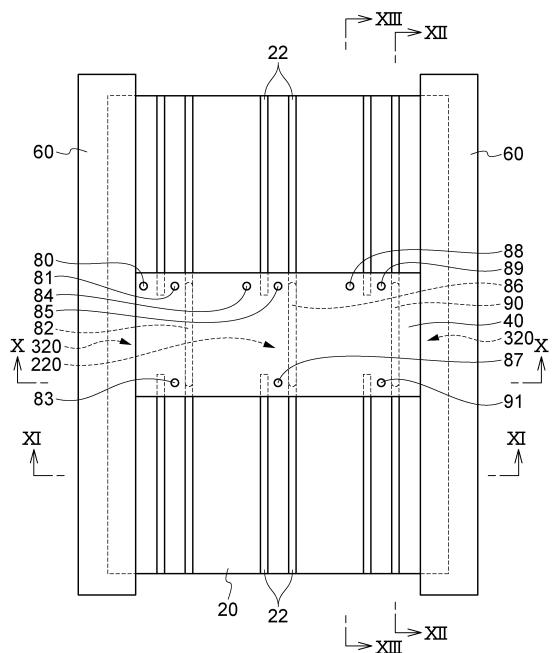

【図9】第1実施形態に係る半導体モジュールの製造方法の一工程における構造体を模式的に示す平面図である。

【図10】図9のX-X線に沿った構造体の断面図である。

【図11】図9のXI-XI線に沿った構造体の断面図である。

【図12】図9のXII-XII線に沿った構造体の断面図である。

【図13】図9のXIII-XIII線に沿った構造体の断面図である。

【図14】第1実施形態に係る半導体モジュールの製造方法の一工程における構造体を模式的に示す平面図である。10

【図15】図14のXV-XV線に沿った構造体の断面図である。

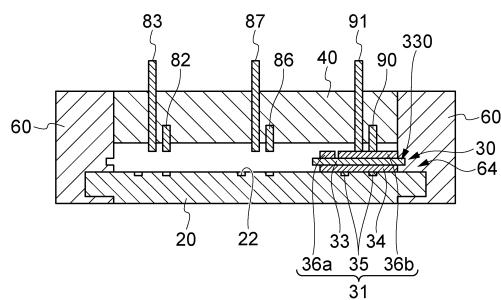

【図16】図14のXVI-XVI線に沿った構造体の断面図である。

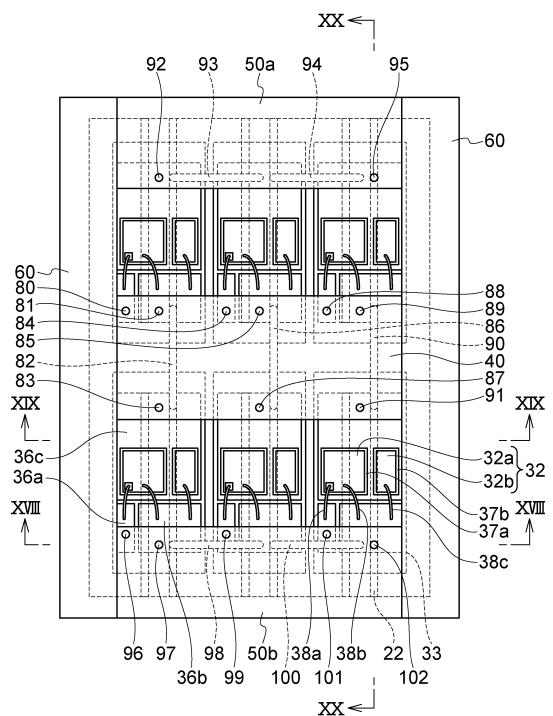

【図17】第1実施形態に係る半導体モジュールの製造方法の一工程における構造体を模式的に示す平面図である。

【図18】図17のXVII-XVII線に沿った構造体の断面図である。

【図19】図17のIX-XIX線に沿った構造体の断面図である。

【図20】図17のXX-XX線に沿った構造体の断面図である。

【図21】第1実施形態に係る半導体モジュールの蓋を模式的に示す平面図である。

【図22】第2実施形態に係る半導体モジュールを模式的に示す平面図である。20

【図23】図22のXXII-XXII線に沿った半導体モジュールの断面図である

。

【図24】図22のXXIV-XXIV線に沿った半導体モジュールの断面図である。

【図25】図22の半導体モジュールの等価回路結線図である。

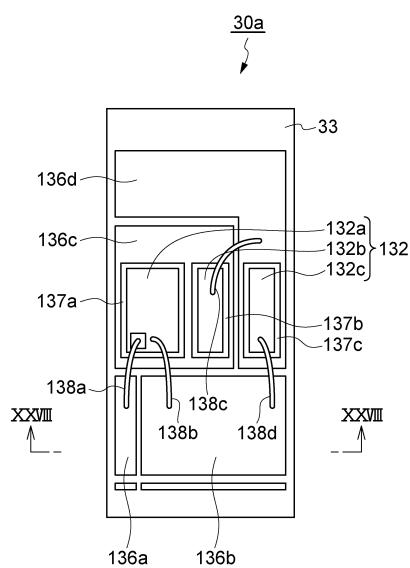

【図26】図22の半導体モジュールを構成する回路基板を模式的に示す平面図である。

【図27】図26の回路基板の裏面を模式的に示す平面図である。

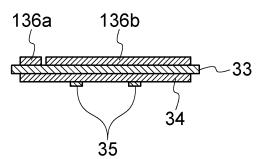

【図28】図26のXXVII-XXVII線に沿った回路基板の断面図である。

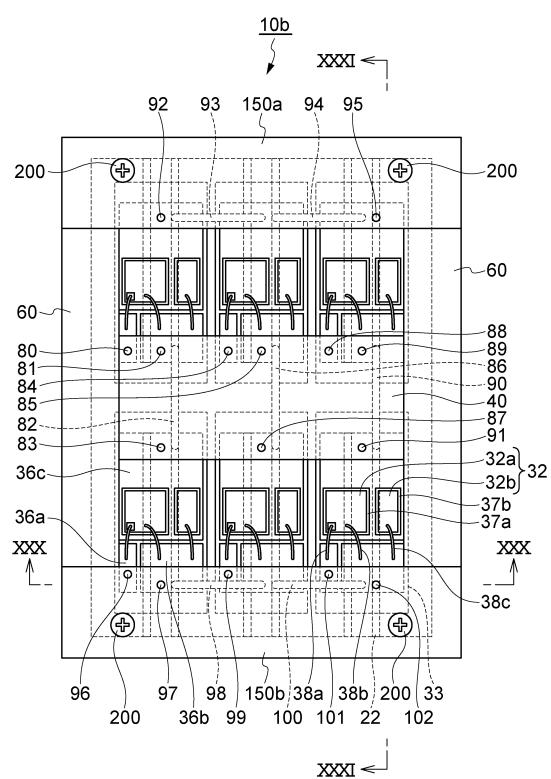

【図29】第3実施形態に係る半導体モジュールを模式的に示す平面図である。

【図30】図29のXXX-XXX線に沿った半導体モジュールの断面図である。

【図31】図29のXXXI-XXXI線に沿った半導体モジュールの断面図である。30

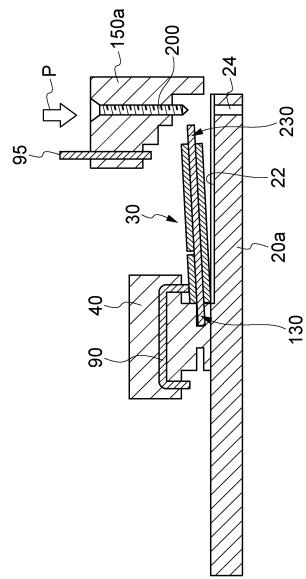

【図32】第3実施形態に係る半導体モジュールの製造方法の一工程における構造体を模式的に示す図である。

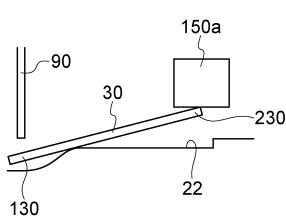

【図33】回路基板をベースに嵌め合わせるための構造の一例を示す図である。

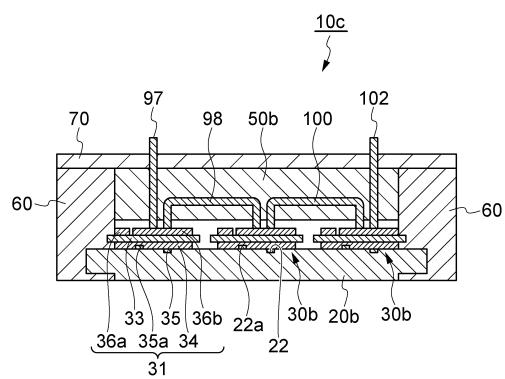

【図34】第4実施形態に係る半導体モジュールを模式的に示す断面図である。

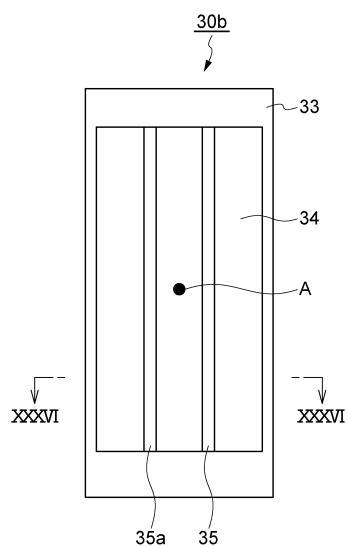

【図35】図34の半導体モジュールを構成する回路基板を模式的に示す平面図である。

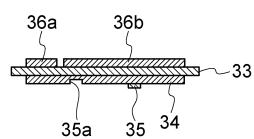

【図36】図35のXXXVI-XXXVI線に沿った回路基板の断面図である。

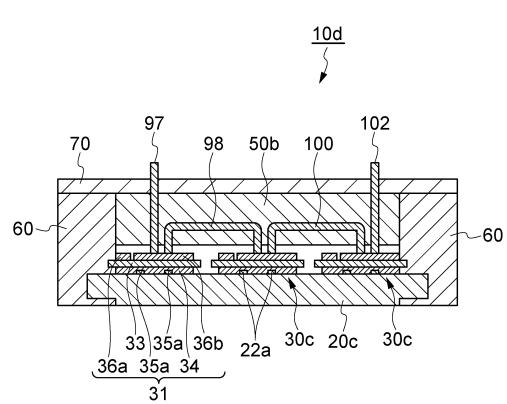

【図37】第5実施形態に係る半導体モジュールを模式的に示す断面図である。

【図38】第6実施形態に係る半導体モジュールを模式的に示す断面図である。

【図39】第7実施形態に係る半導体モジュールを模式的に示す断面図である。

【図40】第8実施形態に係る半導体モジュールを模式的に示す断面図である。40

【発明を実施するための形態】

【0028】

以下、添付図面を参照しながら本発明の実施形態を詳細に説明する。なお、図面の説明において、同一又は同等の要素には同一符号を用い、重複する説明を省略する。

【0029】

(第1実施形態)

<半導体モジュール>

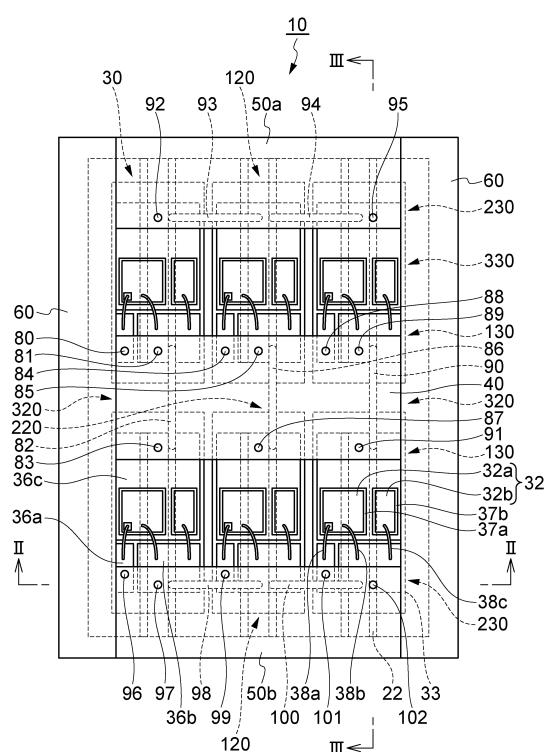

図1は、第1実施形態に係る半導体モジュールを模式的に示す平面図である。図2は、図1のII-II線に沿った半導体モジュールの断面図である。図3は、図1のIII-III線に沿った半導体モジュールの断面図である。図1において蓋70は便宜上表示さ

れていない。

#### 【0030】

図1～3に示される半導体モジュール10は、ベース20と、複数の回路基板30（本実施形態では例えば6つ）とを備える。複数の回路基板30は、ベース20上にアレイ配置され得る。半導体モジュール10は、単一の回路基板30を備えてもよい。複数の回路基板30のそれぞれは、支持基板31と支持基板31によって支持される半導体素子32とを有する（図6～図8参照）。

#### 【0031】

ベース20は、例えばCu、Al等の金属を含む金属ベースであり得る。ベース20は、放熱板として機能し得る。ベース20は、回路基板30をベース20に嵌め合わせるための構造として溝22を有してもよい。溝22は、ベース20の互いに対向する端部120からベース20の中央部220に向けて形成され得る。溝22は凹部であってもよい。

10

#### 【0032】

支持基板31は、絶縁基板33と、絶縁基板33の正面に設けられた電極パッド36a, 36b, 36cと、絶縁基板33の正面とは反対側の面に設けられた金属層34とを備え得る。絶縁基板33は例えばAlN、Al<sub>2</sub>O<sub>3</sub>等のセラミックスを含む。電極パッド36a, 36b, 36c及び金属層34は、例えばCuを含む。金属層34上には、ベース20の溝22に嵌め合わされる凸部35が形成され得る。凸部35は、一方向に延在し得る。凸部35は、例えばCu等の金属を含む。凸部35の延在方向に垂直な断面形状は例えば矩形である。

20

#### 【0033】

半導体素子32は、例えば半導体チップである。半導体素子32は、ワイドバンドギャップ半導体を含む。この場合、シリコンに比べて半導体素子32の発生する熱量は大きくなるが、ベース20により放熱が適切に行われる。ワイドバンドギャップ半導体としては、例えばSiC又はGaN等の化合物半導体が挙げられる。このような場合、半導体素子32はパワー半導体素子として機能し得る。

#### 【0034】

半導体素子32は、トランジスタ32a及びダイオード32bを備え得る。トランジスタ32aとしては、例えばバイポーラトランジスタ、MOSFET、絶縁ゲートバイポーラトランジスタ（IGBT）等が挙げられる。トランジスタ32aは、半田37aを介して電極パッド36cに電気的に接続されている。ダイオード32bは、半田37bを介して電極パッド36cに電気的に接続されている。トランジスタ32aのゲートは、ワイヤ38aを介して電極パッド36aに電気的に接続されている。トランジスタ32aのソースは、ワイヤ38bを介して電極パッド36bに電気的に接続されている。ダイオード32bは、ワイヤ38cを介して電極パッド36bに電気的に接続されている。

30

#### 【0035】

半導体モジュール10は、ベース20に取り付けられる絶縁支持体40を備えてもよい。絶縁支持体40は、ベース20の中央部220に取り付けられる。絶縁支持体40は、回路基板30の端部130（第1の端部）を把持する把持部42を有する。絶縁支持体40は、半導体素子32と電気的に接続される端子80～91を支持する。端子80～91は、ベース20上の回路基板30の端部130に向けて絶縁支持体40から突出している。

40

#### 【0036】

半導体モジュール10は、ベース20に取り付けられる絶縁支持体50a, 50bを備えてもよい。絶縁支持体50a, 50bは、ベース20の互いに対向する端部120にそれぞれ取り付けられる。絶縁支持体50a, 50bのそれぞれは、ベース20の端部120を把持する把持部52と、回路基板30の端部230（第2の端部）を把持する把持部54とを有する。回路基板30の端部230は、溝22の延在方向に沿って端部130と反対側に位置する。絶縁支持体50aは、半導体素子32と電気的に接続される端子92～95を支持する。端子92～95は、ベース20上の回路基板30の端部230に向

50

て絶縁支持体 50a から突出している。絶縁支持体 50b は、半導体素子 32 と電気的に接続される端子 96 ~ 102 を支持する。端子 96 ~ 102 は、ベース 20 上の回路基板 30 の端部 230 に向けて絶縁支持体 50b から突出している。

#### 【0037】

半導体モジュール 10 は、ベース 20 に取り付けられる絶縁支持体 60 を備えてよい。絶縁支持体 60 は、絶縁支持体 40, 50a, 50b を挟むように、ベース 20 の互いに対向する側部 320 にそれぞれ取り付けられる。絶縁支持体 60 は、ベース 20 の互いに対向する側部 320 を把持する把持部 62 と、回路基板 30 の側部 330 を把持する把持部 64 とを有する。絶縁支持体 60 は、端子を支持していない。

#### 【0038】

絶縁支持体 40, 50a, 50b, 60 は例えば樹脂を含む。端子 80 ~ 102 は例えば金属ワイヤである。端子 80 ~ 102 は、半導体素子 32 に直接接触（例えばスプリングコンタクト）してもよいし、ワイヤボンディング等により半導体素子 32 に接続されてよい。

#### 【0039】

端子 80 は、第 1 の半導体素子 32 の電極パッド 36a に接続され、絶縁支持体 40 を貫通して半導体モジュール 10 の外部に突出する。端子 81 は、第 1 の半導体素子 32 の電極パッド 36b に接続され、絶縁支持体 40 を貫通して半導体モジュール 10 の外部に突出する。端子 82 は、第 1 の半導体素子 32 の電極パッド 36b に接続され、絶縁支持体 40 中を通過して第 2 の半導体素子 32 の電極パッド 36c に接続される。端子 83 は、第 2 の半導体素子 32 の電極パッド 36a に接続され、絶縁支持体 40 を貫通して半導体モジュール 10 の外部に突出する。

#### 【0040】

端子 84 は、第 3 の半導体素子 32 の電極パッド 36a に接続され、絶縁支持体 40 を貫通して半導体モジュール 10 の外部に突出する。端子 85 は、第 3 の半導体素子 32 の電極パッド 36b に接続され、絶縁支持体 40 を貫通して半導体モジュール 10 の外部に突出する。端子 86 は、第 3 の半導体素子 32 の電極パッド 36b に接続され、絶縁支持体 40 中を通過して第 4 の半導体素子 32 の電極パッド 36c に接続される。端子 87 は、第 4 の半導体素子 32 の電極パッド 36a に接続され、絶縁支持体 40 を貫通して半導体モジュール 10 の外部に突出する。

#### 【0041】

端子 88 は、第 5 の半導体素子 32 の電極パッド 36a に接続され、絶縁支持体 40 を貫通して半導体モジュール 10 の外部に突出する。端子 89 は、第 5 の半導体素子 32 の電極パッド 36b に接続され、絶縁支持体 40 を貫通して半導体モジュール 10 の外部に突出する。端子 90 は、第 5 の半導体素子 32 の電極パッド 36b に接続され、絶縁支持体 40 中を通過して第 6 の半導体素子 32 の電極パッド 36c に接続される。端子 91 は、第 6 の半導体素子 32 の電極パッド 36a に接続され、絶縁支持体 40 を貫通して半導体モジュール 10 の外部に突出する。

#### 【0042】

端子 92 は、第 1 の半導体素子 32 の電極パッド 36c に接続され、絶縁支持体 50a を貫通して半導体モジュール 10 の外部に突出する。端子 93 は、第 1 の半導体素子 32 の電極パッド 36c に接続され、絶縁支持体 50a 中を通過して第 3 の半導体素子 32 の電極パッド 36c に接続される。端子 94 は、第 3 の半導体素子 32 の電極パッド 36c に接続され、絶縁支持体 50a 中を通過して第 5 の半導体素子 32 の電極パッド 36c に接続される。端子 95 は、第 5 の半導体素子 32 の電極パッド 36c に接続され、絶縁支持体 50a を貫通して半導体モジュール 10 の外部に突出する。

#### 【0043】

端子 96 は、第 2 の半導体素子 32 の電極パッド 36a に接続され、絶縁支持体 50b を貫通して半導体モジュール 10 の外部に突出する。端子 97 は、第 2 の半導体素子 32 の電極パッド 36b に接続され、絶縁支持体 50b を貫通して半導体モジュール 10 の外

10

20

30

40

50

部に突出する。端子 9 8 は、第 2 の半導体素子 3 2 の電極パッド 3 6 b に接続され、絶縁支持体 5 0 b 中を通って第 4 の半導体素子 3 2 の電極パッド 3 6 b に接続される。端子 9 9 は、第 4 の半導体素子 3 2 の電極パッド 3 6 a に接続され、絶縁支持体 5 0 b を貫通して半導体モジュール 1 0 の外部に突出する。端子 1 0 0 は、第 4 の半導体素子 3 2 の電極パッド 3 6 b に接続され、絶縁支持体 5 0 b 中を通って第 6 の半導体素子 3 2 の電極パッド 3 6 b に接続される。端子 1 0 1 は、第 6 の半導体素子 3 2 の電極パッド 3 6 a に接続され、絶縁支持体 5 0 b を貫通して半導体モジュール 1 0 の外部に突出する。端子 1 0 2 は、第 6 の半導体素子 3 2 の電極パッド 3 6 b に接続され、絶縁支持体 5 0 b を貫通して半導体モジュール 1 0 の外部に突出する。

## 【0044】

10

半導体モジュール 1 0 は、絶縁支持体 4 0 , 5 0 a , 5 0 b , 6 0 上に配置されると共にベース 2 0 に対向配置される蓋 7 0 を更に備えてもよい。蓋 7 0 には、端子 8 0 , 8 1 , 8 3 , 8 4 , 8 5 , 8 7 , 8 8 , 8 9 , 9 1 , 9 2 , 9 5 , 9 6 , 9 7 , 9 9 , 1 0 1 , 1 0 2 通る貫通孔が形成され得る。蓋 7 0 は例えば樹脂を含む。

## 【0045】

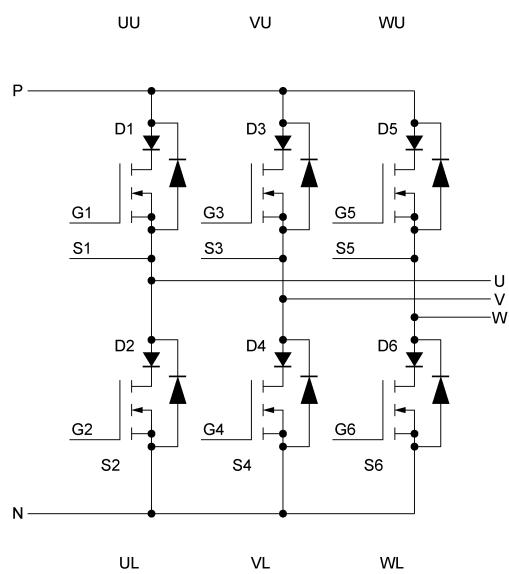

図 4 は、図 1 の半導体モジュールの等価回路結線図である。図 5 は、図 1 の半導体モジュールの端子の配置を模式的に示す図である。図 4 及び図 5 に示されるように、半導体モジュール 1 0 は、U 相、V 相及びW 相を有する 3 相インバータ用モジュールとして機能し得る。各回路基板 3 0 において、トランジスタ 3 2 a はダイオード 3 2 b と逆並列接続されている。

20

## 【0046】

半導体モジュール 1 0 では、回路基板 3 0 をベース 2 0 に嵌め合わせることによって、回路基板 3 0 とベース 2 0 との間ににおいて高い位置決め精度が得られる。

## 【0047】

半導体素子を支持基板に搭載する際に、実装（ダイシング、ダイボンディング、ワイヤボンディング等）によるストレスによって不良品の半導体素子が発生する可能性がある。半導体素子を直接検査することは困難であるため、通常、支持基板に搭載した後に半導体素子を検査する。ここで、複数の半導体素子が単一の支持基板によって支持されていると、検査により 1 つでも不良品の半導体素子が見つかると、支持基板によって支持された全ての半導体素子が無駄になってしまう。一方、半導体モジュール 1 0 では、個々の回路基板 3 0 を検査して良品の回路基板 3 0 を選別し、選別された良品の回路基板 3 0 を選択的にベース 2 0 に嵌め合わせることができる。このため、複数の半導体素子が単一の支持基板によって支持される場合に比べて、半導体モジュール 1 0 の製造歩留まりを向上させることができることができる。

30

## 【0048】

また、複数の半導体素子が単一の支持基板によって支持される場合、不良品の半導体素子が見つかった場合に備えて、良品の半導体素子を新たに搭載するためのスペースを支持基板に設けることがある。この場合、支持基板のサイズは大きくなる。一方、半導体モジュール 1 0 では、複数の回路基板 3 0 のそれぞれが支持基板 3 1 と半導体素子 3 2 とを有している。そのため、良品の半導体素子を新たに搭載するためのスペースが必要ないので、半導体モジュール 1 0 を小型化できる。さらに、半導体モジュール 1 0 では、複数の半導体素子が単一の支持基板によって支持される場合に比べて、個々の回路基板 3 0 のサイズを小さくすることができるので、回路基板 3 0 が応力によって撓むことを抑制できる。

40

## 【0049】

半導体モジュール 1 0 が、端子 8 0 ~ 9 1 を支持する絶縁支持体 4 0 を備える場合、端子 8 0 ~ 9 1 と絶縁支持体 4 0 とが一体化しているので、半導体モジュール 1 0 の組み立てが容易になる。

## 【0050】

50

半導体モジュール 1 0 が、溝 2 2 を有するベース 2 0 を備える場合、溝 2 2 に沿って回路基板 3 0 をスライドさせてベース 2 0 に嵌め合わせることができるので、半導体モジュ

ール 10 の組み立てが容易になる。

**【0051】**

<半導体モジュールの製造方法>

図 6 ~ 図 21 を参照しながら、本実施形態に係る半導体モジュールの製造方法の一例として、図 1 ~ 3 に示される半導体モジュール 10 の製造方法について説明する。半導体モジュール 10 は例えば以下のようにして製造される。

**【0052】**

(回路基板の準備工程)

まず、図 6 ~ 図 8 に示されるように、回路基板 30 を準備する。回路基板 30 の凸部 35 は、例えば以下のようにして形成される。まず、絶縁基板 33 の正面とは反対側の面に設けられた金属層 34 上に金属膜を形成する。次に、フォトリソグラフィー法を用いて当該金属膜をエッチングすることによって凸部 35 を形成する。

10

**【0053】**

回路基板 30 は、必要に応じて電気試験等によって検査され得る。検査により、良品の回路基板 30 が選別される。

**【0054】**

(第 1 の絶縁支持体の取り付け工程)

次に、図 9 ~ 図 13 に示されるように、ベース 20 に絶縁支持体 40 を取り付ける。絶縁支持体 40 は、ベース 20 の溝 22 に端子 80 ~ 91 が対向配置されるように取り付けられ得る。絶縁支持体 40 は、樹脂中に端子 80 ~ 91 を圧入し、樹脂を成型することにより形成される。また、ベース 20 に絶縁支持体 60 を取り付けてもよい。ベース 20 の溝 22 は、フォトリソグラフィー法を用いてベースをエッチングすることによって形成され得る。

20

**【0055】**

(回路基板の嵌め合わせ工程)

次に、図 14 ~ 図 16 に示されるように、回路基板 30 をベース 20 に嵌め合わせる。回路基板 30 の凸部 35 が、ベース 20 の溝 22 に嵌め合わされ得る。例えば、凸部 35 が溝 22 に嵌め合わされた状態で、回路基板 30 をベース 20 の溝 22 に沿ってベース 20 の端部 120 から中央部 220 に向かってスライドさせることによって、端子 80 ~ 91 とベース 20との間に、回路基板 30 の第 1 の端部 130 を挿入する。これにより、半導体素子 32 の電極パッド 36a, 36b, 36c が端子 80 ~ 91 と接触して電気的に接続され得る。

30

**【0056】**

(第 2 の絶縁支持体の取り付け工程)

次に、図 17 ~ 図 20 に示されるように、ベース 20 に絶縁支持体 50a, 50b を取り付ける。絶縁支持体 50a, 50b は、樹脂中に端子 92 ~ 102 を圧入し、樹脂を成型することにより形成される。これにより、回路基板 30 の端部 230 がベース 20 に固定され得る。また、半導体素子 32 の電極パッド 36a, 36b, 36c が端子 92 ~ 102 と接触して電気的に接続され得る。

40

**【0057】**

(蓋の貼り付け工程)

次に、図 21 に示されるように、蓋 70 を絶縁支持体 40, 50a, 50b, 60 に貼り付ける。蓋 70 によって、ベース 20 及び絶縁支持体 40, 50a, 50b, 60 によって囲まれた空間が封止される。

**【0058】**

なお、上記各工程の順序を入れ替えててもよいし、複数の工程を同時に実行してもよい。例えば、第 1 の絶縁支持体の取り付け工程の前に回路基板の嵌め合わせ工程を行ってもよい。また、第 1 の絶縁支持体の取り付け工程の後に回路基板の準備工程を行ってもよい。また、回路基板の嵌め合わせ工程と第 2 の絶縁支持体の取り付け工程とを同時に行ってもよい。

50

**【0059】**

上記半導体モジュールの製造方法では、回路基板30をベース20に嵌め合わせることによって、回路基板30とベース20との間に於いて高い位置決め精度を有する半導体モジュール10が得られる。

**【0060】**

## (第2実施形態)

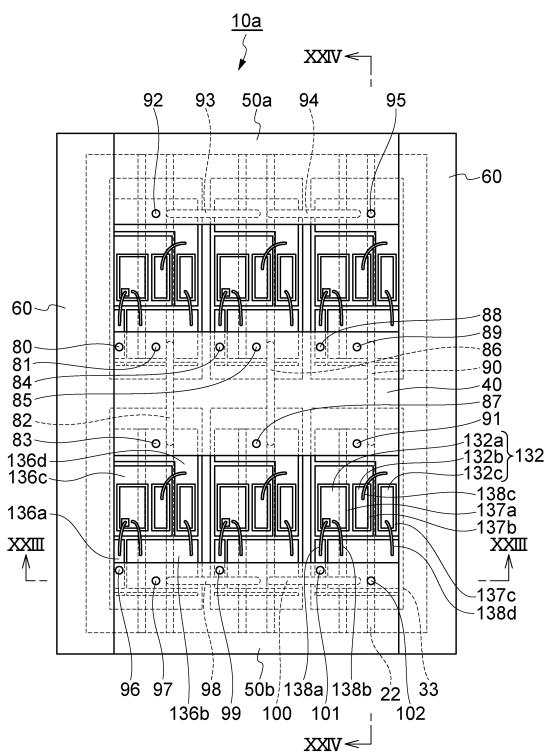

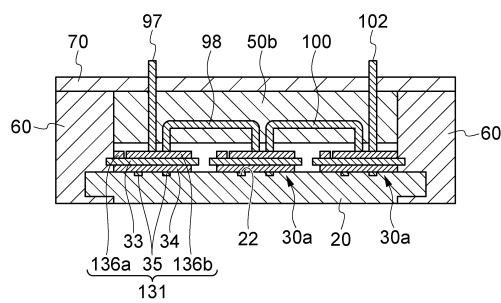

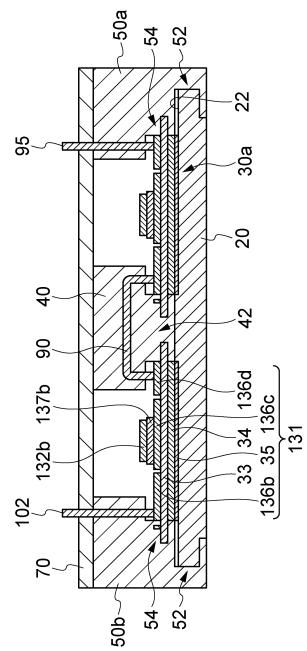

図22は、第2実施形態に係る半導体モジュールを模式的に示す平面図である。図23は、図22のXXII - XXII線に沿った半導体モジュールの断面図である。図24は、図22のXXIV - XXIV線に沿った半導体モジュールの断面図である。図22において蓋70は便宜上表示されていない。

10

**【0061】**

図22～23に示される半導体モジュール10aは、回路基板30に代えて回路基板30aを備えること以外は半導体モジュール10と同じ構成を備える。回路基板30aは、支持基板131と支持基板131によって支持される半導体素子132とを有する(図26～図28参照)。

**【0062】**

支持基板131は、絶縁基板33と、絶縁基板33の正面に設けられた電極パッド136a, 136b, 136c, 136dと、絶縁基板33の正面とは反対側の面に設けられた金属層34とを備え得る。

**【0063】**

半導体素子132は、トランジスタ132a、ダイオード132b及びダイオード132cを備え得る。トランジスタ132aは、半田137aを介して電極パッド136cに電気的に接続されている。ダイオード132bは、半田137bを介して電極パッド136cに電気的に接続されている。トランジスタ132aのゲートは、ワイヤ138aを介して電極パッド136aに電気的に接続されている。ダイオード132cは、半田137cを介して電極パッド136dに電気的に接続されている。トランジスタ132aのソースは、ワイヤ138bを介して電極パッド136bに電気的に接続されている。ダイオード132bは、ワイヤ138cを介して電極パッド136dに電気的に接続されている。ダイオード132cは、ワイヤ138dを介して電極パッド136bに電気的に接続されている。

20

**【0064】**

図25は、図22の半導体モジュールの等価回路結線図である。半導体モジュール10aの端子の配置は、図5に示される半導体モジュール10の端子の配置と同じである。図5及び図25に示されるように、半導体モジュール10aは、U相、V相及びW相を有する3相インバータ用モジュールとして機能し得る。各回路基板30において、トランジスタ132aはMOSFETであり、ダイオード132bはトランジスタ132aに直列接続され、ダイオード132cはトランジスタ132a及びダイオード132bの両端に逆並列接続される。ダイオード132bはMOSFET中の寄生ダイオードの動作を抑制し得る。

30

**【0065】**

半導体モジュール10aでは、半導体モジュール10と同様の作用効果が得られる。また、半導体モジュール10aは、半導体モジュール10の製造方法と同様の方法によって製造され得る。

40

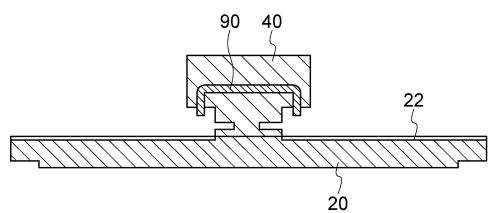

**【0066】**

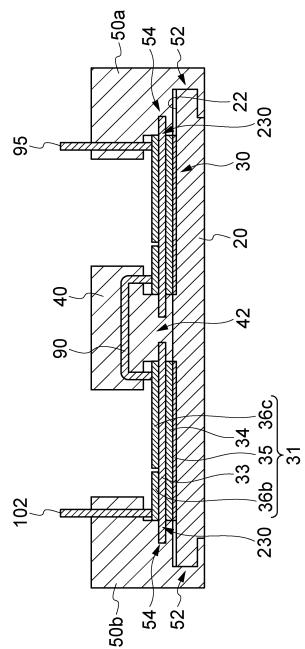

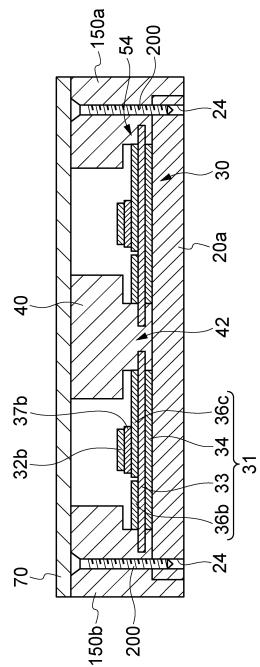

## (第3実施形態)

図29は、第3実施形態に係る半導体モジュールを模式的に示す平面図である。図30は、図29のXXX - XXX線に沿った半導体モジュールの断面図である。図31は、図29のXXXI - XXXI線に沿った半導体モジュールの断面図である。図29において蓋70は便宜上表示されていない。

**【0067】**

50

図29～31に示される半導体モジュール10bは、絶縁支持体50a, 50bに代えて絶縁支持体150a, 150bを備え、ベース20に代えてベース20aを備え、固定部材としてのねじ200を更に備えること以外は半導体モジュール10と同じ構成を備える。

#### 【0068】

ベース20aは、ねじ孔24を更に備えること以外はベース20と同じ構成を備える。

絶縁支持体150a, 150bは、把持部52を備えておらず、ねじ200が貫通していること以外は絶縁支持体50a, 50bと同じ構成を備える。

#### 【0069】

ねじ200は、回路基板30をベース20aに固定する。ねじ200は、絶縁支持体150a, 150bを介して、回路基板30の端部230をベース20aに固定する。ねじ200は、ベース20のコーナーにおいて、絶縁支持体150a, 150bを通ってベース20aのねじ孔24に取り付けられている。10

#### 【0070】

半導体モジュール10bでは、半導体モジュール10と同様の作用効果が得られる。また、半導体モジュール10bは、半導体モジュール10の製造方法と同様の方法によって製造され得る。本実施形態では、回路基板の嵌め合わせ工程と第2の絶縁支持体の取り付け工程とが同時に行われる。

#### 【0071】

まず、凸部35が溝22に嵌め合わされた状態で、回路基板30をベース20の溝22に沿ってベース20の端部120から中央部220に向かってスライドさせることによって、端子80～91とベース20との間に、回路基板30の第1の端部130を挿入する。その後、図32に示されるように、絶縁支持体150a, 150bを圧力Pによってベース20aに押圧し、ねじ200をねじ孔24に取り付けることによって、回路基板30の端部230をベース20aに固定する。これにより、端子80～91を半導体素子32と電気的に接続すると共に、回路基板30をベース20aの溝22に嵌め合わせる。20

#### 【0072】

半導体モジュール10bの製造方法では、回路基板30の端部130を端子80～91とベース20aとの間に挿入する際に、図32に示されるように、端子80～91が端部130を押圧することによって回路基板30の端部230が浮き上がってしまっても、ねじ200によって回路基板30をベース20aの溝22に嵌め合わせることができる。30

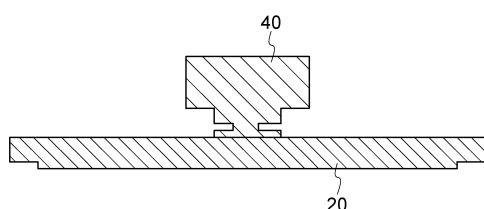

#### 【0073】

溝22は、図33に示されるように、溝22の延在方向に沿って深くなってもよい。溝22は、溝22の全体又は一部において、溝22の延在方向に沿って徐々に深くなってしまいし、溝22の延在方向に沿って階段状に深くなってもよい。溝22は、端子80～91に向かって深くなっている。この場合、端子80～91と溝22の底との間のスペースを広く維持することができるので、回路基板30の端部130を斜めに挿入することができる。その結果、半導体モジュール10bの組み立てが容易になる。また、ねじ200によってベース20aに回路基板30の端部230を固定する際に、てこの原理によって端子80～91と半導体素子32との間の電気的接続がより確実に得られる。40

#### 【0074】

なお、固定部材として、ねじ200に代えて例えば接着剤を用いてもよい。

#### 【0075】

##### (第4実施形態)

図34は、第4実施形態に係る半導体モジュールを模式的に示す断面図である。図34に示される半導体モジュール10cは、回路基板をベースに嵌め合わせるための構造が異なること以外は半導体モジュール10と同じ構成を備える。半導体モジュール10cは、回路基板30b及びベース20bを備える。

#### 【0076】

回路基板30bは、凹部35a及び凸部35を備えること以外は回路基板30と同じ構

50

成を備える(図35～図36参照)。凹部35a及び凸部35は、回路基板30bの主面の中心(例えば重心)を通ると共に主面に垂直な軸線Aの両側に配置されている。回路基板30bをベース20bに嵌め合わせるための構造は、軸線Aに対して非対称に形成されている。凹部35aは金属層34をエッティングすることにより形成され得る。ベース20bは、凸部35に嵌め合わされる溝22に加えて、凹部35aに嵌め合わされる凸部22aを有する。凸部22aは、ベースをエッティングすることにより形成され得る。

#### 【0077】

半導体モジュール10cでは、半導体モジュール10と同様の作用効果が得られる。また、半導体モジュール10cは、半導体モジュール10の製造方法と同様の方法によって製造され得る。さらに、半導体モジュール10cでは、ベース20bに対する回路基板30bの向きが1つに決まるので、間違った向きで回路基板30bをベース20bに嵌め合わせることを抑制できる。その結果、半導体モジュール10cの組み立てが容易になる。

10

#### 【0078】

##### (第5実施形態)

図37は、第5実施形態に係る半導体モジュールを模式的に示す断面図である。図37に示される半導体モジュール10dは、回路基板をベースに嵌め合わせるための構造が異なること以外は半導体モジュール10と同じ構成を備える。半導体モジュール10dは、回路基板30c及びベース20cを備える。回路基板30cは、金属層34に形成された凹部35aを備える。ベース20cは、凹部35aに対応する凸部22aを備える。

#### 【0079】

20

半導体モジュール10dでは、半導体モジュール10と同様の作用効果が得られる。また、半導体モジュール10dは、半導体モジュール10の製造方法と同様の方法によって製造され得る。

#### 【0080】

##### (第6実施形態)

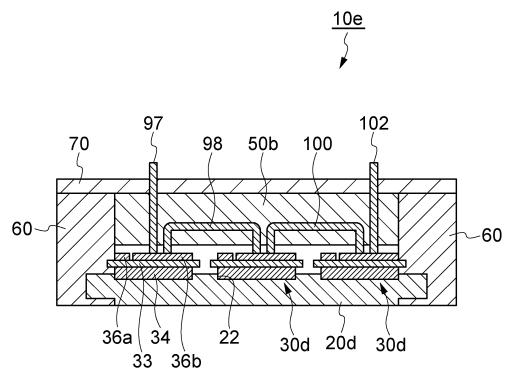

図38は、第6実施形態に係る半導体モジュールを模式的に示す断面図である。図38に示される半導体モジュール10eは、回路基板をベースに嵌め合わせるための構造が異なること以外は半導体モジュール10と同じ構成を備える。半導体モジュール10eは、回路基板30d及びベース20dを備える。回路基板30dは、凸部35及び凹部35aを備えていない。ベース20dは、回路基板30d全体に対応する溝22を備える。

30

#### 【0081】

半導体モジュール10eでは、半導体モジュール10と同様の作用効果が得られる。また、半導体モジュール10eは、半導体モジュール10の製造方法と同様の方法によって製造され得る。

#### 【0082】

##### (第7実施形態)

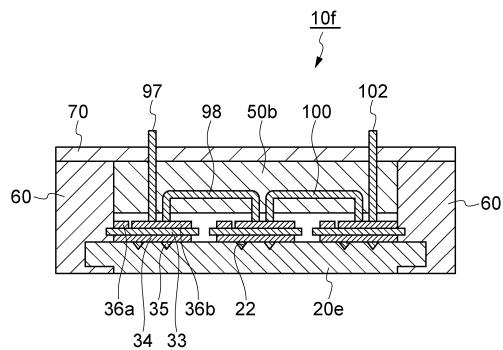

図39は、第7実施形態に係る半導体モジュールを模式的に示す断面図である。図39に示される半導体モジュール10fは、回路基板をベースに嵌め合わせるための構造が異なること以外は半導体モジュール10と同じ構成を備える。半導体モジュール10fは、回路基板30e及びベース20eを備える。回路基板30eでは、凸部35の延在方向に垂直な断面形状が三角形になっている。このため、ベース20eでは、溝22の延在方向に垂直な断面形状も三角形になっている。

40

#### 【0083】

半導体モジュール10fでは、半導体モジュール10と同様の作用効果が得られる。また、半導体モジュール10fは、半導体モジュール10の製造方法と同様の方法によって製造され得る。

#### 【0084】

##### (第8実施形態)

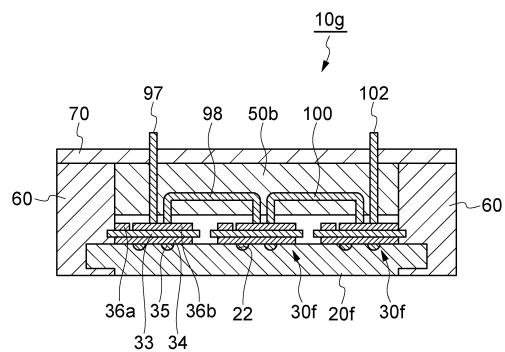

図40は、第8実施形態に係る半導体モジュールを模式的に示す断面図である。図40に示される半導体モジュール10gは、回路基板をベースに嵌め合わせるための構造が異

50

なること以外は半導体モジュール 10 と同じ構成を備える。半導体モジュール 10 g は、回路基板 30 f 及びベース 20 f を備える。回路基板 30 f では、凸部 35 の延在方向に垂直な断面形状が半円になっている。このため、ベース 20 f では、溝 22 の延在方向に垂直な断面形状も半円になっている。

#### 【 0 0 8 5 】

半導体モジュール 10 g では、半導体モジュール 10 と同様の作用効果が得られる。また、半導体モジュール 10 g は、半導体モジュール 10 の製造方法と同様の方法によって製造され得る。

#### 【 0 0 8 6 】

以上、本発明の好適な実施形態について詳細に説明したが、本発明は上記各実施形態に限定されない。第 1 ~ 第 8 実施形態に係る半導体モジュールの各構成は、互いに組み合わされてもよい。ベースが凹部を有し、支持基板が凹部に対応する凸部を有してもよい。ベースが凸部を有し、支持基板が凸部に対応する凹部を有してもよい。ベースが凹部を有し、支持基板が凹部にそのまま嵌め合わされてもよい。回路基板をベースに嵌め合わせるための構造は、任意の形状を有する凹部、溝、凸部、レール等であってもよい。

10

#### 【 符号の説明 】

#### 【 0 0 8 7 】

10 , 10 a , 10 b , 10 c , 10 d , 10 e , 10 f , 10 g ... 半導体モジュール

、 20 , 20 a , 20 b , 20 c , 20 d , 20 e , 20 f ... ベース、 22 ... 溝（回路基板をベースに嵌め合わせるための構造）、 30 , 30 a , 30 b , 30 c , 30 d , 30

e , 30 f ... 回路基板、 31 , 131 ... 支持基板、 32 , 132 ... 半導体素子、 40 ... 絶縁支持体、 80 ~ 91 ... 端子、 130 ... 回路基板の第 1 の端部、 200 ... ねじ（固定部材）

、 230 ... 回路基板の第 2 の端部、 A ... 軸線。

20

【 図 1 】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

---

フロントページの続き

審査官 木下 直哉

(56)参考文献 特開平11-214612(JP,A)

特開2001-127238(JP,A)

特開2009-188327(JP,A)

特開2001-168256(JP,A)

特開2001-203320(JP,A)

特開2011-091088(JP,A)

特開2004-103936(JP,A)

特開2000-031358(JP,A)

特開平02-266557(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 25/00-25/18

H01L 23/34-23/473