(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

15 September 2011 (15.09.2011)

(10) International Publication Number

**WO 2011/111490 A1**

(51) International Patent Classification:

**H04N 5/374 (2011.01) H01L 27/146 (2006.01)**

**G01J 1/44 (2006.01)**

(21) International Application Number:

**PCT/JP2011/053312**

(22) International Filing Date:

**9 February 2011 (09.02.2011)**

(25) Filing Language:

**English**

(26) Publication Language:

**English**

(30) Priority Data:

**2010-050776 8 March 2010 (08.03.2010) JP**

(71) Applicant (for all designated States except US): **SEMICONDUCTOR ENERGY LABORATORY CO., LTD.**

[JP/JP]; 398, Hase, Atsugi-shi, Kanagawa, 2430036 (JP).

(72) Inventors; and

(75) Inventors/Applicants (for US only): **KUROKAWA, Yoshiyuki** [JP/JP]; c/o SEMICONDUCTOR ENERGY LABORATORY CO., LTD., 398, Hase, Atsugi-shi, Kanagawa, 2430036 (JP). **IKEDA, Takayuki**. **KOZUMA, Munehiro**. **AOKI, Takeshi**.

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

Published:

— with international search report (Art. 21(3))

(54) Title: SEMICONDUCTOR DEVICE AND DRIVING METHOD THEREOF

FIG. 2

(57) Abstract: A semiconductor device includes a photodiode, a first transistor, a second transistor, and a third transistor. The second transistor and the third transistor have a function of retaining a charge accumulated in a gate of the first transistor. In a period during which the second transistor and the third transistor are off, a voltage level of a voltage applied to a gate of the second transistor is set to be lower than a voltage level of a source of the second transistor and a voltage level of a drain of the second transistor, and a voltage level of a voltage applied to a gate of the third transistor is set to be lower than a voltage level of a source of the third transistor and a voltage level of a drain of the third transistor.

## DESCRIPTION

**SEMICONDUCTOR DEVICE AND DRIVING METHOD THEREOF**5 **TECHNICAL FIELD**

[0001]

The technical field relates to a photosensor and a driving method thereof. The technical field also relates to a display device including a photosensor and a driving method thereof. Further, the technical field relates to a semiconductor device 10 including a photosensor and a driving method thereof.

**BACKGROUND ART**

[0002]

In recent years, a display device provided with a light-detecting sensor (also 15 referred to as a "photosensor") has attracted attention. In the display device including a photosensor, a display screen also serves as an input region. A display device having an image capturing function is an example of such a display device (see Patent Document 1, for example).

[0003]

20 Examples of a semiconductor device provided with a photosensor are a CCD image sensor and a CMOS image sensor. Such image sensors are used in, for example, electronic apparatuses like digital still cameras or cellular phones.

[0004]

In a display device provided with a photosensor, first, light is emitted from the 25 display device. When the light enters a region where an object to be detected exists, the light is blocked by the object to be detected, and is partly reflected. The light reflected by the object to be detected is detected by the photosensor provided in a pixel in the display device, whereby the object to be detected can be found in the region.

[0005]

30 In a semiconductor device including a photosensor, light emitted from an object to be detected or external light reflected by the object to be detected is detected directly by the photosensor or condensed by an optical lens or the like and then

detected.

[Reference]

[0006]

[Patent Document 1] Japanese Published Patent Application No. 2001-292276

5

## DISCLOSURE OF INVENTION

[0007]

In a semiconductor device including photosensors, each pixel is provided with a circuit including a transistor so as to collect electric signals generated by detection of 10 light with the photosensors provided in the respective pixels.

[0008]

However, it is difficult to accurately convert incident light into an electric signal because of variation in the electrical characteristics such as threshold voltage of a transistor provided in each pixel.

15 [0009]

An object of one embodiment of the present invention is to provide a semiconductor device including a photosensor in which incident light can be accurately converted into an electric signal.

[0010]

20 One embodiment of the present invention is a semiconductor device including a photodiode, a first transistor, a second transistor, a third transistor, and a fourth transistor. The photodiode has a function of supplying a charge corresponding to incident light to a gate of the first transistor through the second transistor. The first transistor has a function of accumulating the charge supplied to the gate and a function 25 of converting the accumulated charge into an output signal. The second transistor has a function of retaining the charge accumulated in the gate of the first transistor. The third transistor has a function of discharging the charge accumulated in the gate of the first transistor and a function of retaining the charge accumulated in the gate of the first transistor. The fourth transistor has a function of controlling reading of the output 30 signal. In a period during which the second transistor and the third transistor are off, a voltage level of a voltage applied to a gate of the second transistor is lower than a voltage level of a source of the second transistor and a voltage level of a drain of the

second transistor, and a voltage level of a voltage applied to a gate of the third transistor is lower than a voltage level of a source of the third transistor and a voltage level of a drain of the third transistor.

[0011]

5 Another embodiment of the present invention is a semiconductor device including a photodiode, a first transistor, a second transistor, a third transistor, and a fourth transistor. The photodiode has a function of supplying a charge corresponding to incident light to a gate of the first transistor through the second transistor. The first transistor has a function of accumulating the charge supplied to the gate and a function 10 of converting the accumulated charge into an output signal. The second transistor has a function of retaining the charge accumulated in the gate of the first transistor. The third transistor has a function of discharging the charge accumulated in the gate of the first transistor. The fourth transistor has a function of controlling reading of the output signal. In a period during which the second transistor and the third transistor are off, a 15 voltage level of a voltage applied to a gate of the second transistor is lower than a voltage level of a wiring electrically connected to the photodiode, and a voltage level of a voltage applied to a gate of the third transistor is lower than a voltage level of a photosensor reference signal line.

[0012]

20 Another embodiment of the present invention is a semiconductor device including a photodiode, a first transistor, a second transistor, a third transistor, and a fourth transistor. The photodiode has a function of supplying a charge corresponding to incident light to a gate of the first transistor through the second transistor. The first transistor has a function of accumulating the charge supplied to the gate and a function 25 of converting the accumulated charge into an output signal. The second transistor has a function of retaining the charge accumulated in the gate of the first transistor. The third transistor has a function of discharging the charge accumulated in the gate of the first transistor and a function of retaining the charge accumulated in the gate of the first transistor. The fourth transistor has a function of controlling reading of the output signal. A semiconductor layer of the second transistor and a semiconductor layer of the third transistor which are electrically connected to the gate of the first transistor 30 include an oxide semiconductor. In a period during which the second transistor and

the third transistor are off, a voltage level of a voltage applied to a gate of the second transistor is lower than a voltage level on a low voltage side of a source and a drain of the second transistor, and a voltage level of a voltage applied to a gate of the third transistor is lower than a voltage level on a low voltage side of a source and a drain of the third transistor.

5

[0013]

Another embodiment of the present invention is a semiconductor device including a photodiode, a first transistor, a second transistor, a third transistor, and a fourth transistor. The photodiode has a function of supplying a charge corresponding 10 to incident light to a gate of the first transistor through the second transistor. The first transistor has a function of accumulating the charge supplied to the gate and a function of converting the accumulated charge into an output signal. The second transistor has a function of retaining the charge accumulated in the gate of the first transistor. The third transistor has a function of discharging the charge accumulated in the gate of the 15 first transistor. The fourth transistor has a function of controlling reading of the output signal. A semiconductor layer of the second transistor and a semiconductor layer of the third transistor which are electrically connected to the gate of the first transistor include an oxide semiconductor. In a period during which the second transistor and the third transistor are off, a voltage level of a voltage applied to a gate of the second 20 transistor is lower than a voltage level of a wiring electrically connected to the photodiode, and a voltage level of a voltage applied to a gate of the third transistor is lower than a voltage level of a photosensor reference signal line.

[0014]

Note that the semiconductor device refers to an element having a 25 semiconductor property, and all the objects having the element. For example, a display device having a transistor is simply referred to as a semiconductor device in some cases.

[0015]

A semiconductor device including a photosensor in which incident light can be accurately converted into an electric signal can be provided.

30 [0016]

In addition, since accumulation operation is simultaneously performed in the plurality of photosensors, the accumulation operation can be completed in a short time,

so that an image of an object to be detected can be taken with little blur even when the object moves fast.

[0017]

Furthermore, a transistor controlling the accumulation operation includes an oxide semiconductor and thus has an extremely low off-current. Consequently, incident light can be accurately converted into an electric signal even when the number of photosensors increases and selection operation requires longer time. Thus, an image with high resolution can be taken.

## 10 BRIEF DESCRIPTION OF DRAWINGS

[0018]

In the accompanying drawings:

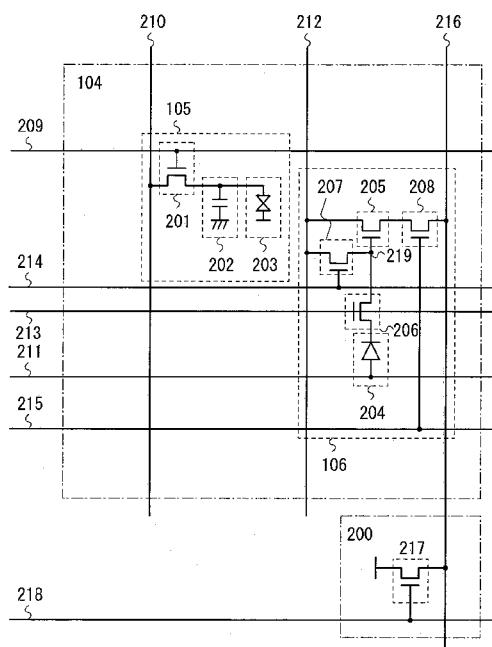

FIG. 1 illustrates an example of a display device according to one embodiment of the present invention;

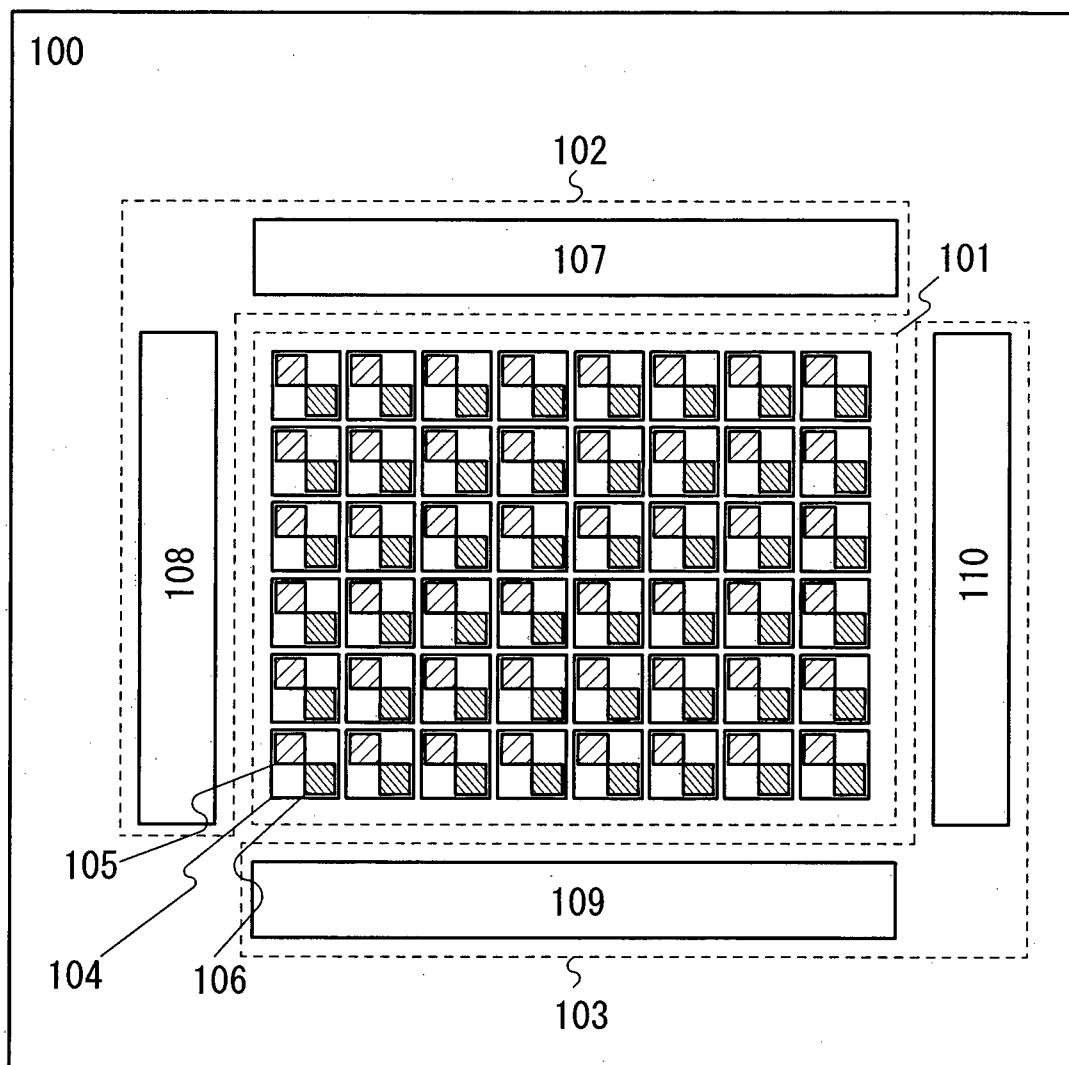

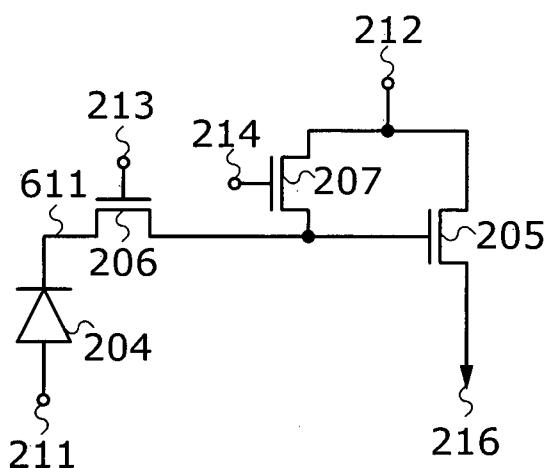

15 FIG. 2 illustrates an example of a display device according to one embodiment of the present invention;

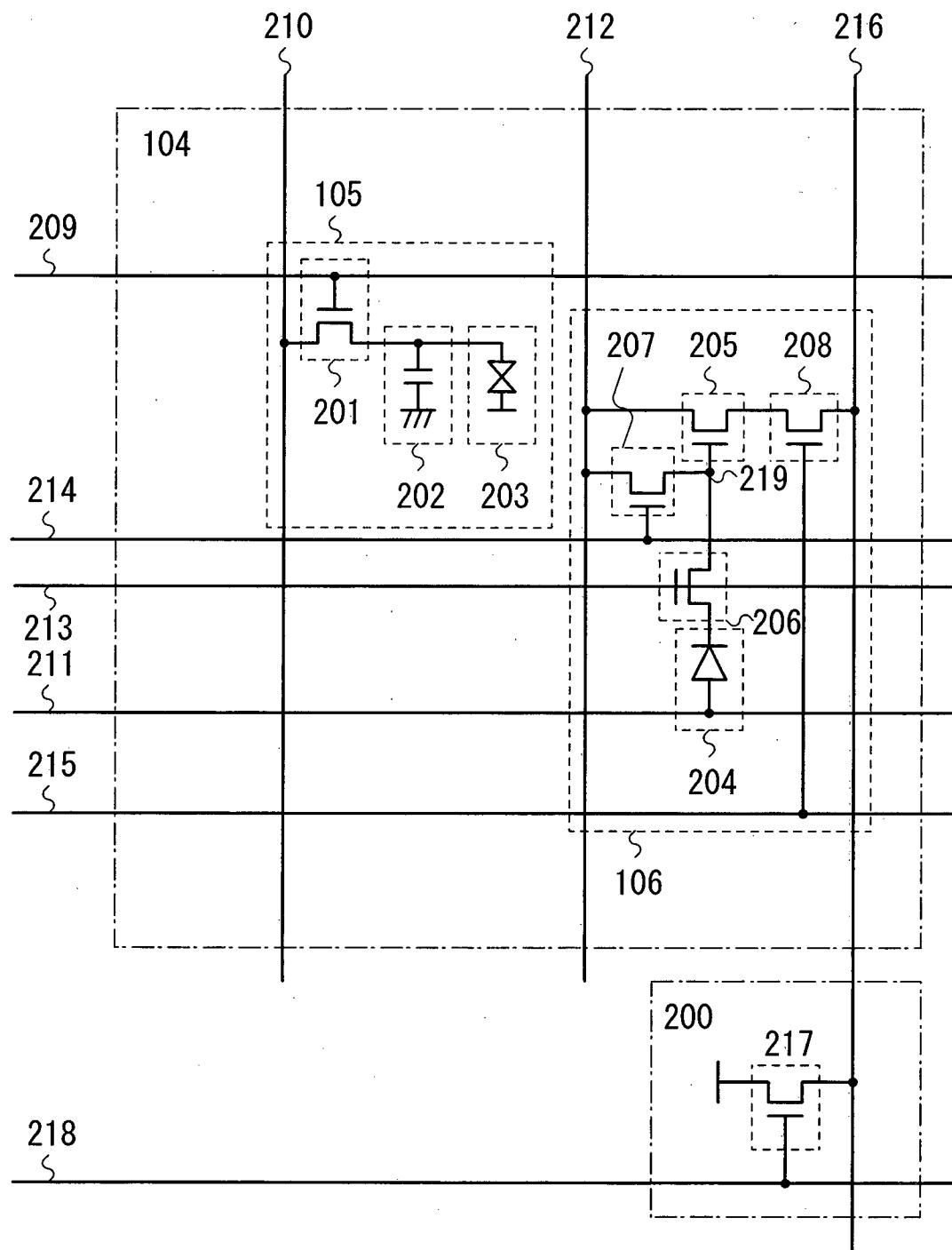

FIG. 3 is a timing chart according to one embodiment of the present invention;

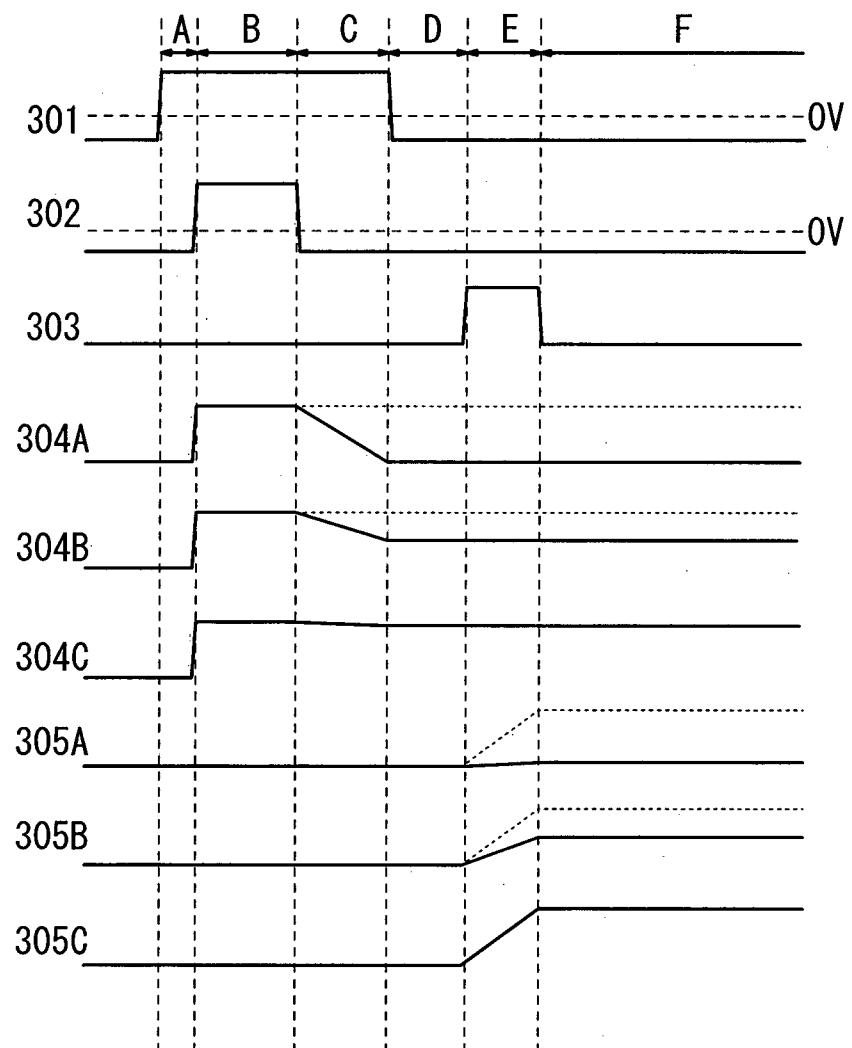

FIG. 4 is a timing chart according to one embodiment of the present invention;

FIG. 5 is a timing chart according to one embodiment of the present invention;

20 FIGS. 6A to 6C are circuit diagrams each illustrating an example of a photosensor according to one embodiment of the present invention;

FIG. 7 illustrates an example of a semiconductor device according to one embodiment of the present invention;

FIG. 8 is a graph showing the electrical characteristics of a transistor;

25 FIG. 9 illustrates an example of a semiconductor device according to one embodiment of the present invention; and

FIG. 10 is a timing chart according to one embodiment of the present invention.

## BEST MODE FOR CARRYING OUT THE INVENTION

30 [0019]

Embodiments will be described in detail below with reference to drawings. Note that the following embodiments can be implemented in many different modes, and

it is apparent to those skilled in the art that modes and details can be modified in various ways without departing from the spirit and scope of the present invention. Therefore, the present invention is not construed as being limited to the description of the embodiments. Note that in all the drawings for explaining the embodiments, like 5 portions or portions having a similar function are denoted by like reference numerals, and the description thereof is omitted.

[0020]

(Embodiment 1)

In this embodiment, a structure of a display device which is a semiconductor 10 device including a photosensor and operation thereof will be described with reference to FIG. 1, FIG. 2, and FIG. 3. Note that the display device including a photosensor can be used as an optical touch sensor.

[0021]

A structure of the display device will be described with reference to FIG. 1. A 15 display panel 100 includes a pixel circuit 101, a display element control circuit 102, and a photosensor control circuit 103.

[0022]

The pixel circuit 101 includes a plurality of pixels 104 arranged in matrix in a 20 row direction and a column direction. Each of the pixels 104 includes a display element 105 and a photosensor 106. The photosensor is not necessarily provided in each of the pixels 104, and may be provided in every two or more pixels 104. Alternatively, the photosensor may be provided outside the pixels 104.

[0023]

A circuit diagram of the pixel 104 will be described with reference to FIG. 2. 25 The pixel 104 includes the display element 105 provided with a transistor 201 (also referred to as a pixel transistor), a storage capacitor 202, and a liquid crystal element 203; and the photosensor 106 provided with a photodiode 204 which is a light-receiving element, a transistor 205 (also referred to as a first transistor), a transistor 206 (also referred to as a second transistor), a transistor 207 (also referred to as a third transistor), 30 and a transistor 208 (also referred to as a fourth transistor).

[0024]

In the display element 105, a gate of the transistor 201 is connected to a gate

signal line 209, one of a source and a drain of the transistor 201 is connected to a video data signal line 210, and the other of the source and the drain is connected to one electrode of the storage capacitor 202 and one electrode of the liquid crystal element 203. The other electrode of the storage capacitor 202 and the other electrode of the liquid crystal element 203 are each kept at a constant voltage level. The liquid crystal element 203 is an element including a pair of electrodes and a liquid crystal layer interposed between the pair of electrodes.

[0025]

10 Note that when it is explicitly described that "A and B are connected", the case where A and B are electrically connected, the case where A and B are functionally connected, and the case where A and B are directly connected are included therein.

[0026]

15 The transistor 201 has a function of controlling injection or release of charges to or from the storage capacitor 202. For example, when a high-level voltage is applied to the gate signal line 209, a voltage at the voltage level of the video data signal line 210 is applied to the storage capacitor 202 and the liquid crystal element 203. The storage capacitor 202 has a function of retaining a charge corresponding to a voltage applied to the liquid crystal element 203. The contrast (gray scale) of light passing through the liquid crystal element 203 is made by utilizing the change in the polarization direction due to voltage application to the liquid crystal element 203, whereby image display is realized. As the light passing through the liquid crystal element 203, light emitted from a light source (a backlight) on the back surface of the display device is used.

[0027]

20 25 For the transistor 201, an amorphous semiconductor, a microcrystal semiconductor, a polycrystalline semiconductor, an oxide semiconductor, a single crystal semiconductor, or the like can be used. In particular, display quality can be increased by using an oxide semiconductor to obtain a transistor with an extremely low off-current.

30 [0028]

Although the display element 105 described here includes the liquid crystal element, the display element 105 may include other elements such as a light-emitting

element. The light-emitting element is an element whose luminance is controlled with current or voltage, and specific examples thereof are a light-emitting diode and an organic light-emitting diode (OLED). Note that in this embodiment, a structure of an optical touch sensor (also referred to as an optical touch panel) provided with the 5 display element 105 and the photosensor 106 is described; however, a structure in which a display element is eliminated can also be employed. In that case, an image sensor in which a plurality of photosensors is provided can be obtained.

[0029]

In the photosensor 106, one electrode of the photodiode 204 is connected to a 10 wiring 211 (also referred to as a ground line), and the other electrode thereof is connected to one of a source and a drain of the transistor 206. One of a source and a drain of the transistor 205 is connected to a photosensor reference signal line 212, and the other of the source and the drain is connected to one of a source and a drain of the transistor 208. A gate of the transistor 206 is connected to a gate signal line 213, and 15 the other of the source and the drain of the transistor 206 is connected to a gate of the transistor 205 and one of a source and a drain of the transistor 207. A gate of the transistor 207 is connected to a photodiode reset signal line 214, and the other of the source and the drain of the transistor 207 is connected to the photosensor reference signal line 212. A gate of the transistor 208 is connected to a gate signal line 215, and 20 the other of the source and the drain of the transistor 208 is connected to a photosensor output signal line 216.

[0030]

For the photodiode 204, an amorphous semiconductor, a microcrystal semiconductor, a polycrystalline semiconductor, an oxide semiconductor, a single 25 crystal semiconductor, or the like can be used. In particular, a single crystal semiconductor (e.g., single crystal silicon) with few crystal defects is preferably used so as to improve the proportion of an electric signal generated from incident light (the quantum efficiency). As the semiconductor material, it is preferable to use silicon semiconductor such as silicon or silicon germanium, the crystallinity of which can be 30 easily increased.

[0031]

For the transistor 205, an amorphous semiconductor, a microcrystal

semiconductor, a polycrystalline semiconductor, an oxide semiconductor, a single crystal semiconductor, or the like can be used. In particular, the transistor 205 has a function of accumulating a charge which is supplied from the photodiode 204 through the transistor 206, in a node connected to the gate and converting the accumulated 5 charge into an output signal. Therefore, a single crystal semiconductor is preferably used to obtain a transistor with high mobility. As the semiconductor material, it is preferable to use silicon semiconductor such as silicon or silicon germanium, the crystallinity of which can be easily increased.

[0032]

10 For the transistor 206, an amorphous semiconductor, a microcrystal semiconductor, a polycrystalline semiconductor, an oxide semiconductor, a single crystal semiconductor, or the like can be used. In particular, the transistor 206 has a function of retaining a charge of the gate of the transistor 205 by controlling on/off of the transistor 206. Therefore, the transistor 206 preferably uses an oxide 15 semiconductor to have an extremely low off-current.

[0033]

For the transistor 207, an amorphous semiconductor, a microcrystal semiconductor, a polycrystalline semiconductor, an oxide semiconductor, a single crystal semiconductor, or the like can be used. In particular, the transistor 207 has a 20 function of discharging a charge of the gate of the transistor 205 and a function of retaining a charge of the gate of the transistor 205, by controlling on/off of the transistor 207. Therefore, the transistor 207 preferably uses an oxide semiconductor to have an extremely low off-current.

[0034]

25 For the transistor 208, an amorphous semiconductor, a microcrystal semiconductor, a polycrystalline semiconductor, an oxide semiconductor, a single crystal semiconductor, or the like can be used. In particular, a single crystal semiconductor is preferably used for the transistor 208 so that the transistor 208 has high mobility and has a function of supplying an output signal of the transistor 205 to 30 the photosensor output signal line 216. As the semiconductor material, it is preferable to use silicon semiconductor such as silicon or silicon germanium, the crystallinity of which can be easily increased.

## [0035]

The display element control circuit 102 is a circuit for controlling the display element 105, and includes a display element driver circuit 107 from which a signal is input to the display element 105 through a signal line (also referred to as a source signal line) such as the video data signal line; and a display element driver circuit 108 from which a signal is input to the display element 105 through a scan line (also referred to as a gate signal line). For example, the display element driver circuit 108 on the scan line side has a function of selecting a display element included in a pixel in a specified row. The display element driver circuit 107 on the signal line side has a function of supplying a predetermined-level voltage to the display element included in the pixel in the selected row. Note that in the display element 105 connected to the gate signal line to which a high-level voltage is applied from the display element driver circuit 108 on the scan line side, the transistor is turned on and supplied with a voltage at the same level as the voltage applied to the video data signal line from the display element driver circuit 107 on the signal line side.

## [0036]

The photosensor control circuit 103 is a circuit for controlling the photosensor 106, and includes a photosensor reading circuit 109 on the signal line side, where the signal line includes such as the photosensor output signal line or the photosensor reference signal line; and a photosensor driver circuit 110 on the scan line side.

## [0037]

The photosensor driver circuit 110 has a function of performing the hereinafter described reset operation, accumulation operation, and selection operation on the photosensor 106 included in a pixel in a specified row.

## 25 [0038]

The photosensor reading circuit 109 has a function of extracting an output signal of the photosensor 106 included in a pixel in a selected row. Note that from the photosensor reading circuit 109, an output of the photosensor 106, which is an analog signal, is extracted as it is to the outside of the display panel with the use of an OP amplifier. Alternatively, the output of the photosensor 106 is converted into a digital signal with the use of an A/D converter circuit and then extracted to the outside of the display panel.

[0039]

A precharge circuit included in the photosensor reading circuit 109 will be described with reference to FIG. 2. In FIG. 2, a precharge circuit 200 for one column of pixels includes a transistor 217 and a precharge signal line 218. Note that the 5 photosensor reading circuit 109 can include an OP amplifier or an A/D converter circuit connected to a subsequent stage of the precharge circuit 200.

[0040]

In the precharge circuit 200, before the operation of the photosensor in the pixel, the voltage level of the photosensor output signal line is set to a reference voltage 10 level. In FIG. 2, the precharge signal line 218 is set to an H level (hereinafter, abbreviated to "H") so that the transistor 217 is turned on, whereby the voltage level of the photosensor output signal line 216 can be set to a reference voltage level (here, a low voltage level). Note that it is effective to provide a storage capacitor for the photosensor output signal line 216 so that the voltage level of the photosensor output 15 signal line 216 is stabilized. Note that the reference voltage level can be set to a high voltage level. In that case, the conductivity type of the transistor 217 is made opposite to that of FIG. 2 and the precharge signal line 218 is set to an L level (hereinafter, abbreviated to "L"), whereby the voltage level of the photosensor output signal line 216 can be set to a reference voltage level.

20 [0041]

Note that an H-level voltage and an L-level voltage in this embodiment correspond to a voltage which is based on a high power source voltage level and a voltage which is based on a low power source voltage level, respectively. In other words, the H-level voltage is a constant voltage of 3 V to 20 V, and the L-level voltage 25 is a constant voltage of 0 V (also referred to as a reference voltage level or a ground voltage level).

[0042]

Next, the operation of the photosensor 106 will be described with reference to the timing chart of FIG. 3. In FIG. 3, a signal 301, a signal 302, and a signal 303 30 respectively correspond to the voltage levels of the gate signal line 213, the reset signal line 214, and the gate signal line 215 in FIG. 2. Further, signals 304A to 304C each correspond to the voltage level of the gate of the transistor 205 (the voltage level of a

node 219 in FIG. 2). The signal 304A shows the case where the illuminance of light which enters the photodiode 204 is high (hereinafter, high illuminance), the signal 304B shows the case where the illuminance of light which enters the photodiode 204 is middle (hereinafter, middle illuminance), and the signal 304C shows the case where the illuminance of light which enters the photodiode 204 is low (hereinafter, low illuminance). Further, the signals 305A to 305C each correspond to the voltage level of the photosensor output signal line 216, and the signals 305A to 305C show the high illuminance, the middle illuminance, and the low illuminance, respectively.

[0043]

10 In a period A, the voltage level of the gate signal line 213 (the signal 301) is set to "H", the voltage level of the reset signal line 214 (the signal 302) is set to a level lower than 0 V (hereinafter, abbreviated to "L2"), and the voltage level of the gate signal line 215 (the signal 303) is set to "L". Next, in a period B, the voltage level of the gate signal line 213 (the signal 301) is set to "H", the voltage level of the reset signal line 15 214 (the signal 302) is set to "H", and the voltage level of the gate signal line 215 (the signal 303) is set to "L". As a result, the photodiode 204 and the transistor 206 are turned on, and the voltage level of the node 219 (the signals 304A to 304C) becomes "H". At this time, reverse bias is applied to the photodiode 204. Further, when the voltage level of the precharge signal line 218 is set to the H level, the voltage level of 20 the photosensor output signal line 216 (the signals 305A to 305C) is precharged to "L". As described above, the period A and the period B are a reset operation period.

[0044]

25 Note that in this specification, the level lower than 0 V means, specifically, a voltage level which is lower than the voltage level of the source of the transistor 206, the voltage level of the drain of the transistor 206, the voltage level of the source of the transistor 207, and the voltage level of the drain of the transistor 207. In this embodiment, the voltage level on the low voltage side of the sources and the drains of the transistors 206 and 207 is 0 V which is the voltage level of the ground line, and the voltage level of the gate signal line 213 and the voltage level of the reset signal line 214 30 in a predetermined period may be referred to as the level lower than 0 V. In other words, the voltage level on the low voltage side of the source and the drain of the transistor 206 and the voltage level on the low voltage side of the source and the drain

of the transistor 207 can be respectively referred to as the voltage level of the wiring 211 connected to the photodiode 204 and the voltage level of the photosensor reference signal line 212, based on the circuit configuration illustrated in FIG. 2.

[0045]

5 Next, in a period C, the voltage level of the gate signal line 213 (the signal 301) is set to "H", the voltage level of the reset signal line 214 (the signal 302) is set to "L2", and the voltage level of the gate signal line 215 (the signal 303) is set to "L". As a result, the voltage level of the node 219 (the signals 304A to 304C) starts to decrease with current due to light irradiation to the photodiode 204 (hereinafter, referred to as 10 photocurrent). In the photodiode 204, photocurrent is increased with increase in the amount of incident light; accordingly, the voltage level of the node 219 (the signals 304A to 304C) changes in accordance with the amount of incident light. Specifically, since photocurrent is largely increased in the signal 304A having a large amount of incident light, the signal 304A which is the voltage level of the node 219 is largely 15 decreased in the period C. Further, since photocurrent hardly flows in the signal 304C having a small amount of incident light, the signal 304C which is the voltage level of the node 219 hardly changes in the period C. Furthermore, since the amount of photocurrent is increased to an amount between the amount of the signal 304A and that of the signal 304C in the signal 304B having a middle amount of incident light, the 20 amount of the signal 304B which is the voltage level of the node 219 is decreased to an amount between the decreased amount of the signal 304A and the decreased amount of the signal 304C. In other words, the photodiode 204 has a function of supplying a charge corresponding to the incident light to the gate of the transistor 205 through the transistor 206. Then, the channel resistance between the source and the drain of the 25 transistor 205 changes. As described above, the period C is an accumulation operation period.

[0046]

Next, in a period D, the voltage level of the gate signal line 213 (the signal 301) is set to "L2", the voltage level of the reset signal line 214 (the signal 302) is set to 30 "L2", and the voltage level of the gate signal line 215 (the signal 303) is set to "L". The signals 304A to 304C which are the voltage level of the node 219 become constant. Here, the voltage levels of the signals 304A to 304C in the period D are determined by

the amount of photocurrent of the photodiode 204 in the above-described accumulation operation period (the period C). That is, the amount of charge accumulated in the node 219 changes in accordance with the incident light to the photodiode 204. Note that an oxide semiconductor is used for a semiconductor layer of the transistor 206 and a semiconductor layer of the transistor 207 to obtain transistors with extremely low off-currents, whereby the accumulated charge can be kept constant until the subsequent selection operation is performed.

[0047]

Next, in a period E, the voltage level of the gate signal line 213 (the signal 301) 10 is set to "L2", the voltage level of the reset signal line 214 (the signal 302) is set to "L2", and the voltage level of the gate signal line 215 (the signal 303) is set to "H". As a result, the transistor 208 is turned on and the photosensor reference signal line 212 and the photosensor output signal line 216 are brought into electrical conduction through the transistors 205 and 208. Then, the voltage level of the photosensor output signal line 15 216 (the signals 305A to 305C) is increased in accordance with incident light to the above-described photodiode 204. Note that in a period before the period E, the voltage level of the precharge signal line 218 is set to "H" so that the precharge of the photosensor output signal line 216 is completed. Here, the rate at which the voltage level of the photosensor output signal line 216 (the signals 305A to 305C) is increased 20 depends on the current between the source and the drain of the transistor 205, namely, the amount of incident light to the photodiode 204 during the period C which is the accumulation operation period. As described above, the period E is a selection operation period.

[0048]

25 Next, in a period F, the voltage level of the gate signal line 213 (the signal 301) is set to "L2", the voltage level of the reset signal line 214 (the signal 302) is set to "L2", and the voltage level of the gate signal line 215 (the signal 303) is set to "L". As a result, the transistor 208 is turned off, and the voltage level of the photosensor output signal line 216 (the signals 305A to 305C) becomes constant. The constant value here 30 is determined in accordance with the amount of incident light to the photodiode 204. Thus, the amount of incident light to the photodiode 204 during the accumulation operation can be determined by obtaining the voltage level of the photosensor output

signal line 216. As described above, the period F is a reading operation period.

[0049]

As described above, in the semiconductor device of this embodiment, the voltage level of the voltage applied to the gate of the transistor 206 and the voltage level of the voltage applied to the gate of the transistor 207 are set to lower than 0 V in the periods D, E, and F during which the transistor 206 is off and the periods A, D, E, and F during which the transistor 207 is off. In other words, the voltage level of the voltage applied between the gate and the source of the transistor 206 is set to a level of the threshold voltage of the transistor 206 or lower, and the voltage level of the voltage applied between the gate and the source of the transistor 207 is set to a level of the threshold voltage of the transistor 207 or lower. Thus, the function of retaining the charge retained in the gate of the transistor 205 can be improved.

[0050]

More specifically, the operation of individual photosensors is realized by repeatedly performing the reset operation, the accumulation operation, the selection operation, and the reading operation. As described above, in this embodiment, the voltage level of the voltage applied to the gate of the transistor 206 and the voltage level of the voltage applied to the gate of the transistor 207 are lower than 0 V in a period during which the transistors 206 and 207 are off. Therefore, the transistors 206 and 207 can be turned off more reliably, which can improve the function of retaining the charge retained in the gate of the transistor 205 at the time of the accumulation operation and the reading operation. Further, the function of accurately converting the incident light into an electric signal in a photosensor can be improved. Furthermore, a semiconductor layer of the transistor 206 and a semiconductor layer of the transistor 207 preferably use an oxide semiconductor to obtain transistors having extremely low off-currents. With such a structure, the function of more accurately converting the incident light into an electric signal in a photosensor can be improved.

[0051]

This embodiment can be combined with any of the other embodiments as appropriate.

[0052]

(Embodiment 2)

In this embodiment, a method for driving a plurality of photosensors will be described.

[0053]

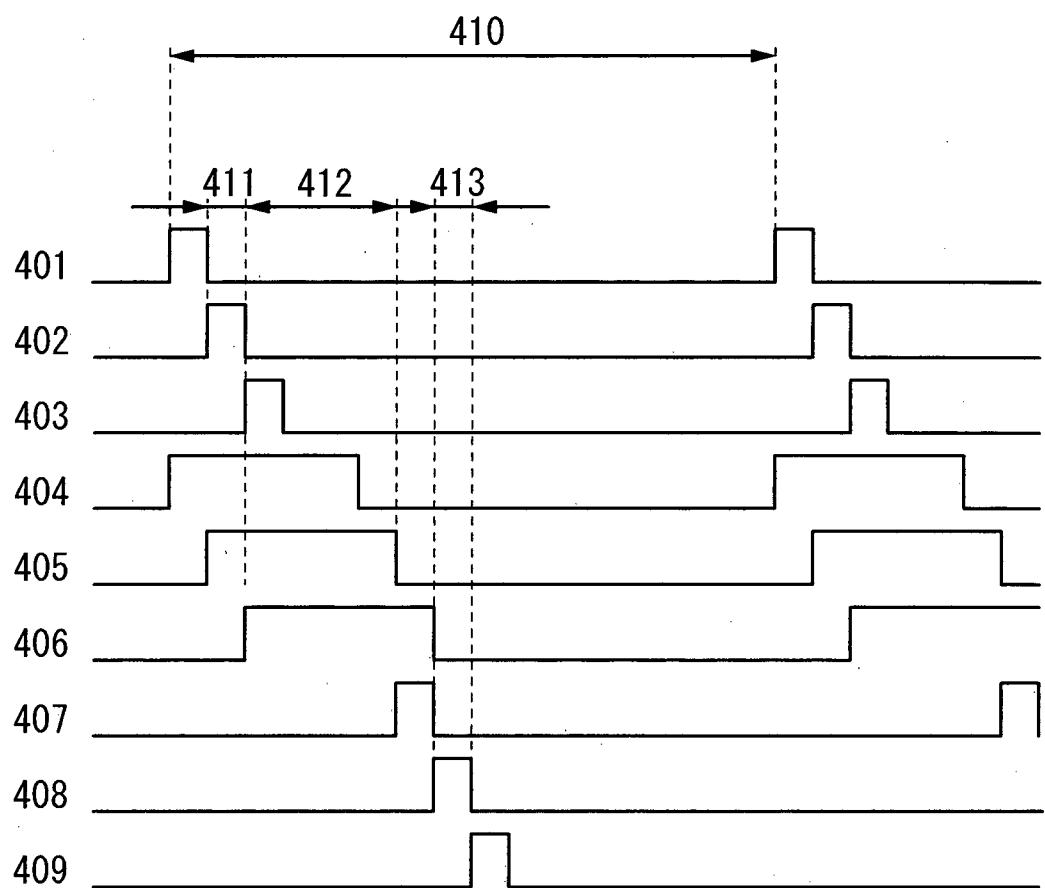

First, a driving method illustrated in the timing chart of FIG. 4 is described. In FIG. 4, a signal 401, a signal 402, and a signal 403 are signals showing voltage changes of the reset signal lines 214 in photosensors of the first row, the second row, and the third row, respectively. A signal 404, a signal 405, and a signal 406 are signals showing voltage changes of the gate signal lines 213 in the photosensors of the first row, the second row, and the third row, respectively. A signal 407, a signal 408, and a signal 409 are signals showing voltage changes of the gate signal lines 215 in the photosensors of the first row, the second row, and the third row, respectively. A period 410 is a period required for one imaging. A period 411 is a period during which the reset operation is performed in the photosensor of the second row, a period 412 is a period during which the accumulation operation is performed in the photosensor of the second row, and a period 413 is a period during which the selection operation is performed in the photosensor of the second row. By thus sequentially driving the photosensor of each row, images can be taken.

[0054]

It is found here that the accumulation operation in the photosensor of each row has a time lag. That is, imaging in the photosensor of each row is not performed simultaneously, leading to blurring of the image taken. In particular, an image of an object to be detected which moves fast is easily taken to have a distorted shape: if the object to be detected moves in a direction from the first row to the third row, an enlarged image is taken leaving a trail behind it; and if the object to be detected moves in the opposite direction, a reduced image is taken.

[0055]

In order to prevent the time lag of the accumulation operation in the photosensor of each row, it is effective that the photosensor of each row is sequentially driven in a shorter cycle. In that case, however, the output signal of the photosensor needs to be obtained at very high speed with an OP amplifier or an A/D converter circuit, which causes an increase in power consumption, and makes it very difficult to obtain an image with high resolution, in particular.

[0056]

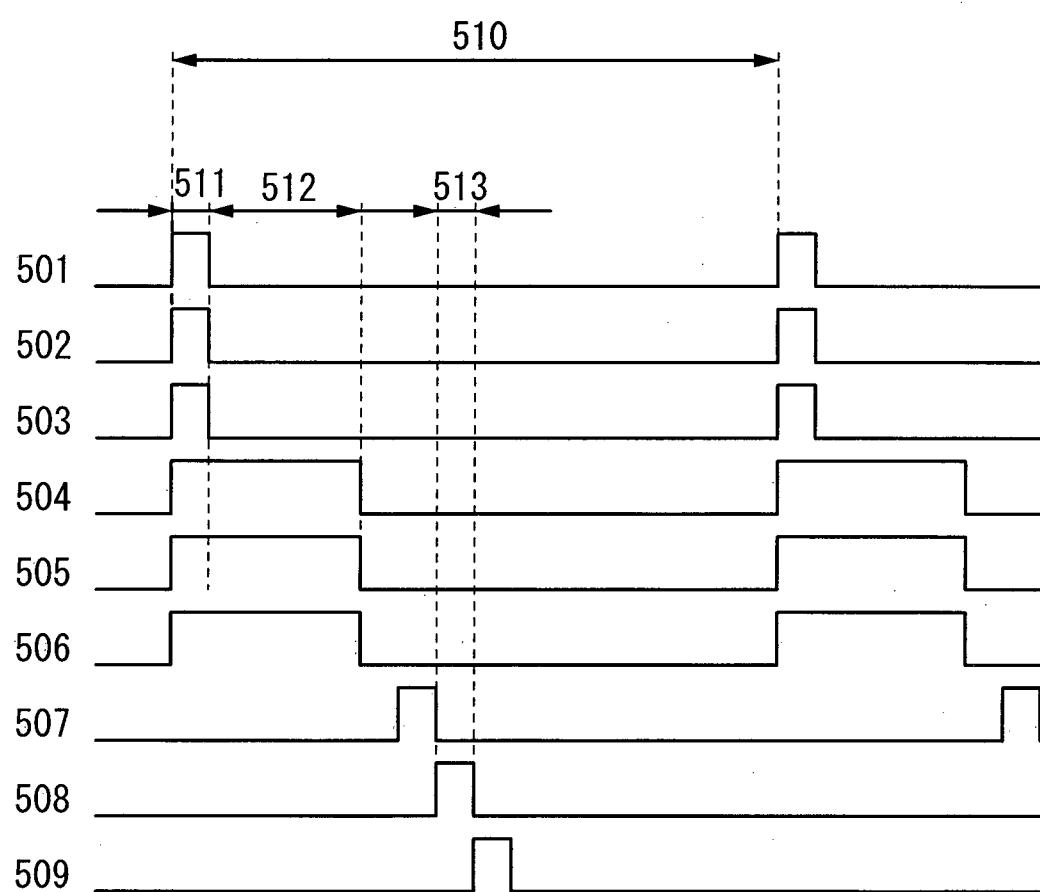

Thus, a driving method illustrated in the timing chart of FIG. 5 is proposed. In FIG. 5, a signal 501, a signal 502, and a signal 503 are signals showing voltage changes of the reset signal lines 214 in the photosensors of the first row, the second row, and the 5 third row, respectively. A signal 504, a signal 505, and a signal 506 are signals showing voltage changes of the gate signal lines 213 in the photosensors of the first row, the second row, and the third row, respectively. A signal 507, a signal 508, and a signal 509 are signals showing voltage changes of the gate signal lines 215 in the photosensors of the first row, the second row, and the third row, respectively. A period 10 510 is a period required for one imaging. A period 511 is a period during which the reset operation (at the same time in all the rows) is performed in the photosensor of the second row, a period 512 is a period during which the accumulation operation (at the same time in all the rows) is performed in the photosensor of the second row, and a period 513 is a period during which the selection operation is performed in the 15 photosensor of the second row.

[0057]

FIG. 5 is different from FIG. 4 in that the reset operation and the accumulation operation are each performed in the same period in the photosensors of all the rows, and after the accumulation operation, the selection operation is sequentially performed in 20 each row without synchronization with the accumulation operation. When the accumulation operation is performed in the same period, imaging in the photosensor of each row is performed simultaneously and an image of an object to be detected can be easily taken with little blur even when the object moves fast. Since the accumulation operation is performed at the same time, a driver circuit can be provided in common for 25 the reset signal line 214 of each photosensor. Further, a driver circuit can also be provided in common for the gate signal line 213 of each photosensor. Such driver circuits provided in common are effective in reducing the number of peripheral circuits or reducing power consumption. In addition, the selection operation sequentially performed in each row makes it possible to lower the operation rate of an OP amplifier 30 or an A/D converter circuit when the output signal of the photosensor is obtained. At this time, the total time for the selection operation is preferably longer than the time for the accumulation operation, which is particularly effective in the case of obtaining an

image with high resolution.

[0058]

Note that FIG. 5 illustrates the timing chart of the method for sequentially driving the photosensor of each row; it is also effective to sequentially drive the photosensor only in a certain row in order to obtain an image in a specified region. As a result, a desired image can be obtained while the operation and power consumption of the OP amplifier or the A/D converter circuit are reduced. Further, a method for driving the photosensor of every few rows, namely, some of a plurality of photosensors, is also effective. As a result, an image with desired resolution can be obtained while the operation and power consumption of the OP amplifier or the A/D converter circuit are reduced.

[0059]

In order to realize the above driving method, the voltage level of the gate of the transistor 205 in each photosensor needs to be kept constant even after the accumulation operation is completed. Thus, the transistor 207 preferably uses an oxide semiconductor to have an extremely low off-current as described in the above embodiment.

[0060]

In the above manner, it is possible to provide a low-power consumption display device or semiconductor device which allows a high-resolution image of an object to be detected to be taken with little blur even when the object moves fast.

[0061]

This embodiment can be combined with any of the other embodiments as appropriate.

25 [0062]

(Embodiment 3)

In this embodiment, a modified example of the circuit configuration of the photosensor 106 in FIG. 2 will be described.

[0063]

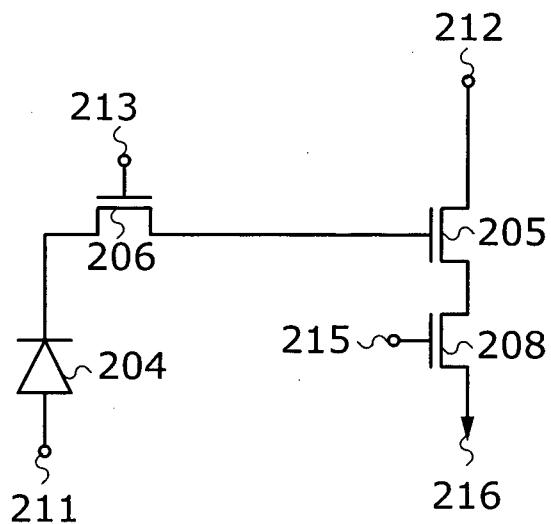

30 FIG. 6A illustrates a configuration in which the transistor 207 for controlling the reset operation of the photosensor, which is connected to the gate of the transistor 205 in FIG. 2, is omitted. In the configuration of FIG. 6A, when the reset operation of

the photosensor is performed, the charge accumulated in the gate of the transistor 205 may be discharged by changing the voltage level of the wiring 211.

[0064]

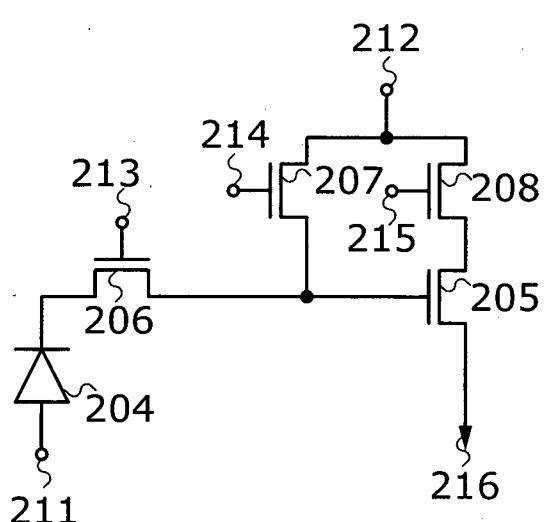

FIG. 6B illustrates a configuration in which the transistor 205 and the transistor 208 are connected in a manner opposite to that in the photosensor 106 in FIG. 2. Specifically, the one of the source and the drain of the transistor 205 is connected to the photosensor output signal line 216, and the one of the source and the drain of the transistor 208 is connected to the photosensor reference signal line 212.

[0065]

FIG. 6C illustrates a configuration in which the transistor 208 is omitted in the configuration of the photosensor 106 in FIG. 2. The configuration of FIG. 6C is different from those of FIG. 2 and FIGS. 6A and 6B: when the selection operation and the reading operation of the photosensor are performed, a change of the signal corresponding to the charge accumulated in the gate of the transistor 205 may be read by changing the voltage level of the photosensor reference signal line 212.

[0066]

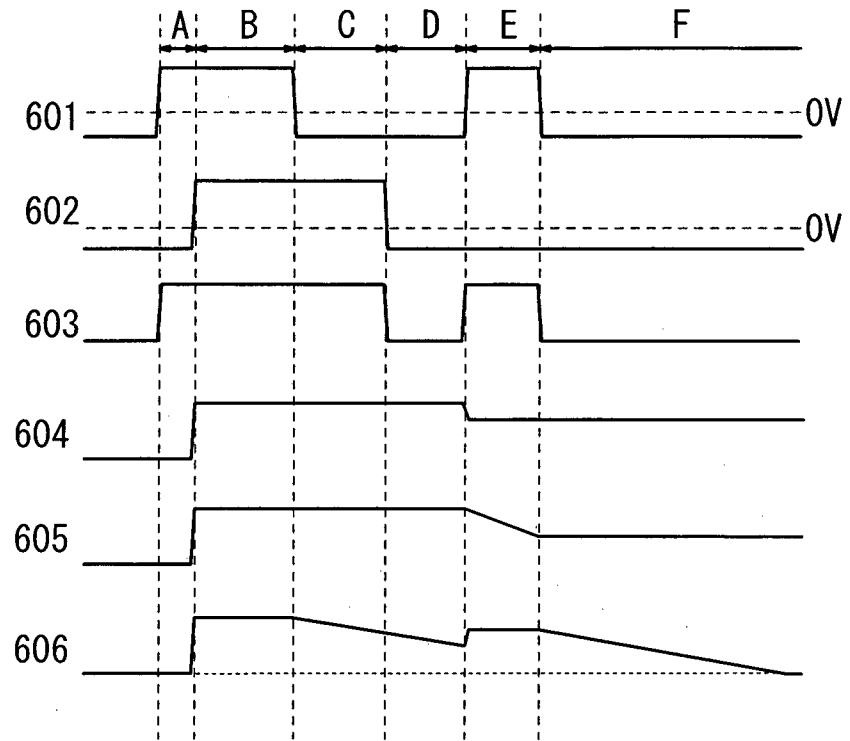

A timing chart relating to the operation of the photosensor 106 illustrated in FIG. 6C is shown in FIG. 10. In FIG. 10, a signal 601, a signal 602, and a signal 603 respectively correspond to the voltage levels of the gate signal line 213, the reset signal line 214, and the photosensor reference signal line 212 in FIG. 6C. A signal 604 corresponds to the voltage level of the gate of the transistor 205 and shows the case where the illuminance of light which enters the photodiode 204 is middle (hereinafter, middle illuminance). A signal 605 shows the voltage level of the photosensor output signal line 216. A signal 606 shows the voltage level of a node 611 in FIG. 6C.

[0067]

The timing chart of FIG. 10 is described. In a period A, the voltage levels of the signal 601 and the signal 603 are set to "H", and the voltage level of the signal 602 is set to "L2". Then, in a period B, when the voltage level of the signal 602 is set to "H", the voltage level of the signal 604 is reset, and the voltage levels of the signal 605 and the signal 606 are increased. That is, the period A and the period B are a reset operation period. Next, in a period C, when the voltage level of the signal 601 is set to "L2", the voltage level of the signal 606 is decreased. Then, in a period D, the voltage

levels of the signal 602 and the signal 603 are set to "L2". That is, the period C and the period D are an accumulation operation period. Next, in a period E, when the voltage levels of the signal 601 and the signal 603 are set to "H", the voltage level of the signal 604 and the voltage level of the signal 606 become the same voltage level, and the voltage level of the signal 605 changes in accordance with an output signal of the photosensor. That is, the period E is a selection operation period. Then, in a period F, the voltage levels of the signal 601 and the signal 603 are set to "L2", and the voltage level of the signal 605 is read. That is, the period F is a reading operation period. In such a manner, the operation of the photosensor 106 illustrated in FIG. 6C may be performed.

[0068]

This embodiment can be combined with any of the other embodiments as appropriate.

[0069]

15 (Embodiment 4)

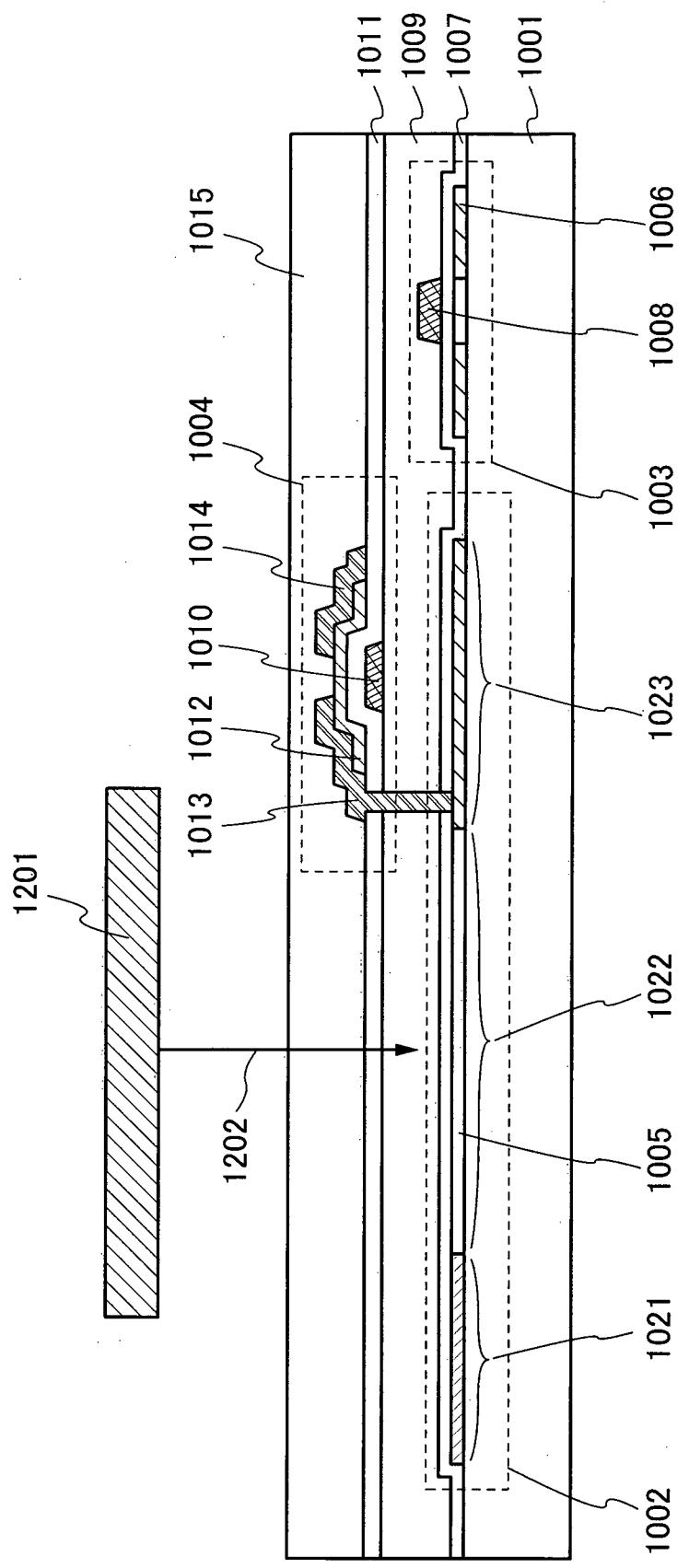

In this embodiment, a structure and manufacturing method of a semiconductor device including a photosensor will be described. FIG. 7 is a cross-sectional view of a semiconductor device. Note that the following semiconductor device can be applied to a display device.

20 [0070]

In FIG. 7, a photodiode 1002, a transistor 1003, and a transistor 1004 are provided over a substrate 1001 having an insulating surface. The photodiode 1002, the transistor 1003, and the transistor 1004 are respectively cross-sectional views of the photodiode 204, the transistor 205, and the transistor 206 in FIG. 2. Light 1202 emitted from an object to be detected 1201, external light 1202 reflected by the object to be detected 1201, or light 1202 emitted from the inside of the device and reflected by the object to be detected 1201 enters the photodiode 1002. An object to be detected may be provided on the substrate 1001 side.

[0071]

30 The substrate 1001 can be an insulating substrate (e.g., a glass substrate or a plastic substrate), the insulating substrate on which an insulating film (e.g., a silicon oxide film or a silicon nitride film) is formed, a semiconductor substrate (e.g., a silicon

substrate) on which the insulating film is formed, or a metal substrate (e.g., an aluminum substrate) on which the insulating film is formed.

[0072]

The photodiode 1002 is a lateral-junction pin diode and includes a 5 semiconductor film 1005. The semiconductor film 1005 includes a region having p-type conductivity (a p-layer 1021), a region having i-type conductivity (an i-layer 1022), and a region having n-type conductivity (an n-layer 1023). Note that the photodiode 1002 may be a pn diode.

[0073]

10 The lateral-junction pin or pn diode can be formed by adding a p-type impurity and an n-type impurity to predetermined regions of the semiconductor film 1005.

[0074]

15 In the photodiode 1002, a single crystal semiconductor (e.g., single crystal silicon) with few crystal defects is preferably used for the semiconductor film 1005 so as to improve the proportion of an electric signal generated from incident light (the quantum efficiency).

[0075]

The transistor 1003 is a top-gate thin film transistor and includes a semiconductor film 1006, a gate insulating film 1007, and a gate electrode 1008.

20 [0076]

The transistor 1003 has a function of converting a charge supplied from the photodiode 1002 into an output signal. Therefore, a single crystal semiconductor (e.g., single crystal silicon) is preferably used for the semiconductor film 1006 to obtain a transistor with high mobility.

25 [0077]

An example of forming the semiconductor film 1005 and the semiconductor film 1006 with the use of a single crystal semiconductor will be described. A damaged region is formed at a desired depth of a single crystal semiconductor substrate (e.g., a single crystal silicon substrate) by ion irradiation or the like. The single crystal 30 semiconductor substrate and the substrate 1001 are bonded to each other with an insulating film interposed therebetween; then, the single crystal semiconductor substrate is split along the damaged region, whereby a semiconductor film is formed over the

substrate 1001. The semiconductor film is processed (patterned) into a desired shape by etching or the like, so that the semiconductor film 1005 and the semiconductor film 1006 are formed. Since the semiconductor film 1005 and the semiconductor film 1006 can be formed in the same process, cost reduction can be realized. In this manner, the 5 photodiode 1002 and the transistor 1003 can be formed on the same surface.

[0078]

Note that an amorphous semiconductor, a microcrystal semiconductor, a polycrystalline semiconductor, an oxide semiconductor, or the like can also be used for the semiconductor film 1005 and the semiconductor film 1006. In particular, a single 10 crystal semiconductor is preferably used to obtain a transistor with high mobility. As the semiconductor material, it is preferable to use silicon semiconductor such as silicon or silicon germanium, the crystallinity of which can be easily increased.

[0079]

Here, the semiconductor film 1005 is preferably made thick in order to improve 15 the quantum efficiency of the photodiode 1002. Further, the semiconductor film 1006 is preferably made thin in order to improve the electrical characteristics such as the S value of the transistor 1003. In that case, the semiconductor film 1005 is only required to be made thicker than the semiconductor film 1006.

[0080]

20 A crystal semiconductor is also preferably used for the transistor 208 in FIG. 2 so as to obtain a transistor with high mobility. By using the same semiconductor material as the transistor 1003, the transistor 208 can be formed in the same process as the transistor 1003, resulting in cost reduction.

[0081]

25 Note that the gate insulating film 1007 is formed as a single layer or stacked layers using a silicon oxide film, a silicon nitride film, or the like. The gate insulating film 1007 may be formed by plasma CVD or sputtering.

[0082]

30 Note that the gate electrode 1008 is formed as a single layer or stacked layers using a metal material such as molybdenum, titanium, chromium, tantalum, tungsten, aluminum, copper, neodymium, or scandium, or an alloy material including any of these materials as a main component. The gate electrode 1008 may be formed by sputtering

or vacuum evaporation.

[0083]

The photodiode 1002 can have a stacked structure of a p-layer, an i-layer, and an n-layer instead of the lateral-junction structure. The transistor 1003 can be a 5 bottom-gate transistor, and can have a channel-stop structure or a channel-etched structure.

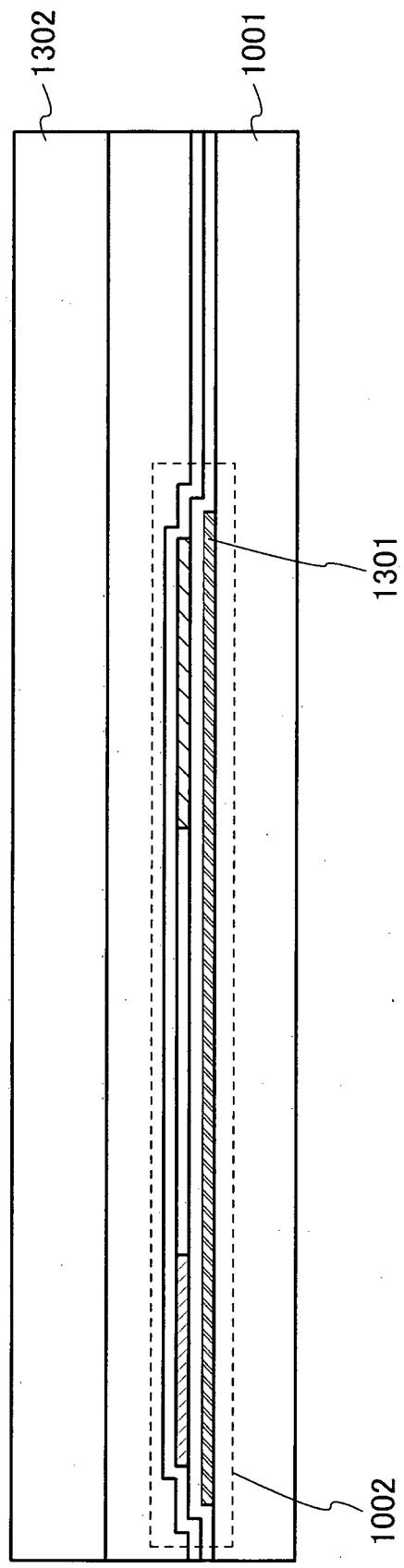

[0084]

Note that as illustrated in FIG. 9, a light-blocking film 1301 may be provided under the photodiode 1002, so that light other than light which should be detected can 10 be blocked. A light-blocking film may be provided over the photodiode 1002. In that case, a light-blocking film can be provided, for example, over a substrate 1302 opposite to the substrate 1001 provided with the photodiode 1002

[0085]

The transistor 1004 is a bottom-gate inverted-staggered thin film transistor and 15 includes a gate electrode 1010, a gate insulating film 1011, a semiconductor film 1012, an electrode 1013, and an electrode 1014. An insulating film 1015 is provided over the transistor 1004. Note that the transistor 1004 may be a top-gate transistor.

[0086]

A feature of the structure is that the transistor 1004 is formed over the 20 photodiode 1002 and the transistor 1003 with an insulating film 1009 interposed therebetween. When the transistor 1004 and the photodiode 1002 are formed on different layers in this manner, the area of the photodiode 1002 can be increased to increase the amount of light received by the photodiode 1002.

[0087]

25 Furthermore, part or the whole of the transistor 1004 is preferably formed to overlap with either the n-layer 1023 or the p-layer 1021 of the photodiode 1002. This is because the area of the photodiode 1002 can be increased and the overlapping area of the transistor 1004 and the i-layer 1022 can be made as small as possible so that light can be received efficiently. Also in the case of a pn diode, a smaller overlapping area 30 of the transistor 1004 and a pn junction enables efficient light reception.

[0088]

The function of the transistor 1004 is to accumulate an output signal of the

photodiode 1002 as a charge in the gate of the transistor 1003 and retain the charge. Therefore, an oxide semiconductor is preferably used for the semiconductor film 1012 so that the transistor has an extremely low off-current.

[0089]

5 It is also preferable that the transistor 207 in FIG. 2 use an oxide semiconductor to have an extremely low off-current. By using the same semiconductor material as the transistor 1004, the transistor 207 can be formed in the same process as the transistor 1004, resulting in cost reduction. Note that for each of the above semiconductor elements, a thin film semiconductor or a bulk semiconductor may be

10 used.

[0090]

An example of forming the semiconductor film 1012 using an oxide semiconductor will be shown below.

[0091]

15 One of the factors that increase the off-current of a transistor is an impurity such as hydrogen (e.g., hydrogen, water, or a hydroxyl group) contained in an oxide semiconductor. Hydrogen or the like might be a carrier supplier (a donor) in an oxide semiconductor, which causes electric current even in the off state. That is, an oxide semiconductor containing a large amount of hydrogen or the like becomes an n-type

20 oxide semiconductor.

[0092]

25 Thus, in the manufacturing method shown below, the amount of hydrogen in an oxide semiconductor is reduced as much as possible and the concentration of oxygen which is a constituent element is increased, whereby the oxide semiconductor is highly purified. The highly-purified oxide semiconductor is an intrinsic or substantially intrinsic semiconductor, resulting in a reduction in off-current.

[0093]

First, an oxide semiconductor film is formed over the insulating film 1009 by sputtering.

30 [0094]

As a target used for forming the oxide semiconductor film, a target of a metal oxide containing zinc oxide as a main component can be used. For example, it is

possible to use a target with a composition ratio of  $\text{In}_2\text{O}_3$ :  $\text{Ga}_2\text{O}_3$ :  $\text{ZnO}$  = 1:1:1, that is,  $\text{In: Ga: Zn} = 1:1:0.5$ . It is also possible to use a target with a composition ratio of  $\text{In: Ga: Zn} = 1:1:1$  or a composition ratio of  $\text{In: Ga: Zn} = 1:1:2$ . Further, a target which includes  $\text{SiO}_2$  at 2 wt% to 10 wt% inclusive can be used.

5 [0095]

Note that the oxide semiconductor film may be formed in a rare gas (typically, argon) atmosphere, an oxygen atmosphere, or a mixed atmosphere of a rare gas and oxygen. Here, a sputtering gas used for forming the oxide semiconductor film is a high-purity gas in which impurities such as hydrogen, water, hydroxyl groups, or 10 hydride are reduced to such a level that the concentration thereof can be expressed by ppm, preferably ppb.

[0096]

The oxide semiconductor film is formed by introducing a sputtering gas from which hydrogen and moisture are removed while removing moisture remaining in a 15 treatment chamber. In order to remove moisture remaining in the treatment chamber, an entrapment vacuum pump is preferably used. For example, a cryopump, an ion pump, or a titanium sublimation pump is preferably used.

[0097]

The thickness of the oxide semiconductor film may be 2 nm to 200 nm 20 inclusive, preferably 5 nm to 30 nm inclusive. Then, the oxide semiconductor film is processed (patterned) into a desired shape by etching or the like, whereby the semiconductor film 1012 is formed.

[0098]

Although an In-Ga-Zn-O is used for the oxide semiconductor film in the above 25 example, the following oxide semiconductors can also be used: In-Sn-Ga-Zn-O, In-Sn-Zn-O, In-Al-Zn-O, Sn-Ga-Zn-O, Al-Ga-Zn-O, Sn-Al-Zn-O, In-Zn-O, Sn-Zn-O, Al-Zn-O, Zn-Mg-O, Sn-Mg-O, In-Mg-O, In-O, Sn-O, Zn-O, and the like. The oxide semiconductor film may contain Si. Further, the oxide semiconductor film may be amorphous or crystalline. Further, the oxide semiconductor film may be 30 non-single-crystal or single crystal.

[0099]

As the oxide semiconductor film, a thin film represented by  $\text{InMO}_3(\text{ZnO})_m$  ( $m > 0$ ) can also be used. Here, M denotes one or more of metal elements selected from Ga, Al, Mn, and Co. For example, M can be Ga, Ga and Al, Ga and Mn, or Ga and Co.

5 [0100]

Next, first heat treatment is performed on the oxide semiconductor film (the semiconductor film 1012). The temperature of the first heat treatment is higher than or equal to 400 °C and lower than or equal to 750 °C, preferably higher than or equal to 400 °C and lower than the strain point of the substrate.

10 [0101]

Through the first heat treatment, hydrogen, water, hydroxyl groups, and the like can be removed from the oxide semiconductor film (the semiconductor film 1012) (dehydrogenation treatment). The dehydrogenation treatment through the first heat treatment is significantly effective because such impurities become donors in the oxide semiconductor film and increase the off-current of the transistor.

15 [0102]

Note that the first heat treatment can be performed with an electric furnace. Alternatively, heat conduction or heat radiation from a heating element such as a resistance heating element may be used for the first heat treatment. In that case, a 20 rapid thermal anneal (RTA) apparatus such as a gas rapid thermal anneal (GRTA) apparatus or a lamp rapid thermal anneal (LRTA) apparatus can be used.

[0103]

An LRTA apparatus is an apparatus for heating an object to be processed by radiation of light (an electromagnetic wave) emitted from a lamp such as a halogen lamp, a metal halide lamp, a xenon arc lamp, a carbon arc lamp, a high-pressure sodium lamp, or a high-pressure mercury lamp.

[0104]

A GRTA apparatus is an apparatus for heat treatment using a high-temperature gas. As the gas, an inert gas (typically, a rare gas such as argon) or a nitrogen gas can 30 be used. The use of the GRTA apparatus is particularly effective because high-temperature heat treatment in a short time is enabled.

[0105]

The first heat treatment may be performed before the patterning of the oxide semiconductor film, after the formation of the electrode 1013 and the electrode 1014, or after the formation of the insulating film 1015. However, the first heat treatment is 5 preferably performed before the formation of the electrode 1013 and the electrode 1014 so that the electrodes are not damaged by the first heat treatment.

[0106]

During the first heat treatment, oxygen deficiencies might be generated in the oxide semiconductor. Therefore, after the first heat treatment, oxygen is preferably 10 introduced to the oxide semiconductor (treatment for supplying oxygen) so that the concentration of oxygen which is a constituent element is increased, whereby the oxide semiconductor is highly purified.

[0107]

Specifically, as the treatment for supplying oxygen, the first heat treatment is 15 followed by second heat treatment in an oxygen atmosphere or an atmosphere containing nitrogen and/or oxygen (for example, the volume ratio of nitrogen to oxygen is 4 to 1), for example. Alternatively, plasma treatment may be performed in an oxygen atmosphere, so that the oxygen concentration in the oxide semiconductor film can be increased and the oxide semiconductor film can be highly purified. The 20 temperature of the second heat treatment is higher than or equal to 200 °C and lower than or equal to 400 °C, preferably higher than or equal to 250 °C and lower than or equal to 350 °C.

[0108]

As another example of the treatment for supplying oxygen, an oxide insulating 25 film (the insulating film 1015) is formed on and in contact with the semiconductor film 1012, and then third heat treatment is performed. Oxygen in the insulating film 1015 moves to the semiconductor film 1012 to increase the oxygen concentration in the oxide semiconductor, whereby the oxide semiconductor film can be highly purified. The temperature of the third heat treatment is higher than or equal to 200 °C and lower than 30 or equal to 400 °C, preferably higher than or equal to 250 °C and lower than or equal to 350 °C. Note that also in the case of a top-gate transistor, the oxide semiconductor can

be highly purified in such a manner that a gate insulating film on and in contact with the semiconductor film 1012 is formed of a silicon oxide film or the like and similar heat treatment is performed.

[0109]

5 As described above, the oxide semiconductor film can be highly purified through the treatment for supplying oxygen such as the second heat treatment or the third heat treatment after the dehydrogenation treatment by the first heat treatment. When being highly purified, the oxide semiconductor can be made intrinsic or substantially intrinsic, resulting in a reduction in the off-current of the transistor 1004.

10 [0110]

Note that the insulating film 1009 is a single layer or stacked layers using a silicon oxide film, a silicon nitride film, or the like, and is formed over the photodiode 1002 and the transistor 1003. The insulating film 1009 may be formed by plasma CVD or sputtering. The insulating film 1009 may also be formed of a resin film such 15 as a polyimide film by coating or the like.

[0111]

20 The gate electrode 1010, which is formed over the insulating film 1009, is formed as a single layer or stacked layers using a metal material such as molybdenum, titanium, chromium, tantalum, tungsten, aluminum, copper, neodymium, or scandium, or an alloy material including any of these materials as a main component. The gate electrode 1010 may be formed by sputtering or vacuum evaporation.

[0112]

25 The gate insulating film 1011 is formed as a single layer or stacked layers using a silicon oxide film, a silicon nitride film, or the like. The gate insulating film 1011 may be formed by plasma CVD or sputtering.

[0113]

30 The electrode 1013 and the electrode 1014, which are formed over the gate insulating film 1011 and the semiconductor film 1012, each are a single layer or stacked layers using a metal such as molybdenum, titanium, chromium, tantalum, tungsten, aluminum, copper, or yttrium, an alloy material including any of these materials as a main component, or a metal oxide having conductivity such as indium oxide. The electrode 1013 and the electrode 1014 may be formed by sputtering or vacuum

evaporation. Here, it is preferable that the electrode 1013 be connected to the n-layer 1023 of the photodiode 1002 through a contact hole formed in the gate insulating film 1007, the insulating film 1009, and the gate insulating film 1011.

[0114]

5 The highly-purified oxide semiconductor and a transistor using the same will be described in detail below.

[0115]

As an example of the highly-purified oxide semiconductor, there is an oxide semiconductor whose carrier concentration is lower than  $1 \times 10^{14} / \text{cm}^3$ , preferably lower 10 than  $1 \times 10^{12} / \text{cm}^3$ , and more preferably lower than  $1 \times 10^{11} / \text{cm}^3$  or lower than  $6.0 \times 10^{10} / \text{cm}^3$ .

[0116]

15 A transistor using a highly-purified oxide semiconductor is characterized in that the off-current is much lower than that of a transistor including a semiconductor containing silicon, for example.

[0117]

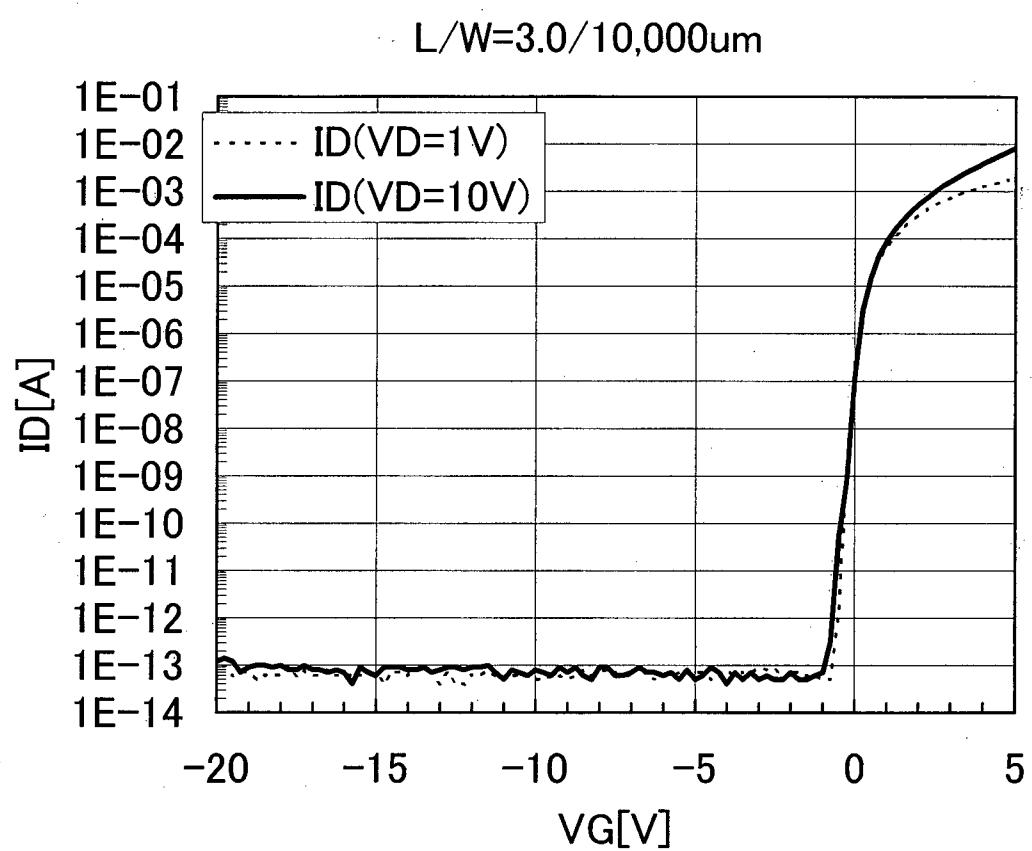

The following shows the result of measuring the off-current characteristics of a transistor with an evaluation element (also referred to as TEG: Test Element Group). Note that the description is made here on an n-channel transistor.

20 [0118]

In the TEG, a transistor with  $L/W = 3 \mu\text{m}/10000 \mu\text{m}$ , which includes 200 transistors with  $L/W = 3 \mu\text{m}/50 \mu\text{m}$  (thickness  $d$ : 30 nm) connected in parallel, is provided. FIG. 8 illustrates the initial characteristics of the transistor. Here, VG is in the range of -20 V to +5 V inclusive. In order to measure the initial characteristics of 25 the transistor, the characteristics of changes in the source-drain current (hereinafter, referred to as a drain current or ID), i.e., VG-ID characteristics, were measured under the conditions where the substrate temperature was set to room temperature, the voltage between the source and the drain (hereinafter, referred to as a drain voltage or VD) was set to 1 V or 10 V, and the voltage between the source and the gate (hereinafter, referred 30 to as a gate voltage or VG) was changed from -20 V to +20 V.

[0119]

As illustrated in FIG. 8, the transistor with a channel width  $W$  of 10000  $\mu\text{m}$  has an off-current of  $1 \times 10^{-13}$  A or less at  $VD$  of 1 V and 10 V, which is less than or equal to the resolution (100 fA) of a measurement device (a semiconductor parameter analyzer, Agilent 4156C manufactured by Agilent Technologies Inc.). The off-current per 5 micrometer of the channel width corresponds to 10 aA/ $\mu\text{m}$ .

[0120]

Note that in this specification, the off-current (also referred to as leakage current) means a current flowing between a source and a drain of an n-channel transistor when a predetermined gate voltage in the range of -20 V to -5 V inclusive is applied at 10 room temperature in the case where the n-channel transistor has a positive threshold voltage  $V_{th}$ . Note that the room temperature is 15 °C to 25 °C inclusive. A transistor including the oxide semiconductor that is disclosed in this specification has a current per unit channel width ( $W$ ) of 100 aA/ $\mu\text{m}$  or less, preferably 1 aA/ $\mu\text{m}$  or less, and more preferably 10 zA/ $\mu\text{m}$  or less at room temperature.

15 [0121]

Moreover, the transistor including a high-purity oxide semiconductor has favorable temperature characteristics. Typically, in the temperature range of -25 °C to 150 °C inclusive, the current-voltage characteristics of the transistor, such as an on-current, an off-current, field-effect mobility, an S value, and a threshold voltage, 20 hardly change and deteriorate due to temperature.

[0122]

This embodiment can be combined with any of the other embodiments as appropriate.

25 This application is based on Japanese Patent Application serial no. 2010-050776 filed with Japan Patent Office on March 8, 2010, the entire contents of which are hereby incorporated by reference.

## CLAIMS

1. A semiconductor device comprising:

5 a photodiode;

a first transistor;

a second transistor;

a third transistor; and

a fourth transistor,

wherein a first terminal of the photodiode is electrically connected to a first

10 terminal of the second transistor,

wherein a second terminal of the second transistor is electrically connected to a gate of the first transistor and a first terminal of the third transistor,

wherein a first terminal of the first transistor is electrically connected to a first terminal of the fourth transistor,

15 wherein in a first period, a charge corresponding to an amount of incident light to the photodiode is accumulated to the gate of the first transistor,

wherein in a second period, the charge is retained in the gate of the first transistor while a first voltage is supplied to a gate of the second transistor and a second voltage is supplied to a gate of the third transistor, and

20 wherein a voltage level of the first voltage is lower than a voltage level of the first terminal of the second transistor and a voltage level of the second terminal of the second transistor, and a voltage level of the second voltage is lower than a voltage level of the first terminal of the third transistor and a voltage level of a second terminal of the third transistor.

25

2. The semiconductor device according to claim 1,

wherein a semiconductor layer of the second transistor comprises an oxide semiconductor.

30

3. The semiconductor device according to claim 1,

wherein a semiconductor layer of the third transistor comprises an oxide semiconductor.

4. The semiconductor device according to claim 1,

wherein a semiconductor layer of the second transistor and a semiconductor layer of the third transistor comprise an oxide semiconductor.

5

5. The semiconductor device according to claim 1,

wherein the voltage level of the first voltage is lower than a voltage level of a second terminal of the photodiode.

10

6. The semiconductor device according to claim 1,

wherein the charge is discharged from the gate of the first transistor while a third voltage is supplied to the gate of the third transistor and a fourth voltage is supplied to the second terminal of the third transistor.

15

7. The semiconductor device according to claim 1,

wherein the charge is discharged from the gate of the first transistor while a fifth voltage is supplied to a second terminal of the photodiode and a sixth voltage is supplied to the gate of the second transistor.

20

8. A semiconductor device comprising:

a photodiode;

a first transistor;

a second transistor; and

a third transistor,

25

wherein a first terminal of the photodiode is electrically connected to a first terminal of the second transistor,

wherein a second terminal of the second transistor is electrically connected to a gate of the first transistor and a first terminal of the third transistor,

30

wherein in a first period, a charge corresponding to an amount of incident light to the photodiode is accumulated to the gate of the first transistor,

wherein in a second period, the charge is retained in the gate of the first transistor while a first voltage is supplied to a gate of the second transistor and a second

voltage is supplied to a gate of the third transistor, and

wherein a voltage level of the first voltage is lower than a voltage level of the first terminal of the second transistor and a voltage level of the second terminal of the second transistor, and a voltage level of the second voltage is lower than a voltage level 5 of the first terminal of the third transistor and a voltage level of a second terminal of the third transistor.

9. The semiconductor device according to claim 8,

wherein a semiconductor layer of the second transistor comprises an oxide 10 semiconductor.

10. The semiconductor device according to claim 8,

wherein a semiconductor layer of the third transistor comprises an oxide semiconductor.

15

11. The semiconductor device according to claim 8,

wherein a semiconductor layer of the second transistor and a semiconductor layer of the third transistor comprise an oxide semiconductor.

20

12. The semiconductor device according to claim 8,

wherein the voltage level of the first voltage is lower than a voltage level of a second terminal of the photodiode.

25 13. The semiconductor device according to claim 8,

wherein the charge is discharged from the gate of the first transistor while a third voltage is supplied to the gate of the third transistor and a fourth voltage is supplied to the second terminal of the third transistor.

30 14. The semiconductor device according to claim 8,

wherein the charge is discharged from the gate of the first transistor while a fifth voltage is supplied to a second terminal of the photodiode and a sixth voltage is supplied to the gate of the second transistor.

15. A semiconductor device comprising:

a photodiode;

a first transistor; and

5 a second transistor;

wherein a first terminal of the photodiode is electrically connected to a first terminal of the second transistor,

wherein a second terminal of the second transistor is electrically connected to a gate of the first transistor,

10 wherein in a first period, a charge corresponding to an amount of incident light to the photodiode is accumulated to the gate of the first transistor,

wherein in a second period, the charge is retained in the gate of the first transistor while a first voltage is supplied to a gate of the second transistor, and

15 wherein a voltage level of the first voltage is lower than a voltage level of the first terminal of the second transistor and a voltage level of the second terminal of the second transistor.

16. The semiconductor device according to claim 15,

wherein a semiconductor layer of the second transistor comprises an oxide 20 semiconductor.

17. The semiconductor device according to claim 15,

wherein the voltage level of the first voltage is lower than a voltage level of a second terminal of the photodiode.

25

18. The semiconductor device according to claim 15,

wherein the charge is discharged from the gate of the first transistor while a fifth voltage is supplied to a second terminal of the photodiode and a sixth voltage is supplied to the gate of the second transistor.

30

19. A driving method of a semiconductor device comprising:

accumulating a charge to a gate of a first transistor by supplying a first voltage

to a first terminal of a photodiode, a second voltage to a gate of a second transistor, and a third voltage to a gate of a third transistor,

retaining the charge in the gate of the first transistor by supplying a fourth voltage to the gate of the second transistor and a fifth voltage to the gate of the third transistor, and

discharging the charge from the gate of the first transistor by supplying a sixth voltage to the gate of the third transistor and a seventh voltage to a first terminal of the third transistor,

wherein the charge corresponds to an amount of incident light to the photodiode, and

wherein a voltage level of the fourth voltage is lower than a voltage level of a first terminal of the second transistor and a voltage level of a second terminal of the second transistor, and a voltage level of the fifth voltage is lower than a voltage level of the first terminal of the third transistor and a voltage level of a second terminal of the third transistor in retaining.

20. The driving method according to claim 19,

wherein a voltage level of the third voltage equals to the voltage level of the fifth voltage.

20

21. A driving method of a semiconductor device comprising:

accumulating a charge to a gate of a first transistor by supplying a first voltage to a first terminal of a photodiode, and a second voltage to a gate of a second transistor,

retaining the charge in the gate of the first transistor by supplying a third voltage to the gate of the second transistor, and

discharging the charge from the gate of the first transistor by supplying a fourth voltage to the gate of the second transistor and a fifth voltage to the first terminal of the photodiode,

wherein the charge corresponds to an amount of incident light to the photodiode, and

wherein a voltage level of the third voltage is lower than a voltage level of a first terminal of the second transistor and a voltage level of a second terminal of the

second transistor in retaining.

22. The driving method according to claim 21,

wherein a voltage level of the second voltage equals to a voltage level of the

5 fourth voltage.

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6A

FIG. 6B

FIG. 6C

FIG. 7

FIG. 8

FIG. 9

FIG. 10

## EXPLANATION OF REFERENCE