(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5063180号

(P5063180)

(45) 発行日 平成24年10月31日(2012.10.31)

(24) 登録日 平成24年8月17日(2012.8.17)

(51) Int.Cl.

F 1

G02F 1/1368 (2006.01)

G02F 1/1368

G02F 1/1343 (2006.01)

G02F 1/1343

G02F 1/1335 (2006.01)

G02F 1/1335 500

G02F 1/1335 520

請求項の数 4 (全 23 頁)

(21) 出願番号

特願2007-126799 (P2007-126799)

(22) 出願日

平成19年5月11日 (2007.5.11)

(65) 公開番号

特開2007-304599 (P2007-304599A)

(43) 公開日

平成19年11月22日 (2007.11.22)

審査請求日

平成22年5月11日 (2010.5.11)

(31) 優先権主張番号

10-2006-0042595

(32) 優先日

平成18年5月11日 (2006.5.11)

(33) 優先権主張国

韓国 (KR)

(73) 特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路 129

129, Samsung-ro, Yeon

gton-gu, Suwon-si, G

yeonggi-do, Republic

of Korea

(74) 代理人 100121382

弁理士 山下 託嗣

(74) 代理人 100094145

弁理士 小野 由己男

(74) 代理人 100106367

弁理士 稲積 朋子

最終頁に続く

(54) 【発明の名称】薄膜トランジスタ基板、それを含む液晶表示パネル、及びその液晶表示パネルの製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

下部基板上に形成されたゲートライン、前記ゲートラインと電気的に絶縁状態で交差するデータライン、前記ゲートライン及びデータラインに接続された薄膜トランジスタ、前記薄膜トランジスタと接続された画素電極、前記薄膜トランジスタに接続され前記ゲートラインを遮蔽するように形成された反射電極、前記薄膜トランジスタのドレイン電極と電気的に絶縁状態で重なって第1ストレージキャパシタを形成するストレージ電極、前記ストレージ電極に接続され前記ゲートラインの一側端に隣接した第1ストレージライン、前記画素電極と電気的に絶縁状態で重なって第2ストレージキャパシタを形成し前記ゲートラインの他側端に隣接した第2ストレージライン、前記データラインより広い幅で前記データラインと重なるシールドパターンを含む薄膜トランジスタ基板と、

前記下部基板と対向する上部基板上に形成されたカラーフィルタ及び前記反射電極と電界を形成する共通電極を含み、前記薄膜トランジスタ基板と液晶を挟んで対向するカラーフィルタ基板と、

を含み、

前記シールドパターンは前記第2ストレージラインと電気的に接続され、

前記カラーフィルタ基板は、

前記カラーフィルタ上に一側端及び他側端が前記反射電極と重なるオーバーコート層を

さらに含むことを特徴とする液晶表示パネル。

## 【請求項 2】

前記第2ストレージラインは前記データライン方向に隣接した2つの画素電極と全て重なることを特徴とする請求項1に記載の液晶表示パネル。

【請求項3】

前記反射電極は前記ゲートラインと隣接した前記第2ストレージライン側部と重なることを特徴とする請求項1に記載の液晶表示パネル。

【請求項4】

前記シールドパターンは前記ゲートラインと同一の平面上に同一の金属からなることを特徴とする請求項1に記載の液晶表示パネル。

【発明の詳細な説明】

【技術分野】

10

【0001】

本発明は薄膜トランジスタ基板、それを含む液晶表示パネル、及びその液晶表示パネルの製造方法に係り、さらに詳しくはフリッカを防止すると共に反射率を向上させることができる薄膜トランジスタ基板、それを含む液晶表示パネル、及びその液晶表示パネルの製造方法に関する。

【背景技術】

【0002】

液晶表示装置は液晶の電気的及び光学的特性を用いて映像を表示する。そのため、液晶表示装置は画素マトリックスを通じて画像を表示する液晶表示パネル(以下、液晶パネル)と、液晶パネルを駆動する駆動回路と、液晶パネルに光を供給するバックライトユニットを備える。このような液晶表示装置は移動通信端末機、携帯用コンピュータ、モニター、液晶テレビなどのように小型表示装置から大型表示装置に至るまで幅広く使用される。

20

【0003】

液晶表示装置は、内蔵された光源からの内部光を用いる透過型と、外部光を用いる反射型と、内部光及び外部光の両方を用いる半透過型とに大別される。これらのうち半透過型液晶表示装置は外部光が十分ならば反射モードで、不十分ならばバックライトユニットを用いた透過モードで画像を表示することにより消費電力を節減できる反射型の長所と外部光の制約を受けない透過型の長所を両方有する。

【0004】

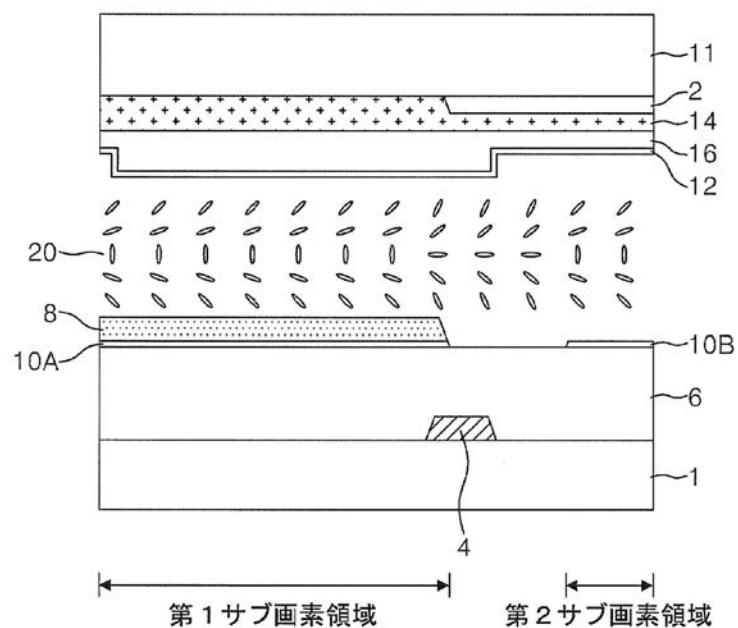

このような半透過型液晶表示装置は、図1に示したように、光学補償ペンド(Optically compensated bend:OCB)モードの液晶分子20を挟んで下部基板1と上部基板11が対向するように形成される。

30

下部基板1上には絶縁膜6により覆われたゲートライン4を挟んで第1サブ画素領域の反射電極8及び画素電極10Aが第2サブ画素領域の画素電極10Bと対向するように形成される。

【0005】

上部基板11上に各サブ画素領域を区分するブラックマトリックス2と、各サブ画素領域毎に形成されるカラーフィルタ2と、反射領域と透過領域とで異なる厚さを有するオーバーコート層14と、画素電極10及び反射電極8と垂直電界を形成する共通電極12が形成される。

40

このように上部基板11上に形成された共通電極12(または、反射電極8)とゲートライン4との間に形成される電界によって、液晶分子の配列が反射電極8(または、ゲートライン4)の縁部で反転される。これにより、反射電極8の縁部と残り領域の液晶分子12の配列が異なることとなり、反射電極8の縁部から光が漏れ出てフリッカのように見える問題点がある。特に、光漏れ現象はゲートライン4を挟んで隣り合う画素電極10A、10Bに相異なる極性のデータ電圧を供給するラインインバージョン方式の場合に目立つ傾向にある。

【0006】

このような光漏れ現象を防止するため、反射電極8の縁部を遮るようにブラックマトリックス2の面積を第1サブ画素領域と一部重なるように広めると、反射電極8の面積が縮

50

小さることとなり、反射率が低下するという問題点がある。

【発明の開示】

【発明が解決しようとする課題】

【0007】

本発明は前述した問題点を解決するために案出されたもので、その目的はフリッカを防止すると共に反射率を向上させることができる薄膜トランジスタ基板、それを含む液晶表示パネル、及びその液晶表示パネルの製造方法を提供するところにある。

【課題を解決するための手段】

【0008】

前記技術的課題を達成するため、本発明の実施例による液晶表示パネルは下部基板上に形成されたゲートライン、前記ゲートラインと電気的に絶縁状態で交差するデータライン、前記ゲートライン及びデータラインに接続された薄膜トランジスタ、前記薄膜トランジスタに接続され前記ゲートラインを遮蔽するように形成された反射電極を含む薄膜トランジスタ基板と、前記下部基板と対向する上部基板上に形成されたカラーフィルタ及び前記反射電極と電界を形成する共通電極を含み、前記薄膜トランジスタ基板と液晶を挟んで対向するカラーフィルタ基板を含むことを特徴とする。

【0009】

ここで、前記液晶表示パネルは前記薄膜トランジスタに接続された画素電極をさらに含むように構成できる。

そして、前記カラーフィルタ基板は前記カラーフィルタ上に一側端及び他側端が前記反射電極と重なるオーバーコート層をさらに含むように構成できる。

また、前記薄膜トランジスタ基板は前記薄膜トランジスタのドレイン電極と電気的に絶縁状態で重なって第1ストレージキャパシタを形成するストレージ電極と、前記ストレージ電極に接続され前記ゲートラインの一側端に隣接した第1ストレージラインと、前記画素電極と電気的に絶縁状態で重なって第2ストレージキャパシタを形成し前記ゲートラインの他側端に隣接した第2ストレージラインをさらに含むように構成できる。

【0010】

一方、前記第2ストレージラインはデータライン方向に隣接した2つの画素電極と全て重なるように構成できる。

そして、前記薄膜トランジスタ基板は前記データラインより広い幅で前記データラインと重なるシールドパターンをさらに含むように構成できる。

一方、前記薄膜トランジスタ基板は前記薄膜トランジスタのドレイン電極と電気的に絶縁状態で重なって第1ストレージキャパシタを形成するストレージ電極と、前記ストレージ電極に接続され前記ゲートラインの一側端に隣接した第1ストレージラインと、前記画素電極と電気的に絶縁状態で重なって第2ストレージキャパシタを形成し前記ゲートラインの他側端に隣接した第2ストレージラインをさらに含み、前記シールドパターンは前記第2ストレージラインに電気的に接続されるように構成できる。

【0011】

前記技術的課題を達成するため、本発明に係る薄膜トランジスタ基板は基板上に形成されたゲートラインと、前記ゲートラインと電気的に絶縁状態で交差するデータラインと、前記ゲートライン及びデータラインに接続された薄膜トランジスタと、前記薄膜トランジスタに接続され前記ゲートラインを覆うように形成された反射電極とを備えることを特徴とする。

【0012】

この際、前記第2ストレージラインは極性が異なるデータ信号が供給される画素電極の間に位置するように構成できる。

前記技術的課題を達成するため、本発明に係る液晶表示パネルの製造方法は下部基板上に形成されたゲートライン、前記ゲートラインと電気的に絶縁状態で交差するデータライン、前記ゲートライン及びデータラインに接続された薄膜トランジスタ、前記薄膜トランジスタに接続され前記ゲートラインを遮蔽するように形成された反射電極を含む薄膜

10

20

30

40

50

トランジスタ基板を設ける段階と、前記下部基板と対向する上部基板上に形成されたカラーフィルタ、前記反射電極と電界を形成する共通電極を含むカラーフィルタ基板を設ける段階と、液晶を挟むように前記薄膜トランジスタ基板とカラーフィルタ基板を結合する段階とを含むことを特徴とする。

【0013】

ここで、前記薄膜トランジスタ基板を設ける段階は、前記基板上にゲートライン及びデータラインと、そのゲートライン及びデータラインと接続された薄膜トランジスタを形成する段階と、前記薄膜トランジスタを覆うように保護膜を形成する段階と、前記保護膜上に前記薄膜トランジスタと接続された画素電極を形成する段階と、前記ゲートラインと重なる反射電極を形成する段階とを含むように構成できる。

10

【0014】

また、前記薄膜トランジスタ基板を設ける段階は、前記薄膜トランジスタのドレイン電極と電気的に絶縁状態で重なって第1ストレージキャパシタを形成するストレージ電極、前記ストレージ電極に接続され前記ゲートラインの一側端に隣接した第1ストレージライン、前記画素電極と電気的に絶縁状態で重なって第2ストレージキャパシタを形成し、前記ゲートラインの他側端に隣接した第2ストレージラインを前記ゲートラインと同一平面上に同一金属で形成する段階をさらに含むように構成できる。

【0015】

そして、前記薄膜トランジスタ基板を設ける段階は、前記データラインより広い幅で前記データラインと重なるシールドパターンを前記ゲートラインと同一平面上に同一金属で形成する段階をさらに含むように構成できる。

20

具体的に、前記シールドパターンを形成する段階は前記第2ストレージラインと電気的に接続されるように形成する段階であることが好ましい。

【0016】

一方、前記カラーフィルタ基板を設ける段階は、前記上部基板上にカラーフィルタを形成する段階と、前記カラーフィルタ上に一側端及び他側端が前記反射電極と重なるオーバーコート層を形成する段階と、前記オーバーコート層が形成された上部基板上に前記共通電極を形成する段階とを含むように構成できる。

前記技術的課題を解決すること以外に、本発明の他の特徴及び利点は添付した図面を参考して実施例に対する詳細な説明を通じて明らかになる。

30

【発明の効果】

【0017】

以上述べたように、本発明に係る薄膜トランジスタ基板、それを含む液晶表示パネル、及びその液晶表示パネルの製造方法は、ゲートラインが反射電極により覆われるように形成される。これにより、本発明に係る薄膜トランジスタ基板、それを含む液晶表示パネル、その製造方法及びその液晶表示パネルの製造方法は、ゲート信号により反射電極の縁部から発生する液晶配列のバラツキ現象を防止することができる。液晶配列のバラツキ現象を防止できることによって、フリッカ発生を防ぐことができ、反射率も向上する。

【0018】

また、本発明に係る薄膜トランジスタ基板、それを含む液晶表示パネル、その製造方法及びその液晶表示パネルの製造方法は、反射電極、ストレージライン及びシールドパターンを用いて光漏れ現象を防止することにより、別のブラックマトリックスを必要としない。これにより、本発明に係る薄膜トランジスタ基板、それを含む液晶表示パネル、その製造方法及びその液晶表示パネルの製造方法はブラックマトリックスを形成するためのマスク工程が不要なので、工程を単純化することができると共に、コストダウン及び収率を向上させ、また開口率も向上する。

40

【発明を実施するための最良の形態】

【0019】

以下、本発明の望ましい実施例を添付した図2～図10bを参考して詳述する。

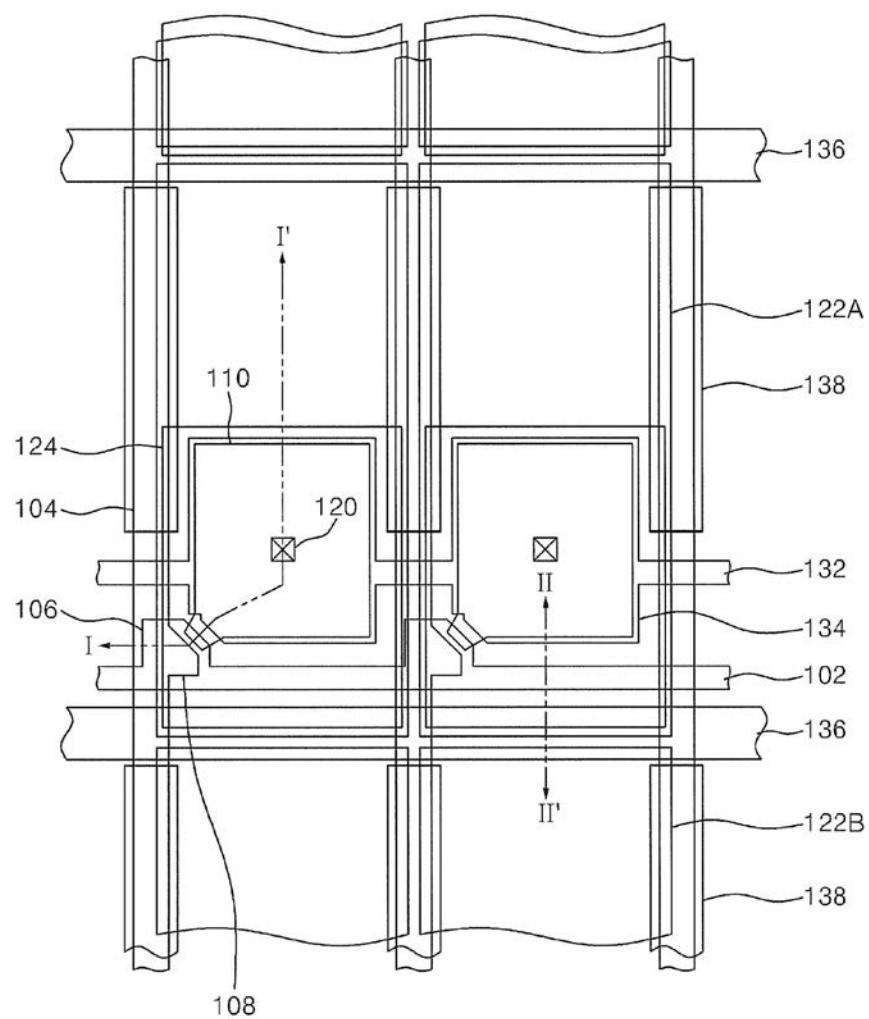

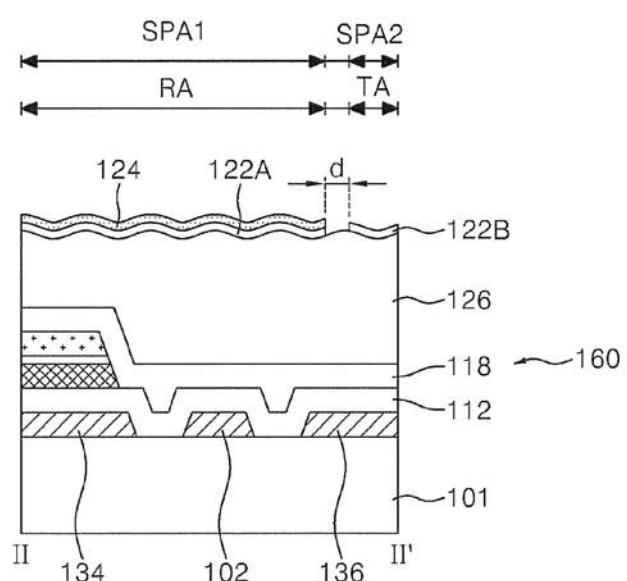

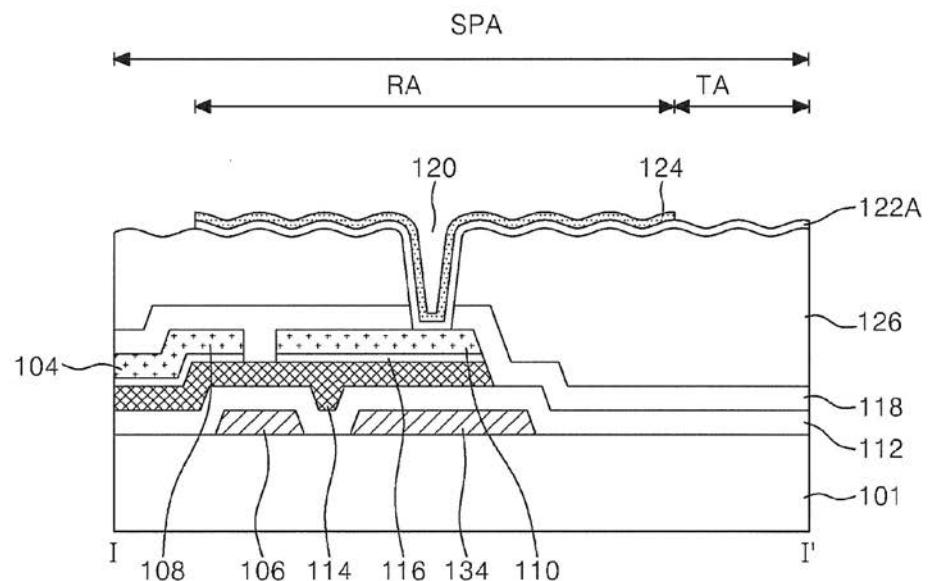

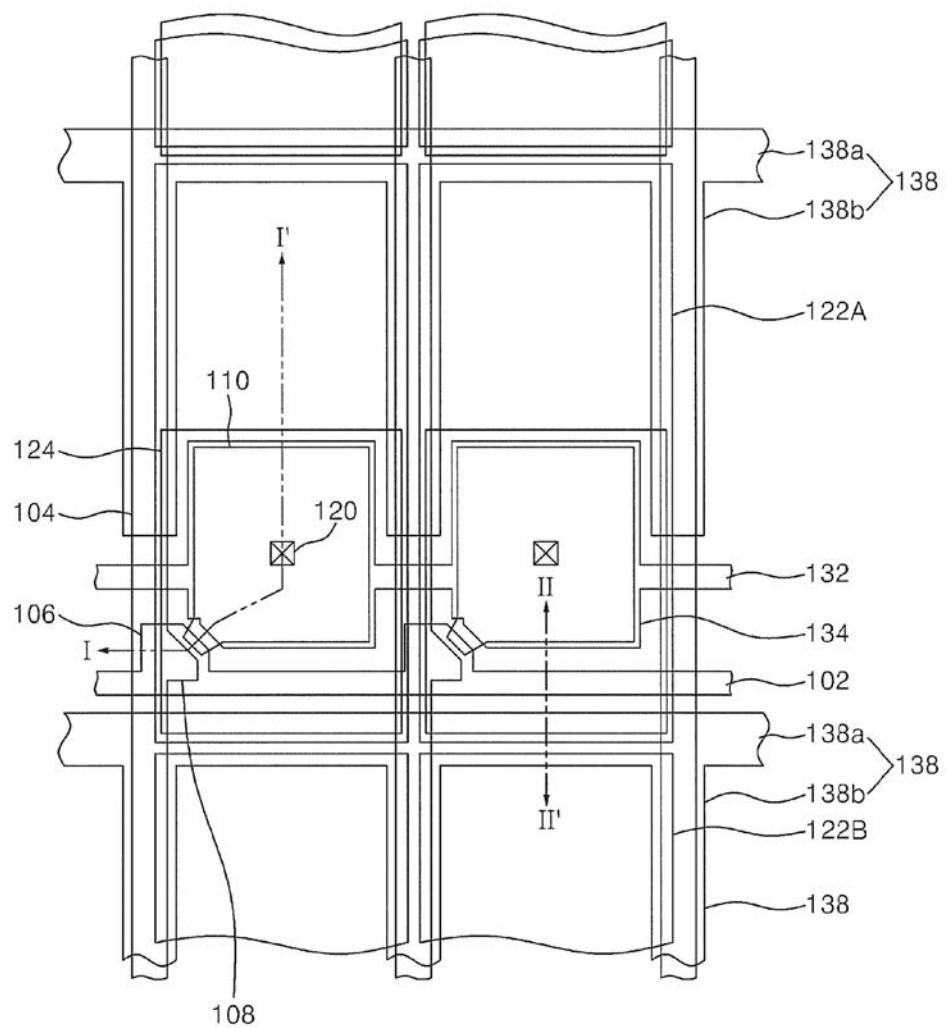

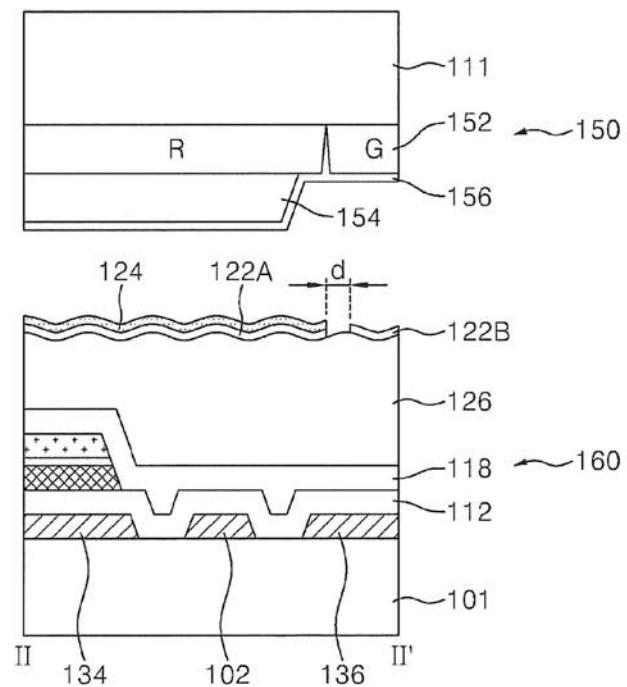

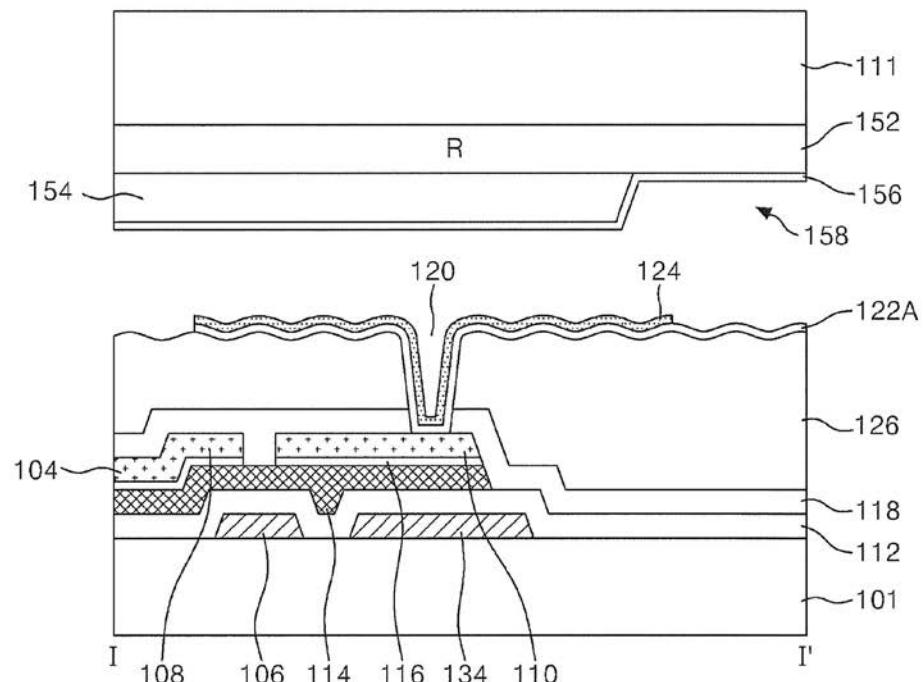

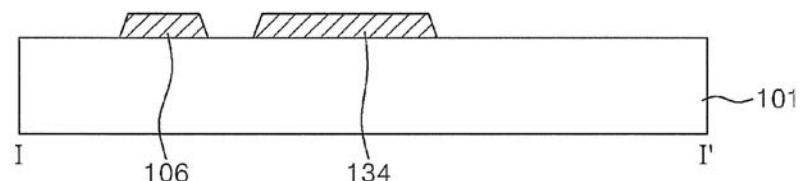

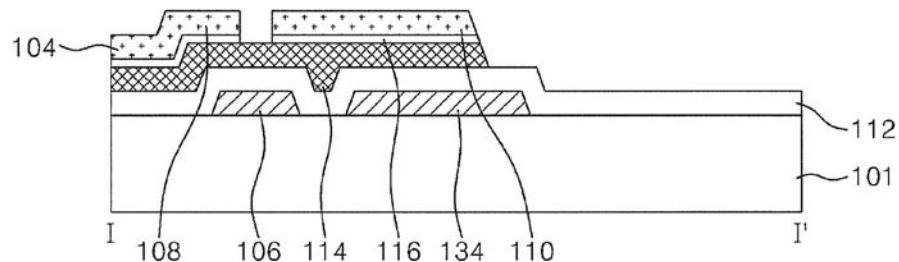

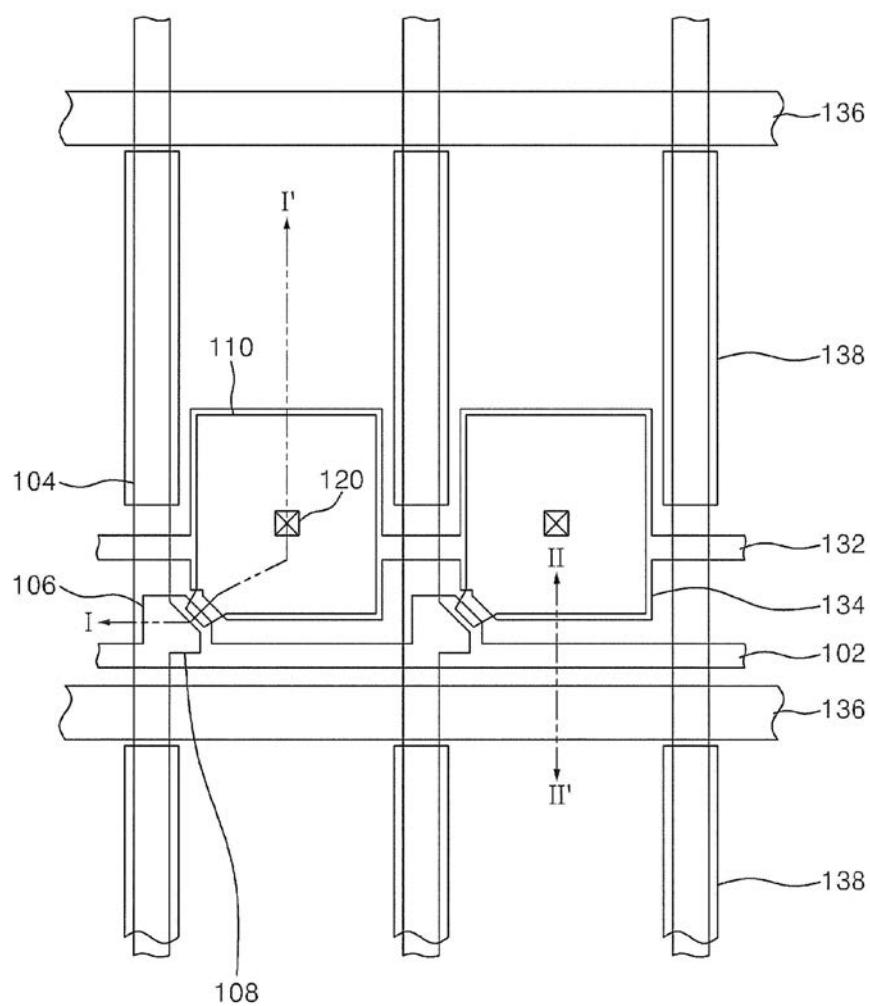

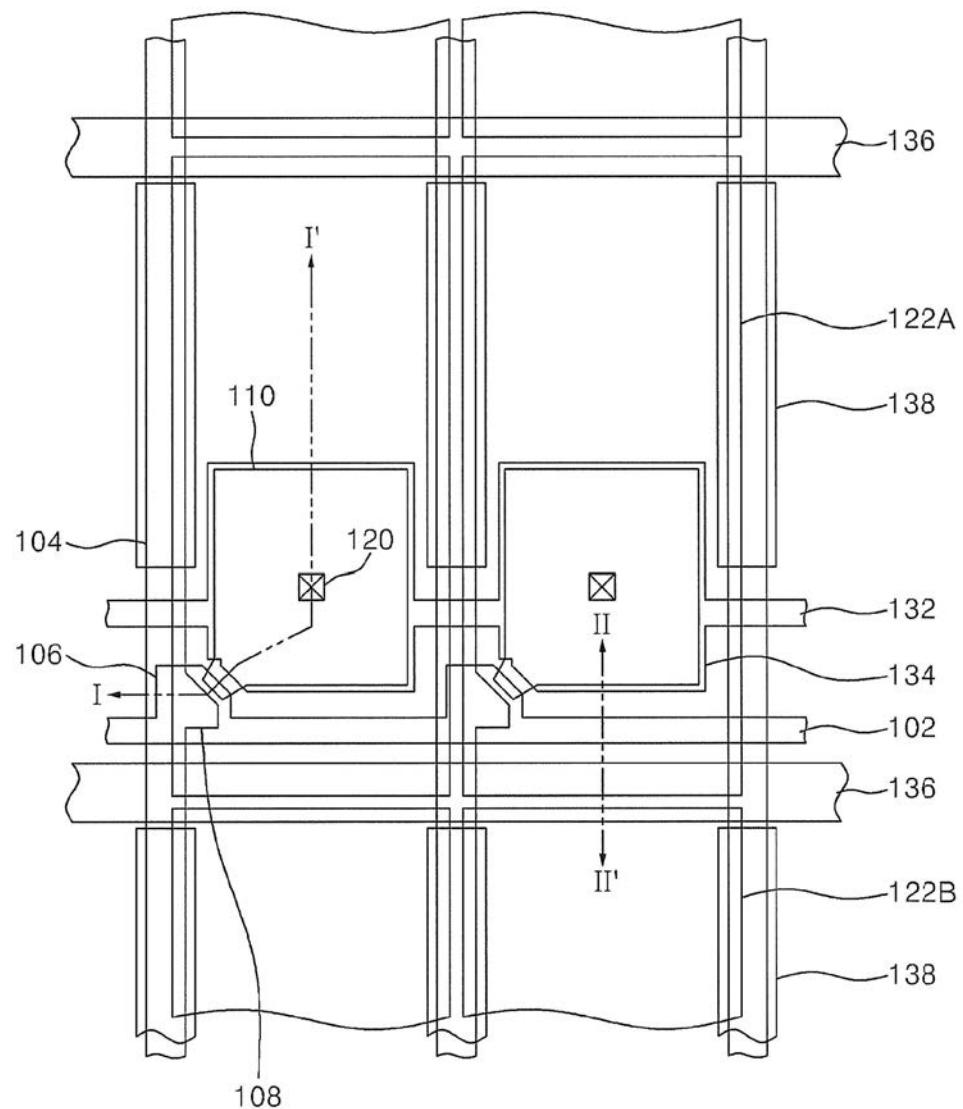

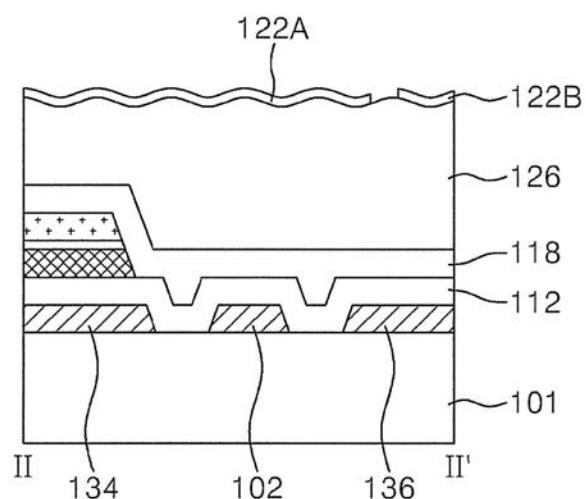

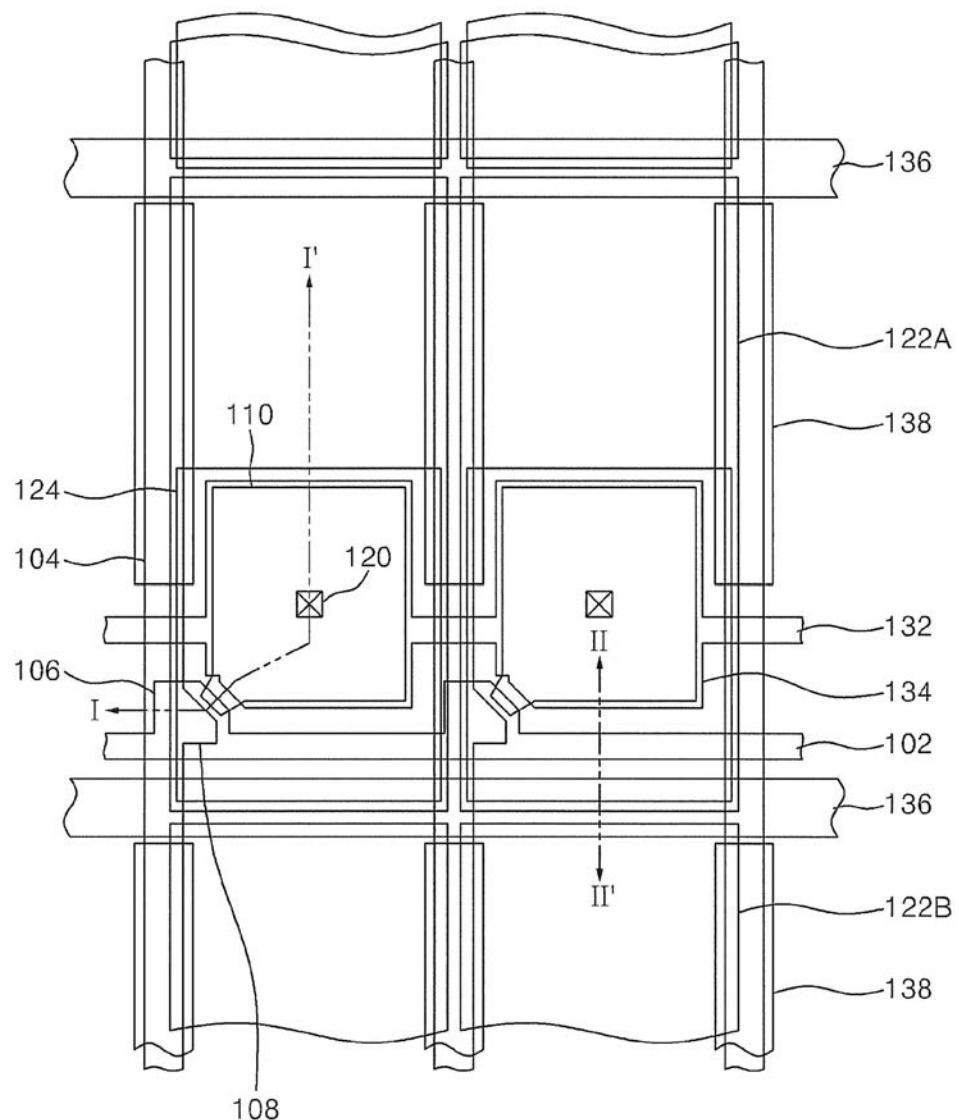

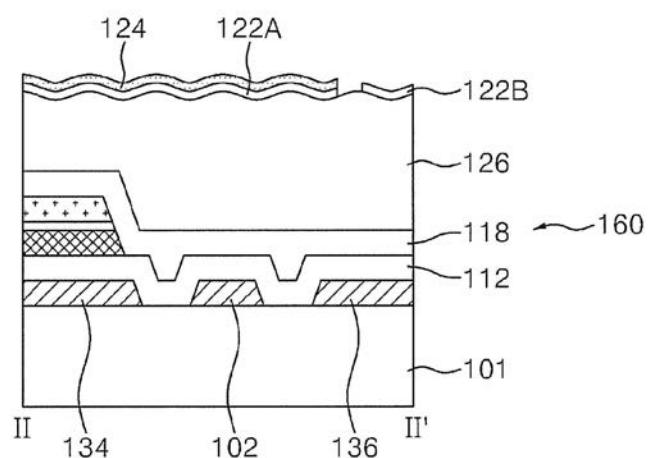

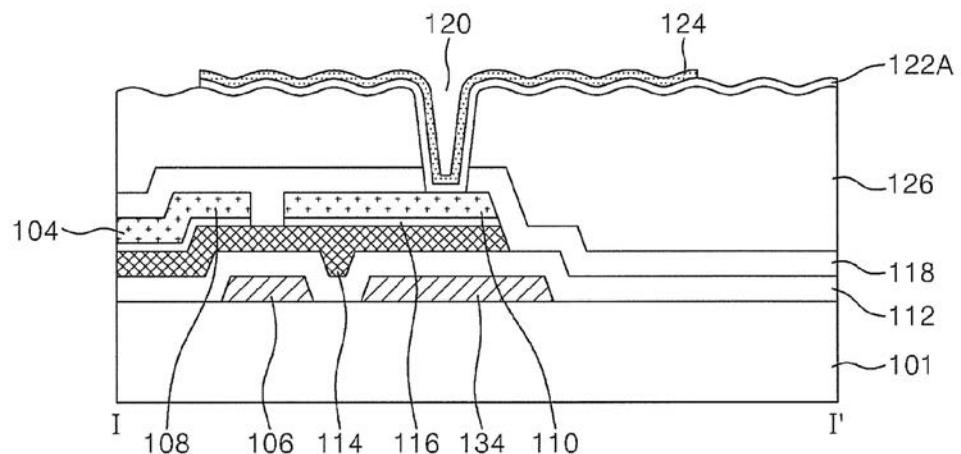

図2及び図3は本発明に係る半透過型液晶表示装置の薄膜トランジスタ基板を示す平面

50

図及び断面図である。

図2及び図3に示す薄膜トランジスタ基板160は、互いに交差するように形成されたゲートライン102及びデータライン104と、ゲートライン102及びデータライン104と接続された薄膜トランジスタ(TFT)と、薄膜トランジスタ(TFT)と接続され各サブ画素領域(SPA)に形成された画素電極122と、薄膜トランジスタ(TFT)に接続され各サブ画素領域(SPA)の反射領域(RA)と透過領域(TA)を定義する反射電極124と、画素電極に充電されたビデオ信号を安定的に維持できるようにする第1及び第2ストレージキャパシタとを備える。

【0020】

データライン104は薄膜トランジスタ(TFT)を通じてデータ信号を画素電極122及び反射電極124に供給する。ゲートライン102は薄膜トランジスタ(TFT)のゲート電極106にゲート信号を供給する。このようなゲートライン102の一側端は第1ストレージライン132に隣接して形成され、ゲートライン102の他側端は第2ストレージライン136に隣接して形成される。

【0021】

薄膜トランジスタ(TFT)はゲートラインに接続されたゲート電極106、ゲート絶縁膜112を挟んでゲート電極106と重なった活性層114、データライン104に接続され活性層114の一側部に接続されたソース電極108、活性層114の他側部に接続されたドレイン電極110を備える。また薄膜トランジスタ(TFT)はソース電極108及びドレイン電極110と活性層114との間のオーミック接触のためのオーミック接触層116をさらに備える。ゲート電極106はゲートライン102と共に下部基板101上に同一金属で形成される。活性層114及びオーミックコンタクト層116は絶縁膜112上に積層され、その上にソース電極108とドレイン電極110がデータライン104と同一平面上に同一金属で形成される。そして、薄膜トランジスタ(TFT)はその上に形成された無機保護膜118及び有機保護膜126を貫通するコンタクトホール120を通じて画素電極122及び反射電極124に接続される。これにより薄膜トランジスタ(TFT)はゲートライン102のゲート信号に応答してデータライン104のデータ信号を画素電極122及び反射電極124に供給する。

【0022】

画素電極122は各サブ画素領域(SPA)の有機保護膜126上に形成され、コンタクトホール120を通じてドレイン電極110に接続される。画素電極122は透過率が高い透明導電物質で形成され、バックライトユニットからの内部光を透過させる。画素電極122のうち第2ストレージライン136を挟んで相異なる極性のビデオ信号が充電される第1及び第2画素電極122A、122Bは、互いに影響を与えない程度の間隔で離間して形成することが望ましい。例えば、第1及び第2画素電極122A、122Bは約7~20μmの距離で離間して形成することができる。

【0023】

反射電極124は各サブ画素領域(SPA)の反射領域(RA)に形成され、その下部の画素電極122を通じてドレイン電極110と接続される。各サブ画素領域(SPA)のうち、反射電極124が形成された領域は反射領域(RA)と定義され、反射電極124が形成されていない領域は透過領域(TA)と定義される。反射電極124は反射率が高い導電物質で形成され外部光を反射する。反射効率をアップするために反射電極124がエンボス表面を有するように形成され、この反射電極124の下に位置する有機保護膜126の表面も同様にエンボス表面を有するように形成される。また、反射電極124の外周部がデータライン104の一側部と重なるように形成されると共に、薄膜トランジスタ(TFT)と重なるように形成される。この反射電極124により薄膜トランジスタ(TFT)のチャネル部が保護されるため、別のブラックマトリックスが不要である。そして、反射電極124は第1及び第2ストレージライン132、136の間に位置するゲートライン102と重なるように形成されるとともに、ゲートライン102に隣接した第2ストレージライン136の一側部と重なるように形成される。このようにゲートライン102のゲート信

10

20

30

40

50

号が反射電極 124 により遮蔽されることにより反射電極 124 の全領域で液晶分子配列のバラツキが発生しない。これにより、本発明に係る液晶表示装置は液晶分子配列のバラツキを抑えるための従来のような別のブラックマトリックスが不要なので、従来より反射率が向上する。一方、従来と同じ反射率を維持する場合、本発明に係る液晶表示装置は透過率が従来より約 20% 以上向上する。さらに、本発明に係る液晶表示装置は光漏れ現象を防止することによって光漏れ現象によってフリッカを防止できる。

#### 【0024】

第 1 及び第 2 ストレージキャパシタは画素電極 122 に充電されたビデオ信号が次の信号が充電されるまで安定的に維持できるようになる。

第 1 ストレージキャパシタは画素電極 122 と接続されたドレイン電極 110 がゲート絶縁膜 112 を挟んでストレージ電極 134 と重なって形成される。ここで、ストレージ電極 134 は第 1 ストレージライン 132 から突出して形成される。

#### 【0025】

第 2 ストレージキャパシタは画素電極 122 がゲート絶縁膜 112、無機保護膜 118 及び有機保護膜 126 を挟んで第 2 ストレージライン 136 と重なって形成される。ここで、第 2 ストレージライン 136 はゲートライン 102 と平行である方向に形成され、データライン 120 方向に隣接した 2 つの画素電極 122A、122B と全て重なる。

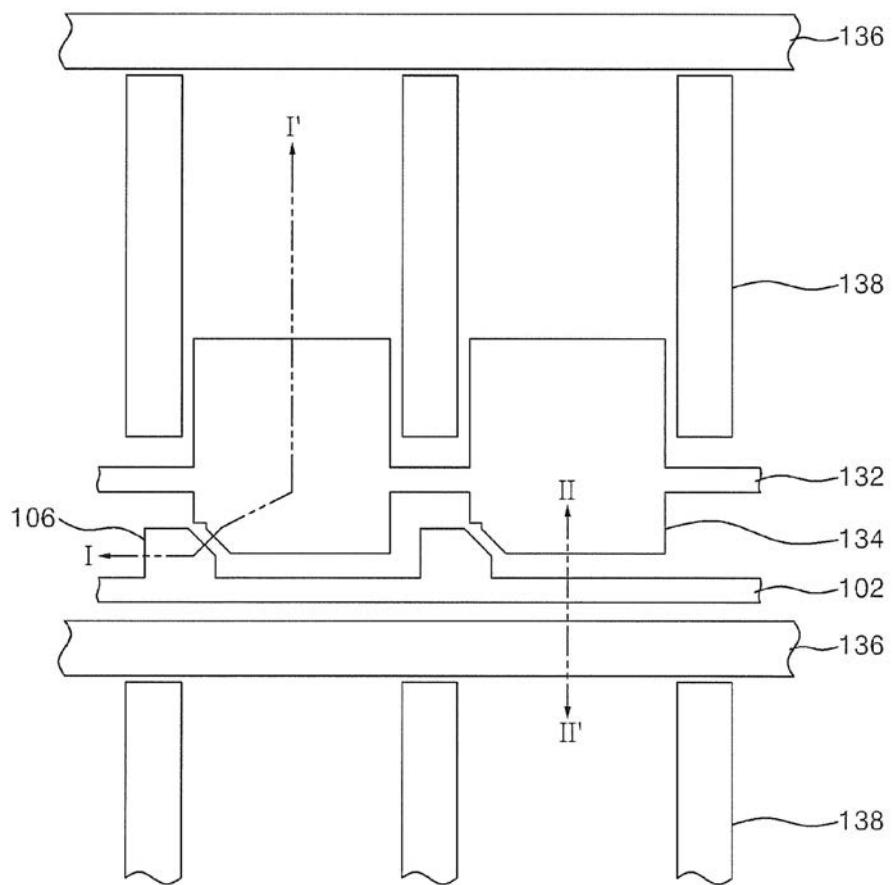

また、第 2 ストレージライン 136 はデータライン 104 と重なるように形成されたシールドパターン 138 と所定間隔で離間して形成される。このようなシールドパターン 138 は、データライン 104 と広い幅でデータライン 104 と重なって形成することにより、データライン 104 と画素電極 122 との間の光漏れを遮断できる。

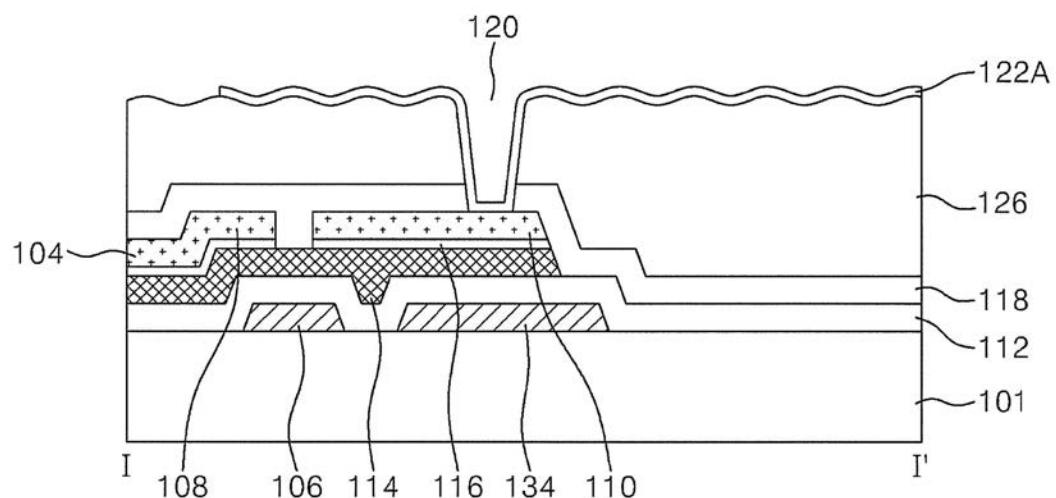

#### 【0026】

一方、シールドパターン 138 は、図 4 に示したように、データラインと重なるシールド部 138a と、ゲートライン 102 と並んで形成される第 2 ストレージライン部 138b を含む。ここで、第 2 ストレージライン部 138b とシールド部 138a は電気的に接続され一体型で形成することもできる。シールドパターン 138 には第 2 ストレージライン部 138b を通じて液晶駆動時基準となる共通電圧またはストレージ電圧が供給される。この場合、シールドパターン 138 はデータライン 104 と画素電極 122 との光漏れを遮断すると共に、データライン 104 のビデオ信号を遮蔽することにより、データライン 104 と画素電極 122 との寄生キャパシタによるカップリング現象を抑えることができる。

#### 【0027】

また、シールド部 138a と電気的に一体型に形成された第 2 ストレージライン部 138b は、シールド部 138 により全体的な面積を増加することができる。面積が増加した第 2 ストレージライン部 138b により、第 2 ストレージライン部 138b と画素電極 122 との重畳面積が増加し、第 2 ストレージキャパシタの容量値も増加する。容量値が増加した第 2 ストレージキャパシタに半比例するキックバック電圧が小さくなる。この際、ストレージ電極 134 の面積が縮小する場合、容量値が減った第 1 ストレージキャパシタに対して、増加したキックバック電圧は第 2 ストレージキャパシタにより減少する。

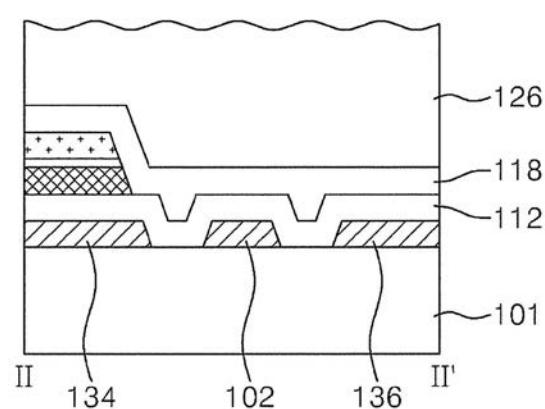

#### 【0028】

一方、図 3 または図 4 に示された薄膜トランジスタ基板 160 は、図 5 に示すように、液晶層を挟むように、カラーフィルタ 152 が形成されたカラーフィルタ基板 150 と結合される。ここでは、図 3 に示された薄膜トランジスタ基板とカラーフィルタ基板が結合され、図 5 に示す液晶表示パネルを構成する。

カラーフィルタ基板 150 は上部基板 111 上に形成されたカラーフィルタ 152 と、カラーフィルタ 152 上に積層されたオーバーコート層 154 及び共通電極 156 を備える。

#### 【0029】

カラーフィルタ 152 は上部基板 111 上に赤色 (R)、緑色 (G)、青 (B) サブ画素領域 (SPA) 別に形成され、R、G、B サブ画素を定義する。

10

20

30

40

50

オーバーコート層 154 は反射領域(RA)で液晶層を2回経由して出射する外部光と、透過領域(TA)で液晶層を1回経由して出射する内部光の光経路差を補償する。このため、オーバーコート層 154 は、透過領域でカラーフィルタ 152 を露出させる透過ホール 158 を有するように形成される。または、光経路差を補償すると共に、カラーフィルタ 152 間の段差を補償するため、オーバーコート層 154 の一部を貫通する透過ホール 158 を有するように形成される。

【0030】

また、オーバーコート層 154 の一側端は第2ストレージライン 136 と隣接した反射電極 124 と重なり、オーバーコート層 154 の他側端はストレージ電極 134 と隣接するように形成されると共に、反射電極 124 と重なる。これにより、図1に示した従来の構造に比べて液晶配向が上下対称構造に近くなる。

このようなオーバーコート層 154 上には透明導電物質よりなる共通電極 156 が形成される。

【0031】

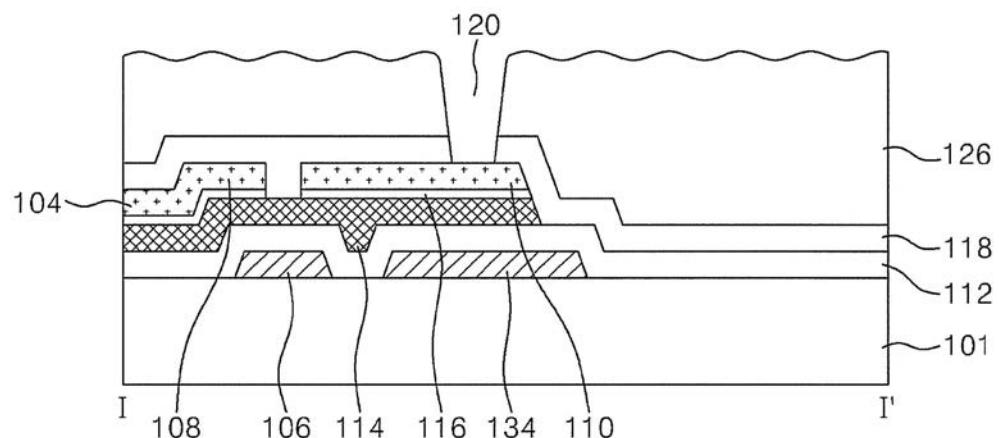

図6a～図10bは本発明に係る薄膜トランジスタ基板の製造方法を示す平面図及び断面図である。ここでは、図2に示された薄膜トランジスタ基板の製造方法を例として説明する。

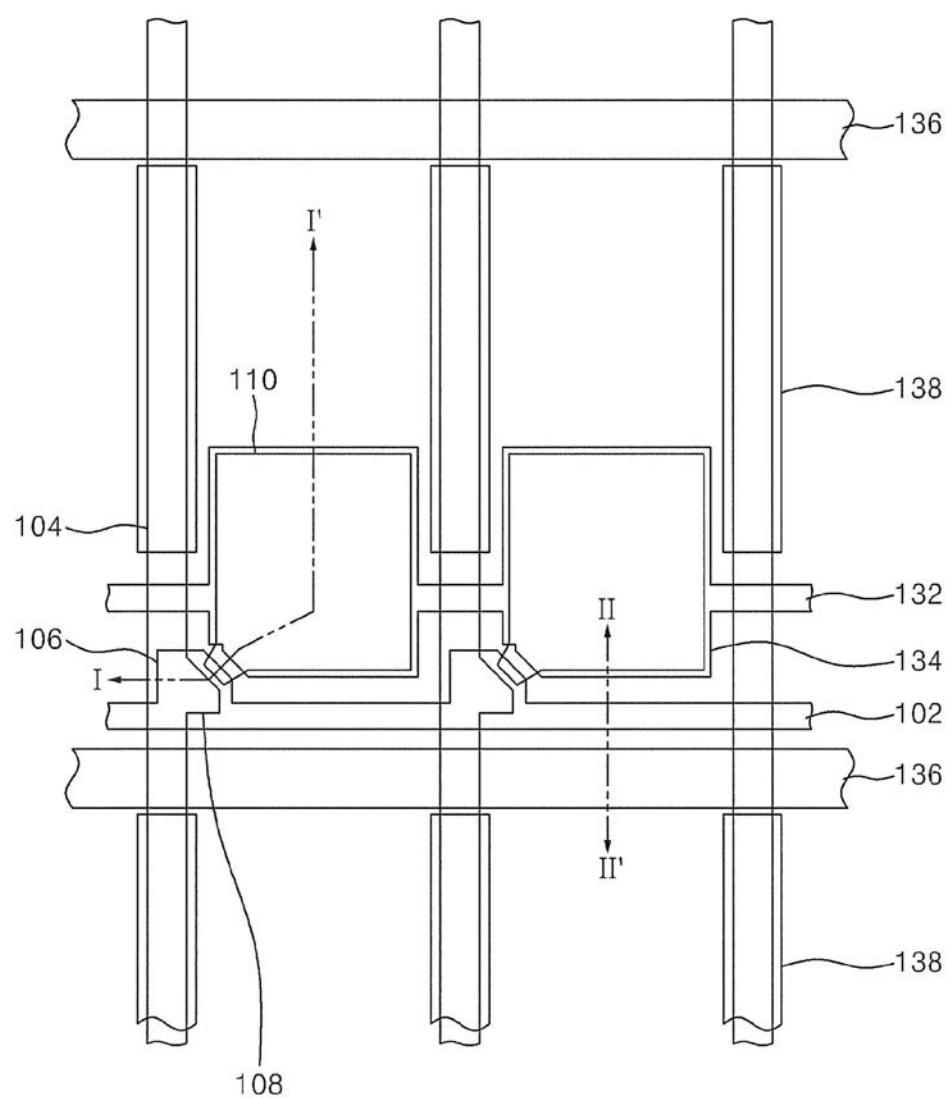

図6a及び図6bに示したように、下部基板 101 上にゲートライン 102、ゲートライン 102 に接続されたゲート電極 106、ゲートライン 106 に隣接した第1及び第2ストレージライン 132、136、第1ストレージライン 132 に接続されたストレージ電極 134、第2ストレージライン 136 に隣接したシールドパターン 138 を含む第1導電パターン群が形成される。

【0032】

具体的に、下部基板 142 上にスパッタリング方法などの蒸着方法を通じてゲート金属層を形成する。ゲート金属層としてはMo、Ti、Cu、AlNd、Al、Cr、Mo合金、Cu合金、Al合金などのように金属物質が単一層として用いることができ、前述の金属を用いて二重層以上に積層した構造で形成する。次いで、ゲート金属層をフォトリソグラフィ工程及び食刻工程でパターンングすることにより、ゲートライン 102、ゲート電極 106、第1及び第2ストレージライン 132、136、ストレージ電極 134 及びシールドパターン 138 を含む第1導電パターン群を形成する。

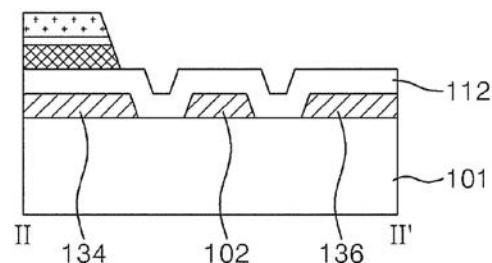

【0033】

図7a及び図7bに示すように、第1導電パターン群が形成された下部基板 101 上にゲート絶縁膜 112 を形成し、その上にデータライン 104、ソース電極 108、ドレイン電極 110 を含む第2導電パターン群と、第2導電パターン群に沿ってその下部に重なった活性層 114 及びオーミック接触層 116 を含む半導体パターン群を形成する。このような半導体パターン群と第2導電パターン群は回折露光マスクまたはハーフトーン(Half Tone)を用いた1つのマスク工程で形成することができる。

【0034】

具体的に、第1導電パターン群が形成された下部基板 101 上にゲート絶縁膜 112、非晶質シリコン層、不純物(n+またはp+)がドーピングされた非晶質シリコン層、ソース/ドレイン金属層を順に形成する。ゲート絶縁膜 112 としては、酸化シリコン(SiO<sub>x</sub>)、窒化シリコン(SiNx)などの無機絶縁物質を用いることができ、ソース/ドレイン金属層としてはMo、Ti、Cu、AlNd、Al、Cr、Mo合金、Cu合金、Al合金などの金属物質を単一層として用いることができ、また前述の金属を用いた二重層以上を積層した構造とすることができます。そして、ソース/ドレイン金属層上にフォトレジストを塗布した後、回折露光マスクを用いたフォトリソグラフィ工程で、フォトレジストを露光及び現像することにより、段差を有する第1及び第2フォトレジストパターンを形成する。第1フォトレジストパターンは半導体パターン群及び第2導電パターン群が形成される領域に位置するように形成される。第2フォトレジストパターンは第1フォトレジストパターンより薄く、薄膜トランジスタのチャンネルが形成される領域に位置するように形成される。このようなフ

10

20

30

40

50

オトレジストパターンを用いた食刻工程で、ソース/ドレイン金属層をパターニングすることにより、第2導電パターン群と、その下部の半導体パターン群を形成する。この場合、第2導電パターン群のうちソース電極108とドレイン電極110は電気的に接続した構造を有する。

【0035】

酸素(O<sub>2</sub>)プラズマを用いたアシング工程で、第1フォオトレジストパターンが薄くなるように形成し、第2フォオトレジストパターンを除去する。次いで、アシングされた第1フォオトレジストパターンを用いた食刻工程で、第2フォオトレジストパターンの除去により露出された第2導電パターン群と、その下部のオーミック接触層116を除去することにより、ソース電極108とドレイン電極110は分離され、活性層114が露出される。

10

【0036】

そして、ストリップ工程でソース/ドレイン金属パターン上に残存していた第1フォオトレジストパターンを除去する。

図8a及び図8bに示すように、第2導電パターン群が形成されたゲート絶縁膜112上に無機保護膜118と、無機保護膜118上にエンボス形状の表面を有する有機保護膜126を形成する。

【0037】

具体的に、第2導電パターン群が形成されたゲート絶縁膜112上に、無機保護膜118を形成する。無機保護膜118はゲート絶縁膜のような無機絶縁物質で形成されうる。このような無機保護膜118上にエンボス形状の表面を有する有機保護膜126を形成する。有機保護膜126はアルカリ可溶基を含む樹脂、PAC(Photo Active Compound)、溶媒及び添加物(接着力低下剤、界面活性剤など)などよりなる。この無機保護膜118と有機保護膜126とをフォトリソグラフィ工程と食刻工程でパターニングすることにより、無機保護膜118及び有機保護膜126を貫通してドレイン電極110を露出させるコンタクトホール120を形成する。

20

【0038】

図9a及び図9bに示すように、有機保護膜126上に画素電極を含む第3導電パターン群を形成する。

具体的に、有機保護膜126上にスパッタリングなどの蒸着方法を通じて、エンボス形状を維持するように透明導電層を形成し、その透明導電層をフォトリソグラフィ工程と食刻工程でパターニングすることにより、各サブ画素領域に画素電極122を形成する。画素電極122は、コンタクトホール120を介してドレイン電極110に接続される。透明導電層としては、酸化スズ(Tin Oxide : T0)、酸化インジウムスズ(Indium Tin Oxide : ITO)、酸化亜鉛インジウム(Indium Zinc Oxide : IZO)、スズ酸化亜鉛インジウム(Indium Tin Zinc Oxide : ITZO)などを用いることができる。

30

【0039】

図10a及び図10bに示すように、第3導電パターン群上に反射電極124を含む第4導電パターン群を形成する。

具体的に、画素電極が形成された有機保護膜126上に、エンボス形状を維持しつつ反射金属層を積層する。反射金属層としては、Al、INDなどのように反射率が高い金属を用いることができる。次いで、反射金属層をフォトリソグラフィ工程及び食刻工程でパターニングすることにより、各サブ画素領域毎に反射電極124を含む第4導電パターン群を形成する。

40

【0040】

以上の実施例では半透過型液晶表示装置に本発明を適用したが、反射型液晶表示装置にも適用できる。その場合は、第2ストレージラインを反射電極と重なるように形成する。また以上の実施例では反射電極を画素電極上に形成したが、これは必須のことではなく、逆順で形成することもでき、同一層に形成することもできる。

以上述べた内容を通じて、当業者ならば本発明の技術思想を逸脱しない範囲で多様な変更及び修正が可能である。従って、本発明の技術的範囲は明細書の詳細な説明に記載され

50

た内容に限定されることではなく、特許請求の範囲によって定まるべきである。

【図面の簡単な説明】

【0041】

【図1】従来の半透過型液晶表示パネルを示す断面図である。

【図2】本発明に係る半透過型液晶表示パネルの薄膜トランジスタ基板を示す平面図である。

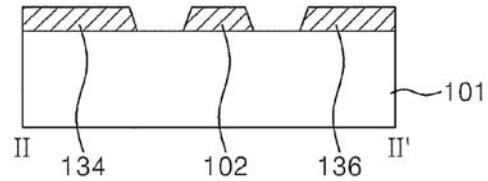

【図3】図2において線I-I'、II-II'に沿って切り取った薄膜トランジスタ基板を示す断面図である。

【図4】図2に示されたシールドパターンの他の形態を示す平面図である。

【図5】図3に示した薄膜トランジスタ基板とカラーフィルタ基板を含む液晶表示パネルを示す断面図である。 10

【図6A】本発明に係る薄膜トランジスタの基板製造方法のうち第1導電パターン群の製造方法を説明するための平面図である。

【図6B】本発明に係る薄膜トランジスタの基板製造方法のうち第1導電パターン群の製造方法を説明するための断面図である。

【図7A】本発明に係る薄膜トランジスタ基板の製造方法のうち第2導電パターン群と半導体パターン群の製造方法を説明するための平面図である。

【図7B】本発明に係る薄膜トランジスタ基板の製造方法のうち第2導電パターン群と半導体パターン群の製造方法を説明するための断面図である。

【図8A】本発明に係る薄膜トランジスタ基板の製造方法のうち無機保護膜及び有機保護膜の製造方法を説明するための平面図である。 20

【図8B】本発明に係る薄膜トランジスタ基板の製造方法のうち無機保護膜及び有機保護膜の製造方法を説明するための断面図である。

【図9A】本発明に係る薄膜トランジスタ基板の製造方法のうち第3導電パターン群の製造方法を説明するための平面図である。

【図9B】本発明に係る薄膜トランジスタ基板の製造方法のうち第3導電パターン群の製造方法を説明するための断面図である。

【図10A】本発明に係る薄膜トランジスタ基板の製造方法のうち第4導電パターン群の製造方法を説明するための平面図である。

【図10B】本発明に係る薄膜トランジスタ基板の製造方法のうち第4導電パターン群の製造方法を説明するための断面図である。 30

【符号の説明】

【0042】

101、111：基板

102：ゲートライン

104：データライン

106：ゲート電極

108：ソース電極

110：ドレイン電極

112：ゲート絶縁膜

114：活性層

116：オーミック接触層

118、126：保護膜

120：コンタクトホール

122：画素電極

124：反射電極

132、136：ストレージライン

134：ストレージ電極

138：シールドパターン

150：カラーフィルタ基板

10

20

30

40

50

152 : カラーフィルタ

154 : オーバーコート層

156 : 共通電極

158 : 透過ホール

160 : 薄膜トランジスタ基板

S P A : サブ画素領域

T A : 透過領域

R A : 反射領域

【図1】

【図2】

【図3】

【図4】

【図5】

【図6A】

【図6B】

【図 7 A】

【図 7 B】

【図 8 A】

【図 8 B】

【図9A】

【図9B】

【図10A】

【図10B】

---

フロントページの続き

(72)発明者 李 承 珪

大韓民国京畿道水原市靈通区網捕洞485-4番地2層202号

(72)発明者 朴 源 祥

大韓民国京畿道龍仁市器興区新葛洞セ千年グリーンビル5團地501棟903号

(72)発明者 金 宰 賢

大韓民国京畿道水原市靈通区靈通洞972-2癡積滑住公アパート845棟501号

(72)発明者 趙 容 ソク

大韓民国ソウル特別市冠岳区奉天11洞銀川アパート205棟901号

(72)発明者 呂 廉 碩

大韓民国忠清北道堤川市青田洞ドゥジン白鷺アパート201棟1502号

審査官 藤田 都志行

(56)参考文献 特開2006-011399(JP, A)

特開2004-077544(JP, A)

特開2005-4206(JP, A)

(58)調査した分野(Int.Cl., DB名)

G 02 F 1 / 1368

G 02 F 1 / 1343

G 02 F 1 / 1335