(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6208350号

(P6208350)

(45) 発行日 平成29年10月4日(2017.10.4)

(24) 登録日 平成29年9月15日(2017.9.15)

(51) Int.Cl.

H01L 21/82 (2006.01)

F 1

H01L 21/82

W

請求項の数 15 (全 11 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2016-529862 (P2016-529862)  |

| (86) (22) 出願日 | 平成26年7月23日(2014.7.23)         |

| (65) 公表番号     | 特表2016-527724 (P2016-527724A) |

| (43) 公表日      | 平成28年9月8日(2016.9.8)           |

| (86) 國際出願番号   | PCT/US2014/047834             |

| (87) 國際公開番号   | W02015/013415                 |

| (87) 國際公開日    | 平成27年1月29日(2015.1.29)         |

| 審査請求日         | 平成29年1月30日(2017.1.30)         |

| (31) 優先権主張番号  | 61/858,567                    |

| (32) 優先日      | 平成25年7月25日(2013.7.25)         |

| (33) 優先権主張国   | 米国(US)                        |

| (31) 優先権主張番号  | 14/338,229                    |

| (32) 優先日      | 平成26年7月22日(2014.7.22)         |

| (33) 優先権主張国   | 米国(US)                        |

早期審査対象出願

|           |                                                                                                               |

|-----------|---------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 595020643<br>クアルコム・インコーポレイテッド<br>QUALCOMM INCORPORATED<br>アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775 |

| (74) 代理人  | 100108855<br>弁理士 蔵田 昌俊                                                                                        |

| (74) 代理人  | 100109830<br>弁理士 福原 淑弘                                                                                        |

| (74) 代理人  | 100158805<br>弁理士 井関 守三                                                                                        |

| (74) 代理人  | 100194814<br>弁理士 奥村 元宏                                                                                        |

最終頁に続く

(54) 【発明の名称】クリティカル技術ピッチ整合をもつSOC設計

## (57) 【特許請求の範囲】

## 【請求項1】

システムオンチップ(SOC)装置であって、

最小ピッチgをもつ複数のゲート相互接続と、

最小ピッチmをもつ複数の金属相互接続と、

前記ゲート相互接続と前記金属相互接続とを相互接続する複数のビアと、前記ビアが最小ピッチvを有する、を備え、

ここにおいて、 $g^2 + m^2 \geq v^2$ であり、前記最小ピッチvは、前記装置で使用される前記最小ピッチgおよび前記最小ピッチmよりも大きく、gとmとの最小公倍数(LCM)が20gよりも小さい、装置。 10

## 【請求項2】

gが約96nmであり、mが約64nmであり、vが約115nmである、請求項1に記載の装置。

## 【請求項3】

前記複数の金属相互接続が、第1の相互接続レベルおよび第2の相互接続レベルの上にあり、ビアが、前記第1の相互接続レベルと前記第2の相互接続レベルとの間で前記金属相互接続を相互接続する、ここにおいて、前記複数の金属相互接続は、第3の相互接続レベル上にある、請求項1に記載の装置。

## 【請求項4】

前記第1の相互接続レベルが第1の金属層であり、前記第2の相互接続レベルが第2の

金属層である、請求項 3 に記載の装置。

**【請求項 5】**

$m_2$  の最小ピッチをもつ第 2 の複数の金属相互接続をさらに備え、ここにおいて、 $m_2 > m$  であり、 $g$  と  $m$  と  $m_2$  との前記 LCM が 20 g よりも小さい、請求項 1 に記載の装置。

**【請求項 6】**

$g$  が約 96 nm であり、 $m$  が約 72 nm であり、 $v$  が約 115 nm であり、 $m_2$  が約 80 nm である、請求項 5 に記載の装置。

**【請求項 7】**

前記複数の金属相互接続が第 3 の相互接続レベル上にあり、前記第 2 の複数の金属相互接続が第 5 の相互接続レベル上にあり、ここにおいて、ビアが、前記複数の金属相互接続と前記第 2 の複数の金属相互接続との間で金属相互接続を相互接続する、請求項 5 に記載の装置。 10

**【請求項 8】**

前記第 3 の相互接続レベルが第 3 の金属層であり、前記第 5 の相互接続レベルが第 5 の金属層である、請求項 7 に記載の装置。

**【請求項 9】**

システムオンチップ (SOC) 装置を動作させる方法であって、

最小ピッチ  $g$  をもつ複数のゲート相互接続に電流を流すことと、

最小ピッチ  $m$  をもつ複数の金属相互接続に電流を流すことと、

前記ゲート相互接続と前記金属相互接続とを相互接続する複数のビアに電流を流すことと、前記ビアが最小ピッチ  $v$  を有する、を備え、

ここにおいて、 $g^2 + m^2 = v^2$  であり、前記最小ピッチ  $v$  は、前記装置で使用される前記最小ピッチ  $g$  および前記最小ピッチ  $m$  よりも大きく、 $g$  と  $m$  との最小公倍数 (LCM) が 20 g よりも小さい、方法。 20

**【請求項 10】**

前記複数の金属相互接続が、第 1 の相互接続レベルおよび第 2 の相互接続レベルの上にあり、ビアが、前記第 1 の相互接続レベルと前記第 2 の相互接続レベルとの間で前記金属相互接続を相互接続する、ここにおいて、前記複数の金属相互接続は、第 3 の相互接続レベル上にある、請求項 9 に記載の方法。 30

**【請求項 11】**

前記第 1 の相互接続レベルが第 1 の金属層であり、前記第 2 の相互接続レベルが第 2 の金属層である、請求項 10 に記載の方法。

**【請求項 12】**

$m_2$  の最小ピッチをもつ第 2 の複数の金属相互接続に電流を流すことをさらに備え、ここにおいて、 $m_2 > m$  であり、 $g$  と  $m$  と  $m_2$  との前記 LCM が 20 g よりも小さい、請求項 9 に記載の方法。

**【請求項 13】**

前記複数の金属相互接続が第 3 の相互接続レベル上にあり、前記第 2 の複数の金属相互接続が第 5 の相互接続レベル上にあり、ここにおいて、ビアが、前記複数の金属相互接続と前記第 2 の複数の金属相互接続との間で金属相互接続を相互接続する、請求項 12 に記載の方法。 40

**【請求項 14】**

前記第 3 の相互接続レベルが第 3 の金属層であり、前記第 5 の相互接続レベルが第 5 の金属層である、請求項 13 に記載の方法。

**【請求項 15】**

最小ピッチ  $g$  をもつ前記複数のゲート相互接続に電流を流すための手段と、

最小ピッチ  $m$  をもつ前記複数の金属相互接続に電流を流すための手段と、

前記ゲート相互接続と前記金属相互接続とを相互接続する前記複数のビアに電流を流すための手段と、をさらに備える、請求項 1 に記載の装置。 50

## 【発明の詳細な説明】

## 【技術分野】

【0001】

## 関連出願の相互参照

[0001]本出願は、その全体が参照により本明細書に明確に組み込まれる、2013年7月25日に出願された「A SOC design with critical technology pitch alignment」と題する米国仮出願第61/858,567号、および2014年7月22日に出願された「A SOC DESIGN WITH CRITICAL TECHNOLOGY PITCH ALIGNMENT」と題する米国非仮出願第14/338,229号の利益を主張する。

## 【0002】

10

[0002]本開示は、一般に回路レイアウトに関し、より詳細には、クリティカル技術ピッチ整合をもつシステムオンチップ(SOC)設計に関する。

## 【背景技術】

【0003】

[0003]ピッチは、同じタイプの隣接する要素間の距離である。 $\times\%$ だけピッチをスケーリングすることのコスト利益、電力利益、および性能利益を達成するためには、約 $\times^2\%$ のエリアスケーリングが取得されるべきである。たとえば、70%ピッチスケーリングの完全なコスト利益、電力利益、および性能利益を達成するためには、約50%エリアスケーリングが取得されるべきである。しかしながら、 $\times^2\%$ エリアスケーリングを取得するための要件を仮定すれば、 $\times\%$ ピッチスケーリングは、最良のコスト利益、電力利益、および性能利益を与えないことがある。したがって、所望のエリアスケーリングを仮定すればピッチまたはピッチスケーリングを決定するための方法および装置が必要とされる。

20

## 【発明の概要】

【0004】

[0004]本開示の一態様では、方法および装置が提供される。SOC装置は、最小ピッチ $g$ をもつ複数のゲート相互接続と、最小ピッチ $m$ をもつ複数の金属相互接続と、ゲート相互接続と金属相互接続とを相互接続する複数のビアとを含む。ビアは最小ピッチ $v$ を有する。値 $m$ 、 $g$ 、および $v$ は、 $g^2 + m^2 = v^2$ であり、 $g$ と $m$ とのLCMが $20g$ よりも小さいようなものである。

## 【図面の簡単な説明】

30

【0005】

【図1】[0005]ピッチスケーリングを示す図。

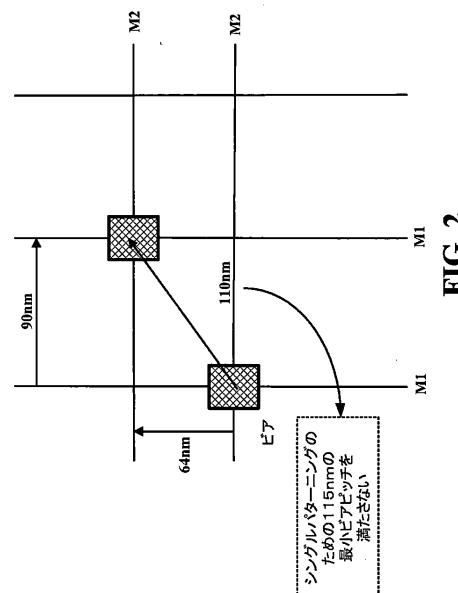

【図2】[0006]ゲート相互接続ピッチと金属相互接続ピッチとビアピッチとを示す図。

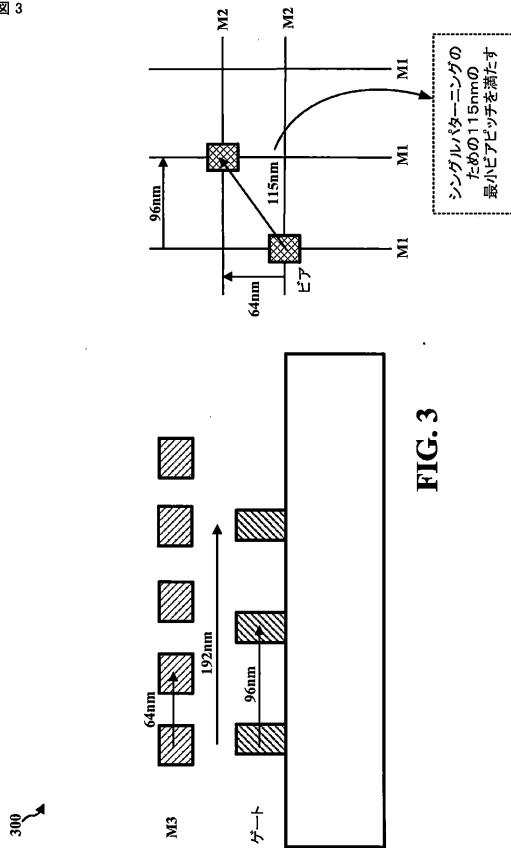

【図3】[0007]例示的なゲート相互接続ピッチと金属相互接続ピッチとビアピッチとの第1のセットを示す図。

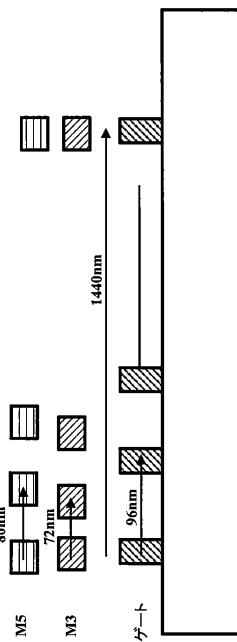

【図4】[0008]例示的なゲート相互接続ピッチと金属相互接続ピッチとビアピッチとの第2のセットを示す図。

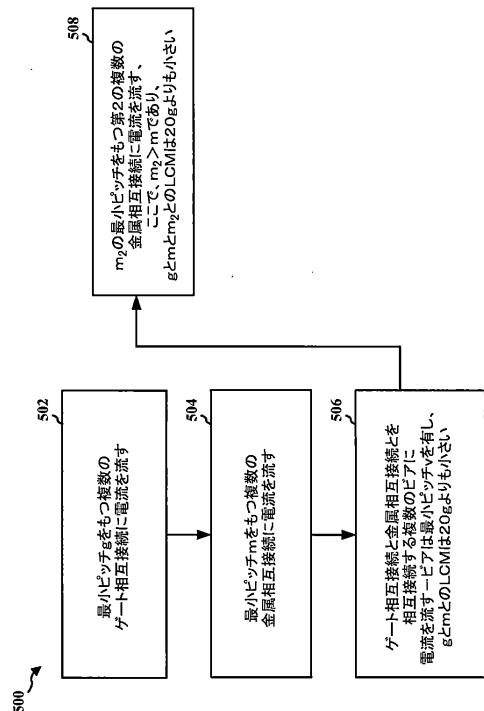

【図5】[0009]SOC装置を動作させる方法のフローチャート。

## 【発明を実施するための形態】

【0006】

40

[0010]添付の図面に関して以下に記載する発明を実施するための形態は、様々な構成を説明するものであり、本明細書で説明する概念が実施され得る構成のみを表すものではない。発明を実施するための形態は、様々な概念の完全な理解を与えるための具体的な詳細を含む。しかしながら、これらの概念はこれらの具体的な詳細なしに実施され得ることが、当業者には明らかであろう。いくつかの事例では、そのような概念を不明瞭にしないように、よく知られている構造および構成要素をブロック図の形式で示す。装置および方法が、以下の発明を実施するための形態において説明され、様々なブロック、モジュール、構成要素、回路、ステップ、プロセス、アルゴリズム、要素などによって添付の図面に示され得る。

【0007】

50

[0011] 図 1 は、ピッチスケーリングを示す図 100 である。図 1 に示されているように、28 nm 製造プロセス技術では、（「ポリ」相互接続と呼ばれることがある）ゲート相互接続は、 $g_1$  の最小ピッチを有し得る（任意の 2 つのゲート相互接続間の距離は最小でも  $g_1$  である）。20 nm、16 nm、14 nm、および / または他の製造プロセス技術においてスケーリングすると、ゲート相互接続は  $g_2$  の最小ピッチを有し得る（任意の 2 つのゲート相互接続間の距離は最小でも  $g_2$  である）。一例では、 $g_1$  は 130 nm であり得る。ゲート相互接続ピッチの 70 % スケーリングは 90 nm の  $g_2$  を生じるであろう。

28 nm 製造プロセス技術では、第 1 の金属層 M 1 は  $m_{1,1}$  の最小ピッチを有し得る（任意の 2 つの第 1 の金属層 M 1 相互接続間の距離は最小でも  $m_{1,1}$  である）。20 nm、16 nm、14 nm、および / または他の製造プロセス技術においてスケーリングすると、

第 1 の金属層 M 1 は  $m_{1,2}$  の最小ピッチを有し得る（任意の 2 つの第 1 の金属層 M 1 相互接続間の距離は最小でも  $m_{1,2}$  である）。一例では、 $m_{1,1}$  は 90 nm であり得る。第 1 の金属層 M 1 相互接続ピッチの 70 % スケーリングは 64 nm の  $m_{1,2}$  を生じるであろう。

28 nm 製造プロセス技術では、他の金属層 M a（たとえば、M 2、M 3、M 4、M 5）は  $m_{a,1}$  の最小ピッチを有し得る（任意の 2 つの金属層 M a 相互接続間の距離は最小でも  $m_{a,1}$  である）。20 nm、16 nm、14 nm、および / または他の製造プロセス技術においてスケーリングすると、金属層 M a は  $m_{a,2}$  の最小ピッチを有し得る（任意の 2 つの金属層 M a 相互接続間の距離は最小でも  $m_{a,2}$  である）。一例では、 $m_{a,1}$  は 90 nm であり得る。金属層 M a 相互接続ピッチの 70 % スケーリングは 64 nm の  $m_{a,2}$  を生じるであろう。

20 nm、16 nm、14 nm、および / または他の製造プロセス技術では、M b 金属層は  $m_b$  のピッチを有し得る。

M b 金属層は、M a 金属層よりも高く、M a 金属層よりも広いことがある。たとえば、M a 金属層は M 2 金属層と M 3 金属層とを含み得、M b 金属層は M 4 金属層を含み得る。別の例では、M a 金属層は M 2 金属層と M 3 金属層と M 4 金属層とを含み得、M b 金属層は M 5 金属層を含み得る。一例では、 $m_b$  は 80 nm である。

28 nm 製造プロセス技術では、ビアは  $v_1$  の最小ピッチを有し得る（任意の 2 つのビア間の距離は最小でも  $v_1$  である）。20 nm、16 nm、14 nm、および / または他の製造プロセス技術においてスケーリングすると、ビアは  $v_2$  の最小ピッチを有し得る（任意の 2 つのビア間の距離は最小でも  $v_2$  である）。一例では、 $v_1$  は 130 nm であり得る。（ダブルパターニングプロセスにおける複数のマスクではなく、ただ 1 つのマスクを使用する）シングルパターニングプロセスによるプロセス限界を維持することは、任意の 2 つのビアの最小ピッチを制限する。

115 nm 最小ピッチを仮定すると（すなわち、 $v_2$  が 115 nm であると仮定すると）、ビアの 88 % スケーリングが生じる。この例では、ビアピッチは、必ずしもゲート相互接続および金属相互接続などの他の要素と同様にスケーリングされるとは限らない。

#### 【0008】

[0012] 図 1 の上述の例では、ビアのための 88 % ピッチスケーリング限界を仮定すれば、70 % だけ他の金属層のすべてをスケーリングすることは、相互接続とビアとが位置合わせされないので、理想的でない。上記で説明したように、x % だけピッチをスケーリングすることのコスト利益、電力利益、および性能利益を達成するためには、約  $x^2$  % のエリアスケーリングが取得されるべきである。たとえば、70 % ピッチスケーリングの完全なコスト利益、電力利益、および性能利益を達成するためには、約 50 % エリアスケーリングが取得されるべきである。しかしながら、図 2 に関してさらに説明するように、 $x^2$  % エリアスケーリングを取得するための要件を仮定すれば、x % ピッチスケーリングは、ビアピッチスケーリングを制限するとき、最良のコスト利益、電力利益、および性能利益を与えないことがある。

#### 【0009】

[0013] 図 2 は、ゲート相互接続ピッチと金属相互接続ピッチとビアピッチとを示す図 200 である。図 2 では、2 つの図示された金属層 M 1 相互接続は、ゲート相互接続と同じ方向に延び、ゲート相互接続に接続され、ゲート相互接続と同じピッチを有する。他の金属層 M 1 相互接続は、64 nm などのより小さいピッチを有し得る。したがって、図 2 に

40

50

示されているように、ゲート相互接続ピッチ  $g_2$  が最小値 90 nm であり、金属層 M 2 ピッチ  $m a_2$  が最小値 64 nm であるとき、ビアピッチ  $v_2$  は 110 nm である。シングルパターニングのためのプロセス限界がビアピッチについて 115 nm である場合、110 nm のビアピッチは、シングルパターニングのための最小ビアピッチ要件を満たさないであろう。115 nm のビアピッチと、ゲート相互接続および金属層 M 2 のための 70 % ピッチスケーリングとを仮定すると、ゲート相互接続ピッチとビアピッチと金属相互接続ピッチとは整合せず、このことは、ピンアクセス困難を生じ、場所およびルート効率を低下させ、低い場所およびルート利用率を生じることがある（利用されるエリアは 50 % に低減されないことがある）。一構成では、ゲート相互接続ピッチ  $g_2$  および / または金属層 M 2 相互接続ピッチ  $m a_2$  のスケーリングは、ビアピッチ  $v_2$  の必須のスケーリングを満たし、ピンアクセスと、場所およびルート効率と、場所およびルート利用率との改善を可能にするために増加させられ得る。

10

#### 【0010】

[0014] 図 3 は、例示的なゲート相互接続ピッチと金属相互接続ピッチとビアピッチとの第 1 のセットを示す図 300 である。上記で説明したように、ゲート相互接続ピッチ  $g_2$  および / または金属層 M 2 相互接続ピッチ  $m a_2$  のスケーリングは、ビアピッチ  $v_2$  の必須のスケーリングを満たすために増加させられ得る。たとえば、図 3 に示されているように、ゲート相互接続ピッチ  $g_2$  のスケーリングは 73.85 % に増加させられる。ゲート相互接続ピッチ  $g_2$  が最小値 96 nm であり、金属層 M 2 ピッチ  $m a_2$  が最小値 64 nm であるとき、ビアピッチ  $v_2$  は、前述の 115 nm ビアピッチ限界を満たす 115 nm である。

20 図 3 に示されているように、金属層 M 3 ピッチも 64 nm の最小値であり得る。96 nm と 64 nm との（最小公倍数（lowest common multiple）とも呼ばれる）最小公倍数（LCM：least common multiple）は 192 nm である。一構成では、最小ゲート相互接続ピッチと最小金属相互接続ピッチとの LCM は、最小ゲート相互接続ピッチの 20 倍よりも小さくなるように制約され得る。たとえば、最小ゲート相互接続ピッチと最小金属相互接続ピッチとの LCM は、1920 nm (20 \* 96 nm) よりも小さくなるように制約され得る。この場合、96 nm および 64 nm の最小ゲート相互接続ピッチおよび最小金属相互接続ピッチは、それぞれ、そのような要件を満たす。

#### 【0011】

[0015] 図 4 は、例示的なゲート相互接続ピッチと金属相互接続ピッチとビアピッチとの第 2 のセットを示す図 400 である。この例では、最小ゲート相互接続ピッチは 96 nm であり得、最小金属層 M 2 は 64 nm であり得、最小金属層 M 3 ピッチは 72 nm であり得、最小金属層 M 5 ピッチは 80 nm であり得る。96 nm と 72 nm と 80 nm との LCM は 1440 nm である。

30

#### 【0012】

[0016] 一構成では、SOC 装置は、最小ピッチ  $g$  をもつ複数のゲート相互接続と、最小ピッチ  $m$  をもつ複数の金属相互接続と、ゲート相互接続と金属相互接続とを相互接続する複数のビアとを有し得る。ビアは最小ピッチ  $v$  を有する。ピッチ  $g$ 、 $m$ 、および  $v$  は、 $g^2 + m^2 - v^2$  であり、 $g$  と  $m$  との LCM が 20 g よりも小さいものである。一例では、 $g$  は 96 nm に等しいかまたはそれにほぼ等しく、 $m$  は 64 nm に等しいかまたはそれにほぼ等しく、 $v$  は 115 nm に等しいかまたはそれにほぼ等しい。 $g = 96 \text{ nm}$  および  $m = 64 \text{ nm}$  のピッチの場合、LCM は、1920 nm よりも小さい 192 nm である。 $g^2 + m^2 - v^2$  と LCM ( $g, m$ ) < 20 g によって制約される。一構成では、ビアピッチ  $v$  が仮定され、ゲート相互接続ピッチ  $g$  および金属相互接続ピッチ  $m$  は、上式を満たすように調整される。複数の金属相互接続は、第 1 の相互接続レベルまたは第 2 の相互接続レベルのうちの少なくとも 1 つ上にあり、ビアは、第 1 の相互接続レベルと第 2 の相互接続レベルとの間で金属相互接続を相互接続する。第 1 の相互接続レベルは第 1 の金属層 M 1 であり得、第 2 の相互接続レベルは第 2 の金属層 M 2 であり得る。

40

#### 【0013】

10

20

30

40

50

[0017] S O C 装置は、 $m_2$ の最小ピッチをもつ第2の複数の金属相互接続をさらに含み得、ここで、 $m_2 > m$ であり、 $g$ と $m$ と $m_2$ とのLCMは20 gよりも小さい。一例では、 $g$ は96 nmに等しいかまたはそれにほぼ等しく、 $m$ は72 nmに等しいかまたはそれにほぼ等しく、 $v$ は115 nmに等しいかまたはそれにほぼ等しく、 $m_2$ は80 nmに等しいかまたはそれにほぼ等しい。 $g = 96 \text{ nm}$ 、 $m = 72 \text{ nm}$ 、および $m_2 = 80 \text{ nm}$ のピッヂの場合、LCMは1440 nmである。ピッヂ $g$ 、 $m$ 、 $m_2$ 、および $v$ は、式 $g^2 + m^2 - v^2$ とLCM( $g$ ,  $m$ ,  $m_2$ ) < 20 gによって制約される。一構成では、ビアピッヂ $v$ が仮定され、ゲート相互接続ピッヂ $g$ 、金属相互接続ピッヂ $m$ 、および金属相互接続ピッヂ $m_2$ は、上式を満たすように調整される。複数の金属相互接続は、第3の相互接続レベル(たとえば、金属層M3)上にあり得、第2の複数の金属相互接続は、第3の相互接続レベルよりも高い第5の相互接続レベル(たとえば、金属層M5)上にあり得る。ビアは、複数の金属相互接続と第2の複数の金属相互接続との間で金属相互接続を相互接続する。第3の相互接続レベルは第3の金属層M3であり得、第5の相互接続レベルは第5の金属層M5であり得る。

## 【0014】

[0018] 図5は、SOC装置を動作させる方法のフローチャート500である。ステップ502において、最小ピッヂ $g$ をもつ複数のゲート相互接続に電流を流す。ステップ504において、最小ピッヂ $m$ をもつ複数の金属相互接続に電流を流す。ステップ506において、ゲート相互接続と金属相互接続とを相互接続する複数のビアに電流を流す。ビアは最小ピッヂ $v$ を有する。ゲート相互接続、金属相互接続、およびビアのピッヂは $g^2 + m^2 - v^2$ を満たす。さらに、 $g$ と $m$ とのLCMは20 gよりも小さい。複数の金属相互接続は、第1の相互接続レベルまたは第2の相互接続レベルのうちの少なくとも1つ上にあり得、ビアは、第1の相互接続レベルと第2の相互接続レベルとの間で金属相互接続を相互接続し得る。第1の相互接続レベルは第1の金属層であり得、第2の相互接続レベルは第2の金属層であり得る。ステップ508において、 $m_2$ の最小ピッヂをもつ第2の複数の金属相互接続に電流を流し、ここで、 $m_2 > m$ であり、 $g$ と $m$ と $m_2$ とのLCMは20 gよりも小さい。複数の金属相互接続は第3の相互接続レベル上にあり得、第2の複数の金属相互接続は第5の相互接続レベル上にあり得る。ビアは、複数の金属相互接続と第2の複数の金属相互接続との間で金属相互接続を相互接続し得る。第3の相互接続レベルは第3の金属層であり得、第5の相互接続レベルは第5の金属層であり得る。

## 【0015】

[0019] 一構成では、SOC装置は、最小ピッヂ $g$ をもつ複数のゲート相互接続に電流を流すための手段と、最小ピッヂ $m$ をもつ複数の金属相互接続に電流を流すための手段と、ゲート相互接続と金属相互接続とを相互接続する複数のビアに電流を流すための手段とを含む。ビアは最小ピッヂ $v$ を有し、 $g^2 + m^2 - v^2$ であり、 $g$ と $m$ とのLCMは20 gよりも小さい。複数のゲート相互接続に電流を流すための手段は複数のゲート相互接続であり、複数の金属相互接続に電流を流すための手段は複数の金属相互接続であり、複数のビアに電流を流すための手段は複数のビアである。SOC装置は、 $m_2$ の最小ピッヂをもつ第2の複数の金属相互接続に電流を流すための手段をさらに含み得、ここで、 $m_2 > m$ であり、 $g$ と $m$ と $m_2$ とのLCMは20 gよりも小さい。第2の複数の金属相互接続に電流を流すための手段は第2の複数の金属相互接続である。

## 【0016】

[0020] 上記で与えたように、 $x\%$ エリアスケーリングを取得するための要件を仮定すれば、いくつかの相互接続のために $x\%$ よりも大きいピッヂスケーリングが使用され得る。最小ピッヂスケーリングは、最小ビアピッヂ限界に基づいて決定され得る。そのようなスケーリングは、すべての相互接続について、 $x\%$ ピッヂスケーリングに勝る、コスト利益、電力利益、および性能利益の改善を与え得る。

## 【0017】

[0021] 開示したプロセスにおけるステップの特定の順序または階層は、例示的な手法の一例であることを理解されたい。設計上の選好に基づいて、プロセスにおけるステップの

10

20

30

40

50

特定の順序または階層は並べ替えられ得ることを理解されたい。さらに、いくつかのステップは組み合わされるかまたは省略され得る。添付の方法クレームは、様々なステップの要素を例示的な順序で提示したものであり、提示された特定の順序または階層に限定されるものではない。

#### 【0018】

[0022]以上の説明は、当業者が本明細書で説明された様々な態様を実行できるようにするため提供される。これらの態様に対する様々な変更は当業者には容易に明らかであり、本明細書で定義された一般原理は他の態様に適用され得る。したがって、特許請求の範囲は、本明細書に示された態様に限定されるものではなく、クレーム文言に矛盾しない全範囲を与えられるべきであり、ここにおいて、単数形の要素への言及は、そのように明記されていない限り、「唯一無二の」を意味するものではなく、「1つまたは複数の」を意味するものである。「例示的」という単語は、本明細書では「例、事例、または例示の働きをすること」を意味するために使用する。「例示的」として本明細書で説明するいかなる態様も、必ずしも他の態様よりも好適または有利なものと解釈すべきではない。別段に明記されていない限り、「いくつかの」という用語は「1つまたは複数の」を指す。「A、B、またはCのうちの少なくとも1つ」、「A、B、およびCのうちの少なくとも1つ」、および「A、B、C、またはそれらの任意の組合せ」などの組合せは、A、B、および/またはCの任意の組合せを含み、複数のA、複数のB、または複数のCを含み得る。詳細には、「A、B、またはCのうちの少なくとも1つ」、「A、B、およびCのうちの少なくとも1つ」、ならびに「A、B、C、またはそれらの任意の組合せ」などの組合せは、Aのみ、Bのみ、Cのみ、AおよびB、AおよびC、BおよびC、またはAおよびBおよびCであり得、ここで、いかなるそのような組合せも、A、B、またはCのうちの1つまたは複数の部材を含んでいることがある。当業者に知られている、または後に知られることになる、本開示全体にわたって説明した様々な態様の要素のすべての構造的および機能的均等物は、参照により本明細書に明確に組み込まれ、特許請求の範囲に包含されるものである。その上、本明細書で開示したいかなることも、そのような開示が特許請求の範囲に明示的に具陳されているかどうかにかかわらず、公に供するものではない。いかなるクレーム要素も、その要素が「そのための手段」という語句を使用して明確に具陳されていない限り、ミーンズプラスファンクションとして解釈されるべきではない。

以下に本願発明の当初の特許請求の範囲に記載された発明を付記する。

10

20

30

#### [C 1]

最小ピッチgをもつ複数のゲート相互接続と、

最小ピッチmをもつ複数の金属相互接続と、

前記ゲート相互接続と前記金属相互接続とを相互接続する複数のビアと、前記ビアが最小ピッチvを有する、を備え、

ここにおいて、 $g^2 + m^2 = v^2$ であり、gとmとの最小公倍数(LCM)が20gよりも小さい、システムオンチップ(SOC)装置。

#### [C 2]

gが約96nmであり、mが約64nmであり、vが約115nmである、C 1に記載の装置。

40

#### [C 3]

前記複数の金属相互接続が、第1の相互接続レベルまたは第2の相互接続レベルのうちの少なくとも1つ上にあり、前記ビアが、前記第1の相互接続レベルと前記第2の相互接続レベルとの間で前記金属相互接続を相互接続する、C 1に記載の装置。

#### [C 4]

前記第1の相互接続レベルが第1の金属層であり、前記第2の相互接続レベルが第2の金属層である、C 3に記載の装置。

#### [C 5]

$m_2$ の最小ピッチをもつ第2の複数の金属相互接続をさらに備え、ここにおいて、 $m_2 > m$ であり、gとmと $m_2$ との前記LCMが20gよりも小さい、C 1に記載の装置。

50

## [ C 6 ]

g が約 9 6 nm であり、m が約 7 2 nm であり、v が約 1 1 5 nm であり、 $m_2$  が約 8 0 nm である、C 5 に記載の装置。

## [ C 7 ]

前記複数の金属相互接続が第 3 の相互接続レベル上にあり、前記第 2 の複数の金属相互接続が第 5 の相互接続レベル上にあり、ここにおいて、前記ビアが、前記複数の金属相互接続と前記第 2 の複数の金属相互接続との間で金属相互接続を相互接続する、C 5 に記載の装置。

## [ C 8 ]

前記第 3 の相互接続レベルが第 3 の金属層であり、前記第 5 の相互接続レベルが第 5 の金属層である、C 7 に記載の装置。

10

## [ C 9 ]

最小ピッチ g をもつ複数のゲート相互接続に電流を流すことと、

最小ピッチ m をもつ複数の金属相互接続に電流を流すことと、

前記ゲート相互接続と前記金属相互接続とを相互接続する複数のビアに電流を流すことと、前記ビアが最小ピッチ v を有する、を備え、

ここにおいて、 $g^2 + m^2 = v^2$  であり、g と m との最小公倍数 (LCM) が 20 g よりも小さい、システムオンチップ (SOC) 装置を動作させる方法。

## [ C 10 ]

前記複数の金属相互接続が、第 1 の相互接続レベルまたは第 2 の相互接続レベルのうちの少なくとも 1 つ上にあり、前記ビアが、前記第 1 の相互接続レベルと前記第 2 の相互接続レベルとの間で前記金属相互接続を相互接続する、C 9 に記載の方法。

20

## [ C 11 ]

前記第 1 の相互接続レベルが第 1 の金属層であり、前記第 2 の相互接続レベルが第 2 の金属層である、C 10 に記載の方法。

## [ C 12 ]

$m_2$  の最小ピッチをもつ第 2 の複数の金属相互接続に電流を流すことをさらに備え、ここにおいて、 $m_2 > m$  であり、g と m と  $m_2$  との前記 LCM が 20 g よりも小さい、C 9 に記載の方法。

## [ C 13 ]

前記複数の金属相互接続が第 3 の相互接続レベル上にあり、前記第 2 の複数の金属相互接続が第 5 の相互接続レベル上にあり、ここにおいて、前記ビアが、前記複数の金属相互接続と前記第 2 の複数の金属相互接続との間で金属相互接続を相互接続する、C 12 に記載の方法。

30

## [ C 14 ]

前記第 3 の相互接続レベルが第 3 の金属層であり、前記第 5 の相互接続レベルが第 5 の金属層である、C 13 に記載の方法。

## [ C 15 ]

最小ピッチ g をもつ複数のゲート相互接続に電流を流すための手段と、

最小ピッチ m をもつ複数の金属相互接続に電流を流すための手段と、

前記ゲート相互接続と前記金属相互接続とを相互接続する複数のビアに電流を流すための手段と、前記ビアが最小ピッチ v を有する、を備え、

ここにおいて、 $g^2 + m^2 = v^2$  であり、g と m との最小公倍数 (LCM) が 20 g よりも小さい、システムオンチップ (SOC) 装置。

40

## [ C 16 ]

前記複数の金属相互接続が、第 1 の相互接続レベルまたは第 2 の相互接続レベルのうちの少なくとも 1 つ上にあり、前記ビアが、前記第 1 の相互接続レベルと前記第 2 の相互接続レベルとの間で前記金属相互接続を相互接続する、C 15 に記載の装置。

## [ C 17 ]

前記第 1 の相互接続レベルが第 1 の金属層であり、前記第 2 の相互接続レベルが第 2 の

50

金属層である、C 1 6に記載の装置。

【 C 1 8 】

$m_2$ の最小ピッチをもつ第2の複数の金属相互接続に電流を流すための手段をさらに備え、ここにおいて、 $m_2 > m$ であり、 $g$ と $m$ と $m_2$ との前記LCMが20gよりも小さい、C 1 5に記載の装置。

【 C 1 9 】

前記複数の金属相互接続が第3の相互接続レベル上にあり、前記第2の複数の金属相互接続が第5の相互接続レベル上にあり、ここにおいて、前記ビアが、前記複数の金属相互接続と前記第2の複数の金属相互接続との間で金属相互接続を相互接続する、C 1 8に記載の装置。

10

【 C 2 0 】

前記第3の相互接続レベルが第3の金属層であり、前記第5の相互接続レベルが第5の金属層である、C 1 9に記載の装置。

【図1】

図1

|     |                       |                             |

|-----|-----------------------|-----------------------------|

|     | 28nm                  | 20/16/14nm                  |

| ゲート | $g$ (e.g., 130nm)     | $g$ (e.g., 90nm (70%))      |

| M1  | $m_1$ (e.g., 90nm)    | $m_1$ (e.g., 64nm (70%))    |

| Ma  | $m_{a1}$ (e.g., 90nm) | $m_{a2}$ (e.g., 64nm (70%)) |

| Mb  | $m_b$ (e.g., 80nm)    | $m_b$ (e.g., 80nm)          |

| ビア  | $v_1$ (e.g., 130nm)   | $v_2$ (e.g., 115nm (88%))   |

FIG. 1

【図2】

図2

FIG. 2

【図3】

図3

【図4】

図4

【図5】

図5

---

フロントページの続き

(72)発明者 チェン、シャンドン

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775、クワアルコム・インコーポレイテッド気付

(72)発明者 クウォン、オーサン

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775、クワアルコム・インコーポレイテッド気付

(72)発明者 タージオグル、イージン

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775、クワアルコム・インコーポレイテッド気付

(72)発明者 ブンナリム、ハディ

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775、クワアルコム・インコーポレイテッド気付

審査官 戸次 一夫

(56)参考文献 特開平06-037279(JP,A)

特開2007-234804(JP,A)

特開2005-244978(JP,A)

特開2008-171977(JP,A)

特表2011-501876(JP,A)

国際公開第2012/053125(WO,A1)

米国特許出願公開第2013/0072020(US,A1)

米国特許第08198655(US,B1)

米国特許第07492013(US,B1)

(58)調査した分野(Int.Cl., DB名)

H01L 21/82