(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6723175号

(P6723175)

(45) 発行日 令和2年7月15日(2020.7.15)

(24) 登録日 令和2年6月25日(2020.6.25)

(51) Int.Cl.

F 1

H02M 1/08 (2006.01)

H02M 1/38 (2007.01)H02M 1/08

H02M 1/38

A

請求項の数 10 (全 14 頁)

(21) 出願番号 特願2017-25164 (P2017-25164)

(22) 出願日 平成29年2月14日 (2017.2.14)

(65) 公開番号 特開2018-133892 (P2018-133892A)

(43) 公開日 平成30年8月23日 (2018.8.23)

審査請求日 平成31年2月28日 (2019.2.28)

(73) 特許権者 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

(74) 代理人 110000062

特許業務法人第一国際特許事務所

(72) 発明者 栗原 直樹

東京都千代田区丸の内一丁目6番6号 株式会社日立製作所内

(72) 発明者 秋山 悟

東京都千代田区丸の内一丁目6番6号 株式会社日立製作所内

(72) 発明者 河野 恒彦

東京都千代田区丸の内一丁目6番6号 株式会社日立製作所内

最終頁に続く

(54) 【発明の名称】パワー半導体のゲート駆動装置およびゲート駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

制御論理部からゲートのオン指令またはゲートのオフ指令を受けてパワー半導体のゲートに印加するゲート電圧を制御するゲート駆動装置であって、

前記ゲート電圧を監視して前記パワー半導体のオン／オフの状態を判定するオン／オフ状態判定回路と、

前記ゲート電圧を、前記オン指令を受けると第一の電圧に制御し、前記オフ指令を受けると第二の電圧に制御するゲート出力回路と、

前記オン／オフ状態判定回路が出力するオフ状態の判定を検知することにより一定時間の信号を前記ゲート出力回路へ出力するタイマ回路と

10

を備え、

前記ゲート出力回路は、前記一定時間の信号を入力している間は前記ゲート電圧を前記第二の電圧よりも低い第三の電圧に制御することを特徴とするゲート駆動装置。

## 【請求項 2】

請求項 1 に記載のゲート駆動装置であって、

前記パワー半導体が有する一対の主端子から一方の主端子の電圧を検出し、当該パワー半導体のオフ後に前記検出した電圧が変化するか否かを判定する主端子電圧判定回路を更に備え、

前記タイマ回路は、前記オン／オフ状態判定回路が出力するオフ状態の判定と前記主端

20

子電圧判定回路が出力する前記検出した電圧が変化しないことの判定とを検知することにより、前記一定時間の信号を前記ゲート出力回路へ出力することを特徴とするゲート駆動装置。

【請求項3】

請求項1に記載のゲート駆動装置であって、

前記パワー半導体が有する一対の主端子のいずれか一方の主端子に寄生するインダクタ

ンスに発生する起電圧を検出し、前記パワー半導体の主電流の変化の有無を判定する電流

判定回路を更に備え、

前記タイマ回路は、前記オン／オフ状態判定回路が出力するオフ状態の判定と前記電流

判定回路が出力する前記主電流が変化しないことの判定とを検知することにより、前記一

定時間の信号を前記ゲート出力回路へ出力する

ことを特徴とするゲート駆動装置。

10

【請求項4】

請求項1～3のいずれか1項に記載のゲート駆動装置であって、

当該ゲート駆動装置は、前記パワー半導体を上アームおよび下アームに備えて構成した

電力変換装置を駆動し、

前記タイマ回路は、前記上アームおよび前記下アームが備える前記パワー半導体各々の

オン／オフに伴うデッドタイムを一定にした状態で、前記一定時間の信号を前記ゲート出

力回路へ出力するタイミングを調整する

ことを特徴とするゲート駆動装置。

20

【請求項5】

請求項1～4のいずれか1項に記載のゲート駆動装置であって、

前記パワー半導体は、シリコンカーバイドで構成した半導体である

ことを特徴とするゲート駆動装置。

【請求項6】

パワー半導体のゲート電圧を制御するゲート駆動方法であって、

前記パワー半導体のゲートにオン指令が印加されると前記パワー半導体のゲート電圧を

第一の電圧に制御し、

前記ゲート電圧を監視して前記パワー半導体のオン／オフの状態を判定し、

前記パワー半導体のゲートにオフ指令が印加されると前記ゲート電圧を第二の電圧に制

御すると共に、前記オン／オフのオフ状態を判定すると一定時間の間は前記ゲート電圧を

前記第二の電圧よりも低い第三の電圧に制御する

ことを特徴とするゲート駆動方法。

30

【請求項7】

請求項6に記載のゲート駆動方法であって、

前記パワー半導体が有する一対の主端子から一方の主端子の電圧を検出することで、当

該パワー半導体のオフ後に前記検出した電圧が変化するか否かを判定し、

前記オフ状態を判定しつつ前記検出した電圧が変化しないことを判定することにより、

前記一定時間の間は前記ゲート電圧を前記第二の電圧よりも低い前記第三の電圧に制御す

る

ことを特徴とするゲート駆動方法。

40

【請求項8】

請求項6に記載のゲート駆動方法であって、

前記パワー半導体が有する一対の主端子のいずれか一方の主端子に寄生するインダクタ

ンスに発生する起電圧を検出することで、前記パワー半導体の主電流が変化するか否かを

判定し、

前記オフ状態を判定しつつ前記主電流が変化しないことを判定することにより、前記一

定時間の間は前記ゲート電圧を前記第二の電圧よりも低い前記第三の電圧に制御す

ることを特徴とするゲート駆動方法。

【請求項9】

50

請求項 6～8 のいずれか 1 項に記載のゲート駆動方法であって、

当該ゲート駆動方法により、前記パワー半導体を上アームおよび下アームに備えて構成

した電力変換装置を駆動し、

前記上アームおよび前記下アームが備える前記パワー半導体各々のオン／オフに伴うデ

ッドタイムを一定にした状態で、前記一定時間を設定するタイミングを調整する

ことを特徴とするゲート駆動方法。

【請求項 10】

請求項 6～9 のいずれか 1 項に記載のゲート駆動方法であって、

前記パワー半導体として、シリコンカーバイドで構成した半導体を対象とする

ことを特徴とするゲート駆動方法。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、インバータ、コンバータあるいは直流チョッパ回路等の電力変換装置に用い

られるパワー半導体のゲート駆動装置およびゲート駆動方法に関する。

【背景技術】

【0002】

直流電力を交流電力に変換するインバータ、交流電力を直流電力に変換するコンバータ

あるいは直流電圧の昇圧や降圧を行う直流チョッパ回路等の電力変換装置では、IGBT

等のパワー半導体素子が広く使われている。このパワー半導体素子は、ゲート駆動装置から

のオン／オフ信号により駆動される。ゲート駆動装置は、電力変換装置のコントローラ

である制御論理部からの信号により制御されている。

20

【0003】

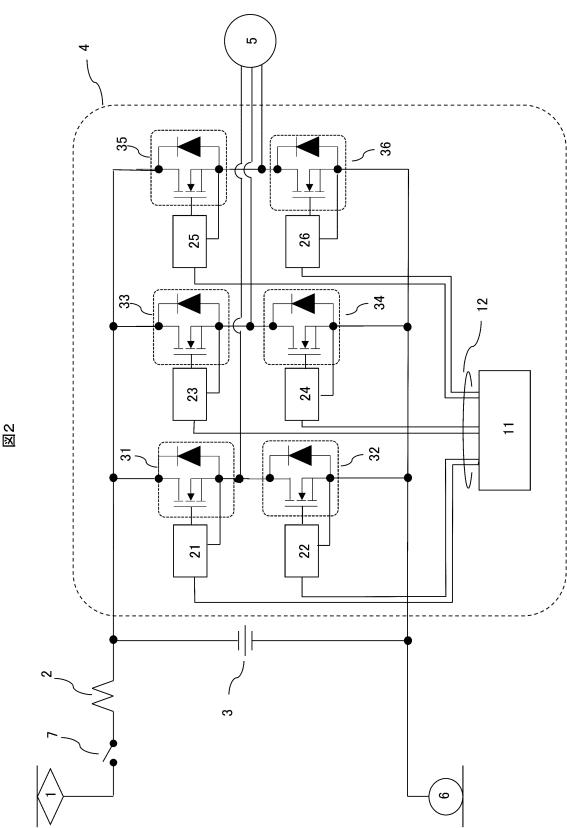

ゲート駆動装置を使用する一例として、図 2 に、鉄道車両用電力変換装置として用いる

2 レベルインバータの全体構成を示す。

電力変換装置 4 は、制御論理部 11、ゲート駆動装置 21～26、制御論理部 11 とゲ

ート駆動装置 21～26 を接続する信号線 12 およびパワー半導体 31～36 から構成さ

れる。プラス電源線はパンタグラフ 1 を介して架線に接続され、マイナス電源線は車輪 6

を介してレールに接続されている。フィルタリアクトル 2 とフィルタコンデンサ 3 は、數

十 Hz で動作する軌道回路（図示せず）が電力変換装置 4 の動作による誘導障害で誤動作

しないために、設けている。また、遮断機 7 は、過電流および過電圧が発生した際に電源

を遮断し電力変換装置 4 を保護するために、設けている。

30

【0004】

次に、電力変換装置 4 の動作を説明する。ゲート駆動装置 21～26 は、制御論理部 1

1 から送信されたパワー半導体 31～36 のオン／オフ指令に基づき、オン指令の場合にはソース

に対してゲートに正の電圧を、オフ指令の場合にはソースに対してゲートに負の

電圧を、出力する。パワー半導体 31～36 は、ゲート駆動装置 21～26 から出力され

る前記電圧に応じて導通／非導通を繰り返すことで、架線から供給される直流電力をバル

ス列の交流電力に変換して、交流モータ 5 を駆動する。

40

【0005】

近年、環境負荷の低減という大きな社会潮流の中で、電力変換装置の高効率化や低損失

化の要求が高まっている。この要求に応える方法として、従来のシリコン製パワー半導

体素子に代わって、バンドギャップの大きいシリコンカーバイド（SiC）やガリウムナ

イトライド（GaN）で構成したパワー半導体を用いた電力変換装置が普及しつつある。こ

れらのバンドギャップの大きいパワー半導体では、絶縁耐圧がシリコン製パワー半導体の

10 倍程度あるため、半導体のチップの厚みを 1/10 程度に小さくできる。このため、

導通時の抵抗は 1/10 程度に下がり、導通損失を小さくできるという特長を持つ。

【先行技術文献】

【特許文献】

50

## 【0006】

【特許文献1】特開2013-219874号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0007】

電力変換装置の高効率化や低損失化の要求を満たすために、上述のSiCで構成したパワー半導体を用いるに際して、SiCのMOSゲート型パワー半導体は、ゲートに負の電圧を出力するオフ状態時に所定の電圧よりも低い電圧を長時間印加すると、閾値が負側にシフトするという問題がある。例えば、閾値が4VのSiCのMOSFETの場合には、長時間の負バイアスにより閾値が1V低下して3Vになる。閾値が負側にシフトすると、インバータの対となるアームのダイオードが、リバースリカバリする際のドレイン電圧の急峻な変動でゲート電圧も変動し、MOSFETが誤オノンすることにより、上下アームのSiCパワー半導体素子がアーム短絡（同時にオンする現象）を起こす恐れがある。ゲート電圧のシフトは、ゲートの負バイアスの大きさに依存して大きくなるため、極力負バイアスを小さくして使うことが望ましい。しかし、負バイアスが小さいと、上述したリカバリの際に、ゲート電圧が変動すると誤オノンするリスクが高まるため、単純に小さくすることはできない。この対策として、例えば、特許文献1（特開2013-219874号公報）には、リカバリ時だけ負バイアス電圧を低くし、上述した閾値のシフトの問題を解決する技術が開示されている。

## 【0008】

また、鉄道用電力変換器のように、変換する電圧が600～3000Vと高い場合、装置の信頼性を確保するため、低電圧で動作する制御論理部と高電圧の主回路に接続して動作させるゲート駆動装置間、および、上下アームで対となっているゲート駆動装置間、の信号伝送は、光ファイバやフォトカプラ等の絶縁素子を介する必要がある。

## 【0009】

上述した特許文献1に開示された技術では、上下アームのうちの一方のアームのオン指令をトリガとして、負バイアス電圧を通常より低くしている。しかし、この方式では、制御論理部とゲート駆動装置との間で伝送するオン／オフ指令のほかに、制御論理部とゲート駆動装置間、または一方のゲート駆動装置と対となるアームのゲート駆動装置間で、新たにオン／オフ指令を伝送する手段が必要となる。このため、信号線や絶縁素子などで構成される信号送受信回路を新たに設ける必要があり、装置が大型化するという課題があった。

## 【課題を解決するための手段】

## 【0010】

ゲート出力回路により、パワー半導体のゲートに印加するゲート電圧をゲートのオン指令を受けると第一の電圧に制御しゲートのオフ指令を受けると第二の電圧に制御し、オン／オフ状態判定回路により、ゲート電圧を監視してパワー半導体のオン／オフの状態を判定し、タイマ回路により、オン／オフ状態判定回路が outputするオフ状態の判定を検知することにより一定時間の信号をゲート出力回路へ出力し、ゲート出力回路は、一定時間の信号を入力している間はゲート電圧を第二の電圧よりも低い第三の電圧に制御する。

## 【発明の効果】

## 【0011】

本発明によれば、制御論理部とゲート駆動装置間およびゲート駆動装置と対となるアームのゲート駆動装置間の絶縁素子を介した信号伝達経路を新たに追加することなく、リカバリ時のみ負バイアスを低くすることが可能となり、パワー半導体素子の劣化を抑制しながら装置の大型化を伴わない、高信頼で小型の電力変換装置を提供する。

## 【図面の簡単な説明】

## 【0012】

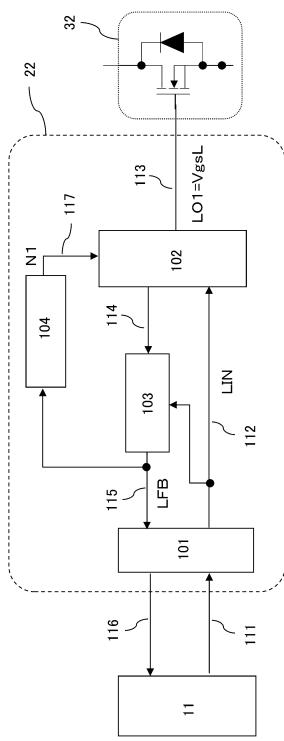

【図1】図1は、本発明に係るゲート駆動装置の実施例1の構成を示すブロック図である。

10

20

30

40

50

【図2】図2は、鉄道車両用電力変換装置として用いる2レベルインバータの全体構成図を示す図である。

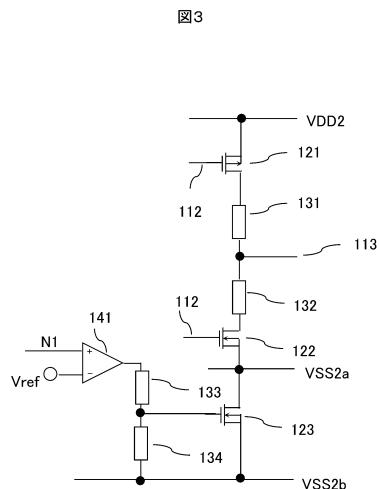

【図3】図3は、実施例1のゲート出力回路の具体的構成例を示す図である。

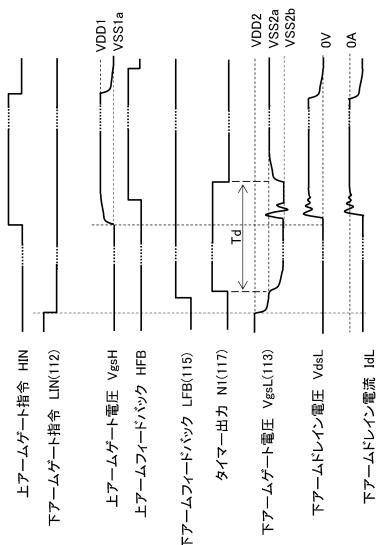

【図4】図4は、実施例1によるリカバリ時の動作態様をタイムチャートで示した図である。

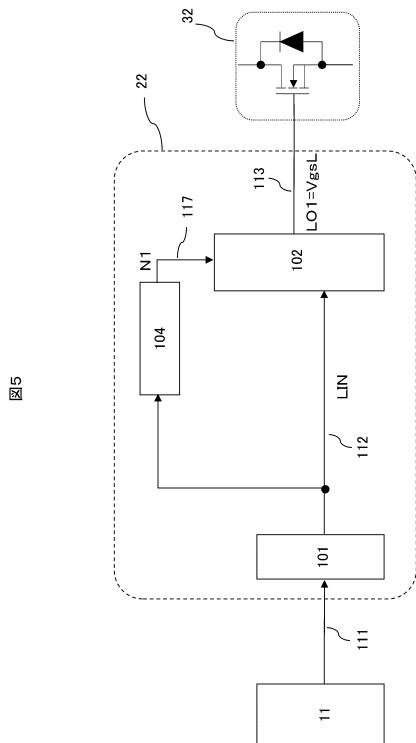

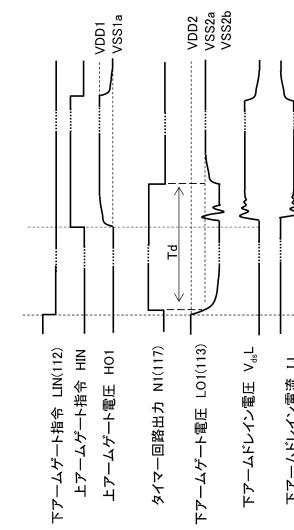

【図5】図5は、本発明に係るゲート駆動装置の実施例2の構成を示す図である。

【図6】図6は、実施例2によるリカバリ時の動作態様をタイムチャートで示した図である。

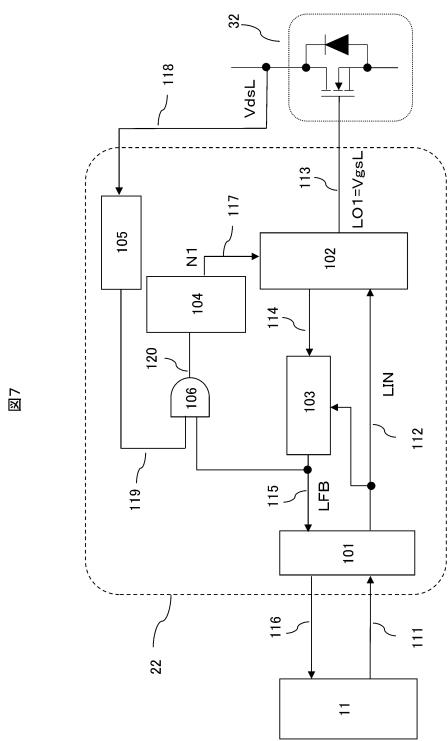

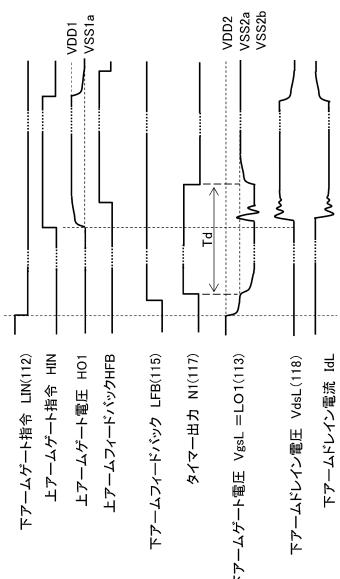

【図7】図7は、本発明に係るゲート駆動装置の実施例3の構成を示す図である。

【図8】図8は、実施例3におけるターンオフ後にゲート電圧をV<sub>SS2b</sub>に下げる場合のタイムチャートを示す図である。 10

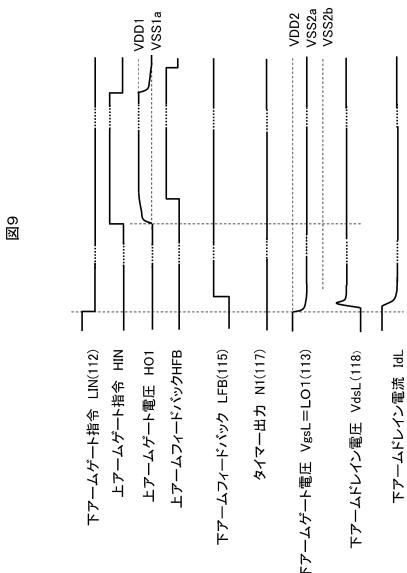

【図9】図9は、実施例3におけるターンオフ後にゲート電圧をV<sub>SS2b</sub>に下げない場合のタイムチャートを示す図である。

【図10】図10は、本発明に係るゲート駆動装置の実施例4の構成を示す図である。

【図11】図11は、実施例4の構成要素である電流検知回路を示す図である。

【図12】図12は、実施例4におけるターンオフ後にゲート電圧をV<sub>SS2b</sub>に下げる場合のタイムチャートを示す図である。

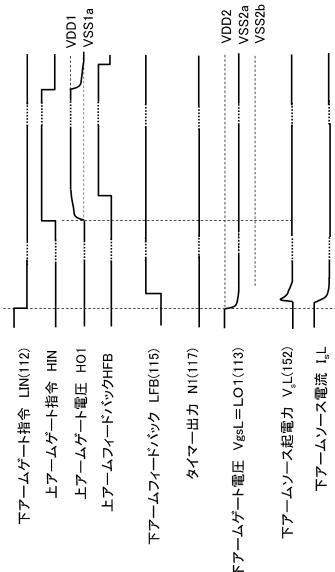

【図13】図13は、実施例4におけるターンオフ後にゲート電圧をV<sub>SS2b</sub>に下げない場合のタイムチャートを示す図である。

【図14】図14は、ターンオフ後に対アームのターンオンする時間を予測し必要最小限の時間のみゲート電圧をV<sub>SS2b</sub>に下げる場合のタイムチャートを示す図である。 20

#### 【発明を実施するための形態】

##### 【0013】

本発明を実施するための形態として、本発明に係るゲート駆動装置の実施例1～4について、図を参照しながら以下に説明する。

##### 【実施例1】

##### 【0014】

図1は、本発明に係るゲート駆動装置の実施例1の構成を示すブロック図である。実施例1は、リカバリ時のみ負のバイアス電圧を引き下げる機能を奏するものである。

ゲート駆動装置22は、ゲートオン／オフ指令111をレベル変換するゲート指令レベル変換回路101、ゲート指令レベル変換回路101でレベル変換されたゲートオン／オフ指令L<sub>IN</sub>(112)およびタイマ回路104の出力を受けてゲート出力電圧L<sub>O1</sub>(113)をパワー半導体素子のゲートに出力するゲート出力回路102、ゲート出力回路102によるゲート電圧監視信号114からパワー半導体素子のゲートの状態を判定するオン／オフ状態判定回路103およびオン／オフ状態判定回路103の出力であるフィードバック信号L<sub>FB</sub>(115)により一定時間タイマ回路出力N1(117)を駆動するタイマ回路104、から構成される。 30

##### 【0015】

ゲート駆動装置22には、制御論理部11から出力されたゲートオン／オフ指令111が、絶縁素子(図示せず)を介してゲート指令レベル変換回路101に入力される。このオン／オフ指令111は、ゲート指令レベル変換回路101でSiCパワー半導体32を駆動できる振幅レベルにレベル変換されたゲートオン／オフ指令L<sub>IN</sub>(112)となる。ゲート出力回路(102)は、受け取ったゲートオン／オフ指令L<sub>IN</sub>(112)に基づいたゲート電圧L<sub>O1</sub>(113)をSiCパワー半導体32のベースに出力する。 40

##### 【0016】

また、ゲート出力回路102から出力されたゲート電圧監視信号114は、オン／オフ状態判定回路(103)で基準電圧と比較され、基準電圧以上ならばフィードバック信号L<sub>FB</sub>(115)はオン信号として出力され、基準電圧以下ならばフィードバック信号L<sub>FB</sub>(115)はオフ信号として出力される。ゲート指令レベル変換回路(101)でレベル変換したフィードバック信号116は、制御論理部(11)に送信される。 50

## 【0017】

なお、制御論理部11とゲート駆動装置22間を光ファイバで接続した場合には、ゲート指令レベル変換回路101はゲート指令111およびフィードバック信号115の振幅を変換するだけである。一方、制御論理部11とゲート駆動装置22間を電線で接続した場合には、低電圧で駆動する制御論理部11と高電圧で駆動するSiCパワー半導体32およびゲート出力回路102を絶縁する機能をゲート指令レベル変換回路101に設けることになる。

## 【0018】

本実施例1の特徴は、フィードバック信号LFB(115)をトリガとして、リカバリ時の負バイアス電圧を通常時のオフ電圧よりも下げ、リカバリ終了後には負バイアス電圧を通常時のオフ電圧に戻すことにある。これにより、対アームからのオン／オフの情報無しで、ゲートの負バイアスをリカバリ時のみ引き下げるこ<sup>10</sup>と可能にする。

## 【0019】

図3は、実施例1のゲート電圧出力回路102の具体的構成例を示す図である。ゲート電圧出力回路102は、3台のMOSトランジスタ121、122および123、SiCパワー半導体32のスイッチング特性を制御するためのゲート抵抗131および132、MOSトランジスタ123をオンさせるためのバイアス抵抗133および134、並びに、タイマ回路104の出力N1(117)と基準電圧Vrefとを比較する負バイアス切替コンパレータ141から構成される。

## 【0020】

ゲート指令112がオンの場合は、MOSトランジスタ121がオンしてゲート出力電圧LO1(113)は正のバイアス電圧VDD2となり、ゲート指令112がオフの場合は、MOSトランジスタ122がオンして、ゲート出力電圧LO1(113)は負のバイアス電圧VSS2aとなる。なお、図3では、トランジスタ121～123は、MOSトランジスタの場合を示しているが、バイポーラトランジスタとした場合でも同じ効果が得られることは明白である。

## 【0021】

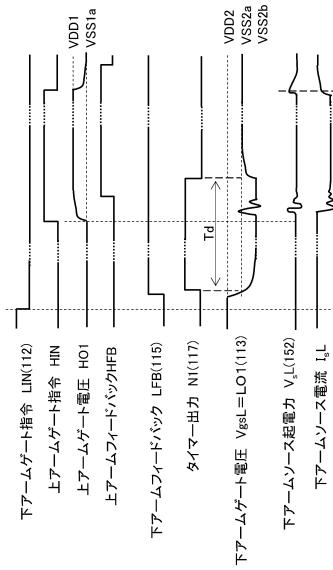

次に、リカバリ時の動作態様を、図4のタイムチャートを使って説明する。図4は、インバータ側から負荷側に電流が流れ出している状態での各部の動作波形を示した図である。図4で初めて示す信号として、HINは上アームのゲートオン／オフ指令、VgsHは上アームのゲート電圧、HFBは上アームのフィードバック信号、VdSLは下アームのドレイン-ソース間電圧、IdLは下アームのドレイン電流を示し、ドレインからソースに向かって電流が流れる場合を正とする。

## 【0022】

下アームのゲートオン／オフ指令LIN(112)が、ゲートオフ指令によりLレベルとなると、ゲート電圧VgsL(113)は、正のバイアス電圧VDD2から負のバイアス電圧VSS2aに変化するが、パワー半導体を構成するMOSFETと逆並列接続されているフリー・ホイル・ダイオードに電流が流れているため、下アームのドレイン電圧VdS<sup>30</sup>Lとドレイン電流IdLは変化しない。この状態は、電力変換装置4から交流モータ5に向かってモータ電流が流れ、下アームのSiCパワー半導体32では、パワー半導体を構成するMOSFETではなく逆並列されているフリー・ホイル・ダイオードに電流が流れるモードである。しかし、ゲート電圧VgsL(113)が負バイアス電圧VSS2aとなることで、ゲート駆動装置22内のオン／オフ状態判定回路103はターンオフしたと判断し、フィードバック信号LFB(115)はターンオフ状態のHレベルの信号に変化する。フィードバック信号LFB(115)がHレベルに変化すると、タイマ回路104が動作し、一定時間TdだけHレベルとなる信号N1(117)を出力する。

## 【0023】

信号N1(117)のHレベルがVrefより高くなると、コンパレータ141(図3)の出力はLレベルからHレベルとなり、MOSトランジスタ123がオンする。これにより、ゲート出力電圧LO1(113)の負バイアス電圧は、VSS2aからVSS2b

10

20

30

40

50

に下がる。上アームのSiCパワー半導体31がターンオンすると、下アームのSiCパワー半導体32はリバースリカバリし、急激なドレイン電圧V<sub>dsL</sub>の変化により下アームのゲート電圧V<sub>gSL</sub>(113)が一瞬上昇する。しかしながら、ゲート電圧V<sub>gSL</sub>はV<sub>SS2b</sub>まで引き下げられているため、パワー半導体を構成するMOSFETの閾値には達せず、パワー半導体を構成するMOSFETが誤オンすることは無い。リカバリ動作が終了し、タイマ回路104の出力N1(117)がHレベルである時間T<sub>d</sub>が経過すると、N1(117)の出力がLレベルとなりV<sub>ref</sub>より低くなる。これにより、コンパレータ141がオフし、ゲート出力電圧LO1(113)の負バイアス電圧はV<sub>SS2a</sub>に戻る。

## 【0024】

10

本実施例1によると、上述したように、簡素なシステム構成でリカバリ時の誤点弧を防止するとともに、しきい値V<sub>th</sub>のシフトを防止し、パワー半導体素子の劣化を抑制し該素子の寿命を延ばすことを可能にする。これにより、信頼性を保ちつつゲート駆動装置の大型化を防ぐことができる。

## 【0025】

上述の構成としては、例えば通常のオフ時電圧V<sub>SS2a</sub>は-5Vとし、タイマ回路104がHレベルを出す時間T<sub>d</sub>は、ゲート出力回路102の出力が変化してから対アームのゲート出力回路102の出力が変化するまでのデットタイムとリカバリ時間の合計で決まる5μs～10μs程度である。この期間のみ、負バイアス電圧V<sub>SS2b</sub>を-10Vに下げる。但し、ノイズの影響が極めて少ない環境では、V<sub>SS2a</sub>は0V、V<sub>SS2b</sub>は-3Vとすることで、SiCパワー半導体素子の劣化をさらに抑制することができる。

20

## 【0026】

以上においては、SiCパワー半導体を例に説明したところ、負バイアスを長時間印加するとパワー半導体素子の閾値電圧V<sub>th</sub>が負側にシフトし、劣化するパワー半導体素子すべてに対して有効である。

## 【実施例2】

## 【0027】

30

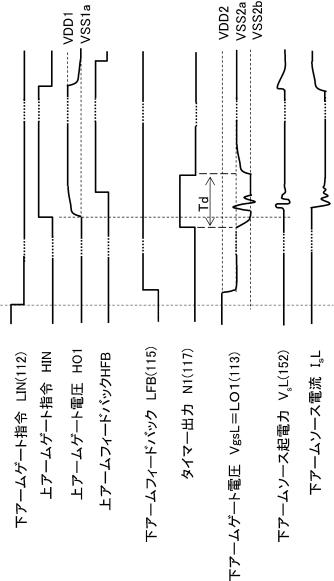

図5は、本発明に係るゲート駆動装置の実施例2の構成を示す図である。図1に示す実施例1の構成と異なる点は、ゲート駆動装置22にオンオフ状態判定回路103を設けず、制御論理部11にオン／オフ状態のフィードバック信号116を伝送する機能を有しない点である。このため、図6のタイムチャートに示すように、下アームのゲートオン／オフ指令LIN(112)のオフを検知すると、タイマ回路104は、無条件に一定時間T<sub>d</sub>だけHレベルとなる信号N1(117)を出力する。

## 【0028】

本実施例2の特徴は、上位のコントローラである制御論理部11にフィードバック信号116を伝送しない簡易なシステム構成であっても、ゲート駆動装置22の信号だけでリカバリ時の負バイアス電圧を下げることができるることである。

## 【実施例3】

## 【0029】

40

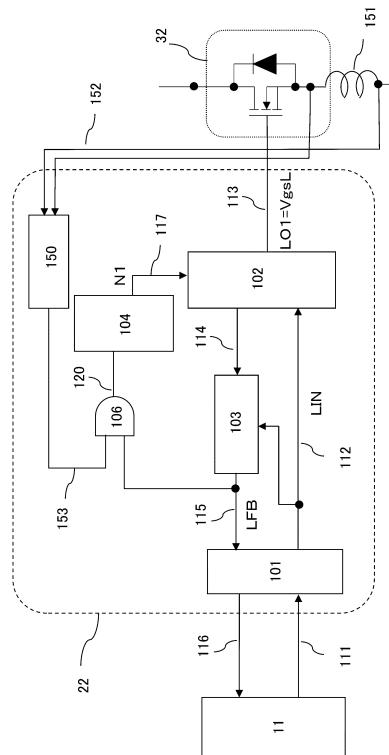

図7は、本発明に係るゲート駆動装置の実施例3の構成を示す図である。図1に示す実施例1の構成と異なる点は、ゲート駆動装置22にドレイン電圧を監視する機能が追加され、構成要素として、ドレイン電圧判定回路105およびAND機能によるタイマ計測開始回路106が追加されている点である。以下に、図8および図9のタイムチャートによって、本実施例3の動作態様を説明する。

## 【0030】

図8は、下アームのSiCパワー半導体32がリカバリする場合のタイムチャートを示す図である。制御論理部11からの下アームのゲートオン／オフ指令LIN(112)がオフになると、ゲート出力電圧LO1(113)がV<sub>SS2a</sub>に低下するが、ドレインソース間電圧V<sub>dsL</sub>やドレイン電流I<sub>dL</sub>は変化しない。この状態は、電力変換装置4から交流モータ5に向かってモータ電流が流れ、下アームのSiCパワー半導体32では、

50

パワー半導体を構成するMOSFETではなく逆並列されているフリーホイルダイオードに電流が流れるモードである。このため、ゲート出力電圧が正バイアス電圧VDD2から負バイアス電圧VSS2aに変わっても、動作様様（ドレインソース間電圧VdSLやドレイン電流IdL）に変化はないことになる。

#### 【0031】

このモードでは、フィードバック信号LFB(115)がターンオフ状態を検知しても、ドレインソース間電圧VdSL(118)が変化しないことをドレイン電圧判定回路105が検知する。これにより、ドレイン電圧判定回路105はHレベルのドレイン電圧L0wレベル検出信号119を出力し、タイマ計測開始回路106によりフィードバック信号LFB(115)とのANDがとられ、タイマ回路104に入力される。タイマ回路104から一定時間TdだけHレベルの信号が出力され、ゲート出力電圧LO1(113)の負バイアス電圧をVSS2bに下げる。

#### 【0032】

次に、図9は、下アームのSiCパワー半導体32がリカバリしない場合のタイムチャートを示す図である。図8のタイムチャートとの違いは、図2において交流モータ5から電力変換装置4に向かってモータ電流が流れるモード（回生モード）である点である。このモードでは、下アームゲート指令がオフになると、ゲート出力電圧LO1(113)がVSS2aに低下し、ドレインソース間電圧VdSLは上昇、ドレイン電流IdLは減少する。この時、ドレイン電圧判定回路105は、VdSLの上昇を検知して、Lレベルのドレイン電圧L0wレベル検出信号119を出力し、タイマ回路104を動作させない。このため、ゲート出力電圧LO1(113)はVSS2aのままとなる。

#### 【0033】

以上のとおり、本実施例3の特徴は、リカバリ動作しないモードでは閾値のシフトの原因となる負バイアス電圧をVSS2bに下げることを行わないため、パワー半導体素子の劣化をより防ぐことができる。

#### 【0034】

上述のタイムチャートでは、フィードバック信号LFB(115)の変化はVdSLが変化するよりも遅い場合を想定したが、逆の場合もあり得る。この場合は、フィードバック信号LFB(115)の変化より一定時間経過した後のドレインソース間電圧VdSLの状態をドレイン電圧判定回路105で判定して、ドレイン電圧L0wレベル検出信号119を出力し、タイマ回路104の動作を決めることがある。これにより、フィードバック信号LFB(115)の変化がVdSLの変化よりも速い場合でも、上述と同様に、ゲート出力電圧LO1(113)をコントロールすることができ、パワー半導体素子の劣化をより防ぐことができる。

#### 【実施例4】

#### 【0035】

図10は、本発明に係るゲート駆動装置の実施例4の構成を示す図である。図1に示す実施例1の構成と異なる点は、ゲート駆動装置22にSiCパワー半導体に電流が流れた際にソース寄生インダクタンス151に発生する起電圧を監視する機能が追加され、構成要素として、電流検知回路150およびAND機能によるタイマ計測開始回路106が追加されている点である。

#### 【0036】

本実施例4では、電流検知回路150によりソース寄生インダクタンス151に発生する起電圧を検知することにより、SiCパワー半導体32のソース電流IsLが監視できる。電流検知回路150は、ソース電流IsLの変化を検知するとターンオフ検出信号153を出力し、タイマ計測開始回路106によりフィードバック信号LFB(115)とのANDをとり、負バイアス電圧切替指令120をタイマ回路104に入力する。

#### 【0037】

図12のタイムチャートに示すように、制御論理部11からのゲートオフ指令によって下アームのSiCパワー半導体32がターンオフ指令を受けた後、ソース電流IsLに変

10

20

30

40

50

化が無い場合にはリカバリが発生すると判断し、一定期間負バイアス V<sub>SS2b</sub> を掛ける。これにより、SiC パワー半導体 32 のゲート電圧が持ち上がり誤点弧することを防止する。

#### 【0038】

一方、図 13 のタイムチャートに示すように、制御論理部 11 からのゲートオフ指令によって下アームの SiC パワー半導体 32 がターンオフ指令を受けた後、ソース電流 I<sub>S</sub> に変化がある（図 2 の交流モータ 5 から電力変換装置 4 に向かってモータ電流が流れるモード（回生モード）である）場合には、リカバリは発生しないと判断し、SiC パワー半導体 32 には負バイアス V<sub>SS2b</sub> を掛けないように機能する。これにより、SiC パワー半導体 32 の劣化を抑えることができる。

10

#### 【0039】

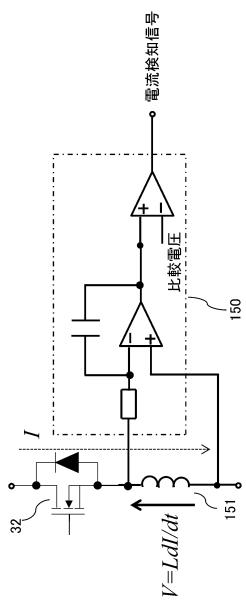

図 11 は、電流検知回路 150 の基本的構成例を示す図である。電流検知回路 150 は、電流変化により  $V = L di/dt$ （V は電圧、L はインダクタンス、i は電流）の起電圧が発生することを利用して電流を検知する。図 11 に示す回路構成により、ノイズの影響を抑えて誤動作を防止する。

#### 【0040】

以上のとおり、本実施例 4 では、ソース寄生インダクタンスに発生する起電圧を利用したところ、ドレイン寄生インダクタンスに発生する起電圧を利用して同様の仕組みで負バイアス時間を制御することができる。

20

また、カレントトランジスタやロゴスキーコイルといった絶縁された電流 / 電圧変換部品を使用することで SiC パワー半導体 32 の電流変化を捉える手法によっても、同様の仕組みで負バイアス時間を制御できる。カレントトランジスタやロゴスキーコイル等は絶縁されているため、ゲート駆動装置のサイズに大きな影響を与えることはない。

#### 【0041】

次に、より SiC パワー半導体の劣化を抑制するための手法を、図 14 を用いて説明する。ゲート電圧に負バイアス V<sub>SS2b</sub> を印加する時間は短い方が、SiC パワー半導体の劣化につながる閾値電圧の変化を抑えることができる。そのためには、負バイアス時間を極力短くすることが望ましい。これを実現するためには、下アームのゲートへのオン / オフ指令 L<sub>IN</sub> (102) が変化してから、上アームのゲートへのオン / オフ指令 H<sub>IN</sub> が変化する時間（デットタイム）を一定とすることで、ゲート駆動装置 22 はリカバリが発生するタイミングが予測できる。すなわち、フィードバック信号 L<sub>FB</sub> (115) が変化してから負バイアスを印加するのではなく、タイマ回路 104 でタイミングを調整することでリカバリが発生するタイミングに絞って、より短い時間負バイアスを印加するようになる。この手法は、先に示した実施例 1 ~ 4 の全てに適用することができる。

30

#### 【符号の説明】

#### 【0042】

1 ... パンタグラフ、2 ... フィルタリアクトル、3 ... フィルタコンデンサ、

4 ... 電力変換装置、5 ... 交流モータ、6 ... 車輪、

11 ... 制御論理部、12 ... 制御指令信号線、

21 ... U 層上アームゲートドライバ、22 ... U 層下アームゲートドライバ、

40

23 ... V 層上アームゲートドライバ、24 ... V 層下アームゲートドライバ、

25 ... W 層上アームゲートドライバ、26 ... W 層下アームゲートドライバ、

31 ... U 層上アーム SiC パワー半導体、32 ... U 層下アーム SiC パワー半導体、

33 ... V 層上アーム SiC パワー半導体、34 ... V 層下アーム SiC パワー半導体、

35 ... W 層上アーム SiC パワー半導体、36 ... W 層下アーム SiC パワー半導体、

101 ... ゲート指令レベル変換回路、102 ... ゲート電圧出力回路、

103 ... オン / オフ状態判定回路、104 ... タイマ回路、

105 ... ドレイン電圧判定回路、106 ... タイマ計測開始回路、

111 ... 制御論理部から受信されるオン / オフ指令、

112 ... レベル変換されたゲートオン / オフ指令 L<sub>IN</sub>、

50

1 1 3 ... ゲート出力電圧 L O 1、 1 1 4 ... ゲート電圧監視信号、

1 1 5 ... フィードバック信号 L F B、 1 1 6 ... 制御論理部に送信するフィードバック信号

,

1 1 7 ... タイマ回路出力 N 1、 1 1 8 ... ドレイン - ソース間電圧検知信号、

1 1 9 ... ドレイン電圧 L o w レベル検出信号、 1 2 0 ... 負バイアス電圧切替指令、

1 2 1、 1 2 2、 1 2 3 ... M O S トランジスタ、 1 3 1、 1 3 2 ... ゲート抵抗、

1 3 3、 1 3 4 ... バイアス抵抗、 1 4 1 負バイアス切替コンパレータ

1 5 0 ... 電流検知回路、 1 5 1 ... ソース寄生インダクタンス、

1 5 2 ... ソース寄生インダクタンスによる起電圧検知信号、 1 5 3 ... ターンオフ検出信号

【 四 1 】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

図11

【図 1 3】

図13

【図 1 2】

図12

【図 1 4】

図14

---

フロントページの続き

(72)発明者 小西出 政臣

東京都千代田区丸の内一丁目6番6号 株式会社日立製作所内

審査官 土井 悠生

(56)参考文献 特開2016-167498 (JP, A)

米国特許第05408150 (US, A)

特開2005-045590 (JP, A)

特開2016-092884 (JP, A)

特開2008-278552 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H02M 1/00 - 1/44

H03K 17/00 - 17/70