(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4942998号

(P4942998)

(45) 発行日 平成24年5月30日(2012.5.30)

(24) 登録日 平成24年3月9日(2012.3.9)

|               |           |              |         |

|---------------|-----------|--------------|---------|

| (51) Int.Cl.  | F 1       |              |         |

| HO 1 L 27/04  | (2006.01) | HO 1 L 27/04 | D       |

| HO 1 L 21/822 | (2006.01) | HO 1 L 27/04 | L       |

| HO 1 L 21/82  | (2006.01) | HO 1 L 21/82 | L       |

| HO 1 L 29/786 | (2006.01) | HO 1 L 29/78 | 6 1 3 Z |

| GO 6 K 19/07  | (2006.01) | GO 6 K 19/00 | H       |

請求項の数 7 (全 23 頁) 最終頁に続く

|              |                               |                 |           |

|--------------|-------------------------------|-----------------|-----------|

| (21) 出願番号    | 特願2005-370476 (P2005-370476)  | (73) 特許権者       | 000153878 |

| (22) 出願日     | 平成17年12月22日 (2005.12.22)      | 株式会社半導体エネルギー研究所 |           |

| (65) 公開番号    | 特開2006-203187 (P2006-203187A) | 神奈川県厚木市長谷398番地  |           |

| (43) 公開日     | 平成18年8月3日 (2006.8.3)          | (72) 発明者        | 加藤 清      |

| 審査請求日        | 平成20年10月6日 (2008.10.6)        | 神奈川県厚木市長谷398番地  | 株式会社      |

| (31) 優先権主張番号 | 特願2004-374913 (P2004-374913)  | 半導体エネルギー研究所内    |           |

| (32) 優先日     | 平成16年12月24日 (2004.12.24)      | (72) 発明者        | 守屋 芳隆     |

| (33) 優先権主張国  | 日本国 (JP)                      | 神奈川県厚木市長谷398番地  | 株式会社      |

|              |                               | 半導体エネルギー研究所内    |           |

審査官 増山 慎也

最終頁に続く

(54) 【発明の名称】半導体装置及び半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に設けられた素子形成層と、前記素子形成層に電気的に接続されたアンテナとを有し、

前記素子形成層と前記アンテナとは少なくとも一部が重なるように設けられ、

前記素子形成層は、複数のトランジスタを有し、

前記複数のトランジスタを用いて、電源回路及び機能回路を構成し、

前記電源回路と、前記機能回路との間で十字形状となるように、接地配線が設けられ、

前記電源回路と、前記機能回路とを囲んでコの字形状となるように、電源配線が設けられたことを特徴とする半導体装置。

## 【請求項 2】

基板上に設けられた素子形成層と、前記素子形成層に電気的に接続されたアンテナとを有し、

前記素子形成層と前記アンテナとは少なくとも一部が重なるように設けられ、

前記素子形成層は、複数のトランジスタを有し、

前記複数のトランジスタのソース電極又はドレイン電極の一方と電気的に接続される導電膜とを有し、

前記複数のトランジスタを用いて、電源回路及び機能回路を構成し、

前記電源回路と、前記機能回路との間で十字形状となるように、接地配線が設けられ、

前記電源回路と、前記機能回路とを囲んでコの字形状となるように、電源配線が設けら

10

20

れ、

前記接地配線及び前記電源配線は、前記導電膜と同一層に設けられたことを特徴とする半導体装置。

【請求項 3】

基板上に設けられた素子形成層と、前記素子形成層に電気的に接続されたアンテナとを有し、

前記素子形成層と前記アンテナとは少なくとも一部が重なるように設けられ、

前記素子形成層は、複数のトランジスタを有し、

前記複数のトランジスタのソース電極又はドレイン電極の一方と電気的に接続される導電膜とを有し、

10

前記複数のトランジスタを用いて、電源回路及び第1乃至第3の機能回路を構成し、

前記電源回路と前記第1の機能回路との間、前記電源回路と前記第2の機能回路との間、前記第1の機能回路と前記第3の機能回路との間、及び前記第2の機能回路と前記第3の機能回路との間で十字形状となるように、接地配線が設けられ、

前記電源回路と、前記第1の機能回路と、前記第3の機能回路と、前記第2の機能回路とを順に囲んでコの字形状となるように、電源配線が設けられ、

前記接地配線及び前記電源配線は、前記導電膜と同一層に設けられたことを特徴とする半導体装置。

【請求項 4】

請求項1乃至3のいずれか一において、

20

前記電源回路から前記電源配線に電源電圧が供給されるように、前記電源回路と前記電源配線とは電気的に接続していることを特徴とする半導体装置。

【請求項 5】

基板上に設けられた素子形成層と、前記素子形成層に電気的に接続されたアンテナとを有し、

前記素子形成層と前記アンテナとは少なくとも一部が重なるように設けられ、

前記素子形成層は、複数のトランジスタと、記憶素子部とを有し、

前記記憶素子部は、前記複数のトランジスタのソース電極又はドレイン電極の一方と電気的に接続される第1の導電膜と、

30

前記第1の導電膜上に形成された有機化合物層と、

前記有機化合物層上に形成された第2の導電膜とを有し、

前記複数のトランジスタを用いて、電源回路及び機能回路を構成し、

前記電源回路と、前記機能回路との間で十字形状となるように、接地配線が設けられ、

前記電源回路と、前記機能回路とを囲んでコの字形状となるように、電源配線が設けられた半導体装置の作製方法であって、

前記アンテナを形成した後に前記有機化合物層を形成することを特徴とする半導体装置の作製方法。

【請求項 6】

基板上に設けられた素子形成層と、前記素子形成層に電気的に接続されたアンテナとを有し、

40

前記素子形成層と前記アンテナとは少なくとも一部が重なるように設けられ、

前記素子形成層は、複数のトランジスタと、記憶素子部とを有し、

前記記憶素子部は、前記複数のトランジスタのソース電極又はドレイン電極の一方と電気的に接続される第1の導電膜と、

前記第1の導電膜上に形成された有機化合物層と、

前記有機化合物層上に形成された第2の導電膜とを有し、

前記複数のトランジスタを用いて、電源回路及び機能回路を構成し、

前記電源回路と、前記機能回路との間で十字形状となるように、接地配線が設けられ、

前記電源回路と、前記機能回路とを囲んでコの字形状となるように、電源配線が設けられた半導体装置の作製方法であって、

50

前記接地配線及び前記電源配線は、前記第1の導電膜と同時に形成され、前記アンテナを形成した後に前記有機化合物層を形成することを特徴とする半導体装置の作製方法。

【請求項7】

請求項5または6において、

前記電源回路から前記電源配線に電源電圧が供給されるように、前記電源回路と前記電源配線とは電気的に接続していることを特徴とする半導体装置の作製方法。

【発明の詳細な説明】

【技術分野】

【0001】

10

本発明は、非接触で情報の送受信が可能である半導体装置に関する。

【背景技術】

【0002】

近年、個々の対象物にID(個体識別番号)を与えることで、その対象物の履歴等の情報を明確にし、生産・管理等に役立てるといった個体認識技術が注目されている。その中でも、非接触でデータの送受信が可能な半導体装置の開発が進められている。このような半導体装置として、RFIDタグ(Radio Frequency Identification)(IDタグ、ICタグ、ICチップ、RFタグ(Radio Frequency)、無線タグ、電子タグ、無線チップともよばれる)等が企業内、市場等で導入され始めている。

20

【0003】

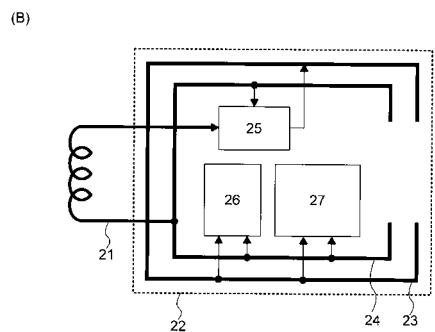

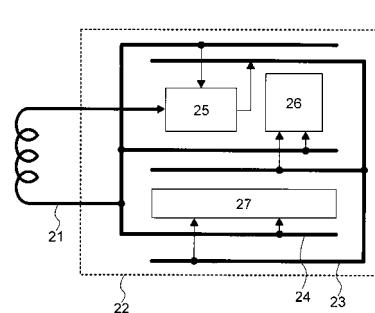

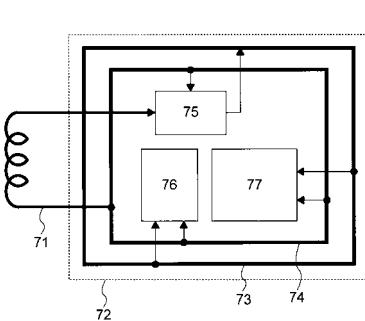

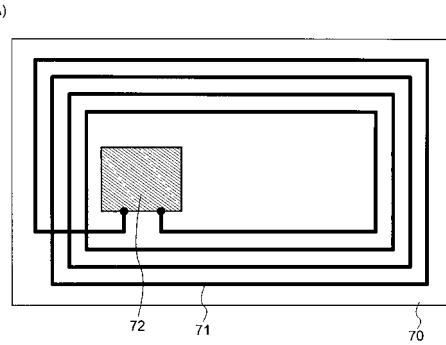

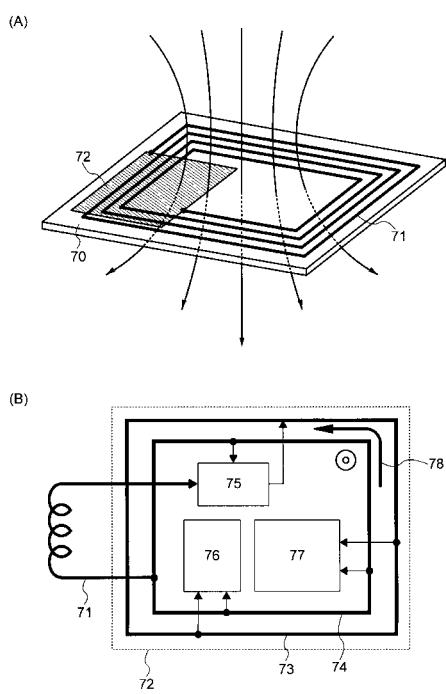

一般的に、現在実用化されているRFIDタグの多くは、例えば、図4(A)に示すように基板70上にトランジスタ等の素子から構成される回路を有する素子形成層72(IC(Integrated Circuit)チップとも呼ばれる)とアンテナ71とを有している。これらの、半導体装置は、電磁波を用いてリーダ/ライタとの間の通信を行うことができる。具体的には、リーダ/ライタから発せられる電磁波によりアンテナコイルを通る磁界が変化し、それによって生じる誘導起電力を用いて、素子形成層を動作させる。また、素子形成層から出力された信号を用いてアンテナに負荷変調を与えることで、リーダ/ライタに信号を送ることができる。

30

【発明の開示】

【発明が解決しようとする課題】

【0004】

ところで、素子形成層72においては、素子形成層に設けられた複数の機能回路に十分な電源の供給を行うために電源配線や接地配線等が複数の機能回路の周りを囲むように設けられている。具体的には、図4(B)に示すように、電源配線73や接地配線74等の配線が電源回路75および機能回路76、77等を囲むように配置され、環状となっている。

【0005】

しかしながら、非接触で情報の送受信を行う半導体装置において、素子形成層72に設けられる配線等の形状によっては、電磁誘導を利用する場合に問題が生じる恐れがある。例えば、図4(B)に示すように電源配線や接地配線等の配線が環状である場合、電源配線や接地配線等に囲まれた領域で磁界が変化すると、これらの配線には磁界の変化を打ち消すように電流(渦電流)が発生する。具体的には、図5(A)に示すように、例えば、半導体装置にリーダ/ライタから電磁波が送られてきた場合(ここでは基板70の上方から下方に向かって磁界が生じた場合)、アンテナ71を介して素子形成層72に電源電圧を発生するが、その一方で、素子形成層72における環状の電源配線73や接地配線74にも、当該磁界の変化を打ち消すように電流78が発生し、基板の下方から上方に向かう磁界が発生する(図5(B))。

40

【0006】

その結果、リーダ/ライタから送られてくる電磁波が減少することによって通信距離が

50

低減したり、配線等に生じる電流により素子形成層にジュークル熱が発生し電磁エネルギーの一部が熱エネルギーとして消費され、素子形成層が発熱するといった問題等が生じる。特に、コイル状に設けられたアンテナと重なるように素子形成層が設けられている場合には、この問題はより顕著になる。

【0007】

上記の実情を鑑み、本発明は、リーダ／ライタから送られてくる電磁波の減少を防ぎ、また磁界の変化に伴う素子形成層の発熱を防止することが可能である半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

上記課題を解決するために、本発明では以下の手段を講ずる。

【0009】

本発明の半導体装置は、基板上に設けられた素子形成層と、素子形成層に接続されたアンテナとを有し、素子形成層は電源配線および接地配線とを有し、電源配線および接地配線が非環状であることを特徴としている。なお、本発明における環状とは、円状だけではなく楕円状や四角形状等も含み、配線の端点同士が接続しているかまたは配線があるものを囲むように1周囲以上設けてある形状も含まれる。つまり、円状や四角形状の配線はもちろん、らせん状やコイル状に配置されている配線も含まれる。また、立体的(3次元)において上記形状をなしている場合も含まれる。そして、環状以外の形状を非環状という。

10

【0010】

また、本発明の半導体装置の他の構成として、基板上に設けられた素子形成層と、素子形成層に接続されたアンテナとを有し、素子形成層とアンテナとは少なくとも一部が重なるように設けられ、素子形成層は電源配線および接地配線とを有し、電源配線および接地配線は非環状であることを特徴としている。また、アンテナは、素子形成層の上方に設けてもよいし下方に設けてもよい。

【0011】

また、上記構成において、本発明は電源配線や接地配線等の配線を、コの字型形状や櫛形形状や十字状等に設けることができる。

【0012】

30

また、本発明の半導体装置の他の構成として、基板上に設けられた半導体膜と、半導体膜上にゲート絶縁膜を介して設けられたゲート電極と、ゲート電極上に設けられた絶縁膜と、絶縁膜上に設けられ且つ半導体膜のソースまたはドレイン領域に接続されたソースまたはドレイン電極と、ソースまたはドレイン電極に電気的に接続された電源配線や接地配線等の配線と、配線に電気的に接続されたアンテナとを有し、配線は非環状であることを特徴としている。

【0013】

また、本発明の半導体装置の他の構成として、基板上に設けられた半導体膜と、半導体膜上にゲート絶縁膜を介して設けられたゲート電極と、ゲート電極上に設けられた絶縁膜と、絶縁膜上に設けられ且つ半導体膜のソースまたはドレイン領域に接続されたソースまたはドレイン電極と、ソースまたはドレイン電極の上方に設けられ且つソースまたはドレイン電極と電気的に接続された電源配線や接地配線等の配線と、半導体膜と少なくとも一部が重なって配置され且つ配線に電気的に接続されたアンテナとを有し、配線は非環状であることを特徴としている。

40

【発明の効果】

【0014】

電源配線や接地配線等の配線を非環状で設けることによって、磁界の変化に伴い電源配線や接地配線等の配線に発生する電流を抑制し、リーダ／ライタから送られてくる電磁波が減少することを防止することができる。また、磁界の変化に伴い電源配線や接地配線で発生する電流を抑制することによって、素子形成層の発熱を防止することができる。特に

50

コイル状に設けられたアンテナと重なるように素子形成層が配置する場合に効果的となる。

【発明を実施するための最良の形態】

【0015】

本発明の実施の形態について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いる場合がある。

【0016】

10

(実施の形態1)

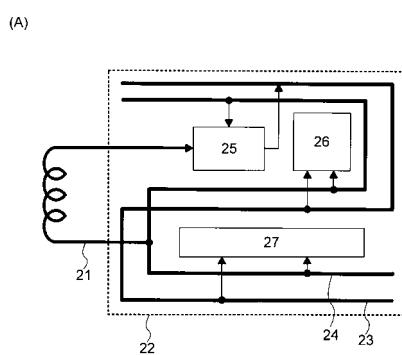

本発明の半導体装置の一構成例について図面を用いて以下に説明する。なお、図1(A)は半導体装置の上面図を表し、図1(B)は半導体装置における素子形成層の模式図を表している。

【0017】

20

図1(A)に示すように、本実施の形態で示す半導体装置は、基板20上に、素子形成層22とアンテナ21が設けられている。素子形成層22とアンテナ21はどのように配置してもよいが、半導体装置の小型化を考慮して素子形成層22とアンテナ21とが重なるように設けることが好ましい。また、アンテナ21をコイル状で設ける場合には、素子形成層22は、アンテナ21の端部と重なるように配置することが好ましい。これは、アンテナ21の中心に素子形成層22が配置されることによって、アンテナ21を通る電磁波が減少することを防ぐためである。

【0018】

基板20は、バリウムホウケイ酸ガラスや、アルミノホウケイ酸ガラスなどのガラス基板、石英基板、セラミック基板等を用いることができる。また、ステンレス等の金属基板または半導体基板の表面に絶縁膜を形成したものを用いても良い。他にも、PET等のプラスチック等の可撓性を有する合成樹脂からなる基板を用いてもよい。

【0019】

30

素子形成層22は、少なくともトランジスタおよび配線とを有している。当該トランジスタにより、CPU (central processing unit)、記憶回路またはマイクロプロセッサ等のありとあらゆる集積回路を設けることができる。また、素子形成層22におけるトランジスタは、ガラス基板等に薄膜トランジスタ(TFT)を設けてもよいし、基板としてSi等の半導体基板やSOI基板等を用い当該基板をチャネル部として利用する電界効果トランジスタ(FET)を設けてもよいし、有機TFTで設けてもよい。

【0020】

40

アンテナ21は、アルミニウム(Al)、チタン(Ti)、銀(Ag)、銅(Cu)から選択された元素、又はこれらの元素を主成分とする合金材料若しくは化合物材料等の導電物質で形成されている。また、アンテナ21は、素子形成層22と共に形成してもよいし、素子形成層22とは別個に形成し、後に素子形成層22に電気的に接続するように貼り合わせることによって設けてもよい。

【0021】

次に、図1(B)を用いて半導体装置における素子形成層22のより具体的な構成を説明する。

【0022】

素子形成層22は、アンテナ21と接続しており、電源配線23、接地配線24、電源回路25、機能回路26、27等を有している。アンテナ21の端部は、それぞれ電源回路25と接地配線24に接続されており、リーダ/ライタから発せられる電磁波によってアンテナ21を通る磁界が変化し、その変化により生じる誘導起電力により電源回路25に交流電圧が供給される。電源回路25は、アンテナから供給された交流電圧を整流して

50

平滑化し電源電圧を生成する。また、電源配線 23 は電源回路 25 と接続しており、電源回路 25 から電源配線 23 に電源電圧が供給される。そして、機能回路 26、27 は、電源配線 23 および接地配線 24 に接続しており、そこから電源電圧が供給されることによって機能回路 26、27 が動作する。なお、機能回路としては、クロック発生回路、データ復調/変調回路、各種回路を制御する制御回路、記憶回路等が含まれる。

#### 【0023】

また、本実施の形態では、電源配線 23 および接地配線 24 を非環状とする。つまり、従来のように機能回路等を囲むように環状に設けていた電源配線や接地配線等（図 4（B）参照）を環状にならないように設ける。例えば、図 1（B）に示すように、電源配線 23 および接地配線 24 を機能回路等を一周させて囲うように設けるのではなく、コの字の形状に設けることによって非環状とすることができる。

10

#### 【0024】

なお、ここでいう環状とは、円状だけではなく橙円状や四角形状も含み、配線の端点同士が接続しているかまたは配線があるものを囲むように 1 周囲以上設けてある形状も含まれる。つまり、円状や四角形状の配線はもちろん、コイル状に配置されている場合も含む。また、立体的（3 次元）において上記形状をなしている場合も含まれる。なお、ここでは、上記環状以外の形状を非環状と記す。

#### 【0025】

このように、電源配線や接地配線等の配線を非環状とすることによって、磁界の変化による電源配線や接地配線等に生じる電流を抑制し、リーダ/ライタから送られてくる電磁波の減少を防止することができる。また、当該電流による素子形成層の発熱も防止することができる。また、本実施の形態で示したように、コイル状に設けられたアンテナと素子形成層とを重ねて配置する場合（コイル状のアンテナの内側に素子形成層を設ける場合）には、素子形成層における電源配線や接地配線等を非環状とすることによって、リーダ/ライタから送られてくる電磁波の減少を防止することができる。

20

#### 【0026】

##### （実施の形態 2）

本実施の形態では、上記実施の形態と異なる半導体装置の一構成例について図面を用いて説明する。

#### 【0027】

30

上記実施の形態では、機能回路等を囲むように環状に設けられた電源配線や接地配線等の配線の一部分を切り取るようにコの字型にする例を示したが、これに限られず、外部からの磁界の変化に対して影響を受けにくい形状であれば、電源配線や接地配線等の配線をどのように配置してもよい。以下に、上記実施の形態で示した構造以外の具体例について図面に示す。

#### 【0028】

図 2 では、電源配線 23 や接地配線 24 が電源回路 25 や各機能回路 26、27 間を通りに設けられている。図 2（A）では、電源配線 23 や接地配線 24 を環状にせずに交互に折れ曲がった形状で設けることにより電源回路 25 および各機能回路 26、27 を囲むように配置している。

40

#### 【0029】

また、図 2（B）に示すように、電源配線 23 および接地配線 24 をそれぞれ櫛形に設け、左右から組み合わせることによって配線を設けることも可能である。このように、電源配線 23 や接地配線 24 等を櫛形に設けることによって、電源回路 25 や機能回路 26、27 の周囲に電源配線 23 や接地配線 24 を配置することができるため、電源回路 25 や機能回路 26、27 等に十分な電圧の供給を行うことができる。

#### 【0030】

このように電源配線 23 や接地配線 24 を非環状で配置することによって、磁界の変化による電源配線 23 や接地配線 24 等に生じる電流を防止することができる。

#### 【0031】

50

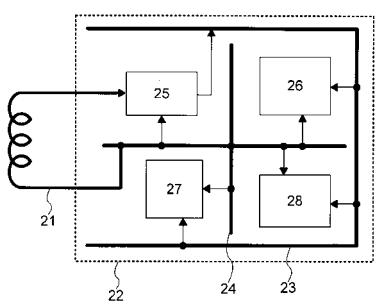

また、電源配線 23 や接地配線 24 等の配線は図 2 に示した構成に限られない。例えば、図 3 に示すように電源配線 23 と接地配線 24 の一方または両方（ここでは、接地配線 24）を十字形状に設けてもよい。そして、十字形状に設けられた配線の周辺に電源回路 25 や機能回路 26 ~ 28 を設けることができる。

【0032】

上記実施の形態に示した形態の他にも、例えば電源配線 23 や接地配線 24 等の配線を階段形等のジグザグ形状、V 字型、まんじ（卍）等の形状とすることも可能である。このように、素子形成層 22 において、電源配線 23 や接地配線 24 等の配線を環状でない形狀であればどのように設けてもよく、実施者が適宜選択して、十分に電源回路や機能回路等に電圧の供給を行えるようにすればよい。

10

【0033】

以上のように、電源配線や接地配線等の配線を非環状とすることによって、磁界の変化による電源配線や接地配線等に生じる電流を抑制し、リーダ / ライタから送られてくる電磁波の減少を防止することができる。また、当該電流による素子形成層の発熱も防止することが可能となる。

【0034】

なお、本実施の形態は上記実施の形態と自由に組み合わせて行うことができる。

（実施の形態 3）

本実施の形態では、本発明の半導体装置の作製方法の一例について、図面を参照して説明する。具体的には、素子形成層におけるトランジスタとして薄膜トランジスタ（TFT）を用い、支持基板上に TFT を設けた後に支持基板から TFT を分離する剥離法により半導体装置を作製する例を示す。

20

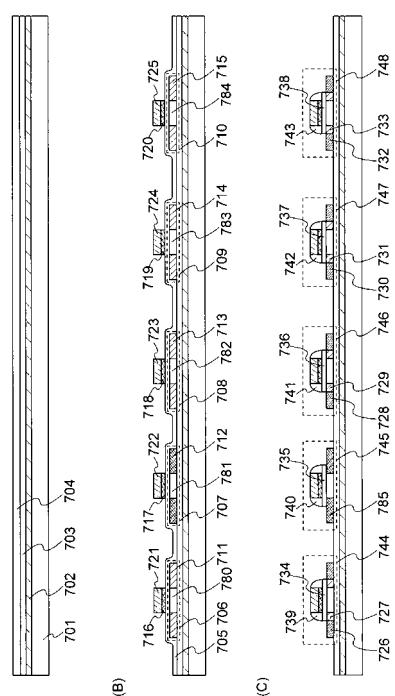

【0035】

まず、基板 701 の一表面に、剥離層 702 を形成する（図 6（A））。基板 701 は、ガラス基板、石英基板、ステンレス基板等の金属基板の一表面に絶縁膜を形成したもの、本工程の処理温度に耐えうる耐熱性があるプラスチック基板等を用いるとよい。このような基板 701 であれば、その面積や形状に大きな制限はないため、基板 701 として、例えば、1 辺が 1 メートル以上あって、矩形状のものを用いれば、生産性を格段に向上させることができる。このような利点は、円形のシリコン基板を用いる場合と比較すると、大きな優位点である。なお、本工程では、剥離層 702 は、基板 701 の全面に設けているが、必要に応じて、基板 701 の全面に剥離層を設けた後に、フォトリソグラフィ法により選択的に設けてもよい。また、基板 701 に接するように剥離層 702 を形成しているが、必要に応じて、基板 701 に接するように下地となる絶縁膜を形成し、当該絶縁膜に接するように剥離層 702 を形成してもよい。

30

【0036】

剥離層 702 は、金属膜と当該金属酸化膜により形成されている。金属膜は、公知の手段（スパッタリング法やプラズマ CVD 法等）により、タンゲステン（W）、モリブデン（Mo）、チタン（Ti）、タンタル（Ta）、ニオブ（Nb）、ニッケル（Ni）、コバルト（Co）、ジルコニウム（Zr）、亜鉛（Zn）、ルテニウム（Ru）、ロジウム（Rh）、鉛（Pb）、オスミウム（Os）、イリジウム（Ir）から選択された元素または前記元素を主成分とする合金材料若しくは化合物材料からなる層を、単層又は積層して形成する。金属酸化膜は、金属膜に酸素雰囲気下でプラズマ処理を行うか、金属膜に酸素雰囲気下で熱処理を行うことによって金属膜の表面に形成する。なお、金属酸化膜の他にも金属酸化窒化物を用いてもよい。

40

【0037】

金属膜が単層構造の場合、例えば、タンゲステン層、モリブデン層またはタンゲステンとモリブデンの混合物を含む層を形成する。そして、金属膜の表面に、タンゲステンの酸化物若しくは酸化窒化物を含む層、モリブデンの酸化物若しくは酸化窒化物を含む層またはタンゲステンとモリブデンの混合物の酸化物若しくは酸化窒化物を含む層を形成する。なお、タンゲステンとモリブデンの混合物とは、例えば、タンゲステンとモリブデンの合

50

金に相当する。

【0038】

また、剥離層702として、基板701上に金属膜を形成した後に、酸素雰囲気下で上記金属膜の材料をターゲットとして、スパッタ法により金属酸化膜を形成してもよい。この場合、金属膜と金属酸化膜を別の金属元素を用いて形成することもできる。なお、基板701上に、直接金属酸化膜を形成しこれを剥離層702として用いてもよい。

【0039】

次に、剥離層702を覆うように、下地となる絶縁膜703を形成する。絶縁膜703は、公知の手段（スパッタ法やプラズマCVD法等）により、珪素の酸化物または珪素の窒化物を含む膜を、単層又は積層で形成する。下地となる絶縁膜が2層構造の場合、例えば、1層目として窒化酸化珪素膜を形成し、2層目として酸化窒化珪素膜を形成するとよい。下地となる絶縁膜が3層構造の場合、1層目の絶縁膜として酸化珪素膜を形成し、2層目の絶縁膜として窒化酸化珪素膜を形成し、3層目の絶縁膜として酸化窒化珪素膜を形成するとよい。または、1層目の絶縁膜として酸化窒化珪素膜を形成し、2層目の絶縁膜として窒化酸化珪素膜を形成し、3層目の絶縁膜として酸化窒化珪素膜を形成するとよい。下地となる絶縁膜は、基板701からの不純物の侵入を防止するプロッキング膜として機能する。

【0040】

次に、絶縁膜703上に、非晶質半導体膜704（例えば非晶質珪素を含む膜）を形成する。非晶質半導体膜704は、公知の手段（スパッタ法、LPCVD法、プラズマCVD法等）により、25～200nm（好ましくは30～150nm）の厚さで形成する。続いて、非晶質半導体膜704を公知の結晶化法（レーザ結晶化法、RTA又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法とレーザ結晶化法を組み合わせた方法等）により結晶化して、結晶質半導体膜を形成する。その後、得られた結晶質半導体膜を所望の形状にエッティングして、結晶質半導体膜706～710を形成する（図6（B））。なお、剥離層702、絶縁膜703および非晶質半導体膜704は、連続して形成することができる。

【0041】

結晶質半導体膜706～710の作製工程の一例を以下に簡単に説明すると、まず、プラズマCVD法を用いて、膜厚66nmの非晶質半導体膜を形成する。次に、結晶化を助長する金属元素であるニッケルを含む溶液を非晶質半導体膜上に保持させた後、非晶質半導体膜に脱水素化の処理（500、1時間）と、熱結晶化の処理（550、4時間）を行って結晶質半導体膜を形成する。その後、必要に応じてレーザ光を照射し、フォトリソグラフィ法を用いることによって結晶質半導体膜706～710を形成する。

【0042】

レーザ結晶化法で結晶質半導体膜を形成する場合、連続発振またはパルス発振の気体レーザ又は固体レーザを用いる。気体レーザとしては、エキシマレーザ、YAGレーザ、YVO<sub>4</sub>レーザ、YLFレーザ、YAlO<sub>3</sub>レーザ、ガラスレーザ、ルビーレーザ、Ti：サファイアレーザ等を用いる。固体レーザとしては、Cr、Nd、Er、Ho、Ce、Co、Ti又はTmがドーピングされたYAG、YVO<sub>4</sub>、YLF、YAlO<sub>3</sub>などの結晶を使ったレーザを用いる。特に、連続発振のレーザの基本波、及び当該基本波の第2高調波から第4高調波のレーザを照射することで、大粒径の結晶を得ることができる。例えば、Nd：YVO<sub>4</sub>レーザ（基本波1064nm）の第2高調波（532nm）や第3高調波（355nm）を用いることができる。なお連続発振の基本波のレーザ光と連続発振の高調波のレーザ光とを照射するようにしてもよいし、連続発振の基本波のレーザ光とパルス発振の高調波のレーザ光とを照射するようにしてもよい。複数のレーザ光を照射することにより、エネルギーを補うことができる。またパルス発振型のレーザであって、半導体膜がレーザ光によって溶融してから固化するまでに、次のパルスのレーザ光を照射できるような発振周波数でレーザ光を発振させることで、走査方向に向かって連続的に成長した

10

20

30

40

50

結晶粒を得ることができる。すなわち、パルス発振の周期が、半導体膜が溶融してから完全に固化するまでの時間よりも短くなるように、発振の周波数の下限を定めたパルス発振のレーザを使用することができる。このようなレーザとして、発振周波数が 10 MHz 以上のパルス発振のレーザ光を用いてもよい。

#### 【0043】

また、結晶化を助長する金属元素を用いて非晶質半導体膜の結晶化を行うと、低温で短時間の結晶化が可能となるうえ、結晶の方向が揃うという利点がある一方、金属元素が結晶質半導体膜に残存するためにオフ電流が上昇し、特性が安定しないという欠点がある。そこで、結晶質半導体膜上に、ゲッタリングサイトとして機能する非晶質半導体膜を形成するとよい。ゲッタリングサイトとなる非晶質半導体膜には、リンやアルゴンの不純物元素を含有させる必要があるため、好適には、アルゴンを高濃度に含有させることができなスパッタ法で形成するとよい。その後、加熱処理 (RTA 法やファーネスアニール炉を用いた熱アニール等) を行って、非晶質半導体膜中に金属元素を拡散させ、続いて、当該金属元素を含む非晶質半導体膜を除去する。そうすると、結晶質半導体膜中の金属元素の含有量を低減又は除去することができる。

10

#### 【0044】

次に、結晶質半導体膜 706 ~ 710 を覆うゲート絶縁膜 705 を形成する。ゲート絶縁膜 705 は、公知の手段 (プラズマ CVD 法やスパッタ法) により、珪素の酸化物又は珪素の窒化物を含む膜を、単層又は積層して形成する。具体的には、酸化珪素を含む膜、酸化窒化珪素を含む膜、窒化酸化珪素を含む膜を、単層又は積層して形成する。

20

#### 【0045】

次に、ゲート絶縁膜 705 上に、第 1 の導電膜と第 2 の導電膜とを積層して形成する。第 1 の導電膜は、公知の手段 (プラズマ CVD 法やスパッタリング法) により、20 ~ 100 nm の厚さで形成する。第 2 の導電膜は、公知の手段により、100 ~ 400 nm の厚さで形成する。第 1 の導電膜と第 2 の導電膜は、タンタル (Ta)、タングステン (W)、チタン (Ti)、モリブデン (Mo)、アルミニウム (Al)、銅 (Cu)、クロム (Cr)、ニオブ (Nb) 等から選択された元素又はこれらの元素を主成分とする合金材料若しくは化合物材料で形成する。または、リン等の不純物元素をドーピングした多結晶珪素に代表される半導体材料により形成する。第 1 の導電膜と第 2 の導電膜の組み合わせの例を挙げると、窒化タンタル膜とタングステン膜、窒化タングステン膜とタングステン膜、窒化モリブデン膜とモリブデン膜等が挙げられる。タングステンや窒化タンタルは、耐熱性が高いため、第 1 の導電膜と第 2 の導電膜を形成した後に、熱活性化を目的とした加熱処理を行うことができる。また、2 層構造ではなく、3 層構造の場合は、モリブデン膜とアルミニウム膜とモリブデン膜の積層構造を採用するとよい。

30

#### 【0046】

次に、フォトリソグラフィ法を用いてレジストからなるマスクを形成し、ゲート電極とゲート線を形成するためのエッチング処理を行って、ゲート電極として機能する導電膜 (ゲート電極とよぶことがある) 716 ~ 725 を形成する。また、導電膜 716 ~ 725 と同一の層に電源配線や接地配線等の配線を形成してもよい。この場合、導電膜 716 ~ 725 と同時に同じ材料を用いて設けることができる。なお、電源配線や接地配線の配線は上記実施の形態で示したように非環状で設ける。

40

#### 【0047】

次に、フォトリソグラフィ法により、レジストからなるマスクを形成して、結晶質半導体膜 706、708 ~ 710 に、イオンドープ法又はイオン注入法により、N 型を付与する不純物元素を低濃度に添加して、N 型不純物領域 711、713 ~ 715 とチャネル形成領域 780、782 ~ 784 を形成する。N 型を付与する不純物元素は、15 族に属する元素を用いれば良く、例えばリン (P)、砒素 (As) を用いる。

#### 【0048】

次に、フォトリソグラフィ法によりレジストからなるマスクを形成して、結晶質半導体膜 707 に、P 型を付与する不純物元素を添加して、P 型不純物領域 712 とチャネル形

50

成領域 781 を形成する。P 型を付与する不純物元素は、例えばボロン (B) を用いる。

【0049】

次に、ゲート絶縁膜 705 と導電膜 716～725 を覆うように、絶縁膜を形成する。絶縁膜は、公知の手段 (プラズマ CVD 法やスパッタ法) により、珪素、珪素の酸化物又は珪素の窒化物の無機材料を含む膜や、有機樹脂などの有機材料を含む膜を、単層又は積層して形成する。次に、絶縁膜を、垂直方向を主体とした異方性エッティングにより選択的にエッティングして、導電膜 716～725 の側面に接する絶縁膜 (サイドウォールともよばれる) 739～743 を形成する (図 6 (C))。また、絶縁膜 739～743 の作製と同時に、絶縁膜 705 がエッティングされた絶縁膜 734～738 を形成する。絶縁膜 739～743 は、後に LDD (Lightly Doped drain) 領域を形成する際のドーピング用のマスクとして用いる。

【0050】

次に、フォトリソグラフィ法により形成したレジストからなるマスクと、絶縁膜 739～743 をマスクとして用いて、結晶質半導体膜 706、708～710 に N 型を付与する不純物元素を添加して、第 1 の N 型不純物領域 (LDD 領域ともよぶ) 727、729、731、733 と、第 2 の N 型不純物領域 726、728、730、732 を形成する。第 1 の N 型不純物領域 727、729、731、733 が含む不純物元素の濃度は、第 2 の N 型不純物領域 726、728、730、732 の不純物元素の濃度よりも低い。上記工程を経て、N 型の薄膜トランジスタ 744、746～748 と、P 型の薄膜トランジスタ 745 が完成する。

【0051】

なお、LDD 領域を形成するためには、ゲート電極を 2 層以上の積層構造として、当該ゲート電極をテーパー状にエッティングしたりゲート電極に異方性エッティング等を行って、当該ゲート電極を構成する下層の導電膜をマスクとして用いる手法と、サイドウォールの絶縁膜をマスクとして用いる手法がある。前者の手法を採用して形成された薄膜トランジスタは、ゲート絶縁膜を介して LDD 領域をゲート電極と重ねて配置させた構造となっているが、この構造は、ゲート電極をテーパー状にエッティングしたりゲート電極に異方性エッティングを行うために、LDD 領域の幅を制御することが難しく、エッティング工程が良好に行われなければ、LDD 領域を形成することが出来ない場合がある。一方、後者のサイドウォールの絶縁膜をマスクとして用いる手法は、前者の手法と比較すると、LDD 領域の幅の制御が容易であり、また、LDD 領域を確実に形成することができる。

【0052】

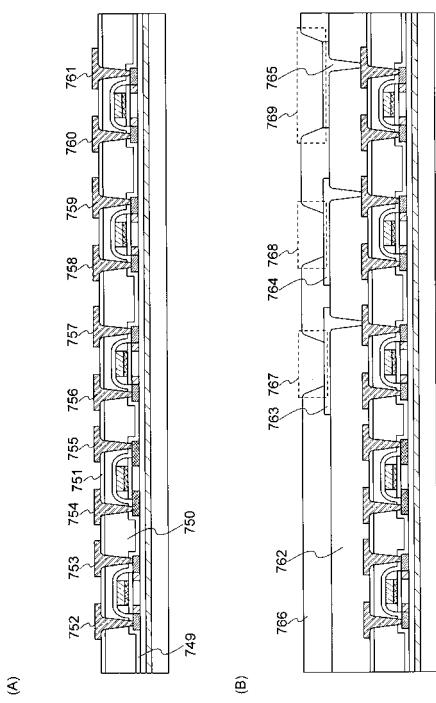

続いて、薄膜トランジスタ 744～748 を覆うように、絶縁膜を単層又は積層して形成する (図 7 (A))。薄膜トランジスタ 744～748 を覆う絶縁膜は、公知の手段 (SOG 法、液滴吐出法等) により、珪素の酸化物や珪素の窒化物等の無機材料、ポリイミド、ポリアミド、ベンゾシクロブテン、アクリル、エポキシ、シロキサン等の有機材料等により、単層又は積層で形成する。シロキサン系の材料とは、例えば、シリコン (Si) と酸素 (O) との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基 (例えばアルキル基、芳香族炭化水素) が用いられる。置換基として、フルオロ基を用いてもよい。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。例えば、薄膜トランジスタ 744～748 を覆う絶縁膜が 3 層構造の場合、1 層目の絶縁膜 749 として酸化珪素を含む膜を形成し、2 層目の絶縁膜 750 として樹脂を含む膜を形成し、3 層目の絶縁膜 751 として窒化珪素を含む膜を形成するとよい。

【0053】

なお、絶縁膜 749～751 を形成する前、又は絶縁膜 749～751 のうちの 1 つ又は複数の薄膜を形成した後に、半導体膜の結晶性の回復や半導体膜に添加された不純物元素の活性化、半導体膜の水素化を目的とした加熱処理を行うとよい。加熱処理には、熱アニール、レーザアニール法又は RTA 法などを適用するとよい。

【0054】

次に、フォトリソグラフィ法により絶縁膜 749～751 をエッティングして、N 型不純

10

20

30

40

50

物領域 726、728、730、732、P型不純物領域 785を露出させるコンタクトホールを形成する。続いて、コンタクトホールを充填するように、導電膜を形成し、当該導電膜をパターン加工して、ソースドレイン配線として機能する導電膜 752～761を形成する。また、この時、ソースドレイン配線として機能する導電膜 752～761と同一の層に電源配線や接地配線等の配線を形成してもよい。この場合、導電膜 752～761と同時に同じ材料を用いて設けることができる。なお、電源配線や接地配線の配線は上記実施の形態で示したように非環状で設ける。

#### 【0055】

導電膜 752～761は、公知の手段（プラズマCVD法やスパッタリング法）により、チタン（Ti）、アルミニウム（Al）、ネオジウム（Nd）から選択された元素、又はこれらの元素を主成分とする合金材料若しくは化合物材料で、単層又は積層で形成する。アルミニウムを主成分とする合金材料とは、例えば、アルミニウムを主成分としニッケルを含む材料、又は、アルミニウムを主成分とし、ニッケルと、炭素と珪素の一方又は両方とを含む合金材料に相当する。導電膜 752～761は、例えば、バリア膜とアルミニウムシリコン（Al-Si）膜とバリア膜の積層構造、バリア膜とアルミニウムシリコン（Al-Si）膜と窒化チタン膜とバリア膜の積層構造を採用するとよい。なお、バリア膜とは、チタン、チタンの窒化物、モリブデン、又はモリブデンの窒化物からなる薄膜に相当する。アルミニウムやアルミニウムシリコンは抵抗値が低く、安価であるため、導電膜 752～761を形成する材料として最適である。また、上層と下層のバリア層を設けると、アルミニウムやアルミニウムシリコンのヒロックの発生を防止することができる。また、還元性の高い元素であるチタンからなるバリア膜を形成すると、結晶質半導体膜上に薄い自然酸化膜ができていたとしても、この自然酸化膜を還元し、結晶質半導体膜と良好なコンタクトをとることができる。

#### 【0056】

次に、導電膜 752～761を覆うように、絶縁膜 762を形成する（図7（B））。絶縁膜 762は、公知の手段（SOG法、液滴吐出法等）を用いて、無機材料又は有機材料により、単層又は積層で形成する。また、絶縁膜 762は、好適には、0.75μm～3μmの厚さで形成する。

#### 【0057】

続いて、フォトリソグラフィ法により絶縁膜 762をエッチングして、導電膜 757、759、761を露出させるコンタクトホールを形成する。続いて、コンタクトホールを充填するように、導電膜を形成する。導電膜は、公知の手段（プラズマCVD法やスパッタリング法）を用いて、導電性材料により形成する。次に、導電膜をパターン加工して、導電膜 763～765を形成する。なお、導電膜 763～765は、記憶素子が含む一対の導電膜のうちの一方の導電膜となる。従って、好適には、導電膜 763～765は、チタン、又はチタンを主成分とする合金材料若しくは化合物材料により、単層又は積層で形成するとよい。チタンは、抵抗値が低いため、記憶素子のサイズの縮小につながり、高集積化を実現することができる。また、導電膜 763～765を形成するためのフォトリソグラフィ工程においては、下層の薄膜トランジスタ 744～748にダメージを与えないために、ウエットエッチング加工を行うとよく、エッチング剤にはフッ化水素（HF）又はアンモニア過水を用いるとよい。なお、導電膜 763～765と同一の層に電源配線や接地配線等を設けてもよい。この場合、導電膜 763～765と同時に同じ材料を用いて設けることができる。また、電源配線や接地配線は上記実施の形態で示したように非環状で設ける。

#### 【0058】

次に、導電膜 763～765を覆うように、絶縁膜 766を形成する。絶縁膜 766は、公知の手段（SOG法、液滴吐出法等）を用いて、無機材料又は有機材料により、単層又は積層で形成する。また、絶縁膜 766は、好適には、0.75μm～3μmの厚さで形成する。続いて、フォトリソグラフィ法により、絶縁膜 766をエッチングして、導電膜 763～765を露出させるコンタクトホール 767～769を形成する。

10

20

30

40

50

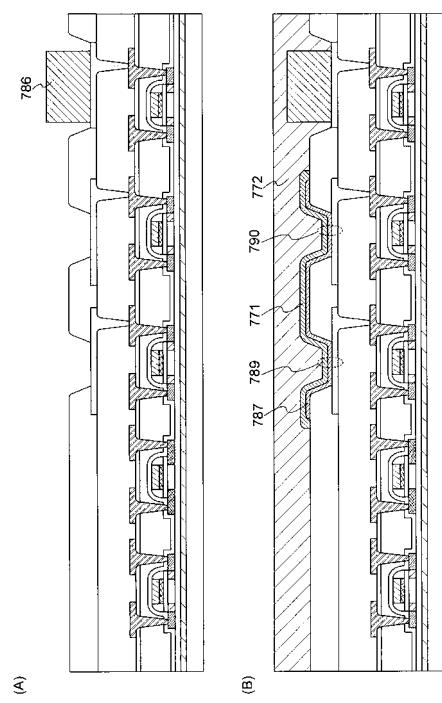

## 【0059】

次に、導電膜765に接し、アンテナとして機能する導電膜786を形成する(図8(A))。導電膜786は、公知の手段(プラズマCVD法、スパッタリング法、印刷法、液滴吐出法)を用いて、導電性材料により形成する。好ましくは、導電膜786は、アルミニウム(A1)、チタン(Ti)、銀(Ag)、銅(Cu)から選択された元素、又はこれらの元素を主成分とする合金材料若しくは化合物材料で、単層又は積層で形成する。ここでは、導電膜786は、スクリーン印刷法により、銀を含むペーストを用いて形成し、その後、50~350度の加熱処理を行って形成する。又は、スパッタリング法によりアルミニウム膜を形成し、当該アルミニウム膜をパターン加工することにより形成する。アルミニウム膜のパターン加工は、ウエットエッチング加工を用いるとよく、ウエットエッチング加工後は200~300度の加熱処理を行うとよい。なお、導電膜786と同一の層に電源配線や接地配線等を設けてもよい。この場合、導電膜786と同時に同じ材料を用いて設けることができる。また、電源配線や接地配線は上記実施の形態で示したように非環状で設ける。

10

## 【0060】

次に、導電膜763、764に接するように有機化合物層787を形成する(図8(B))。有機化合物層787は、公知の手段(液滴吐出法や蒸着法等)により形成する。続いて、有機化合物層787に接するように、導電膜771を形成する。導電膜771は、公知の手段(スパッタリング法や蒸着法)により形成する。

20

## 【0061】

また、導電膜771の形成と同時に電源配線や接地配線等を設けてもよい。電源配線や接地配線は上記実施の形態で示したように非環状で設ける。このように、電源配線や接地配線等は、導電膜716~725と同一の層、導電膜752~761と同一の層、導電膜763~765と同一の層、導電膜786と同一の層または導電膜771と同一の層等どこに設けてもよく実施者が適宜選択することができる。また、電源配線と接地配線をそれぞれ異なる層に設けることも可能である。さらに、素子形成層を多層に形成することによって、電源配線や接地配線を薄膜トランジスタの上方に設け、素子形成層の小型化を達成することができる。

## 【0062】

以上の工程を経て、導電膜763、有機化合物層787及び導電膜771の積層体からなる記憶素子部789と、導電膜764、有機化合物層787及び導電膜771の積層体からなる記憶素子部790が完成する。

30

## 【0063】

なお、上記の作製工程では、有機化合物層787の耐熱性が強くないため、アンテナとして機能する導電膜786を形成する工程の後に、有機化合物層787を形成する工程を行うことを特徴とする。また、アンテナとして機能する導電膜786は、導電膜716~725と同一の層、導電膜752~761と同一の層、導電膜763~765と同一の層または導電膜771と同一の層に設けることも可能である。また、アンテナは、アンテナとして機能する導電膜786を直接形成せずに、別の基板に別途設けた導電膜と導電膜765とを導電性微粒子等を含む接着剤を用いて貼り合わせることによって設けることも可能である。この場合は、有機化合物層787を設けた後であってもアンテナを形成することができる。

40

## 【0064】

なお、ここでは、記憶素子部789、790として、有機化合物材料を用いた例を示したが、これに限られない。例えば、結晶状態と非晶質状態の間で可逆的に変化する材料や第1の結晶状態と第2の結晶状態の間で可逆的に変化する材料等の相変化材料を用いることができる。また、非晶質状態から結晶状態にのみ変化する材料を用いることも可能である。

## 【0065】

結晶状態と非晶質状態の間で可逆的に変化する材料とは、ゲルマニウム(Ge)、テル

50

ル (Te)、アンチモン (Sb)、硫黄 (S)、酸化テルル (TeO<sub>x</sub>)、Sn (スズ)、金 (Au)、ガリウム (Ga)、セレン (Se)、インジウム (In)、タリウム (Tl)、Co (コバルト) 及び銀 (Ag) から選択された複数を有する材料であり、例えば、Ge - Te - Sb - S、Te - TeO<sub>2</sub> - Ge - Sn、Te - Ge - Sn - Au、Ge - Te - Sn、Sn - Se - Te、Sb - Se - Te、Sb - Se、Ga - Se - Te、Ga - Se - Te - Ge、In - Se、In - Se - Tl - Co、Ge - Sb - Te、In - Se - Te、Ag - In - Sb - Te 系材料が挙げられる。また、第1の結晶状態と第2の結晶状態の間で可逆的に変化する材料とは、銀 (Ag)、亜鉛 (Zn)、銅 (Cu)、アルミニウム (Al)、ニッケル (Ni)、インジウム (In)、アンチモン (Sb)、セレン (Se) 及びテルル (Te) から選択された複数を有する材料であり、例えば、Te - TeO<sub>2</sub>、Te - TeO<sub>2</sub> - Pd、Sb<sub>2</sub>Se<sub>3</sub> / Bi<sub>2</sub>Te<sub>3</sub> が挙げられる。この材料の場合、相変化は2つの異なる結晶状態の間で行われる。また、非晶質状態から結晶状態にのみ変化する材料とは、テルル (Te)、酸化テルル (TeO<sub>x</sub>)、アンチモン (Sb)、セレン (Se) 及びビスマス (Bi) から選択された複数を有する材料であり、例えば、Ag - Zn、Cu - Al - Ni、In - Sb、In - Sb - Se、In - Sb - Te が挙げられる。

10

## 【0066】

次に、記憶素子部 789、790、アンテナとして機能する導電膜 786 を覆うように、公知の手段 (SOG法、液滴吐出法等) により、保護膜として機能する絶縁膜 772 を形成する。絶縁膜 772 は、DLC (ダイヤモンドライクカーボン) などの炭素を含む膜、窒化珪素を含む膜、窒化酸化珪素を含む膜、有機材料により形成し、好ましくはエポキシ樹脂により形成する。

20

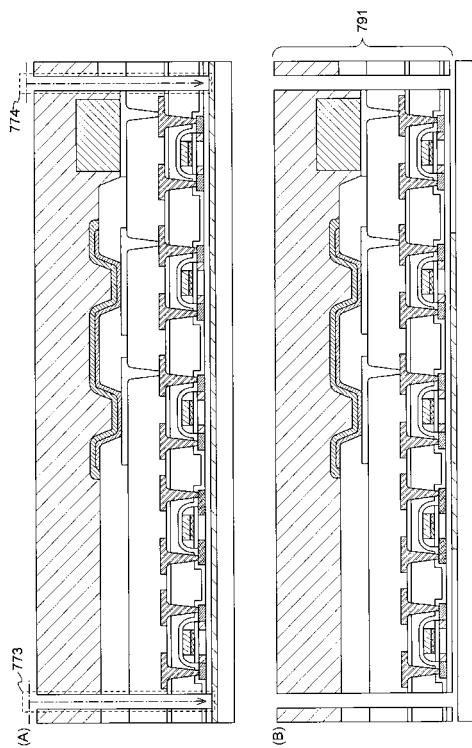

## 【0067】

次に、薄膜トランジスタ 744 ~ 748、記憶素子部 789、790 等を含む素子形成層 791 を基板 701 から剥離する。ここでは、レーザ光 (例えばUV光) を照射することによって開口部 773、774 を形成後 (図9(A))、物理的な力を用いて基板 701 から素子形成層 791 を剥離することができる。また、基板 701 から素子形成層 791 を剥離する前に、開口部 773、774 にエッティング剤を導入して、剥離層 702 を除去してもよい。エッティング剤は、フッ化ハロゲンまたはハロゲン間化合物を含む気体又は液体を使用する。例えば、フッ化ハロゲンを含む気体として三フッ化塩素 (ClF<sub>3</sub>) を使用する。そうすると、素子形成層 791 は、基板 701 から剥離された状態となる。なお、剥離層 702 は、全て除去せず一部分を残存させてもよい。こうすることによって、エッティング剤の消費量を抑え剥離層 702 の除去に要する処理時間を短縮することが可能となる。

30

## 【0068】

また、素子形成層 791 が剥離された基板 701 は、コストの削減のために、再利用することが好ましい。また、絶縁膜 772 は、剥離層 702 を除去した後に、素子形成層 791 が飛散しないように形成したものである。素子形成層 791 は小さく薄く軽いために、剥離層 702 を除去した後は、基板 701 に密着していないために飛散しやすい。しかしながら、素子形成層 791 上に絶縁膜 772 を形成することで、素子形成層 791 に重みが付き、基板 701 からの飛散を防止することができる。また、素子形成層 791 単体では薄くて軽いが、絶縁膜 772 を形成することで、基板 701 から剥離した素子形成層 791 が応力等により巻かれた形状になることがなく、ある程度の強度を確保することができる。

40

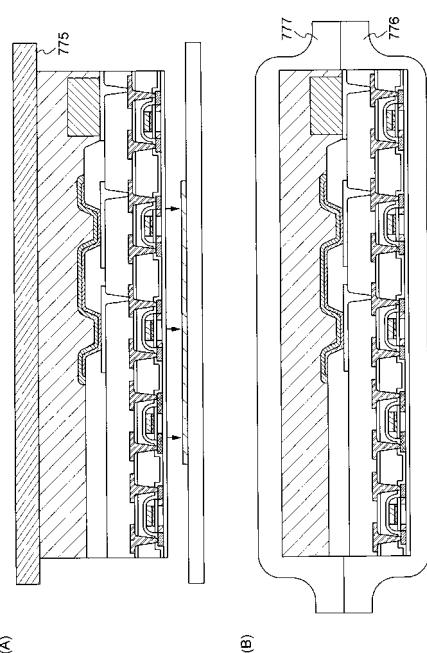

## 【0069】

次に、素子形成層 791 の一方の面を、第1のシート材 775 に接着させて基板 701 から完全に剥離する (図10(A))。剥離層 702 を全て除去せず一部を残した場合には、物理的手段を用いて基板 701 から素子形成層 791 を剥離する。続いて、素子形成層 791 の他方の面に、第2のシート材 776 を設け、その後加熱処理と加圧処理の一方または両方を行って、第2のシート材 776 を貼り合わせる。また、第2のシート材 77

50

6を設けると同時または設けた後に第1のシート材775を剥離し、代わりに第3のシート材777を設ける。そして、加熱処理と加圧処理の一方または両方を行って、第3のシート材777を貼り合わせる。そうすると、第2のシート材776と第3のシート材777により封止された半導体装置が完成する(図10(B))。

【0070】

なお、第1のシート材775と第2のシート材776によって封止を行っても良いが、基板701から素子形成層791を剥離するためのシート材と素子形成層791を封止するためのシート材に異なるシート材を用いる場合には、上述したように、第2のシート材776と第3のシート材777で素子形成層791を封止する。これは、例えば、基板701から素子形成層791を剥離する際に、第1のシート材775が素子形成層791のみならず基板701への接着が懸念される場合等、粘着力が弱いシート材を利用したいときに有効となる。

【0071】

封止に用いる第2のシート材776、第3のシート材777として、ポリプロピレン、ポリエステル、ビニル、ポリフッ化ビニル、塩化ビニルなどからなるフィルム、繊維質な材料からなる紙、基材フィルム(ポリエステル、ポリアミド、無機蒸着フィルム、紙類等)と接着性合成樹脂フィルム(アクリル系合成樹脂、エポキシ系合成樹脂等)との積層フィルム等を利用することができる。また、フィルムは、熱圧着により、被処理体と加熱処理と加圧処理が行われるものであり、加熱処理と加圧処理を行う際には、フィルムの最表面に設けられた接着層か、又は最外層に設けられた層(接着層ではない)を加熱処理によって溶かし、加圧により接着する。また、第2のシート材776と第3のシート材777の表面には接着層が設けられていてもよいし、接着層が設けられていてもよい。接着層は、熱硬化樹脂、紫外線硬化樹脂、エポキシ樹脂系接着剤、樹脂添加剤等の接着剤を含む層に相当する。また、封止後に内部への水分等の侵入を防ぐために封止するシート材にシリカコートを行うことが好ましく、例えば、接着層とポリエステル等のフィルムとシリカコートを積層させたシート材を利用することができる。

【0072】

また、第2のシート材776、第3のシート材777として、静電気等を防止する帯電防止対策を施したフィルム(以下、帯電防止フィルムと記す)を用いることもできる。帯電防止フィルムとしては、帯電防止可能な材料を樹脂中に分散させたフィルム、及び帯電防止可能な材料が貼り付けられたフィルム等が挙げられる。帯電防止可能な材料が設けられたフィルムは、片面に帯電防止可能な材料を設けたフィルムであってもよいし、両面に帯電防止可能な材料を設けたフィルムであってもよい。さらに、片面に帯電防止可能な材料が設けられたフィルムは、帯電防止可能な材料が設けられた面をフィルムの内側になるように層に貼り付けてもよいし、フィルムの外側になるように貼り付けてもよい。なお、帯電防止可能な材料はフィルムの全面、あるいは一部に設けてあればよい。ここでの帯電防止可能な材料としては、金属、インジウムと錫の酸化物(ITO)、両性界面活性剤や陽イオン性界面活性剤や非イオン性界面活性剤等の界面活性剤用いることができる。また、他にも帯電防止材料として、側鎖にカルボキシル基および4級アンモニウム塩基をもつ架橋性共重合体高分子を含む樹脂材料等を用いることができる。これらの材料をフィルムに貼り付けたり、練り込んだり、塗布したりすることによって帯電防止フィルムとすることができる。帯電防止フィルムで封止を行うことによって、商品として取り扱う際に、外部からの静電気等によって半導体素子に悪影響が及ぶことを抑制することができる。

【0073】

なお、本実施の形態は、上記実施の形態と自由に組み合わせて行うことができる。

【0074】

(実施の形態4)

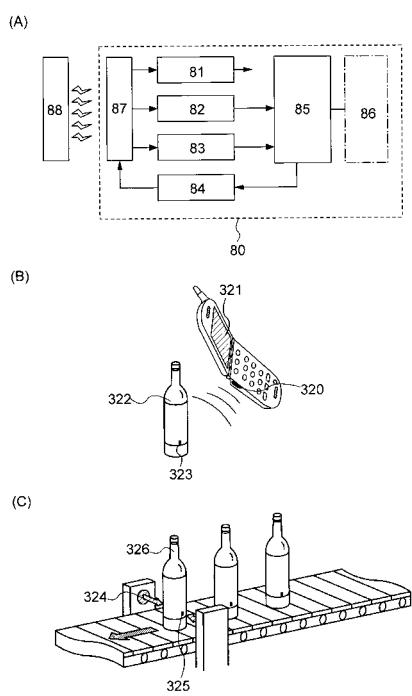

本実施の形態では、本発明の半導体装置を非接触でデータの送受信が可能であるRFIDタグとして利用した場合に関して図11を用いて説明する。

【0075】

10

20

30

40

50

R F I D タグ 8 0 は、非接触でデータを交信する機能を有し、電源回路 8 1、クロック発生回路 8 2、データ復調回路 8 3、データ変調回路 8 4、他の回路を制御する制御回路 8 5、記憶回路 8 6、アンテナ 8 7 とを有している(図11(A))。なお、記憶回路は1つに限定されず、複数であっても良く、S R A M、フラッシュメモリ、R O MまたはF e R A M等や上記実施の形態で示した有機化合物層を記憶素子部に用いたものを用いることができる。

【0076】

リーダ/ライタ 8 8 から電磁波として送られてきた信号は、アンテナ 8 7 において電磁誘導により交流の電気信号に変換される。電源回路 8 1 では、交流の電気信号を用いて電源電圧を生成し、電源配線を用いて各回路へ電源電圧を供給する。クロック発生回路 8 2 は、アンテナ 8 7 から入力された交流信号を基に、各種クロック信号を生成し、制御回路 8 5 に供給する。データ復調回路 8 3 では、当該交流の電気信号を復調し、制御回路 8 5 に供給する。制御回路 8 5 では、入力された信号に従って各種演算処理を行う。より具体的には、制御回路 8 5 は、例えばデータ復調回路 8 3 によって復調された信号を解読する命令解析部や解読された信号をチェックするC R C (C y c l i c R e d u n d a n c y C h e c k)回路、記憶回路 8 6 を制御するメモリコントローラ等を含んでいる。記憶回路 8 6 では、制御回路 8 5 において用いられるプログラムやデータ等が記憶されている他、演算処理時の作業エリアとしても用いることができる。そして、制御回路 8 5 からデータ変調回路 8 4 にデータが送られ、データ変調回路 8 4 から当該データに従ってアンテナ 8 7 に負荷変調を加えることができる。リーダ/ライタ 8 8 は、アンテナ 8 7 に加えられた負荷変調を電磁波で受け取ることにより、結果的にデータを読み取ることが可能となる

【0077】

また、上記回路の周辺に電源配線や接地配線等の配線が設けられており、電源配線や接地配線等の配線は上記実施の形態で示したように非環状で設けられている。なお、R F I D タグは上記構成に制約されず、例えば、電源電圧のリミッタ回路や暗号処理専用ハードウェアといった他の要素を追加した構成であってもよい。

【0078】

また、R F I D タグは、各回路への電源電圧の供給を電源(バッテリ)を搭載せず電磁波により行うタイプとしてもよいし、電源(バッテリ)を搭載して電磁波と電源(バッテリ)により各回路に電源電圧を供給するタイプとしてもよい。

【0079】

本発明の半導体装置をR F I D タグ等に利用した場合、非接触で通信を行う点、複数読み取りが可能である点、データの書き込みが可能である点、様々な形状に加工可能である点、選択する周波数によっては、指向性が広く、認識範囲が広い点等の利点を有する。R F I D タグは、非接触による無線通信で人や物の個々の情報を識別可能なI C タグ、ラベル加工を施して目標物への貼り付けを可能としたラベル、イベントやアミューズメント向けのリストバンド等に適用することができる。また、R F I D タグを樹脂材料により成型加工してもよいし、無線通信を阻害する金属に直接固定してもよい。さらに、R F I D タグは、入退室管理システムや精算システムといった、システムの運用に活用することができる。

【0080】

次に、半導体装置をR F I D タグとして実際に使用するときの一形態について説明する。表示部 3 2 1 を含む携帯端末の側面には、リーダ/ライタ 3 2 0 が設けられ、品物 3 2 2 の側面にはR F I D タグ 3 2 3 が設けられる(図11(B))。品物 3 2 2 が含むR F I D タグ 3 2 3 にリーダ/ライタ 3 2 0 をかざすと、表示部 3 2 1 に品物の原材料や原産地、生産工程ごとの検査結果や流通過程の履歴等、更に商品の説明等の商品に関する情報が表示される。また、商品 3 2 6 をベルトコンベアにより搬送する際に、リーダ/ライタ 3 2 4 と、商品 3 2 6 に設けられたR F I D タグ 3 2 5 を用いて、該商品 3 2 6 の検品を行うことができる(図11(C))。このように、システムにR F I D タグを活用するこ

10

20

30

40

50

とで、情報の取得を簡単に行うことができ、高機能化と高付加価値化を実現する。

#### 【0081】

なお、本実施の形態は、上記実施の形態と自由に組み合わせて行うことができる。

#### 【0082】

##### (実施の形態5)

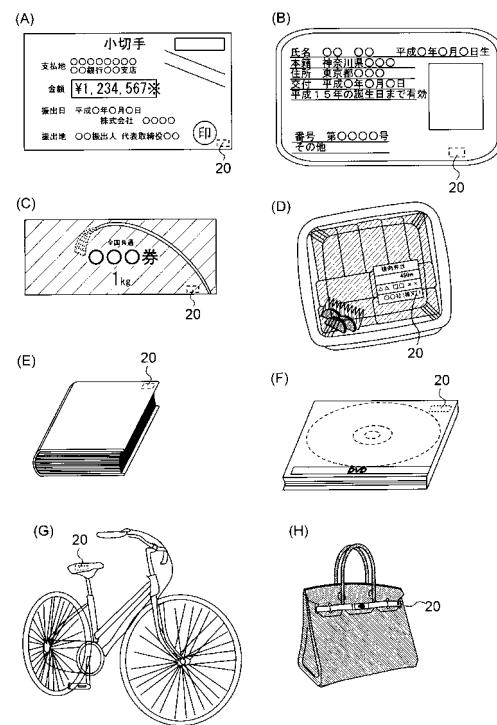

本発明の半導体装置の用途は広範にわたり、非接触で対象物の履歴等の情報を明確にし、生産・管理等に役立てる商品であればどのようなものにも適用することができる。例えば、紙幣、硬貨、有価証券類、証書類、無記名債券類、包装用容器類、書籍類、記録媒体、身の回り品、乗物類、食品類、衣類、保健用品類、生活用品類、薬品類及び電子機器等に設けて使用することができる。これらの例に関して図12を用いて説明する。

10

#### 【0083】

紙幣、硬貨とは、市場に流通する金銭であり、特定の地域で貨幣と同じように通用するもの（金券）、記念コイン等を含む。有価証券類とは、小切手、証券、約束手形等を指す（図12（A）参照）。証書類とは、運転免許証、住民票等を指す（図12（B）参照）。無記名債券類とは、切手、おこめ券、各種ギフト券等を指す（図12（C）参照）。包装用容器類とは、お弁当等の包装紙、ペットボトル等を指す（図12（D）参照）。書籍類とは、書物、本等を指す（図12（E）参照）。記録媒体とは、DVDソフト、ビデオテープ等を指す（図12（F）参照）。乗物類とは、自転車等の車両、船舶等を指す（図12（G）参照）。身の回り品とは、鞄、眼鏡等を指す（図12（H）参照）。食品類とは、食料品、飲料等を指す。衣類とは、衣服、履物等を指す。保健用品類とは、医療器具、健康器具等を指す。生活用品類とは、家具、照明器具等を指す。薬品類とは、医薬品、農薬等を指す。電子機器とは、液晶表示装置、EL表示装置、テレビジョン装置（テレビ受像機、薄型テレビ受像機）、携帯電話等を指す。

20

#### 【0084】

紙幣、硬貨、有価証券類、証書類、無記名債券類等にRFIDタグを設けることにより、偽造を防止することができる。また、包装用容器類、書籍類、記録媒体等、身の回り品、食品類、生活用品類、電子機器等にRFIDタグを設けることにより、検品システムやレンタル店のシステムなどの効率化を図ることができる。乗物類、保健用品類、薬品類等にRFIDタグを設けることにより、偽造や盗難の防止、薬品類ならば、薬の服用の間違いを防止することができる。RFIDタグの設け方としては、物品の表面に貼ったり、物品に埋め込んだりして設ける。例えば、本ならば紙に埋め込んだり、有機樹脂からなるパッケージなら当該有機樹脂に埋め込んだりするとよい。また、後に光学的作用を加えて書き込み（追記）をする場合には、チップに設けられた記憶素子の部分に光が照射できるよう透明な材料で形成しておくことが好ましい。さらに、一度書き込んだデータの書き換えが不可能である記憶素子を用いることによって、効果的に偽造を防止することができる。また、ユーザーが商品を購入した後のプライバシー等の問題についても、RFIDタグに設けられた記憶素子のデータを消去するシステムを設けておくことによって解決することができる。

30

#### 【0085】

このように、包装用容器類、記録媒体、身の回り品、食品類、衣類、生活用品類、電子機器等にRFIDタグを設けることにより、検品システムやレンタル店のシステムなどの効率化を図ることができる。また乗物類にRFIDタグを設けることにより、偽造や盗難を防止することができる。また、動物等の生き物に埋め込むことによって、個々の生き物の識別を容易に行うことができる。例えば、家畜等の生き物にセンサを備えたRFIDタグを埋め込むことによって、生まれた年や性別または種類等はもちろん現在の体温等の健康状態を容易に管理することができる。

40

#### 【0086】

以上のように、本発明の半導体装置はどのようなものにでも設けて使用することができる。なお、本実施の形態は、上記実施の形態と自由に組み合わせて行うことができる。

#### 【図面の簡単な説明】

50

## 【0087】

- 【図1】本発明の半導体装置の一構成例を示す図。

【図2】本発明の半導体装置の一構成例を示す図。

【図3】本発明の半導体装置の一構成例を示す図。

【図4】従来の半導体装置の一構成例を示す図。

【図5】従来の半導体装置の一構成例を示す図。

【図6】本発明の半導体装置の作製方法の一構成例を示す図。

【図7】本発明の半導体装置の作製方法の一構成例を示す図。

【図8】本発明の半導体装置の作製方法の一構成例を示す図。

【図9】本発明の半導体装置の作製方法の一構成例を示す図。

【図10】本発明の半導体装置の作製方法の一構成例を示す図。

【図11】本発明の半導体装置の使用形態を示す図。

【図12】本発明の半導体装置の使用形態を示す図。

10

## 【符号の説明】

## 【0088】

- 20 基板

21 アンテナ

22 素子形成層

23 電源配線

24 接地配線

25 電源回路

26 機能回路

27 機能回路

28 機能回路

70 基板

71 アンテナ

72 素子形成層

73 電源配線

74 接地配線

75 電源回路

76 機能回路

77 機能回路

78 電流

701 基板

702 剥離層

703 絶縁膜

704 非晶質半導体膜

705 絶縁膜

706 結晶質半導体膜

707 結晶質半導体膜

708 結晶質半導体膜

709 結晶質半導体膜

710 結晶質半導体膜

711 N型不純物領域

712 P型不純物領域

713 N型不純物領域

714 N型不純物領域

715 N型不純物領域

716 導電膜

717 導電膜

20

30

40

50

|       |          |    |

|-------|----------|----|

| 7 1 8 | 導電膜      |    |

| 7 1 9 | 導電膜      |    |

| 7 2 0 | 導電膜      |    |

| 7 2 1 | 導電膜      |    |

| 7 2 2 | 導電膜      |    |

| 7 2 3 | 導電膜      |    |

| 7 2 4 | 導電膜      |    |

| 7 2 5 | 導電膜      |    |

| 7 2 6 | N型不純物領域  | 10 |

| 7 2 7 | N型不純物領域  |    |

| 7 2 8 | N型不純物領域  |    |

| 7 2 9 | N型不純物領域  |    |

| 7 3 0 | N型不純物領域  |    |

| 7 3 1 | N型不純物領域  |    |

| 7 3 2 | N型不純物領域  |    |

| 7 3 3 | N型不純物領域  |    |

| 7 3 4 | 絶縁膜      |    |

| 7 3 5 | 絶縁膜      |    |

| 7 3 6 | 絶縁膜      |    |

| 7 3 7 | 絶縁膜      | 20 |

| 7 3 8 | 絶縁膜      |    |

| 7 3 9 | 絶縁膜      |    |

| 7 4 0 | 絶縁膜      |    |

| 7 4 1 | 絶縁膜      |    |

| 7 4 2 | 絶縁膜      |    |

| 7 4 3 | 絶縁膜      |    |

| 7 4 4 | 薄膜トランジスタ |    |

| 7 4 5 | 薄膜トランジスタ |    |

| 7 4 6 | 薄膜トランジスタ |    |

| 7 4 7 | 薄膜トランジスタ | 30 |

| 7 4 8 | 薄膜トランジスタ |    |

| 7 4 9 | 絶縁膜      |    |

| 7 5 0 | 絶縁膜      |    |

| 7 5 1 | 絶縁膜      |    |

| 7 5 2 | 導電膜      |    |

| 7 5 3 | 導電膜      |    |

| 7 5 4 | 導電膜      |    |

| 7 5 5 | 導電膜      |    |

| 7 5 6 | 導電膜      |    |

| 7 5 7 | 導電膜      | 40 |

| 7 5 8 | 導電膜      |    |

| 7 5 9 | 導電膜      |    |

| 7 6 0 | 導電膜      |    |

| 7 6 1 | 導電膜      |    |

| 7 6 2 | 絶縁膜      |    |

| 7 6 3 | 導電膜      |    |

| 7 6 4 | 導電膜      |    |

| 7 6 5 | 導電膜      |    |

| 7 6 6 | 絶縁膜      |    |

| 7 6 7 | コンタクトホール | 50 |

|       |            |    |

|-------|------------|----|

| 7 6 8 | コンタクトホール   |    |

| 7 6 9 | コンタクトホール   |    |

| 7 7 1 | 導電膜        |    |

| 7 7 2 | 絶縁膜        |    |

| 7 7 3 | 開口部        |    |

| 7 7 4 | 開口部        |    |

| 7 8 0 | チャネル形成領域   |    |

| 7 8 1 | チャネル形成領域   |    |

| 7 8 2 | チャネル形成領域   |    |

| 7 8 3 | チャネル形成領域   | 10 |

| 7 8 4 | チャネル形成領域   |    |

| 7 8 5 | P型不純物領域    |    |

| 7 8 6 | 導電膜        |    |

| 7 8 7 | 有機化合物層     |    |

| 7 8 9 | 記憶素子部      |    |

| 7 9 0 | 記憶素子部      |    |

| 7 9 1 | 素子形成層      |    |

| 7 7 5 | 第1のシート材    |    |

| 7 7 6 | 第2のシート材    |    |

| 7 7 7 | 第3のシート材    | 20 |

| 8 0   | R F I D タグ |    |

| 8 1   | 電源回路       |    |

| 8 2   | クロック発生回路   |    |

| 8 3   | データ復調回路    |    |

| 8 4   | データ変調回路    |    |

| 8 5   | 制御回路       |    |

| 8 6   | 記憶回路       |    |

| 8 7   | アンテナ       |    |

| 8 8   | リーダ/ライタ    |    |

| 3 2 1 | 表示部        | 30 |

| 3 2 0 | リーダ/ライタ    |    |

| 3 2 2 | 品物         |    |

| 3 2 3 | R F I D タグ |    |

| 3 2 6 | 商品         |    |

| 3 2 4 | リーダ/ライタ    |    |

| 3 2 5 | R F I D タグ |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

---

フロントページの続き

(51)Int.Cl. F I

**G 0 6 K 19/077 (2006.01)** G 0 6 K 19/00 K

(56)参考文献 特開2003-109819 (JP, A)

特開2001-284460 (JP, A)

特開平06-053449 (JP, A)

再公表特許第2003/015169 (JP, A1)

特開2003-078023 (JP, A)

特開2004-282050 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/822

G 06 K 19/07

G 06 K 19/077

H 01 L 21/82

H 01 L 27/04

H 01 L 29/786