(19) 日本国特許庁 (JP)

(12) 公表特許公報(A)

(11) 特許出願公表番号

特表2020-507176

(P2020-507176A)

(43) 公表日 令和2年3月5日(2020.3.5)

(51) Int.Cl.

**G 06 F 13/42 (2006.01)**

HO3K 5/00 (2006.01)

G06F 1/12 (2006.01)

F 1

GO 6 F 13/42

HO3K 5/00

GO 6 F 1/12

350

510

### テーマコード（参考）

5 B 077

審查請求 未請求 予備審查請求 未請求 (全 15 頁)

|                    |                              |

|--------------------|------------------------------|

| (21) 出願番号          | 特願2019-562234 (P2019-562234) |

| (86) (22) 出願日      | 平成30年1月31日 (2018. 1. 31)     |

| (85) 翻訳文提出日        | 令和1年9月30日 (2019. 9. 30)      |

| (86) 國際出願番号        | PCT/US2018/016206            |

| (87) 國際公開番号        | W02018/144583                |

| (87) 國際公開日         | 平成30年8月9日 (2018. 8. 9)       |

| (31) 優先権主張番号       | 15/420, 267                  |

| (32) 優先日           | 平成29年1月31日 (2017. 1. 31)     |

| (33) 優先権主張国・地域又は機関 | 米国 (US)                      |

(71) 出願人 390020248

日本テキサス・インスツルメンツ合同会社

東京都新宿区西新宿六丁目24番1号

(71) 出願人 507107291

テキサス インスツルメンツ インコーポ

レイテッド

アメリカ合衆国 テキサス州 75265

-5474 ダラス メイル ステイショ

ン 3999 ピーオーボックス 655

474

(74) 上記1名の代理人 100098497

弁理士 片寄 泰三

最終頁に続く

(54) 【発明の名称】低速周辺機器のための中止処理方法及び装置

(57) 【要約】

記載される例は、中断処理回路要素（100）と、第2のクロック信号（SCLK）に従って動作される低速クロックドメイン回路（102）によって第1のクロック信号（FCLK）に従って動作される高速クロックドメイン回路（101）の中断を処理する方法を含み、中断生成器回路（110）が、第2のクロック信号（SCLK）に同期される中断入力信号（INT\_IN）を生成し、中断クリア回路（114、116）が、第2のクロック信号（SCLK）に対して非同期に第1の回路（101）からの確認信号（ACK）に応答して中断生成器回路（110）を選択的にリセットする。

FIG. I

**【特許請求の範囲】****【請求項 1】**

第1のクロック信号より遅い第2のクロック信号に従って動作される第2の回路によって前記第1のクロック信号に従って動作される前記第1の回路の中止を管理する中止処理回路であって、

中止処理回路であって、中止要求信号を受信するための第1の中止生成器入力と、中止クリア信号を受信するための第2の中止生成器入力と、前記第1の回路を選択的に中止するために前記中止要求信号に同期される中止入力信号を提供するための中止生成器出力を含む、前記中止生成器回路、及び

前記第1の回路からの確認信号に応答して前記中止生成器回路をリセットするため前記中止クリア信号を選択的に提供するために前記第1のクロック信号に同期される出力を含む中止クリア回路、

を含む、中止処理回路。

**【請求項 2】**

請求項1に記載の中止処理回路であって、

前記中止要求信号が、前記第2の回路によって中止が要求されていないことを示す第1の状態と、前記第2の回路によって中止が要求されていることを示す異なる第2の状態とを有し、

前記中止クリア信号が、第1の状態と、異なる第2の状態とを有し、

前記中止生成器出力が、第1の状態の前記中止クリア信号を受信する前記第2の中止生成器入力に応答して前記第1の状態の前記中止入力信号を提供するように、及び、前記中止クリア信号が第2の状態にあるとき前記第1の状態から前記第2の状態に遷移する前記中止要求信号に応答して異なる第2の状態の中止入力信号を提供するように構成され、

前記中止クリア回路が、前記第1の回路からの前記確認信号に応答して前記中止入力信号を前記第1の状態に設定するために前記中止生成器回路をリセットするために、前記第1の状態の前記中止クリア信号を選択的に提供するように構成される、

中止処理回路。

**【請求項 3】**

請求項2に記載の中止処理回路であって、同期化回路を更に含み、

前記同期化回路が、前記中止入力信号を受信するために前記中止生成器出力に結合される入力と、前記第1の回路に中止出力信号を提供するために前記第1のクロック信号に同期される出力を含む、

中止処理回路。

**【請求項 4】**

請求項3に記載の中止処理回路であって、前記同期化回路が、

前記中止生成器出力に接続されるデータ入力と、前記第1のクロック信号を受信するために前記第1の回路に接続されるクロック入力と、出力とを含む第1のフリップフロップ、及び

第2のフリップフロップであって、前記第1のフリップフロップの前記出力に接続されるデータ入力と、前記第1のクロック信号を受信するため前記第1の回路に接続されるクロック入力と、前記第1の回路に同期される前記中止出力信号を提供するため前記第1の回路に接続される出力を含む、前記第2のフリップフロップ、

を含む、中止処理回路。

**【請求項 5】**

請求項4に記載の中止処理回路であって、

前記中止生成器回路が第3のフリップフロップを含み、前記第3のフリップフロップが、基準電圧に接続されるデータ入力と、前記中止要求信号を受信するために接続されるクロック入力と、前記中止クリア信号を受信するため前記中止クリア回路の前記出力に接続されるクリア入力と、前記中止入力信号を前記第1のフリップフロップの前記データ入力に提供するため前記中止生成器出力に接続される出力を含む、

10

20

30

40

50

中断処理回路。

【請求項 6】

請求項 3 に記載の中断処理回路であって、

前記中断生成器回路がフリップフロップを含み、前記フリップフロップが、基準電圧に接続されるデータ入力と、前記中断要求信号を受信するために接続されるクロック入力と、前記中断クリア信号を受信するために前記中断クリア回路の前記出力に接続されるクリア入力と、前記中断入力信号を前記同期化回路の前記入力に提供するため前記中断生成器出力に接続される出力を含む、

中断処理回路。

【請求項 7】

10

請求項 2 に記載の中断処理回路であって、

前記中断生成器回路がフリップフロップを含み、前記フリップフロップが、基準電圧に接続されるデータ入力と、前記中断要求信号を受信するために接続されるクロック入力と、前記中断クリア信号を受信するために前記中断クリア回路の前記出力に接続されるクリア入力と、前記中断入力信号を提供するため前記中断生成器出力に接続される出力を含む、

中断処理回路。

【請求項 8】

20

請求項 7 に記載の中断処理回路であって、

第 2 のフリップフロップを更に含み、前記第 2 のフリップフロップが、前記中断要求信号を受信するために前記第 2 の回路に接続されるデータ入力と、前記第 2 のクロック信号を受信するために接続されるクロック入力と、前記第 2 のクロック信号に同期される同期された中断要求信号を提供するための出力を含む、

中断処理回路。

【請求項 9】

請求項 1 に記載の中断処理回路であって、前記第 1 の回路、前記第 2 の回路、前記中断生成器回路、及び前記中断クリア回路が单一の集積回路において形成される、中断処理回路。

【請求項 10】

30

第 1 のクロック信号より遅い第 2 のクロック信号に従って動作される第 2 の回路によって前記第 1 のクロック信号に従って動作される前記第 1 の回路の中断を管理する中断処理回路であって、前記中断処理回路が、

前記第 1 のクロック信号に対して同期して前記第 1 の回路を選択的に中断するための中斷生成器回路、及び

前記第 2 のクロック信号に対して非同期に前記第 1 の回路からの確認信号に応答して前記生成器回路を選択的にリセットするための出力を含む中断クリア回路、

を含む、中断処理回路。

【請求項 11】

40

請求項 10 に記載の中断処理回路であって、前記中断生成器回路の出力に結合される入力と、前記第 1 の回路に中断出力信号を提供するために前記第 1 のクロック信号に同期される出力を含む同期化回路を更に含む、中断処理回路。

【請求項 12】

請求項 11 に記載の中断処理回路であって、前記同期化回路が、

前記中断生成器回路の出力に接続されるデータ入力と、前記第 1 のクロック信号を受信するために前記第 1 の回路に接続されるクロック入力と、出力を含む第 1 のフリップフロップ、及び

前記第 1 のフリップフロップの前記出力に接続されるデータ入力と、前記第 1 のクロック信号を受信するために前記第 1 の回路に接続されるクロック入力と、前記第 1 のクロック信号に同期される前記中断出力信号を提供するために前記第 1 の回路に接続される出力を含む第 2 のフリップフロップ、

50

を含む、中断処理回路。

**【請求項 1 3】**

請求項 1 2 に記載の中断処理回路であって、前記中断生成器回路が第 3 のフリップフロップを含み、

前記第 3 のフリップフロップが、基準電圧に接続されるデータ入力と、中断要求信号を受信するために前記第 1 の回路に接続されるクロック入力と、前記中断クリア回路から中断クリア信号を受信するために接続されるクリア入力と、前記中断生成器回路をリセットするための中断入力信号を選択的に提供するための出力とを含む、

中断処理信号。

**【請求項 1 4】**

請求項 1 0 に記載の中断処理回路であって、フリップフロップを更に含み、

前記フリップフロップが、前記第 2 の回路から中断要求信号を受信するためのデータ入力と、前記第 2 のクロック信号を受信するために接続されるクロック入力と、前記第 1 の回路を選択的に中断するため、前記第 2 のクロック信号に同期される同期された中断要求信号を前記中断生成器回路に提供するための出力とを含む、

中断処理生成器回路。

**【請求項 1 5】**

請求項 1 0 に記載の中断処理回路であって、前記第 1 の回路、前記第 2 の回路、前記中断生成器回路、及び前記中断クリア回路が、単一の集積回路に形成される、中断処理回路。

。

**【請求項 1 6】**

第 1 のクロック信号より遅い第 2 のクロック信号に従って動作される第 2 の回路によって前記第 1 のクロック信号に従って動作される第 1 の回路の中断を管理する方法であって、前記方法が、

前記第 2 のクロック信号に同期される中断入力信号を生成すること、

前記中断入力信号に応答して前記第 1 の回路に中断出力信号を提供すること、及び

前記第 1 の回路からの確認信号に応答して前記第 2 のクロック信号に対して非同期に前記中断入力及び出力信号をクリアすること、

を含む、方法。

**【請求項 1 7】**

請求項 1 6 に記載の方法であって、前記中断出力信号を前記第 1 のクロック信号に同期させることを更に含む、方法。

**【請求項 1 8】**

請求項 1 7 に記載の方法であって、前記確認信号の前記第 1 のクロック信号の 2 サイクル以内に前記中断入力及び出力信号をクリアすることを更に含む、方法。

**【請求項 1 9】**

請求項 1 6 に記載の方法であって、前記確認信号の前記第 1 のクロック信号の 2 サイクル以内に前記中断入力及び出力信号をクリアすることを更に含む、方法。

**【請求項 2 0】**

請求項 1 6 に記載の方法であって、

前記第 2 の回路から中断要求信号を受信すること、

前記中断要求信号に応答して前記中断入力信号を生成すること、及び

前記第 2 のクロック信号に対して非同期に前記中断入力信号に応答して前記第 1 の回路に前記中断出力信号を提供すること、

を更に含む、方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

電子回路及びシステムは、しばしば、様々なクロック速度で動作する複数の回路セグメント又はクロックドメインを含む。例えば、プロセッサ回路は、大抵、高クロック速度で

動作し、ずっと低いクロック速度で動作する一つ又は複数の周辺機器回路と相互作用する。低速クロックドメイン回路は、高速クロックドメイン回路によるサービスのための中止（interrupt）サービス要求を生成することが多い。低速クロックドメイン回路からの中断をサービス及びクリアすることは、多くの高速クロックサイクルを要し得、高速クロックドメイン回路が他の中断をサービスすることができないことにつながる可能性がある。一例では、非常に遅い周波数（例えば、10～100 kHz）で動作する周辺機器回路からの中断が、1～100 MHz又はそれ以上の高クロックの周波数で動作するCPUによって実行されるアプリケーションソフトウェアが、カウンタ値が所定の値に達することによってトリガされた中断に応答して、低クロック速度パルス幅変調（PWM）制御回路のレジスタに新しいカウンタ値を更新又は書き込む必要がある場合がある。以前の中止処理手法及び回路は、サービスしているCPUからのクリア要求を低速クロック信号に同期させ、及び／又は、中断要求をクリアするためにハンドシェーカープローチを用いる。この結果、周辺機器回路がクリア要求を受信し、中断要求信号を除去するまでに、二つ又はそれ以上の遅いクロックサイクルの遅延となる。この中断クリア遅延は、特に高速及び低速クロック速度の大きな差に対して著しい。10 kHzの機能クロックで動作する周辺機器の場合、遅延は少なくとも200マイクロ秒であり、これは100 MHzで動作するCPUにとって著しい。この時間の間、高速クロックドメインCPUは、同じサービスルーティングへの再エンタリ回避するために待機しなければならない。また、初期の中止がクリアされる前に周辺機器回路内に別の中断事象が生じた場合、同じ周辺機器からの新しい中断事象が失われることになる。また、従来の中止処理回路及び手法は、ある程度のレイテンシを伴う中断要求を生成する。例えば、低速クロックドメイン中止生成条件は、立ち上がり低速クロックエッジに基づき得、中断要求信号は立ち上がり低速クロックエッジに従って生成されるか、又はその逆であり、低速クロック信号への同期化が、中断事象をサービスする際に更なる遅延をもたらす。

10

20

30

40

#### 【発明の概要】

#### 【0002】

記載される例は、低速クロックドメイン第2の回路による高速クロックドメイン第1の回路の中止を処理するための中止処理回路要素及び方法を含み、第1の回路は第1のクロック信号に従って動作し、第2の回路は第1のクロック信号より低速の第2のクロック信号に従って動作する。説明される中止処理回路が、中止入力信号を生成する中止生成器回路と、第2のクロック信号に対して非同期に第1の回路からの確認信号に応答して中止生成器回路をリセットする中止クリア回路とを含む。

#### 【0003】

特定の例において、中止生成器回路は、中止要求信号を受信するための第1の入力と、中止クリア信号を受信するための第2の入力と、第1の回路を選択的に中止するために中止要求信号に同期される中止入力信号を提供するための出力とを含む。一例における中止クリア回路は、第1の回路からの確認信号に応答して中止生成器回路をリセットするための中止クリア信号を提供するために、第1のクロック信号に同期される出力を含む。

#### 【0004】

より低速の第2のクロック信号に従って動作される第2の回路によって第1のクロック信号に従って動作される第1の回路の中止を管理する方法を説明する。この方法は、第2のクロック信号に同期される中止入力信号を生成すること、中止入力信号に応答して第1の回路に中止出力信号を提供すること、第1の回路からの確認信号に応答して第2のクロック信号に対して非同期に中止入力及び出力信号をクリアすることを含む。

#### 【図面の簡単な説明】

#### 【0005】

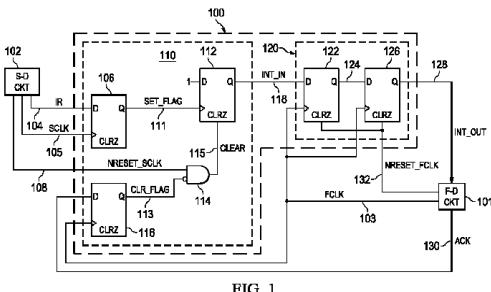

【図1】低速クロックドメイン第2の回路による高速クロックドメイン第1の回路の中止を管理するように構成される中止処理回路を示す概略図である。

#### 【0006】

50

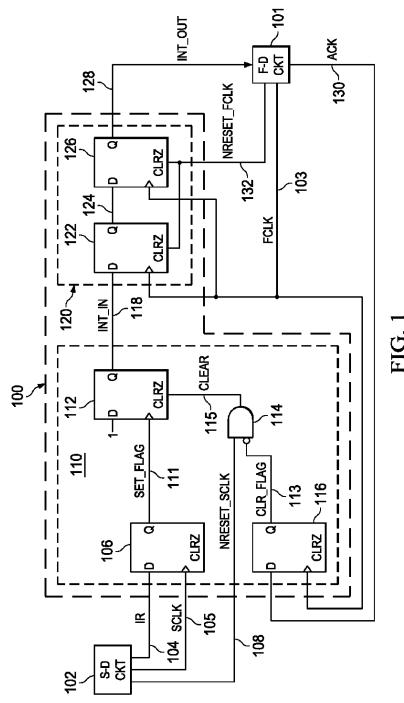

【図2】高速及び低速クロック速度の任意の比に対する図1の回路における動作信号を示す信号図である。

【0007】

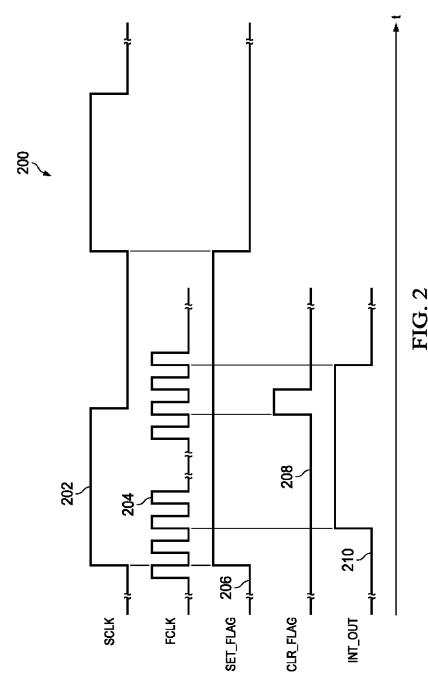

【図3】高速及び低速クロック速度の1つの例示的な比に対する図1の回路における動作信号を示す信号図である。

【0008】

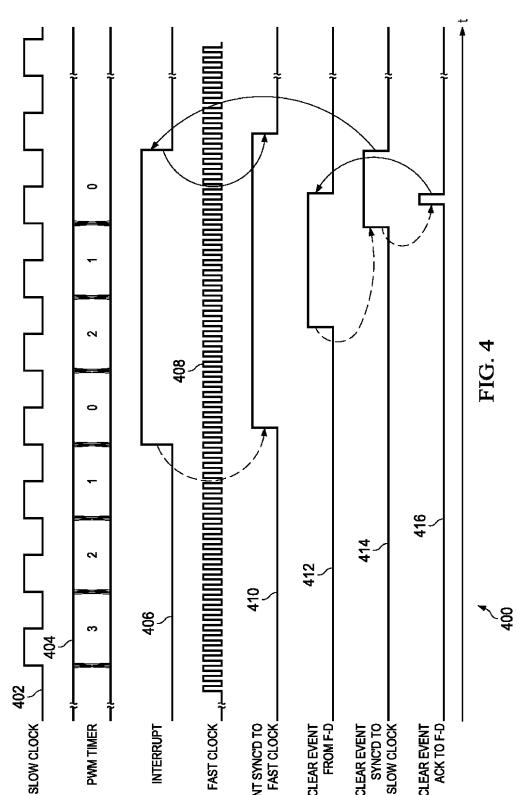

【図4】ミスした中断事象を有するハンドシェーティング確認中断処理手法を示す信号図である。

【0009】

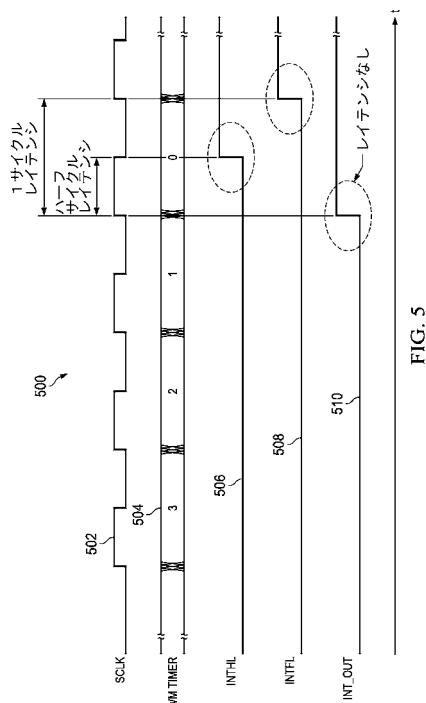

【図5】同期化遅延を有する中断生成を示す信号図である。

10

【0010】

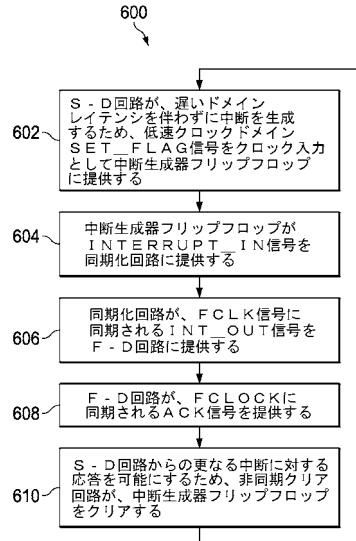

【図6】低速ドメイン回路による高速ドメイン回路の中断を管理するためのプロセス又は方法を図示するフローチャートである。

【発明を実施するための形態】

【0011】

図面において、全体を通して同様の参照番号は同様の要素を示し、種々の特徴は必ずしも一定の縮尺で描いてはいらない。本説明において、「結合する」という用語は、間接的又は直接的な電気的又は機械的接続又はそれらの組み合わせを含む。例えば、第1のデバイスが第2のデバイスに結合するか、又は第2のデバイスと結合される場合、その接続は、直接電気的接続を介し得、又は一つ又は複数の介在デバイス及び接続を介した間接的電気的接続を介し得る。

20

【0012】

記載される例は、集積回路と、より遅い第2のクロック信号に従って動作される第2の回路によって第1のクロック信号に従って動作される第1の回路の中断を管理するための中断処理回路要素及びプロセスとを含む。記載された手法は、第1及び第2のクロックドメイン又は回路が、互いに非同期又は同期であり得る異なるクロック速度に従って動作される、種々の異なる応用例において用いられ得る。また、本記載される例は、単一の集積回路の第1及び第2のクロックドメイン回路に関連して、又は個別のI C上の高速及び低速クロックドメイン回路又はその組み合わせに対して用いられ得る中断処理回路要素及び方法を提供する。

30

【0013】

図1は、中断処理回路100と、第1の回路101(図ではF D CKTと記される「高速ドメイン回路」と、第2の回路102(図1ではS D CKTと記される「低速ドメイン回路」と)を含むシステムを示す。第1及び第2の回路101及び102は、それぞれ、異なった第1及び第2のクロック信号のFCLK及びSCLKに従って動作する。回路101及び102は個別の集積回路(I C)において形成することもでき、又は、単一の集積回路上の複数の回路ともし得る。回路101、102は、対応するクロック信号FCLK、SCLKに従ったオペレーションを介する2つの個別のクロックドメインの一部である。クロック信号FCLK及びSCLKはすべての実施例の厳密な要件ではないが、クロック位相及び/又はクロック周波数に関して互いに独立して動作し得る。第1のクロック信号FCLKは、回路ノード103上の第1の回路101のクロックソース(図示せず)によって提供され、クロック信号SCLKは、ノード105上の第2の回路102のクロックソース(図示せず)によって提供される。第2のクロック信号SCLKは、この例において第1のクロック信号FCLKよりも遅い。

40

【0014】

中断処理回路100は、中断生成器回路110と、同期化回路120と、第1の回路101によってサービスされる第2の回路102に関連する中断事象のシグナリング及びクリアを管理する中断クリア回路114、116とを含む。この例において、中断生成器回路110は、入力104及び105並びに出力118を含み、第1のクロック信号のFCLKに対して同期して第1の回路101を選択的に中断する。中断クリア回路114、116

50

16は、フリップフロップ116と、ANDゲート114と、第1の回路101からの確認信号ACKに応答して中断生成器回路110をリセットする中断クリア信号CLEARを選択的に提供するために第1のクロック信号CLKに同期される出力115とを含む。また、中断クリア回路114、116は、第2のクロック信号のSCLKに対して非同期に中断生成器回路110をクリア又はリセットする。このようにして、中断処理回路100は、従来の中断クリア回路に関連する同期化遅延を軽減又は回避し、中断生成器回路110による第2の回路102からの更なる中断への応答を容易にする。

#### 【0015】

オペレーションにおいて、第2の回路102は、中断生成器回路110への入力としてノード104上に中断要求信号IRを提供する。第2の回路102はまた、中断生成器回路をリセットするためリセット信号RESET\_SCLKを提供する出力ノード108を含む。中断生成器回路110は、同期化回路120への入力としてノード118において中断入力信号INT\_INを提供する。同期化回路120は、第1の回路101に接続されるノード128において中断出力信号IN\_OUTを提供する。次に、第1の回路101は、中断をサービスし、中断クリア回路114、116への入力として提供される、回路ノード130上の確認信号ACKを生成する。中断クリア回路114、116は、中断入力信号INT\_INをクリアするため、ノード115において中断クリア信号CLEARを生成する。

10

#### 【0016】

従来の高速／低速クロックドメイン中断処理回路及び手法は、典型的に、中断要求シグナリングにレイテンシ又は遅延を導入し、低速クロックドメインクリア信号同期化に起因する著しい遅延を受け、これは、中断のサービス及びクリアにおける遅延、及び潜在的に中断事象が失われるか又はミスされることにつながる恐れがある。

20

#### 【0017】

第1の問題に対処するため、本開示は、著しいレイテンシなしに中断を生成し得る解決策を提供する。この例では、中断生成器回路110は、このケースではデータ又は「D」フリップフロップである中断フラグ又は中断生成器フリップフロップ112を含み、これは、フリップフロップ106から受信した回路ノード111上の同期された中断要求信号SET\_FLAGに従って中断入力信号INT\_INを生成する。フリップフロップ106は、ノード104からの中断要求信号IRをデータ入力として受信し、低速クロックノード105に接続されるクロック入力を含む。オペレーションにおいて、第2の回路102は、アクティブハイ状態の中断要求信号IRを活性化し、フリップフロップ106は、低速クロック信号SCLKの次の立ち上がりエッジで、ハイ状態のノード111上の信号SET\_FLAGを生成する。中断生成器フリップフロップ112のデータ(D)入力は、論理ハイ信号(図1における「1」)に接続され、フリップフロップ112のクロック入力は、同期された中断要求信号SET\_FLAGをノード111から受信するよう接続される。ANDゲート114は、フリップフロップ112のクリア入力CLRZにCLEAR信号を提供して、第1の回路101からの確認信号ACKに応答して中断生成器回路110を選択的にリセットする。

30

#### 【0018】

中断生成器出力118は、ローの第1の状態の中断クリア信号CLEARを受信する第2の中断生成器入力115に応答して、ローの第1の状態の中断入力信号INT\_INを提供する。出力118は、中断クリア信号CLEARがハイの第2の状態にあるとき、ローへハイ遷移及び同期された中断要求信号SET\_FLAGに応答して、ハイの第2の状態の中断入力信号INT\_INを提供する。CLEAR信号がハイであるとき、フリップフロップ112は、中断要求信号IRがハイ状態でアサートされたとき、低速クロック信号SCLKの立ち上がりエッジ時又はその直後に、アクティブハイ状態の中断入力信号INT\_INを生成する。このようにして、中断要求信号SET\_FLAGは、準安定性の問題を回避又は緩和するために、フリップフロップ106によって第2のクロック信号のSCLKに同期される。中断生成回路要素110は、図5に関連して以下に説明するように

40

50

ハーフサイクル又はフルサイクル同期化遅延を被ることが多い、その他の中断生成回路要素と比較して著しい利点を提供する。回路 110 は、有利にも、第 2 の回路 102 から受信した中断要求信号 IR の立ち上がりエッジに対してタイマリーに中断入力信号 INT\_IN をアサートする。

#### 【0019】

中断クリア回路 114、116 は、第 1 の回路 101 からの確認信号 ACK に応答して、中断クリア信号 CLEAR を低レベルの第 1 の状態で提供して、中断生成器回路 110 をリセットして、中断入力信号 INT\_IN を低レベルの第 1 の状態に設定する。この例において、フリップフロップ 116 は D フリップフロップであり、データ入力「D」は、確認信号 ACK を受信するためにノード 130 に接続され、クロック入力が、第 1 のクロック信号 FCLK を受信するためにノード 103 に接続される。フリップフロップ 116 の出力「Q」は、図 1 に示すように、ノード 113 上にクリアフラグ信号 CLR\_FLAG を提供するように接続される。AND ゲート 114 は、反転入力を介して CLR\_FLAG 信号を受信し、ノード 108 を介して第 2 の回路 102 からリセット信号 RESET\_SCLK を受信する。AND ゲート 114 へのこの第 2 の入力は、第 2 の回路 102 が AND ゲート 114 をリセットすることを可能にする。他のあり得る実装において、AND ゲート 114 を省くことができ、CLR\_FLAG 信号が中断生成器フリップフロップ 112 の CLRZ 入力に直接的に提供され得る。オペレーションにおいて、クリア回路要素 114、116 は、第 2 のクロック信号 SCLK に関連する遅延を同期させることなくハイに向かう ACK 信号に応答してフリップフロップ 112 を迅速にクリアし、中断入力信号 INT\_IN 及び中断出力信号 INT\_OUT を低速クロック信号 SCLK に対して非同期的にローにする。このようにして、第 1 の回路 101 が保留中の中断をサービスすると、保留中の中断信号 INT\_OUT は迅速にクリアされ、したがって、第 1 の回路 101 は、第 2 の回路 102 からの更なる後続の中断を受信し、適切にサービスし得る。

#### 【0020】

この例において、中断処理回路 100 は同期化回路 120 も含む。オペレーションにおいて、回路 120 は、中断生成器回路 110 によって生成された INT\_IN 信号に関する準安定性の問題を回避するために、高速の第 1 のクロック信号 FCLK に対して中断入力信号 INT\_IN を迅速に同期させる。同期化回路 120 は、中断入力信号 INT\_IN を受信するために中断生成器出力 118 に結合される入力と、中断出力信号 INT\_OUT を第 1 の回路 101 に提供するために第 1 のクロック信号 FCLK に同期される出力 128 とを含む。この例において回路 120 は、中断生成器出力 118 に接続されるデータ入力 D を有する第 1 のフリップフロップ 122 と、第 1 のクロック信号 FCLK を受信するように接続されるクロック入力を含む。第 1 の同期フリップフロップ 122 の出力 124 (Q) は、ノード 103 において第 1 のクロック信号 FCLK に接続されるクロック入力も有する第 2 の同期フリップフロップ 126 のデータ入力 D に接続される。第 2 の同期フリップフロップ 126 の出力 Q は、第 1 の回路 101 に接続されて、第 1 のクロック信号 FCLK に同期される中断出力信号 INT\_OUT を提供する。同期化フリップフロップ 122 及び 126 は、各々、第 1 の回路 101 によって回路ノード 132 上に提供されるリセット信号 RESET\_FCLK を受け取るように接続されるアクティブローのクリア入力 CLRZ を含む。

#### 【0021】

図 2 は、高速及び低速クロック速度の任意の比のための図 1 の中断処理回路 100 における動作信号を図示する信号図 200 を示す。この例において、第 2 のクロック信号 SCLK の 2 つの例示的なサイクルがカーブ (curve) 202 として示され、FCLK カーブ 204 が、任意の数の高速クロック信号遷移を有し得、第 1 及び第 2 のクロック信号 FCLK 及び SCLK は、クロック速度及び位相関係に関して互いに対しても完全に非同期とし得る。図 2 において分かるように、中断生成器回路 110 のフリップフロップ 106 は、第 2 のクロック信号 SCLK (カーブ 202) の立ち上がりエッジで第 2 の回路 102 からの中断要求信号 IR の立ち上がりエッジに応答して、SET\_FLAG 信号 (カーブ 2

10

20

30

40

50

06) アクティブハイをアサートする。中断生成器回路110は、中断入力信号INT\_INを生成し、同期化回路120はこの信号を同期化し、第2のクロック信号SCLKに對して非同期に2つのFCLKサイクル内で中断出力信号INT\_OUT(カーブ210)において立ち上がりエッジを生成する。高速ドメインの第1の回路101が、関連する中断サービスルーチンを完了すると、第1の回路101はノード130において確認信号ACKをアサートし、これにより、中断クリアフリップフロップ116にアクティブハイデータ入力が提供される。第1のクロック信号FCLKの次の立ち上がりエッジで、フリップフロップ116は、クリアフラグ信号CLR\_FLAG(アクティブハイ、図2のカーブ208)をアサートする。この信号遷移は、信号生成器フリップフロップ112をクリアし、中断入力信号INTをローに向かわせる。同期化回路120は、この立ち下がりエッジ遷移を2つの高速クロックサイクル内に同期化して、中断出力信号INT\_OUTの立ち下がりエッジを引き起こす。このようにして、中断処理回路要素100は、確認信号ACKの2つのFCLKサイクル内に第1のクロック101に提供される中断信号INT\_OUTを効果的にクリアする。

#### 【0022】

図3は、高速及び低速クロック速度の1つの例示的な比(例えば、約8)について、図1の回路における動作信号を示す。この例において、低速ドメイン(第2の)回路102は、高速ドメインCPU又はプロセッサ第1回路101によるPWMタイマー周辺機器サービスである。この例において、高速ドメインCPUは、電力コンバータ信号(図示せず)のパルス幅を制御するため閉ループ制御応用例において、PWM制御周辺機器第2回路102にカウンタ値を提供する。周辺機器第2回路102は、カウント値をデクリメントし、カウント値が所定の値(例えば、本実装において「1」)に達すると、中断要求信号IRを発行する。図3におけるカーブ302は低速クロック信号SCLKを図示し、カーブ304は、PWMタイマーカウンタデータ値を概略的に図示し、このケースでは、初期的に値3、2、1、0とデクリメントし、その後、高速クロックドメインCPUによって別の値2に再プログラムされる。その後、周辺機器パルス幅変調タイマー第2回路102は、この値2から1にデクリメントし、その後、再び0にデクリメントする。この例において、カーブ306は、フリップフロップ106からのSET\_FLAG信号出力を図示し、カーブ308が、高速ドメインクロック信号FCLKを図示し、カーブ310が、同期化回路120からの中断出力信号INT\_OUTを図示し、カーブ312が、フリップフロップ116からのCLEAR\_FLAG信号を示す。この例において第2の回路102は、カウンタ値が「1」に達することに応答して中断要求信号をアサートする。図3において分かるように、中断出力信号INT\_OUTは、SET\_FLAG信号の立ち上がりエッジの2つの高速クロックサイクル内で立ち上がりエッジ遷移を受ける。中断出力信号に応答して、第1の回路101は、中断サービスルーチン又はプロセスを開始する。第1の回路101が中断サービスを完了すると、第1の回路101は確認信号ACKをアサートし、フリップフロップ116は、カーブ312として示されるCLEAR\_FLAG信号において立ち上がりエッジを生成する。CLEAR\_FLAG信号遷移は、中断生成器フリップフロップ112をクリアし、同期化回路120は、2つの高速クロックサイクル内で中断出力信号INT\_OUT(カーブ310)において、結果として生じる立ち下がりエッジを生じさせる。

#### 【0023】

図2及び図3の例は、第2の回路102に関連する(例えば、2つの高速クロックサイクルにおける)中断事象の出現の第1の回路101の迅速な通知に関する中断処理回路100の有利なオペレーションを図示する。また、回路100は、第1の回路101による確認信号ACKのアサートに応答して、(例えば、2つの高速クロックサイクル内で)中断信号の高速非同期クリアを提供する。上述した中断処理回路要素101のこれらの迅速な応答利点は、図2及び図3に示すような著しい利点を提供する。また、これらの利点は、速いクロック速度と遅いクロック速度との間の比が増大される場合により顕著である。したがって、記載された回路及び手法の利点は、比較的遅いクロック速度の第2の回路1

10

20

30

40

50

0 2 と相互作用する、高速 C P U 又は他の高速クロックドメイン回路要素に関連して特定の有用性を見出す。

#### 【 0 0 2 4 】

図 4 は、ミスした中断事象を備える、ハンドシェーティング確認中断処理手法を示す信号図 4 0 0 を提供する。図 4 におけるカーブ 4 0 2 は、例示的な低速クロック信号（図 4 において L O W C L O C K と記される）を図示し、カーブ 4 0 4 が、P W M タイマー周辺機器におけるカウンタ又はタイマー値（P W M D A T A ）の別の例を図示し、カーブ 4 0 6 が、P W M タイマー周辺機器から高速クロックドメインプロセッサ回路への中断信号（I N T E R R U P T ）を図示し、カーブ 4 0 8 が、例示的な高速クロック信号（F A S T C L O C K ）を示す。図 4 のカーブ 4 1 0 は、高速クロック信号に同期される中断信号を示し、カーブ 4 1 2 が、高速クロックドメイン回路からの例示的な中断クリア事象を示す。更なるカーブ 4 1 4 が、低速クロック信号に同期される中断クリア事象信号を図示し、カーブ 4 1 6 が、周辺機器回路から高速クロックドメイン回路への中断クリア事象確認ハンドシェーティング信号を図示する。図 4 の信号は、高速及び低速クロックドメイン回路要素間の従来のハンドシェーティング / 確認ベースの中止処理の不利な結果を図示する。カーブ 4 0 4 及び 4 0 6 に見られるように、例えば、遅いドメイン回路 1 0 2 は、カウンタ値が「1」に達することに応答して中断信号 I R を生成し、後続の高速ドメイン回路中止サービスルーチンは、遅いドメイン P W M カウンタ値を「2」に再プログラムする。しかしながら、（カーブ 4 1 2 、 4 1 4 、 及び 4 1 6 に示される）低速の第 2 のクロック信号への中断クリア事象の同期化は、中断シグナリング（カーブ 4 1 4 の立ち下がりエッジ）を実際に終了させるために信号（カーブ 4 0 6 の立ち下がりエッジ）を提供する際に著しい同期化遅延をもたらす。暫定遅延において、この例では、P W M カウンタ値は再度 1 に遷移しているが、高速クロックドメイン回路は、この第 2 の中断事象に応答して適切にサービスすることができない。図 1 ~ 図 3 に関連して上述したように、上述の中止処理回路要素 1 0 0 は、中断要求シグナリングの迅速な非同期クリアを有利に提供し、それによって、図 4 に図示された欠点を回避又は緩和するために高速クロックドメイン回路 1 0 1 による適切な中断サービス処理を助ける。

#### 【 0 0 2 5 】

図 5 は、高速中断要求信号生成に関する中止処理回路要素 1 0 0 の利点を図示する信号図 5 0 0 を提供する。図 5 は、低速クロック信号 S C L K を図示するカーブ 5 0 2 と、P W M のタイマー周辺機器カウンタ値を図示するカーブ 5 0 4 と、異なるレイテンシの生成された中断信号を図示するカーブ 5 0 6 、 5 0 8 、 5 1 0 とを含む。特に、カーブ 5 0 6 は、低速クロック信号サイクルの半分に対応するハーフサイクルレイテンシを有する中止信号（例えば、高速クロックドメインサービス回路に提供される I N T H L ）を図示し、カーブ 5 0 8 は、フルの低速クロックサイクルレイテンシを有する中止信号の I N T F L を図示する。対照的に、カーブ 5 1 0 は、上述した図 1 ( I N T \_ O U T ) において中止生成器 1 1 0 及び同期化器 1 2 0 によって提供される高速中止生成を示す。前述のように、以前の解決策は同期化回路要素（図示せず）を用いて、ハーフサイクル遅延（たとえば、カーブ 5 0 6 ）又はフル低速クロックサイクル遅延（カーブ 5 0 8 ）を導入する、低速クロック回路要素における中断事象に関連するシグナリングを同期させる。対照的に、上述の回路 1 0 0 は、低速クロックドメイン同期化器を用いず、中断要求信号 S E T \_ F L A G を、非同期ロジックが完全に含まれるように信号 I N T \_ O U T として高速クロックドメインに同期された後、中断要求ラインとして搬送する。この点に関し、ノード 1 1 1 上の S E T \_ F L A G 信号は、中断入力信号 I N T \_ I N を生成するフリップフロップ 1 1 2 へのクロックとして用いられ、回路要素 1 1 0 、 1 2 0 は、低速クロックドメインにおいていかなる不利益もなしに中断出力信号 I N T \_ O U T を生成する。

#### 【 0 0 2 6 】

図 6 は、第 1 のクロック信号より遅い第 2 のクロック信号に従って動作される第 2 の回路（例えば、回路 1 0 2 ）によって第 1 のクロック信号に従って動作される第 1 の回路（例えば、上述の回路 1 0 1 ）の中止を管理する方法 6 0 0 を示す。方法 6 0 0 は、上述の

10

20

30

40

50

回路 100 など、又は他の回路要素（図示せず）における、任意の好適な中断処理回路要素を用いて実装され得る。602において、第2のクロック信号に同期される中断信号が生成される。一例において、上述の低速クロックドメイン回路 102 は、フリップフロップ 106 を介して SCLK 信号に同期される SET\_FLG 信号を中断生成器フリップフロップ 112 に提供する。これは、遅いクロックドメインレイテンシを伴わずに、602において中断入力信号 INT\_IN を生成する（例えば、上述の図 5 のカーブ 506 及び 508 に示される遅延を回避する）。

【0027】

604 及び 606において、中断出力信号が、中断入力信号に応答して第1の回路 101 に提供される。上述した例では、図 6 における 604 において、中断生成器フリップフロップ 112 が中断入力信号 INT\_IN を同期化回路 120 に提供し、同期化回路 120 は、高速クロック信号 FCLK に同期して、606 において中断出力信号 INT\_OUT を第1の回路 101 に提供する。608 において、第1の回路は、高速クロック信号 FCLK に同期される確認信号（例えば、上述の ACK）を提供する。方法 600 は、610 において中断入力及び出力信号をクリアすることを更に含む。いくつかの例において、INT\_IN 及び INT\_OUT 信号は、確認信号 ACK に応答して、クリア回路要素 114、116 によって第2のクロック信号 SCLK に対して非同期にクリアされる。回路 100 において、中断入力及び出力信号 INT\_IN 及び INT\_OUT は、クリアフリップフロップ 116 が確認信号 ACK を受信した後、第1のクロック信号 FCLK の 2 サイクル内に迅速にクリアされる。

10

20

30

【0028】

記載される例は、高速クロックドメインにおいて生成されるクリア事象信号の低速クロックドメイン同期化を用いる他の解決策に比して著しい応答時間利点を提供する。図 4 に示すように、そのような代替解決策は、高速クロックドメイン回路要素に提供される中断信号を実際にクリアする前に、同期化のために 2 つの追加の低速クロックサイクルを消費する。これに対し、記載された回路要素 100 及び方法 600 は、低速クロック信号 SCLK に非同期的に低速クロックドメインにおいて生成された中断をクリアすることによって、そのような追加の中断クリアレイテンシ又は遅延を回避する。例えば、回路 100 において、高速クロックドメイン回路 101 からのクリア事象信号 ACK を非同期的に用いて、中断入力信号 INT\_IN を生成する同じフリップフロップ 112 をクリアして、低速クロックドメインにおける何の不利益もなく、中断出力信号 INT\_OUT を確実にクリアする。中断生成のため、説明された回路及び方法は、同期化回路 120 を用いて高速クロック信号 FCLK に対して同期して中断出力信号 INT\_OUT を搬送して、クリアなシグナリングを保証し、如何なる非同期経路（例えば、準安定性）も回避する。この同期化は実際には、特に第1のクロック速度が低速クロック速度より著しく高い場合に、小さな遅延である。また、記載された回路 100 は、高速クロックドメインに完全に同期されるように最終的な中断ラインを依然として維持しながら、高速非同期クリア経路を実装する。

【0029】

本発明の特許請求の範囲内で、説明した例示の実施例に改变が成され得、他の実施例が可能である。

40

【図 1】

【図 2】

【図 3】

【図 4】

【図 5】

【図 6】

FIG. 6

## 【国際調査報告】

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                    |                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------|

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                    | International application No.<br>PCT/US 2018/016206 |

| A. CLASSIFICATION OF SUBJECT MATTER<br><b>G06F 9/48 (2006.01)</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |                                                     |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |                                                     |

| B. FIELDS SEARCHED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                    |                                                     |

| Minimum documentation searched (classification system followed by classification symbols)<br><br>G06F 9/00, 9/06, 9/46, 9/48                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                    |                                                     |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                    |                                                     |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)<br><br>PatSearch (RUPTO internal), USPTO, PAJ, Esp@cenet, Information Retrieval System of FIPS                                                                                                                                                                                                                                                                                                                                                                               |                                                                                    |                                                     |

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                    |                                                     |

| Category*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No.                               |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | EP 0469543 A2 (GOLD STAR CO. LTD) 05.02.1992, abstract                             | 1-20                                                |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | US 2002/0019898 A1 (HITACHI, LTD) 14.02.2002, claim 10                             | 1-20                                                |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | US 2006/0064529 A1 (IBM CORP.) 23.03.2006, paragraphs [0024] - [0031]              | 1-20                                                |

| <input type="checkbox"/> Further documents are listed in the continuation of Box C. <input type="checkbox"/> See patent family annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                    |                                                     |

| * Special categories of cited documents:<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"E" earlier document but published on or after the international filing date<br>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed |                                                                                    |                                                     |

| Date of the actual completion of the international search<br>17 April 2018 (17.04.2018)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Date of mailing of the international search report<br>04 May 2018 (04.05.2018)     |                                                     |

| Name and mailing address of the ISA/RU:<br>Federal Institute of Industrial Property,<br>Berezhkovskaya nab., 30-1, Moscow, G-59,<br>GSP-3, Russia, 125993<br>Facsimile No: (8-495) 531-63-18, (8-499) 243-33-37                                                                                                                                                                                                                                                                                                                                                                                           | Authorized officer<br>V. Alexandrov<br>Telephone No. (495) 531-64-81               |                                                     |

---

フロントページの続き

(81)指定国・地域 AP(BW,GH,GM,KE,LR,LS,MW,MZ,NA,RW,SD,SL,ST,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,RU,TJ,TM),EP(AL,AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MK,MT,NL,NO,PL,PT,R0,RS,SE,SI,SK,SM,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,KM,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BN,BR,BW,BY,BZ,CA,CH,CL,CN,CO,CR,CU,CZ,DE,DJ,DK,DM,DO,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,HR,HU,ID,IL,IN,IR,IS,JO,JP,KE,KG,KH,KN,KP,KR,KW,KZ,LA,LK,LR,LS,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PA,PE,PG,PH,PL,PT,QA,RO,RS,RU,RW,SA,SC,SD,SE,SG,SK,SL,SM,ST,SV,SY,TH,TJ,TM,TN,TR,TT

(72)発明者 マネーシュ ソニ

インド 560 066 バンガロール, ホワイトフィールド, プレスティージ オゾン 2

24

(72)発明者 ラジェーヴ スヴァルナ

インド 560 100 バンガロール, エレクトロニック シティ, ラマサガラ, コンコード シルヴァン ビュー 106

(72)発明者 ニクンジ カレ

インド 560 035 バンガロール, オフ サルジャプラ ロード, マナル シルバー

シャドウ, アルバ 302

F ターム(参考) 5B077 GG13 MM01 MM02