**Erfolgspatent für die Schweiz und Liechtenstein**

Schweizerisch-liechtensteinischer Patentschutzvertrag vom 22. Dezember 1978

12 PATENTSCHRIFT A5

11

621 898

21 Gesuchsnummer: 4887/77

73 Inhaber:

Siemens Aktiengesellschaft, Berlin und München,

München 2 (DE)

22 Anmeldungsdatum: 20.04.1977

72 Erfinder:

Dr. Friedrich Kühne, München 71 (DE)

Karl Lang, München 45 (DE)

24 Patent erteilt: 27.02.1981

45 Patentschrift

veröffentlicht: 27.02.1981

74 Vertreter:

Siemens-Albis Aktiengesellschaft, Zürich

54 Anordnung zum empfangsseitigen Rückgewinnen von Takten mehrerer in einem Pulsrahmen mittels Positiv-Negativ-Stopfens verschachtelter Digitalsignale.

57 Auf der Empfangsseite eines Zeitmultiplexsystems für plesiochrone Signale werden in einer Pulswiederherstellungseinrichtung (1) ein Digitalsignal (D12) und der zugehörige ungleichmässige Takt (T12) wiederhergestellt. In einem nachgeschalteten elastischen Speicher (7) wird ein taktkorrigiertes wiederhergestelltes Digitalsignal (D2) mit zugehörigem gleichmässigem Takt (T2) gebildet. Als Hilfsmittel dient dabei ein Phasenvergleicher (14'), der in Abhängigkeit vom Füllungsgrad des elastischen Speichers (7) eine Torschaltung (18') steuert, über die verschiedene Takte einer Taktzentrale (26) ausgewählt werden.

## PATENTANSPRÜCHE

1. Anordnung zum empfangsseitigen Rückgewinnen von Takten mehrerer in einem Pulsrahmen mittels Positiv-Negativ-Stopfens verschachtelter Digitalsignale mit jeweils einem zugehörigen, die Stopfinformation und gegebenenfalls ein Informationsbit enthaltenden Zusatzsignal, pro Datensignal bestehend aus einer Pulswiederherstellungseinrichtung (1), der das Digitalsignal (D11), das Zusatzsignal (D1) und ein aus dem Digitalsignal abgeleiteter Takt zugeführt und ein nach dem Stopfen wiederhergestelltes Digitalsignal (D12) mit zugehörigem ungleichmässigem Takt entnommen werden, aus einem einschreibbaren und gleichzeitig mit einer anderen Taktfrequenz auslesbaren elastischen Speicher (7), dem das wiederhergestellte Digitalsignal mit zugehörigem ungleichmässigem Takt sowie ein gleichmässiger Takt zugeführt werden und ein taktkorrigiertes wiederhergestelltes Digitalsignal entnommen wird, aus einem dem elastischen Speicher zugeordneten Phasenvergleicher, der ein Steuersignal abgibt, und aus einer Takteinrichtung (18), die von dem Steuersignal in ihrer Frequenz gesteuert den gleichmässigen Takt erzeugt, dadurch gekennzeichnet, dass eine Taktzentrale (26) vorgesehen ist, die einen ersten Takt (T20) erzeugt, der in der Frequenz dem aus jedem Digitalsignal (D1) abgeleiteten Takt (T1) entspricht, die einen zweiten Takt (T21) erzeugt, der in der Frequenz vom ersten Takt (T20) um einen negativen Betrag abweicht, die einen dritten Takt (T22) erzeugt, der in der Frequenz vom ersten Takt (T20) um einen positiven Betrag abweicht und die einen Umschalttakt (TU) erzeugt, derart, dass in einer Periode (T) des Umschalttaktes (TU) n Perioden des ersten Taktes (T20), n-1 Perioden des zweiten Taktes (T21) und n+1 Perioden des dritten Taktes (T22) auftreten, wobei n eine ganze Zahl grösser Eins ist, dass pro Digitalsignal (D1) ferner ein Phasenvergleicher (14') vorgesehen ist, der eine erste Steuerspannung (S1) abgibt, wenn ein Sollwert des Füllungsgrades des elastischen Speichers (7) um einen ersten Betrag überschritten wird, und der eine zweite Steuerspannung (S2) abgibt, wenn dieser Sollwert um einen zweiten Betrag unterschritten wird, und dass schliesslich pro Digitalsignal (D1) als Takteinrichtung (18') eine Torschaltung vorgesehen ist, die beim Fehlen eines Steuersignals den ersten Takt (T20), beim Auftreten der ersten Steuerspannung (S1) den zweiten Takt (T21) und beim Auftreten der zweiten Steuerspannung (S2) den dritten Takt (T22) als gleichmässigen Takt (T2) abgibt, derart, dass die Umschaltung zu Beginn einer Periode (T) des Umschalttaktes (TU) erfolgt.

2. Anordnung nach Anspruch 1, dadurch gekennzeichnet, dass n eine Potenz von 2 ist.

3. Anordnung nach Anspruch 1, dadurch gekennzeichnet, dass der erste und zweite Betrag, welche die Abweichungen vom Sollwert des Füllungsgrades des elastischen Speichers betreffen, gleich gross gewählt sind.

4. Anordnung nach Anspruch 3, dadurch gekennzeichnet, dass die gleich grossen Beträge zu  $1/2 \sum$  Speicherzellen gewählt sind.

5. Anordnung nach Anspruch 1, dadurch gekennzeichnet, dass der elastische Speicher (7) acht Speicherzellen hat und dass die Periode (T) des Umschalttaktes (TU) grösser als  $1/6\Delta f_{max}$  und kleiner als  $1/3\Delta f_{max}$  ist, wobei  $\Delta f_{max}$  die maximale Abweichung der Frequenz des ursprünglichen Digitalsignals von der Frequenz des Digitalsignals im Hauptkanal ist.

6. Anordnung nach Anspruch 1, dadurch gekennzeichnet, dass ein Phasenvergleicher (14') vorgesehen ist, der einmal pro Speicherzyklus die Ordnungszahl der Speicherzelle, in die eingelesen wird, mit der Ordnungszahl der Speicherzelle, aus der ausgelesen wird, vergleicht, der aus diesem Vergleich den Füllungsgrad des elastischen Speichers (7) gewinnt und der bei einem unteren Grenzwert des Füllungsgrades einen ersten Speicher (48, 49) und bei einem oberen Grenzwert des Füll-

lungsgrades einen zweiten Speicher (46, 47) setzt.

5

10

15

20

25

30

35

40

45

50

55

60

Die Erfindung betrifft eine Anordnung zum empfangsseitigen Rückgewinnen von Takten mehrerer in einem Pulsrahmen mittels Positiv-Negativ-Stopfens verschachtelter Digitalsignale mit jeweils einem zugehörigen, die Stopfinformation und gegebenenfalls ein Informationsbit enthaltenden Zusatzsignal, pro Datensignal bestehend aus einer Pulswiederherstellungseinrichtung, der das Digitalsignal, das Zusatzsignal und ein aus dem Digitalsignal abgeleiteter Takt zugeführt und ein nach dem Stopfen wiederhergestelltes Digitalsignal mit zugehörigem ungleichmässigem Takt entnommen werden, aus einem einschreibbaren und gleichzeitig mit einer anderen Taktfrequenz auslesbaren elastischen Speicher, dem das wiederhergestellte Digitalsignal mit zugehörigem ungleichmässigem Takt sowie ein gleichmässiger Takt zugeführt werden und ein taktkorrigiertes wiederhergestelltes Digitalsignal entnommen wird, aus einem dem elastischen Speicher zugeordneten Phasenvergleicher, der ein Steuersignal abgibt und aus einer Takteinrichtung, die von dem Steuersignal in ihrer Frequenz gesteuert den gleichmässigen Takt erzeugt.

Eine derartige Anordnung ist aus dem Buch «Transmission Systems for Communications», revidierte vierte Auflage, Dez. 1971, Bell Telephone Laboratories, Incorporated, Seiten 616 bis 618, bekannt. Als Takteinrichtungen dienen bei dieser Anordnung Quarzoszillatoren.

Aus den Nachrichtentechnischen Fachberichten, Band 42, 1972, «PCM-Technik», VDE-Verlag GmbH, Berlin-Charlottenburg, Seiten 245 bis 256, ist weiterhin eine Anordnung bekannt, die anstelle des Oszillators eine digitale Schaltung zur Erzeugung des gleichmässigen Taktes (Auslesetaktes) verwendet.

Die digitale Schaltung liefert einen Takt mit einer Frequenz  $f_1$ , solange nicht gestopft wird. Nach einem Stopfvorgang wird die Taktfrequenz erhöht bzw. erniedrigt. Dies geschieht dadurch, dass Korrekturschritte, das heisst Bittaktpausen mit veränderter Dauer eingefügt werden. Diese bekannte Anordnung hat den Nachteil, dass die aufwendige Schaltung zur Erzeugung des Auslesetaktes für jedes Digitalsignal vorgesehen ist.

Schliesslich ist aus der DT-PS 2 117 344 noch eine Einrichtung zur Ableitung eines Taktimpulses aus einem Impulslücken aufweisenden Puls unter Beibehaltung der mittleren Zahl der Impulse pro Zeiteinheit bekannt. Diese Einrichtung ist jedoch nur für ein Positiv-Stopfen geeignet.

Aufgabe der Erfindung ist es, eine Anordnung zum empfangsseitigen Rückgewinnen von Takten mehrerer in einem Pulsrahmen mittels Positiv-Negativ-Stopfens verschachtelter Digitalsignale mit geringem Schaltungsaufwand zu realisieren.

Ausgehend von einer Anordnung der einleitend geschilderten Art wird diese Aufgabe erfindungsgemäss dadurch gelöst, dass eine Taktzentrale vorgesehen ist, die einen ersten Takt erzeugt, der in der Frequenz dem aus dem Digitalsignal abgeleiteten Takt entspricht, die einen zweiten Takt erzeugt, der in der Frequenz vom ersten Takt um einen negativen Betrag abweicht, die einen dritten Takt erzeugt, der in der Frequenz vom ersten Takt um einen positiven Betrag abweicht und die einen Umschalttakt erzeugt, derart, dass in einer Periode des Umschalttaktes n Perioden des ersten Taktes, n-1 Perioden des zweiten Taktes und n+1 Perioden des dritten Taktes auftreten, wobei n eine ganze Zahl grösser Eins ist, dass pro Digitalsignal ferner ein Phasenvergleicher vorgesehen ist, der eine erste Steuerspannung abgibt, wenn ein Sollwert des Füllungsgrades des elastischen Speichers um einen ersten Betrag überschritten wird, und die eine zweite Steuerspannung abgibt,

wenn dieser Sollwert um einen zweiten Betrag unterschritten wird, und dass schliesslich pro Digitalsignal als Takteinrichtung eine Torschaltung vorgesehen ist, die beim Fehlen eines Steuersignals den ersten Takt, beim Auftreten der ersten Steuerspannung den zweiten Takt und beim Auftreten der zweiten Steuerspannung den dritten Takt als gleichmässigen Takt abgibt, derart dass die Umschaltung zu Beginn einer Periode des Umschalttaktes erfolgt.

Vorteilhaft ist es, wenn  $n$  eine Potenz von 2 ist.

Unter dem Füllungsgrad eines elastischen Speichers versteht man den Speicherzellenabstand zwischen Ein- und Auslesen geteilt durch die Summe der vorhandenen Speicherzellen.

Vorteilhaft ist es, wenn ein Phasenvergleicher vorgesehen ist, der je ein Steuersignal abgibt, wenn der Sollwert des Füllungsgrades des elastischen Speichers um einen Betrag  $\Delta X$  unter- oder überschritten wird. Vorteilhaft ist es dabei, wenn gleich grosse Beträge  $\pm \Delta X$  gewählt sind oder  $X = 1/2 \Sigma$  Speicherzellen gewählt ist.

Vorteilhaft ist es weiter, wenn der elastische Speicher acht Speicherzellen hat und wenn die Periode des Umschalttaktes grösser als  $1/6\Delta f_{max}$  und kleiner als  $1/3\Delta f_{max}$  ist, wobei  $\Delta f_{max}$  die maximale Abweichung der Frequenz des ursprünglichen Digitalsignals von der Frequenz des Digitalsignals im Hauptkanal ist.

Vorteilhaft ist es schliesslich, wenn ein Phasenvergleicher vorgesehen ist, der einmal pro Speicherzyklus die Ordnungszahl der Speicherzelle, in die eingelesen wird, mit der Ordnungszahl der Speicherzelle, aus der ausgelesen wird, vergleicht, aus diesem Vergleich den Füllungsgrad des elastischen Speichers gewinnt und der bei einem unteren Grenzwert des Füllungsgrades einen ersten Speicher und bei einem oberen Grenzwert des Füllungsgrades einen zweiten Speicher setzt.

Anhand von Ausführungsbeispielen wird die Erfindung nachstehend näher erläutert.

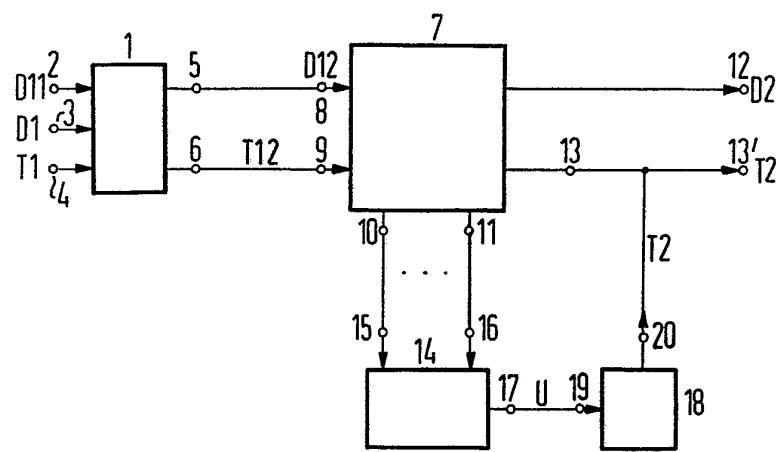

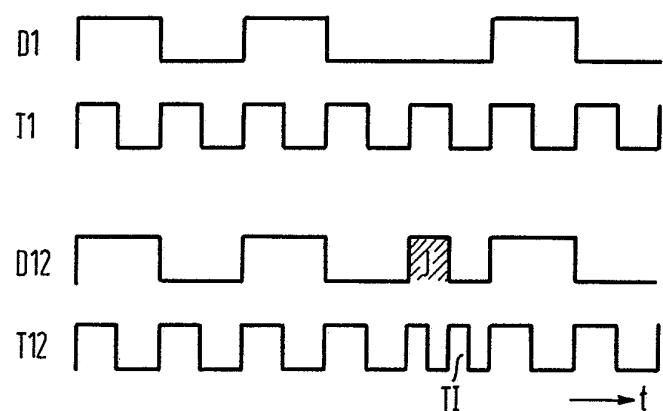

Fig. 1 zeigt eine bekannte Anordnung zum empfangsseitigen Rückgewinnen des Taktes eines in einem Pulsrahmen mittels Positiv-Negativ-Stopfens verschachtelten Digitalsignals.

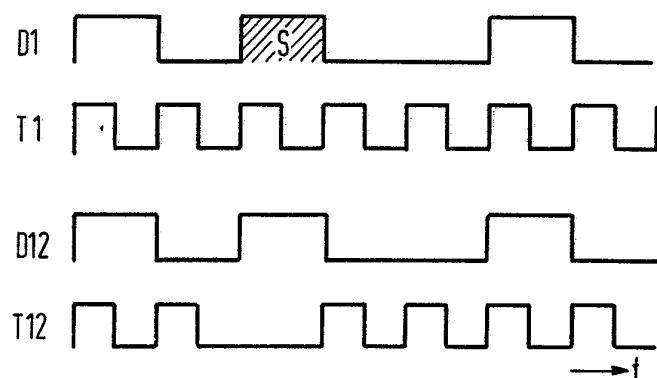

Fig. 2 zeigt Vorgänge bei der Entfernung eines Stopfbits aus dem Digitalsignalen in der Anordnung nach Fig. 1.

Fig. 3 zeigt Vorgänge bei der Einfügung eines zusätzlichen Informationsbit in das Digitalsignal in der Anordnung nach Fig. 1.

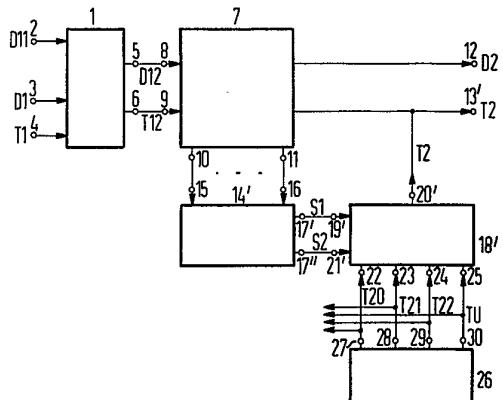

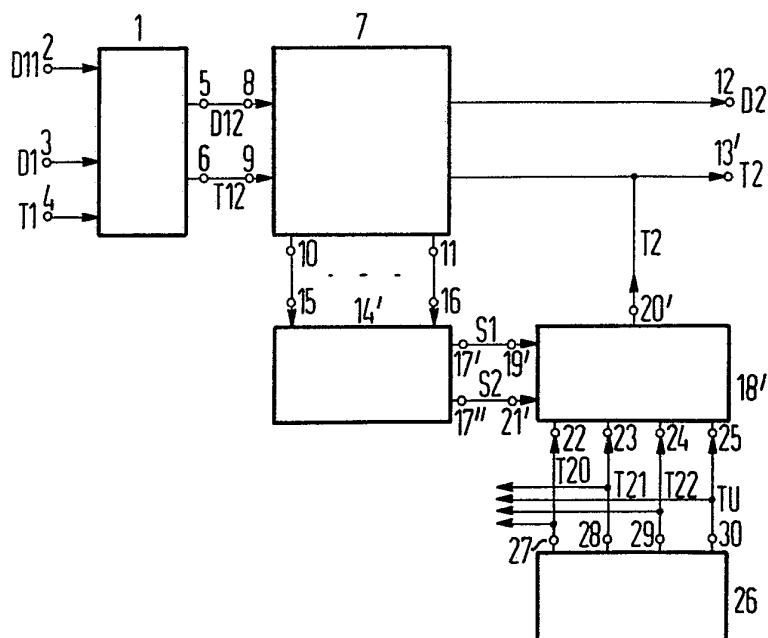

Fig. 4 zeigt eine erfindungsgemäss Anordnung zur empfangsseitigen Rückgewinnung des Taktes eines mit einem Pulsrahmen mittels Positiv-Negativ-Stopfens verschachtelten Digitalsignals.

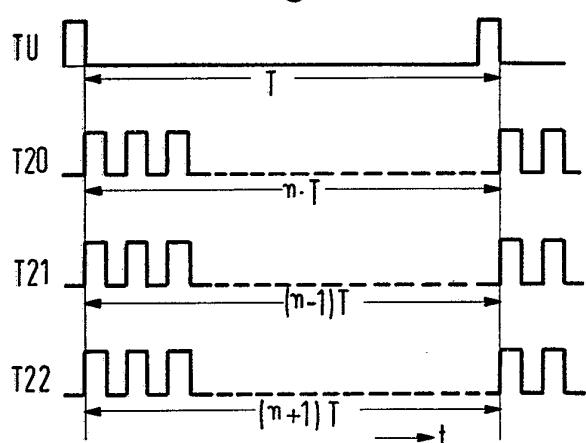

Fig. 5 zeigt ein Phasendiagramm der Takte in der Anordnung nach Fig. 4.

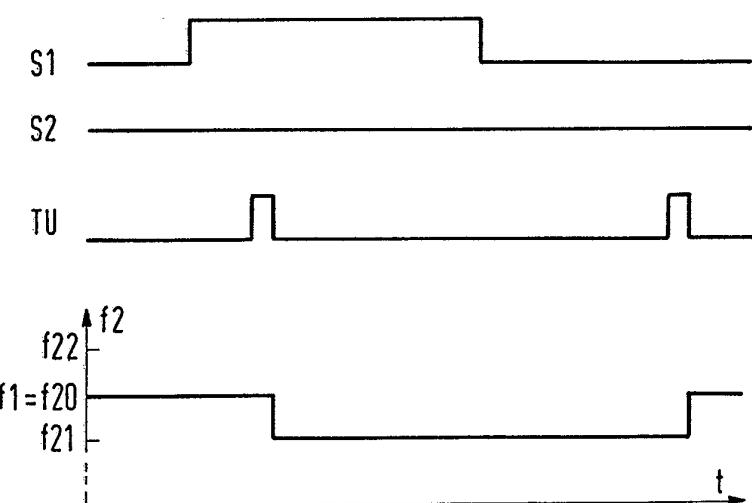

Fig. 6 zeigt Vorgänge beim Ausgleich eines Positiv-Stopfvorganges in der Anordnung nach Fig. 4.

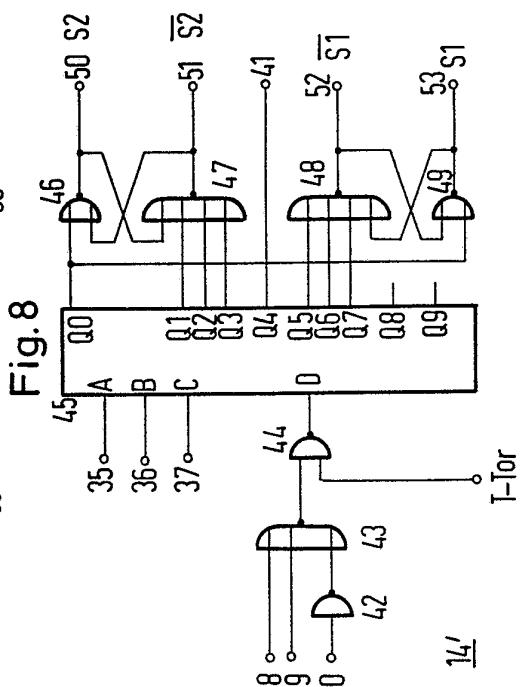

Fig. 7 zeigt ein bekanntes Ausführungsbeispiel eines elastischen Speichers für die Anordnung nach Fig. 4.

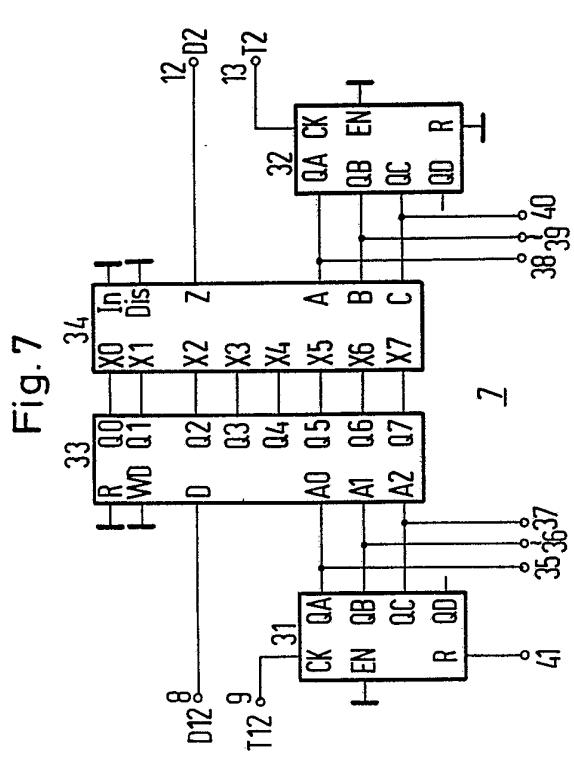

Fig. 8 zeigt ein erfindungsgemässes Ausführungsbeispiel eines Phasenvergleichers für die Anordnung nach Fig. 4 und

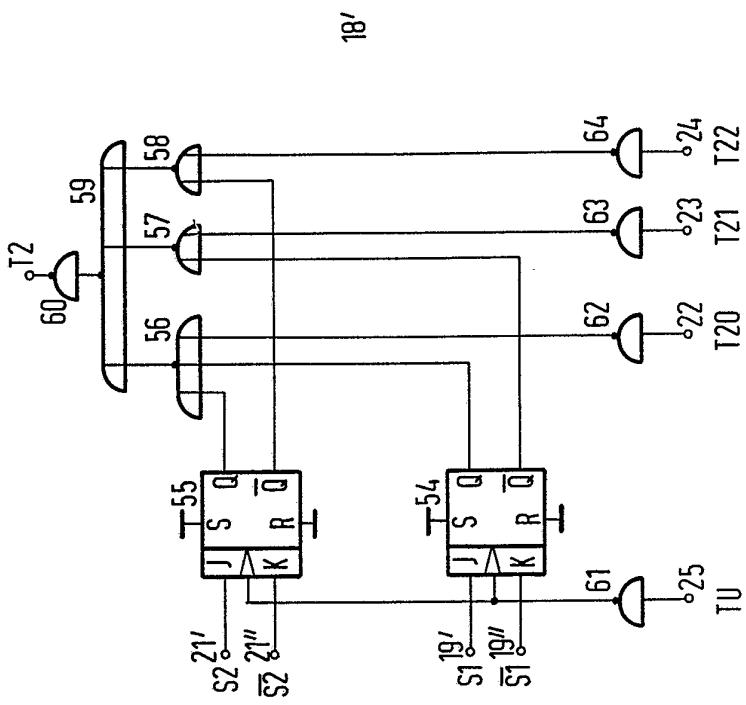

Fig. 9 zeigt ein erfindungsgemässes Ausführungsbeispiel einer Torschaltung für die Anordnung nach Fig. 4.

Fig. 1 zeigt eine bekannte Anordnung zum empfangsseitigen Rückgewinnen eines Digitalsignals und dessen Taktes. Sie enthält eine Pulswiederherstellungseinrichtung 1 mit einem Eingang 2 für ein Digitalsignal D11 eines Stopfkanals mit einem Eingang 3 für ein Digitalsignal D1 eines Hauptkanals und mit einem zum Digitalsignal D1 zugehörigen Taktignal T1, einen Ausgang 5 für ein wiederhergestelltes Digitalsignal D12 und einen Ausgang 6 für einen zum wiederhergestellten Digitalsignal D12 zugehörigen ungleichmässigen Takt T12, einen elastischen Speicher 7 mit Ausgängen 10 und 11 für den Anschluss eines Phasenvergleichers, mit einem Ausgang 12 für ein taktkorrigiertes wiederhergestelltes Digitalsignal D2, mit einem

Eingang 13 für einen dem Digitalsignal D2 zugehörigen gleichmässigen Takt T2, mit einem Phasenvergleicher 14 mit Eingängen 15 und 16 und mit einem Ausgang 17 sowie eine Takteinrichtung 18 in Form eines Taktoszillators mit einem Steuereingang 19 und einem Ausgang 20.

Der Pulswiederherstellungseinrichtung 1 werden das Digitalsignal D1 des Hauptkanals, das zugehörige Taktignal T1 und das Digitalsignal D11 des Stopfkanals zugeführt. Die Pulswiederherstellungseinrichtung 1 wertet das Digitalsignal D11 aus. Bei einer Stopfinformation «Positiv-Stopfen» wird aus dem Digitalsignal D1 ein Bit entfernt. Bei der Stopfinformation «Negativ-Stopfen» wird in das Digitalsignal D1 das im Stopfkanal übertragene Informationsbit eingefügt. Die Pulswiederherstellungseinrichtung 1 gibt an den elastischen Speicher 7 das wiederhergestellte Digitalsignal D12 mit dem zugehörigen Taktignal T12 ab.

Fig. 2 zeigt die Vorgänge bei der Entfernung eines Stopfbits S aus dem Digitalsignal D1. In diesem Fall wird der zugehörige Taktimpuls des Taktes T1 unterdrückt, so dass das Stopfbit S nicht in den elastischen Speicher 7 eingelesen wird.

Fig. 3 zeigt die Vorgänge bei der Einfügung eines Informationsbits J in das Digitalsignal D1. In diesem Fall wird ein zusätzlicher Taktimpuls TJ in das Taktignal T1 eingefügt.

Die Pulswiederherstellungseinrichtung 1 gibt das wiederhergestellte Digitalsignal D12 mit dem ungleichmässigen Takt T12 an den elastischen Speicher 7 ab. Aus diesem wird die Information mit dem gleichmässigen Takt T2 des Taktoszillators 18 wieder ausgelesen. Der Phasenvergleicher 14 gibt eine Regelspannung U an den Taktoszillator 18 ab, die dem Füllungsgrad des elastischen Speichers 7 proportional ist.

Die Frequenz f2 des Taktoszillators 18 wird so geregelt, dass der Füllungsgrad des elastischen Speichers 7 auf seinem Sollwert  $1/2$  gehalten wird. Bei der Einfügung beispielsweise eines Bits steigt der Füllungsgrad des elastischen Speichers 7 um 1 Bit über seinen Sollwert an. Dadurch wird die Frequenz f2 erhöht bis der Füllungsgrad des elastischen Speichers 7 wieder auf seinen Sollwert gesunken ist.

Das aus dem elastischen Speicher 7 ausgelesene Digitalsignal D2 ist somit das wiederhergestellte ursprüngliche Datenignal, das im Sender der Digital-Multiplex-Einrichtung der Gegenstelle mit anderen Digitalsignalen zu einem Digital-Multiplex-Signal gebündelt wurde.

Der Takt T2 hat über einen längeren Zeitraum gemittelt dieselbe Frequenz wie der Takt des ursprünglichen Digitalsignals. Er ist jedoch durch die Ausgleichsvorgänge verjittert. Der Maximalwert des Jitters beträgt 1 Bit.

Fig. 4 zeigt eine erfindungsgemäss Anordnung, die sich von der nach Fig. 1 durch einen anderen Phasenvergleicher 14', eine andere Takteinrichtung 18' und eine Taktzentrale 26 unterscheidet. Der Phasenvergleicher 14' weist einen Ausgang 17' für ein Steuersignal S1 und einen Ausgang 17'' für ein Steuersignal S2 auf. Die Takteinrichtung 18' ist eine Torschaltung mit einem Eingang 19' für das erste Steuersignal S1, mit einem Eingang 21' für ein zweites Steuersignal S2, mit einem Eingang 22 für einen Takt T20, mit einem Eingang 23 für einen Takt T21, mit einem Eingang 24 für einen Takt T22, mit einem Eingang 25 für einen Umschalttakt TU und mit einem Ausgang 20' für den Takt T2. Die Taktzentrale 26 gibt für alle Torschaltungen 18' der Digital-Demultiplex-Einrichtung am Ausgang 27 den Takt T20, am Ausgang 28 den Takt T21, am Ausgang 29 den Takt T22 und am Ausgang 30 den Umschalttakt TU ab. Der Phasenvergleicher 14' kann analog arbeiten und vor seinen Ausgängen 17' und 17'' Schwellenwertschaltungen aufweisen, an deren Ausgang jeweils dann ein Steuersignal erfolgt, wenn der Füllungsgrad des elastischen Speichers einen vorgegebenen Wert überschritten oder unterschritten hat. Der Phasenvergleicher 14' kann aber auch digital arbeiten.

Die Frequenzen und Phasenlagen der von der Taktzentrale

erzeugten Takte sind so gewählt, dass in einer Periode T des Taktes TU n Perioden des Taktes T20, n-1 Perioden des Taktes T21 und n+1 Perioden des Taktes T22 liegen, wobei n eine ganze Zahl ist. Dies ist in Fig. 5 dargestellt. Die Frequenz f20 des Taktes T20 ist gleich der Frequenz f1 des Taktes T1 gewählt.

Fig. 6 zeigt die Vorgänge beim Ausgleich eines Positiv-Stopfvorganges. Wird nicht gestopft, schaltet die Torschaltung 18' den Takt T20 als Auslesetakt T2 ein. Die Information wird mit der Frequenz f1 in den elastischen Speicher 7 ein- und ausgelesen, so dass sein Füllungsgrad dem Sollwert exakt entspricht. Nach einem Positiv-Stopfvorgang sinkt der Füllungsgrad um 1 Bit unter seinen Sollwert. Der Phasenvergleicher 14' gibt ein digitales Steuersignal S1 an die Torschaltung 18' ab. Beim nächstmöglichen Umschaltzeitpunkt schaltet die Torschaltung 18' den Takt T21 für eine Periode des Umschalttaktes TU an. Während dieser Periode werden n Bit in den elastischen Speicher 7 eingelesen und n-1 Bit aus dem elastischen Speicher 7 ausgelesen. Damit ist der Füllungsgrad wieder exakt auf den Sollwert angestiegen. Das Signal S1 nimmt den Wert «0» an, sobald der Füllungsgrad sich von seinem Sollwert um weniger als  $\Delta X$  unterscheidet. Nach einem Negativ-Stopfvorgang veranlasst das Steuersignal S2 die Anschaltung des Taktes T22 für eine Periode T des Umschalttaktes TU.

Der Bedarf an Speicherzellen in elastischen Speichern ist ein Minimum, wenn nach jedem Stopfvorgang ein Ausgleichsvorgang eingeleitet wird, das heißt dass der Phasenvergleicher 14' so ausgeführt werden muss, dass der Betrag, um den der Sollwert des Füllungsgrades unter- oder überschritten werden kann,  $\frac{1}{2}$  Bit beträgt.

Die mittlere Frequenz der Stopfvorgänge ist gleich der Differenz  $\Delta f$  der Taktfrequenzen des ursprünglichen Digital-signals und des Hauptkanals. Ist beispielsweise die Taktfrequenz des ursprünglichen Digitalsignals um 1 Hz grösser als die Taktfrequenz des Hauptkanals, so muss im Mittel in 1 s einmal gestopft werden. Da für den Ausgleich eines Stopfvorganges eine Periode T des Umschalttaktes TU benötigt wird, muss  $T = \frac{1}{\Delta f}$  sein. In Nachrichtennetzen werden häufig mehrere Übertragungsabschnitte mit Digital-Multiplex-Einrichtungen in Serie geschaltet. Ein einzelnes Digitalsignal kann deshalb mehrere Bündelungs- und Auflösungsvorgänge durchlaufen. Dabei können die Abstände zwischen zwei aufeinanderfolgenden Stopfvorgängen beträchtlich schwanken. Sie können erheblich über oder unter dem mittleren Abstand  $1/\Delta f$  liegen. Damit die Taktrückgewinnung auch bei diesen Verhältnissen einwandfrei arbeitet, muss die Periode T des Umschalttaktes TU kleiner als  $1/\Delta f$  gewählt werden und der elastische Speicher 7 eine ausreichende Reserve an Speicherplätzen enthalten.

Eine vorteilhafte Dimensionierung ist  $T = 1/6\Delta f_{\text{max}}$  bis  $1/3\Delta f_{\text{max}}$  in Verbindung mit einem elastischen Speicher 7, der acht Speicherzellen hat.

Fig. 4 zeigt in Verbindung mit den Figuren 7, 8 und 9 ein praktisches Ausführungsbeispiel. Für eine Digital-Multiplex-Einrichtung, die 64-kbit/s-Signale zu einem 2048-kbit/s-Signal bündelt. Die Bitrate des Hauptkanals hat den Nennwert 64 kbit/s, der um  $\pm 0,5 \cdot 10^{-4}$  abweichen kann. Die Bitraten der 64-kbit/s-Signale können um  $\pm 1 \cdot 10^{-4}$  von ihrem Nennwert abweichen. Die maximale Differenz der Taktfrequenzen ist somit  $\Delta f = 9,6$  Hz. Dies bedeutet, dass im ungünstigsten Fall etwa alle 100 ms ein Stopfvorgang erforderlich ist.

Die Frequenz des Taktes T1 ist  $f_1 = 64$  kHz. Für n wurde der Wert  $2^{11} = 2048$  gewählt, damit ergeben sich Frequenz und Periode des Umschalttaktes TU zu  $f_U = 31,25$  Hz,  $T = 32$  ms und  $T\Delta f = 0,31$ . Beim Ausgleich eines Stopfvorganges erhöht oder erniedrigt sich die Frequenz des Auslesetaktes um etwa  $5 \cdot 10^{-4}$ .

Der elastische Speicher 7 ist mit acht Speicherzellen ausgeführt. Damit ist sichergestellt, dass während der 32 ms dauern-

den Ausgleichs eines Stopfvorganges weitere Stopfvorgänge aufgefangen werden können.

Fig. 7 zeigt einen bekannten elastischen Speicher. Er ist mit CMOS-Bausteinen realisiert, und zwar mit dem Baustein CD 14520, der zwei Vier-Bit-Zähler 31 und 32 enthält, dem adressierbaren 8-Bit-Speicher 33 (CD 4099) und dem Datenselektor 34 (MC 14512).

Der ungleichmässige Takt T12 gelangt über die Klemme 9 zum Takteingang CK des Zählers 31. Die Ausgänge QA, QB, QC, die ersten drei Stufen des Zählers 31 adressieren den adressierbaren Speicher 33 über dessen Adresseneingänge A0, A1 und A2. Die Bits des Digitalsignals D12 werden deshalb über die Klemme 8 und den Dateneingang D des adressierbaren Speichers 33 zyklisch in die Speicherzellen Q0 bis Q7 eingeschrieben. Der Auslesetakt T2 am Eingang 13 steuert den Zähler 32, dessen Ausgänge QA, QB und QC den Datenselektor 34 adressieren. Mit jedem TaktSchritt des Taktes T2 wird ein Bit über den Ausgang des Datenselektors aus dem adressierbaren Speicher 33 ausgelesen. Im Normalzustand ist der elastische Speicher 7 halb gefüllt. Ein Bit, das in eine Speicherzelle eingelesen wird, wird nach vier TaktSchritten wieder ausgelesen. Schreibt beispielsweise der adressierbare Speicher 33 ein Bit in die Speicherzelle Q0 ein, so liest gleichzeitig der Datenselektor 34 ein Bit aus der Speicherzelle Q4 aus. Der elastische Speicher 7 ist durch die Ausgänge 35 bis 40 und den Eingang 41 mit dem Phasenvergleicher 14' verbunden.

Fig. 8 zeigt ein erfindungsgemässes Ausführungsbeispiel des Phasenvergleichers 14', in dem einmal in jedem Speicherzyklus die Adressen der Einlesung und der Auslesung miteinander verglichen werden und das Ergebnis des Vergleichs in zwei Speichern festgehalten wird.

Der Phasenvergleicher 14' besteht aus einer Torschaltung mit Gattern 42, 43 und 44, einem ersten Speicher mit Gattern 48 und 49, einem zweiten Speicher mit Gattern 46 und 47 sowie einem Adressendecoder 45, der in dem Baustein CD-4028 realisiert ist.

Ein Vergleich wird ausgeführt, wenn der Zähler 32 des elastischen Speichers 7 die Stellung QA = 0, QB = 0 und QC = 1 hat, das heißt wenn die Speicherzelle Q4 des adressierbaren Speichers 33 ausgelesen wird. Bei dieser Stellung des Zählers 32 hat der Ausgang des Gatters 43 den Wert «Eins». Die Zählerstellung wird für eine Periode des 64-kHz-Taktes beibehalten. In der Mitte dieser Periode öffnet ein schmaler Taktimpuls des Taktes T-Tor das Gatter 44, so dass der Eingang D des Adressendecoders 45 den Wert «Null» hat. Der Takt T-Tor hat eine Taktfrequenz 64 kHz und eine Impulsbreite 1  $\mu$ s.

Der Adressendecoder 45 stellt fest, welche Stellung der Zähler 31 zum Vergleichszeitpunkt hat. Solange der Eingang D des Adressendecoders 45 den Wert «Null» hat, nimmt einer der Ausgänge Q0 bis Q7 den Wert «Eins» an.

Ist der elastische Speicher 7 halb gefüllt, so nimmt zum Vergleichszeitpunkt der Ausgang Q0 des Adressendecoders 45 den Wert «Eins» an. Die beiden Speicher, die aus den Gattern 48 und 49 bzw. 46 und 47 bestehen, werden auf den Wert S1 = 0 und S2 = 0 gesetzt.

Weicht der Füllungsgrad um mehr als  $\frac{1}{2}$  Bit nach unten von seinem Sollwert ab, so nimmt einer der Ausgänge Q5, Q6 oder Q7 den Wert «Eins» an und setzt den ersten Speicher mit den Gattern 48 und 49 auf den Wert S1 = 1.

Weicht der Füllungsgrad um mehr als  $\frac{1}{2}$  Bit nach oben ab, so nimmt einer der Ausgänge Q1, Q2, Q3 den Wert «Eins» an und setzt den zweiten Speicher mit den Gattern 46 und 47 auf den Wert S2 = 1.

Nimmt der Ausgang Q4 des adressierbaren Speichers 45 den Wert «Eins» an, so befindet sich der elastische Speicher 7 in seiner Überlaufstellung. Dieser Zustand kann beim Einschalten des Gerätes oder bei Störungen auftreten. In diesem Falle wird der Zähler 31 über seinen R-Eingang auf den Wert «Null»

gesetzt.

Fig. 9 zeigt ein erfindungsgemäße Ausführungsbeispiel der Torschaltung 18'. Diese besteht aus zwei JK-Flip-Flops 54 und 55, die mit CMOS-Bausteinen CD 4027 realisiert sind, aus einer Gatter-Torschaltung, mit Gattern 56, 57, 58 und 59 und aus Invertern 60 bis 64. Letztere können entfallen, wenn die Takte TU, T20, T21 und T22 invertiert zur Verfügung stehen und wenn der Takt T2 invertiert verwendet werden kann.

Den Flip-Flops 54 und 55 werden die Signale S1 und S2 zusammen mit den invertierten Signalen zugeführt. Die Flip-Flops 54 und 55 können ihren Zustand nur mit der fallenden

Flanke des Umschaltetaktes TU ändern. Haben die Signale S1 und S2 beide den Wert 0, so haben auch beide Flip-Flops den Wert  $Q = 0$ . In diesem Zustand sind die Gatter 57 und 58 gesperrt und das Gatter 56 geöffnet, so dass der Takt T20

<sup>5</sup> durchgeschaltet ist.

Nimmt das Signal S1 den Wert «Eins» an, so wird das Flip-Flop 54 bei der nächsten fallenden Flanke auf den Wert  $Q = 1$  geschaltet. Damit wird das Gatter 56 gesperrt und das Gatter 57 geöffnet, so dass der Takt T21 durchgeschaltet wird.

<sup>10</sup> Nimmt das Signal S2 den Wert «Eins» an, so verlaufen die Vorgänge entsprechend.

Fig. 1

Fig.2

Fig.3

Fig. 4

Fig. 5

Fig. 6

Fig. 9