(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-270911

(P2006-270911A)

(43) 公開日 平成18年10月5日(2006.10.5)

| (51) Int.C1.                | F 1            | テーマコード (参考) |

|-----------------------------|----------------|-------------|

| <b>HO4N 5/45 (2006.01)</b>  | HO4N 5/45      | 5C025       |

| <b>G09G 5/14 (2006.01)</b>  | G09G 5/14 E    | 5C053       |

| <b>G09G 5/00 (2006.01)</b>  | G09G 5/00 520V | 5C082       |

| <b>G09G 5/391 (2006.01)</b> | G09G 5/00 510S |             |

| <b>HO4N 5/93 (2006.01)</b>  | HO4N 5/93 E    |             |

審査請求 有 請求項の数 13 O L (全 9 頁)

(21) 出願番号 特願2005-225646 (P2005-225646)

(22) 出願日 平成17年8月3日 (2005.8.3)

(31) 優先権主張番号 094109167

(32) 優先日 平成17年3月24日 (2005.3.24)

(33) 優先権主張国 台湾(TW)

(71) 出願人 505187596

エバーメディア・テクノロジーズ・インコ

一ポレイテッド

AverMedia TECHNOLOG

IES, INC.

台湾台北市中和区建一路135號

(74) 代理人 100086405

弁理士 河宮 治

(74) 代理人 100098280

弁理士 石野 正弘

(72) 発明者 戴 明火

台湾台北市中和区建一路135號

最終頁に続く

(54) 【発明の名称】映像処理装置およびそれと一体化されたコンピュータシステム

## (57) 【要約】

【課題】 ハードウェアを利用することにより、より速いディンターレース速度とより優れた画面品質とを提供できる映像処理装置を提供する。

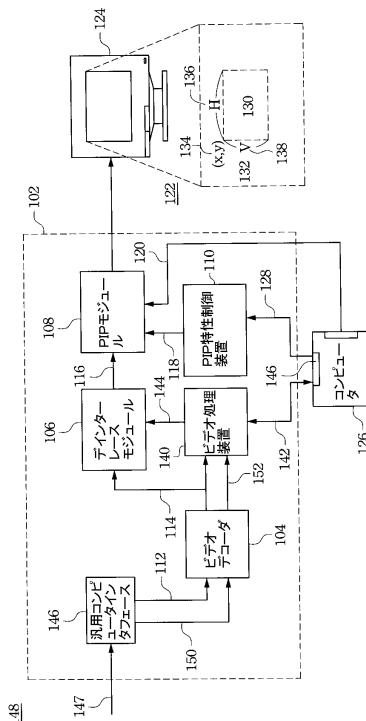

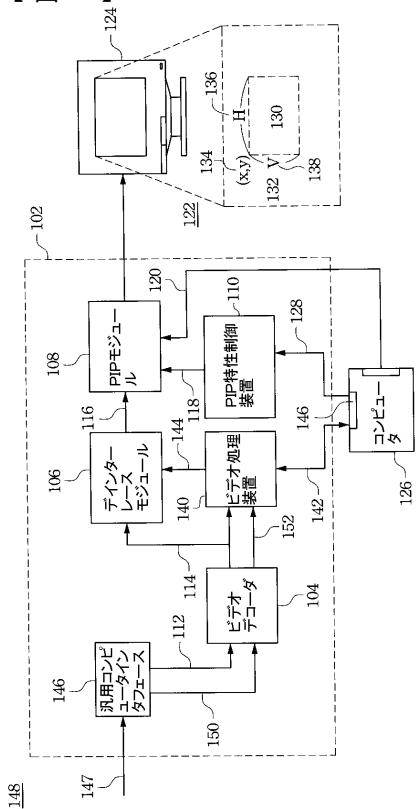

【解決手段】 ビデオデコーダ104、ディンターレースモジュール106、PIPモジュール108およびPIP特性制御装置110を備える。ビデオデコーダ104は、ビデオ信号112を受信して復号化し、デジタルビデオ信号114を生成する。ディンターレースモジュール106は、デジタルビデオ信号114を受信してノンディンターレース信号116を生成する。PIPモジュール108は、PIP特性制御信号118を基にノンディンターレース信号116とスクリーン画面信号120とを重ねて親子画面122を生成して表示装置124で再生する。PIP特性制御装置110は、PIPコマンド128を基にPIP特性制御信号118を出力する。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

ビデオ信号を受信して復号化し、デジタルビデオ信号を生成するビデオデコーダと、前記デジタルビデオ信号を受信してノンインターレース信号を生成するディンターレスモジュールと、

前記ノンインターレース信号およびPIP特性制御信号を受信し、該PIP特性制御信号を基に前記ノンインターレース信号とスクリーン画面信号とを重ねて親子画面を生成して表示装置で再生し、前記PIP特性制御信号が前記親子画面の位置およびサイズを制御し、前記スクリーン画面信号はコンピュータのオペレーティングシステムの背景であるPIPモジュールと、

PIPコマンドを受信し、該PIPコマンドを基に前記PIP特性制御信号を出力し、前記PIPコマンドが前記コンピュータから提供されるPIP特性制御装置とを備える映像処理装置であって、

前記ディンターレスモジュールおよび前記PIPモジュールは、ハードウェアにより構成されることを特徴とする映像処理装置。

**【請求項 2】**

前記デジタルビデオ信号を受信して圧縮ビデオ信号を生成するビデオ処理装置をさらに備え、該圧縮ビデオ信号は、汎用コンピュータインターフェースを介して前記コンピュータに伝送され、前記コンピュータに保存されることを特徴とする請求項1記載の映像処理装置。

**【請求項 3】**

前記ビデオ処理装置はMPEGコーデックを含むことを特徴とする請求項2記載の映像処理装置。

**【請求項 4】**

前記ビデオ処理装置は、前記コンピュータに保存された前記圧縮ビデオ信号を復号化して復号化ビデオ信号を生成し、該復号化ビデオ信号を前記PIPモジュールへ伝送し、該PIPモジュールは、前記復号化ビデオ信号と前記スクリーン画面信号とを重ねてもう一つの親子画面を生成することを特徴とする請求項2記載の映像処理装置。

**【請求項 5】**

放送信号を受信して前記ビデオ信号を生成するチューナをさらに備えることを特徴とする請求項1記載の映像処理装置。

**【請求項 6】**

ビデオ信号を受信して復号化し、デジタルビデオ信号を生成するビデオデコーダと、前記デジタルビデオ信号を受信してノンインターレース信号を生成するディンターレスモジュールと、

PIPコマンドを発するコンピュータと、

表示装置と、

前記ノンインターレース信号、および、前記親子画面の位置およびサイズを制御するPIP特性制御信号を受信し、該PIP特性制御信号を基に前記ノンインターレース信号と、前記コンピュータのオペレーティングシステムの背景であるスクリーン画面信号とを重ねて親子画面を生成して、表示装置で再生するPIPモジュールと、

PIPコマンドを受信し、該PIPコマンドを基に前記PIP特性制御信号を出力するPIP特性制御装置とを備えるコンピュータシステムであって、

前記ディンターレスモジュールおよび前記PIPモジュールは、ハードウェアにより構成されることを特徴とするコンピュータシステム。

**【請求項 7】**

前記デジタルビデオ信号を受信して圧縮ビデオ信号を生成するビデオ処理装置をさらに備え、該圧縮ビデオ信号は、汎用コンピュータインターフェースを介して前記コンピュータに伝送され、前記コンピュータに保存されることを特徴とする請求項6記載のコンピュータシステム。

**【請求項 8】**

前記ビデオ処理装置はMPEGコーデックを含むことを特徴とする請求項7記載のコンピュータシステム。

**【請求項 9】**

前記ビデオ処理装置は、前記コンピュータに保存された前記圧縮ビデオ信号を復号化して復号化ビデオ信号を生成し、該復号化ビデオ信号を前記PIPモジュールへ伝送し、該PIPモジュールは、前記復号化ビデオ信号と前記スクリーン画面信号とを重ねてもう一つの親子画面を生成することを特徴とする請求項7記載のコンピュータシステム。

**【請求項 10】**

放送信号を受信して前記ビデオ信号を生成するチューナをさらに備えることを特徴とする請求項6記載のコンピュータシステム。 10

**【請求項 11】**

ビデオ信号を受信して復号化を行い、デジタルビデオ信号を生成するビデオデコーダと、

前記デジタルビデオ信号を受信してノンインターレース信号を生成するディンターレースモジュールと、

前記ノンインターレース信号をコンピュータビデオ信号へ変換し、該コンピュータビデオ信号は汎用コンピュータインターフェースのフォーマットに合致するブリッジとを備える映像処理装置であって、

前記コンピュータビデオ信号はコンピュータにより受信され、該コンピュータは表示装置を利用して前記コンピュータビデオ信号を再生することを特徴とする映像処理装置。 20

**【請求項 12】**

前記コンピュータは、子画面を利用して前記コンピュータビデオ信号を再生することを特徴とする請求項11記載の映像処理装置。

**【請求項 13】**

放送信号を受信して前記ビデオ信号を生成するチューナをさらに備えることを特徴とする請求項11記載の映像処理装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は映像処理装置に関し、特にコンピュータの表示装置によりテレビ映像を見ることができる映像装置に関する。 30

**【背景技術】****【0002】**

従来はテレビカードを利用して、テレビ信号を汎用コンピュータインターフェースフォーマット（例えばPCIインターフェース）に合致する信号に変換していたため、ユーザはコンピュータの表示装置を利用してテレビ番組を見ることができた。

**【0003】**

テレビ信号をコンピュータの表示装置で見ることのできる信号に変換する過程ではディンターレース(deinterlace)を行う必要があった。テレビ信号がデジタル化されてコンピュータ内に入力されると、コンピュータはこのテレビ信号をソフトウェアによりディンターレースしてから表示装置上の子画面上で再生することができる。そのため、ユーザはコンピュータを使用しながら、子画面中のテレビ番組を見ることができた。また、コンピュータによりテレビ信号を圧縮してハードディスク中に保存してから、後で表示装置により再生することもできた。 40

**【0004】**

しかし、映像処理を行うには非常に大きな計算量が必要となるため、コンピュータを利用してディンターレースを実行した場合、コンピュータ資源が占用され、コンピュータにとって大きな負担となつた。そのため、従来技術ではコンピュータのアルゴリズムを減らすために、ディンターレースのアルゴリズムを簡単化していた。しかし、アルゴリズムを 50

簡単化すると、画面の品質が劣化する上、ソフトウェアを利用してデインターレースを実行すると、速度が遅くなつて画面の動きもスムーズでなくなつた。

【発明の開示】

【発明が解決しようとする課題】

【0005】

そのため、上述の問題を解決するため、速度が速くて画質が良く、さらにはコンピュータ資源を占用しない映像処理装置が求められていた。

【0006】

本発明の第1の目的は、ハードウェアを利用することによりさらにより速いデインターレース速度とより優れた画面品質とを提供することができる映像処理装置を提供することにある。10

本発明の第2の目的は、コンピュータと合わせて使用したときに、コンピュータ資源の使用を節減できる映像処理装置を提供することにある。

本発明の第3の目的は、デインターレースされた信号とスクリーン画面信号とを重ね、表示装置上に親子画面を表示する映像処理装置を提供することにある。

【課題を解決するための手段】

【0007】

上述の目的を達成するため、本発明の映像処理装置は、ビデオデコーダ、デインターレースモジュール、PIP (Picture-In-Picture) モジュールおよびPIP特性制御装置を備える。20

【0008】

ビデオデコーダは、ビデオ信号を受信して復号化し、デジタルビデオ信号を生成する。デインターレースモジュールは、デジタルビデオ信号を受信するとノンインターレース信号を生成する。

【0009】

PIPモジュールは、ノンインターレース信号およびPIP特性制御信号を受信する。PIPモジュールは、PIP特性制御信号を基にノンインターレース信号とスクリーン画面信号とを重ねて親子画面を生成して表示装置で再生する。PIP特性制御信号は親子画面の位置およびサイズを制御する。スクリーン画面信号は、コンピュータのオペレーティングシステムの背景である。30

【0010】

PIP特性制御装置はPIPコマンドを受信する。PIP特性制御装置は、PIPコマンドを基にPIP特性制御信号を出力する。このPIPコマンドはコンピュータから提供される。また、デインターレースモジュールおよびPIPモジュールはハードウェアにより構成される。

【0011】

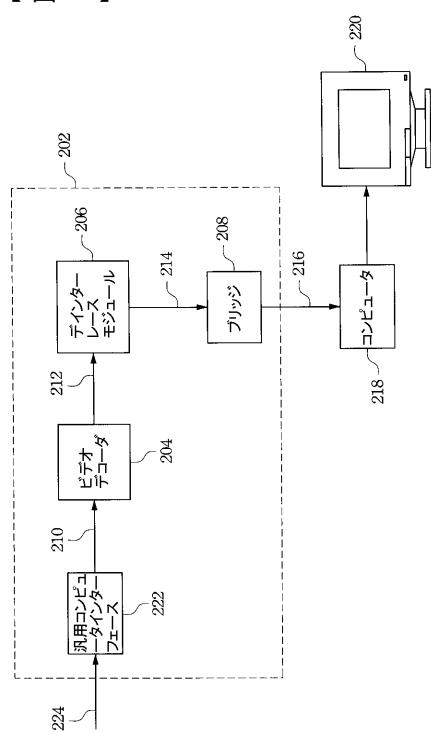

また、本発明の映像処理装置は、ビデオデコーダ、デインターレースモジュールおよびブリッジを含む。

【0012】

ビデオデコーダは、ビデオ信号を受信して復号化を行い、デジタルビデオ信号を生成する。デインターレースモジュールは、デジタルビデオ信号を受信してノンインターレース信号を生成する。ブリッジは、ノンインターレース信号をコンピュータビデオ信号へ変換する。そして、このコンピュータビデオ信号は汎用コンピュータインターフェースのフォーマットに合致する。コンピュータビデオ信号はコンピュータにより受信される。また、コンピュータは、表示装置を利用してコンピュータビデオ信号を再生する。40

【発明の効果】

【0013】

本発明は少なくとも以下の長所を有し、それぞれの実施形態は一つ以上の長所を有する。本発明の映像処理装置は、ハードウェアを利用してさらに速いデインターレース速度とさらに優れた画面品質とを提供できる。コンピュータと合わせて使用すると、コンピュ50

タはデインターレースを実行する必要がないため、コンピュータ資源の使用を節減できる。本発明の映像処理装置は、デインターレースされた後の信号とスクリーンの画面信号とを重ね、表示装置上に親子画面を表示できる。

#### 【発明を実施するための最良の形態】

##### 【0014】

図1は、本発明の一実施形態による映像処理装置を示すブロック図である。図1に示すように、映像処理装置102は、ビデオデコーダ104、デインターレースモジュール106、PIPモジュール108およびPIP特性制御装置110を備える。ビデオデコーダ104は、ビデオ信号112を受信すると、復号化を行ってデジタルビデオ信号114を生成する。デインターレースモジュール106は、デジタルビデオ信号114を受信すると、ノンインターレース信号116を生成する。10

##### 【0015】

PIPモジュール108は、ノンインターレース信号116およびPIP特性制御信号118を受信する。PIPモジュール108は、PIP特性制御信号118を基に、ノンインターレース信号116とスクリーン画面信号120とを重ね、母子画面122を生成して表示装置124で再生する。PIP特性制御信号118は、母子画面の位置およびサイズを制御する。スクリーン画面信号120は、コンピュータ126のオペレーティングシステムのバックグラウンドである。

##### 【0016】

PIP特性制御装置110はPIPコマンド128を受信する。PIP特性制御装置110は、PIPコマンド128を基にPIP特性制御信号118を出力する。PIPコマンド128はコンピュータ126から提供される。デインターレースモジュール106およびPIPモジュール108はハードウェアにより構成される。20

##### 【0017】

一つのコンピュータ126のユーザは、コンピュータの表示装置124を利用してオペレーティングシステムの環境下でビデオ信号112（このビデオ信号112はたとえばテレビ信号である）を再生するため、表示装置上には母子画面122を表示する必要がある。母子画面122には、オペレーティングシステムオリジナル画面132およびビデオ信号112の再生画面130が含まれる。

##### 【0018】

ビデオ信号112は、デインターレースモジュールによりノンインターレース信号116を生成する。ユーザは、コンピュータ126を介してコマンドを送り（PIPコマンド128）、オペレーティングシステムオリジナル画面132上の再生画面130の位置134（例えば座標（X、Y））およびサイズ（例えばH：136、V：138）の再生画面130を指定する。30

##### 【0019】

PIP特性制御装置110がPIPコマンド128を受信して復号化（コンパイル）すると、PIPモジュール108に適合するPIP特性制御信号118が生成される。PIPモジュール108は、PIP特性制御信号118を基に画面を重ねることにより、母子画面122を得ることができる。40

##### 【0020】

他の実施形態において、映像処理装置102はビデオ処理装置140を含んでもよい。ビデオ処理装置140は、デジタルビデオ信号114を受信して圧縮ビデオ信号142を生成する。圧縮ビデオ信号142は、汎用コンピュータインターフェース146を介してコンピュータ126へ伝送され、コンピュータ126に保存される。

##### 【0021】

ビデオ処理装置140は、例えばMPEGコーデックである。ビデオ処理装置140は、デジタルビデオ信号114を、MPEG2やMPEG4などのフォーマットに暗号化してコンピュータ126に保存する。ビデオ処理装置140はまたコンピュータ126に保存された圧縮ビデオ信号142を復号化して、復号化ビデオ信号144を生成することも50

できる。復号化ビデオ信号 144 は、デインターレースされてから PIP モジュール 108 へ伝送される。PIP モジュール 108 は、復号化ビデオ信号 144 とスクリーン画面信号 120 とを重ねてもう一つの母子画面を生成する。汎用コンピュータインターフェース 146 とは、例えばユニバーサルシリアルバス (USB) 、PCI インタフェース、IEEE 1394 インタフェースやピーシーアイエクスプレス (PCI express) インタフェースなどである。

#### 【0022】

その他の実施形態において、映像処理装置 102 はチューナ 222 を含んでもよい。チューナ 222 は、放送信号 147 を受信してビデオ信号 112 を生成する。チューナ 222 はさらにオーディオ信号 150 を生成することもできる。ビデオデコーダ 104 内には、オーディオ信号 150 を復号化してデジタルオーディオ信号 152 を生成するオーディオデコーダが含まれていてもよい。デジタルオーディオ信号 152 は、類似の方法を利用してコンピュータ 126 へ保存したり直接生成したりしてもよい。

#### 【0023】

映像処理装置 102 はコンピュータシステム 148 と一体化することもできる。また、コンピュータシステム 148 は、コンピュータ 126 および表示装置 124 を含んでもよい。コンピュータシステム 148 は、例えばデスクトップ型コンピュータやノートブック型コンピュータである。映像処理装置 102 は、コンピュータ 126 や表示装置 124 中に内蔵したり、外付ボックスとして製作したりすることもできる。

#### 【0024】

デインターレースモジュール 106 および PIP モジュール 108 は、ハードウェアにより構成される。そのため、ソフトウェアによるデインターレースと比べて、デインターレースの速度は速く、映像品質も優れている上、コンピュータ 126 のソフトウェアおよびハードウェアの資源を占用することもない。

#### 【0025】

図 2 は、本発明の一実施形態による映像処理装置を示すブロック図である。図 2 に示すように、映像処理装置 202 は、ビデオデコーダ 204 、デインターレースモジュール 206 およびブリッジ回路 208 を含む。

#### 【0026】

ビデオデコーダ 204 は、ビデオ信号 210 を受信すると復号化を行い、デジタルビデオ信号 212 を生成する。デインターレースモジュール 206 は、デジタルビデオ信号 212 を受信してノンインターレース信号 214 を生成する。ブリッジ回路 208 は、ノンインターレース信号 214 をコンピュータビデオ信号 216 に変換する。このコンピュータビデオ信号 216 は汎用コンピュータインターフェースフォーマットに合致する。コンピュータビデオ信号 216 はコンピュータ 218 により受信される。そして、コンピュータ 218 は、表示装置 220 を利用してコンピュータビデオ信号 216 を再生する。

#### 【0027】

コンピュータ 218 は、子画面を利用してコンピュータビデオ信号 216 を再生できる。上述の汎用コンピュータインターフェースフォーマットとは、例えばユニバーサルシリアルバス (USB) 、PCI インタフェース、IEEE 1394 インタフェースやピーシーアイエクスプレス (PCI express) インタフェースなどである。上述した映像処理装置 202 はチューナ 222 を含む。チューナ 222 は、放送信号 224 を受信してビデオ信号 210 を生成する。

#### 【0028】

一般にデインターレースされた後のノンインターレース信号 214 のデータ量はデジタルビデオ信号 212 のデータ量よりも大きい。コンピュータ 218 のアルゴリズム能力が強力で、容量が大きいときには、この方式を利用してノンインターレース信号 214 を受信できる。コンピュータ 218 がコンピュータビデオ信号 216 を受信すると、ソフトウェアを利用して表示装置 220 上に生成された子画面により再生できる。コンピュータビデオ信号 216 は、圧縮されてコンピュータ 218 内に保存されてから、表示装置 220

10

20

30

40

50

により再生される。

【0029】

本発明は少なくとも以下の長所を有し、それぞれの実施形態は一つ以上の長所を有する。本発明の映像処理装置は、ハードウェアを利用してより速いデインターレース速度とより優れた画面品質とを提供できる。コンピュータと合わせて使用すると、コンピュータはデインターレースを実行する必要がないため、コンピュータ資源の使用を節減できる。本発明の映像処理装置は、デインターレースされた後の信号とスクリーンの画面信号とを重ねて、表示装置上に母子画面を表示できる。

【0030】

本発明では好適な実施形態を前述の通り開示したが、これらは決して本発明を限定するものではなく、当該技術を熟知するものなら誰でも、本発明の主旨と領域を脱しない範囲内で各種の変更や修正を加えることができる。従って本発明の保護の範囲は、特許請求の範囲で指定した内容を基準とする。

【図面の簡単な説明】

【0031】

【図1】本発明の一実施形態による映像処理装置を示すブロック図である。

【図2】本発明の一実施形態による映像処理装置を示すブロック図である。

【符号の説明】

【0032】

102 映像処理装置、 104 ビデオデコーダ、 106 デインターレースモジュール、 108 PIPモジュール、 110 PIP特性制御装置、 112 ビデオ信号、 114 デジタルビデオ信号、 116 ノンインターレース信号、 118 PIP特性制御信号、 120 スクリーン画面信号、 122 母子画面、 124 表示装置、 126 コンピュータ、 128 PIPコマンド、 130 再生画面、 132 オペレーティングシステムオリジナル画面、 134 位置、 136 H、 138 V、 140 ビデオ処理装置、 142 圧縮ビデオ信号、 144 復号化ビデオ信号、 146 汎用コンピュータインターフェース、 147 放送信号、 148 コンピュータシステム、 150 オーディオ信号、 152 デジタルオーディオ信号、 202 映像処理装置、 204 ビデオデコーダ、 206 デインターレースモジュール、 208 ブリッジ回路、 210 ビデオ信号、 212 デジタルビデオ信号、 214 ノンインターレース信号、 216 コンピュータビデオ信号、 218 コンピュータ、 220 表示装置、 222 チューナ、 224 放送信号

10

20

30

【 四 1 】

【 四 2 】

フロントページの続き

(72)発明者 張 文建

台灣台北縣中和市建一路 135 號

(72)発明者 楊 瑞祥

台灣台北縣中和市建一路 135 號

F ターム(参考) 5C025 BA28 CA06 DA01

5C053 FA06 GA19 GB37 LA11

5C082 AA01 AA02 BA20 BA29 BA35 BA41 BB44 BC06 BC07 BC19

CA64 DA26 DA51 MM10