(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2015-0128743

(43) 공개일자 2015년11월18일

- (51) 국제특허분류(Int. C1.)

*H01G 4/005* (2006.01) *H01G 4/20* (2006.01)

*H03K 5/14* (2014.01) *H05K 1/18* (2006.01)

*B82Y 30/00* (2011.01)

- (52) CPC특허분류

*H01G 4/005* (2013.01)

*B82Y 30/00* (2013.01)

- (21) 출원번호 10-2015-7026181

- (22) 출원일자(국제) 2014년03월06일

심사청구일자 없음

- (85) 번역문제출일자 2015년09월22일

- (86) 국제출원번호 PCT/US2014/021173

- (87) 국제공개번호 WO 2014/158970

국제공개일자 2014년10월02일

- (30) 우선권주장

61/783,373 2013년03월14일 미국(US)

- (71) 출원인

사우디 베이식 인더스트리즈 코포레이션

사우디아라비아 리야드 11422 페.오. 박스 5101

- (72) 발명자

알마드호운, 마흐무드, 엔.

사우디아라비아, 11422, 리야드, 페.오. 박스 5101, 사우디 베이식 인더스트리즈 코포레이션 내

엘스후라파, 암로

사우디아라비아, 11422, 리야드, 페.오. 박스 5101, 사우디 베이식 인더스트리즈 코포레이션 내

(뒷면에 계속)

- (74) 대리인

손민

전체 청구항 수 : 총 44 항

(54) 발명의 명칭 전도성 나노-필러로 도핑된 유전성 폴리머 기반 프랙셔널 오더 커패시터

### (57) 요 약

제1 측과 상기 제1 측 반대편의 제2 측을 포함하며 두께  $t$ 를 가진 유전성 나노복합체층, 유전성 나노복합체 층의 제1 측에 연결된 제1 전극층, 유전성 나노복합체 층의 제2 측에 연결된 제2 전극층, 적어도 유전성 나노복합체층 내 충전 물질의 물질 중량 백분율에 종속적인 복소 임피던스 위상 각을 포함하는 프랙셔널 오더 커패시터가 개시된다.

### 대 표 도 - 도2

(52) CPC특허분류

*H01G 4/206* (2013.01)

*H03K 5/14* (2013.01)

*H05K 1/182* (2013.01)

(72) 발명자

**살라마, 칼리드**

사우디아라비아, 11422, 리야드, 피.오. 박스

5101, 사우디 베이식 인더스트리즈 코포레이션 내

**알사리프, 후삼, 엔.**

사우디아라비아, 11422, 리야드, 피.오. 박스

5101, 사우디 베이식 인더스트리즈 코포레이션 내

---

## 명세서

### 청구범위

#### 청구항 1

제1 측과 상기 제1 측 반대편의 제2 측을 포함하며 두께  $t$ 를 가진 유전성 나노복합체층;

상기 유전성 나노복합체 층의 상기 제1 측에 커플링되는 제1 전극층;

상기 유전성 나노복합체 층의 상기 제2 측에 커플링되는 제2 전극층; 및

적어도 유전성 나노복합체 층 내 충전 물질의 물질 중량 백분율에 종속적인 복소 임피던스 위상 각(complex impedance phase angle)을 포함하는,

프랙셔널 오더 커패시터(fractional order capacitor).

#### 청구항 2

제1항에 있어서,

상기 유전성 나노복합체 층은 매트릭스 물질 및 전도성 충전 물질을 포함하는,

프랙셔널 오더 커패시터.

#### 청구항 3

제2항에 있어서,

상기 전도성 충전 물질은 그래핀(graphene)인,

프랙셔널 오더 커패시터.

#### 청구항 4

제3항에 있어서,

상기 그래핀은 부분적으로 산화된(oxidized),

프랙셔널 오더 커패시터.

#### 청구항 5

제3항에 있어서,

상기 그래핀은 완전히 비산화된(un-oxidized),

프랙셔널 오더 커패시터.

#### 청구항 6

제3항에 있어서,

상기 그래핀의 상기 물질 중량 백분율은 상기 유전성 나노복합체 층의 총 중량을 기준으로 약 0.1% 내지 15%를 포함하는,

프랙셔널 오더 커패시터.

#### 청구항 7

제2항에 있어서,

상기 매트릭스 물질은 폴리머(polymer)를 포함하는,

프랙셔널 오더 커패시터.

#### 청구항 8

제1항에 있어서,

상기 제1 및 제2 전극 층은 전도성 물질을 포함하는,

프랙셔널 오더 커패시터.

#### 청구항 9

제8항에 있어서,

상기 제1 전극 층은 백금을 포함하며, 상기 제2 전극 층은 알루미늄을 포함하는,

프랙셔널 오더 커패시터.

#### 청구항 10

제8항에 있어서,

상기 제1 및 제2 전극 층은 PEDOT:PSS를 포함하는,

프랙셔널 오더 커패시터.

#### 청구항 11

제1항에 있어서,

0° 내지 - 90° 사이의 복소 임피던스 위상각을 포함하는,

프랙셔널 오더 커패시터.

#### 청구항 12

제1항에 있어서,

주파수에 대해 대략 일정한 손실 탄젠트(loss tangent)를 포함하는,

프랙셔널 오더 커패시터.

#### 청구항 13

제1항에 있어서,

상기 프랙셔널 오더 커패시터는 10kHz 내지 2MHz의 주파수에 대하여 프랙셔널 거동(fractional behavior)을 나타내는,

프랙셔널 오더 커패시터.

#### 청구항 14

청구항 1의 프랙셔널 오더 커패시터를 포함하는 인쇄회로보드.

#### 청구항 15

청구항 1의 프랙셔널 오더 커패시터를 포함하는 접적 회로.

#### 청구항 16

제14항에 있어서,

상기 프랙셔널 오더 커패시터는 통신 회로의 적어도 일부를 포함하는,

인쇄회로보드

### 청구항 17

제14항에 있어서,

상기 프랙셔널 오더 커패시터는 감지 회로의 적어도 일부를 포함하는,

인쇄회로보드

### 청구항 18

제14항에 있어서,

상기 프랙셔널 오더 커패시터는 제어 회로의 적어도 일부를 포함하는,

인쇄회로보드

### 청구항 19

제15항에 있어서,

상기 프랙셔널 오더 커패시터는 통신 회로의 적어도 일부를 구성하는,

집적 회로.

### 청구항 20

제15항에 있어서,

상기 프랙셔널 오더 커패시터는 감지 회로의 적어도 일부를 포함하는,

집적 회로.

### 청구항 21

제15항에 있어서,

상기 프랙셔널 오더 커패시터는 제어 회로의 적어도 일부를 포함하는,

집적 회로.

### 청구항 22

제1항의 프랙셔널 오더 커패시터를 포함하는 전자 기기.

### 청구항 23

제1 전극 층을 획득하는 단계;

특정의 복소 임피던스 위상각을 얻기 위한, 유전성 나노복합체층 내 충전 물질의 물질 중량 백분율을 선택하는 단계;

상기 제1 전극 층 상에 상기 유전성 나노복합체층을 배치하는 단계; 및

상기 유전성 나노복합체 층이 상기 제1 전극층과 제2 전극층 사이에 배치되도록 상기 유전성 나노복합체층 상에

상기 제2 전극 층을 배치하는 단계;를 포함하는,

프랙셔널 오더 커패시터의 제조 방법.

### 청구항 24

제23항에 있어서,

상기 유전성 나노복합체 층은 적어도 매트릭스 물질 및 전도성 충전 물질을 포함하는,

프랙셔널 오더 커패시터의 제조 방법.

**청구항 25**

제24항에 있어서,

상기 전도성 충전 물질은 그래핀인,

프랙셔널 오더 커패시터의 제조 방법.

**청구항 26**

제25항에 있어서,

상기 그래핀은 부분적으로 산화된,

프랙셔널 오더 커패시터의 제조 방법.

**청구항 27**

제25항에 있어서,

상기 그래핀은 완전히 비산화된,

프랙셔널 오더 커패시터의 제조 방법.

**청구항 28**

제25항에 있어서,

상기 그래핀의 상기 물질 중량 백분율은 상기 유전성 나노복합체층의 총 중량을 기준으로, 약 0.1% 내지 15% 사이에서 선택되는,

프랙셔널 오더 커패시터의 제조 방법.

**청구항 29**

제24항에 있어서,

상기 매트릭스 물질은 폴리머를 포함하는,

프랙셔널 오더 커패시터의 제조 방법.

**청구항 30**

제23항에 있어서,

상기 제1 및 제2 전극 층은 전도성 물질을 포함하는,

프랙셔널 오더 커패시터의 제조 방법.

**청구항 31**

제30항에 있어서,

상기 제1 전극 층은 백금을 포함하며, 상기 제2 전극 층은 알루미늄을 포함하는,

프랙셔널 오더 커패시터의 제조 방법.

**청구항 32**

제30항에 있어서,

상기 제1 및 제2 전극층은 PEDOT:PSS를 포함하는,

프랙셔널 오더 커패시터의 제조방법.

**청구항 33**

제23항에 있어서,

상기 유전성 나노복합체층은 용액 캐스팅(solution casting)에 의해 상기 제1 전극층 상에 배치되는, 프랙셔널 오더 커패시터의 제조 방법.

#### 청구항 34

제23항에 있어서,

상기 유전성 나노복합체 층은 닉터 블레이드에 의해 상기 제1 전극층 상에 배치되는, 프랙셔널 오더 커패시터의 제조 방법.

#### 청구항 35

제23항에 있어서,

상기 유전성 나노복합체 층은 테이프 캐스팅(tape casting)에 의해 상기 제1 전극층 상에 배치되는, 프랙셔널 오더 커패시터의 제조 방법.

#### 청구항 36

제23항에 있어서,

상기 유전성 나노복합체 층은 실크-스크린 프린팅(silk-screen printing)에 의해 상기 제1 전극층 상에 배치되는, 프랙셔널 오더 커패시터의 제조 방법.

#### 청구항 37

제23항에 있어서,

상기 유전성 나노복합체층은 핫 프레스(hot pressing)에 의해 상기 제1 전극층 상에 배치되는, 프랙셔널 오더 커패시터의 제조 방법.

#### 청구항 38

제23항에 있어서,

상기 제2 전극층은 샐도우 마스크를 이용하여 상기 유전성 나노복합체 층 상에 열증발되는(thermally-evaporated), 프랙셔널 오더 커패시터의 제조 방법.

#### 청구항 39

제23항에 있어서,

상기 복소 임피던스 위상각은  $0^\circ$  내지  $-90^\circ$  인, 프랙셔널 오더 커패시터의 제조 방법.

#### 청구항 40

제23항에 있어서,

상기 프랙셔널 오더 커패시터를 접적 회로 내에 패키징하는 단계를 더 포함하는, 프랙셔널 오더 커패시터의 제조 방법.

#### 청구항 41

제23항에 있어서,

상기 프랙셔널 오더 커패시터를 인쇄회로 기판 내에 패키징하는 단계를 더 포함하는,

프랙셔널 오더 커패시터의 제조 방법.

#### 청구항 42

제1항 내지 제13항 중 어느 한 항에 따른 프랙셔널 오더 커패시터로 전기 신호 상에 선택 지연(selected delay)을 부과하는 지연 회로 작동 방법으로서,

특정 복소 임피던스 위상각을 얻기 위하여 상기 프랙셔널 오더 커패시터의 유전성 나노복합체층 내 충전 물질의 물질 중량 백분율을 선택하는 단계;

입력 신호에 응답하는 충전율로 상기 프랙셔널 오더 커패시터를 제1 전압으로 충전하는 단계;

상기 입력 신호에 응답하는 충전율로 상기 프랙셔널 오더 커패시터를 제2 전압으로 방전하는 단계;

상기 프랙셔널 오더 커패시터의 상기 복소 임피던스 위상각의 함수로 지연 신호(delayed signal)를 생성하는 단계;를 포함하는,

지연 회로 작동 방법.

#### 청구항 43

저항 및 제1항 내지 제13항 중 어느 한 항에 따른 프랙셔널 오더 커패시터를 포함하는 필터의 주파수 응답을 조절하는 방법으로서,

특정 복소 임피던스 위상각을 얻기 위하여 상기 프랙셔널 오더 커패시터의 유전성 나노복합체층 내 충전 물질의 물질 중량 백분율을 선택하는 단계;

상기 프랙셔널 커패시터와 저항의 직렬 연결에 대해 입력 전압을 공급하는 단계;

상기 저항에 걸친 상기 전압에 기초하여 출력 전압을 공급하는 단계;

특정 주파수에서 상기 필터의 게인(gain)을 측정하는 단계;

상기 복소 임피던스 위상각을 변화시킴으로써 상기 특정 주파수에서 상기 필터의 상기 게인에 따라 상기 프랙셔널 오더 커패시터의 커패시턴스를 조절하는 단계;를 포함하는,

주파수 응답을 조절하는 방법.

#### 청구항 44

제1항 내지 제10항 중 어느 한 항에 따른 프랙셔널 오더 커패시터를 포함하는 RF 통신 회로 작동 방법으로서,

특정 복소 임피던스 위상각을 얻기 위하여 상기 프랙셔널 오더 커패시터의 유전성 나노복합체층 내 충전 물질의 물질 중량 백분율을 선택하는 단계;

공진 주파수에서 RF 신호를 발생시키는 단계;

상기 RF 통신회로 내의 다른 구성요소들의 직렬 저항값을 검출하는 단계;

상기 복소 임피던스 위상각을 변화시킴으로써 상기 RF 통신회로 내의 다른 구성요소들의 등가 직렬 저항값의 적어도 일부를 오프셋하기 위하여 상기 프랙셔널 오더 커패시터의 음의 저항값을 설정하는 단계를 포함하는,

RF 통신 회로 작동 방법.

#### 발명의 설명

#### 기술 분야

[0001] 본 출원은 2013년 3월 14일 출원된 미국 가출원 제61/783,373호의 우선권을 주장한다. 인용된 출원(들)의 내용은 본 출원에 참조로서 포함된다.

[0002] 본 명세서는 일반적으로 복소 임피던스 위상각(complex impedance phase angle)을 포함하는 커패시터 특성에 대한 개선된 제어를 갖는 프랙셔널 오더 커패시터(fractional order capacitor)에 관한 것이다. 커패시터는 충전

물질을 갖는 유전성 나노복합체 층을 포함하여 커페시터 특성에 대한 개선된 제어를 허용한다.

## 배경기술

[0003] 역사적으로, 프랙셔널 오더 미적분학은 그의 복잡성과 완전히 허용 가능한 기하학적 또는 물리적 실현성을 갖고 있지 않다는 사실 때문에 공학적으로 미개척되었다. 예를 들면, 전기 부품들은 일반적으로 각각 이상적인 -1, 0, 및 1의  $a$  값을 갖는 인더터, 저항 및 커페시터의 특정한 특성들로 제한된다. 이러한 맥락에서,  $a$ 는  $-a \pi/2$  식을 통해 장치의 전류 및 그 전압 사이의 위상 시프트를 결정하는 데 사용될 수 있다. 각도, 즉 90, 0 및 -90으로 변환될 때, 이를 값은 복소 임피던스 위상각을 나타낸다.

[0004] 그러나, 실제 응용에서 구현될 때 전기 부품들은 정확한 정수 값  $a$ 를 갖지 않으므로, 표준 부품들만 특성을 사이로  $a$  값을 의도적으로 제어할 수 있는 능력을 갖는 것은 자동 제어, 패턴 인식, 시스템 특성화, 신호 처리를 수행하는 것 및 전기화학(electrochemistry), 점탄성(viscoelasticity), 및 심지어 생물학 및 신경 시스템의 분야와 관련하여 필터 및 오실레이터를 적용하는 것을 포함하는 다양한 응용에 유용할 수 있다.

[0005]  $0 < a < 1$  범위 내에서 특정한  $a$  값을 갖는 전기 부품들을 의도적으로 설계하고자 하는 이전의 시도들은 많은 경우에서 실제 응용 또는 회로에서 사용 가능하거나 실용적이지 않은 매우 부피가 큰 설계를 일반적으로 초래하였다. 예를 들면, 액체-전극-기반(liquid-electrode-based, LEB)형 프랙셔널 커페시터에 대하여, 구리 전극을 PMMA-클로로포름 용액 내에 담그고, 위상각은 전극이 담긴 깊이에 따라 변한다. 그러나 이 방법은 분명히 쉽게 인쇄회로보드 및/또는 전자회로와 접적할 수 없다. 또한, 이러한 셋업의 패키징은 매우 부피가 큰 장치를 초래한다.

[0006] 다른 시도들로는 프랙탈형(fractal-type, FT) 프랙셔널 커페시터의 설계를 포함한다. 이를 설계는 일반적으로 웨이퍼 상에 제작되며 전송선 이론(transmission line theory)에 의존한다. 이러한 유형의 커페시터 이면의 기본적인 작동 원리는 스터브, 또는 전송선과 같은 프랙탈 기하(fractal geometries)를 생성하는 것을 수반하는데, 이는 다시 기하 및 기술적 파라미터에 기반한 특정 임피던스를 야기할 수 있다. 커페시터를 생성하는 대신, FT는 임피던스를 발생시키기 위하여 회로 상에 제작되는 일련의 금속 트레이스를 사용한다. 이는 집중요소 설계(lumped element design)에 반하여 분산 요소 설계(distributed element design)로 종종 지칭된다. 또한, FT 프랙셔널 커페시터를 사용할 때, 얻어질 수 있는  $a$  값은 단지 0.46-0.5의 범위이다. 또한, 마이크로파 회로의 성질을 감안하면 매우 높은 주파수 범위(1MHz - 10GHz)에서 일정 위상 거동(constant phase behavior)이 일어나며, 위상각의 변화량은 약 5°이다.

[0007] 다른 접근법은 프랙셔널 오더 문제를 디지털식으로 근사하고 근사적인 방법을 계산하여 시뮬레이션하는 것을 포함한다. 디지털 근사는 대역폭에서 필수적으로 제한되며, 컴퓨터 자원을 많이 소비하고, 유한 정밀도의 산술로 인한 불안정성을 겪을 수 있다. 이러한 한계는 디지털 기술이 빠른 공정이나 강한 대향력(opposing force)이 개입되는 "뻣뻣한(stiff)" 공정을 제어하는 것과 같은 많은 문제들을 해결하지 못하거나 비실용적인 것으로 만들 수 있다.

## 발명의 내용

[0008] 본 발명자들은, 또한 충전 물질로도 기술되는, 2차원 나노 재료의 무게 백분율이 커페시터의 복소 임피던스 각을 제어하는 데 사용될 수 있음을 발견하였다. 구체적으로, 커페시터의 유전층은 폴리머 매트릭스 내의 그 조합에 기반한 그래핀과 같은 충전 물질의 특정 중량%를 선택함으로써 형성될 수 있다. 중량 백분율은  $a$ 에 대해서  $0 < a < 1$  범위 내의 임의의 비-정수 값을 선택하기 위하여 사용될 수 있으며, 이는 상술한 바와 같은 커페시터의 복소 임피던스 위상각을 직접적으로 변경한다.

[0009] 2차원 나노 물질로서 그래핀을 사용하는 것의 고유한 양상 중 하나는 유전층 내에서 마이크로-커페시터의 형성을 수반한다. 구체적으로, 프랙셔널 커페시터는 분산된 마이크로-커페시터의 형성을 초래하는 폴리머 매트릭스 내의 그래핀 시트의 로딩/loading)에 의해 제어된다. 이는 시뮬레이션에서 사용되는 RC 래더 네트워크와 매우 유사하며 복잡하고 큰 회로 설계의 필요 없이  $a$  값을 조율하는 것이 가능하다. 그래핀은 또한 초고속에서 전자의 자유로운 흐름을 촉진하는 고유한 특성을 갖는다.

[0010] 또한, 본 발명의 프랙셔널 오더 커페시터의 제조는 효과적인 제조 및 상업화를 허용한다.

[0011] 본 명세서의 일 양상에 따르면, 프랙셔널 오더 커페시터 두께  $t$ 의 유전성 나노복합체 층을 포함하며 제1 층 및 제1 층 반대편의 제2 층을 포함한다. 프랙셔널 오더 커페시터는 유전성 나노복합체층의 제1 층에 연결된 제1 전

극총과 유전성 나노복합체 층의 제2 측에 연결된 제2 전극층을 더 포함한다. 프랙셔널 오더 커패시터는 또한 적어도 유전성 나노복합체층 내 충전 물질의 물질 중량 백분율에 종속적인 복소 임피던스 위상 각을 포함한다.

[0012] 본 명세서의 다른 양상에 따르면, 프랙셔널 오더 커패시터의 유전성 나노복합체 층은 매트릭스 재료와 전도성 충전 물질을 포함하며, 매트릭스 물질은 폴리머이고 전도성 충전 물질은 그래핀이다. 그래핀은 부분 산화되거나 완전 산화되지 않을 수 있다. 또한, 그래핀의 물질 중량 백분율은 유전성 나노복합체 층의 총 중량을 기준으로, 약 0.1% 내지 15% 사이이다.

[0013] 본 명세서의 또 다른 양상에 따르면, 프랙셔널 오더 커패시터의 제1 및 제2 전극 층은 전도성 물질을 포함한다. 제1 전극 층은 백금을 포함하고, 제2 전극 층은 알루미늄을 포함한다. 제1 및 제2 전극 층은 대안적으로 PEDOT:PSS를 포함할 수 있다.

[0014] 본 명세서의 추가의 양상에 따르면, 프랙셔널 오더 커패시터는  $0^\circ$  내지  $-90^\circ$  사이의 복소 임피던스 위상각을 포함하거나, 주파수에 대해 대략 일정한 손실 탄젠트(loss tangent)를 포함하거나, 10kHz 내지 2MHz 사이의 주파수에 대하여 프랙셔널 거동(fractional behavior)을 나타낸다.

[0015] 본 명세서의 다른 양상에 따르면, 프랙셔널 오더 커패시터는 인쇄회로보드 또는 접적 회로 내에 포함될 수 있으며 통신 회로, 감지 회로, 또는 제어 회로의 적어도 일부 내에서 사용될 수 있다. 프랙셔널 오더 커패시터는 또한 전자 기기 내에 포함될 수 있다.

[0016] 본 명세서의 또 다른 양상에 따르면, 프랙셔널 오더 커패시터의 제조방법은 제1 전극 층을 획득하는 단계를 포함한다. 이 방법은 또한, 특정의 복소 임피던스 위상각을 얻기 위한 유전성 나노복합체층 내 충전 물질의 물질 중량%를 선택하는 단계를 포함한다. 이 방법은 제1 전극층 상에 유전성 나노복합체 층을 배치하는 단계를 추가로 포함한다. 이 방법은 또한 유전성 나노복합체층이 제1 전극층과 제2 전극층 사이에 배치되도록 유전성 나노복합체층 상에 제2 전극층을 배치하는 단계를 포함한다.

[0017] 본 명세서의 추가의 양상에 따르면, 프랙셔널 오더 커패시터의 유전성 나노복합체 층은 매트릭스 재료와 전도성 충전 물질로 제조될 수 있으며, 매트릭스 물질은 폴리머이고 전도성 충전 물질은 그래핀이다. 그래핀은 부분 산화되거나 완전 산화되지 않을 수 있다. 또한, 그래핀의 물질 중량 백분율은 유전성 나노복합체 층의 총 중량을 기준으로, 약 0.1% 내지 15% 사이이다. 또한, 프랙셔널 오더 커패시터는  $0^\circ$  내지  $-90^\circ$ 의 복소 임피던스 위상각을 포함하거나, 주파수에 대해 대략 일정한 손실 탄젠트를 포함하거나, 10kHz 내지 2MHz 사이의 주파수에 대하여 프랙셔널 거동을 나타낸다.

[0018] 본 명세서의 다른 양상에 따르면, 프랙셔널 오더 커패시터는 전도성 물질을 포함하는 제1 및 제2 전극층으로 제조될 수 있다. 제1 전극층은 백금을 포함하고, 제2 전극층은 알루미늄을 포함한다. 제1 및 제2 전극층은 대안적으로 PEDOT:PSS를 포함할 수 있다.

[0019] 본 명세서의 또 다른 양상에 따르면, 프랙셔널 오더 커패시터의 유전성 나노복합체층은 용액 캐스팅에 의해, 닥터 블레이드에 의해, 또는 테이프 캐스팅에 의해, 또는 실크-스크린 인쇄에 의해, 또는 핫 프레스에 의해 제1 전극층 상에 배치될 수 있다. 제2 전극 층은 새도우 마스크를 이용하여 유전성 나노복합체 층 상에 열증발(thermally-evaporated)될 수 있다. 본 명세서의 다른 양상에 따르면, 프랙셔널 오더 커패시터는 인쇄회로보드 또는 접적 회로 내에 패키징될 수 있다.

[0020] 본 명세서의 추가의 양상에 따르면, 본 발명의 프랙셔널 오더 커패시터 중 임의의 것으로 전기 신호 상에 선택지연을 부과하는 지연회로 작동 방법은 특정의 복소 임피던스 위상각을 얻기 위하여 상기 프랙셔널 오더 커패시터의 유전성 나노복합체층 내 충전 물질의 물질 중량%를 선택하는 단계를 포함한다. 이 방법은 또한 입력 신호에 응답하는 충전율로 상기 프랙셔널 오더 커패시터를 제1 전압으로 충전하는 단계를 포함한다. 이 방법은 입력 신호에 응답하는 충전율로 상기 프랙셔널 오더 커패시터를 제2 전압으로 방전하는 단계를 추가로 포함한다. 이 방법은 또한 상기 프랙셔널 오더 커패시터의 복소 임피던스 위상각의 함수로 지연 신호를 생성하는 단계를 포함한다.

[0021] 본 명세서의 추가의 양상에 따르면, 저항과 본 발명의 프랙셔널 오더 커패시터 중 어느 하나를 포함하는 필터의 주파수 응답을 조절하는 방법은, 특정의 복소 임피던스 위상각을 얻기 위하여 프랙셔널 오더 커패시터의 유전성 나노복합체층 내 충전 물질의 물질 중량 백분율을 선택하는 단계를 포함한다. 이 방법은 또한 프랙셔널 커패시터 및 저항의 직렬 결합에 걸쳐 입력 전압을 공급하는 단계를 포함한다. 이 방법은 저항에 걸친 전압에 기초하여 출력 전압을 공급하는 단계를 추가로 포함한다. 이 방법은 또한 특정의 주파수에서 필터의 게인(gain)을 측정하는 단계를 포함한다. 이 방법은 복소 임피던스 위상각을 변화시킴으로써 특정 주파수에서 필터의 게인에 따라

라 프랙셔널 오더 커패시터의 커패시턴스를 조절하는 단계를 추가로 포함한다.

[0022] 본 명세서의 다른 양상에 따르면, 본 발명의 프랙셔널 오더 커패시터 중 임의의 하나를 포함하는 RF 통신회로 작동 방법은, 특정의 복소 임피던스 위상각을 얻기 위하여 프랙셔널 오더 커패시터의 유전성 나노복합체총 내 충전 물질의 물질 중량%를 선택하는 단계를 포함한다. 이 방법은 또한 공진 주파수에서 RF 신호를 발생시키는 단계를 포함한다. 이 방법은 RF 통신 회로 내의 다른 구성요소의 직렬 저항 값을 검출하는 단계를 추가로 포함한다. 이 방법은 또한 복소 임피던스 위상각을 변화시킴으로써 RF 통신회로 내의 다른 구성요소의 등가 직렬 저항값의 적어도 일부를 오프셋(offset) 하기 위하여 프랙셔널 오더 커패시터의 음의 저항값을 설정하는 단계를 포함한다.

[0023] 또한, 이하에서 본 발명의 구현예 1 내지 44가 개시된다. 구현예 1은 제1 측, 및 제1 측 반대편의 제2 측을 포함하는, 두께  $t$ 의 유전성 나노복합체 층; 유전성 나노복합체 층의 제1 측에 연결된 제1 전극 층; 유전성 나노복합체 층의 제2 측에 연결된 제2 전극층; 및 적어도 유전성 나노복합체 층 내 충전 물질의 물질 중량%에 종속적인 복소 임피던스 위상각을 포함하는 프랙셔널 오더 커패시터이다. 구현예 2는 유전성 나노복합체 층이 매트릭스 물질 및 전도성 충전 물질을 포함하는, 구현예 1의 프랙셔널 오더 커패시터이다. 구현예 3은 전도성 충전 물질이 그래핀인, 구현예 2의 프랙셔널 오더 커패시터이다. 구현예 4는 그래핀이 부분적으로 산화된, 구현예 3의 프랙셔널 오더 커패시터이다. 구현예 5는 그래핀이 완전히 비산화된, 구현예 3의 프랙셔널 오더 커패시터이다. 구현예 6은 그래핀의 물질 중량 백분율이 유전성 나노복합체 층의 총 중량을 기준으로, 약 0.1% 내지 15%를 포함하는, 구현예 3 내지 5 중 어느 하나의 프랙셔널 오더 커패시터이다. 구현예 7은 매트릭스 물질이 폴리머를 포함하는, 구현예 2 내지 6 중 어느 하나의 프랙셔널 오더 커패시터이다. 구현예 8은 제1 및 제2 전극 층이 전도성 물질을 포함하는, 구현예 1 내지 7 중 어느 하나의 프랙셔널 오더 커패시터이다. 구현예 9는 제1 전극층은 백금을 포함하고, 제2 전극층은 알루미늄을 포함하는, 구현예 8의 프랙셔널 오더 커패시터이다. 구현예 10은 제1 및 제2 전극층이 PEDOT:PSS를 포함하는, 구현예 8의 프랙셔널 오더 커패시터이다. 구현예 11은  $0^{\circ}$  내지  $-90^{\circ}$  사이의 복소 임피던스 위상각을 포함하는, 구현예 1 내지 10 중 어느 하나의 프랙셔널 오더 커패시터이다. 구현예 12는 주파수에 대해 대략 일정한 손실 탄젠트를 포함하는, 구현예 1 내지 11 중 어느 하나의 프랙셔널 오더 커패시터이다. 구현예 13은 프랙셔널 오더 커패시터가 10kHz내지 2MHz 사이의 주파수에 대하여 프랙셔널 거동을 나타내는, 구현예 1 내지 13 중 어느 하나의 프랙셔널 오더 커패시터이다. 구현예 14는 구현예 1 내지 13 중 어느 하나의 프랙셔널 오더 커패시터를 포함하는 인쇄회로보드이다. 구현예 15는 구현예 1 내지 13 중 어느 하나의 프랙셔널 오더 커패시터를 포함하는 접적 회로이다. 구현예 16은 프랙셔널 오더 커패시터가 통신 회로의 적어도 일부를 포함하는, 구현예 14의 인쇄회로보드이다. 구현예 17은 프랙셔널 오더 커패시터가 감지 회로의 적어도 일부를 포함하는, 구현예 14의 인쇄회로 기판이다. 구현예 18은 프랙셔널 오더 커패시터가 제어회로의 적어도 일부를 포함하는, 구현예 14의 인쇄회로보드이다. 구현예 19는 프랙셔널 오더 커패시터가 통신회로의 적어도 일부를 포함하는, 구현예 15의 접적 회로이다. 구현예 20은 프랙셔널 오더 커패시터가 감지회로의 적어도 일부를 포함하는, 구현예 15의 접적 회로이다. 구현예 21은 프랙셔널 오더 커패시터가 제어회로의 적어도 일부를 포함하는, 구현예 15의 접적 회로이다. 구현예 22는 구현예 1 내지 13 중 어느 하나의 프랙셔널 오더 커패시터를 포함하는 전자장치이다. 구현예 23은 제1 전극층을 획득하는 단계; 특정 복소 임피던스 위상각을 얻기 위한 유전성 나노복합체총 내 충전 물질의 물질 중량 백분율을 선택하는 단계; 제1 전극층 상에 유전성 나노복합체총을 배치하는 단계; 및 유전성 나노복합체총이 제1 전극층과 제2 전극층 사이에 배치되도록 유전성 나노복합체총 상에 제2 전극 층을 배치하는 단계를 포함하는, 프랙셔널 오더 커패시터의 제조방법이다. 구현예 24는 유전성 나노복합체 층이 적어도 매트릭스 물질 및 전도성 충전 물질을 포함하는, 구현예 23의 방법이다. 구현예 25는 전도성 충전 물질이 그래핀인, 구현예 24의 방법이다. 구현예 26은 그래핀이 부분적으로 산화된, 구현예 25의 방법이다. 구현예 27은 그래핀이 완전히 비산화된, 구현예 25의 방법이다. 구현예 28은 그래핀의 물질 중량%가 유전성 나노복합체 층의 총 중량을 기준으로, 약 0.1% 내지 15% 사이에서 선택되는, 구현예 25 내지 27 중 어느 하나의 방법이다. 구현예 29는 매트릭스 물질이 폴리머를 포함하는, 구현예 24 내지 28 중 어느 하나의 방법이다. 구현예 30은 제1 및 제2 전극층이 전도성 물질을 포함하는, 구현예 23 내지 29 중 어느 하나의 방법이다. 구현예 31은 제1 전극층은 백금을 포함하고, 제2 전극층은 알루미늄을 포함하는, 구현예 30의 방법이다. 구현예 32는 제1 및 제2 전극층이 PEDOT:PSS를 포함하는, 구현예 30의 방법이다. 구현예 33은 유전성 나노복합체 층이 용액 캐스팅에 의해 제1 전극층 상에 배치되는, 구현예 23 내지 32 중 어느 하나의 방법이다. 구현예 33은 유전성 나노복합체총이 용액 캐스팅에 의해 제1 전극 층 상에 배치되는, 구현예 23 내지 32 중 어느 하나의 방법이다. 구현예 34는 유전성 나노복합체총이 닉터 블레이드에 의해 제1 전극층 상에 배치되는, 구현예 23 내지 33 중 어느 하나의 방법이다. 구현예 35는 유전성 나노복합체총이 테이프 캐스팅에 의해 제1 전극층 상에 배치되는, 구현예 23 내지 34 중 어느 하나의 방법이다. 구현예 36은 유전성 나노복합체 층이 실크스크린 인쇄

에 의해 제1 전극층 상에 배치되는, 구현예 23 내지 35 중 어느 하나의 방법이다. 구현예 37은 유전성 나노복합체 층이 핫 프레스에 의해 제1 전극층 상에 배치되는, 구현예 23 내지 36 중 어느 하나의 방법이다. 구현예 38은 제2 전극층이 새도우 마스크를 이용하여 유전성 나노복합체 층 상에 열증발되는(thermally-evaporated), 구현예 23 내지 37 중 어느 하나의 방법이다. 구현예 39는 복소 임피던스 위상각이 0° 내지 - 90° 사이인, 구현예 23 내지 38 중 어느 하나의 방법이다. 구현예 40은 프랙셔널 오더 커패시터를 접적 회로 내에 패키징하는 단계를 추가로 포함하는, 구현예 23 내지 39 중 어느 하나의 방법이다. 구현예 41은 프랙셔널 오더 커패시터를 인쇄 회로 기판 내에 패키징하는 단계를 추가로 포함하는, 구현예 23 내지 40 중 어느 하나의 방법이다. 구현예 42는 구현예 1 내지 13으로부터의 프랙셔널 오더 커패시터 중 어느 하나로 전기 신호 상에 선택 지연을 부과하는 지연 회로 작동 방법으로서, 이 방법은 특정 복소 임피던스 위상각을 얻기 위하여 프랙셔널 오더 커패시터의 유전성 나노복합체 층 내 충전 물질의 물질 중량%를 선택하는 단계; 입력 신호에 응답하는 충전율로 상기 프랙셔널 오더 커패시터를 제1 전압으로 충전하는 단계; 입력 신호에 응답하는 충전율로 상기 프랙셔널 오더 커패시터를 제2 전압으로 방전하는 단계; 상기 프랙셔널 오더 커패시터의 복소 임피던스 위상각의 함수로, 지연된 신호를 생성하는 단계를 포함한다. 구현예 43은 저항과 구현예 1 내지 13 중 어느 하나로부터의 프랙셔널 오더 커패시터 중 어느 하나를 포함하는 필터의 주파수 응답을 조절하는 방법으로서, 이 방법은 특정 복소 임피던스 위상각을 얻기 위하여 프랙셔널 오더 커패시터의 유전성 나노복합체 층 내 충전 물질의 물질 중량%를 선택하는 단계; 프랙셔널 커패시터 및 저항의 직렬 결합에 걸쳐 입력 전압을 공급하는 단계; 저항에 걸친 전압에 기초하여 출력 전압을 공급하는 단계; 특정 주파수에서 필터의 계인을 측정하는 단계; 복소 임피던스 위상각을 변화시킴으로써 특정 주파수에서 필터의 계인에 따라 프랙셔널 오더 커패시터의 커패시턴스를 조절하는 단계를 포함한다. 구현예 44는 구현예 1 내지 13 중 어느 하나로부터의 프랙셔널 오더 커패시터 중 어느 하나를 포함하는 RF 통신 회로 작동 방법으로서, 이 방법은 특정의 복소 임피던스 위상각을 얻기 위하여 프랙셔널 오더 커패시터의 유전성 나노복합체 층 내 충전 물질의 물질 중량%를 선택하는 단계; 공진 주파수에서 RF 신호를 발생시키는 단계; RF 통신 회로 내의 다른 구성요소의 저항값을 검출하는 단계; 복소 임피던스 위상각을 변화시킴으로써 RF 통신회로 내의 다른 구성요소의 등가 직렬 저항값의 적어도 일부를 오프셋하기 위하여 프랙셔널 오더 커패시터의 음의 저항값을 설정하는 단계를 포함한다.

[0024] "약" 또는 "대략"의 용어는 이 분야의 통상의 기술자에게 이해되는 것과 근사한 것으로 정의되며, 하나의 비제한적인 구현예에서 이 용어들은 10% 이내, 바람직하게는 5% 이내, 더 바람직하게는 1% 이내, 그리고 가장 바람직하게는 0.5% 이내인 것으로 정의된다.

[0025] 단어 "하나"(a 또는 an)의 사용은 청구범위 또는 명세서에서 "포함하는(comprising)"의 용어와 함께 사용되는 경우 "하나"(one)를 의미할 수 있지만, 이는 또한 "하나 또는 그 이상", "적어도 하나", 및 "하나 또는 하나보다 많은"의 의미와도 일치한다.

[0026] "포함하는"(comprising)"(및 "~들을 포함하다"(comprise) 및 "~을 포함하다"(comprises)와 같은 이의 임의의 형태), "갖는" (having) (및 "~들을 갖다" (have) 및 "~을 갖다"(has)와 같은 이의 임의의 형태), "포함하는"(including) (및 "~을 포함하다"(includes) 및 "~들을 포함하다"(include)와 같은 이의 임의의 형태), "함유하는"(containing)(및 "~을 함유하다"(contains) 및 "~들을 함유하다"(contain)와 같은 이의 임의의 형태)의 단어들은 포함적이거나 또는 개방적인 것이며 추가의 열거되지 않은 요소 또는 방법 단계를 배제하지 않는다.

[0027] "연결된"(coupled)의 용어는 반드시 직접적으로는 아니며 또한 반드시 기계적으로도 아니더라도, 연결된(connected) 것으로 정의된다.

[0028] 본 발명의 유전성 재료, 전극층, 프랙셔널 오더 커패시터, 및 전자장치는 명세서에 걸쳐 개시된 특정성분, 구성요소, 조성물 등을 "포함하거나"(comprise), "~로 본질적으로 구성되거나"(consist essentially of) 또는 "~로 구성될"(consist of) 수 있다. 하나의 비제한적인 양상에서, 전이 단계 "~로 본질적으로 구성된(consist essentially of)"에 대하여, 본 발명의 커패시터의 기본적이고 신규한 특성은 커패시터의 복소 임피던스 각을 제어하는 능력이다.

[0029] 본 발명의 다른 목적, 특징 및 이점들은 이하의 도면, 상세한 설명 및 실시예들로부터 명백해질 것이다. 그러나, 도면, 상세한 설명, 실시예는 본 발명의 특정한 구현예를 지시하더라도 예시의 목적으로만 제시된 것이며 제한하고자 하는 의도가 아님이 이해되어야 한다. 또한, 이 상세한 설명으로부터 이 분야의 기술자들에게 본 발명의 정신 및 범위 내에서 변화와 변경이 명백하게 될 것임이 고려된다.

## 도면의 간단한 설명

[0030]

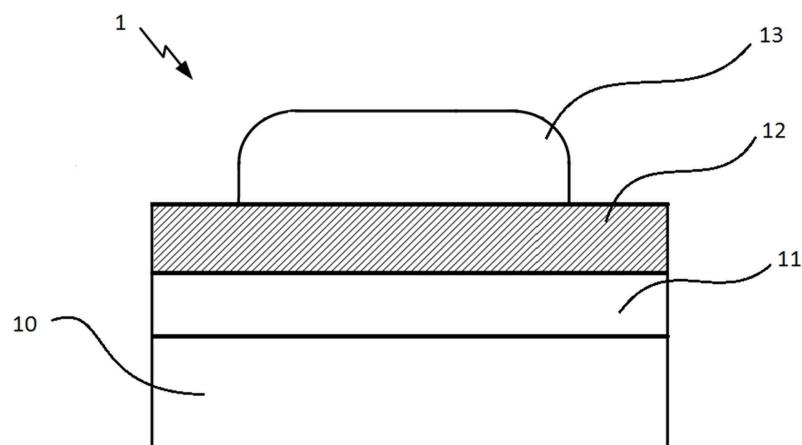

도 1은 본 발명의 프랙셔널 오더 커패시터이다.

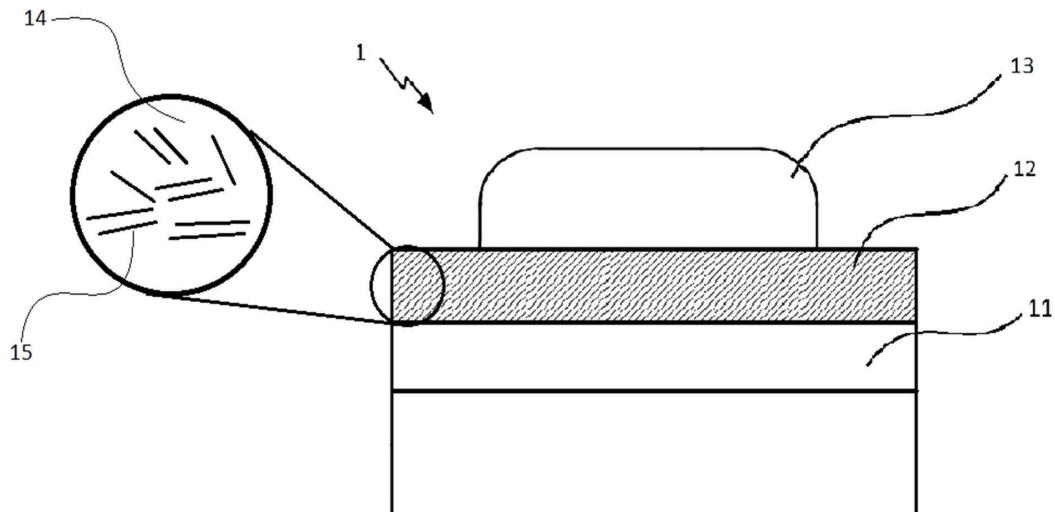

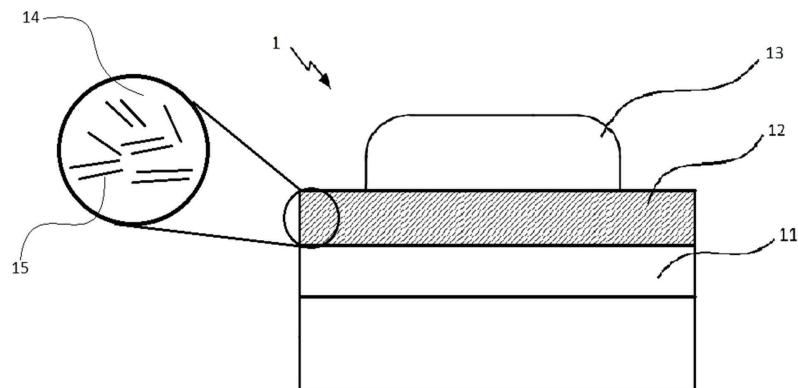

도 2는 프랙셔널 오더 커패시터의 유전성 나노복합체 내의 충전 물질을 보여주는 단면도이다.

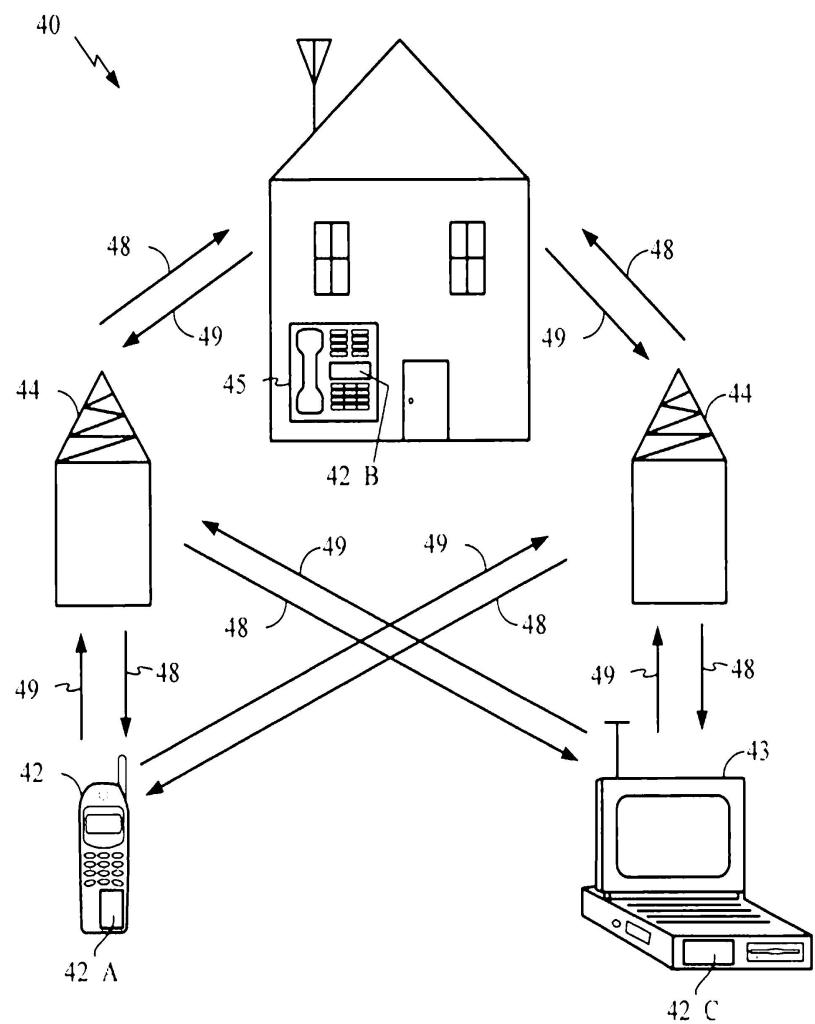

도 3은 본 발명의 프랙셔널 오더 커패시터가 유리하게 사용될 수 있는 예시적인 무선 통신 시스템을 나타내는 블록도이다.

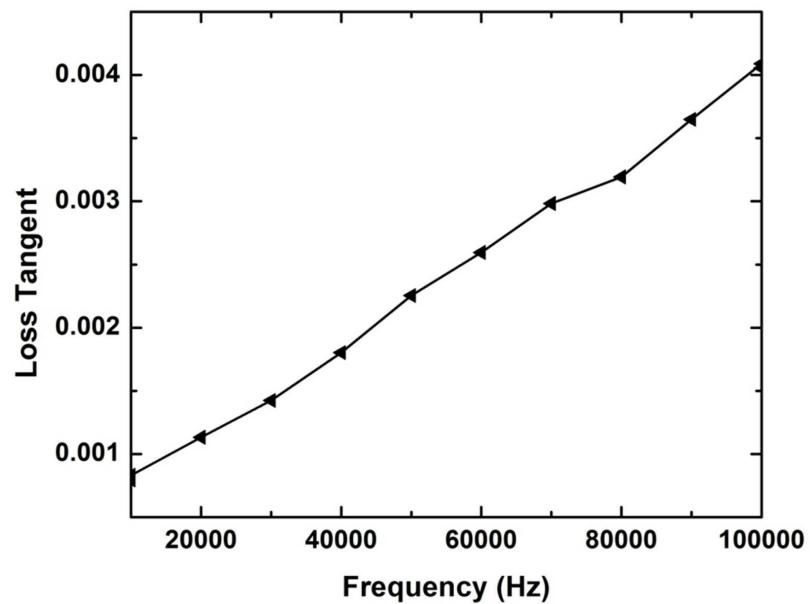

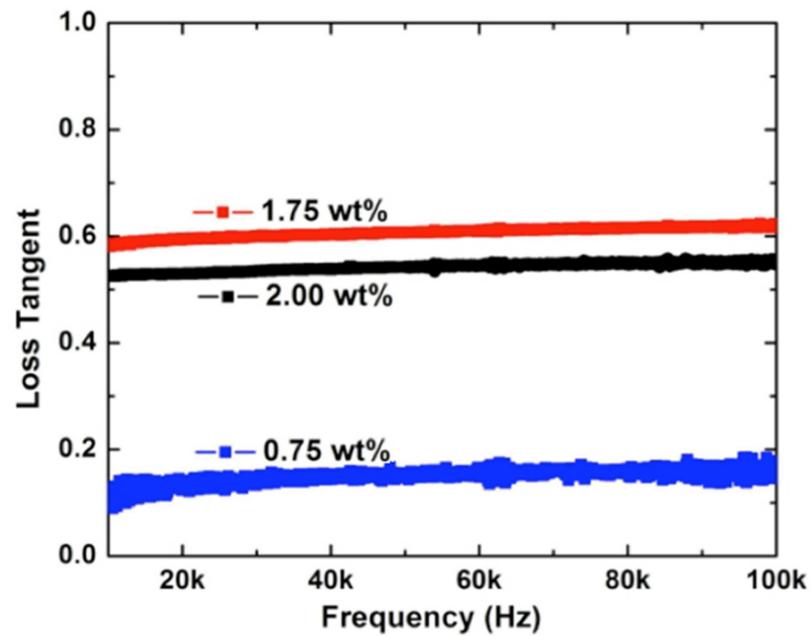

도 4는 측정된 주파수 범위에 걸쳐 일정한 값을 갖는 제조된 나노복합체 커패시터의 손실 탄젠트를 보여주는 그레핀을 갖는 P(VDF-TrFE-CFE)이다.

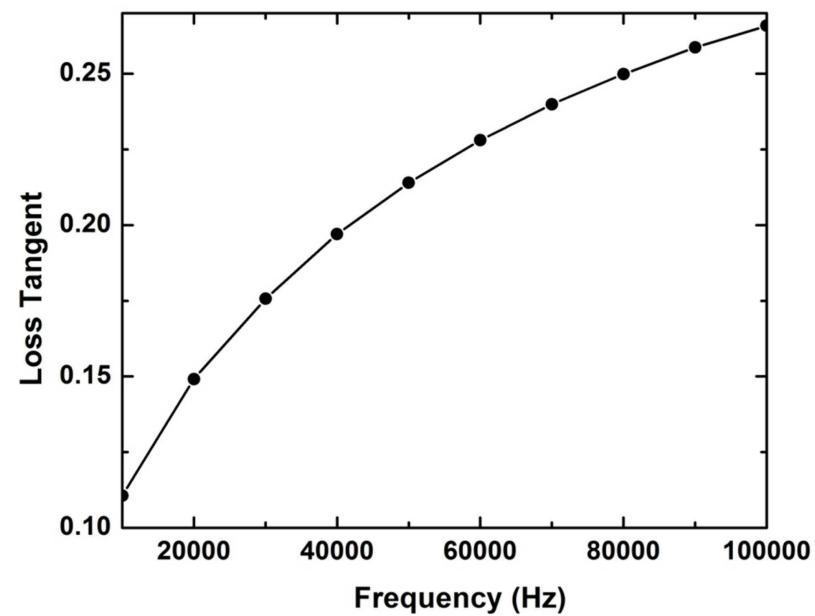

도 5는 10-100 kHz 사이의 증가하는 주파수에서 손실 탄젠트의 큰 증가를 보여주는 그레핀이 없는 P(VDF-TrFE-CFE)이다.

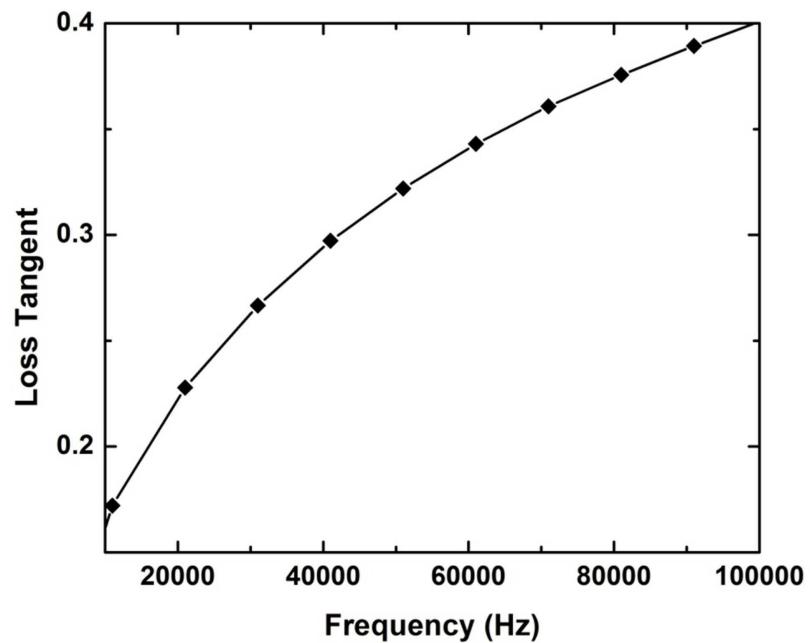

도 6은 10-100 kHz 사이의 증가하는 주파수에서 손실 탄젠트의 큰 증가를 보여주는 P(VDF-TrFE-CFE)/폴리아닐린 나노복합체이다.

도 7은 10-100 kHz 사이의 증가하는 주파수에서 손실 탄젠트의 큰 증가를 보여주는 폴리스티렌이다.

### 발명을 실시하기 위한 구체적인 내용

[0031]

프랙셔널 오더 커패시터의 실현을 가능하게 하는, 커패시터를 위한 개선된 유전성 물질이 발견되었다. 특히, 그 래핀과 같은 2차원 나노복합체 충전 물질을 폴리머 매트릭스 내로 결합하고, 충전 물질의 중량%를 변화시킴으로써, 커패시터의 복소 임피던스 위상각이 변할 수 있어, 프랙셔널 오더 커패시터의 실현을 가능하게 한다.

[0032]

본 발명의 이들 및 다른 비제한적인 양상들이 다음 섹션에서 자세히 논의된다.

[0033]

#### A. 프랙셔널 오더 커패시터

[0034]

도 1은 유전성 나노복합체 층을 포함하는 본 발명의 프랙셔널 오더 커패시터의 단면도이다. 프랙셔널 오더 커패시터(1)는 기판(10), 하부 전극(11), 유전성 나노복합체층(12), 및 단부 전극(13)을 포함할 수 있다. 프랙셔널 오더 커패시터는 두 개의 전도성 전극(11 및 13) 사이에, 폴리머 매트릭스와, 또한 충전 물질로도 기술되는 2차원 나노 물질을 포함하는 유전성 나노복합체 층을 센드위치함에 의하여 기판 상에 제조될 수 있다.

[0035]

실질적으로 정수-차수 임피던스를 갖는 표준 커패시터와 대조적으로, 본 발명의 프랙셔널 오더 커패시터는 -90도의 값에 제한되지 않는 위상각 시프트를 얻을 수 있다. 예를 들면, 프랙셔널 오더 커패시터는 저항과 커패시터의 위상각 사이에 위상각 시프트(예로서 -0.5)를 가질 수 있다. 그 결과, 이는 전기 설계자가 특정한 필요에 대한 위상 및 에너지 저장/발산 관계를 선택하는 데 더 많은 옵션을 제공하며 이에 따라 통상적으로 사용 가능하지 않은 전기 회로 및 방법의 구현을 허용한다.

[0036]

#### 1. 기판(10)

[0037]

기판(10)은 지지체로 사용된다. 본 발명의 프랙셔널 오더 커패시터는 여러 다른 기판을 사용하여 제조될 수 있다. 이 분야의 통상적인 기술자에게 알려진 많은 추가적인 기판 물질이 본 발명의 프랙셔널 오더 커패시터(1)와 함께 사용될 수 있다. 이러한 재료의 비제한적인 예는 실리콘, 플라스틱, 종이 등과 같은 무기 물질을 포함한다. 다른 예는 SABIC 폴리머, 및 폴리에테르아미드(예를 들어 ULETEM, EXTEM, SILITEM), 폴리(에틸렌테레프탈레이트), 폴리(부틸렌 테레프탈레이트), 폴리카보네이트(예를 들어 LEXAN), 폴리(페닐렌 옥사이드), 폴리올레핀, 폴리스티렌 및 폴리(비닐 클로라이드)를 포함하는 그의 코폴리머 및 혼합물을 기반으로 하는 기판이다. 프랙셔널 오더 커패시터는 실리콘 기판 및 금속 전극 상의 장치에서 또한 동일하게 수행하는 것으로 나타났다. 기판은 일반적으로 열 또는 유기 용제에 의해 쉽게 변경 또는 열화되지 않는 물질로 만들어진다.

[0038]

#### 2. 하부 전극 및 상부 전극(11, 13)

[0039]

하부 전극(11)은 전도성 물질로 만들어진다. 일반적으로, 하부 전극(11)은 그러한 물질을 사용하여 막을 형성함으로써 얻어진다(예를 들면, 진공 증착, 스퍼터링, 이온-플레이팅, 플레이팅, 코팅 등). 대안적으로, 기판은 바닥 전극의 역할을 하는 높은 도전성의 폴리머(폴리(3,4-에틸렌디이옥시티오펜):폴리(스티렌 설폰산), ~4%의 디메틸설록사이드(DMSO)로 도핑된 PEDOT:PSS Clevios PH-1000 (Heraeus))의 얇은 층으로 코팅될 수 있다. 전도성 막을 형성하기 위하여 사용될 수 있는 전도성 재료의 다른 비제한적인 예는 금, 백금, 은, 알루미늄 및 구리, 이리듐, 이리듐 산화물 등을 포함한다. 또한, 전도성 폴리머 재료의 비제한적인 예는 PEDOT: PSS, 폴리아닐린, 그레핀 등과 같은 전도성 폴리머를 포함한다. 하부 전극(11)을 위한 막의 두께는 일반적으로 20 nm 내지 500 nm

이다.

[0040] 상부 전극(13)은 패터닝 및 프로빙(probing)을 위한 새도우 마스크(shadow mask)를 사용하여 열 증발(thermally evaporating)에 의하여 유전성 나노복합체 층(12) 상에 배치될 수 있다. 상부 전극은 또한 도핑된 PH1000의 잉크젯 인쇄를 통해 패터닝될 수 있다. 이러한 커패시터는 실리콘 기판 및 금속 전극 상의 장치에서 또한 동일하게 수행하는 것을 나타났다. 상부 전극(13)을 위해 사용되는 물질은 또한 전도성이며, 바람직하게는 알루미늄이다. 이러한 다른 재료의 비제한적인 예는 하부 전극(11)과 관련하여 위에서 논의된 것과 같은 금속, 금속 산화물 및 전도성 폴리머(예를 들면, 폴리아닐린, 폴리티오펜, 등)을 포함한다. 상부 전극(13)은 단일층 또는 각각 서로 다른 작업 기능을 갖는 물질로 이루어진 박판의 층들(laminated layers)일 수 있다. 또한, 이는 낮은 작업 기능을 갖는 하나 또는 그 이상의 재료와 금, 은, 백금, 구리, 망간, 티타늄, 코발트, 니켈, 텉스텐, 및 주석으로 이루어진 군으로부터 선택된 적어도 하나의 합금일 수 있다. 합금의 예는 리튬-알루미늄 합금, 리튬-마그네슘 합금, 리튬-인듐 합금, 마그네슘-은 합금, 마그네슘-인듐 합금, 마그네슘-알루미늄 합금, 인듐-은 합금, 및 칼슘-알루미늄 합금을 포함한다. 상부 전극(13) 막의 두께는 일반적으로 20 nm 내지 500 nm 사이이다.

### 3. 유전성 나노복합체 층(12)

[0041] 도 2는 하부 전극(11)과 상부 전극(13) 사이에 개재된 유전성 나노복합체 층(12)의 단면이다. 유전성 나노복합체 층(12)은 충전 물질(15) 및 폴리머 물질(14)을 포함한다. 일 예에서, 유전성 나노복합체 층(12)은 충전 물질로 산화되지 않거나 일부 산화된 그래핀과 폴리머(14)를 사용한 혼합 용액일 수 있다. 폴리머(14)에 대한 그래핀의 농도는 0.1 중량% 내지 15 중량% 사이이다. 그래핀 합성의 비제한적인 예는 변경된 Hummer 방법에 따라 그라파이트로부터 그라파이트 산화물을 준비하는 것 (DOI: 10.1021/ja01539a017) 또는 그라파이트 산화물을 박리하여 그래핀 산화물 형성을 초래하는 하이드라진 모노하이드레이트 환원 (DOI:10.1016/j.carbon.2011.02.071)을 포함한다.

[0042] [0043] 유전성 나노복합체 층은 폴리머와 혼탁된(suspended) 충전 물질을 포함하는 용액을 얻는 것에 의하여 증착될 수 있다. 용액은 닥터 블레이드 코팅, 드롭-캐스팅, 스픈 코팅, 메니스커스 코팅, 전사 인쇄, 잉크젯 인쇄, 오프셋 인쇄, 스크린 인쇄 프로세스, 딥 코팅, 캐스팅, 바 코팅, 롤 코팅, 와이어 바 코팅, 스프레이, 스크린 인쇄, 그라비어 인쇄, 플렉소 인쇄, 오프셋 인쇄, 그라비어 오프셋 인쇄, 디스펜서 코팅, 노즐 코팅, 캐필러리 코팅(capillary coating) 등에 의해 증착될 수 있다.

### B. 프랙셔널 오더 커패시터 제조를 위한 방법의 구현예

[0044] [0045] 도 2를 참조하면, 프랙셔널 오더 커패시터(1)는 두 전도성 전극 사이에 충전 물질(15) 및 폴리머(14)의 유전성 나노복합체 층(12)을 배치함으로써 실리콘 기판 상에 제조된다. Pt 코팅된 실리콘 기판이 사용될 수 있으며 장치 제조 전에 아세톤, IPA 및 DI수로 세정된다. 원하는 로딩/loading)에 따라 0.1 내지 15 중량%의 그래핀 파우더가 계량되고 용액 내에 혼탁되며, 1-10 시간 동안 초음파처리된다. 폴리머(14)가 용액에 첨가되고 연속적으로 교반된다. 그래핀/폴리머 용액이 1-300분으로부터 4번 초음파처리되어 결과적으로 캐스팅 준비가 완료된 폴리머 용액 내의 그래핀 혼탁액(suspension)이 된다.

[0046] 유전성 나노복합체 층(12) 용액은 드롭 캐스팅에 의해 증착될 수 있으며 이어서 1-24 시간 동안 건조되도록 둔다. 공기-건조된 막은 진공으로 이송되고 1-48 시간 동안 건조된다. 위 알루미늄 전극은 새도우 마스크를 사용하여 막의 상부 표면 상에 열 증착되고 패터닝된다.

[0047] 본 발명의 과정은 고성능 프랙셔널 오더 커패시터를 효과적으로 대량 생산할 수 있다.

### C. 프랙셔널 오더 커패시터의 응용

[0048] [0049] 커패시터는 집적 회로 내의 매우 중요한 요소 중의 하나이며 많은 전자 기기 내에서 광범위하게 사용된다. 본 발명의 프랙셔널 오더 커패시터는 일반적으로 이용 가능하지 않은 전기 회로 및 방법을 구현하는 데 사용될 수 있다. 이는 회로 내에서 요구되는 구성요소의 수를 줄이는 것, 회로의 공진 주파수를 높이는 것, 전자 필터의 주파수 응답 형성(shaping)에 더 큰 유통성을 허용하는 것, 및 음의 저항 및 주파수 의존 음의 저항의 실현을 가능하게 하는 것을 포함한다. 이들 후자의 이익은 매우 큰 가치를 가질 수 있으며 더 다재다능한 전자 회로로의 문호를 개방한다.

[0050] 프랙셔널 오더 커패시터는 또한 에너지-저장 기능을 제공한다. 전압이 플레이트를 가로질러 인가될 때, 유전체 내의 전기장이 전하를 치환하며 이에 따라 에너지를 저장한다. 프랙셔널 오더 커패시터에 의해 저장되는 에너지의 양은 절연재료의 유전율 및 유전체의 치수(전체 면적 및 두께)에 의존한다. 본 발명의 프랙셔널 오더 커패시

터의 유전율은 충전 물질의 양과 유형을 변경함에 의해 바뀔 수 있다. 커패시터가 축적할 수 있는 에너지의 전체 양을 최대화하기 위하여, 유전율은 최대화되고, 유전총의 두께는 최소화된다.

[0051] 위에서 개시된 프랙셔널 오더 커패시터는 또한 접적 회로 내에 채용될 수 있다. 예를 들면, 프랙셔널 오더 커패시터는 마이크로프로세서와 같은 논리 장치의 NAND 또는 NOR 게이트의 일부일 수 있다. 특정한 회로가 설명되었지만 이 분야의 기술자라면 개시된 회로 모두가 본 명세서를 실현하는 데 필요한 것이 아님을 이해할 것이다. 또한, 특정한 공지의 회로는 본 명세서의 초점을 유지하기 위하여 설명되지 않았다.

[0052] 도 3은 본 명세서의 구현예가 유리하게 채용될 수 있는 예시적인 무선통신 시스템(40)을 나타내는 블록도이다. 설명을 위하여, 도 3은 3개의 원격 유닛(42, 43, 45) 및 두 개의 베이스 스테이션(44)을 나타낸다. 무선통신 시스템이 더 많은 원격 유닛과 베이스 스테이션을 가질 수 있음을 알 수 있을 것이다. 원격 유닛(42, 43, 45)은 개시된 프랙셔널 오더 커패시터를 포함하는 접적회로 또는 인쇄회로 기판을 포함할 수 있는 회로장치(42A, 42C, 42B)를 포함한다. 베이스 스테이션, 스위칭 장치, 및 네트워크 장비를 포함하여, 접적회로 또는 인쇄회로 기판을 포함하는 임의의 장치가 또한 여기에서 개시된 프랙셔널 오더 커패시터를 포함할 수 있음을 알 수 있을 것이다. 도 3은 베이스 스테이션(44)으로부터 원격 유닛(42, 43, 45)으로의 순방향 링크 신호(48) 및 원격 유닛(42, 43, 45)으로부터 베이스 스테이션(44)으로의 역방향 링크 신호(49)를 보여준다.

[0053] 도 3에서, 원격 유닛(42)은 이동전화로 도시되며, 원격 유닛(43)은 휴대용 컴퓨터로 도시되며, 원격 유닛(45)은 무선 로컬 루프 시스템 내의 고정위치 원격 유닛으로 도시되어 있다. 예를 들면, 원격 유닛은 이동전화, 휴대용 개인용 통신 시스템(hand-held personal communication systems, PCS) 유닛, 개인용 데이터 도우미(personal data assistants)와 같은 이동식 데이터 유닛, GPS 구동 장치, 내비게이션 장치, 셋업 박스, 음악 재생기, 비디오 재생기, 엔터테인먼트 유닛, 미터 판독 장치와 같은 고정 위치 데이터 유닛, 또는 데이터 또는 컴퓨터 명령을 저장하거나 검색하는 임의의 다른 장치, 또는 그 임의의 조합일 수 있다. 도 3이 본 명세서의 가르침에 따라 원격 유닛을 예시하고 있지만, 본 명세서는 이러한 예시적인 유닛에 제한되지 않는다. 본 명세서의 구현예는 프랙셔널 오더 커패시터(1)를 포함하는 임의의 장치에 적합하게 채용될 수 있다.

[0054] 본 명세서와 그 이점들이 여기에서 자세히 설명되었지만, 첨부된 청구범위에 의해 정의되는 본 명세서의 기술로부터 벗어나지 않고 다양한 변화, 대체 및 변경이 이루어질 수 있음이 이해되어야 할 것이다. 또한, 본 출원의 범위는 명세서 내에 기재된 특정한 구현예의 공정, 기계, 제조, 조성물, 수단, 방법 및 단계에 제한하고자 하는 것이 아니다. 이 분야의 통상의 기술자라면 본 명세서에 따라 여기에서 기재된 대응하는 구현예와 실질적으로 동일한 기능을 수행하거나 실질적으로 동일한 결과를 획득하는 현재 존재하거나 이후에 개발될 공정, 기계, 제조, 조성물, 수단, 방법 및 단계가 사용될 수 있다는 점을 본 명세서로부터 쉽게 이해할 것이다. 따라서, 첨부된 청구범위는 그 범위 내에 이러한 공정, 기계, 제조, 조성물, 수단, 방법 및 단계를 포함하는 것으로 의도된다.

### 실시예

[0056] 본 발명이 특정한 실시예에 의하여 더 자세히 설명된다. 이하의 실시예는 예시의 목적으로만 제공되는 것이며, 어떤 방법으로도 발명을 제한하고자 의도하지 않는다. 이 분야의 기술자는 변화 또는 변경될 수 있는 여러 중요하지 않은 파라미터가 본질적으로 동일한 결과를 가져올 수 있음을 쉽게 인식할 것이다.

### 실시예 1

[0058] 측정된 주파수 범위에 걸쳐 일정한 값을 갖는 제조된 나노복합체 커패시터의 손실 탄젠트를 보여주는 그래핀을 갖는 P(VDF-TrFE-CFE)

[0059] 프랙셔널 커패시터가 주파수에 대하여 일정한 위상 거동을 나타내는 것을 보여주는 손실 탄젠트 테스트를 수행하였다. 동일하게, 프랙셔널 커패시터는 주파수에 대해 일정한 손실 탄젠트를 나타낼 것이다(즉,  $\tan(\text{손실 탄젠트}) + \text{위상} = 90^\circ$  ). 실시예에서, 다른 로딩/loading)의 그래핀을 갖는 세 개의 샘플이 나타나 있으며, 큰 주파수 범위에 걸쳐 손실 탄젠트 및/또는 위상이 일정하다는 것이 명백하게 관찰된다. 도 4는 또한 0.75%의 로딩에 비하여 2% 및 1.75%의 로딩이 더 안정함을 보여준다(도 4 참조).

### 실시예 2

[0061] (10-100 kHz 사이의 증가하는 주파수에서 손실 탄젠트 값의 큰 증가를 보여주는

[0062] 그래핀이 없는 P(VDF-TrFE-CFE) )

[0063] 본 발명의 프랙셔널 오더 커패시터의 고유한 결과를 확인하기 위하여, 3개의 다른 정전 커패시터로부터의 추가적인 손실 탄젠트 데이터를 획득하였다. 선택된 막은: (1) 그래핀이 없는 P(VDF-TrFE-CFE), (2) P(VDF-TrFE-CFE) + 폴리아닐린 (PANI), 및 (3) 폴리스티렌이다. 이들 테스트에서, 결과는 10-100 kHz 사이에서 P(VDF-TrFE-CFE) 폴리머 막에 대해 손실 탄젠트의 현저한 변화(~140% 편차)를 보여준다. 이는 일차적으로 그래핀 시트의 부재와 따라서 마이크로커패시터 형성이 이루어지지 않는 것에 기인한다. 손실 탄젠트의 안정성은 폴리머 매트릭스 내에 전도성 그래핀을 추가한 것의 효과임이 명백하다(도 5 참조).

#### 실시예 3

[0065] (10-100 kHz 사이의 증가하는 주파수에서 손실 탄젠트 값의 큰 증가를 보여주는 P(VDF-TrFE-CFE)/폴리아닐린 나노복합체)

[0066] 다른 복합체 시스템을 사용하여 추가적인 테스트를 수행하였으며, P(VDF-TrFE-CFE)는 전도성 PANI 입자로 충전하였다. 도 6에서, 이들 막의 성능은 동일한 선택된 주파수 범위 내에서 손실 탄젠트의 큰 변화(>130%)를 명백히 나타낸다. 이것이 그래핀 시트에 비하여 삼투성인 복합체이지만, PANI 입자는 훨씬 낮은 종횡비를 가지며 RC 네트워크 시뮬레이션에 필요한 마이크로 커패시터 구조를 닮을 수 없다.

#### 실시예 4

[0068] (10-100 kHz 사이의 증가하는 주파수에서 손실 탄젠트 값의 큰 증가를 보여주는

[0069] 폴리스티렌)

[0070] 도 7에서 폴리스티렌의 통상적인 커패시터 막을 또한 테스트 하였다. 위의 커패시터 테스트와 비교할 때, 손실 탄젠트 값은 약 3차 규모 낮지만, 폴리스티렌은 손실에서 가장 큰 편차를 보인다(>400%).

## 도면

### 도면1

도면2

도면3

도면4

도면5

도면6

도면7