【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第6部門第1区分

【発行日】平成22年4月15日(2010.4.15)

【公開番号】特開2008-191137(P2008-191137A)

【公開日】平成20年8月21日(2008.8.21)

【年通号数】公開・登録公報2008-033

【出願番号】特願2007-122080(P2007-122080)

【国際特許分類】

G 01 R 19/00 (2006.01)

G 01 R 31/36 (2006.01)

H 01 M 10/48 (2006.01)

【F I】

G 01 R 19/00 B

G 01 R 31/36 A

H 01 M 10/48 P

【手続補正書】

【提出日】平成22年2月26日(2010.2.26)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

正電極、および負電極を有する蓄電素子の電圧検出器であって、

エミッタ端子を前記負電極に接続し、ベース端子とコレクタ端子を接続した第1pnpp型トランジスタと、

一端を前記正電極に接続した電圧電流変換素子と、

エミッタ端子を前記電圧電流変換素子の他端に接続し、ベース端子を前記第1pnpp型トランジスタの前記ベース端子に接続した第2pnpp型トランジスタと、

前記第1pnpp型トランジスタの前記コレクタ端子に接続され、前記コレクタ端子から電流を引く電流源と、

前記第2pnpp型トランジスタのコレクタ端子に接続され、コレクタ電流を検出する電流検出回路と、

前記電流検出回路の出力から前記正電極と前記負電極の間の電圧を出力する電圧出力回路とを備え、

前記蓄電素子の前記負電極は前記電流検出回路に対して正の電圧にバイアスされており、前記蓄電素子は直列に接続されるとともに、

複数の前記蓄電素子の最大電圧を有する正電極と、複数の前記蓄電素子の最小電圧を有する負電極を除く他の負電極との間にそれぞれ電流補償抵抗器を接続した構成を有し、

前記電流補償抵抗器は、前記各蓄電素子の負電極に接続された前記第1pnpp型トランジスタの前記コレクタ端子から引かれる電流と前記各電圧電流変換素子に流れる電流の和電流を供給でき、かつ前記蓄電素子の電圧が均等である場合は前記各電流補償抵抗器に流れ

る電流と前記和電流が等しくなるよう抵抗値を有するようにするとともに、

前記電流源の電流値が直列接続された前記蓄電素子の総電圧に比例するようにした蓄電素子の電圧検出器。

【請求項2】

前記第1pnpp型トランジスタ、および前記第2pnpp型トランジスタに替えて、それぞ

れ第1p型FET、および第2p型FETを備え、

前記第1pnp型トランジスタ、および前記第2pnp型トランジスタの前記エミッタ端子への接続を、前記第1p型FET、および前記第2p型FETのソース端子に、それぞれ行い、

前記第1pnp型トランジスタ、および前記第2pnp型トランジスタの前記ベース端子への接続を、前記第1p型FET、および前記第2p型FETのゲート端子に、それぞれ行い、

前記第1pnp型トランジスタ、および前記第2pnp型トランジスタの前記コレクタ端子への接続を、前記第1p型FET、および前記第2p型FETのドレイン端子に、それぞれ行った請求項1に記載の蓄電素子の電圧検出器。

#### 【請求項3】

正電極、および負電極を有する蓄電素子の電圧検出器であって、

エミッタ端子を前記正電極に接続し、ベース端子とコレクタ端子を接続した第1npn型トランジスタと、

一端を前記負電極に接続した電圧電流変換素子と、

エミッタ端子を前記電圧電流変換素子の他端に接続し、ベース端子を前記第1npn型トランジスタの前記ベース端子に接続した第2npn型トランジスタと、

前記第1npn型トランジスタの前記コレクタ端子に接続され、前記コレクタ端子に電流を供給する電流源と、

前記第2npn型トランジスタのコレクタ端子に接続され、コレクタ電流を検出する電流検出回路と、

前記電流検出回路の出力から前記正電極と前記負電極の間の電圧を出力する電圧出力回路とを備え、

前記蓄電素子の前記正電極は前記電流検出回路に対して負の電圧にバイアスされており、複数の前記蓄電素子は直列に接続されるとともに、

複数の前記蓄電素子の最小電圧を有する負電極と、複数の前記蓄電素子の最大電圧を有する正電極を除く他の正電極との間にそれぞれ電流補償抵抗器を接続した構成を有し、

前記電流補償抵抗器は、前記各蓄電素子の正電極に接続された前記第1npn型トランジスタの前記コレクタ端子に供給される電流と前記各電圧電流変換素子に流れる電流の和電流を供給でき、かつ前記蓄電素子の電圧が均等である場合は前記各電流補償抵抗器に流れる電流と前記和電流が等しくなるような抵抗値を有するようにするとともに、

前記電流源の電流値が直列接続された前記蓄電素子の総電圧に比例するようにした蓄電素子の電圧検出器。

#### 【請求項4】

前記第1npn型トランジスタ、および前記第2npn型トランジスタに替えて、それぞれ第1n型FET、および第2n型FETを備え、

前記第1npn型トランジスタ、および前記第2npn型トランジスタの前記エミッタ端子への接続を、前記第1n型FET、および前記第2n型FETのソース端子に、それぞれ行い、

前記第1npn型トランジスタ、および前記第2npn型トランジスタの前記ベース端子への接続を、前記第1n型FET、および前記第2n型FETのゲート端子に、それぞれ行い、

前記第1npn型トランジスタ、および前記第2npn型トランジスタの前記コレクタ端子への接続を、前記第1n型FET、および前記第2n型FETのドレイン端子に、それぞれ行った請求項3に記載の蓄電素子の電圧検出器。

#### 【請求項5】

前記電流源を駆動、停止させる駆動スイッチを前記電流源に接続し、前記蓄電素子の電圧検出時にのみ前記駆動スイッチをオンにして前記電流源を駆動させる請求項1、または3に記載の蓄電素子の電圧検出器。

#### 【請求項6】

前記電圧電流変換素子は抵抗器からなり、前記抵抗器の抵抗値が切替可能な構成とした請求項1、または3に記載の蓄電素子の電圧検出器。

【請求項7】

前記電流源の電流が前記蓄電素子の前記正電極と前記負電極の間の電圧に比例するようにした請求項1、または3に記載の蓄電素子の電圧検出器。

【請求項8】

前記電流源の電流、および前記電流補償抵抗器の電流を駆動停止する駆動スイッチを前記電流源、および前記電流補償抵抗器の一端に接続し、前記蓄電素子の電圧検出時にのみ前記駆動スイッチをオンにして前記電流源および前記電流補償抵抗器を駆動させる請求項1、または3に記載の蓄電素子の電圧検出器。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0008

【補正方法】変更

【補正の内容】

【0008】

前記従来の課題を解決するために、本発明の蓄電素子の電圧検出器は、正電極、および負電極を有する蓄電素子に対し、エミッタ端子を前記負電極に接続し、ベース端子とコレクタ端子を接続した第1pnP型トランジスタと、一端を前記正電極に接続した電圧電流変換素子と、エミッタ端子を前記電圧電流変換素子の他端に接続し、ベース端子を前記第1pnP型トランジスタの前記ベース端子に接続した第2pnP型トランジスタと、前記第1pnP型トランジスタの前記コレクタ端子に接続され、前記コレクタ端子から電流を引く電流源と、前記第2pnP型トランジスタのコレクタ端子に接続され、コレクタ電流を検出する電流検出回路と、前記電流検出回路の出力から前記正電極と前記負電極の間の電圧を出力する電圧出力回路とを備え、前記蓄電素子の前記負電極は前記電流検出回路に対して正の電圧にバイアスされており、前記蓄電素子は直列に接続されるとともに、複数の前記蓄電素子の最大電圧を有する正電極と、複数の前記蓄電素子の最小電圧を有する負電極を除く他の負電極との間にそれぞれ電流補償抵抗器を接続した構成を有し、前記電流補償抵抗器は、前記各蓄電素子の負電極に接続された前記第1pnP型トランジスタの前記コレクタ端子から引かれる電流と前記各電圧電流変換素子に流れる電流の和電流を供給でき、かつ前記蓄電素子の電圧が均等である場合は前記各電流補償抵抗器に流れる電流と前記和電流が等しくなるような抵抗値を有するようにするとともに、前記電流源の電流値が直列接続された前記蓄電素子の総電圧に比例するようにしたものである。

【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0009

【補正方法】変更

【補正の内容】

【0009】

また、本発明の蓄電素子の電圧検出器は、正電極、および負電極を有する蓄電素子に対し、エミッタ端子を前記正電極に接続し、ベース端子とコレクタ端子を接続した第1nPN型トランジスタと、一端を前記負電極に接続した電圧電流変換素子と、エミッタ端子を前記電圧電流変換素子の他端に接続し、ベース端子を前記第1nPN型トランジスタの前記ベース端子に接続した第2nPN型トランジスタと、前記第1nPN型トランジスタの前記コレクタ端子に接続され、前記コレクタ端子に電流を供給する電流源と、前記第2nPN型トランジスタのコレクタ端子に接続され、コレクタ電流を検出する電流検出回路と、前記電流検出回路の出力から前記正電極と前記負電極の間の電圧を出力する電圧出力回路とを備え、前記蓄電素子の前記正電極は前記電流検出回路に対して負の電圧にバイアスされており、複数の前記蓄電素子は直列に接続されるとともに、複数の前記蓄電素子の最小電圧を有する負電極と、複数の前記蓄電素子の最大電圧を有する正電極を除く他の正電

極との間にそれぞれ電流補償抵抗器を接続した構成を有し、前記電流補償抵抗器は、前記各蓄電素子の正電極に接続された前記第1n p n型トランジスタの前記コレクタ端子に供給される電流と前記各電圧電流変換素子に流れる電流の和電流を供給でき、かつ前記蓄電素子の電圧が均等である場合は前記各電流補償抵抗器に流れる電流と前記和電流が等しくなるような抵抗値を有するようにするとともに、前記電流源の電流値が直列接続された前記蓄電素子の総電圧に比例するようにしたものである。

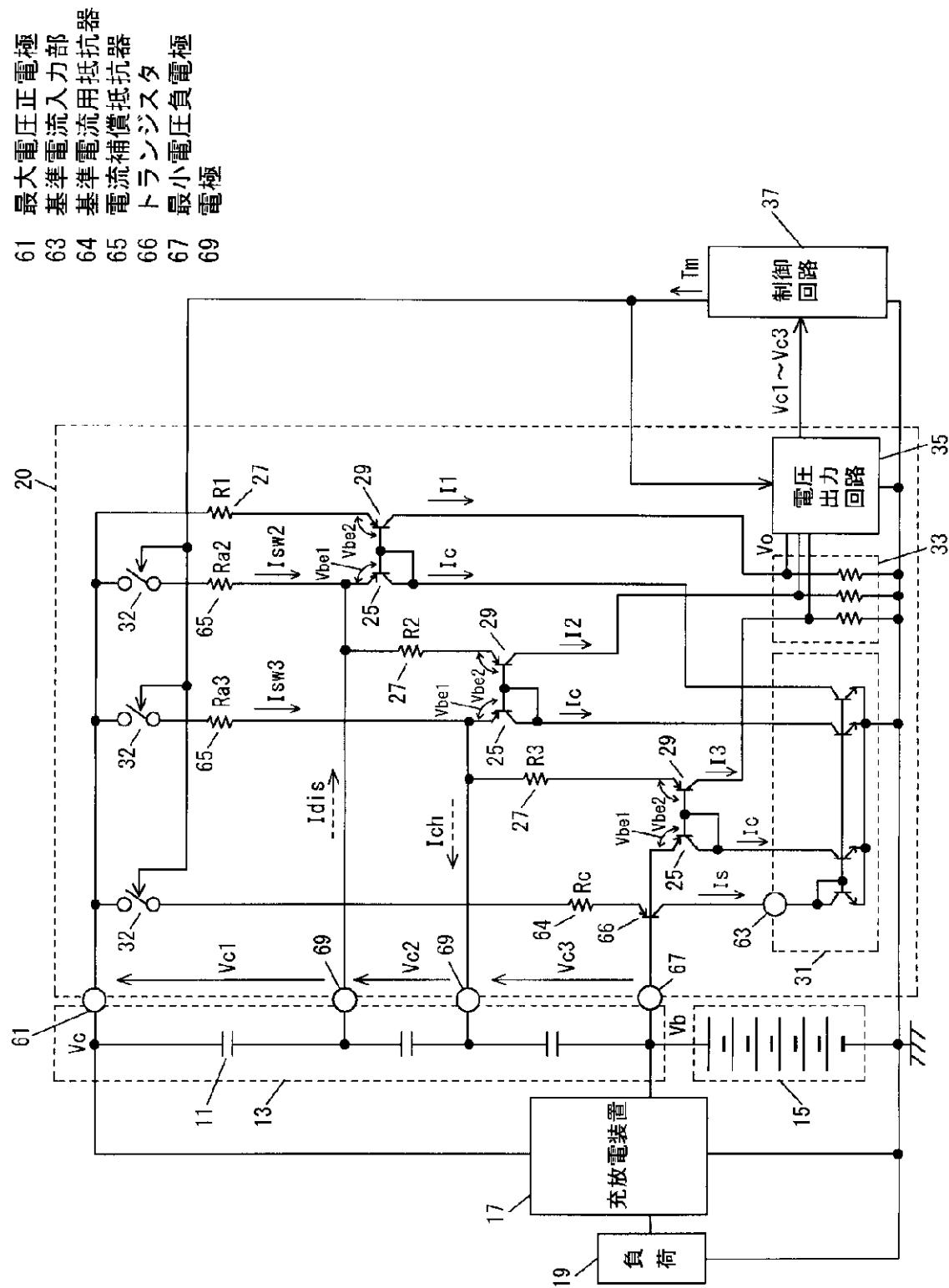

【手続補正4】

【補正対象書類名】図面

【補正対象項目名】図8

【補正方法】変更

【補正の内容】

【図 8】