(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4376323号

(P4376323)

(45) 発行日 平成21年12月2日(2009.12.2)

(24) 登録日 平成21年9月18日(2009.9.18)

(51) Int.Cl.

F 1

|                    |                  |            |      |

|--------------------|------------------|------------|------|

| <b>H01L 29/786</b> | <b>(2006.01)</b> | H01L 29/78 | 619A |

| <b>H01L 21/336</b> | <b>(2006.01)</b> | H01L 29/78 | 627A |

| <b>G02F 1/136</b>  | <b>(2006.01)</b> | H01L 29/78 | 627G |

| <b>G09F 9/35</b>   | <b>(2006.01)</b> | H01L 29/78 | 627Z |

|                    |                  | GO2F 1/136 |      |

請求項の数 13 (全 12 頁) 最終頁に続く

(21) 出願番号

特願平9-90927

(22) 出願日

平成9年4月9日(1997.4.9)

(65) 公開番号

特開平10-41518

(43) 公開日

平成10年2月13日(1998.2.13)

審査請求日

平成16年4月5日(2004.4.5)

(31) 優先権主張番号

96-10607

(32) 優先日

平成8年4月9日(1996.4.9)

(33) 優先権主張国

韓国(KR)

(31) 優先権主張番号

97-12306

(32) 優先日

平成9年4月3日(1997.4.3)

(33) 優先権主張国

韓国(KR)

(73) 特許権者

390019839

三星電子株式会社

SAMSUNG ELECTRONICS

CO., LTD.大韓民国京畿道水原市靈通区梅灘洞416

416, Maetan-dong, Yeon

gton-gu, Suwon-si,

Gyeonggi-do 442-742

(KR)

(74) 代理人

100094145

弁理士 小野 由己男

(74) 代理人

100106367

弁理士 稲積 朋子

最終頁に続く

(54) 【発明の名称】表示装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上にポリシリコン膜からなる半導体層、ゲート、前記半導体層と前記ゲートとの間に配置されたゲート絶縁膜、ソース及びドレインを備える薄膜トランジスタを形成する段階と、

前記薄膜トランジスタが形成された基板上に水分を含有する絶縁膜である平坦化膜を形成する段階と、

前記平坦化膜に含まれた水分を前記薄膜トランジスタに拡散させるために前記平坦化膜を300～400で熱処理する段階と、

前記熱処理された平坦化膜上に窒化膜または酸化膜と窒化膜との複合膜よりなる絶縁膜を形成する段階と、

前記平坦化膜上の前記絶縁膜の所定部分に前記ドレインと電気的に連結するように画素電極を形成する段階と、

前記画素電極が形成された基板結果物を150～200で熱処理する段階とを備えることを特徴とする表示装置の製造方法。

## 【請求項 2】

前記平坦化膜はスピノングラス(SOG)膜で形成する請求項1に記載の表示装置の製造方法。

## 【請求項 3】

前記平坦化膜は1000～3000の厚さに形成する請求項1に記載の表示装置の製

10

20

造方法。

**【請求項 4】**

基板上に形成されたポリシリコン膜からなる半導体層、ゲート電極、前記半導体層と前記ゲートとの間に配置されたゲート絶縁膜、ソース電極及びドレイン電極を備える薄膜トランジスタを形成する段階と、

前記薄膜トランジスタが形成された基板上に第1絶縁膜を形成する段階と、

前記第1絶縁膜上に水分を含有する第2絶縁膜を形成する段階と、

第2絶縁膜に含まれた水分を前記薄膜トランジスタに拡散させるため、前記第2絶縁膜を300～400で熱処理する段階と、

前記熱処理された第2絶縁膜の表面が平坦化されるように前記第2絶縁膜の表面を所定の厚さだけエッチバックする段階と、

前記平坦化された前記第2絶縁膜上に窒化膜または酸化膜と窒化膜との複合膜からなる第3絶縁膜を形成する段階と、

前記第3、第2及び第1絶縁膜を貫通して、前記第3絶縁膜上に前記ドレインとコンタクトするように画素電極を形成する段階と、

前記画素電極が形成された基板結果物を150～200で熱処理する段階とを含むことを特徴とする表示装置の製造方法。

**【請求項 5】**

前記薄膜トランジスタを形成する段階は、

前記基板上に結晶質シリコン膜で半導体膜パターンを形成する段階と、

前記基板及び半導体膜パターン上にゲート絶縁膜を形成する段階と、

前記ゲート絶縁膜上の所定部分にゲート電極を形成する段階と、

前記ゲート電極の両側の半導体膜パターンに不純物を注入して、前記ソース及びドレインを形成する段階と、

前記ゲート絶縁膜及び前記ゲート電極上に層間絶縁膜を形成する段階と、

前記層間絶縁膜上に前記ソース及びドレインと各々コンタクトされるソース電極及びドレイン電極を形成する段階とを含む請求項4に記載の表示装置の製造方法。

**【請求項 6】**

前記半導体膜パターンを形成する段階は、

前記基板上に非晶質シリコン膜を蒸着する段階と、

前記非晶質シリコン膜をレーザで結晶化する段階と、

前記結晶化されたシリコン膜をパターニングする段階とを含む請求項5に記載の表示装置の製造方法。

**【請求項 7】**

前記ソース及びドレインはイオンシャワードーピングによって形成される請求項4に記載の表示装置の製造方法。

**【請求項 8】**

前記第2絶縁膜はSOG膜で形成する請求項4に記載の表示装置の製造方法。

**【請求項 9】**

前記第2絶縁膜は1000～3000の厚さに形成する請求項4に記載の表示装置の製造方法。

**【請求項 10】**

前記第3絶縁膜は窒化膜または酸化膜と窒化膜との複合膜で形成する請求項4に記載の表示装置の製造方法。

**【請求項 11】**

前記第2絶縁膜を形成する段階と、前記第2絶縁膜を熱処理する段階とを少なくとも1回繰り返して実施する請求項4に記載の表示装置の製造方法。

**【請求項 12】**

前記画素電極はITO(Indiumtin oxide)で形成する請求項1に記載の表示装置の製造方法。

10

20

30

40

50

**【請求項 1 3】**

前記第2絶縁膜をエッチバックする段階で、前記第2絶縁膜を前記第3絶縁膜の表面が露出されるまでエッチバックする請求項4に記載の表示装置の製造方法。

**【発明の詳細な説明】****【0 0 0 1】****【発明の属する技術分野】**

本発明は、半導体装置の製造方法及び液晶表示装置の製造方法に係り、特に薄膜トランジスタ(Thin Film Transistor:以下TFTという)を含む半導体装置の製造方法及び該薄膜トランジスタを能動素子として使用する液晶表示装置の製造方法に関する。

**【0 0 0 2】**

10

**【従来の技術】**

液晶表示装置(Liquid Crystal Display:以下LCDという)は、電場により分子の配列が変化する液晶の光学的性質を用いる液晶技術と半導体技術を融合した代表的な平板表示装置である。

**【0 0 0 3】**

液晶表示装置の一種である薄膜トランジスタ液晶表示装置(Thin Film Transistor-LCD:以下TFT-LCDという)は、低消費電力、低電圧駆動力、薄型、軽量といった長所を有している。このTFTは、チャンネルで使用される半導体層の材料により多結晶シリコンTFTと非晶質シリコンTFTとに分けられる。多結晶シリコン膜TFT-LCDを製造する工程は、400以下の温度で行われる低温工程と900以上の高温で行われる高温工程とに分けられる。この中でも、特に350以下の温度で工程が行われる低温工程は、ガラス基板上での工程が可能であるため大面積化されたLCDの製造に適する。これは多結晶シリコン膜TFT-LCDが非晶質シリコン膜TFT-LCDに対して競争力を有し得る1つの要件となる。

20

**【0 0 0 4】**

ところが、上記の低温工程と高温工程を経ると、いずれの工程においても、多結晶シリコン膜自体のグレーン境界面に起因して、電子や正孔の移動を妨害するトラッピング中心が存在することになる。このトラッピング中心の存在はキャリヤの移動度を低下させ、TFTのスレショルド電圧を増加させる。

**【0 0 0 5】**

低温工程を用いて高性能のTFTを製造するためには様々な技術が必要である。

30

**【0 0 0 6】**

第1は、基板を熱的に変形させることなく、基板上に良質の多結晶シリコン膜を形成する技術である。良質の多結晶シリコン膜を形成するためにはレーザー誘導による急速な結晶化が好適な方法である。レーザを用いたシリコン薄膜の結晶化は高温で基板を加熱せずに行われるので基板の損傷が少ない。レーザーアニーリングによる多結晶シリコン膜のキャリヤ移動度は約100平方cm/Vsより大きい。

**【0 0 0 7】**

第2は、低温で、多結晶シリコン膜と酸化膜との良質の界面を形成する技術である。多結晶シリコン膜と酸化膜との界面でトラップ密度が高ければ、TFTのスレショルドが高くなる。例えば、プラズマを用いた化学気相蒸着(Plasma Enhanced CVD:以下PECVDという)方法が、低温(例えば200~400)で酸化膜を形成するに適しているが、PECVD方法は多結晶シリコン膜と酸化膜との界面を著しく低下させる。このような界面の低下を低減する方法として、電子サイクロトロン共鳴プラズマCVD(Electron Cyclotron Resonance Plasma CVD:ECR CVD)とRF平行平板型リモートプラズマCVD(Radio Frequency Parallel-plate Remote Plasma CVD)等がある。RF平行平板型リモートプラズマCVD法で形成された酸化膜を有する多結晶シリコン膜TFTは、例えば400平方cm/Vs程度の高移動度と、1.5Vほどの低スレショルド電圧を有する。

40

**【0 0 0 8】**

第3は、金属化後のアニーリング工程である。空気中270の温度でTFTをアニーリングすればTFTの特性を改善することができる。しかし、このようなアニーリング方法では

50

、酸化膜や酸化膜とシリコン膜との界面の再現性がよくない。このようなアニーリング法で最も調節しにくい要素は空気の湿度である。従って、このような問題点を解決するために、低温で水蒸気 (H<sub>2</sub>O vapor) を調節する方法によるアニーリング法が提案された。空気中の水蒸気は、リモートプラズマ CVD 法で形成された酸化膜を使用する TFT を低温でアニーリングするために最も効果的な成分である。

#### 【0009】

上記の基本技術等を用いる従来技術が “Naoki Sano, IEEE Electron Device, vol. 16, No. 5, May 1995, pp. 157-160” に掲載されている。

#### 【0010】

この従来技術においては、TFT を製造する過程で多結晶シリコン膜と酸化膜との界面に存在するトラッピング中心を除去するために基板を水蒸気雰囲気でアニーリングする他、トラッピング中心をさらに効果的に除去するために、酸化膜を一般的な CVD 法で形成せずにリモートプラズマ CVD 法で形成する。このような方法は、多結晶シリコン膜と酸化膜との界面でトラッピングを除去するには効果がある。しかし、アニーリングのための追加的な工程が必要であり、例えば水蒸気を形成するために水を加熱する別のシリンダーをさらに具備する必要があり、設備の付加が余儀なくされる。また、プラズマを用いて酸化膜を形成する場合、多結晶シリコン膜の表面が損傷され素子の特性が悪くなる。

10

#### 【0011】

【発明が解決しようとする課題】

本発明は、上記の問題点を鑑みてなされたものであり、その 1 つの目的は、水分を多量に含有する絶縁膜を用いてトラッピングを除去すると共に平坦なパッシベーション膜を形成し得る薄膜トランジスタの製造方法を提供することにある。

20

#### 【0012】

また、本発明の他の目的は、上記の薄膜トランジスタの製造方法を用いて、特性の良好な薄膜トランジスタ液晶表示装置の製造方法を提供することにある。

#### 【0013】

【課題を解決するための手段】

発明 1 は、以下の段階を含む表示装置の製造方法に関する。

- ・基板上にゲート、ソース及びドレインを備える薄膜トランジスタを形成する段階。

- ・前記薄膜トランジスタが形成された基板上に水分を含有する絶縁膜である平坦化膜を形成する段階。

- ・前記平坦化膜に含まれた水分を前記薄膜トランジスタに拡散させるために前記平坦化膜を 300 ~ 400 で熱処理する段階。

- ・前記平坦化膜上に窒化膜または酸化膜と窒化膜との複合膜よりなる絶縁膜を形成する段階。

- ・前記平坦化膜上の所定部分に前記ドレインと電気的に連結するように画素電極を形成する段階。

- ・前記基板結果物を 150 ~ 200 で熱処理する段階。

30

#### 【0014】

発明 2 は、発明 1 において、前記平坦化膜はスピンドルグラス (SOG) 膜で形成することを特徴とする。

40

発明 3 は、発明 1 において、前記平坦化膜は 1000 ~ 3000 の厚さに形成することを特徴とする。

#### 【0015】

発明 4 は、以下の段階を含む表示装置の製造方法に関する。

- ・基板上にゲート、ソース及びドレインを備える薄膜トランジスタを形成する段階。

- ・前記薄膜トランジスタが形成された基板上に第 1 絶縁膜を形成する段階。

- ・前記第 1 絶縁膜上に水分を含有する第 2 絶縁膜を形成する段階。

- ・第 2 絶縁膜に含まれた水分を前記薄膜トランジスタに拡散させるため、前記第 2 絶縁膜を 300 ~ 400 で熱処理する段階。

50

- ・前記第2絶縁膜の表面が平坦化されるように前記第2絶縁膜の表面を所定の厚さだけエッチバックする段階。

- ・平坦化された前記第2絶縁膜上に第3絶縁膜を形成する段階。

- ・前記第3及び第2絶縁膜を貫通して、前記第3絶縁膜上に前記ドレインとコンタクトするように画素電極を形成する段階。

- ・前記画素電極が形成された基板結果物を150～200で熱処理する段階。

**【0016】**

発明5は、発明4において、前記薄膜トランジスタを形成する段階は、前記基板上に結晶質シリコン膜で半導体膜パターンを形成する段階と、前記基板及び半導体膜パターン上にゲート絶縁膜を形成する段階と、前記ゲート絶縁膜上の所定部分にゲート電極を形成する段階と、前記ゲート電極の両側の半導体膜パターンに不純物を注入して、前記ソース及びドレインを形成する段階と、前記ゲート絶縁膜及び前記ゲート電極上に層間絶縁膜を形成する段階と、前記層間絶縁膜上に前記ソース及びドレインと各々コンタクトされるソース電極及びドレイン電極を形成する段階と、を含むことを特徴とする。10

**【0017】**

発明6は、発明5において、前記半導体膜パターンを形成する段階は、前記基板上に非晶質シリコン膜を蒸着する段階と、前記非晶質シリコン膜をレーザで結晶化する段階と、前記結晶化されたシリコン膜をパターニングする段階と、を含むことを特徴とする。

**【0018】**

発明7は、発明4において、前記ソース及びドレインはイオンシャワードーピングによって形成されることを特徴とする。20

発明8は、発明4において、前記第2絶縁膜はSOG膜で形成することを特徴とする。

発明9は、発明4において、前記第2絶縁膜は1000～3000程度の厚さに形成することを特徴とする。

**【0019】**

発明10は、発明4において、前記第3絶縁膜は窒化膜または酸化膜と窒化膜との複合膜で形成することを特徴とする。

発明11は、発明4において、前記第2絶縁膜を形成する段階と、前記第2絶縁膜を熱処理する段階とを少なくとも1回繰り返して実施することを特徴とする。30

**【0020】**

発明12は、発明1において、前記画素電極はITO(Indiumtin oxide)で形成することを特徴とする。

発明13は、発明4において、前記第2絶縁膜をエッチバックする段階で、前記第2絶縁膜を前記第3絶縁膜の表面が露出されるまでエッチバックすることを特徴とする。

**【0021】****【発明の実施の形態】**

以下、添付図面に基づき本発明の好適な実施の形態に係る薄膜トランジスタ液晶表示装置の製造方法を詳しく説明する。

**【0022】**

この実施の形態では、350以下の温度で工程が実行され、LCDの大面積化に容易な低温多結晶シリコン膜工程において、水分を多量に含む絶縁膜を使用してパッシベーション膜を形成し、これによって、前記絶縁膜内に含まれた水分子を素子内部に拡散させることにより前記界面のトラップを修復する。40

**【0023】**

水分を含む絶縁膜の中で、特にスピノンガラス(Spin On Glass:SOG)膜内には各種有機物と共に水分(H<sub>2</sub>O)や水素(H<sub>2</sub>)が多量に含まれている。またSOG膜は液体状態の絶縁物質であって、ポリアミドのように非常に狭いスペースを充填することができる。この場合において、他のCVD薄膜はボイドを形成する可能性があるが、SOG膜はボイドを形成する可能性が非常に低い。

**【0024】**

10

20

30

40

50

SOG膜には他にも多くの利点がある。即ち、例えばパターン中に角部があっても良好な段差塗布性が得られる。この場合、スペースが狭いほどその効果は優れる。そして、SOG膜は、膜の形成工程が簡単であり、膜内の欠陥密度が低く、生産性が高い。また、加工費用が安く、危険なガスの取扱いがないので安全な作業ができる。SOG膜は、アルコールをベースとするソルベントに混合されたシリケートであって、このソルベントはベーク工程時に揮発するため、ベーク後には固形成分のみが残って酸化膜( $\text{SiO}_2$ )と類似したものになる。

#### 【0025】

以下、このようなSOGを使用する薄膜トランジスタの製造方法の一例を添付図面を参照しながら説明するが、本発明はこの方法に限定されるものではない。

10

#### 【0026】

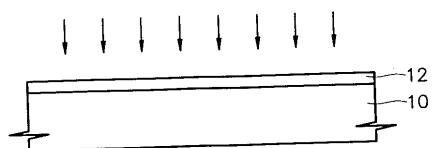

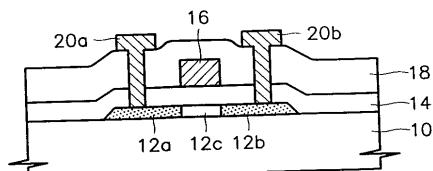

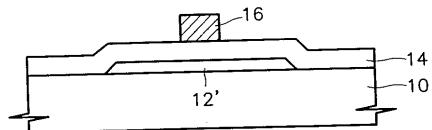

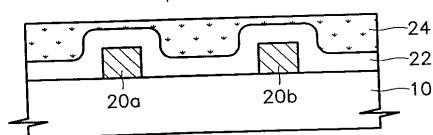

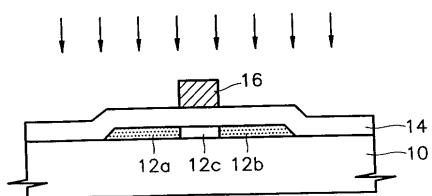

図1乃至図8は、本発明の好適な実施の形態に係る薄膜トランジスタ液晶表示装置の製造方法を工程順に示した断面図であって、本発明を上部ゲート(*top gate type*)型TFTに適用した例を示している。

#### 【0027】

図1に示す工程では、例えばガラスのような光透過性基板10上に非晶質シリコン膜を300~1500の厚さで蒸着した後に、この非晶質シリコン膜を結晶化することによりTFTのチャンネルに使用される半導体膜12を形成する。この非晶質シリコン膜の結晶化は、例えばレーザーを用いて行われる。

#### 【0028】

図2に示す工程では、半導体膜12をパタニングして半導体膜パターン12'を形成した後に、その結果物の全面に、例えば厚さが500~2500の酸化膜または1000~5000の窒化膜を蒸着して、ゲート絶縁膜14を形成する。次いで、ゲート絶縁膜14上に、例えばアルミニウムまたはアルミニウム合金を2000~4000の厚さで蒸着した後に、これをパタニングしてゲート電極16を形成する。

20

#### 【0029】

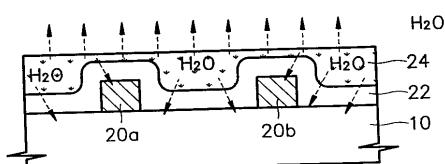

図3に示す工程では、半導体膜パターン12'に不純物イオンを注入してソース領域12a及びドレイン領域12bを形成する。このイオン注入は、ゲート電極16をマスクとして使用し、例えばイオンシャワードーピング方法を使用して行われる。そして、注入する不純物としては、形成すべきTFTのタイプによりホウ素または燐を使用し得る。この際、半導体膜パターン12'上のゲート電極16によりマスキングされて、不純物イオンが注入されない部分がTFTのチャンネル12cとなる。

30

#### 【0030】

図4に示す工程では、ソース領域12a及びドレイン領域12bが形成された結果物の全面に、例えば酸化膜または窒化膜を蒸着して層間絶縁膜18を形成する。次いで、写真蝕刻工程を使用して層間絶縁膜18を部分的に蝕刻し、ソース領域12a及びドレイン領域12bを露出させるコンタクトホールを形成する。次いで、コンタクトホールが形成された結果物上に、例えばアルミニウムのような導電物質を4000~8000の厚さで蒸着した後に、これをパタニングしてソース電極20a及びドレイン電極20bを形成する。

40

#### 【0031】

図5に示す工程では、ソース電極20a及びドレイン電極20bが形成された結果物の全面に絶縁膜を蒸着して第1絶縁膜22を形成する。第1絶縁膜22は、例えばCVD法で形成することができる。より具体的には、第1絶縁膜22は、例えば、プラズマ化学気相蒸着法(Plasma Enhanced Chemical Vapor Deposition: PECVD)若しくは大気圧化学気相蒸着法(Atmosphere Pressure Chemical Vapor Deposition: APCVD)で蒸着されたシリコン酸化膜又はプラズマ化学気相蒸着法(PECVD)で蒸着されたシリコン窒化膜等で構成することができる。また、第1絶縁膜22は、例えば1000~10000程度の厚さで形成すれば良いが、後続工程で第1絶縁膜22上に形成される膜からTFTへの水分の拡散を容易にするために、可能な限り薄く形成することが望ましい。例えば、第1絶縁膜22がシリ

50

コン酸化膜の場合は、4000～50000 程度に形成することが望ましく、5000 を超えない範囲内で適切に調節することができる。

#### 【0032】

なお、図5乃至図7においては、第1乃至第3絶縁膜の形成工程の理解を容易にするために、第1絶縁膜22の下部の構造が簡略化して示されている。

#### 【0033】

次いで、第1絶縁膜22上にパッシベーション膜(passivation layer)として第2絶縁膜24を形成する。この第2絶縁膜24は、水分を多量に含む絶縁膜で形成するが、これは、水分及び水素を多量に含んでいるために平坦化が容易なSOG膜で形成することが望ましい。

10

#### 【0034】

このSOG膜は液体状態であり、フォトレジストと同一の方法(例えばスピンドルリング法)により第1絶縁膜22上に均一な厚さで塗布することができる。また、SOG膜によれば、狭いスペースでも優れた平坦度が得られるので、ゲート電極16、ソース電極20a及びドレイン電極20bその他の段差を起こすパターン間を、欠陥(例えばボイド)を発生させることなく充填することができる。

#### 【0035】

このSOG膜を構成するソルベントは、SOG膜が塗布された後に、蒸発が急速に起こる。従って、適切な厚さの均一性を得るために、最適のSOG噴射及びスピンドルリングサイクルを選択する必要がある。

20

#### 【0036】

第2絶縁膜24(即ちSOG膜)の厚さは、1000～3500 の厚さの範囲内で自由に選択し得る。しかし、後続のベーク工程で多量のソルベントが蒸発して水分が外部に拡散して、これによりSOGに張力が加えられるため、これを考慮してSOG膜の厚さを決定する必要がある。

#### 【0037】

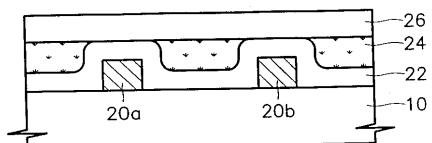

図6に示す工程では、第2絶縁膜24、即ちスピンドルリングされたSOG膜を300～400 の温度で0.5～4時間ベークする。

#### 【0038】

ここで、SOG膜24のベーク過程をより具体的に説明する。ベークが進行すると、SOG膜24からソルベントが先に蒸発する。次いで、H<sub>2</sub>OがSOG膜24から外部に拡散される。図6において、矢印はH<sub>2</sub>Oがベーク過程でSOG膜24の外部に拡散される様子を模式的に示している。H<sub>2</sub>Oは、SOG膜24の下部に形成された第1絶縁膜22の他、素子の内部にも拡散される。このようにSOG膜24からH<sub>2</sub>Oが外部に拡散されるのは、SOG膜24をベークすることにより、SOG膜24内のシラノール基(SiOH)が重合されるからである。

30

#### 【0039】

H<sub>2</sub>Oは、シリコン膜と酸化膜の界面に形成されたトラップを修復して該界面のトラップ密度を減少させる作用を奏することが知られている。この作用は、1995年にIEEEにおいて“High Quality SiO<sub>2</sub>/Si Interfaces of Poly-Crystalline Silicon Thin Film Transistors by Annealing in Wet Atmosphere”という題目の論文に発表されたことがある。H<sub>2</sub>Oの拡散によりシリコン膜と酸化膜の界面に形成されたトラップ密度が低くなり、トランジスタのスレショルド電圧が低くなる。また、シリコン膜と酸化膜の界面での漏れ電流が小さくなり、キャリヤの移動度が高くなつてデータの処理が速くなる。

40

#### 【0040】

一方、第2絶縁膜24で使用されるSOG膜の良好な厚さ均一性を得るために、1回のコーティングでは充分でない。そこで、SOG膜を平坦化する前に、再びSOG膜をコーティングして一定温度でベークしても良い。即ち、SOGコーティング/ベーキング/SOGコーティング/ベーキング・・・のようにSOGコーティング及びベーキング工程を2～3回繰り返すことが望ましい。勿論SOG膜の厚さの均一性及びストレスに対する安定性が優れていれば、1回のコーティング及びベーク工程でSOG膜(第2絶縁膜)の形成工程を終えて次の工

50

程に進んでも良い。

**【0041】**

図7に示す工程では、ベーク工程を経た第2絶縁膜24の表面を平坦化する。この平坦化工程は、第1絶縁膜22の表面が現れるまで第2絶縁膜24をエッチバックすることにより行われる。このエッチバック工程において、ゲート電極16、ソース電極20a及びドレイン電極20bその他の段差を成すパターン間に第2絶縁膜が充填されることにより全体的に平坦化が行われる。

**【0042】**

次いで、平坦化工程を経た第2絶縁膜24と第1絶縁膜22の全面に、例えば窒化膜または酸化膜と窒化膜とを二重に蒸着して第3絶縁膜26を形成する。この第3絶縁膜26の厚さは、ソース電極20a及びドレイン電極20bと、後続工程において第3絶縁膜26上に形成される画素電極との間の寄生キャパシタンスにより決定されるが、一般的には、3000～5000程度である。以上の第1乃至第3絶縁膜は、全てTFTを保護するパッシベーション膜として作用する。特に、第3絶縁膜26は、後続工程で外部と素子との間でH<sub>2</sub>Oが移動することを抑制する役割をする。

10

**【0043】**

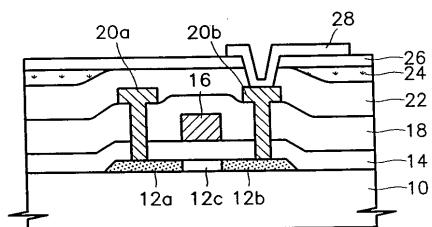

図8に示す工程では、先ず、写真蝕刻工程を使用して第1乃至第3絶縁膜を異方性蝕刻してドレイン電極20bを部分的に露出させるコンタクトホールを形成する。次いで、コンタクトホールが形成された結果物上に透明導電膜、例えばインジウム錫酸化膜(ITO)を350～1500程度の厚さで形成する。次いで、このITO膜をパタニングすることにより、ドレイン電極20bと連結された画素電極28を形成する。

20

**【0044】**

次いで、画素電極28が形成された結果物を150～250の低温でアニーリングする。このアニーリング工程により、上記のSOG膜のベーク工程で膜内に流入した水素が膜内部で再配列されながら安定的なSi-H、Si-OHボンディングが形成され、SOG膜のベーク工程でSOG膜内に形成されたストレスが緩和される。この2回目の熱処理工程は、第3絶縁膜26を形成する直前に行うこともできる。

**【0045】**

この実施の形態によれば、1次熱処理工程(即ちSOG膜のベーク工程)と2次熱処理工程(即ち画素電極形成後のアニーリング工程)の2回の熱処理工程を経るため、パッシベーション膜として一般的なCVD酸化膜を使用する従来の方法に比べてTFTの移動度の増加及びスレショルド電圧の減少等の特性向上が成される。

30

**【0046】**

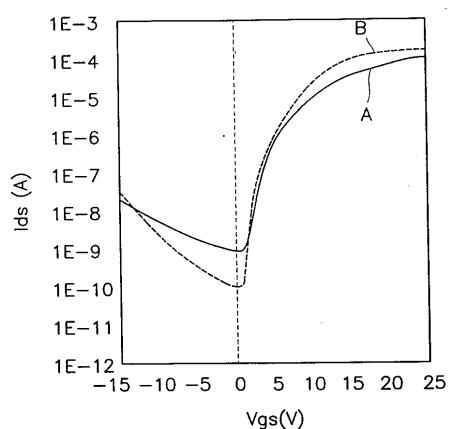

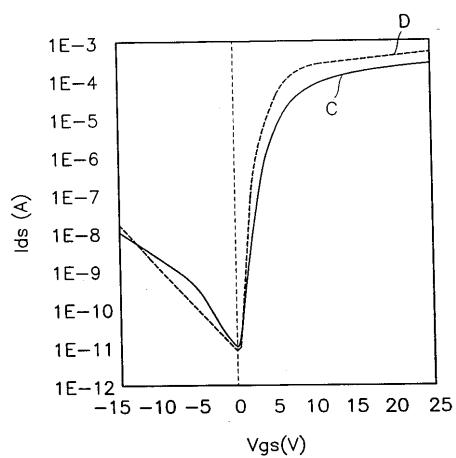

このような効果は、図9及び図10から容易に理解される。図9及び図10は、パッシベーション膜として、PECVD酸化膜、SOG膜を使用した場合のゲート電圧に対するソース／ドレイン電流を示したグラフである。

**【0047】**

図9及び図10において、横軸はゲート電極に印加された電圧Vgsを示し、縦軸はTFTのソース及びドレイン間に流れる電流Idsを示している。なお、ドレインとソース間の電圧Vdsは10Vである。符号Aはパッシベーション膜としてPECVD酸化膜を使用した場合、B及びCはSOG膜コーティング／1次熱処理した場合、DはSOG膜コーティング／1次熱処理／2次熱処理した場合の結果を示す。

40

**【0048】**

2つのグラフを比較すると、パッシベーション膜としてSOG膜を使用する場合BがPECVD酸化膜として使用する場合Aより、またSOG膜形成後に2回の熱処理をした場合Dが1回の熱処理をした場合Cより、同一のゲート電圧においてソースとドレイン間に大きな電流が流れることがわかる。すなわち、上記の実施の形態に基づいてパッシベーション膜としてSOG膜を使用して適切な熱処理を行うと、一般的なCVD酸化膜を使用する場合よりも漏れ電流が相当に小さくなることがわかる。

**【0049】**

50

上記の実施の形態に係る薄膜トランジスタ液晶表示装置の製造方法によれば、パッシベーション膜として多量の水分及び水素を含んでいるSOG膜を使用することによりTFTの特性を向上させることができる。このような効果は高温と低温の2回の熱処理工程により達成される。即ち、1次熱処理工程（SOG膜のベーク工程）でSOG膜に含まれていた水分及び水素分子がTFTのチャンネル部位に流入し、グレーン境界内部のトラップを修復する。また、画素電極形成の前又は後の2次熱処理工程では、流入したその水素分子が内部で再配列されながら膜質を安定化し、1次熱処理工程（ベーク工程）時に発生したSOG膜のストレスを緩和させる役割をする。

#### 【0050】

その結果、一定温度と圧力の水蒸気を用いてシリコン膜と酸化膜との界面に水分子を浸透させ、その界面に形成されたトラップの密度を減少させようとした従来の方法に比べ、上記の実施の形態によれば、TFTのスレショルド電圧を低くする反面、キャリヤの移動度を増加させて漏れ電流を減少させる。

10

#### 【0051】

また、このSOG膜は、狭いスペースを含む結果物上で優れた平坦性を有するという特徴がある。従って、パッシベーション膜としてSOG膜を使用すれば、シリコン膜と酸化膜との界面のトラップの修復工程と共にパッシベーション膜の形成及び平坦化工程を実行することができるため、製造工程を効率化することができる。

#### 【0052】

また、SOG膜を使用すれば、水蒸気を形成するための付加的な設備も不要になるため、経済性、生産性の点でも利点がある。

20

#### 【0053】

本発明は、上記の実施の形態に限定されず、本発明の技術的思想の範囲内で様々な変形が可能である。

#### 【0054】

##### 【発明の効果】

本発明に拠れば、水分を多量に含有する絶縁膜を用いてパッシベーション膜を形成することにより、キャリヤの移動度を増加させて漏れ電流を減少させることができる。

#### 【0055】

##### 【図面の簡単な説明】

30

【図1】本発明の好適な実施の形態に係る薄膜トランジスタ液晶表示装置の製造方法を示す断面図である。

【図2】本発明の好適な実施の形態に係る薄膜トランジスタ液晶表示装置の製造方法を示す断面図である。

【図3】本発明の好適な実施の形態に係る薄膜トランジスタ液晶表示装置の製造方法を示す断面図である。

【図4】本発明の好適な実施の形態に係る薄膜トランジスタ液晶表示装置の製造方法を示す断面図である。

【図5】本発明の好適な実施の形態に係る薄膜トランジスタ液晶表示装置の製造方法を示す断面図である。

40

【図6】本発明の好適な実施の形態に係る薄膜トランジスタ液晶表示装置の製造方法を示す断面図である。

【図7】本発明の好適な実施の形態に係る薄膜トランジスタ液晶表示装置の製造方法を示す断面図である。

【図8】本発明の好適な実施の形態に係る薄膜トランジスタ液晶表示装置の製造方法を示す断面図である。

【図9】薄膜トランジスタのゲート電圧とソース／ドレイン間に流れる電流との関係を示すグラフである。

【図10】薄膜トランジスタのゲート電圧とソース／ドレイン間に流れる電流との関係を示すグラフである。

50

## 【符号の説明】

- 10 光透過性基板

12 半導体膜

12' 半導体膜パターン

12a ソース電極

12b ドレイン電極

12c チャンネル

14 ゲート絶縁膜

16 ゲート電極

18 層間絶縁膜

20a ソース電極

20b ドレイン電極

22 第1絶縁膜

24 第2絶縁膜

26 第3絶縁膜

28 画素電極

- 10

【図1】

【図4】

【図2】

【図5】

【図3】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(51)Int.Cl.

F I

G 0 9 F 9/35 3 0 2

(72)発明者 李柱亨

大韓民国ソウル特別市江南区大峙洞970番地住公アパート311棟1102号

審査官 河口 雅英

(56)参考文献 特開平08-055858(JP,A)

特開平07-078997(JP,A)

特開平06-196702(JP,A)

特開平07-147412(JP,A)

特開平06-250214(JP,A)

特開平07-302912(JP,A)

特開平07-056190(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/786

H01L 21/336

G02F 1/136

G09F 9/35