(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4149634号

(P4149634)

(45) 発行日 平成20年9月10日(2008.9.10)

(24) 登録日 平成20年7月4日(2008.7.4)

(51) Int.Cl.

F 1

|                   |                  |                   |          |

|-------------------|------------------|-------------------|----------|

| <b>H03K 23/00</b> | <b>(2006.01)</b> | <b>H03K 23/00</b> | <b>A</b> |

| <b>H03K 21/00</b> | <b>(2006.01)</b> | <b>H03K 21/00</b> | <b>J</b> |

| <b>H03K 23/66</b> | <b>(2006.01)</b> | <b>H03K 23/66</b> | <b>Z</b> |

請求項の数 1 (全 13 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2000-112792 (P2000-112792)  |

| (22) 出願日  | 平成12年4月14日 (2000.4.14)        |

| (65) 公開番号 | 特開2001-298358 (P2001-298358A) |

| (43) 公開日  | 平成13年10月26日 (2001.10.26)      |

| 審査請求日     | 平成19年2月15日 (2007.2.15)        |

|           |                                                     |

|-----------|-----------------------------------------------------|

| (73) 特許権者 | 000001960<br>シチズンホールディングス株式会社<br>東京都西東京市田無町六丁目1番12号 |

| (74) 代理人  | 100126583<br>弁理士 宮島 明                               |

| (74) 代理人  | 100100871<br>弁理士 土屋 繁                               |

| (72) 発明者  | 矢野 敬和<br>埼玉県所沢市大字下富字武野840番地<br>シチズン時計株式会社技術研究所内     |

| (72) 発明者  | 岩倉 良樹<br>埼玉県所沢市大字下富字武野840番地<br>シチズン時計株式会社技術研究所内     |

最終頁に続く

(54) 【発明の名称】分周回路

## (57) 【特許請求の範囲】

## 【請求項 1】

発振回路から発生される所定の周波数のクロック信号を入力し、これを分周して所定の分周比の信号を出力する分周回路であって、

セット機能またはリセット機能のどちらかを有するフリップフロップ回路を複数段備えると共に前記クロック信号を基に分周する同期式の前段部回路と、

フリップフロップ回路を複数段備えると共に前記前段部回路の結果として出力される分周信号を基に分周する非同期式の後段部回路と、を有し、

所定の調整信号を入力することで、前記セット機能または前記リセット機能を有効にして前記所定の分周比の微調整ができる分周回路において、

前記前段部回路は、前記クロック信号をクロック入力として直接入力することで、クロック入力ゲートの容量を前記発振回路を構成する容量 Cout に繰り込むように接続され、

前記前段部回路は、前記クロック信号の少なくとも 1 / 4 分周までを前記クロック信号を基に分周し、

前記前段部回路は、セット機能を有するフリップフロップ回路とリセット機能を有するフリップフロップ回路とを少なくとも 1 組備え、初段の前記フリップフロップ回路に前記セット機能を備えたとき、他の前記フリップフロップ回路は前記リセット機能を備えたとき、他の前記フリップフロップ回路は前記セット機能を備え、

10

20

前記調整信号は、前記セット機能を有効にするセット信号と、前記リセット機能を有効にするリセット信号と、の2つの信号であり、

前記前段部回路は、前記調整信号である前記2つの信号の組み合わせにより、前記クロック信号の立ち下がりまたは立ち上がりに同期して初段の前記フリップフロップ回路の出力信号の開始タイミングを変化させることを特徴とする分周回路。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は電子時計等に使われる分周回路の構成にかんし、とくに低電力化と分周精度技術の分周回路にかんする。

10

【0002】

【従来の技術】

分周回路は種々の電子機器に使われている。とくに電子時計においては分周回路は中心的な役割を果たしている。

【0003】

現在の電子時計は約32KHzの水晶発振回路から発生されるクロックパルスを基にして1秒になるまで分周して秒単位で時刻表示を行う。

分周を行なうのは分周回路であり、分周回路は分周以外に製造ばらつきによる周波数ずれを吸収するための微調整も行なえるようになっている。

【0004】

20

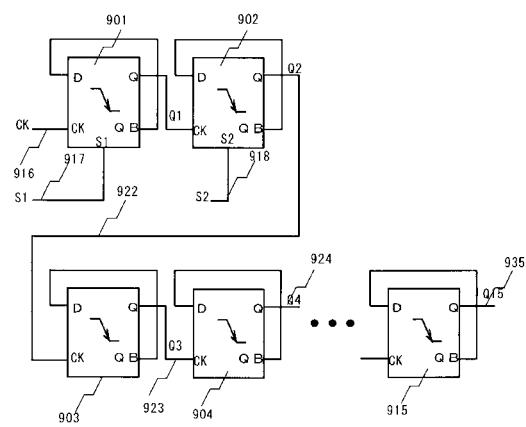

図9の回路図は、従来技術のバイナリカウンタ方式の分周回路を示しており、第1番目のデータ型フリップフロップ回路(DFF回路)901から第15番目のDFF回路915から構成されている。

【0005】

図9では、DFF回路901はS1信号917を入力するためのセット付きのDFF回路であり、水晶発振器から発生された32KHzの周期であるCK信号916の立ち下がりに同期して1/2分周されたQ1信号921を出力する回路である。

【0006】

DFF回路902はS2信号918を入力するためのセット付きのDFF回路であり、DFF回路901から発生されたQ1信号921の立ち下がりに同期して1/2分周されたQ2信号922を出力する回路である。

30

【0007】

DFF回路903はデータ型フリップフロップ回路であり、DFF回路902から発生されたQ2信号922の立ち下がりに同期して1/2分周されたQ3信号923を出力する回路であり、DFF回路904はデータ型フリップフロップ回路であり、DFF回路903から発生されたQ3信号923の立ち下がりに同期して1/2分周されたQ4信号924を出力する回路である。

【0008】

以下同様に分周されてDFF回路915は約1HzのQ15信号935を出力する。

【0009】

40

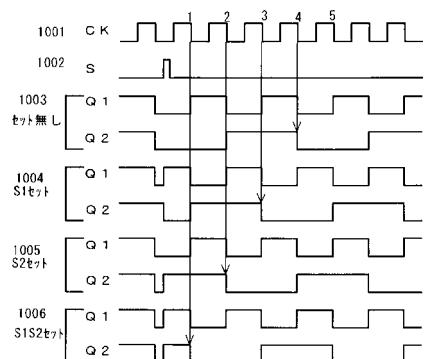

図10は、DFF回路901とDFF回路902のセットすることによる分周精度の微調整について説明するタイミングチャートを示す波形図である。

【0010】

図10において、CKタイミングチャート1001はCK信号916のタイミングを示し、Sタイミングチャート1002はS1信号917とS2信号918のタイミングを示す。

【0011】

セット無しタイミングチャート1003はセットが無い場合のQ1信号921とQ2信号922のタイミングを示し、S1セットタイミングチャート1004はS1信号917がSタイミングチャート1002に従ってDFF回路901をセットした場合のQ1信号9

50

21とQ2信号922のタイミングを示す。

**【0012】**

S2セットタイミングチャート1005は、S2信号がSタイミングチャート1002に従ってDFF回路902をセットした場合のQ1信号921とQ2信号922のタイミングを示し、S1-2セットタイミングチャート1006はセットがS1信号917およびS2信号918がSタイミングチャート1002に従ってDFF回路901とDFF回路902に発生した場合のQ1信号921とQ2信号922のタイミングを示す。

**【0013】**

セット無しタイミングチャート1003の場合、Sタイミングチャート1002で示されるセットのタイミングを基準にQ1信号921の最初の立ち下がりはCK信号916の2番目の立ち下がりに同期して立ち下がり、Q2信号922の最初の立ち下がりは、CK信号916の4番目の立ち下がりに同期して立ち下がる。

10

**【0014】**

さらに、S1セットタイミングチャート1004の場合、Sタイミングチャート1002で示されるセットのタイミングを基準にQ1信号921の最初の立ち下がりはCK信号916の1番目の立ち下がりに同期して立ち下がり、Q2信号922の最初の立ち下がりはCK信号916の3番目の立ち下がりに同期して立ち下がる。

**【0015】**

また、S2セットタイミングチャート1005の場合、Sタイミングチャート1002で示されるセットのタイミングを基準にQ1信号921の最初の立ち下がりは、CK信号916の2番目の立ち下がりに同期して立ち下がり、Q2信号922の最初の立ち下がりはCK信号916の2番目の立ち下がりに同期して立ち下がる。

20

**【0016】**

S1-2セットタイミングチャート1006の場合、Sタイミングチャート1002で示されるセットのタイミングを基準にQ1信号921の最初の立ち下がりはCK信号916の1番目の立ち下がりに同期して立ち下がり、Q2信号922の最初の立ち下がりはCK信号916の1番目の立ち下がりに同期して立ち下がる。

**【0017】**

すなわち、S1およびS2を入力してQ2信号922のタイミングを変化させることによって最終的に発生されるQ15信号935の周期を微調整できる。

30

**【0018】**

**【発明が解決しようとする課題】**

バイナリカウンタ型分周回路のみを用いた図9に示すような電子時計の分周回路では、高い周波数で駆動するゲートが多いため低電力化に限界がある。

**【0019】**

**【発明の目的】**

本発明は上記課題を解決するために分周回路の形態を工夫し、低電力で分周に対する微調整を行なうことができる分周回路を備えた分周回路を提案することを目的とする。

**【0020】**

**【課題を解決するための手段】**

40

本発明は上記目的を達成するために、発振回路から発生される所定の周波数のクロック信号を入力し、これを分周して所定の分周比の信号を出力する分周回路であって、

セット機能またはリセット機能のどちらかを有するフリップフロップ回路を複数段備えると共に前記クロック信号を基に分周する同期式の前段部回路と、

フリップフロップ回路を複数段備えると共に前記前段部回路の結果として出力される分周信号を基に分周する非同期式の後段部回路と、を有し、

所定の調整信号を入力することで、前記セット機能または前記リセット機能を有効にして前記所定の分周比の微調整ができる分周回路において、

前記前段部回路は、前記クロック信号をクロック入力として直接入力することで、クロック入力ゲートの容量を前記発振回路を構成する容量Countに繰り込むように接続され

50

前記前段部回路は、前記クロック信号の少なくとも1/4分周までを前記クロック信号を基に分周し、

前記前段部回路は、セット機能を有するフリップフロップ回路とリセット機能を有するフリップフロップ回路とを少なくとも1組備え、初段の前記フリップフロップ回路に前記セット機能を備えたとき、他の前記フリップフロップ回路は前記リセット機能を備え、初段の前記フリップフロップ回路に前記リセット機能を備えたとき、他の前記フリップフロップ回路は前記セット機能を備え、

前記調整信号は、前記セット機能を有効にするセット信号と、前記リセット機能を有効にするリセット信号と、の2つの信号であり、

前記前段部回路は、前記調整信号である前記2つの信号の組み合わせにより、前記クロック信号の立ち下がりまたは立ち上がりに同期して初段の前記フリップフロップ回路の出力信号の開始タイミングを変化させることとする。

#### 【0021】

##### 〔作用〕

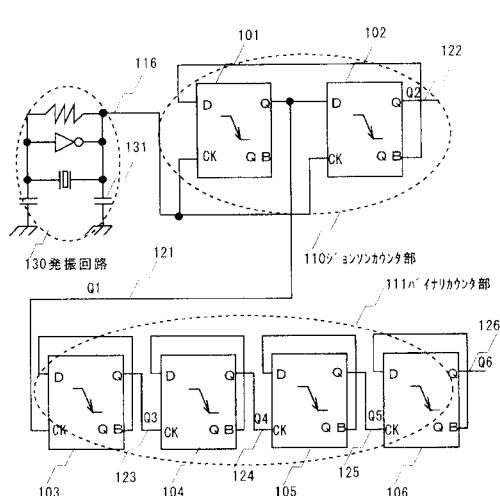

通常、時計回路における分周回路の前段は図1に示すとおり発振回路である。したがって、分周回路のクロック入力は発振回路130中のインバータ回路の消費電力となる。

#### 【0022】

ところで、元々発信のためにはCount131が必要であり、1部分を分周回路のクロック入力ゲートの容量をCountに繰り込んでも発振回路130の消費電力は変わらない。

#### 【0023】

そこで、分周回路の発振回路130からのCK信号116によって駆動されるクロックゲート以外のゲート駆動周波数を下げることのできるジョンソンカウンタ等の同期式カウンタ型分周回路を用いることによって低電力化できる。

#### 【0024】

上記効果は高い周波数においてより効果的である。しかしながら、ジョンソンカウンタ型回路は同分周機能に於いてバイナリカウンタ型分周回路に比べ多大な回路面積を必要とし、さらにCount131の1部を補うのにも限界があるのでバイナリカウンタ型分周回路とジョンソンカウンタ型分周回路の段数割合は適度なバランスをとる必要がある。

#### 【0025】

また、分周回路のもうひとつの役割である微調整機能についてはジョンソンカウンタ部にセット付きおよびリセット付きDFF回路を用いることによって簡単に実現できる。

#### 【0026】

##### 〔発明の実施の形態〕

##### (参考例：図1および図2)

以下図面を用いて本発明の前提となる分周回路の構成を説明する。図1は、その分周回路の構成を示す図面である。分周回路はジョンソンカウンタ部110およびバイナリカウンタ部111の2つの部分から形成されている。

#### 【0027】

ジョンソンカウンタ部分110は、一般に良く知られたDFF回路101およびDFF回路102の2つのDFF回路から構成されるジョンソンカウンタ回路であり、水晶発振回路130から発生された約32KHzのクロック信号であるCK信号916の立ち下がりに同期して1/4分周されたQ1信号121およびQ2信号122を出力する回路である。

#### 【0028】

バイナリカウンタ部分111は一般に良く知られたDFF回路103、DFF回路104、DFF回路105およびDFF回路106の4つのDFF回路から構成されるバイナリカウンタ回路である。

#### 【0029】

DFF回路103はDFF回路101から発生されたQ1信号121の立ち下がりに同期

10

20

30

40

50

して 1 / 2 分周された Q 3 信号 1 2 3 を出力する回路であり、D F F 回路 1 0 4 は D F F 回路 1 0 3 から発生された Q 3 信号 1 2 3 の立ち下がりに同期して 1 / 2 分周された Q 4 信号 1 2 4 を出力する回路である。

**【 0 0 3 0 】**

D F F 回路 1 0 5 と D F F 回路 1 0 6 に関して同様にして Q 6 信号 1 2 6 を出力し、最終的には 1 / 6 4 分周する分周回路である。

**【 0 0 3 1 】**

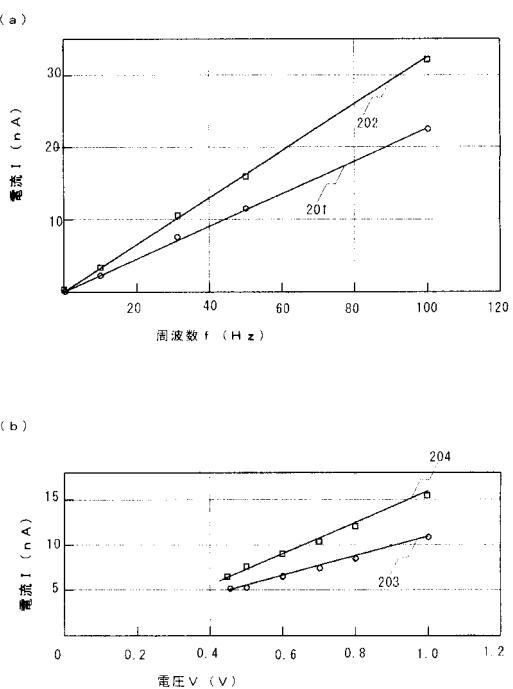

図 2 は、所定の C - M O S プロセスによって作製された 1 / 6 4 分周を行うための前述の本発明による分周回路と従来技術におけるバイナリカウンタ型分周回路（図示せず）の電流測定結果を示す。

10

図 2 において、四角で示されるポイントは、従来の技術におけるバイナリカウンタ型分周回路の電流測定結果を示し、丸で示されるポイントは本発明による分周回路の電流測定結果を示す。

**【 0 0 3 2 】**

図 2 ( a ) は一定電圧 ( 0 . 7 V ) 時の周波数依存性を示す。いずれの分周回路の特性もほぼ周波数に比例するが、従来の技術におけるバイナリカウンタ型分周回路 2 0 2 より本発明による分周回路 2 0 1 の方が低い電流である。

**【 0 0 3 3 】**

図 2 ( b ) は一定周波数 ( 3 2 K H z ) 時の電圧依存性を示す。いずれの分周回路の特性もほぼ電圧に比例するが、従来の技術におけるバイナリカウンタ式分周回路 2 0 4 より本発明による分周回路 2 0 3 の方が低い電流である。

20

**【 0 0 3 4 】**

これは従来のバイナリカウンタ型分周回路においては 1 / 2 分周された Q 1 信号を 2 段目の D F F 回路に入力するのに対して、ジョンソンカウンタ部 1 1 0 においては Q 1 信号 1 2 1 および Q 2 信号 1 2 2 は 1 / 4 分周された信号であり比較的低周波で駆動されるためである。

**【 0 0 3 5 】**

なお、ジョンソンカウンタ部 1 1 0 への C K 1 1 6 による駆動電力はその前段の発振回路 1 3 1 のインバータ電流として消費されるが、容量 C o u t 1 3 1 に組み込まれるので増加分とはならない。

30

**【 0 0 3 6 】**

このようにして低電力の分周回路を作製できる。もちろん、ジョンソンカウンタ系 1 1 0 の段数を多くしてさらなる低電力化をすることは可能であるが、容量 C o u t 1 3 1 の最適値よりも大となるゲート容量となることはトータル電力と安定性に於いては好ましくない。

**【 0 0 3 7 】**

また、バイナリカウンタ型分周回路は n 個の D F F 回路に対して 2 の n 乗分の 1 の分周機能を備えるのに対して、ジョンソンカウンタ型分周回路は 2 n 分の 1 の分周機能しか備えないのでその分面積を要する。

このため、バイナリカウンタ型分周回路とうまくバランスをとった回路にすることが望ましい。とくにジョンソン型カウンタ部 1 1 0 が D F F 回路 2 段で構成された場合はバイナリカウンタ型分周回路と同数の D F F 回路となる。

40

**【 0 0 3 8 】**

今回の例はジョンソンカウンタ型回路にて説明したが、同期式回路であれば同様の効果はある。

**【 0 0 3 9 】**

( 第 1 の実施形態 : 図 3 および図 4 )

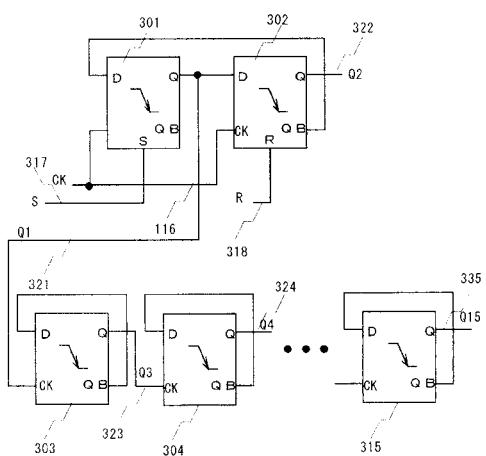

つぎに第 1 の実施形態における分周回路の構成を図 3 を用いて説明する。参考例で示した低電力分周回路に微調整機能を付加した回路を説明する。

**【 0 0 4 0 】**

図3は本発明の微調整機能付きの低電力の分周回路を示しており、第1番目のDFF回路301から第15番目のDFF回路315から構成されている。

【0041】

図3において、DFF回路301はS信号317を入力するためのセット付きのDFF回路であり、水晶発振器から発生されたクロック信号であるCK信号916の立ち下がりに同期して1/4分周されたQ1信号321を出力する回路である。

【0042】

DFF回路302は、R信号318を入力するためのリセット付きのDFF回路であり、CK信号916の立ち下がりに同期して1/4分周されたQ2信号322を出力する回路である。

10

【0043】

DFF回路303はDFF回路301から発生されたQ1信号321の立ち下がりに同期して1/2分周されたQ3信号323を出力する回路であり、DFF回路304はDFF回路303から発生されたQ3信号323の立ち下がりに同期して1/2分周されたQ4信号324を出力する回路である。

【0044】

以下、同じようにしてDFF回路315は約1HzのQ15信号335を出力する。

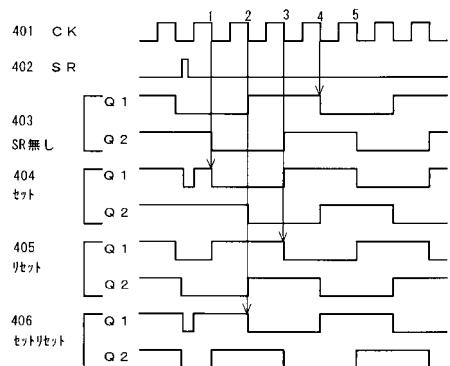

【0045】

図4にはDFF回路301をセットおよびDFF回路302をリセットすることによる分周精度の微調整について説明するタイミングチャートを示す。

20

【0046】

図中、CKタイミングチャート401はCK信号916のタイミングを示し、SRタイミングチャート402は、DFF回路301のセットおよびDFF回路302のリセット信号のタイミングを示す。

【0047】

SR無しタイミングチャート403は、セットが無い場合のQ1信号321とQ2信号322のタイミングを示し、セットタイミングチャート404はS信号317がSRタイミングチャート402にしたがってDFF回路301をセットした場合のQ1信号321とQ2信号322のタイミングを示す。

30

【0048】

リセットタイミングチャート405は、R信号318がSRタイミングチャート402にしたがってDFF回路302をリセットした場合のQ1信号321とQ2信号322のタイミングを示し、SRセットタイミングチャート406は、SRタイミングチャート402にしたがってS信号317がDFF回路301をセットし、R信号318がDFF回路302に発生した場合のQ1信号321とQ2信号322のタイミングを示す。

【0049】

SR無しタイミングチャート403の場合、SRタイミングチャート402で示されるセットのタイミングを基準にQ1信号321の最初の立ち下がりはCK信号916の4番目の立ち下がりに同期して立ち下がる。

40

【0050】

セットタイミングチャート404の場合、SRタイミングチャート402で示されるセットのタイミングを基準にQ1信号321の最初の立ち下がりはCK信号916の1番目の立ち下がりに同期して立ち下がる。

【0051】

リセットタイミングチャート405の場合、SRタイミングチャート402で示されるリセットのタイミングを基準にQ1信号321の最初の立ち下がりは、CK信号916の3番目の立ち下がりに同期して立ち下がる。

【0052】

セットリセットタイミングチャート406の場合、SRタイミングチャート402で示されるセットリセットのタイミングを基準にQ1信号321の最初の立ち下がりはCK信号

50

916の2番目の立ち下がりに同期して立ち下がる。

**【0053】**

すなわち、S信号317およびR信号318を入力してQ1信号321のタイミングを変化させることによって最終的に発生されるQ15信号335の周期を微調整できる。

**【0054】**

また、今までの回路と置き換える場合はセットおよびリセット入力をデコードすることによってつなぎかえることによって、簡単に置き換えることが可能である。

**【0055】**

(第2の実施形態：図5および図6）

つぎに第2の実施形態における分周回路の構成を図5を用いて説明する。第1の実施の形態で示した微調整機能付き低電力分周回路が立ち上がり同期の場合の回路を説明する。10

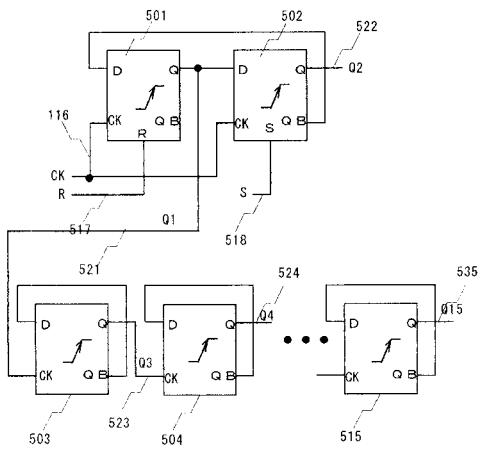

**【0056】**

図5は本発明の微調整機能付きの低電力の分周回路を示しており、第1番目のDFF回路501から第15番目のDFF回路515から構成されている。

**【0057】**

図5において、DFF回路501はR信号517を入力するためのリセット付きのDFF回路であり、水晶発振器から発生されたクロックパルスであるCK信号916の立ち上がりに同期して1/4分周されたQ1信号521を出力する回路である。20

**【0058】**

DFF回路502はS信号518を入力するためのセット付きのDFF回路であり、CK信号916の立ち上がりに同期して1/4分周されたQ2信号522を出力する回路である。20

**【0059】**

DFF回路503はDFF回路501から発生されたQ1信号521の立ち上がりに同期して1/2分周されたQ3信号523を出力する回路であり、DFF回路504はDFF回路503から発生されたQ3信号523の立ち上がりに同期して1/2分周されたQ4信号524を出力する回路である。

**【0060】**

以下、同じようにしてDFF回路515は約1HzのQ15信号535を出力する。

**【0061】**

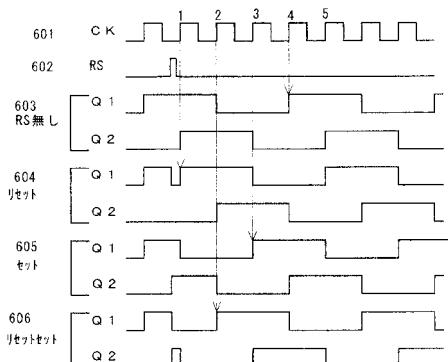

図6にはDFF回路501をリセットおよびDFF回路502をセットすることによる分周精度の微調整について説明するタイミングチャートを示す。30

**【0062】**

図6において、CKタイミングチャート601はCK信号916のタイミングを示し、RSタイミングチャート602はDFF回路501のリセットとDFF回路502のセット信号のタイミングを示す。

**【0063】**

RS無しタイミングチャート603は、セットが無い場合のQ1信号521とQ2信号522のタイミングを示し、リセットタイミングチャート604はR信号517がSRタイミングチャート602にしたがってDFF回路901をリセットした場合のQ1信号521とQ2信号522のタイミングを示す。40

**【0064】**

セットタイミングチャート605は、S信号518がSRタイミングチャート602にしたがってDFF回路502をセットした場合のQ1信号521とQ2信号522のタイミングを示し、RSセットタイミングチャート606はR信号517が、SRタイミングチャート602にしたがってDFF回路501をリセットし、S信号518がSRタイミングチャート602にしたがってDFF回路502をセットした場合のQ1信号521およびQ2信号522のタイミングを示す。

**【0065】**

RS無しタイミングチャート603の場合、RSタイミングチャート602で示されるセ50

ットのタイミングを基準に Q 1 信号 5 2 1 の最初の立ち上がりは C K 信号 9 1 6 の 4 番目の立ち上がりに同期して立ち上がる。

【 0 0 6 6 】

セットタイミングチャート 6 0 4 の場合、 R S タイミングチャート 6 0 2 で示されるセットのタイミングを基準に Q 1 信号 5 2 1 の最初の立ち上がりは C K 信号 9 1 6 の 1 番目の立ち上がりに同期して立ち上がる。

【 0 0 6 7 】

リセットタイミングチャート 6 0 5 の場合、 R S タイミングチャート 6 0 2 にて示されるリセットのタイミングを基準に Q 1 信号 5 2 1 の最初の立ち上がりは C K 信号 9 1 6 の 3 番目の立ち上がりに同期して立ち上がる。 10

【 0 0 6 8 】

リセットセットタイミングチャート 6 0 6 の場合、 R S タイミングチャート 6 0 2 で示されるリセットセットのタイミングを基準に Q 1 信号 5 2 1 の最初の立ち上がりは C K 信号 9 1 6 の 2 番目の立ち上がりに同期して立ち上がる。

【 0 0 6 9 】

すなわち、 R 信号 5 1 7 および S 信号 5 1 8 を入力して Q 1 信号 5 2 1 のタイミングを変化させることによって最終的に発生される Q 1 5 信号 5 3 5 の周期を微調整できる。

【 0 0 7 0 】

また、今までの回路と置き換える場合はセットおよびリセット入力をデコードすることなどによってつなぎかえることにより、簡単に置き換えることが可能である。 20

【 0 0 7 1 】

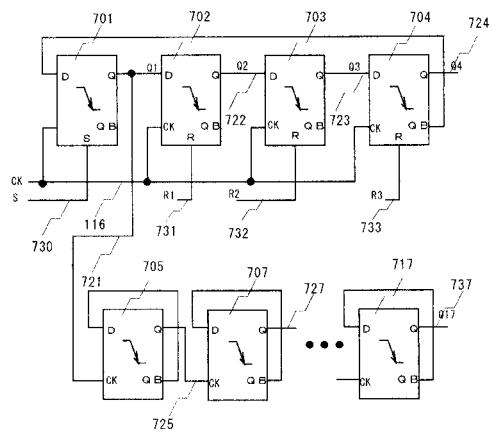

( 第 3 の実施形態 : 図 7 および図 8 )

つぎに第 3 の実施形態における分周回路の構成を図 7 を用いて説明する。第 1 の実施形態で示した微調整機能付き低電力の分周回路のジョンソンカウンタ部分の D F F 回路段数が 4 段の場合の回路を説明する。

【 0 0 7 2 】

図 7 は本発明の微調整機能付きの低電力の分周回路を示しており、第 1 番目の D F F 回路 7 0 1 から第 1 7 番目の D F F 回路 7 1 7 から構成されている。

【 0 0 7 3 】

図 7 において、 D F F 回路 7 0 1 は S 信号 7 3 0 を入力するためのセット付きの D F F 回路であり、水晶発振器から発生されたクロックパルスである C K 信号 9 1 6 の立ち下がりに同期して 1 / 8 分周された Q 1 信号 7 2 1 を出力する回路である。 30

【 0 0 7 4 】

D F F 回路 7 0 2 は R 1 信号 7 3 1 を入力するためのリセット付きの D F F 回路であり、 C K 信号 9 1 6 の立ち下がりに同期して 1 / 8 分周された Q 1 信号 7 2 1 を出力する回路である。

【 0 0 7 5 】

以下同様に、 D F F 回路 7 0 3 は R 2 信号 7 3 2 を入力するためのリセット付きの D F F 回路であり、 C K 信号 9 1 6 の立ち下がりに同期して 1 / 8 分周された Q 3 信号 7 2 3 を出力する回路であり、 D F F 回路 7 0 4 は R 3 信号 7 3 3 を入力するためのリセット付きの D F F 回路であり、 C K 信号 9 1 6 の立ち下がりに同期して 1 / 8 分周された Q 4 信号 7 2 4 を出力する回路である。 40

【 0 0 7 6 】

D F F 回路 7 0 5 は D F F 回路 7 0 1 から発生された Q 1 信号 7 2 1 の立ち下がりに同期して 1 / 2 分周された Q 5 信号 7 2 5 を出力する回路であり、 D F F 回路 7 0 6 は D F F 回路 7 0 5 から発生された Q 5 信号 7 2 5 の立ち下がりに同期して 1 / 2 分周された Q 6 信号 7 2 6 を出力する回路である。

【 0 0 7 7 】

以下、同じようにして D F F 回路 7 1 7 は約 1 H z の Q 1 7 信号 7 3 7 を出力する。

【 0 0 7 8 】

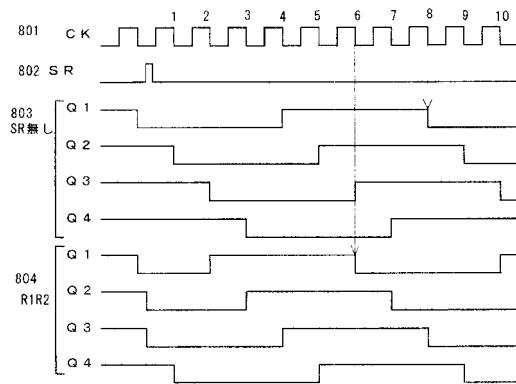

図8にはDFF回路701をセットとDFF回路702、DFF回路703とDFF回路704をリセットすることによる分周精度の微調整について説明するタイミングチャートを示す。

#### 【0079】

図8において、CKタイミングチャート801はCK信号916のタイミングを示し、SRタイミングチャート802はDFF回路701のセットとDFF回路702、DFF回路703およびDFF回路704のリセット信号のタイミングを示す。

#### 【0080】

SR無しタイミングチャート803はセットが無い場合のQ1信号721、Q2信号722、Q3信号723およびQ4信号724のタイミングを示す。

10

R1R2タイミングチャート804はSRタイミングチャート802にしたがってR1信号731がDFF回路702をリセットし、R2信号732がDFF回路703をリセット場合のQ1信号721、Q2信号722、Q3信号723およびQ4信号724のタイミングを示す。

#### 【0081】

SR無しタイミングチャート803の場合、SRタイミングチャート802で示されるセットのタイミングを基準にQ1信号821の最初の立ち下がりはCK信号916の8番目の立ち下がりに同期して立ち下がる。

#### 【0082】

R1R2リセットタイミングチャート804の場合、SRタイミングチャート802で示されるセットのタイミングを基準にQ1信号721の最初の立ち下がりはCK信号916の6番目の立ち下がりに同期して立ち下がる。

20

#### 【0083】

以下、1つのセットと3つのリセットを組み合わせることによってSRタイミングチャート802で示されるセットのタイミングを基準にQ1信号721の最初の立ち下がりをCK信号916の1番目から8番目の立ち下がりに同期して立ち下げることが可能である。

#### 【0084】

すなわち、S信号730、R1信号731、R2信号732、およびR3信号733を入力してQ1信号721のタイミングを変化させることによって最終的に発生されるQ15信号735の周期を微調整できる。

30

#### 【0085】

もちろん、ジョンソンカウンタ部分のリセット付きDFF回路を増やしても微調整が可能である。

また、今までの回路と置き換える場合はセットおよびリセット入力をデコードすることなどによってつなぎかえることにより、簡単に置き換えることが可能である。

#### 【0086】

#### 【発明の効果】

以上の説明からあきらかなように、本発明の分周回路によって電子時計などの分周回路を用いる電子機器を、精度を維持しながら低電力で分周することが可能となる。

#### 【図面の簡単な説明】

40

【図1】 参考例として分周回路の発振回路を含んだ構成を示す回路図である。

【図2】 図1の例における分周回路の電流測定結果を示すグラフである。

【図3】 本発明の実施の形態における微調整機能付き分周回路の構成を示す回路図である。

【図4】 本発明の実施形態における分周回路によるタイミングチャートを示す図面である。

【図5】 本発明の実施形態における分周回路による立ち上がり同期時を示す回路図である。

【図6】 本発明の実施形態における分周回路によるタイミングチャートを示す図面である。

50

【図7】 本発明の実施形態における分周回路による立ち上がり同期時を示す回路図である。

【図8】 本発明の実施形態における分周回路による1/8分周を基にしたタイミングチャートを示す図面である。

【図9】 従来技術における分周回路を示す回路図である。

【図10】 従来技術における分周回路によるタイミングチャートを示す図面である。

【符号の説明】

110：ジョンソンカウンタ部

111：バイナリカウンタ部

116：C K 信号

131：容量 C out

201：本発明による回路の電流 - 周波数特性

203：本発明による回路の電流 - 電圧特性

321：Q1 信号

404：セットタイミングチャート

604：リセットタイミングチャート

804：R2 R3 タイミングチャート

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(72)発明者 大高 幸夫

埼玉県所沢市大字下富字武野 840番地 シチズン時計株式会社技術研究所内

(72)発明者 相原 克好

埼玉県所沢市大字下富字武野 840番地 シチズン時計株式会社技術研究所内

(72)発明者 小峰 伸一

埼玉県所沢市大字下富字武野 840番地 シチズン時計株式会社技術研究所内

審査官 石田 勝

(56)参考文献 特開平04-299614(JP,A)

特開平02-013127(JP,A)

特開平11-046136(JP,A)

特開昭54-8451(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K 23/00-29/06

H03K 21/00-21/40