RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(A n'utiliser que pour les

commandes de reproduction).

**2 460 526**

A1

**DEMANDE

DE BREVET D'INVENTION**

(21) **N° 79 17303**

(54) Procédé de mesure du temps d'accès d'adresse de mémoires mettant en œuvre la technique de recirculation des données, et testeur en résultant.

(51) Classification internationale (Int. Cl. 3). G 11 C 29/00, 8/00.

(22) Date de dépôt..... 29 juin 1979, à 14 h 57 mn.

(33) (32) (31) Priorité revendiquée :

(41) Date de la mise à la disposition du public de la demande ..... B.O.P.I. — « Listes » n° 4 du 23-1-1981.

(71) Déposant : Société dite : COMPAGNIE IBM FRANCE, résidant en France.

(72) Invention de : Jacky Jaccotton et Bernard Vanoudheusden.

(73) Titulaire : *Idem* (71)

(74) Mandataire : Daniel Klein, Département de Propriété Industrielle, Compagnie IBM France,

06610 La Gaude.

### Domaine Technique

La présente invention concerne le test des mémoires. Elle concerne plus particulièrement un procédé de mesure du temps d'accès d'adresse de mémoires (RAM ou ROS), mettant en oeuvre la technique de recirculation des données et son application à un testeur.

### Estat de la technique

Le temps d'accès d'adresse (AAT ou address access time selon la terminologie anglo-saxonne) est une mesure importante de la qualité des mémoires, car il mesure la rapidité de réponse de la mémoire. De façon classique, ce temps est mesuré de la façon suivante: admettons que le contenu de la mémoire à tester correspondant à une adresse  $A_0$  soit disponible sur les lignes de sorties de données, au temps  $t=0$ , l'adresse est changée, l'adresse  $A_1$  est introduite dans la mémoire. L'AAT est le temps mis par les nouvelles données pour apparaître sur les lignes de sortie.

Il est reconnu que les mesures de l'AAT nécessitent la mise en forme et la calibration de signaux très rapides (temps inférieur à 2 ns), des temps de cycle de 5 à 100ns, des temps de décalage entre les niveaux des lignes d'adresse inférieurs à 0,1ns, et des résolutions avec des incrémentations inférieures à 0,1ns. La réalisation de circuits aussi performants, notamment de générateurs de mots hautes fréquences (>100 MHz) conduit à des testeurs sophistiqués et coûteux.

### Exposé de l'invention

Un premier objet de l'invention est l'application des techniques de recirculation au test des mémoires (RAM ou ROS), pour la mesure de l'AAT.

Encore un autre objet de l'invention est de fournir un

testeur à recirculation, capable d'être chargé manuellement ou automatiquement, simple et économique.

La présente invention concerne donc un procédé de mesure du temps d'accès d'adresse (AAT) par recirculation entre n lignes de sortie et n lignes d'adresse d'une mémoire du genre comportant une ligne de sélection lecture/écriture, une pluralité de lignes de sortie de données, une pluralité de lignes d'entrée de données, et une pluralité de lignes d'adresse, caractérisé en ce qu'il comporte les étapes suivantes:

- mise de la ligne de sélection sur la position écriture,

- chargement dans la mémoire d'une configuration désirée de  $2^n$  mots de n bits correspondant aux  $2^n$  adresses: toutes les adresses sont balayées et à chaque adresse (k) on écrit le mot : [mot (k)],

- mise de la ligne de sélection sur la position lecture,

- connexion de n lignes de sortie d'adresse à n lignes d'adresse par n lignes à retard de délai  $\tau$ ; puisqu'il y a un maximum de  $m = 2^n$  différents mots, il existe un entier  $p \leq m$  tel que

$$k = [\text{mot } (\text{mot } (\dots \text{mot } (k)) \dots)]$$

en fait p mots, de telle sorte que la mémoire oscille avec une fréquence F telle que

$$F = \frac{1}{p(\tau + AAT)}$$

AAT représentant une approximation moyenne des AAT correspondant à toutes les combinaisons des adresses intervenant dans la recirculation,

- mesure de la fréquence F et détermination du paramètre p et,

- . détermination de la valeur de l'AAT par la relation

AAT = 1/pF- $\tau$ .

Elle concerne également un testeur pour la mesure automatique des AAT des mémoires du type comportant une ligne de 5 sélection lecture/écriture, une pluralité de lignes d'entrée et de sortie de données, une pluralité de lignes d'adresse, caractérisé en ce qu'il comporte:

- . des moyens pour charger la mémoire selon une configuration désirée contenue dans une mémoire annexe, afin 10 que pour chaque adresse (k) on écrive un [mot (k)] pendant que la ligne de sélection se trouve en position écriture,

- . des moyens pour connecter n lignes de sortie de données de la mémoire à n lignes d'adresse à travers n lignes à 15 retard de délai  $\tau$ , pour la faire recirculer entre ces adresses pendant que la ligne de sélection se trouve en position lecture, et

- . des moyens de synchronisation de ces opérations associés à des moyens d'initialisation et de blocage des 20 séquences de chargement et de recirculation.

D'autres objets, caractéristiques et avantages de la présente invention ressortiront mieux de l'exposé qui suit, fait en référence aux dessins annexés à ce texte, qui représentent un mode de réalisation préféré de celle-ci.

25 Brève description des figures

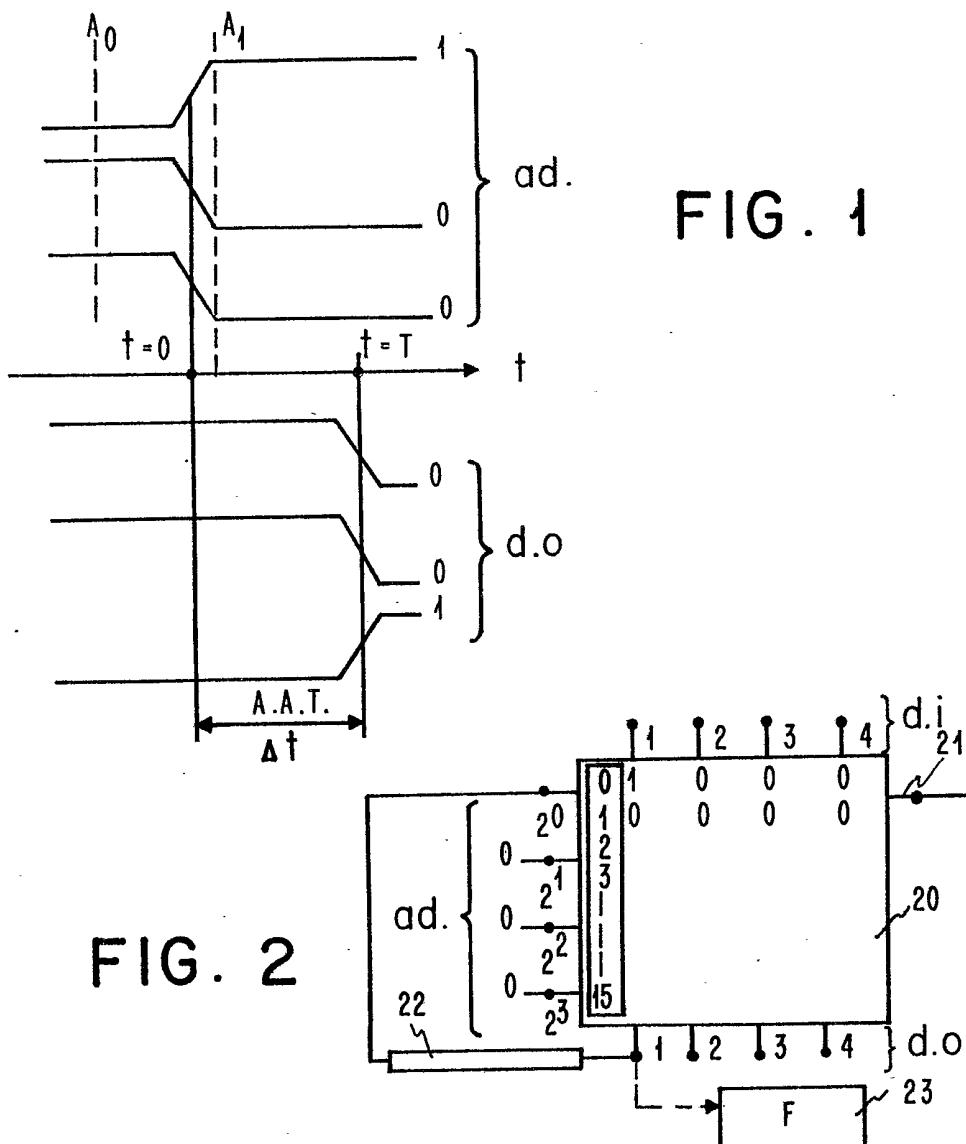

La figure 1 représente la définition du temps d'accès d'adresse (AAT), qui est l'intervalle de temps mesuré entre l'introduction d'une nouvelle adresse dans la mémoire et le moment où le contenu de la mémoire pour cette adresse, est 30 disponible sur les lignes de sortie.

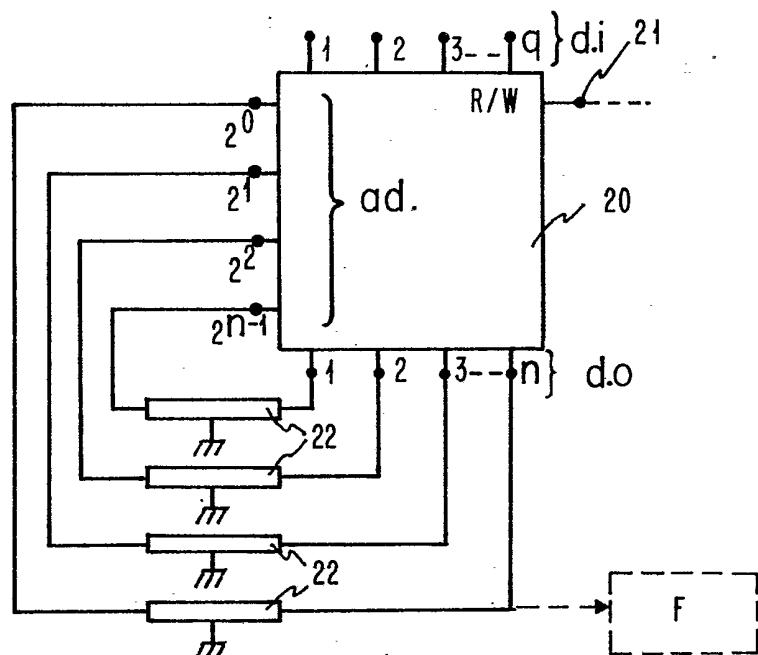

La figure 2 représente une mémoire en cours de test avec une

boucle de recirculation des données entre la ligne de sortie de données d.01 et la ligne d'adresse ad  $2^0$ .

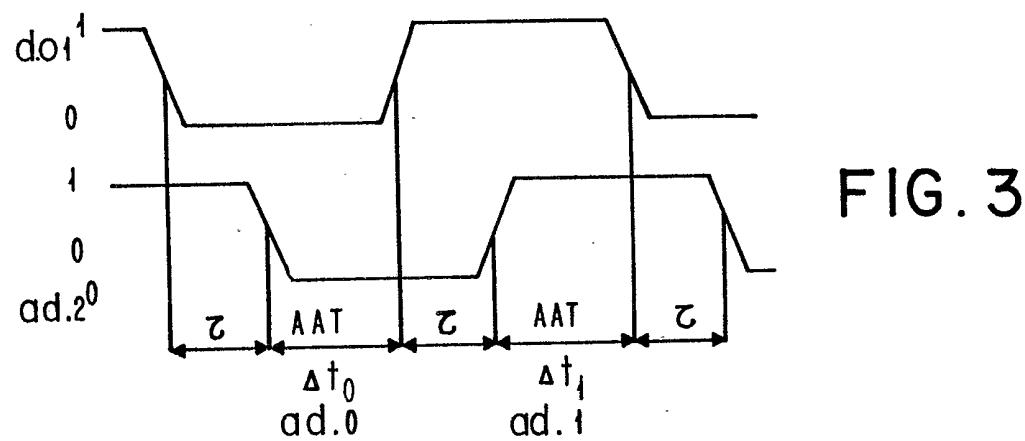

La figure 3 représente les signaux d'oscillation décalés dans le temps sur la ligne de données d.01 et la ligne 5 d'adresse ad  $2^0$ , quand il y a une boucle de recirculation.

La figure 4 représente une mémoire en cours de test identique à celle de la figure 2 avec quatre boucles de recirculation.

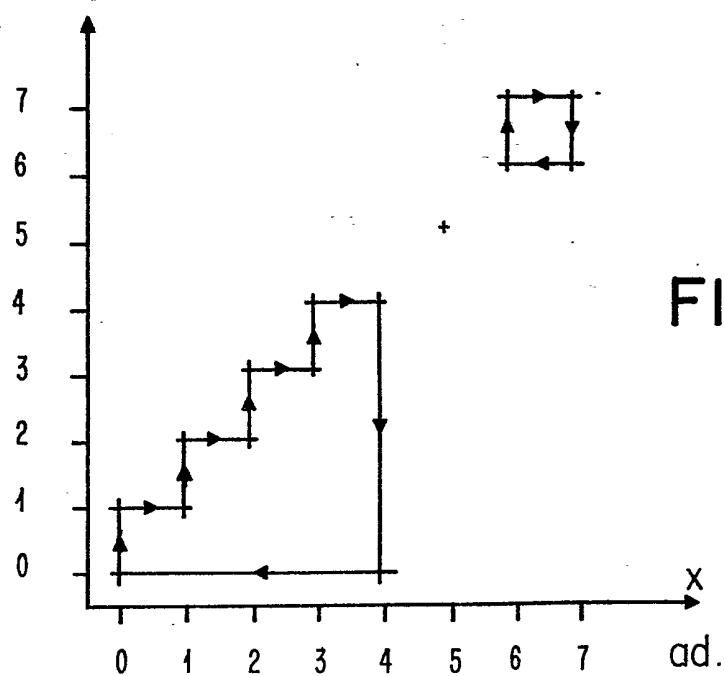

La figure 5 représente le diagramme des différents cas de recirculation possible, soit entre plus de deux adresses, 10 soit entre deux adresses, soit enfin un système stable.

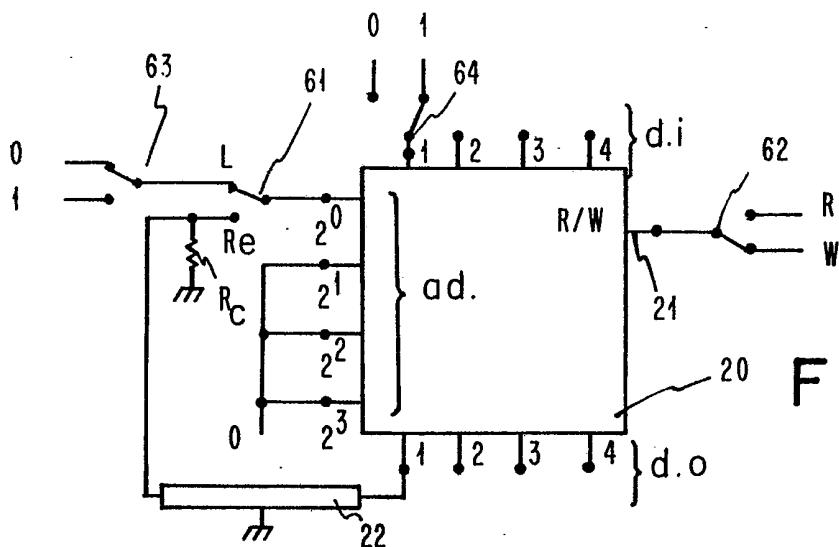

La figure 6 représente la réalisation pratique du test de la mémoire de la figure 2 dans laquelle les étapes de chargement et de recirculation sont entièrement manuelles.

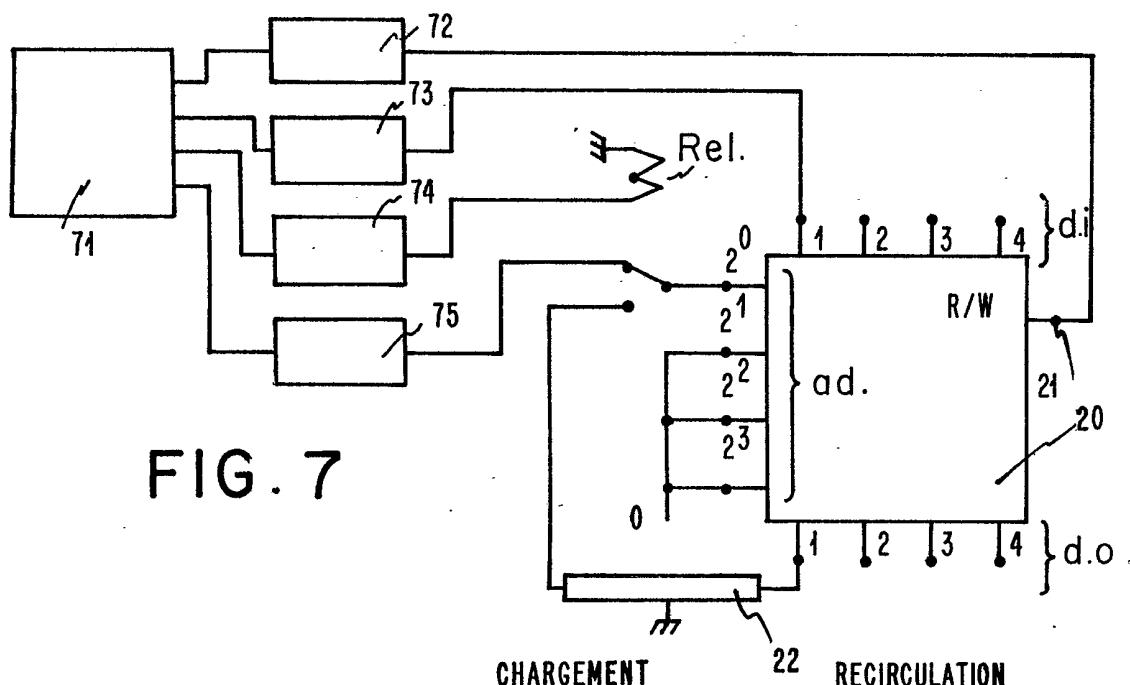

La figure 7 représente une autre réalisation pratique du 15 test de la mémoire de la figure 2 dans laquelle les étapes de chargement et de recirculation sont automatiques.

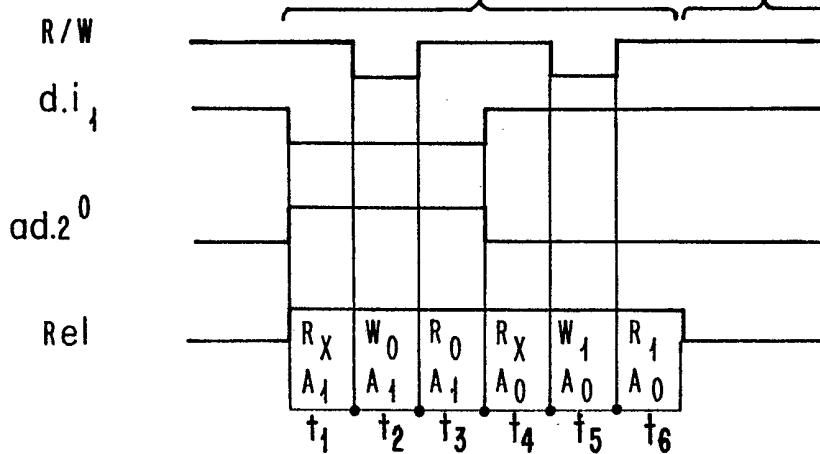

La figure 8 représente le diagramme des niveaux de tension correspondant aux lignes de sélection lecture/écriture R/W, d'entrée de données d.il, d'adresse ad  $2^0$  et du relai pour 20 le test précédent.

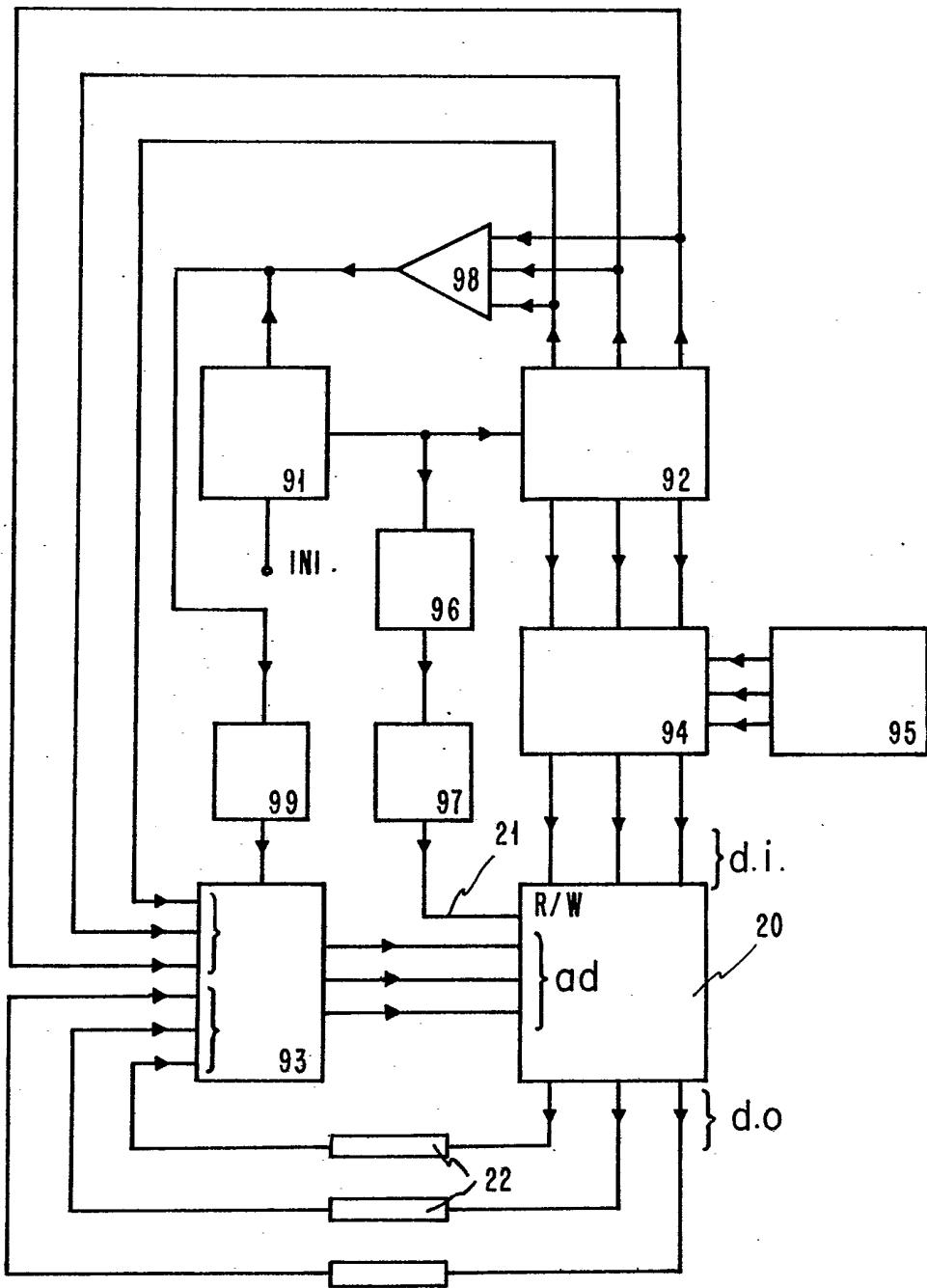

La figure 9 représente un circuit spécialisé pour le test automatique de la mémoire montrée sur la figure 2.

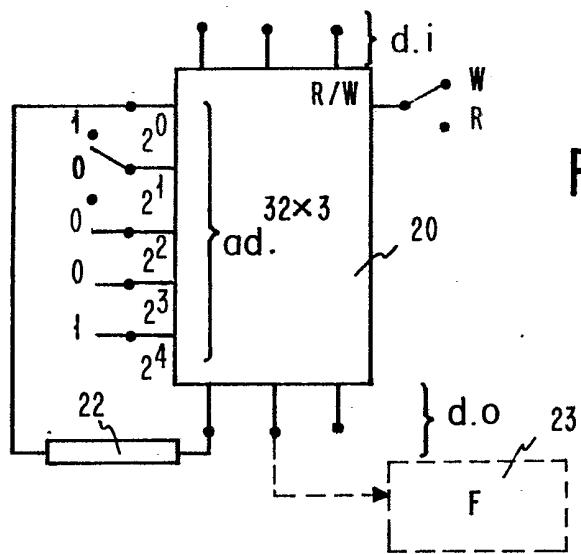

La figure 10 représente une mémoire de 32x3 en cours de test dont les résultats seront détaillés ci-après.

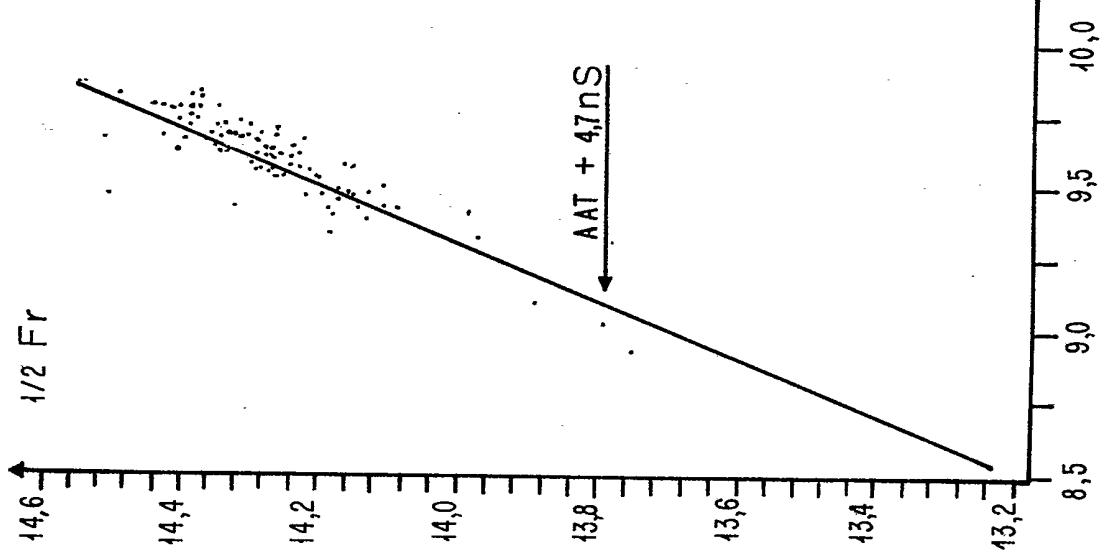

25 Les figures 11 et 12 représentent respectivement les courbes de détermination de l'AAT pour un échantillon de mémoires de 32x3 pour des recirculations entre deux groupes de deux adresses successives.

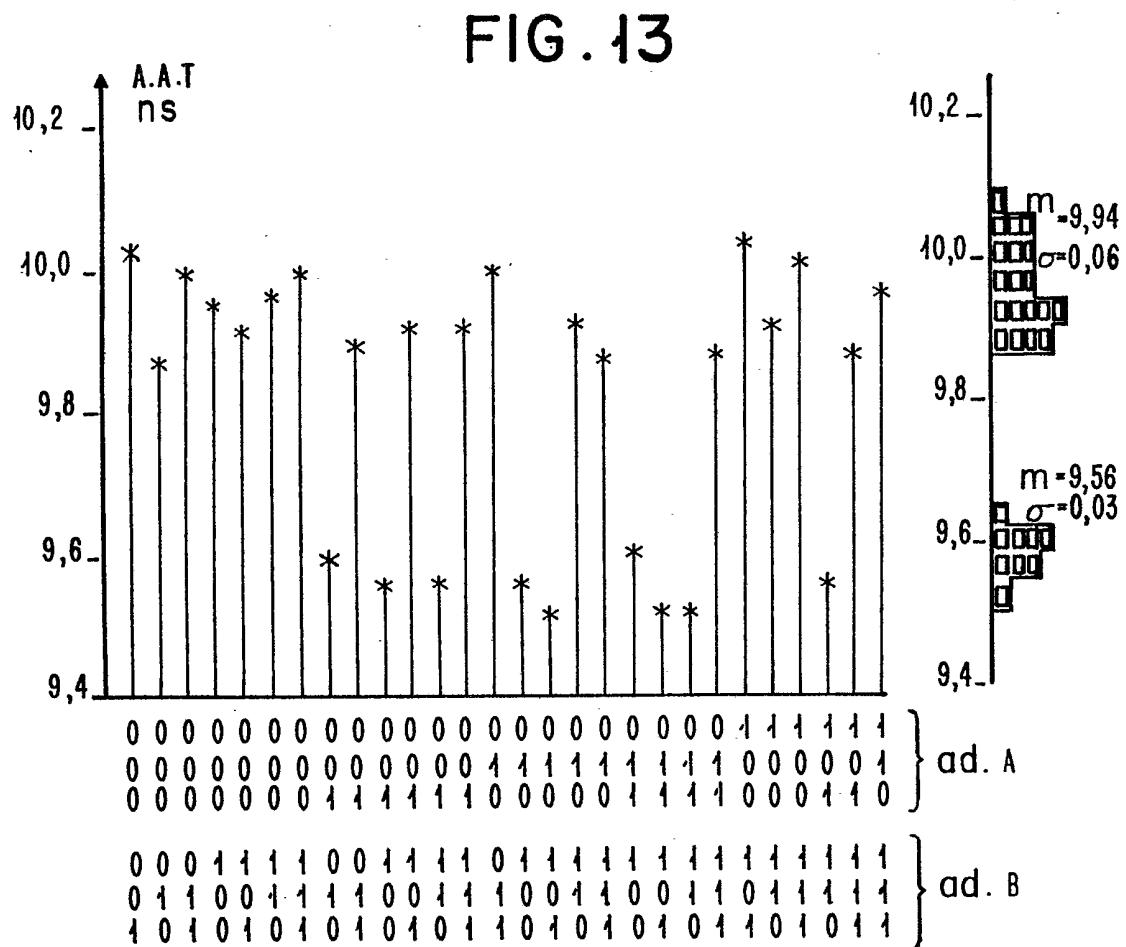

La figure 13 représente les AAT mesurés pour toutes les

combinaisons de deux adresses différentes pour une mémoire de 32x3.

Description de l'invention

5      I. Principe de la technique de recirculation appliquée à la mesure de l'AAT des mémoires

a) Principe de la mesure de l'AAT entre deux adresses

La figure 1 permet de comprendre la définition de l'AAT pour une mémoire présentant trois lignes d'adresse (ad) et trois lignes de données de sortie (d.O). Le contenu de l'adresse A<sub>0</sub> (011) est dans la mémoire, le mot (110) est disponible sur les lignes de données de sortie. Au temps t=0, l'adresse est changée, la nouvelle adresse A<sub>1</sub> (100) est introduite dans la mémoire. Les nouvelles données correspondant à cette adresse (001) sont disponibles au bout d'un temps Δt sur les lignes de données de sortie. Le temps Δt mesure le temps d'accès d'adresse ou AAT.

L'AAT est le temps le plus critique dans la mémoire car c'est lui qui limite le temps de cycle.

20     Sur la figure 2 on a représenté schématiquement une mémoire classique 20 munie de quatre lignes d'adresses 2<sup>0</sup> à 2<sup>3</sup> (soit 16 adresses différentes de 0 à 15) et de quatre lignes de données de sortie d.01 à d.04. Elle munie de façon classique d'une ligne de sélection R/W 21 qui selon son niveau de tension permet de choisir entre les modes d'écriture et de lecture. Elle comporte également un décodeur d'adresses non représenté. Supposons que l'on veuille recirculer entre les adresses 0 et 1. On force un "0" logique sur les lignes d'adresse 2<sup>1</sup>, 2<sup>2</sup>, et 2<sup>3</sup>. On écrit "1" dans le bit de poids 1 (ligne d.i1) à l'adresse 0 et "0" dans le bit de poids 1 (ligne d.i1) à l'adresse 1. Ce qui revient à écrire 0001 et 0000 aux adresses 0 et 1, grâce aux lignes d'entrée de données d.i1 à d.i4. Puis on connecte la ligne de sortie de

données d.01 à la ligne d'adresse ad  $2^0$  à travers une ligne à retard  $\tau$  de délai  $\tau$ .

Supposons que la mémoire soit alors à l'adresse 1, au temps t:0 apparaîtra en sortie le mot (0000), c'est-à-dire qu'on

5 aura 0 sur d.01.

Au temps  $t=\tau$  l'adresse sera égale à 0 sur la ligne  $2^0$ ;

lorsqu'on affiche une adresse sur une mémoire, il lui faut

le temps AAT pour donner le mot correspondant (1000), donc

au temps  $t=AAT+\tau$  le mot (1000) apparaît en sortie, l'itération

10 est la suivante:

|    | Signal sur<br>la ligne<br>d'adresse $2^0$                                                                                                                                                          | Signal sur la<br>ligne de<br>donnée d.01           |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 15 | t = 0<br>t = $\tau$<br>t = $\tau+AAT$<br>t = $(\tau+AAT)+\tau$<br><br>t = $(\tau+AAT) + (\tau+AAT)$<br>t = $2(\tau+AAT) + \tau$<br>20 t = $2(\tau+AAT) + \tau + AAT$<br>t = $3(\tau + AAT) + \tau$ | 1<br>0<br>0<br>1<br><br>1<br>0<br>0<br>0<br>1<br>1 |

|    |                                                                                                                                                                                                    | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1               |

|    |                                                                                                                                                                                                    | .                                                  |

|    |                                                                                                                                                                                                    | .                                                  |

|    |                                                                                                                                                                                                    | .                                                  |

Cette itération peut être présentée différemment. On peut raisonner en termes d'adresses et de mots apparaissant sur les lignes de sortie de données, sachant qu'à l'adresse k on

25 a écrit le mot: [mot (k)]

|   | délais     | adresse                 | mots<br>(sortie d.o)          |

|---|------------|-------------------------|-------------------------------|

| 5 | t=0        | 0001                    | mot (0001) = 0000             |

|   | t=τ+AAT    | (mot (0001)) = 0000     | mot (mot (0001)) = 0001       |

|   | t=2(τ+AAT) | mot (mot (0001)) = 0001 | mot (mot (mot (0001))) = 0000 |

avec une période  $T=2(\tau+AAT)$ . Cette période apparaît également

sur la figure 3, qui représente les signaux apparaissant sur

10 les lignes d.01 et ad<sup>0</sup>.

Le facteur  $\tau$  dépend de la ligne à retard 22 qui est un composant passif, c'est donc un temps parfaitement déterminé, et indréglable. C'est une caractéristique propre au testeur.

La mesure de  $F = 1/T$  avec un fréquencemètre 23 ou à partir

15 de toute autre technique permet de connaître l'AAT pour cette ligne d'adresse.

précises sur la rapidité de la mémoire. Egalement cette approche peut être utile dans le cas de configurations critiques: par exemple quand il y a beaucoup de lignes d'adresse à commuter simultanément.

- 5 On considère que l'on veut recirculer entre  $n$  lignes de sortie de données et  $n$  lignes d'adresses (ce qui correspond à  $2^n$  adresses).

On place la ligne de sélection lecture/écriture en position écriture.

- 10 On charge un mot de  $n$  bits dans chacune des  $m=2^n$  adresses, en d'autres termes, on balaye toutes les adresses et dans chaque adresse  $k$  ( $0 < k < 2^{n-1}$ ) on écrit un mot [mot  $(k)$ ]

- On reboucle les  $n$  lignes de sortie avec les  $n$  lignes d'adresses à travers  $n$  lignes à retard  $2\tau$  (de délai unitaire  $\tau$ ) comme

15 cela est représenté schématiquement sur la figure 4. On positionne la mémoire 20 en mode lecture grâce à la ligne de sélection R/W 21.

- Supposons que la mémoire soit à l'adresse  $(1)$ , au temps  $t=0$ , apparaîtra en sortie le mot [mot  $(1)$ ], à  $t=\tau$  l'adresse sera égale à [mot  $(1)$ ], mais il faut un temps  $\Delta t = AAT$  entre le moment où cette adresse est affichée et le moment où le mot correspondant à cette adresse est disponible sur les lignes de sortie de données:

- aussi au temps  $t = (\tau + AAT)$  apparaîtra en sortie

$[mot (mot (1))]$

- au temps  $t = (\tau + AAT) + \tau$  apparaîtra l'adresse

$[mot (mot (1))]$

- 5 au temps  $t = 2(\tau + AAT)$  apparaîtra en sortie

$[mot (mot (mot (1)))]$

- .

- .

- au temps  $t = j(\tau + AAT)$  apparaîtra en sortie

$[mot (\dots (mot (1)) \dots)]$

10 En fait  $(j+1)$  mots, comme il n'y a au maximum que  $m=2^n$  mots différents, il existe le nombre entier  $p \leq m$ , tel que au bout de  $p$  adresses balayées, le cycle recommence, c'est-à-dire que l'on peut écrire :

$$k = [mot (\dots (mot (k)) \dots)]$$

$\underbrace{\quad\quad\quad}_{p \text{ mots}}$

15 En d'autres termes le mot disponible sur les lignes de sortie correspond en fait à une adresse déjà traitée, ce qui assure la recirculation, en raisonnant comme ci-dessus en termes d'adresse et de mots on a avec  $p$  mots la correspondance suivante:

| Délai                | Adresse                                                                        | Mots<br>(sortie d.O)                                                                                                                                     |

|----------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| $t=0$                | $k$<br>[mot (k)]                                                               | $\left[ \begin{array}{l} \text{[mot (k)]} \\ \text{[mot (mot (k))]} \\ \vdots \\ \text{[mot ( ... (mot (k) ) ... )]} \end{array} \right]$<br>$p$<br>fois |

| $t=(p-1) (\tau+AAT)$ | $\underbrace{\text{[mot ( ... (mot (k) ) ... )]}}_{(p-1) \text{ mots}}$<br>$k$ | $\underbrace{\text{[mot ( ... (mot (k) ) ... )]}}_{p \text{ mots}}$                                                                                      |

| $t=p(\tau+AAT)$      |                                                                                |                                                                                                                                                          |

car par hypothèse

$$k = \underbrace{[\text{mot ( ... (mot (k) ) ... )}]}_{p \text{ mots}}$$

On peut conclure que la mémoire va osciller à une fréquence

$$F = \frac{1}{p(\tau+AAT)}$$

Dans le cas précédent, la figure 3 avait mis en évidence que p=2. De façon générale ce facteur p est facilement déterminé

5 par la séquence chargée.

Par extension de ce qui avait été écrit alors, l'AAT mesuré ici correspond à une moyenne des différents AAT pris en compte lors des différentes combinaisons d'adresse, une explication plus détaillée sera donnée lors de l'étude de la

10 figure 13.

Ce facteur p est tel que  $2 \leq p \leq 2^n$  dépend des mots chargés dans la mémoire, tandis que comme on l'a vu  $\tau$  est une constante. La mesure de la fréquence peut se faire avec un fréquencemètre

23.

15 c) Illustration

Ces considérations théoriques correspondent à différents fonctionnements possibles et vont être explicitées ci-après dans le cas d'une mémoire RAM comprenant huit mots de trois bits donc avec trois lignes d'adresse et

20 trois lignes de sortie de données.

Le contenu de la mémoire est donné dans le tableau I pour chacune des adresses, le mot de trois bits en binaire a été remplacé directement par l'adresse qui lui correspond. Par exemple l'adresse 0 correspond en fait à 000, et si le contenu du mot à l'adresse 4 est 000 on écrira que le contenu est 0.

25

TABLEAU I

| adresse | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|---------|---|---|---|---|---|---|---|---|

| contenu | 1 | 2 | 3 | 4 | 0 | 5 | 7 | 6 |

En partant de cette table on obtient le diagramme de la

5 figure 5. On a représenté respectivement sur l'axe des x les

adresses (numérotées de 0 à 7) et sur l'axe des y le contenu

de la mémoire à l'adresse correspondante qui sera après le

délai  $\tau$  appliquée au décodeur d'adresse pour fournir la

nouvelle adresse.

10 Supposons que la première adresse décodée soit 0, pour cette

adresse le contenu de la mémoire est 1. Après un temps

$\tau + AAT$ , 1 sera la nouvelle adresse décodée. Le nombre 2

contenu à l'adresse 1 sera transféré au décodeur après un

temps  $\tau + AAT$  et ainsi de suite. On peut suivre la séquence

15 sur la figure 5, qui se poursuit jusqu'à ce que l'adresse 0

soit de nouveau retrouvée (ici à l'adresse 4), la mémoire va

alors osciller selon le cycle d'adresse 0-1-2-3-4-0 ... etc. .

Il en sera de même dans le cas où la première adresse décodée

sera l'une des adresses 1, 2, 3 ou 4.

20 Par contre, si la première adresse décodée est 5, le contenu

correspondant est 5 et après le délai  $\tau + AAT$ , 5 sera la

nouvelle adresse décodée. La mémoire restera sur cette

adresse, le système sera stable (voir figure 5).

Si nous supposons maintenant que la première adresse décodée

25 est 6, la donnée de sortie correspondant à cette adresse est

7, ce 7 est transféré après un temps  $\tau + AAT$  comme nouvelle

adresse; à cette adresse correspond le contenu 6. Dans ce

dernier cas comme cela apparaît sur la figure 5, la mémoire

oscille entre les adresses 6 et 7.

Ainsi, on peut confirmer les différents modes de fonctionnement étudiés ci-dessus aux points 1 et 2. Il y a donc trois fonctionnements envisageables:

- . la recirculation entre deux adresses,

- 5 . la recirculation le long d'un cycle comportant plusieurs adresses,

- . et le système stable.

Le mode de fonctionnement dépendant seulement de l'adresse choisie pour initialiser l'opération et du contenu (choisi 10 généralement) de la mémoire.

Des impulsions erratiques (bruit) pourraient faire basculer d'un mode de fonctionnement à un autre mode non désiré. Il est donc souhaitable de choisir une configuration de données qui ne laisse qu'un mode possible. Si l'on veut circuler 15 entre deux adresses seulement, les adresses 0 et 2 par exemple, on choisira les données représentée sur le tableau III.

TABLEAU II

| adresse    | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|------------|---|---|---|---|---|---|---|---|

| 20 contenu | 2 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Le seul mode de fonctionnement possible est entre les adresses 2 et 0. Toutes les autres adresses renvoient à 0, assurant ainsi le cycle  $2 \leftrightarrow 0$ .

## II. Mode de réalisation préféré

25 Ainsi qu'on vient de le voir le chargement de la mémoire et la connexion ultérieure des lignes de sorties de données et des lignes d'adresse représentent deux points clés de l'invention.

Il y a deux façons de procéder:

a) Chargement manuel.

Le circuit est représenté sur la figure 6. La mémoire est chargée grâce à plusieurs commutateurs qui sont opérés manuellement.

5

Chargement : Le commutateur 61 est en position L (charge), le commutateur 62 qui commande le niveau de la ligne de sélection écriture/lecture 21 est en position W (écriture), le commutateur 63 est en position "adresse 0" et le commutateur 64 est en position "écrire 1". C'est la disposition des commutateurs représentée sur la figure 6. Le nombre 1 est ainsi placé à l'adresse 0. Puis en disposant le commutateur 63 sur la position 1, et le commutateur 64 sur la position 0, on introduit un 0 l'adresse 1.

10

Recirculation : le commutateur numéro 62 est mis en position R (lecture), et le commutateur 61 en position Re (recirculation).

20

La mémoire oscille donc entre les adresses 0 et 1 et on peut mesurer avec un fréquencemètre (non représenté) la fréquence d'oscillation et en déduire la valeur de l'AAT. La ligne à retard 22 est fermée sur l'impédance caractéristique  $R_c$  de la ligne; la valeur de  $R_c$  est imposée par les spécifications de la mémoire à tester. La ligne à retard a un délai  $\tau$ , qui est spécifié par le constructeur et qui est fonction de sa longueur.

25

Ce système présente les avantages du coût et de la simplicité, cependant il est très lent (30 secondes sont nécessaires pour charger la mémoire), et nécessite en outre la présence permanente d'un opérateur).

30

b) Chargement automatique

Une première solution est représentée sur la figure 7. Ce système comprend un générateur de mots 71 programmable fonctionnant comme générateur d'impulsions et quatre circuits de mise en forme 72 à 75. Le circuit 74 commande un relai Rel. qui permet de relier la ligne d'adresse ad  $2^0$  à la ligne à retard pendant l'opération de lecture. Les commutateurs de sélection R/W 62 et d'entrée de données 64 (figure 6) ne sont plus nécessaires. L'appareil 71 permet le fonctionnement dans un seul cycle qui est représenté sur la figure 8.

Sur cette figure, on a représenté les niveaux de tension des différentes lignes, de sélection lecture/écriture R/W, d'entrée de données d.il, d'adresse ad  $2^0$  et l'état du relai Rel. Le relai est au niveau 1 (excité) pendant l'étape de chargement (c'est la position représentée sur la figure 7). Pendant cette étape, on écrit 0 à l'adresse 1 pendant le temps t2; le 0 est lu pendant le temps t3; puis on écrit un 1 à l'adresse 0 pendant le temps t5, opération qui est vérifiée pendant le temps t6. Ensuite, le relais passe au niveau 0 et on fait recirculer les données.

Une deuxième solution consistait à réaliser un circuit spécifique pour assurer le chargement, et la recirculation pour permettre les mesures de l'AAT d'une mémoire. Le système complet est représenté sur la figure 9. Dans le test par recirculation, la séquence est chargée dans la mémoire par un circuit spécialisé, qui joue donc le rôle classique du générateur de mots, mais en plus simple et en moins rapide (fréquence d'horloge 1 MHz, et calage des signaux avec une précision inférieure à 50 nanosecondes), puisque comme on l'a vu, l'AAT est essentiellement fonction du délai de la ligne à retard. En outre, tout le circuit spécialisé qui est réalisé en logique TTL standard peut tenir, sur une seule carte, ce qui permet de faire des économies considérables sur le testeur.

Chargement : Dans un premier temps les adresses sont balayées tandis que l'on charge dans chacune d'elles 5 sont contenu. L'horloge 91 incrémente un compteur binaire 92. D'une part, les signaux issus de ce compteur 92 incrémentent le multiplexeur 93 qui pilote les circuits d'adresse de la mémoire 20 en cours de test et d'autre part, simultanément, servent de commande pour 10 le multiplexeur 94 qui balaie le contenu de la matrice de programmation 95 (qui contient les informations à écrire dans la mémoire). Cette matrice peut être une mémoire de type ROM, ou REPROM, ou un simple panneau de commande avec commutateur.

Le circuit de retard 96 permet de compenser les délais 15 dûs au compteur 92 et aux multiplexeurs 93 et 94 (pour être certain que les adresses et les données arrivent en synchronisme sur la mémoire) et d'appliquer à la ligne R/W 21 le potentiel d'écriture pendant le temps approprié. Le circuit de génération d'impulsions d'écriture 20 97 permet de positionner la mémoire en position d'écriture sous la commande du circuit 96. Lorsque toutes les adresses ont été balayées, le circuit ET 98 25 détecte la dernière adresse (par exemple 111) appliquée à la mémoire, et vient bloquer les impulsions d'horloge et après un certain délai dans le circuit 99 vient faire basculer le multiplexeur 93 de manière à boucler les sorties de la mémoire sur les adresses correspondantes afin de la faire recirculer.

Ce circuit permet d'automatiser la mesure. Il suffit 30 d'une impulsion (manuelle ou télécommandée) pour le circuit de remise à zéro de l'horloge, pour déclencher la recirculation.

Pour assurer un test significatif, il est important que 35 les données introduites en mémoire ne puissent subir les modifications non désirées au cours du temps. En d'autres termes le contenu des cellules de mémoire doit

5

être stable. D'où l'utilisation d'alimentations en puissance programmable à faible bruit, le contrôle des températures, le contrôle des cellules de mémoire non concernées par le test, qui pourront néanmoins être chargées.

10

Les mesures de fréquences sont réalisées avec un compteur numérique, la fréquence étant simplement déduite du nombre d'impulsions  $n$  comptées durant l'intervalle  $\tau$ . Dans les résultats qui vont suivre on a utilisé une ligne à retard de 4,7 nanosecondes, pour des mémoires qui ont des AAT moyens de l'ordre de 5 nanosecondes. La fréquence correspondante est

$$F = \frac{1}{2(AAT+\tau)} = 50 \text{ MHz.}$$

### III. Résultats

15

Un montage expérimental montré sur la figure 10 voisin de celui montré sur la figure 2, a été réalisé pour tester une mémoire 32x2 (32 mots de 3 bits). On assure la recirculation entre deux lignes d'adresse consécutives à deux emplacements différents de la mémoire, par exemple entre les adresses 16 et 17 d'une part et 18 et 19 d'autre part. Dans le premier cas, à l'adresse 16 (01111), on a chargé 17 (10000) et à l'adresse 17 (10000) on a chargé 16 (01111). On a procédé de façon similaire pour les adresses 18 et 19, à l'adresse 18 on a chargé 19 et à l'adresse 19 on a chargé 18. En ce qui concerne les autres lignes d'adresse on applique un 1 à la ligne d'adresse  $2^4$  et 0 aux lignes d'adresses  $2^3$  et  $2^2$ . Une ligne à retard de 4,7 nanosecondes assure le rebouclage sur la ligne d'adresse  $ad\ 2^0$ .

30

On a disposé un commutateur sur la ligne d'adresse  $ad\ 2^1$  qui permet d'appliquer des valeurs binaires 0 et 1. Quand le commutateur est sur la position 1, on recircule entre les adresses 18 et 19 et quand il est sur la position 0, on recircule entre les adresses 16 et 17. Un fréquencemètre est

disposé sur d.02 afin de ne pas perturber les mesures. On va donc mesurer la somme des temps d'accès d'adresse correspondant aux adresses 16 et 17 d'une part et 18 et 19 d'autre part.

Les résultats ont été comparés aux temps mesurés par un

5 testeur plus performant de type classique sur un échantillon

de 100 mémoires.

$$Fr = \frac{1}{2(AAT+\tau)} \quad \text{d'où} \quad AAT = \frac{1}{2Fr} - \tau$$

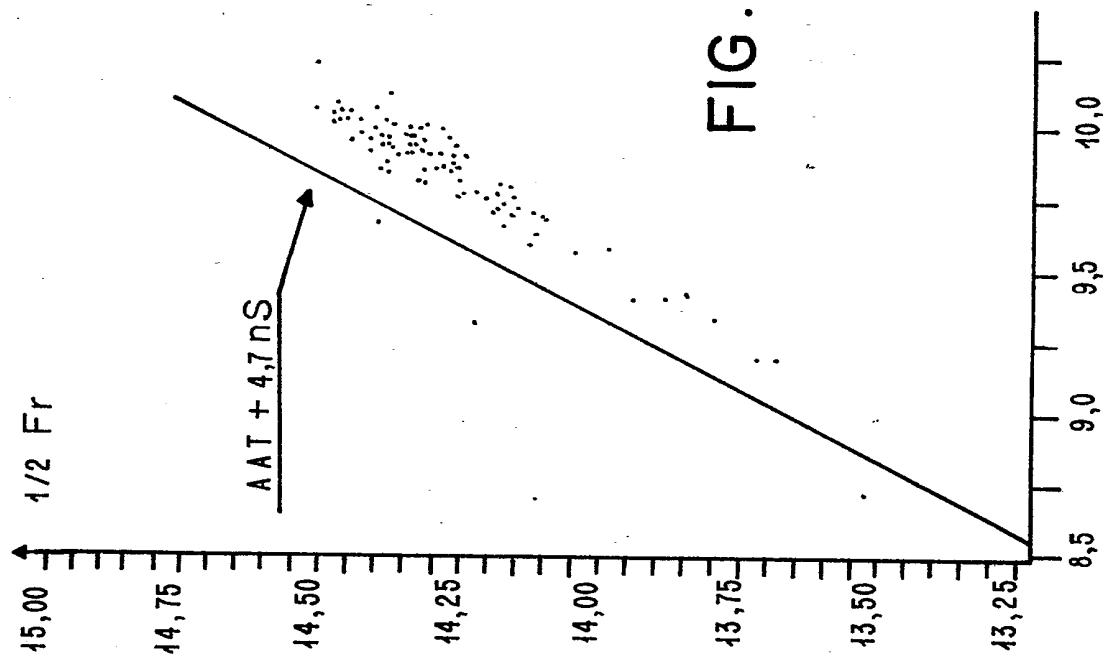

On a corrélé les AAT mesurés sur le testeur classique avec

10 1/2Fr. Les résultats sont montrés sur la figure 11 pour la

recirculation entre les adresses 16 et 17 et sur la figure

12 pour la recirculation entre les adresses 18 et 19. Ils

mettent respectivement en évidence les éléments suivants:

(adresses 16, 17) - Le facteur de corrélation entre AAT et

1/2F est de 0,92.

15 La valeur de la différence moyenne: 1/2F-AAT est de 4,7

secondes, c'est le délai de la ligne à retard et

La déviation standard résiduelle est de 95 picosecondes.

Pour les adresses (18, 19), le facteur de corrélation entre

AAT et 1/2F est de 0,92.

20 La valeur de la différence moyenne: 1/2F-AAT est 4,5 nanosecondes.

La déviation standard résiduelle est de 95 picosecondes.

La technique de recirculation permet des mesures de temps

d'accès d'adresses avec une précision égale ou meilleure que

les appareils classiques les plus performants à ce jour.

25 On a enfin comparé les AAT résultants de différentes combinaisons d'adresses. On a mesuré les AAT pour une recirculation

entre deux adresses de l'adresse A ( $0 \leq A \leq 7$ ) à l'adresse B ( $0 \leq B \leq 7$ ) pour chaque couple A,B ( $A \neq B$ ) ce qui correspond à 28 couples.

On peut voir sur la figure 13 pour chaque couple (A,B) en

5 abscisse, on a représenté la somme des AAT correspondant à ce couple, c'est-à-dire  $(AAT_{(A \rightarrow B)} + AAT_{(B \rightarrow A)})$  en ordonnées. On peut se rendre compte que lorsque les adresses A et B ont au moins deux bits opposés, l'AAT est d'environ 400 picosecondes à 500 picoseconds plus rapide, par exemple pour le

10 couple adA = 010 et adB = 101 l'AAT correspondant est d'environ 9,5 nanosecondes. On a représenté sur la figure, les moyennes et les écarts types.

#### IV. Application industrielle

La technique de test par recirculation permet le test AC (en

15 courant alternatif) des mémoires RAM et ROS, en ce qui concerne l'AAT. Ce test est effectué avec une grande précision de mesure et est très économique car la circuiterie est simple et peu performante (au point de vue des fréquences). En plus elle est indépendante de la vitesse de la mémoire à

20 tester. Les résultats obtenus montrent que les mesures de fréquence peuvent être effectuées facilement avec des résolutions de  $10^{-4}$  soit sur un temps de 30ns, une résolution de 3ps. La résolution sera d'autant meilleure que la mémoire sera plus rapide.

25 Cependant il est limité par le choix des configurations de test pour éviter les impulsions de bruit comme on l'a vu et également dans le test des mémoires ROS qui ont un contenu préalablement déterminé.

Bien que l'on ait décrit dans ce qui précède et représenté

30 sur les dessins les caractéristiques essentielles de l'invention appliquées à un mode de réalisation préféré de celle-ci, il est évident que l'homme de l'art peut y apporter toutes modifications de forme ou de détail qu'il juge utiles, sans pour autant sortir du cadre de ladite invention.

## REVENDICATIONS

1. Procédé de mesure du temps d'accès d'adresse (AAT) par recirculation entre n lignes de sortie et n lignes d'adresse d'une mémoire du genre comportant une ligne de sélection lecture/écriture, une pluralité de lignes de sortie de données, une pluralité de lignes d'entrée de données, et une pluralité de lignes d'adresse, caractérisé en ce qu'il comporte les étapes suivantes:

mise de la ligne de sélection sur la position écriture,

10 chargement dans la mémoire d'une configuration désirée de  $2^n$  mots de n bits correspondant aux  $2^n$  adresses: toutes les adresses sont balayées et à chaque adresse (k) on écrit le mot [mot (k)],

mise de la ligne de sélection sur la position lecture,

15 connexion de n lignes de sortie d'adresse à n lignes d'adresses par n lignes à retard de délai  $\tau$ ; puisqu'il y a un maximum de  $m = 2^n$  différents mots, il existe un entier  $p \leq m$  tel que

$$k = [\text{mot } (\text{mot } (\dots \text{mot } (k) \dots))]$$

20 en fait p mots, de telle sorte que la mémoire oscille avec une fréquence F telle que

$$F = \frac{1}{p(\tau + AAT)}$$

25 le terme AAT représentant une approximation moyenne des AAT correspondant à toutes les combinaisons des adresses intervenant dans la recirculation,

mesure de la fréquence F et détermination du paramètre p et,

détermination de la valeur de l'AAT par la relation

$AAT = 1/pF - \tau$ .

2. Procédé selon la revendication 1 caractérisé en ce que

ladite configuration de mot est telle que si à l'adresse

5 k on écrit le mot [mot (k)] et à l'adresse j le

[mot (j)] on ait [mot (k)] = adresse j et

[mot (j)] = adresse k, de telle sorte que l'on recir-

cule entre les deux adresses k et j, d'où l'on déduit

$$AAT = \frac{AAT_{k \rightarrow j} + AAT_{j \rightarrow k}}{2}$$

10 3. Procédé selon la revendication 1 ou 2 caractérisé en ce

que les lignes d'adresse non utilisées sont reliées à

des potentiels appropriés.

4. Procédé selon la revendication 1, 2 ou 3, caractérisé

en ce que la mémoire est une mémoire de type RAM.

15 5. Testeur pour la mesure automatique des AAT des mémoires

du type comportant une ligne de sélection lecture/écri-

ture, une pluralité de lignes d'entrée et de sortie de

données, une pluralité de lignes d'adresse, caractérisé

en ce qu'il comporte:

20 des moyens pour charger la mémoire selon une configu-

ration désirée contenue dans une mémoire annexe, afin

que pour chaque adresse (k) on écrive un [mot (k)] pen-

dant que la ligne de sélection se trouve en position

écriture,

25 des moyens pour connecter n lignes de sortie de données

de la mémoire à n lignes d'adresse à travers n lignes à

retard de délai  $\tau$ , pour la faire recirculer entre ces

adresses pendant que la ligne de sélection se trouve en

position lecture, et

30 des moyens de synchronisation de ces opérations associés

à des moyens d'initialisation et de blocage des séquences de chargement et de recirculation.

6. Testeur selon la revendication 5 caractérisé en ce que lesdits moyens de chargement comprennent un multiplexeur (94) relié d'une part aux lignes d'entrée de données de la mémoire et d'autre part à la mémoire annexe (95) qui contient la configuration de mots désirée sous la commande d'un compteur (92) contrôlé par les moyens de synchronisation des séquences (91).

- 10 7. Testeur selon la revendication 6 caractérisé en ce que lesdits moyens de recirculation comprennent un multiplexeur (93) alimentant les lignes d'adresse qui reçoit d'une part les données du compteur (92) et d'autre part, les données provenant des lignes de sortie de la mémoire à travers les lignes à retard, la commutation entre ces données s'effectuant sous la contrôle des moyens de synchronisation.

- 15 8. Testeur selon la revendication 7 caractérisé en ce que lesdits moyens de synchronisation (91) sont constitué par une horloge, ils sont associés à des moyens de blocage (98) quand toutes les adresses ont été balayées et à des moyens d'initialisation (INI) pour démarrer la séquence de mesure.

- 20 9. Testeur selon la revendication 8 caractérisé en ce que la ligne de sélection écriture/lecture est commandée par les moyens de sélection contrôlés par les moyens de synchronisation.

- 25 10. Testeur selon la revendication 8 ou 9 caractérisé en ce que lesdits moyens de sélection comportent un circuit de délai (96) et un générateur d'impulsions (97).

- 30 11. Testeur selon la revendication 10 caractérisé en ce que le contrôle de la commutation des données pour le multiplexeur (93) s'effectue par un circuit de délai (99).

FIG. 4

CONTENU MEMOIRE

DISPONIBLE SUR d.o.

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 12

FIG. 11