(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6525475号

(P6525475)

(45) 発行日 令和1年6月5日(2019.6.5)

(24) 登録日 令和1年5月17日(2019.5.17)

(51) Int.Cl.

F 1

G06F 3/041 (2006.01)

G06F 3/041 5 1 2

G06F 3/044 (2006.01)

G06F 3/044 1 2 4

G06F 3/041 5 2 2

請求項の数 20 (全 14 頁)

(21) 出願番号 特願2016-549567 (P2016-549567)

(86) (22) 出願日 平成27年4月14日 (2015.4.14)

(65) 公表番号 特表2017-511518 (P2017-511518A)

(43) 公表日 平成29年4月20日 (2017.4.20)

(86) 國際出願番号 PCT/US2015/025759

(87) 國際公開番号 WO2015/160812

(87) 國際公開日 平成27年10月22日 (2015.10.22)

審査請求日 平成30年4月12日 (2018.4.12)

(31) 優先権主張番号 14/254,164

(32) 優先日 平成26年4月16日 (2014.4.16)

(33) 優先権主張国 米国(US)

(73) 特許権者 397050741

マイクロチップ テクノロジー インコーポレイテッド

MICROCHIP TECHNOLOGY INCORPORATED

アメリカ合衆国 85224-6199

アリゾナ チャンドラー ウエスト チャンドラー ブルヴァード 2355

(74) 代理人 100078282

弁理士 山本 秀策

(74) 代理人 100113413

弁理士 森下 夏樹

最終頁に続く

(54) 【発明の名称】 投影容量式タッチスクリーンおよびパネルの信号／雑音性能を改良するための装置

## (57) 【特許請求の範囲】

## 【請求項 1】

高電圧を発生させ、前記高電圧を複数のノードに選択的に結合するための単一集積回路であって、前記単一集積回路は、

高電圧出力を有する電圧ブースト回路と、

前記電圧ブースト回路に結合されている電圧基準と、

複数の電圧レベルシフタ／ドライバであって、各々は、前記電圧ブースト回路の高電圧出力に結合されている高電圧入力と、独立して制御可能な高電圧出力とを有し、各々は、前記ノードのうちの1つに結合されている、複数の電圧レベルシフタ／ドライバと、

前記複数の電圧レベルシフタ／ドライバに結合されている論理回路であって、前記論理回路は、前記複数の電圧レベルシフタ／ドライバの前記高電圧出力のイネーブルメントを制御する、論理回路と、

前記論理回路および前記電圧ブースト回路に結合されているシリアル／パラレルインターフェースであって、前記シリアル／パラレルインターフェースは、第1のモードにおいて各レベルシフタ／ドライバの出力状態を決定するように、または、第2のモードにおいて前記電圧ブースト回路のパラメータを構成するように構成されている、シリアル／パラレルインターフェースと

を備えている、単一集積回路。

## 【請求項 2】

前記電圧ブースト回路および前記シリアル／パラレルインターフェースに結合されてい

10

20

るパワー・オンリ・セット（P O R）回路をさらに備えている、請求項 1 に記載の单一集積回路。

【請求項 3】

前記電圧ブースト回路に結合されているソフトスタート回路をさらに備え、ソフトスタートの間、前記複数の電圧レベルシフタ／ドライバの前記出力は、ディスエーブルにされている、請求項 1 に記載の单一集積回路。

【請求項 4】

前記論理回路は、複数の A N D ゲートである、請求項 1 に記載の单一集積回路。

【請求項 5】

出力イネーブル制御が、前記複数の A N D ゲートの各々の入力に結合されている、請求項 4 に記載の单一集積回路。 10

【請求項 6】

高電圧出力コンデンサが、前記電圧ブースト回路の出力と電源コモンとの間に結合されている、請求項 1 に記載の单一集積回路。

【請求項 7】

ブーストインダクタが、前記電圧ブースト回路への電力入力と電源との間に結合されている、請求項 1 に記載の单一集積回路。

【請求項 8】

前記複数の電圧レベルシフタ／ドライバの前記出力は、トライステートであり、電源コモン、前記高電圧出力、または高オフ抵抗において選択可能出力状態を有する、請求項 1 に記載の单一集積回路。 20

【請求項 9】

前記シリアル／パラレルインターフェースは、構成レジスタおよびデータ記憶レジスタをさらに備え、前記構成レジスタは、前記電圧ブースト回路の前記パラメータを記憶し、前記データ記憶レジスタは、前記複数の電圧レベルシフタ／ドライバの出力状態を記憶している、請求項 1 に記載の单一集積回路。

【請求項 10】

ソフトスタートの間、前記複数の電圧レベルシフタ／ドライバの前記出力は、ディスエーブルにされている、請求項 1 に記載の单一集積回路。

【請求項 11】

前記複数の電圧レベルシフタ／ドライバの入力回路および前記論理回路は、低電圧および低電力デバイスを備えている、請求項 1 に記載の单一集積回路。 30

【請求項 12】

前記複数の電圧レベルシフタ／ドライバの出力回路は、低インピーダンス駆動能力を有する高電圧デバイスを備えている、請求項 1 に記載の单一集積回路。

【請求項 13】

タッチの場所を決定し、投影容量式タッチ感知表面上のタッチを検出するためのシステムであって、

前記システムは、請求項 1 ～ 12 のいずれかに記載の集積回路を備え、

前記システムは、

第 1 の軸を有する並列配向に配列された第 1 の複数の電極であって、前記第 1 の複数の電極の各々は、自己容量を備えている、第 1 の複数の電極と、

前記第 1 の軸に実質的に垂直な第 2 の軸を有する並列配向に配列された第 2 の複数の電極であって、前記第 1 の複数の電極は、前記第 2 の複数の電極の上に位置し、前記第 1 の複数の電極と前記第 2 の複数の電極との重複交差点を備えている複数のノードを形成し、前記複数のノードの各々は、相互容量を備え、前記第 1 の複数の電極および前記第 2 の複数の電極のうちの選択された電極は、前記ノードと接続されている、第 2 の複数の電極と、

混合信号デバイスであって、

前記第 1 の複数の電極および前記第 2 の複数の電極のうちのそれぞれの 1 つに結合さ 50

れている複数のアナログ入力を有する容量式タッチアナログフロントエンドと、

前記容量式タッチフロントエンドに結合されているアナログ/デジタルコンバータ(ADC)と、

デジタルプロセッサおよびメモリであって、前記ADCからの少なくとも1つの出力が、前記デジタルプロセッサに結合されている、デジタルプロセッサおよびメモリと、

前記デジタルプロセッサと前記集積回路の前記シリアル/パラレルインターフェースとに結合されているシリアルインターフェースであって、前記デジタルプロセッサは、前記シリアルインターフェースを通して前記集積回路の動作を制御するように構成されている、シリアルインターフェースと

を備えている、混合信号デバイスと

をさらに備え、

前記自己容量の値は、前記アナログフロントエンドによって、前記第1の複数の電極の各々に対して前記高電圧を使用して測定され、前記測定された自己容量の値は、前記メモリ内に記憶され、前記自己容量の最大値のうちの少なくとも1つを有する前記第1の電極のうちの少なくとも1つのノードの相互容量の値は、前記アナログフロントエンドによって、前記高電圧を使用して測定され、前記測定された相互容量の値は、前記メモリ内に記憶され、前記デジタルプロセッサは、前記記憶された自己容量値および相互容量値を使用して、前記タッチの場所および前記タッチ感知表面に加えられたそれぞれの力を決定する、

システム。

#### 【請求項14】

前記混合信号デバイスは、混合信号マイクロコントローラ集積回路である、請求項13に記載のシステム。

#### 【請求項15】

前記高電圧は、前記集積回路および前記混合信号デバイスに給電する供給電圧より大きい、請求項13または請求項14に記載のシステム。

#### 【請求項16】

投影容量式タッチ感知表面の信号/雑音性能を改良する方法であって、前記方法は、請求項1~10のいずれかに記載の集積回路を提供するステップと、

前記集積回路の動作を制御するために、マイクロコントローラをシリアルインターフェースを通して前記集積回路に結合するステップと、

タッチセンサ配列を前記集積回路および前記マイクロコントローラに結合するステップであって、前記タッチセンサ配列は、第1の軸を有する並列配向に配列された第1の複数の電極を備え、前記第1の複数の電極の各々は、自己容量を備えている、ステップと、

前記第1の軸に実質的に垂直な第2の軸を有する並列配向に配列された第2の複数の電極を提供するステップであって、前記第1の複数の電極は、前記第2の複数の電極の上に位置し、前記第1の複数の電極と前記第2の複数の電極との重複交差点を備えている複数のノードを形成し、前記複数のノードの各々は、相互容量を備えている、ステップと、

前記集積回路を用いて前記第1の複数の電極を電源電圧より大きい電圧に充電するステップと、

前記第2の複数の電極を電源コモンに放電するステップと、

前記第1の複数の電極を走査し、前記第1の複数の電極の自己容量の値を決定するステップと、

前記走査された自己容量の値を比較し、前記第1の複数の電極のうちのどれが前記自己容量の最大値を有するかを決定するステップと、

前記自己容量の最大値を有する前記第1の複数の電極のうちの1つの複数のノードを走査し、それぞれの複数のノードの相互容量の値を決定するステップと、

前記自己容量の最大値を有する第1の電極上のそれぞれの複数のノードの走査された相互容量の値を比較するステップであって、前記相互容量の最大値を有するノードは、前記タッチ感知表面上のタッチの場所である、ステップと

10

20

30

40

50

を含む、方法。

【請求項 17】

前記自己容量値および相互容量値は、アナログフロントエンドおよびアナログ／デジタルコンバータ（A D C）を用いて測定される、請求項 16 に記載の方法。

【請求項 18】

前記自己容量値および相互容量値は、デジタルプロセッサのメモリ内に記憶される、請求項 16 または請求項 17 に記載の方法。

【請求項 19】

前記自己容量値および相互容量値は、容量式分圧器法によって決定される、請求項 16 17、または 18 に記載の方法。

10

【請求項 20】

前記自己容量値および相互容量値は、充電時間測定ユニットを用いて決定される、請求項 16、17、または 18 に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、投影容量式タッチスクリーンおよびパネルに関し、より具体的には、投影容量式タッチスクリーンおよびパネルの信号／雑音性能の改良に関する。

【背景技術】

【0002】

容量式タッチスクリーンおよびパネルは、電子機器、例えば、コンピュータ、携帯電話、パーソナルポータブルメディアプレーヤ、計算機、電話、レジ、ガソリンポンプ等に対するユーザインターフェースとして使用される。いくつかの用途では、不透明タッチスクリーンおよびパネルが、ソフトキー機能性を提供する。他の用途では、透明タッチスクリーンが、ディスプレイにオーバーレイし、ユーザが、タッチまたは近接性を介して、ディスプレイ上のオブジェクトと相互作用することを可能にする。そのようなオブジェクトは、ディスプレイ上のソフトキー、メニュー、および他のオブジェクトの形態であり得る。容量式タッチスクリーンまたはパネルは、オブジェクト、例えば、ユーザの指の先端が、容量式電極の容量を変化させると、タッチスクリーンまたはパネル内の容量式電極の容量の変化によって起動される（起動を示す信号を制御する）。

20

【0003】

今日の容量式タッチスクリーンおよびパネルは、單一タッチならびに多重タッチを含む、異なる多様性で存在する。單一タッチスクリーンまたはパネルは、タッチスクリーンもしくはパネルに接触または近接する 1 つのオブジェクトの位置を検出し、報告する。多重タッチスクリーンまたはパネルは、タッチスクリーンもしくはパネルに同時に接触または近接する 1 つ以上のオブジェクトの位置を検出し、各オブジェクトに関連する別個の位置情報を報告するか、またはそれに従って行動する。

30

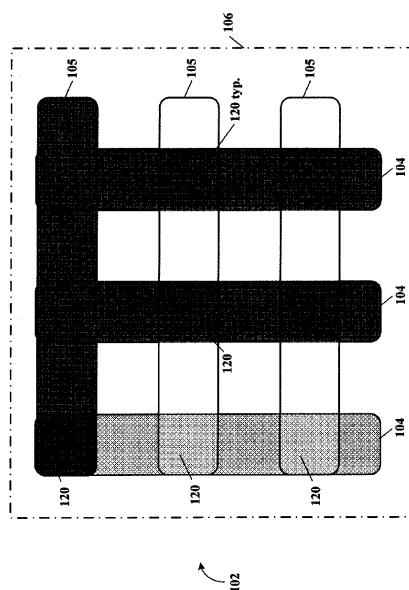

【0004】

單一タッチおよび多重タッチシステムの両方において使用されるタッチスクリーンならびにパネルは、1 つ以上の層を備え得、各層は、互いから電気的に絶縁される複数の電極を有する。多重層タッチセンサでは、層は、互いに近接して固定されるが、電気的に絶縁され得る。1 つ以上の層のタッチスクリーンおよびパネル構造のいずれかでは、電極（容量）は、任意のタイプの座標系（例えば、極、等）を形成し得る。いくつかのタッチセンサは、X - Y またはグリッド状配列を利用し得る。図 1 を参照すると、描写されるのは、本開示の教示による、X - Y グリッド配向に配列されるタッチセンサ電極の基本構想図である。例えば、2 層タッチスクリーンまたはパネル 102 では、電極 104 および 105 は、異なる層（基板 106）上にあり、異なる層上の電極 104 と 105 との間の、以下、ノード 120 と称される、その交差点が、グリッド（または他の座標系）を画定するように、互いに直交して配列され得る。代替単層タッチスクリーンでは、電極の 1 つの組と電極の別の組との間の近接関係が、同様に、グリッド（または他の座標系）を画定し得

40

50

る。

【0005】

タッチスクリーンまたはパネル内の個々の電極の自己容量を測定することは、単一タッチシステムによって採用される方法の1つである。例えば、X-Yグリッドを使用して、タッチセンサコントローラは、X-軸電極105およびY-軸電極104の各々を通して反復し、1度に1つの電極を選択し、その容量を測定する。タッチの位置は、(1)最も有意な容量変化を経験するX-軸電極105、および、(2)最も有意な容量変化を経験するY-軸電極104の近接性によって決定される。

【0006】

全X-軸およびY-軸電極上で自己容量測定を行うことは、合理的高速システム応答時間 10 を提供する。しかしながら、多重タッチスクリーンシステムにおいて要求されるような複数の同時(X, Y)座標の追跡をサポートしない。例えば、16×16電極グリッドでは、位置(1, 5)における1つのオブジェクトと、位置(4, 10)における第2のオブジェクトとによる同時タッチは、4つの可能なタッチ場所：(1, 5)、(1, 10)、(4, 5)、および(4, 10)につながる。自己容量システムは、X-軸電極1および4がタッチされ、Y-軸電極5および10がタッチされたことを決定することが可能であるが、4つの可能な場所のうちのどの2つが実際のタッチ位置を表すかを決定するために曖昧さを取り除くことは可能ではない。

【0007】

多重タッチスクリーンでは、相互容量測定が、1つ以上のオブジェクトによる同時タッチを検出するために使用され得る。X-Yグリッドタッチスクリーンでは、例えば、相互容量は、X-軸電極とY-軸電極との間の容量結合を指し得る。タッチスクリーン上の電極の1つの組は、受信機としての役割を果たし得、他のセット内の電極は、送信機としての役割を果たし得る。送信機電極上の駆動信号は、受信機電極上で行われる容量測定値を変え得る。なぜなら、2つの電極は、それらの間の相互容量を通して結合されるからである。このように、相互容量は、タッチセンサ上のX-Y近接性関係(ノード)毎に効果的に対処することができるため、相互容量測定は、自己容量と関連付けられた曖昧さ問題に遭遇し得ない。

【0008】

より具体的には、相互容量測定を使用する多重タッチコントローラは、電極の第1の組内の1つの電極を受信機として選択し得る。コントローラは、次いで、電極の第2の組内の送信機電極毎に相互容量を(1つずつ)測定し得る。コントローラは、電極の第1の組の各々が受信機として選択されるまで、本プロセスを繰り返し得る。1つ以上のタッチの位置は、最も有意な容量変化を経験する、それらの相互容量ノード、例えば、ノード120によって決定され得る。自己および相互容量式タッチ検出を備えている、投影容量式タッチ技術は、www.microchip.comにおいて利用可能なTodd O'Connnorによる「mTouch™ Projected Capacitive Touch Screen Sensing Theory of Operations」と題されたTechnical Bulletin TB3064、およびJerry Hanauerによる「Capacitive Touch System Using Both Self and Mutual Capacitance」と題された共有に係る米国特許出願公開第US2012/0113047号により完全に説明されており、両方とも、あらゆる目的のために、参照することによって本明細書に組み込まれる。

【0009】

自己容量値および相互容量値は、電極の自己ならびに相互容量に対して電圧を充電または放電することによって決定され得る。例えば、容量式分圧器(CVD)法では、容量値は、最初に、電極コンデンサ上に貯蔵された電圧を測定し、次いで、放電される既知の値のコンデンサを電極コンデンサと並列に結合し、続いて、結果として生じる平衡電圧を測定するか、または、既知の値のコンデンサを充電し、それを放電される電極コンデンサに結合することによって決定され得る。CVD法は、www.microchip.com

10

20

30

40

50

において利用可能なアプリケーションノートAN1208により完全に説明されており、CVD法のより詳細な説明は、Dieter Peterによる「Capacitive Touch Sensing using an Internal Capacitor of an Analog-To-Digital Converter (ADC) and a Voltage Reference」と題された共有に係る米国特許出願公開第US2010/0181180号(特許文献1)に提示されており、両方とも、あらゆる目的のために、参照することによって本明細書に組み込まれる。

#### 【0010】

充電時間測定ユニット(CTMU)を使用して、電極容量の非常に正確な容量測定が、一定電流源を用いて、電極コンデンサを充電または放電し、次いで、正確に測定された期間後、電極コンデンサ上に結果として生じる電圧を測定することによって、得られ得る。CTMU法は、www.microchip.comにおいて利用可能なMicrochipアプリケーションノートAN1250およびAN1375、ならびに両方ともJames E. Bartlingによる「Measuring a long time period」と題された共有に係る米国特許第US7,460,441B2号(特許文献2)および「Current-time digital-to-analog converter」と題された第US7,764,213B2号(特許文献3)により完全に説明されており、それらは全て、あらゆる目的のために、参照することによって本明細書に組み込まれる。

#### 【0011】

容量Cに対する電荷Qは、式： $Q = C * V$ に従って、容量Cに対する電圧Vに正比例する。したがって、コンデンサを充電または放電するために利用可能な電圧が大きいほど、電極の自己および相互容量の容量値を決定する際の分解能がより優れている。加えて、雑音は、概して、電極が、それに対する雑音の拾い上げを低減させるために遮蔽され得る、一定インパルスまたは交流(AC)電圧であるので、容量をより高い(大きい)電圧で充電および放電する能力はまた、容量検出回路の信号/雑音比を改良する。しかしながら、電源、例えば、バッテリからの電圧は、集積回路デバイスによって、電力を節約するために減らされている。したがって、より高い電圧の利用可能性は、減少している。

#### 【先行技術文献】

##### 【特許文献】

##### 【0012】

【特許文献1】米国特許出願公開第2010/0181180号明細書

【特許文献2】米国特許第7,460,441号明細書

【特許文献3】米国特許第7,764,213号明細書

#### 【発明の概要】

#### 【課題を解決するための手段】

##### 【0013】

したがって、その容量値を決定する際にタッチスクリーンまたはパネルの充電要素のために使用され得る、良好に調整されたより高い出力電圧を有する電圧源を提供する、統合的解決策の必要性がある。

##### 【0014】

ある実施形態によると、高電圧を発生させ、高電圧を複数のノードに選択的に結合するための装置は、高電圧出力を有する電圧ブースト回路と、電圧ブースト回路に結合されている電圧基準と、各々が電圧ブースト回路の高電圧出力に結合されている高電圧入力と独立して制御可能な高電圧出力とを有する複数の電圧レベルシフタ/ドライバと、複数の電圧レベルシフタ/ドライバに結合されている論理回路であって、その高電圧出力を制御する論理回路と、論理回路および電圧ブースト回路に結合されているシリアル/パラレルインターフェースとを備え得る。

##### 【0015】

さらなる実施形態によると、パワーオンリセット(POR)回路が、電圧ブースト回路

10

20

30

40

50

およびシリアル／パラレルインターフェースに結合され得る。さらなる実施形態によると、ソフトスタート回路が、電圧ブースト回路に結合され得る。さらなる実施形態によると、論理回路は、複数のANDゲートであり得る。さらなる実施形態によると、出力イネーブル制御が、複数のANDゲートの各々の入力に結合され得る。さらなる実施形態によると、高電圧出力コンデンサが、電圧ブースト回路の出力と電源コモンとの間に結合され得る。さらなる実施形態によると、ブーストインダクタが、電圧ブースト回路への電力入力と電源との間に結合され得る。さらなる実施形態によると、複数の電圧レベルシフタ／ドライバの出力は、トライステートであり、電源コモン、高電圧出力、または高オフ抵抗において選択可能出力状態を有し得る。

【0016】

10

さらなる実施形態によると、シリアル／パラレルインターフェースはさらに、構成レジスタおよびデータ記憶レジスタを備え得、構成レジスタは、電圧ブースト回路のパラメータを記憶し、データ記憶レジスタは、複数の電圧レベルシフタ／ドライバの出力状態を記憶する。さらなる実施形態によると、ソフトスタートの間、複数の電圧レベルシフタ／ドライバの出力は、ディスエーブルにされ得る。さらなる実施形態によると、電圧ブースト回路、電圧基準、複数の電圧レベルシフタ／ドライバ、論理回路、およびシリアル／パラレルインターフェースは、单一集積回路デバイス内に提供され得る。さらなる実施形態によると、複数の電圧レベルシフタ／ドライバの論理回路および入力回路は、低電圧ならびに低電力デバイスを備え得る。さらなる実施形態によると、複数の電圧レベルシフタ／ドライバの出力回路は、低インピーダンス駆動能力を有する高電圧デバイスを備え得る。

【0017】

20

別の実施形態によると、タッチの場所を決定し、投影容量式タッチ感知表面上のタッチを検出するためのシステムは、第1の軸を有する並列配向に配列された第1の複数の電極であって、各々は、自己容量を備え得る、第1の複数の電極と、第1の軸に実質的に垂直な第2の軸を有する並列配向に配列された第2の複数の電極であって、第1の複数の電極は、第2の複数の電極の上に位置し、第1の複数の電極と第2の複数の電極との重複交差点を備え得る複数のノードを形成し得、複数のノードの各々は、相互容量を備え得る、第2の複数の電極と、高電圧ジェネレータ／ドライバであって、高電圧出力を有する電圧ブースト回路と、電圧ブースト回路に結合されている電圧基準と、各々が電圧ブースト回路の高電圧出力に結合されている高電圧入力と第1および第2の複数の電極のうちのそれぞれの1つに結合されている独立して制御可能な高電圧出力とを有する複数の電圧レベルシフタ／ドライバと、複数の電圧レベルシフタ／ドライバに結合されている論理回路であって、その高電圧出力を制御する論理回路と、論理回路および電圧ブースト回路に結合されているシリアル／パラレルインターフェースとを備え得る高電圧ジェネレータ／ドライバと、混合信号デバイスであって、第1および第2の複数の電極のうちのそれぞれの1つに結合されている複数のアナログ入力を有する容量式タッチアナログフロントエンドと、容量式タッチフロントエンドに結合されているアナログ／デジタルコンバータ(ADC)と、デジタルプロセッサおよびメモリであって、ADCからの少なくとも1つの出力は、デジタルプロセッサに結合され得る、デジタルプロセッサおよびメモリと、デジタルプロセッサおよび高電圧ジェネレータ／ドライバのシリアル／パラレルインターフェースに結合されているシリアルインターフェースとを備え得る混合信号デバイスとを備え得、自己容量の値は、アナログフロントエンドによって、第1の複数の電極の各々に対して、高電圧を使用して測定され得、測定された自己容量の値は、メモリ内に記憶され、自己容量の最大値のうちの少なくとも1つを有する第1の電極のうちの少なくとも1つのノードの相互容量の値は、アナログフロントエンドによって、高電圧を使用して測定され得、測定された相互容量の値は、メモリ内に記憶され得、デジタルプロセッサは、タッチの場所ならびにタッチ感知表面に加えられたそれぞれの力を決定するために、記憶された自己容量値および相互容量値を使用する。

【0018】

さらなる実施形態によると、混合信号デバイスは、混合信号マイクロコントローラ集積

30

40

50

回路であり得る。さらなる実施形態によると、高電圧ジェネレータ／ドライバは、集積回路を備え得る。さらなる実施形態によると、高電圧は、高電圧ジェネレータ／ドライバおよび混合信号デバイスに給電する供給電圧を上回り得る。

【0019】

さらに別の実施形態によると、投影容量式タッチ感知表面の信号／雑音性能を改良する方法は、第1の軸を有する並列配向に配列された第1の複数の電極を提供するステップであって、第1の複数の電極の各々は、自己容量を備え得る、ステップと、第1の軸に実質的に垂直な第2の軸を有する並列配向に配列された第2の複数の電極を提供するステップであって、第1の複数の電極は、第2の複数の電極の上に位置し、第1の複数の電極と第2の複数の電極との重複交差点を備え得る、複数のノードを形成し得、複数のノードの各々は、相互容量を備え得る、ステップと、第1の複数の電極を電源電圧より大きい電圧に充電するステップと、第2の複数の電極を電源コモンに放電するステップと、その自己容量の値を決定するために、第1の複数の電極を走査するステップと、走査された自己容量の値を比較し、第1の複数の電極のうちのどれが自己容量の最大値を有するかを決定するステップと、それぞれの複数のノードの相互容量の値を決定するために、自己容量の最大値を有する第1の複数の電極の1つのノードを走査するステップと、自己容量の最大値を有する第1の電極上のそれぞれの複数のノードの走査された相互容量の値を比較するステップであって、相互容量の最大値を有するノードは、タッチ感知表面上のタッチの場所であり得る、ステップとを含み得る。

【0020】

本方法のさらなる実施形態によると、自己容量値および相互容量値は、アナログフロントエンドならびにアナログ／デジタルコンバータ（A D C）を用いて測定され得る。本方法のさらなる実施形態によると、自己容量値および相互容量値は、デジタルプロセッサのメモリ内に記憶され得る。本方法のさらなる実施形態によると、自己容量値および相互容量値は、容量式分圧器法によって決定され得る。本方法のさらなる実施形態によると、自己容量値および相互容量値は、充電時間測定ユニットを用いて決定され得る。

本発明は、例えば、以下を提供する。

(項目1)

高電圧を発生させ、前記高電圧を複数のノードに選択的に結合するための装置であって、

高電圧出力を有する電圧ブースト回路と、

前記電圧ブースト回路に結合されている電圧基準と、

複数の電圧レベルシフタ／ドライバであって、各々は、前記電圧ブースト回路の高電圧出力に結合されている高電圧入力と、独立して制御可能な高電圧出力とを有する、複数の電圧レベルシフタ／ドライバと、

前記複数の電圧レベルシフタ／ドライバに結合されている論理回路であって、前記論理回路は、前記複数の電圧レベルシフタ／ドライバの前記高電圧出力を制御する、論理回路と、

前記論理回路および前記電圧ブースト回路に結合されているシリアル／パラレルインターフェースと

を備えている、装置。

(項目2)

前記電圧ブースト回路および前記シリアル／パラレルインターフェースに結合されているパワーオンリセット（P O R）回路をさらに備えている、項目1に記載の装置。

(項目3)

前記電圧ブースト回路に結合されているソフトスタート回路をさらに備えている、項目1に記載の装置。

(項目4)

前記論理回路は、複数のA N Dゲートである、項目1に記載の装置。

(項目5)

10

20

30

40

50

出力イネーブル制御が、前記複数のANDゲートの各々の入力に結合されている、項目4に記載の装置。

(項目6)

高電圧出力コンデンサが、前記電圧ブースト回路の出力と電源コモンとの間に結合されている、項目1に記載の装置。

(項目7)

ブーストイソダクタが、前記電圧ブースト回路への電力入力と電源との間に結合されている、項目1に記載の装置。

(項目8)

前記複数の電圧レベルシフタ/ドライバの前記出力は、トライステートであり、電源コモン、前記高電圧出力、または高オフ抵抗において選択可能出力状態を有する、項目1に記載の装置。

10

(項目9)

前記シリアル/パラレルインターフェースは、構成レジスタおよびデータ記憶レジスタをさらに備え、前記構成レジスタは、前記電圧ブースト回路のパラメータを記憶し、前記データ記憶レジスタは、前記複数の電圧レベルシフタ/ドライバの出力状態を記憶している、項目1に記載の装置。

(項目10)

ソフトスタートの間、前記複数の電圧レベルシフタ/ドライバの出力は、ディスエーブルにされている、項目1に記載の装置。

20

(項目11)

前記電圧ブースト回路、前記電圧基準、前記複数の電圧レベルシフタ/ドライバ、前記論理回路、および前記シリアル/パラレルインターフェースは、单一集積回路デバイス内に提供されている、項目1に記載の装置。

(項目12)

前記複数の電圧レベルシフタ/ドライバの論理回路および入力回路は、低電圧および低電力デバイスを備えている、項目1に記載の装置。

(項目13)

前記複数の電圧レベルシフタ/ドライバの出力回路は、低インピーダンス駆動能力を有する高電圧デバイスを備えている、項目1に記載の装置。

30

(項目14)

タッチの場所を決定し、投影容量式タッチ感知表面上のタッチを検出するためのシステムであって、

第1の軸を有する並列配向に配列された第1の複数の電極であって、前記第1の複数の電極の各々は、自己容量を備えている、第1の複数の電極と、

前記第1の軸に実質的に垂直な第2の軸を有する並列配向に配列された第2の複数の電極であって、前記第1の複数の電極は、前記第2の複数の電極の上に位置し、前記第1の複数の電極と第2の複数の電極との重複交差点を備えている複数のノードを形成し、前記複数のノードの各々は、相互容量を備えている、第2の複数の電極と、

高電圧ジェネレータ/ドライバであって、

40

高電圧出力を有する電圧ブースト回路と、

前記電圧ブースト回路に結合されている電圧基準と、

複数の電圧レベルシフタ/ドライバであって、各々は、前記電圧ブースト回路の高電圧出力に結合されている高電圧入力と、前記第1および第2の複数の電極のうちのそれぞれの1つに結合されている独立して制御可能な高電圧出力とを有する、複数の電圧レベルシフタ/ドライバと、

前記複数の電圧レベルシフタ/ドライバに結合されている論理回路であって、前記論理回路は、前記複数の電圧レベルシフタ/ドライバの高電圧出力を制御する、論理回路と、

前記論理回路および前記電圧ブースト回路に結合されているシリアル/パラレルイン

50

ターフェースとを備えている、高電圧ジェネレータ／ドライバと、混合信号デバイスであって、前記第1および第2の複数の電極のうちのそれぞれの1つに結合されている複数のアナログ入力を有する容量式タッチアナログフロントエンドと、前記容量式タッチフロントエンドに結合されているアナログ／デジタルコンバータ（A D C）と、デジタルプロセッサおよびメモリであって、前記A D Cからの少なくとも1つの出力が、前記デジタルプロセッサに結合されている、デジタルプロセッサおよびメモリと、前記デジタルプロセッサと前記高電圧ジェネレータ／ドライバの前記シリアル／パラレルインターフェースとに結合されているシリアルインターフェースとを備えている、混合信号デバイスとを備え、前記自己容量の値は、前記アナログフロントエンドによって、前記第1の複数の電極の各々に対して前記高電圧を使用して測定され、前記測定された自己容量の値は、前記メモリ内に記憶され、前記自己容量の最大値のうちの少なくとも1つを有する前記第1の電極のうちの少なくとも1つのノードの相互容量の値は、前記アナログフロントエンドによって、前記高電圧を使用して測定され、前記測定された相互容量の値は、前記メモリ内に記憶され、前記デジタルプロセッサは、前記記憶された自己容量値および相互容量値を使用して、前記タッチの場所および前記タッチ感知表面に加えられたそれぞれの力を決定する

10

シス テ ム。（項目15）前記混合信号デバイスは、混合信号マイクロコントローラ集積回路である、項目14に記載のシステム。（項目16）前記高電圧ジェネレータ／ドライバは、集積回路を備えている、項目14に記載のシステム。（項目17）前記高電圧は、前記高電圧ジェネレータ／ドライバおよび前記混合信号デバイスに給電する供給電圧より大きい、項目14に記載のシステム。

20

（項目18）投影容量式タッチ感知表面の信号／雑音性能を改良する方法であって、前記方法は、第1の軸を有する並列配向に配列された第1の複数の電極を提供するステップであって、前記第1の複数の電極の各々は、自己容量を備えている、ステップと、前記第1の軸に実質的に垂直な第2の軸を有する並列配向に配列された第2の複数の電極提供するステップであって、前記第1の複数の電極は、前記第2の複数の電極の上に位置し、前記第1の複数の電極と第2の複数の電極との重複交差点を備えている複数のノードを形成し、前記複数のノードの各々は、相互容量を備えている、ステップと、前記第1の複数の電極を電源電圧より大きい電圧に充電するステップと、

30

前記第2の複数の電極を電源コモンに放電するステップと、前記第1の複数の電極を走査し、前記第1の複数の電極の自己容量の値を決定するステップと、前記走査された自己容量の値を比較し、前記第1の複数の電極のうちのどれが前記自己容量の最大値を有するかを決定するステップと、前記自己容量の最大値を有する前記第1の複数の電極のうちの1つの複数のノードを走査し、それぞれの複数のノードの相互容量の値を決定するステップと、前記自己容量の最大値を有する第1の電極上のそれぞれの複数のノードの走査された相互容量の値を比較するステップであって、前記相互容量の最大値を有するノードは、前記タッチ感知表面上のタッチの場所である、ステップと

40

50

を含む、方法。

(項目 19)

前記自己容量値および相互容量値は、アナログフロントエンドおよびアナログ／デジタルコンバータ（A D C）を用いて測定される、項目 18 に記載の方法。

(項目 20)

前記自己容量値および相互容量値は、デジタルプロセッサのメモリ内に記憶される、項目 19 に記載の方法。

(項目 21)

前記自己容量値および相互容量値は、容量式分圧器法によって決定される、項目 19 に記載の方法。

10

(項目 22)

前記自己容量値および相互容量値は、充電時間測定ユニットを用いて決定される、項目 19 に記載の方法。

【図面の簡単な説明】

【0021】

本開示のより完全な理解は、付随の図面と関連して検討される以下の説明を参考することによって得られ得る。

【図 1】図 1 は、本開示の教示による、X - Y グリッド配向に配列されるタッチセンサ電極の基本構想図を図示する。

20

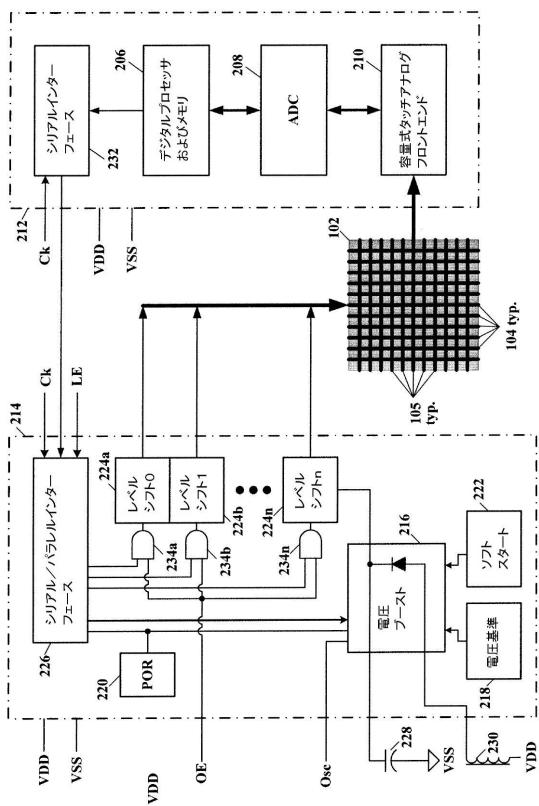

【図 2】図 2 は、本開示の具体的例示的実施形態による、投影容量式タッチスクリーンまたはパネルと、高電圧源／ドライバと、混合信号デバイスとを有する、電子システムの概略ブロック図を図示する。

【発明を実施するための形態】

【0022】

本開示は、種々の修正および代替形態を受け得るが、その具体的例示的実施形態が、図面に図示され、本明細書に詳細に説明されている。しかしながら、具体的例示的実施形態の本明細書における説明は、本開示を本明細書に開示される特定の形態に限定することを意図するものではなく、対照的に、本開示は、添付の請求項によって定義される、あらゆる修正および均等物を網羅することを理解されたい。

【0023】

30

種々の実施形態によると、マイクロコントローラによって制御される複数の投影容量式タッチ要素に結合するために、調整式高電圧源および高電圧／電流ドライバを提供するための統合的解決策が、本明細書に開示される。単一集積回路高電圧ジェネレータ／ドライバは、電圧ブースト回路と、電圧基準と、パワーオンリセット（P O R）と、ソフトスタートと、複数の低入力電流電圧レベルシフタと、投影容量式タッチスクリーンおよびパネルの使用に関連する全機能を制御し得るマイクロコントローラに結合するためのシリアルインターフェースとを備え得る。前述の高電圧ジェネレータ／ドライバはまた、例えば、限定ではないが、真空蛍光ディスプレイ（V F D）、有機発光ダイオード（O L E D）ディスプレイ等の高電圧低電力ディスプレイを駆動するために使用され得ることも想定され、かつ本開示の範囲内である。

40

【0024】

ここで図面を参照すると、具体的例示的実施形態の詳細が、図式的に図示される。図面中の同一要素は、同一番号で表され、類似要素は、異なる小文字の添え字を伴う、同一番号によって表されるであろう。

【0025】

図 2 を参照すると、描寫されるのは、本開示の具体的例示的実施形態による、投影容量式タッチスクリーンまたはパネルと、高電圧源／ドライバと、混合信号デバイスとを有する、電子システムの概略ブロック図である。混合信号デバイス 212 は、容量式タッチアナログフロントエンド 210 と、アナログ／デジタルコンバータ 208 と、デジタルプロセッサおよびメモリ 206 と、シリアルインターフェース 232 とを備え得る。高電圧ジ

50

エネレータ / ドライバ 214 は、電圧ブースト回路 216 と、電圧基準 218 と、パワー オンリセット (P O R) 220 と、ソフトスタート回路 222 と、複数の電圧レベルシフタ 224 と、レベルシフタ 224 から電極 104 および 105 への駆動を制御するための制御論理 234 と、レベルシフタの制御を混合信号デバイス 212 内のシリアルインターフェース 232 に結合するためのシリアル / パラレルインターフェース 226 とを備え得る。P O R 220 は、電源投入起動中、高電圧ジェネレータ / ドライバ 214 内の全メモリ (記憶) 要素を初期化するために使用され得る。

## 【 0026 】

混合信号デバイス 212 のアナログフロントエンド 210 と、高電圧ジェネレータ / ドライバ 214 とは、マトリクスで配列される複数の伝導性列 104 および行 105 から成るタッチスクリーンまたはパネル 102 に結合され得る。伝導性行 105 および / または伝導性列 104 が、クリア基板、例えば、ディスプレイ / タッチスクリーン等上の印刷回路基板導体、ワイヤ、インジウムスズ酸化物 (I T O) コーティング、または任意のそれらの組み合わせであることが想定され、かつ本開示の範囲である。混合信号デバイス 212 は、パッケージ化されて、またはパッケージ化されずに、1 つ以上の集積回路内に提供される、マイクロコントローラ、デジタル信号プロセッサ、特定用途向け集積回路 (A S I C)、プログラマブル論理アレイ (P L A) 等を備え得る (図示せず)。高電圧ジェネレータ / ドライバ 214 は、パッケージ化されて、またはパッケージ化されずに、単一集積回路内に提供され得る (図示せず)。

## 【 0027 】

電圧ブースト回路 216 は、外部容量 228 およびインダクタンス 230 と組み合わせて変調入力信号 (O s c) を使用して、電源 V D D から高電圧 (H V) を発生させる。電圧基準 218 は、電圧ブースト回路 216 から発生される H V がタッチスクリーンまたはパネル 102 の動作全体を通して実質的に同一電圧のままであるように、一定基準電圧を電圧ブースト回路 216 に提供し得る。電圧ブースト回路 216 はさらに、電流制限を組み込み得る。電圧ブースト回路 216 は、例えば、限定ではないが、集積回路電力供給源の設計技術における当業者に周知のスイッチモードブースト電力回路であり得る。電圧ブースト回路 216 からの H V 出力は、レベルシフタ 224 に結合され、A N D ゲート 234 は、電極 104 および 105 に結合され得る、レベルシフタ 224 の H V 駆動出力を制御する。出力イネーブル O E は、群としてレベルシフタ 224 の出力をイネーブル / ディスエーブルするために使用され得、個々のレベルシフタ 224 の出力は、A N D ゲート 234 を通して、シリアル / パラレルインターフェース 226 内のシフトレジスタの記憶されたコンテンツによって制御され得る。他の論理設計が、A N D ゲートの代わりに、同等の有効性を伴って使用され得、デジタル論理設計の当業者および本開示の利益を有する者は、その方法を容易に理解するであろうことが想定され、かつ本開示の範囲である。レベルシフタ 224 の論理回路 (例えば、A N D ゲート 234) および入力回路は、低電圧および高インピーダンス回路を備え、電力を節約し得、レベルシフタ 224 の出力回路は、低インピーダンスを有する高電圧 / 電流出力回路および構成要素 (図示せず) を備え、電極コンデンサを高電圧に急充電し得る。

## 【 0028 】

シリアル / パラレルインターフェース 226 は、例えば、限定ではないが、産業標準的シフトレジスタとラッチタイプシリアルインターフェース (S P I) 等であり得る。シリアル / パラレルインターフェース 226 は、それらの間の制御バスを通して電圧ブースト回路 216 のパラメータを構成することと、例えば、A N D ゲート 234 およびレベルシフタ 224 を通して、アクティブ出力チャネルを選択することとを行うために使用され得る。ラッチャイネーブル (L E) 入力を使用して所望のデータをラッチするステップに先立って、シリアルインターフェース 232 からのクロックおよびシリアルデータストリームが、シリアル / パラレルインターフェース 226 内のシフトレジスタ (図示せず) を構成するために使用され得る。データは、最上位ビット (M S B) を最初または最後としてシフトされ得る。構成ワードまたはデータワードのいずれかが、シリアル / パラレルインタ

10

20

30

40

50

フェース 2 2 6 内でクロックおよびラッチされ得る。データワードは、各レベルシフタドライバ 2 2 4 の出力状態を選択する。ユーザモードでは、構成ワードは、電圧ブースト回路 2 1 6 のブースト電圧および電流制限パラメータを選択し得る。

〔 0 0 2 9 〕

ソフトスタート回路 222 は、電圧ブースト回路 216 に結合され得る。ソフトスタート回路 222 は、高初期突入電流が電源 VDD をプルダウンし、ブラウンアウト状態を生じさせることを防止するために使用され得る。例えば、電圧ブースト回路 216 がイネーブルにされてから最初の 10 ~ 50 ミリ秒間、回路 216 のスイッチングトランジスタの最小セクションのみ、アクティブとなり得、電流は、例えば、最大 200 ミリアンペア（公称）に制限され得る。レベルシフタ 224 の出力はまた、この時間の間、トライステートにされ得る。ソフトスタートがタイムアウトになった後、電流制限およびスイッチングトランジスタ設定は、構成ワードによって選択された通常動作値に戻る。ソフトスタートはまた、完全にディスエーブルにされ得る。ソフトスタートの間の電流制限は、ディスエーブルにされ得る。スイッチングトランジスタの最小セクションが、選択され、その出力は、トライステートにされるが、電流制限回路は、アクティブではない。

10

[ 0 0 3 0 ]

本開示の実施形態が、描写され、説明され、本開示の例示的実施形態を参照することによって定義されるが、そのような参照は、本開示の限定を含意するものではなく、そのような限定が、推測されるべきではない。開示される主題は、それらの当業者および本開示の利益を有する者に想起されるであろうように、形態および機能における多数の修正、改変、ならびに均等物が可能である。本開示の描写および説明される実施形態は、実施例にすぎず、本開示の範囲の包括ではない。

30

〔図 1 〕

Figure 1

【図2】

Figure 2

---

フロントページの続き

(72)発明者 シャーマ， アトマ

アメリカ合衆国 アリゾナ 85224， チャンドラー， ノース コロナド ストリート 7

00， ナンバー 1054

(72)発明者 ウォルトン， コリー

アメリカ合衆国 アリゾナ 85226， チャンドラー， ウエスト ラード ストリート

3834

(72)発明者 ハノーアー， ジェリー

アメリカ合衆国 ウィスコンシン 53022， ジャーマンタウン， カウントリー ポート，

ノース 103 ウエスト 16737

審査官 円子 英紀

(56)参考文献 米国特許出願公開第2013/0265277(US, A1)

特表2010-515969(JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 3 / 041

G 06 F 3 / 044